(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-103655

(P2011-103655A)

(43) 公開日 平成23年5月26日(2011.5.26)

(51) Int.Cl.

HO3F 1/02 (2006.01)

F 1

HO3F 1/02

テーマコード(参考)

5J500

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 12 頁)

(21) 出願番号 特願2010-251003 (P2010-251003)

(22) 出願日 平成22年11月9日 (2010.11.9)

(31) 優先権主張番号 0905399

(32) 優先日 平成21年11月10日 (2009.11.10)

(33) 優先権主張国 フランス (FR)

(71) 出願人 505157485

テールズ

フランス 92200 ノイリーシューレーセーヌ リュー ドゥ ヴィリエール 45

(74) 代理人 100071054

弁理士 木村 高久

(72) 発明者 プチ、ヴァンサン

フランス、78550 バゼンヴィル、プラス サン ルイ、1

(72) 発明者 ルイ、ブルーノ

フランス、94100 サン モール、エ パス デ パンソン、1

最終頁に続く

(54) 【発明の名称】入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システム

## (57) 【要約】

【課題】 入力信号の電力増幅用回路及びそのような回路を組み込んでいる信号発信システムを提供する。

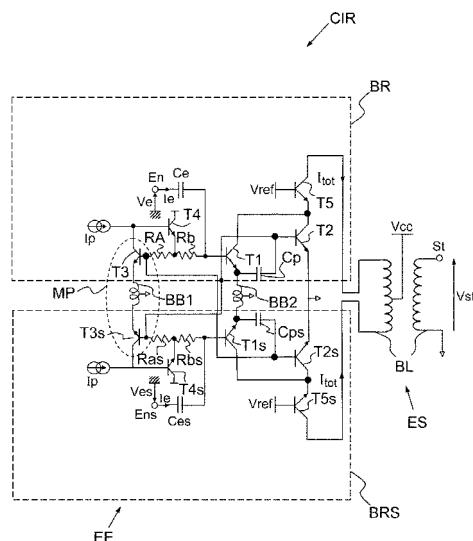

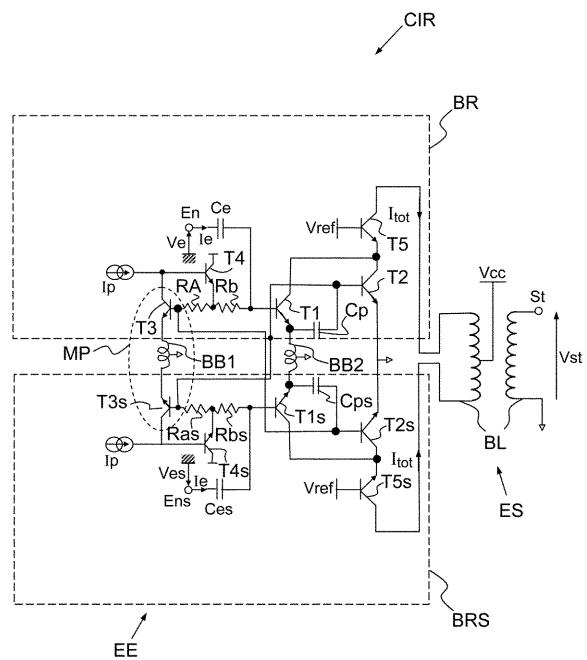

【解決手段】 本発明は、入力段 (EE) 及び出力段 (ES) を含む入力信号の電力増幅用回路 (CIR) に関し、前記入力段 (EE) は：

いわゆる主駆動トランジスタ (T3) を組み込んでいる駆動手段 (MP) と、

入力信号を受信可能で、主駆動トランジスタ (T3) と共に電流ミラーとして組み立てられた、第1のいわゆる主入力トランジスタ (T1) とを備える。

第1の主入力トランジスタ (T1) は、入力段 (EE) 内へ組み込まれた第2のいわゆる主入力トランジスタ (T2) を介して出力段 (ES) に連結され、かつ駆動手段 (MP) によって制御され、第1の主入力トランジスタ (T1) と第2の主入力トランジスタ (T2) は相互に連結され、かつ共振回路 (BB2, Cp) を経由して Darlington 型の構造に従ってアースに連結される。

【選択図】 図1

図1

**【特許請求の範囲】****【請求項 1】**

入力段 ( E E ) 及び出力段 ( E S ) を含む入力信号の電力増幅用回路 ( C I R ) であつて、前記入力段 ( E E ) が：

いわゆる主駆動トランジスタ ( T 3 ) を組み込んでいる駆動手段 ( M P ) と、

入力信号を受信可能で、主駆動トランジスタ ( T 3 ) と共に電流ミラーとして組み立てられた、第 1 のいわゆる主入力トランジスタ ( T 1 ) と

を備える、回路 ( C I R ) において、

第 1 の主入力トランジスタ ( T 1 ) が、入力段 ( E E ) 内へ組み込まれた第 2 のいわゆる主入力トランジスタ ( T 2 ) を介して出力段 ( E S ) に連結され、かつ駆動手段 ( M P ) によって制御され、第 1 の主入力トランジスタ ( T 1 ) と第 2 の主入力トランジスタ ( T 2 ) が相互に連結され、かつ共振回路 ( B B 2 , C p ) を経由して D a r l i n g t o n 型の構造に従いアースに連結されるという事実によって特徴付けられる回路 ( C I R )

。

10

**【請求項 2】**

第 1 の主入力トランジスタ ( T 1 ) と第 2 の主入力トランジスタ ( T 2 ) が、ある誤差内で等価な振幅の電流が通るように構成される、請求項 1 に記載の回路。

**【請求項 3】**

前記入力信号が単純なタイプであり、前記第 2 の主トランジスタが主駆動トランジスタ ( T 3 ) により制御される、請求項 1 または 2 のいずれか一項に記載の回路。

20

**【請求項 4】**

前記入力信号が差動タイプであり、入力段 ( E E ) がさらに：

前記駆動手段 ( M P ) 内に組み込まれた、いわゆる補助駆動トランジスタ ( T 3 s ) と

、

第 1 のいわゆる補助入力トランジスタ ( T 1 s ) と、

第 2 のいわゆる補助入力トランジスタ ( T 2 s ) と

を備え、各々のいわゆる補助素子が、対応するいわゆる主素子に対して対称に組み立てられる、請求項 1 または 2 のいずれか一項に記載の回路。

20

**【請求項 5】**

第 2 の主入力トランジスタ ( T 2 ) が主駆動トランジスタ ( T 3 ) により制御され、第 2 の補助入力トランジスタ ( T 2 s ) が補助駆動トランジスタにより制御される、請求項 4 に記載の回路。

30

**【請求項 6】**

第 2 の主入力トランジスタ ( T 2 ) が補助駆動トランジスタ ( T 3 s ) により制御され、第 2 の補助入力トランジスタ ( T 2 s ) が主駆動トランジスタ ( T 3 ) により制御される、請求項 4 に記載の回路。

40

**【請求項 7】**

第 1 の補助入力トランジスタ ( T 1 s ) と第 2 の補助入力トランジスタ ( T 2 s ) が、ある誤差内で等価な振幅の電流が通るように構成される、請求項 4 ~ 6 のいずれか一項に記載の回路。

40

**【請求項 8】**

さらにシリコン上に作られる、請求項 1 ~ 7 のいずれか一項に記載の回路。

**【請求項 9】**

請求項 1 ~ 8 のいずれか一項に記載の回路を組み込むという事実により特徴付けられる、信号発信 / 送信システム。

**【請求項 10】**

請求項 9 に記載の信号発信 / 送信システムの、レーダー内における使用。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

50

本発明は、特にシリコン上に作られ、周波数がX帯域（従来8～12GHzの間）にある信号を処理可能な、電力增幅回路に関する。

【背景技術】

【0002】

これらの回路は、例えばレーダー内に組み込まれるもののような、能動的送信／受信モジュールにおいて使用され得る。より正確には、これらのモジュールは、受信した信号又は送信されるべき信号を移相及び減衰あるいは増幅できるマイクロチップを含む。増幅機能は、理想的には送信／受信チェーンの良好な線形性を保証する一方で、要求される必要な電力を提供可能でなければならない増幅回路により実行される。

【0003】

理想的な増幅回路は特に：

出力において必要とされる電力レベルを備え、

上流で連結された他の回路を出来る限り妨害せず、

意図される用途のために十分に線形であり、

出力ゲインの制御を可能にしなければならず、

これら全てを出来る限り最小の電力消費で行うことが必須である。

【0004】

増幅回路はとりわけ、その入力インピーダンス、そのゲイン、及びその遷移周波数により定義される。

【0005】

回路の動作が最適であるためには、増幅ゲインの最大且つ制御された値から恩恵を受けるように、それが線形動作領域内で機能することが望ましい。

【0006】

この線形動作領域は、0と遷移周波数F<sub>t</sub>との間にある周波数により形成される。後者は：

$$F_t = F_c \times G_{max}$$

により定義される。

ここで、

F<sub>t</sub>は遷移周波数、

F<sub>c</sub>は遮断周波数、

G<sub>max</sub>は増幅回路の電流について、ゲインによってとられ得る最大値である。

【0007】

最大出力を供給できるようにするには、それに対してゲインが最大値をとる周波数値において、すなわち回路の線形動作領域内で機能することが必要である。

【0008】

これまでには、増幅回路において高いゲイン値で動作することは、とりわけ電流源（例えば電流ミラー）により自己バイアスをかけられたトランジスタの使用に関連し、そして共通エミッタ・モードで搭載される低い入力インピーダンスを意味する。

【0009】

（適切に選ばれた寸法のトランジスタのための）この構成において、入力インピーダンスは：

【数1】

$$Z_e = \frac{\beta}{2gm} \quad (1)$$

の形で表わされる。ここで、

Z<sub>e</sub>は増幅回路の入力インピーダンス、

10

20

30

40

50

は自己バイアスをかけられたトランジスタのゲインである。

【0010】

低い入力インピーダンスの不利な点は：

上流に配置された別の回路との連結に有害であり、

それが遷移周波数の値を低くし、その結果として増幅回路の線形動作領域の範囲を狭めることである。

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明の目的は特にこれらの問題を解決することである。 10

【課題を解決するための手段】

【0012】

このため、本発明の第1の態様によれば、入力段及び出力段を含む、入力信号の電力増幅用の回路が提案され、前記入力段は：

いわゆる主駆動トランジスタを組み込んでいる駆動手段と、

入力信号を受信可能で、主駆動トランジスタと共に電流ミラーとして組み立てられた、第1のいわゆる主入力トランジスタとを備える。

【0013】

本態様の全般的な特性によれば、第1の主入力トランジスタは、入力段の中へ組み込まれた第2のいわゆる主入力トランジスタを介して出力段に連結され、かつ駆動手段により制御され、第1の主入力トランジスタと第2の主入力トランジスタは相互に連結され、かつ共振回路を経由してDarlington型の構造に従ってアースに連結される。 20

【0014】

言い換えれば、回路の増幅機能を保持しながら、自己バイアスをかけられたトランジスタの構造は、とりわけDarlington型の構造で置き換える。

【0015】

本発明は従って回路の入力インピーダンスの値を増すことを可能にし、結果として遷移周波数の値を増すことを可能にする。線形の動作範囲は従って増加する。

【0016】

さらに、第1と第2の主トランジスタの連結に共振回路を使用するため、増幅回路は、周波数がX帯域内にある信号を処理できる。 30

【0017】

1つの実施形態によれば、第1と第2の主入力トランジスタは、ある誤差内で等価な振幅の電流が通るように構成され得る。

【0018】

例えば、前記入力信号は単純なタイプであってもよく、前記第2の主トランジスタは、そのとき主駆動トランジスタにより制御されている。

【0019】

1つの変形として、前記入力信号は差動タイプであり、その場合入力段は更に：

前記駆動手段内に組み込まれたいわゆる補助駆動トランジスタと、

第1のいわゆる補助入力トランジスタと、

第2のいわゆる補助入力トランジスタと

を備え、各々のいわゆる補助素子は、対応するいわゆる主素子に対して対称に組み立てられる。 40

【0020】

1つの実施形態によれば、第2の主入力トランジスタは主駆動トランジスタによって制御され得る。そして第2の補助入力トランジスタは補助駆動トランジスタによって制御され得る。

【0021】

1つの変形として、第2の主入力トランジスタは補助駆動トランジスタによって制御さ

50

れ得る。そして第2の補助入力トランジスタは主駆動トランジスタによって制御され得る。

**【0022】**

好ましくは第1と第2の補助入力トランジスタは、ある誤差内で等価な振幅の電流が通るように構成され得る。

**【0023】**

1つの実施形態において、回路はさらにシリコン上に作られ得る。

**【0024】**

本発明の別の態様によれば、上述のような回路を組み込んでいる信号の発信／送信システムが提案されている。

10

**【0025】**

本発明の別の態様によれば、上述の信号発信／送信システムの、レーダー内における使用が提案されている。

**【0026】**

本発明のその他の利点及び特徴は、本発明による全く制限されない実施形態の詳細な説明、及び本発明による1つの例示的な増幅回路が示されている1つの添付図を検討することにより、明らかになるであろう。

**【図面の簡単な説明】**

**【0027】**

**【図1】**本発明による1つの例示的な増幅回路を示す。

20

**【発明を実施するための形態】**

**【0028】**

1つの図がここで参照される。参照符号CIRは増幅回路を示す。

**【0029】**

増幅回路は、出力段ESに連結される入力段EEを含む。

**【0030】**

入力段はここで、以下により詳細に記述されるように、2つのコイルBB1及びBB2を介して相互に連結された、2つの対称な分枝BR及びBRSで形成される。

**【0031】**

差動タイプの入力信号が考えられるため、回路CIRは2つの分枝BR及びBRSを備える。単純なタイプの入力信号の場合、回路CIRは当然、2つの分枝のうちの1つだけで形成されるであろう。

30

**【0032】**

分枝BRを以下詳細に記述する。分枝BRの各々のいわゆる主素子に対し、分枝BRS内のいわゆる対称な補助素子が対応する。これらの補助素子の参照符号は、図に表わされるように添え字「s」を含む。記述を単純化するために、これから分枝BRのみが記述され、分枝BRSはそれに類似である。

**【0033】**

差動タイプの入力信号が考えられるので、バイアス電流Ipは、分枝BR及び分枝BRSの双方における入力段EEに入力として供給される。

40

**【0034】**

差動入力信号は、回路CIRの分枝BR及びBRSの入力端子En及びEnsにそれぞれ、差動電圧Ve、Vesの形で加えられる。より正確には、差動入力電圧は、Cp及びCpsの符号を付けられた2つのコンデンサを経由して、第1の主トランジスタT1及び第1の補助トランジスタT1sのそれぞれのベースに加えられる。

**【0035】**

バイアス電流Ipは、入力として主バイアス・トランジスタT3に、より正確にはそのコレクタに供給される。

**【0036】**

主バイアス・トランジスタT3は、第1の主トランジスタT1と共に電流ミラーとして

50

組み立てられる。言い換えれば、主バイアス・トランジスタ T 3 のベースは、ここで直列に組み立てられた 2 つの抵抗 R a 及び R b を経由して、第 1 の主トランジスタ T 1 のベースにつながれる。それらのそれぞれの値は、数 100 のオーダーであり得る。

【0037】

主バイアス・トランジスタ T 3 により伝達される駆動電流の損失を制限するために、トランジスタ T 4 はまた、バイアス電流 I p を供給する電流源と 2 つの抵抗 R a 及び R b に共通の分岐点との間に接続される。

【0038】

このトランジスタは、主バイアス・トランジスタ T 3 によって消散される電流の値に相当する値の、追加のいわゆるベース電流を供給する。

10

【0039】

主バイアス・トランジスタ T 3 のエミッタは、コイル B B 1 を経由して、補助バイアス・トランジスタ T 3 s のエミッタにつながれる。2 つのトランジスタ T 3 及び T 3 s は、駆動手段 M P を形成する。

【0040】

同様に、第 1 の主入力トランジスタ T 1 のエミッタは、コイル B B 2 を経由して第 1 の補助入力トランジスタ T 1 s のエミッタにつながれる。

20

【0041】

これらのコイル B B 1 及び B B 2 は、動作周波数において高インピーダンスを作り出すことにより、トランジスタ T 3 、T 3 s 、T 1 及び T 1 s をアースから切り離すことを可能にする。

【0042】

さらに、コイル B B 2 はコンデンサ C p と共に L C タイプの共振回路を形成し、この共振回路は、トランジスタ T 1 と T 2 を相互に連結し、白色の矢印の記号で表わされるアースと連結する。この共振回路は、周波数が X 帯域内にある信号を增幅回路が処理することを可能にする。

30

【0043】

より正確には、第 1 の主入力トランジスタ T 1 は第 2 の主入力トランジスタ T 2 と共に、当業者に良く知られた D a r l i n g t o n 型の構造に従って搭載される。言い換えれば、第 2 の主入力トランジスタ T 2 のコレクタは第 1 の主入力トランジスタ T 1 のコレクタと連結される。さらに、第 2 の主入力トランジスタ T 2 のベースは、コンデンサ C p を介して第 1 の主入力トランジスタ T 1 のエミッタと連結される。

30

【0044】

第 1 及び第 2 の主入力トランジスタは、ある誤差内で類似の値の電流がそれらを通るような方法で構成される。

【0045】

より正確には、本発明者らは（分枝 B R に対して）：

【数 2】

40

$$Z_e = \frac{V_e}{I_e}$$

を有し、ここで

Z e は増幅回路の分枝 B R の入力インピーダンス、

V e は入力電圧、

I e は入力電流である。

しかるに：

$$V_e = V_{be1} + V_{be2}$$

であり、ここで

50

$V_{be1}$  はトランジスタ T 1 のベース / エミッタ電圧、

$V_{be2}$  はトランジスタ T 2 のベース / エミッタ電圧

である。

## 【0046】

単純にするために、 $V_{be1} = V_{be2}$  と考える。そうすると：

$$V_e = 2 \times V_{be2}$$

となる。その結果：

## 【数3】

$$Z_e = \frac{2Vbe}{Ib} = \frac{2Vbe}{\underline{Ic}} = \frac{2Vbe}{gmVbe} * \beta = \frac{2\beta}{gm} \quad (2)$$

10

が得られる。

ここで、

$I_b$  はトランジスタ T 1 (又は T 2) のベース電流であり、

$I_c$  はトランジスタ T 1 (又は T 2) のコレクタ電流であり、

$g_m$  はトランジスタ T 1 (又は T 2) の相互コンダクタンスの値であり、

はトランジスタ T 2 (又は T 1) のゲインである。

20

## 【0047】

本発明による入力インピーダンス(式(2))は、従って従来技術による回路の入力インピーダンス(上記の式(1)を参照のこと)よりも遙かに大きく、上流に連結されたオプション回路との連結を改善する。

## 【0048】

その結果として、回路 CIR の分枝 BR の電流ゲイン G は：

## 【数4】

$$G = \frac{Itot}{Ie} = \frac{2 * gm * \frac{Ve}{2}}{\frac{Ve}{Z_e}} = Z_e * gm$$

30

と書かれ得る。ここで、

G は回路 CIR の電流ゲインであり、

$I_{tot}$  は回路 CIR の分枝 BR から、出力として供給される全電流であり、

$I_e$  は回路の分枝 BR の入力電流であり、

$g_m$  はトランジスタ T 1 (又は T 2) の相互コンダクタンスの値である。

## 【0049】

従って、入力インピーダンス  $Z_e$  の値における増加は、回路の電流ゲイン G の値における増加を意味する。遷移周波数  $F_t$  が

40

## 【数5】

$$F_t = \frac{jG}{2}$$

であるため、電流ゲイン G における増加は実際に遷移周波数の値における増加を意味する。

## 【0050】

50

同じ計算が回路 C I R の分枝 B R S に当てはまる。

【0051】

従って、回路 C I R の線形動作領域の範囲は大幅に増加する。その結果、より広い周波数範囲に対する回路のゲインの最大値の恩恵に浴することができる。

【0052】

図に例示されるように、第 2 の主入力トランジスタ T 2 のベースは、補助バイアス・トランジスタ T 3 s のベースにつながれる。

【0053】

従って、トランジスタは第 1 の主入力トランジスタ T 1 により動的モードで駆動される。静的モードにおいて、第 2 の主入力トランジスタ T 2 は、主バイアス・トランジスタ T 3 によりバイアスをかけられる。10

【0054】

1つの変形として、第 2 の主入力トランジスタ T 2 のベースは、主バイアス・トランジスタ T 3 のベースにつながれ得る。そして第 2 の補助入力トランジスタ T 2 s のベースは、(図に例示されるように)補助バイアス・トランジスタ T 3 s のベースにつながれる。図に例示される交差は、1つの分枝における変化が他方の分枝に伝達されることを可能にし、従って完全に対称の差動信号を保つことを可能にする。

【0055】

さらに、第 2 の主入力トランジスタ T 2 は、トランジスタ T 5 と共にカスコード組立てされる。第 2 の主入力トランジスタ T 2 のエミッタは接地され、そのコレクタはトランジスタ T 5 のエミッタと連結される。エミッタ T 5 のベースは基準電圧 Vref の端子とつながれる。20

【0056】

トランジスタ T 5 は入力段 E E と出力段 E Sとの間で：

第 2 の主入力トランジスタ T 2 のコレクタに対して電圧をかけることと、

第 2 の主入力トランジスタ T 2 のコレクタにおけるインピーダンスを制限することと、回路の Miller 効果、すなわち入力特性に対する增幅回路自体のゲインの影響、とりわけ入力インピーダンスにおける減少を制限すること

によりバッファを形成する。

【0057】

トランジスタ T 5 のコレクタは出力段 E S と連結される。後者はこの差動モードについて、平衡不平衡変成器 B L 、すなわち並列の印刷された線とアース面の上方に印刷された線との間のリンクを有効にできる電気回路を含む。

【0058】

平衡不平衡変成器 B L は供給電圧 Vcc により給電され、回路 C I R の出力端子 S t とアースとの間の出力電圧は Vst として示される。

【0059】

供給電圧 Vcc は又、回路 C I R の全ての能動素子に給電するために用いられる。その接続は、単純にするために表わされていない。

【0060】

本発明による増幅回路 C I R の別の利点は、それが特に小型だということである。事実、トランジスタ T 3 (又は選ばれる構成に応じて T 3 s ) は、トランジスタ T 2 (又は T 2 s ) の静的バイアスに直接関与するため、それをトランジスタ T 2 (又は T 2 s ) の近傍に置くことはとりわけ有利である。これは小さなサイズの回路をもたらす。40

【0061】

本例に使用されるトランジスタはシリコン基板上のバイポーラ・タイプである。 A S G a 又は I n P タイプの基板上のバイポーラ・トランジスタを使用することもまた可能である。

【符号の説明】

【0062】

10

20

30

40

50

|         |                  |    |

|---------|------------------|----|

| B B 1   | コイル              |    |

| B B 2   | コイル              |    |

| B L     | 平衡不平衡変成器         |    |

| B R     | 分枝               |    |

| B R S   | 分枝               |    |

| C I R   | 増幅回路             |    |

| C p     | コンデンサ            |    |

| C p s   | コンデンサ            |    |

| E E     | 入力段              | 10 |

| E n     | 入力端子             |    |

| E n s   | 入力端子             |    |

| E S     | 出力段              |    |

| I e     | 入力電流             |    |

| I p     | バイアス電流           |    |

| I t o t | 全電流              |    |

| M P     | 駆動手段             |    |

| R a     | 抵抗               |    |

| R b     | 抵抗               |    |

| S t     | 出力端子             |    |

| T 1     | 第1の主入力トランジスタ     | 20 |

| T 1 s   | 第1の補助入力トランジスタ    |    |

| T 2     | 第2の主入力トランジスタ     |    |

| T 2 s   | 第2の補助入力トランジスタ    |    |

| T 3     | 主バイアス・トランジスタ     |    |

| T 3 s   | 補助バイアス・トランジスタ    |    |

| T 4     | トランジスタ           |    |

| T 5     | トランジスタ           |    |

| V c c   | 供給電圧             |    |

| V e     | 差動電圧             |    |

| V e s   | 差動電圧             | 30 |

| V r e f | 基準電圧             |    |

| V s t   | S t とアースとの間の出力電圧 |    |

【図1】

図1

---

フロントページの続き

(72)発明者 コルビエール、レミ

フランス、78990 エランクール、リュ デ ブリュクセル、8

F ターム(参考) 5J500 AA04 AA41 AC36 AF10 AH02 AH25 AH29 AH33 AH37 AM17

AS14 CK07

【外國語明細書】

2011103655000001.pdf