(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5440419号

(P5440419)

(45) 発行日 平成26年3月12日(2014.3.12)

(24) 登録日 平成25年12月27日(2013.12.27)

(51) Int.Cl.

F 1

G06F 13/24 (2006.01)

G06F 9/48 (2006.01)G06F 13/24 310D

G06F 9/46 311Z

請求項の数 7 (全 18 頁)

(21) 出願番号 特願2010-147249 (P2010-147249)

(22) 出願日 平成22年6月29日 (2010.6.29)

(65) 公開番号 特開2012-14230 (P2012-14230A)

(43) 公開日 平成24年1月19日 (2012.1.19)

審査請求日 平成25年2月28日 (2013.2.28)

(73) 特許権者 308014341

富士通セミコンダクター株式会社

神奈川県横浜市港北区新横浜二丁目10番

23

(74) 代理人 100072718

弁理士 古谷 史旺

(74) 代理人 100116001

弁理士 森 俊秀

(72) 発明者 久米 隆之

神奈川県横浜市港北区新横浜二丁目10番

23 富士通セミコンダクター株式会社内

(72) 発明者 南里 洋亮

神奈川県横浜市港北区新横浜二丁目10番

23 富士通セミコンダクター株式会社内

最終頁に続く

(54) 【発明の名称】情報処理システム

## (57) 【特許請求の範囲】

## 【請求項 1】

高速バスインターフェースに接続され、プログラムを実行するプロセッサと、

低速バスインターフェースを介してアクセスされ、割り込み要因を示す情報が格納される情報レジスタを含み、前記プロセッサに割り込み要求を発行する少なくとも1つの低速スレーブと、

前記高速バスインターフェースに接続される割り込み処理専用のバッファを含み、前記プロセッサへの前記割り込み要求に応答して、リマップ信号をアサートするとともに、前記情報レジスタに格納されている情報を読み出し、読み出した情報を前記バッファに書き込む割り込み制御回路と、

前記リマップ信号のネゲート中に、前記プロセッサから前記情報レジスタへの読み出しがアクセス要求を前記低速スレーブに供給し、前記リマップ信号のアサート中に、前記バッファから情報を読み出すために前記読み出しがアクセス要求を前記割り込み制御回路を介して前記バッファに供給する切替回路と

を備えていることを特徴とする情報処理システム。

## 【請求項 2】

前記割り込み制御回路は、前記情報レジスタを示すアドレスを書き換え可能に保持するアドレスレジスタを含み、前記割り込み要求に応答して、前記アドレスレジスタに保持されているアドレスを用いて前記情報レジスタから情報を読み出すこと

を特徴とする請求項1記載の情報処理システム。

**【請求項 3】**

複数の前記低速スレーブを備え、

前記割り込み制御回路は、複数の前記低速スレーブからの前記割り込み要求が競合するときに優先順を判定する優先度判定回路を含み、判定された優先順にしたがって対応する割り込み要求を発行した低速スレーブの前記情報レジスタから情報を順に読み出し、読み出した情報を前記バッファに書き込むこと

を特徴とする請求項 1 記載の情報処理システム。

**【請求項 4】**

前記割り込み制御回路は、前記各低速スレーブの前記情報レジスタを示すアドレスを書き換え可能に保持するアドレスレジスタを備えていること

10

を特徴とする請求項 3 記載の情報処理システム。

**【請求項 5】**

前記割り込み制御回路は、前記読み出しアクセス要求に含まれるアドレスが前記アドレスレジスタに保持されているアドレスと一致しているか否かを判定するアドレス比較器を含み、アドレスが一致するときに前記バッファから情報を読み出し、アドレスが一致しないときに、前記読み出しアクセス要求を前記低速スレーブに供給し、前記低速スレーブからデータを読み出し、読み出したデータを前記プロセッサに出力すること

を特徴とする請求項 2 または請求項 4 記載の情報処理システム。

**【請求項 6】**

前記割り込み制御回路は、前記割り込み要求に応答して前記情報レジスタに格納されている情報を前記バッファに書き込む前に前記読み出しアクセス要求が発行されるとき、前記プロセッサにウエイト要求を発行すること

20

を特徴とする請求項 1 ないし請求項 5 のいずれか 1 項記載の情報処理システム。

**【請求項 7】**

前記割り込み制御回路は、

前記低速バスインターフェースに接続され、前記低速スレーブの前記情報レジスタに格納されている情報を読み出すときに使用されるマスターインターフェースと、

前記高速バスインターフェースに接続され、前記読み出しアクセス要求に応答して前記バッファにアクセスするときに使用されるスレーブインターフェースと

を備えていることを特徴とする請求項 1 ないし請求項 6 のいずれか 1 項記載の情報処理システム。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、プログラムを実行するととともに割り込み要求に応答して割り込み処理を実施するプロセッサを含む情報処理システムに関する。

**【背景技術】****【0002】**

CPU 等のプロセッサへの割り込み要求が発生してからプロセッサが割り込み処理プログラムの実行を開始するまでの期間に、割り込み処理プログラムをプリフェッチバッファにプリフェッチする情報処理システムが提案されている（例えば、特許文献 1 参照。）。また、割り込み処理が規則的に発生する情報処理システムにおいて、割り込み処理で使用するデータをキャッシュメモリに予め転送する手法が提案されている（例えば、特許文献 2 参照。）。

40

**【先行技術文献】****【特許文献】****【0003】**

【特許文献 1】特開平 8 - 221270 号公報

【特許文献 2】特開 2004 - 252729 号公報

**【発明の概要】**

50

**【発明が解決しようとする課題】****【0004】**

割り込み処理に使用されるI/Oデバイス等のレジスタの値は、プログラムによる書き換え以外の要因によっても変化する。一方、キャッシュメモリ内のデータは、データが追い出されるまで長い期間にわたり保持されることがある。このため、I/Oデバイス等のレジスタに保持されたデータをキャッシュメモリに保持しても、レジスタの値とキャッシュメモリに保持された値が同じであることを保証できない。すなわち、上述した割り込み処理プログラムはキャッシュメモリにプリフェッチすることが可能であるのに対して、I/Oデバイス等のレジスタに保持されているデータは、キャッシュメモリにプリフェッチすることができない。したがって、割り込み処理プログラムにおいて、I/Oデバイス等のレジスタは、直接アクセスされる必要がある。一般に、I/Oデバイス等は低速なスレーブポートに接続されているため、I/Oデバイス等のレジスタを直接アクセスすることにより、割り込み処理プログラムの実行効率は低下し、情報処理システムの性能は低下する。10

**【課題を解決するための手段】****【0005】**

本発明の一形態では、情報処理システムは、高速バスインターフェースに接続され、プログラムを実行するプロセッサと、低速バスインターフェースを介してアクセスされ、割り込み要因を示す情報が格納される情報レジスタを含み、プロセッサに割り込み要求を発行する少なくとも1つの低速スレーブと、高速バスインターフェースに接続される割り込み処理専用のバッファを含み、プロセッサへの割り込み要求に応答して、リマップ信号をアサートするとともに、情報レジスタに格納されている情報を読み出し、読み出した情報をバッファに書き込む割り込み制御回路と、リマップ信号のネゲート中に、プロセッサから情報レジスタへの読み出しアクセス要求を低速スレーブに供給し、リマップ信号のアサート中に、バッファから情報を読み出すために読み出しアクセス要求を割り込み制御回路を介してバッファに供給する切替回路とを有している。20

**【発明の効果】****【0006】**

低速スレーブの情報レジスタに格納されている情報を割り込み処理専用のバッファに格納し、プロセッサからの読み出しアクセス要求を切替回路を用いてバッファに供給することで、情報処理システムの性能を低下することなく、割り込み処理時間を短縮できる。30

**【図面の簡単な説明】****【0007】**

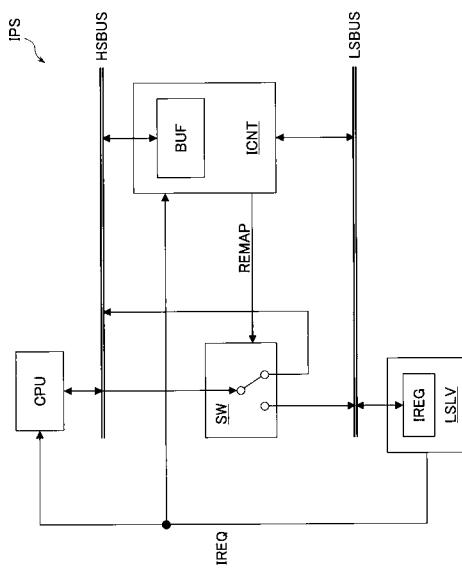

【図1】一実施形態における情報処理システムの例を示している。

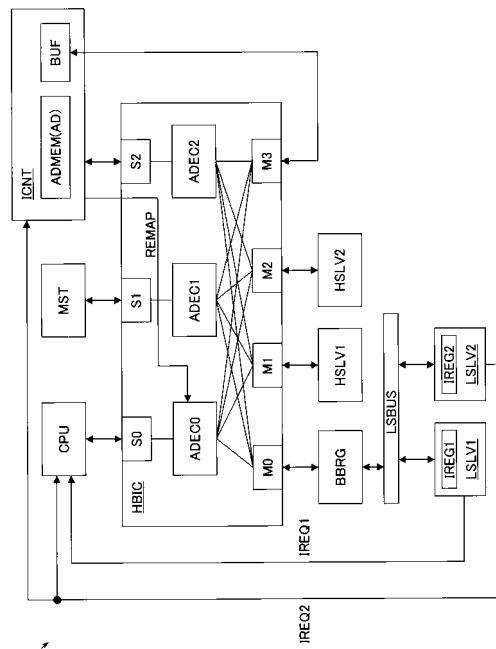

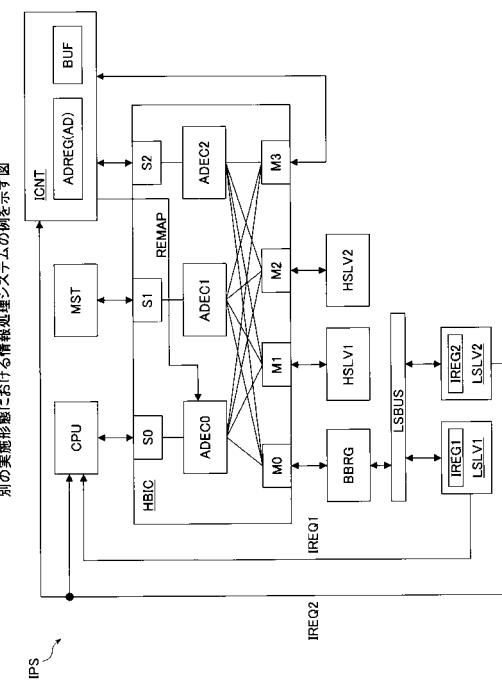

【図2】別の実施形態における情報処理システムの例を示している。

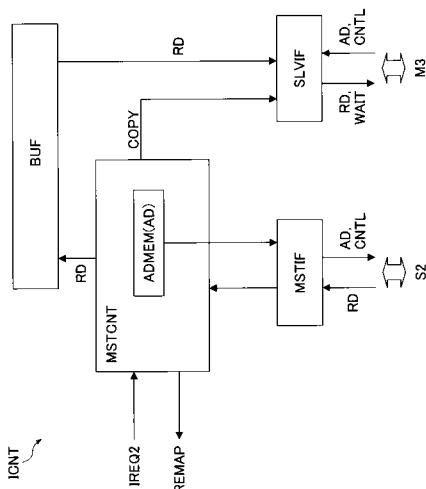

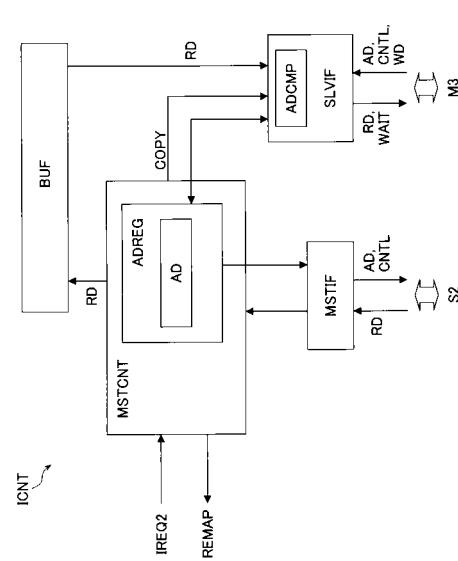

【図3】図2に示した割り込み制御回路の例を示している。

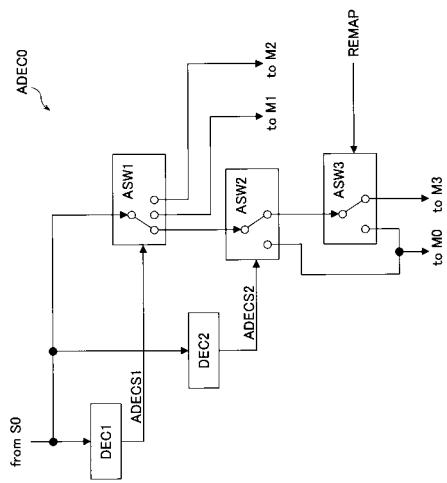

【図4】図2に示したアドレスデコーダの例を示している。

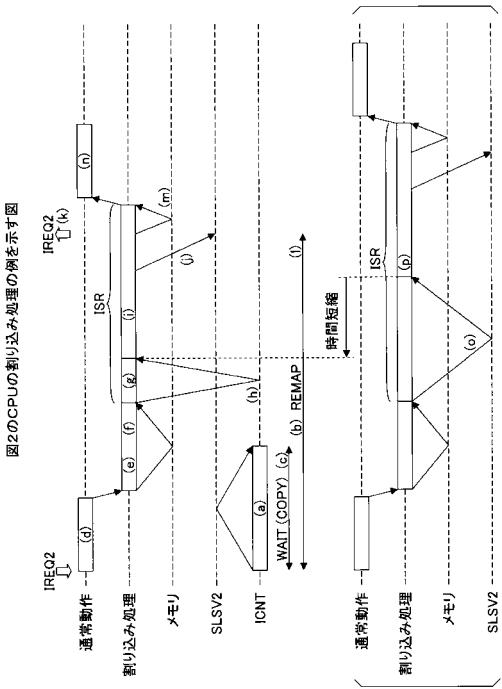

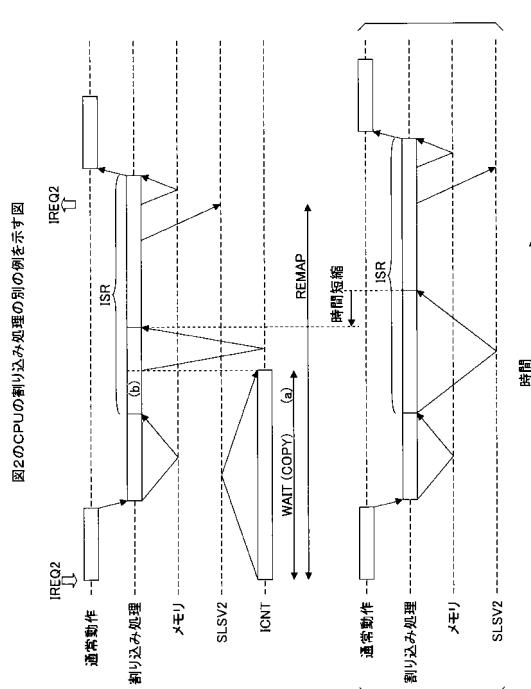

【図5】図2に示したCPUの割り込み処理の例を示している。

【図6】図2に示したCPUの割り込み処理の別の例を示している。

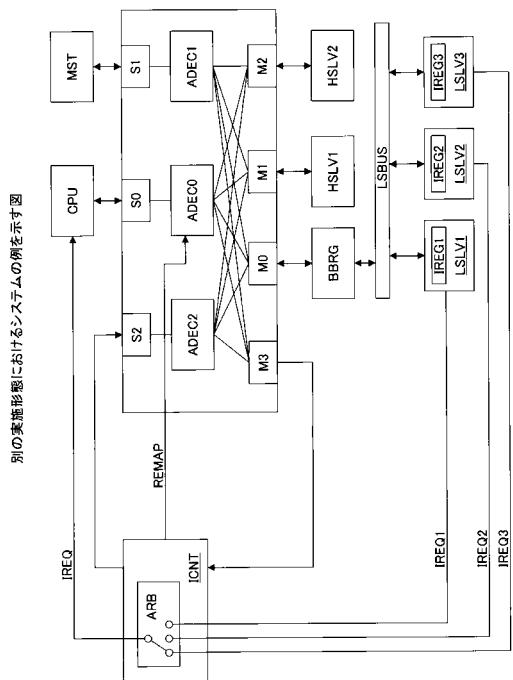

【図7】別の実施形態における情報処理システムの例を示している。

【図8】図7に示した割り込み制御回路の例を示している。

【図9】図7に示したアドレスデコーダの例を示している。

【図10】別の実施形態における情報処理システムの例を示している。

【図11】図10に示した割り込み制御回路の例を示している。

【図12】別の実施形態における割り込み制御回路の例を示している。

【図13】別の実施形態における情報処理システムの例を示している。

**【発明を実施するための形態】****【0008】**

以下、実施形態を、図面を用いて説明する。

**【0009】**

40

50

図1は、一実施形態における情報処理システムIPSの例を示している。情報処理システムIPSは、高速バスインターフェースHSBUsに接続されるCPU(Central Processing Unit)、低速バスインターフェースLSBUSに接続される低速スレーブLSLV、割り込み制御回路ICNTおよび切替回路SWを有している。CPUは、プログラムを実行するプロセッサの一種であり、低速スレーブLSLVからの割り込み要求IREQに応答して、通常のプログラムの実行を中断し、割り込み処理ルーチンを実行する。低速スレーブLSLVは、割り込み要因などの割り込み処理に必要な情報が格納される情報レジスタIREGを有しており、CPUに割り込み要求IREQを発行する機能を有している。

#### 【0010】

10

割り込み制御回路ICNTは、高速バスインターフェースHSBUsに接続され、高速にアクセス可能な割り込み処理専用のバッファBUFを有している。割り込み制御回路ICNTは、低速スレーブLSLVから割り込み要求IREQが発生したときに、CPUが割り込み処理ルーチンを開始するまでの時間を短縮するために動作する。

#### 【0011】

20

具体的には、割り込み制御回路ICNTは、割り込み要求IREQに応答してリマップ信号REMAPをアサートする。また、割り込み制御回路ICNTは、CPUが低速スレーブLSLV用の割り込み処理ルーチンへの移行処理を実施している間に、情報レジスタIREGから割り込み要因等の情報を読み出す。すなわち、割り込み制御回路ICNTは、割り込み処理ルーチンが開始される前に割り込み要因等の情報を先読みし、読み出した情報をバッファBUFに書き込む。

#### 【0012】

切替回路SWは、リマップ信号REMAPのアサート中にCPUからの読み出しアクセス要求を割り込み制御回路ICNTを介してバッファBUFに供給する。図1の切替回路SWは、リマップ信号REMAPがアサートされている状態を示している。切替回路SWは、リマップ信号REMAPのネガート中にCPUからの読み出しアクセス要求を低速スレーブLSLVに供給する。

#### 【0013】

30

これにより、割り込み要求IREQに応答してCPUにより実行される割り込み処理ルーチンにおいて、情報レジスタIREGに保持されている割り込み要因等の情報をCPUにより高速に読み出すことができる。割り込み要因を早く判定できるため、割り込み要求IREQが発生してから、割り込み処理ルーチンが開始されるまでの時間を短縮できる。

#### 【0014】

なお、割り込み要因等の情報は、割り込み要求IREQに応答してバッファBUFに書き込まれる。割り込み要求IREQの直後に情報レジスタIREGに保持されている割り込み要因等の情報が書き換えられることはない。このため、割り込み処理ルーチンによる割り込み要因等の情報の読み出し時に、バッファBUFに保持されている値と、情報レジスタIREGに保持されている値とが相違することはない。

#### 【0015】

40

以上、この実施形態では、低速スレーブLSLVの情報レジスタIREGに格納されている情報を割り込み処理専用のバッファBUFに格納し、CPUからの読み出しアクセス要求に応答してバッファBUFから情報を読み出すことで、情報処理システムIPSの性能を低下することなく、割り込み処理時間を短縮できる。

#### 【0016】

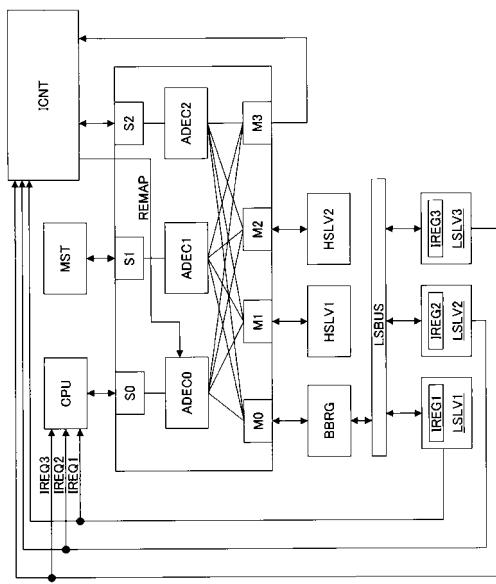

図2は、別の実施形態における情報処理システムIPSの例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。例えば、情報処理システムIPSは、半導体集積回路として1つのチップで形成されている。

#### 【0017】

情報処理システムIPSは、高速バスインターフェースの一種である高速バスインター

50

コネクトH B I Cを介して接続されたC P U、マスターM S T、割り込み制御回路I C N T、バスブリッジB B R G、高速スレーブH S L V 1、H S L V 2と、低速バスインターフェースL S B U Sを介してバスブリッジB B R Gに接続された低速スレーブL S L V 1、L S L V 2とを有している。低速スレーブL S L V 1、L S L V 2は、割り込み要因等の情報が格納される情報レジスタI R E G 1、I R E G 2をそれぞれ有している。

#### 【0018】

C P Uは、プログラムを実行することで、情報処理システムI P S全体の動作を制御する。例えば、C P Uは、プログラムが一時的に格納されるキャッシュメモリを有している。また、C P Uは、割り込み要求I R E Q 1、I R E Q 2を受ける割り込みコントローラを搭載している。なお、割り込みコントローラは、C P Uの外側に形成してもよい。

10

#### 【0019】

例えば、マスターM S Tは、D M A C (Direct Memory Access Controller)である。C P U、マスターM S Tおよび割り込み制御回路I C N Tは、高速バスインターフェースL S B U S側の低速バスプロトコルとの変換を行っている。また、割り込みコントローラは、低速スレーブL S L V 1、L S L V 2は、タイマーや通信インターフェース等の周辺デバイスであり、割り込み要求I R E Q 1、I R E Q 2をそれぞれ発行する。バスブリッジB B R Gは、低速スレーブL S L V 1、L S L V 2から割り込み要求I R E Q 2が発生したときに、C P Uが割り込み処理ルーチンを開始するまでの時間を短縮するために動作する。割り込み制御回路I C N Tの例は、図3に示す。

20

割り込み制御回路I C N Tは、図1と同様に、高速にアクセスされ、割り込み要因等の情報が格納される割り込み処理専用のバッファB U Fを有している。また、割り込み制御回路I C N Tは、低速スレーブL S L V 2の情報レジスタI R E G 2を示すアドレスA Dを記憶するアドレス記憶部A D M E Mを有している。割り込み制御回路I C N Tは、図1と同様に、低速スレーブL S L V 2から割り込み要求I R E Q 2が発生したときに、C P Uが割り込み処理ルーチンを開始するまでの時間を短縮するために動作する。割り込み制御回路I C N Tの例は、図3に示す。

#### 【0020】

例えば、低速スレーブL S L V 1は、割り込み要求I R E Q 1の発生から割り込み処理が開始されるまでの時間が長くても許容されるデバイスである。これに対して、低速スレーブL S L V 2は、割り込み要求I R E Q 2の発生から割り込み処理が開始されるまでの時間が所定時間以下であることが要求されるデバイスである。情報処理システムI P Sを正常に動作するために、低速スレーブL S L V 2の割り込み処理は早く開始される必要がある。このために、割り込み制御回路I C N Tが生成するリマップ信号R E M A PによりアドレスデコーダA D E C 0の機能が切り替えられ、低速スレーブL S L V 2の代わりにバッファB U Fがアクセスされる。

30

#### 【0021】

高速バスインターフェースL S B U S側の低速バスプロトコルとの変換を行っている。また、割り込みコントローラは、低速スレーブL S L V 1、L S L V 2から割り込み要求I R E Q 2が発生したときに、C P Uが割り込み処理ルーチンを開始するまでの時間を短縮するために動作する。割り込み制御回路I C N Tの例は、図3に示す。

40

#### 【0022】

高速バスインターフェースL S B U S側の低速バスプロトコルとの変換を行っている。また、割り込みコントローラは、低速スレーブL S L V 1、L S L V 2から割り込み要求I R E Q 2が発生したときに、C P Uが割り込み処理ルーチンを開始するまでの時間を短縮するために動作する。割り込み制御回路I C N Tの例は、図3に示す。

#### 【0023】

アドレスデコーダA D E C 0は、C P Uからのアドレスをデコードし、デコード結果に応じてアドレスをマスターポートM 0 - 3のいずれかに出力する。アドレスデコーダA D E C 1は、マスターM S Tからのアドレスをデコードし、デコード結果に応じてアドレスをマスターポートM 0 - 3のいずれかに出力する。アドレスデコーダA D E C 2は、割り込み制御回路I C N Tからのアドレスをデコードし、デコード結果に応じてアドレスをマスターポートM 0 - 3のいずれかに出力する。アドレスデコーダA D E C 0の例は、図4

50

に示す。

**【0024】**

なお、図2に示した高速バスインターフェースH B I Cは、主にアドレスの伝達経路を示しているが、制御信号およびデータも伝達される。このために、各アドレスデコーダA D E C 0 - 2は、制御信号およびデータの伝達経路を切り替える機能を有していてもよい。低速バスインターフェースL S B U Sも同様に、アドレスだけでなく、制御信号およびデータも伝達される。高速バスインターフェースH B I Cおよび低速バスインターフェースL S B U Sは、双方向バスである。

**【0025】**

図3は、図2に示した割り込み制御回路I C N Tの例を示している。割り込み制御回路I C N Tは、バッファB U F、アドレス記憶部A D M E Mを有するマスター制御回路M S T C N T、マスターインターフェースM S T I FおよびスレーブインターフェースS L V I Fを有している。

10

**【0026】**

アドレス記憶部A D M E Mは、低速スレーブL S L V 2の情報レジスタI R E G 2を示すアドレスA Dを記憶している。例えば、情報レジスタI R E G 2は、割り込み要求I R E Q 2が発生した要因を示す情報が格納されている。なお、マスター制御回路M S T C N Tは、2つ以上のアドレス記憶部A D M E Mを有していてもよい。

**【0027】**

アドレス記憶部A D M E Mに記憶されているアドレスA Dの値は、半導体集積回路の製造に使用される金属配線層のフォトマスクのパターンとして設定される。あるいは、アドレスA Dの値は、半導体集積回路上に形成されるヒューズ回路を用いて設定される。このため、アドレスA Dの値は、固定値であり、半導体集積回路の出荷後に変更できない。

20

**【0028】**

マスター制御回路M S T C N Tは、割り込み要求I R E Q 2をモニタリングし、割り込み要求I R E Q 2に応答して、アドレス記憶部A D M E Mに記憶されているアドレスA Dを、低速スレーブL S L V 2に読み出しアクセスするための制御信号C N T LとともにマスターインターフェースM S T I Fに出力する。

**【0029】**

マスターインターフェースM S T I Fは、マスター制御回路M S T C N TからのアドレスA Dおよび制御信号C N T Lを、図2に示した高速バスインターフェースH B I CのスレーブポートS 2に出力する。すなわち、マスターインターフェースM S T I Fは、情報レジスタI R E G 2から情報を読み出すためにバストランザクションを発行する機能を有している。

30

**【0030】**

スレーブポートS 2に供給されるバストランザクションは、図2のアドレスデコーダA D E C 2、マスターポートM 0、バスブリッジB B R Gおよび低速バスインターフェースL S B U Sを介して低速スレーブL S L V 2に伝達される。低速スレーブL S L V 2は、バストランザクションに基づいて情報レジスタI R E G 2に格納されている割り込み要因を含む情報を低速バスインターフェースL S B U Sに出力する。低速バスインターフェースL S B U Sに出力される情報は、バスブリッジB B R G、マスターポートM 0およびスレーブポートS 2を介してマスターインターフェースM S T I Fに伝達される。

40

**【0031】**

マスターインターフェースM S T I Fは、低速スレーブL S L V 2から読み出される情報レジスタI R E G 2の値を読み出しデータR Dとして受け、マスター制御回路M S T C N Tに出力する。マスター制御回路M S T C N Tは、読み出しデータR DをバッファB U Fに書き込む。マスター制御回路M S T C N Tは、割り込み要求I R E Q 2を受けてから読み出しデータがバッファB U Fに書き込まれるまでの間、C P Uにより空のバッファB U Fがアクセスされることを防止するため、コピー中信号C O P YをスレーブインターフェースS L V I Fに向けてアサートする。

50

**【 0 0 3 2 】**

バッファBUFは、CPUにより低速スレーブLSLV2に比べて高速にアクセス可能である。バッファBUFのサイズは、情報を読み出す情報レジスタIREG2のサイズに合わせて設計される。例えば、32ビット幅の情報レジスタIREG2から割り込み要因を含む情報が読み出されると、バッファBUFは、32ビット幅のデータRDを格納可能なサイズに設計される。

**【 0 0 3 3 】**

なお、割り込み要求IREQ2に応答して実行される割り込み処理プログラムに必要な情報が、低速スレーブLSLV2の複数の情報レジスタIREG2に格納されるとき、マスター制御回路MSTCNTは、複数のアドレス記憶部ADMEMを有する。複数のアドレス記憶部ADMEMは、低速スレーブLSLV2の複数の情報レジスタIREG2をそれぞれ示す複数のアドレスADをそれぞれ記憶する。そして、マスター制御回路MSTCNTは、複数の情報レジスタIREG2から情報を読み出すために、複数のアドレスADを制御信号CNTLとともにマスターインターフェースMSTIFに順に出力する。10

**【 0 0 3 4 】**

さらに、マスター制御回路MSTCNTは、割り込み要求IREQ2に応答してリマップ信号REMAPをアサートし、図2に示したアドレスデコーダADEC0に出力する。リマップ信号REMAPのアサートにより、アドレスデコーダADEC0は、情報レジスタIREG2を示すアドレスを含む読み出しアクセス要求をCPUから受けたときに、アドレスADおよび制御信号CNTLをマスターポートM0ではなくマスターポートM3に出力する。このように、情報レジスタIREG2を読み出しアクセスするためにCPUから出力されるアドレスADおよび制御信号CNTLは、リマップ信号REMAPのアサート中に、マスターポートM3を介して割り込み制御回路ICNTに伝達される。20

**【 0 0 3 5 】**

割り込み制御回路ICNTのスレーブインターフェースSLVIFは、マスターポートM3を介してCPUから供給されるアドレスADおよび制御信号CNTLに応答してバッファBUFに保持されているデータRDを読み出し、マスターポートM3に出力する。マスターポートM3に出力されたデータRDは、スレーブポートS0を介してCPUに伝達される。そして、CPUは、バッファBUFに保持されている情報を、低速スレーブLSLV2の情報レジスタIREG2に保持している情報として読み出す。なお、コピー中信号COPYがアサートされているとき、スレーブインターフェースSLVIFは、マスターポートM3に向けてウェイト要求WAITをアサートする。これにより、コピー中信号COPYがネゲートされるまで、CPUによる情報レジスタIREG2のアクセスサイクル（実際には、バッファBUFのアクセスサイクル）にウェイトサイクルが挿入される。すなわち、割り込み要求IREQ2に応答して情報レジスタIREG2に格納されている情報をバッファBUFに書き込む前に読み出しアクセス要求が発行されるとき、CPUにウェイト要求WAITが発行される。30

**【 0 0 3 6 】**

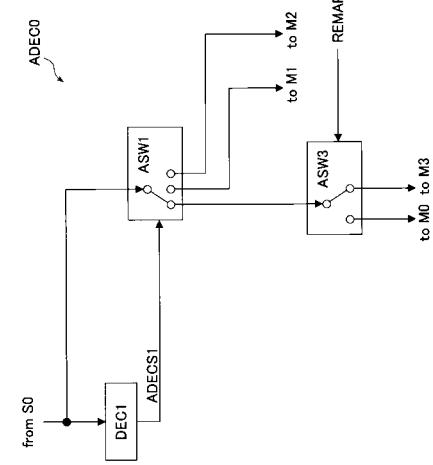

図4は、図2に示したアドレスデコーダADEC0の例を示している。アドレスデコーダADEC0は、デコーダDEC1、DEC2およびスイッチASW1、ASW2、ASW3を有している。例えば、デコーダDEC1は、スレーブポートS0を介してCPUから伝達されるアドレスの上位ビット群をデコードし、生成したアドレスデコード信号ADECS1をスイッチASW1に出力する。40

**【 0 0 3 7 】**

スイッチASW1は、スレーブポートS0を介してCPUから伝達されるアドレスの下位ビット群を、アドレスデコード信号ADECS1に応じて、スイッチASW2、マスターポートM1、M2のいずれかに供給する。具体的には、アドレスの上位ビット群がマスターポートM0を示すときに、アドレスの下位ビット群は、スイッチASW2に供給される。アドレスの上位ビット群がマスターポートM1を示すときに、アドレスの下位ビット群はマスターポートM1に供給される。アドレスの上位ビット群がマスターポートM2を50

示すときに、アドレスの下位ビット群は、マスターポートM 2に供給される。

**【0038】**

例えば、デコーダDEC 2は、スレーブポートS 0を介してCPUから伝達されるアドレスの中位ビット群をデコードし、生成したアドレスデコード信号ADECS 2をスイッチASW 2に出力する。スイッチASW 2は、スイッチASW 1からのアドレスの下位ビット群を、アドレスデコード信号ADECS 2に応じてスイッチASW 3またはマスターポートM 0に供給する。

**【0039】**

具体的には、アドレスの中位ビット群が情報レジスタIREG 2を示すときに、アドレスの下位ビット群はスイッチASW 3に供給される。アドレスの中位ビット群が低速スレーブLSLV 2の情報レジスタIREG 2以外および低速スレーブLSLV 1を示すときに、アドレスの下位ビット群はマスターポートM 0に供給される。10

**【0040】**

スイッチASW 3は、スイッチASW 2からのアドレスの下位ビット群を、リマップ信号REMAPに応じて、マスターポートM 0またはM 3に供給する。具体的には、リマップ信号REMAPのネゲート中、アドレスの下位ビット群はマスターポートM 0に供給される。リマップ信号REMAPのアサート中、アドレスの下位ビット群はマスターポートM 3に供給される。なお、リマップ信号REMAPのアサート中に書き込みアクセスが要求されるとき、アドレスの下位ビット群はマスターポートM 0に供給される。

**【0041】**

このように、アドレスデコーダADEC 0は、リマップ信号REMAPのアサート中に、バッファBUFから情報を読み出すために読み出しアクセス要求を割り込み制御回路ICNTを介してバッファBUFに供給し、リマップ信号REMAPのネゲート中に、CPUから情報レジスタIREG 2への読み出しアクセス要求を低速スレーブLSLV 2に供給する切替回路として動作する。なお、スイッチASW 1 - ASW 3は、アドレスの切り替えだけでなく、アドレスとともにCPUから供給される制御信号およびデータの伝達先を切り替えてよい。20

**【0042】**

図5は、図2に示したCPUの割り込み処理の例を示している。この例では、CPUが通常動作を実行するための通常のプログラムを実行中に、低速スレーブLSLV 2から割り込み要求IREQ 2が発生する。CPUは、通常のプログラムの実行を中断し、割り込み処理プログラムを実行する。30

**【0043】**

図2に示した割り込み制御回路ICNTは、割り込み要求IREQ 2のアサートに応答して、情報レジスタIREG 2に読み出しアクセスし、情報レジスタIREG 2に保持されている情報をバッファBUFに書き込む(図5(a))。すなわち、割り込み要求IREQ 2を発行した低速スレーブLSLV 2の割り込み要因の先読みが実施される。また、割り込み制御回路ICNTは、割り込み要求IREQ 2に応答してリマップ信号REMAPをアサートする(図5(b))。さらに、割り込み制御回路ICNTは、情報レジスタIREG 2から読み出される情報をバッファBUFに書き込むまでウェイト要求WAITをアサートする(図5(c))。40

**【0044】**

CPUは、実行中の命令を、例えば1サイクルから16サイクルの間に中断する(図5(d))。CPUは、割り込み処理ルーチンISR(Interrupt Service Routine)の命令をフェッチするために、メモリにアクセスする(図5(e))。ここで、フェッチされるメモリは、割り込み処理ルーチンISRが格納されているキャッシュメモリまたはメインメモリ等である。もし、キャッシュミスが発生したとき、割り込み処理ルーチンISRをメインメモリからキャッシュメモリにコピーするキャッシュラインファイルが実行される。

**【0045】**

10

20

30

40

50

次に、CPUは、今まで実行していた通常動作の状態を保持するために、CPU内のレジスタの値をSTACKメモリ等に待避する(図5(f))。図5の(e)、(f)は、低速スレーブLSLV2用の割り込み処理ルーチンへの移行処理である。この後、CPUは、割り込み処理ルーチンISRの実行を開始し、割り込み要求IREQ2の発生要因を調べるために、情報レジスタIREG2に読み出しアクセスする(図5(g))。CPUが割り込み処理ルーチンISRの実行を開始するとき、割り込み制御回路ICNTは、情報レジスタIREG2に保持されている情報をバッファBUFに書き込み済みである。このため、図3および図4で説明したように、情報レジスタIREG2がアクセスされる代わりに、割り込み制御回路ICNTのバッファBUFがアクセスされる(図5(h))。これにより、CPUは、情報レジスタIREG2の情報を高速に読み出しできる。

10

#### 【0046】

この後、CPUは、読み出した情報レジスタIREG2の値に基づいて、割り込み要求IREQ2の発生要因を分析し、割り込み要因に応じた割り込み処理を実行する(図5(i))。CPUは、割り込み処理の実行後、割り込み要求IREQ2をネゲートするために、情報レジスタIREG2に書き込みアクセスし、情報レジスタIREG2をリセットする(図5(j))。なお、情報レジスタIREG2のリセットは、書き込みアクセスであるため、アドレスデコーダADEC0は、リマップ信号REMAPのレベルに拘わらず、アドレスおよび制御信号をマスターポートM0に出力する。

#### 【0047】

情報レジスタIREG2のリセットに応答して、割り込み要求IREQ2がネゲートされる(図5(k))。割り込み制御回路ICNTは、割り込み要求IREQ2のネゲートに応答してリマップ信号REMAPをネゲートする(図5(l))。次に、CPUは、STACKメモリ等に待避していた情報をCPU内のレジスタに戻す(図5(m))。そして、CPUは、中断していた通常動作を再び実行するために、命令のフェッチを開始する(図5(n))。

20

#### 【0048】

図5の下側は、CPUが割り込み要求IREQ2の発生要因を調べるために、情報レジスタIREG2に直接読み出しアクセスするときの例を示している。すなわち、情報処理システムIPSが図2に示した割り込み制御回路ICNTを有していないときの動作の例を示している。

30

#### 【0049】

情報レジスタIREG2が直接アクセスされるとき、バッファBUFがアクセスされるときに比べて、読み出しサイクル時間は長くなる(図5(o))。これにより、CPUによる割り込み処理ルーチンISRの実行開始タイミングは遅れる(図5(p))。換言すれば、割り込み制御回路ICNTの動作により、割り込み処理ルーチンISRにおいて、割り込み処理が開始されるまでの時間を短縮でき、情報処理システムIPSの性能を向上できる。

#### 【0050】

図6は、図2に示したCPUの割り込み処理の別の例を示している。図5と同じ動作については、詳細な説明は省略する。図6は、割り込み制御回路ICNTによる情報レジスタIREG2の読み出しアクセスに時間が掛かる例を示している。例えば、割り込み要求IREQ2の発生時に、図2に示した低速バスインターフェースLSBUSが低速スレーブLSLV1等のアクセスで使用されているとき、低速スレーブLSLV2のアクセスは待たされる。

40

#### 【0051】

割り込み制御回路ICNTは、情報レジスタIREG2から読み出される情報のバッファBUFへの書き込みが完了するまでウエイト要求WAITをアサートしている(図6(a))。このため、ウエイト要求WAITのアサート中、割り込み処理ルーチンISRによる情報レジスタIREG2への読み出しアクセスは待たされる(図6(b))。これにより、割り込み処理ルーチンISRの実行時間は、図5に比べて長くなる。しかしながら

50

、ウエイト要求W A I Tがアサートされる要因は所定の確率で発生するため、C P Uによる低速スレーブL S L V 2のアクセスにおいても、ウエイトサイクルが発生する可能性がある。このため、割り込み処理ルーチンI S Rが開始される前に、情報レジスタI R E G 2の内容をアクセス速度の高いバッファB U Fに予めコピーしておくことで、割り込み処理ルーチンI S Rの処理時間を短縮できる。

#### 【0052】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。さらに、情報レジスタI R E G 2の情報がバッファB U Fに書き込まれるまでウエイト要求W A I Tをアサートすることで、C P Uが空のバッファB U Fにアクセスすることを防止でき、情報処理システムI P Sの誤動作を防止できる。割り込み制御回路I C N TにマスターインターフェースM S T I FとスレーブインターフェースS L V I Fを形成することで、低速バスインターフェースへのバストランザクションの発行と、高速バスインターフェースからのバストランザクションの受け付けを容易に実施できる。10

#### 【0053】

図7は、別の実施形態における情報処理システムI P Sの例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。例えば、情報処理システムI P Sは、半導体集積回路として1つのチップで形成されている。この実施形態では、割り込み制御回路I C N TおよびアドレスデコーダA D E C Oが図2と相違している。情報処理システムI P Sのその他の構成は、図2と同様である。C P Uは、割り込み要求I R E Q 1、I R E Q 2を受ける割り込みコントローラを内蔵している。なお、割り込みコントローラは、C P Uの外側に形成してもよい。20

#### 【0054】

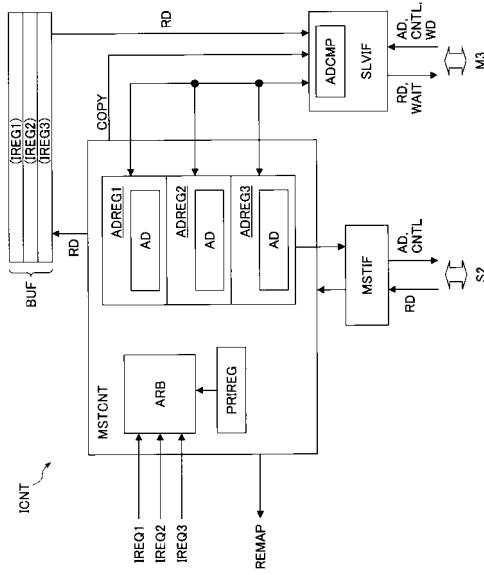

図8は、図7に示した割り込み制御回路I C N Tの例を示している。割り込み制御回路I C N Tは、マスター制御回路M S T C N TおよびスレーブインターフェースS L V I Fが図3と相違している。割り込み制御回路I C N Tのその他の構成は、図3と同様である。。20

#### 【0055】

マスター制御回路M S T C N Tは、図3に示したアドレス記憶部A D M E Mの代わりにアドレスレジスタA D R E Gを有している。アドレスレジスタA D R E Gは、低速スレーブL S L V 2の情報レジスタI R E G 2を示すアドレスA Dを保持している。情報レジスタI R E G 2は、上述した実施形態と同様に、割り込み要求I R E Q 2が発生した要因を示す情報が格納されている。但し、情報レジスタI R E G 2を示すアドレスは1つではない。換言すれば、情報レジスタI R E G 2を示すアドレスは、設計される情報処理システムI P Sにより異なる。あるいは、動作モードに応じて複数の情報レジスタI R E G 2の1つに割り込み要因が格納される。30

#### 【0056】

アドレスレジスタA D R E Gは、図7に示したスレーブポートS 0、マスターポートM 3およびスレーブインターフェースS L V I Fを介して、C P Uにより読み書き可能である。例えば、アドレスレジスタA D R E Gは、システムブート中など、割り込み機能が有効になる前に設定される。アドレスレジスタA D R E Gを書き換え可能にすることで、割り込み要求I R E Q 2の発生要因を示す情報が格納されている情報レジスタI R E G 2のアドレスをシステム仕様に応じて自由に設定できる。あるいは、動作モードに応じて割り込み要求I R E Q 2の発生要因が異なり、参照すべき情報レジスタI R E G 2が異なるときに、C P Uは、動作モード毎にアドレスレジスタA D R E GのアドレスA Dを書き換える。これにより、マスター制御回路M S T C N Tの回路規模を最小限にできる。なお、アドレスレジスタA D R E Gの数は2つ以上でもよい。40

#### 【0057】

スレーブインターフェースS L V I Fは、図3に示したスレーブインターフェースS L V I Fに、アドレスレジスタA D R E Gにアクセスする機能と、アドレス比較器A D C M50

Pとを追加している。アドレス比較器ADCMPは、図7に示したスレーブポートS0およびマスターポートM3を介してCPUから供給される読み出しアクセス要求に含まれるアドレスADと、アドレスレジスタADREGに保持されたアドレスADとを比較する。

#### 【0058】

スレーブインターフェースSLVIFは、CPUからのアドレスADとアドレスレジスタADREGに保持されたアドレスADとが一致するときに、バッファBUFからデータRDを読み出し、CPUに出力する。スレーブインターフェースSLVIFは、CPUからのアドレスADとアドレスレジスタADREGに保持されたアドレスADとが異なるときに、CPUからの読み出しアクセス要求(アドレスADおよび制御信号CNTL)を、マスターインターフェースMSTIFを経由して低速スレーブLSLV2に供給する。

10

#### 【0059】

具体的には、CPUからの読み出しアクセス要求は、マスターインターフェースMSTIF、スレーブポートS2、マスターポートM0、バスブリッジBBRGおよび低速バスインターフェースLSBUSを介して低速スレーブLSLV2に供給される。また、低速スレーブLSLV2から読み出されるデータRDは、低速バスインターフェースLSBUs、バスブリッジBBRG、マスターポートM0、スレーブポートS2、マスターインターフェースMSTIFおよびマスター制御回路MSTCNTを介してスレーブインターフェースSLVIFに伝達される。さらに、読み出されたデータRDは、スレーブインターフェースSLVIFからマスターポートM3およびスレーブポートS0を介してCPUに伝達される。これにより、アドレスレジスタADREGに保持されるアドレスADが書き換えられるときにも、アドレスレジスタADREGに保持されるアドレスADに応じて、バッファBUFからデータRDを確実に読み出すことができる。

20

#### 【0060】

図9は、図7に示したアドレスデコーダADECOの例を示している。アドレスデコーダADECOは、図4に示したアドレスデコーダADECOからデコーダDEC2およびスイッチASW2を削除している。アドレスデコーダADECOのその他の構成は、図4と同様である。スイッチASW3は、リマップ信号REMAPのアサート中、スイッチASW1からのアドレスの下位ビット群をマスターポートM3に供給し、リマップ信号REMAPのネゲート中、スイッチASW1からのアドレスの下位ビット群をマスターポートM0に供給する。これにより、割り込み要求IREQ2のアサート後に、CPUからのアドレスADとアドレスレジスタADREGに保持されたアドレスADとが一致するときのみ、バッファBUFに保持されている情報レジスタIREG2の値を高速に読み出すことができる。

30

#### 【0061】

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。なお、この実施形態では、低速スレーブLSLV2のアクセスにおいて、割り込み制御回路ICNTを経由してアクセスされるときにアクセスレイテンシは大きくなる。しかしながら、情報レジスタIREG2の内容をバッファBUFに予めコピーしておくことで、図5および図6と同様に、割り込み処理ルーチンISRの処理時間を短縮できる。

#### 【0062】

40

図10は、別の実施形態における情報処理システムIPSの例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。例えば、情報処理システムIPSは、半導体集積回路として1つのチップで形成されている。この実施形態では、情報処理システムIPSは、3つの低速スレーブLSLV1、LSLV2、LSLV3を有している。低速スレーブLSLV1 - 3から出力される割り込み要求IREQ1 - 3は、CPUおよび割り込み制御回路ICNTに供給される。CPUは、割り込み要求IREQ1 - 3を受ける割り込みコントローラを内蔵している。なお、割り込みコントローラは、CPUの外側に形成してもよい。情報処理システムIPSのその他の構成は、アドレスデコーダADECOがリマップ信号REMAP1 - 3を受けて動作することを除き、図2と同様である。

50

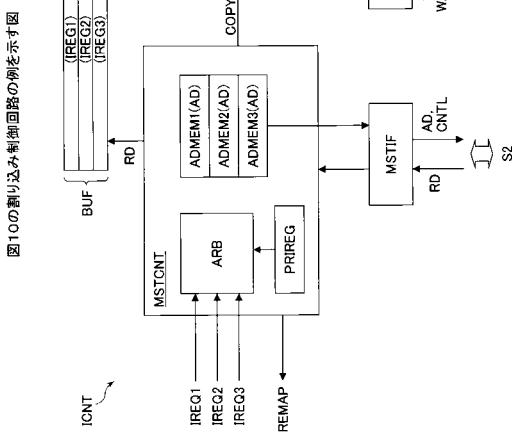

**【 0 0 6 3 】**

図11は、図10に示した割り込み制御回路ICNTの例を示している。割り込み制御回路ICNTは、マスター制御回路MSTCNTが図3と相違している。割り込み制御回路ICNTのその他の構成は、図3と同様である。

**【 0 0 6 4 】**

マスター制御回路MSTCNTは、図3のマスター制御回路MSTCNTに優先度判定回路ARBおよび優先度設定レジスタPRIREGを追加している。また、マスター制御回路MSTCNTは、割り込み要求IREQ1-3にそれぞれ対応してアドレス記憶部ADMEM1-3を有している。

**【 0 0 6 5 】**

優先度判定回路ARBは、割り込み要求IREQ(IREQ1-3のいずれか)が発生したときに、発生した割り込み要求IREQをマスター制御回路MSTCNT内に伝達する。マスター制御回路MSTCNTは、発生した割り込み要求IREQに対応するアドレス記憶部ADMEM(ADMEM1-3のいずれか)に記憶されているアドレスADを用いて、対応する情報レジスタIREG(IREG1-3のいずれか)に読み出しアクセスする。この際、読み出しアクセスは、マスターインターフェースMSTIF、スレーブポートS2、マスターポートM0、バスプリッジBBRGおよび低速バスインターフェースLSBUSを介して行われる。低速スレーブLSLV1-3のいずれかから読み出されたデータRDは、低速バスインターフェースLSBUS、バスプリッジBBRG、マスターポートM0、スレーブポートS2およびマスターインターフェースMSTIFを介してバッファBUFに書き込まれる。バッファBUFは、情報レジスタIREG1-3に対応する記憶領域を有している。

10

**【 0 0 6 6 】**

優先度判定回路ARBは、割り込み要求IREQ1-3の2つ以上が競合するときに、優先度設定レジスタPRIREGに保持されている値に応じて、割り込み処理の優先順を判定する。例えば、優先度設定レジスタPRIREGは、CPU内の割り込み処理の優先順と同じ情報が記憶されている。この例では、CPUおよび優先度設定レジスタPRIREGは、IREQ2 > IREQ1 > IREQ3の優先順が設定されている。優先度設定レジスタPRIREGは、CPUによって書き換え可能である。

20

**【 0 0 6 7 】**

マスター制御回路MSTCNTは、割り込み要求IREQ1-3の2つ以上が競合するときに、優先度判定回路ARBにより決定された優先順にしたがって、情報レジスタIREG1-3に順に読み出しアクセスし、読み出したデータRDをバッファBUFに順に書き込む。

30

**【 0 0 6 8 】**

また、マスター制御回路MSTCNTは、割り込み要求IREQ(IREQ1-3)がアサートされた後、対応する情報レジスタIREG1-3の読み出しアクセス要求が発行される毎に、リマップ信号REMAPをアサートする。マスター制御回路MSTCNTは、CPUが対応する情報をバッファBUFから読み出したことに応答してリマップ信号REMAPをネゲートする。すなわち、リマップ信号REMAPのアサート期間は最小限に設定される。これにより、上述した実施形態と同様に、CPUは、情報レジスタIREG1-3に保持されている割り込み要因を、高速アクセス可能なバッファBUFから読み出すことができる。

40

**【 0 0 6 9 】**

以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。さらに、割り込み制御回路ICNTに優先度判定回路ARBを形成することで、複数の割り込み要求IREQ1-3が競合するときにも情報レジスタIREG1-3の値をバッファBUFに確実に書き込みできる。

**【 0 0 7 0 】**

図12は、別の実施形態における割り込み制御回路ICNTの例を示している。上述し

50

た実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。例えば、情報処理システムIPSは、半導体集積回路として1つのチップで形成されている。割り込み制御回路ICNTを除く情報処理システムIPSの構成は、図10と同様である。

#### 【0071】

割り込み制御回路ICNTは、アドレス記憶部ADMEM1-3の代わりに、割り込み要求IREQ1-3に対応するアドレスレジスタADREG1-3を有している。各アドレスレジスタADREG1-3の機能は、図8に示したアドレスレジスタADREGと同様である。割り込み制御回路ICNTのその他の構成は、図11と同様である。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

10

#### 【0072】

図13は、別の実施形態における情報処理システムIPSの例を示している。上述した実施形態で説明した要素と同一の要素については、同一の符号を付し、これ等については、詳細な説明を省略する。この実施形態では、CPUは、割込みコントローラの機能を搭載していない。図2に示したCPUに搭載されている割り込みコントローラの機能は、割り込み制御回路ICNTに組み込まれている。

#### 【0073】

特に限定されないが、割り込み制御回路ICNTは、図11または図12のいずれかと同様である。そして、割り込み制御回路ICNTの優先度判定回路ARBにより優先された割り込み要求IREQ1-3のいずれかが、割り込み要求IREQとしてCPUに供給される。すなわち、この実施形態では、優先度判定回路ARBは、CPUに形成される割り込み要求IREQ1-3の優先度判定回路を兼ねている。このためCPUは、優先度判定回路を持たない。

20

#### 【0074】

なお、情報処理システムIPSが、CPUに接続される割り込みコントローラを有するとき、割り込みコントローラに図11または図12の割り込み制御回路ICNTの機能を持たせてもよい。以上、この実施形態においても、上述した実施形態と同様の効果を得ることができる。

#### 【0075】

以上の詳細な説明により、実施形態の特徴点および利点は明らかになるであろう。これは、特許請求の範囲がその精神および権利範囲を逸脱しない範囲で前述のような実施形態の特徴点および利点にまで及ぶことを意図するものである。また、当該技術分野において通常の知識を有する者であれば、あらゆる改良および変更に容易に想到できるはずであり、発明性を有する実施形態の範囲を前述したものに限定する意図はなく、実施形態に開示された範囲に含まれる適当な改良物および均等物に拠ることも可能である。

30

#### 【符号の説明】

#### 【0076】

ADCMPI アドレス比較器；ADECO-ADEC2 アドレスデコーダ；ADECS1-ADECS2 アドレスデコード信号；ADMEM アドレス記憶部；ADREG、ADREG1-ADREG3 アドレスレジスタ；ARB 優先度判定回路；ASW1-ASW3 スイッチ；BBRG バスブリッジ；BUF バッファ；COPY コピー中信号；DEC1、DEC2 デコーダ；HVIC 高速バスインターフェース；HSBUS 高速バスインターフェース；HSLV1、HSLV2 高速スレーブ；ICNT 割り込み制御回路；IPS 情報処理システム；IREG1、IREG2 情報レジスタ；IREQ、IREQ1-IREQ3 割り込み要求；LSBUS 低速バスインターフェース；LSLV、LSLV1、LSLV2 低速スレーブ；M0-M3 マスターポート；MST マスター；MSTIF マスターインターフェース；PRIREG 優先度設定レジスタ；REMAP リマップ信号；S0-S2 スレーブポート；SLVIF スレーブインターフェース；SW 切替回路；WAIT ウエイト要求

40

【図1】

一実施形態における情報処理システムの例を示す図

【図2】

【図3】

図2の割り込み制御回路の例を示す図

【図4】

図2のアドレスコードの例を示す図

【図5】

【図6】

( 7 )

〔 四 8 〕

【図 9】

図7のアドレスコーダの例を示す図

【図 10】

別のある施設におけるシステムの例を示す図

【図 11】

図10の割り込み制御回路の例を示す図

【図 12】

別のある施設における割り込み制御回路の例を示す図

【図 1 3】

---

フロントページの続き

審査官 古河 雅輝

(56)参考文献 特開2006-236234(JP,A)

特開2000-242507(JP,A)

特開2005-031933(JP,A)

特開2009-069962(JP,A)

特開2007-272554(JP,A)

特開2005-115658(JP,A)

特開2009-009191(JP,A)

特開平11-272600(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 46 - 9 / 54

G 06 F 13 / 10 - 13 / 14

G 06 F 13 / 20 - 13 / 42