(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5930834号

(P5930834)

(45) 発行日 平成28年6月8日(2016.6.8)

(24) 登録日 平成28年5月13日(2016.5.13)

(51) Int.Cl.

G 0 6 T 1/20 (2006.01)

F 1

G 0 6 T 1/20

A

請求項の数 20 (全 21 頁)

(21) 出願番号 特願2012-106312 (P2012-106312)

(22) 出願日 平成24年5月7日 (2012.5.7)

(65) 公開番号 特開2013-84238 (P2013-84238A)

(43) 公開日 平成25年5月9日 (2013.5.9)

審査請求日 平成27年4月28日 (2015.4.28)

(31) 優先権主張番号 特願2011-211599 (P2011-211599)

(32) 優先日 平成23年9月27日 (2011.9.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 画像処理装置、画像処理方法、画像処理装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

部分画像データに含まれている画素データを逐次的に入力する入力手段と、

前記入力手段から入力される画素データを処理して処理済画素データを出力する処理手段と、

前記入力手段が前記部分画像データに含まれる入力着目画素データを前記処理手段に入力することに応じて、前記処理済画素データのうち後段のブロックと同期をとるための出力着目画素データを出力する出力制御手段と

を有することを特徴とする画像処理装置。

## 【請求項 2】

前記部分画像データは、処理対象画像を帯状に分割したバンド画像であり、

前記入力着目画素データは、前記入力手段が入力するバンド画像に含まれる画素データのうち最後に前記入力手段に入力される画素データであり、

前記出力着目画素データは、前記処理手段が前記バンド画像に関して出力する処理済画素データのうち最後に出力する画素データである

ことを特徴とする請求項 1 に記載の画像処理装置。

## 【請求項 3】

前記入力着目画素データは、前記入力手段が入力する部分画像データに含まれる画素データのうち最後に前記入力手段に入力される画素データであり、

前記出力着目画素データは、前記処理手段が前記部分画像データに関して出力する処理

10

20

済画素データのうち最後に出力する画素データであることを特徴とする請求項 1 に記載の画像処理装置。

**【請求項 4】**

前記入力着目画素データは、前記入力手段が入力する部分画像データに含まれる画素データのうち特定領域または画素を識別するための画素データであり、

前記出力着目画素データは、前記処理手段が前記部分画像データに関して出力する処理済画素データのうち特定領域または画素を識別するための画素データである

ことを特徴とする請求項 1 に記載の画像処理装置。

**【請求項 5】**

前記処理手段は、入力画素数と出力画素数が異なる画像処理を実施することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の画像処理装置。 10

**【請求項 6】**

前記出力制御手段は、前記出力着目画素データを出力する際に、該出力着目画素データを出力したことを示す同期信号を出力することを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の画像処理装置。

**【請求項 7】**

前記同期信号は、サイドバンド信号で伝送されることを特徴とする請求項 6 に記載の画像処理装置。

**【請求項 8】**

前記入力手段は、部分画像データに含まれている複数の画素データを格納するデータパケットを逐次的に入力し、前記入力着目画素データを含むデータパケットが前記入力手段によって入力されることに応じて、前記出力制御手段が前記処理手段の処理済画素データのうち後段のブロックと同期をとるための出力着目画素データを含むデータパケットを出力することを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の画像処理装置。 20

**【請求項 9】**

前記出力制御手段は、前記出力着目画素データを含めることを示すフラグを、前記出力着目画素データを有するデータパケットに格納して出力することを特徴とする請求項 8 に記載の画像処理装置。

**【請求項 10】**

前記出力制御手段は、前記処理手段の処理した処理済画素データを保持する保持手段を備え、 30

前記保持手段に前記出力着目画素データが保持されるまでは前記後段のブロックと 2 線式ハンドシェークを実施し、前記出力着目画素データが前記保持手段に保持されると前記後段のブロックへの v a l i d 信号を無効にすることを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の画像処理装置。

**【請求項 11】**

前記処理手段はトリミング処理を実施することを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載の画像処理装置。

**【請求項 12】**

前記処理手段はフィルタ処理を実施することを特徴とする請求項 1 乃至 11 のいずれか 1 項に記載の画像処理装置。 40

**【請求項 13】**

前記処理手段は変倍処理を実施することを特徴とする請求項 1 乃至 12 のいずれか 1 項に記載の画像処理装置。

**【請求項 14】**

前記出力制御手段からの前記出力着目画素データを受信して出力する、前記後段のブロックとしての出力手段と、

前記出力手段が前記出力着目画素データを受信したことに応じて、前記入力手段に次の部分画像データに含まれる画素データを入力させるように制御するプロセッサと

を更に有することを特徴とする請求項 1 乃至 13 のいずれか 1 項に記載の画像処理装置 50

。

### 【請求項 15】

部分画像データに含まれている画素データを順次入力する入力手段と、

前記入力手段から入力される画素データを処理して処理済画素データを出力する処理手段と、

前記部分画像データにおいて前記入力手段に最後に入力される画素データである入力着目画素データが前記処理手段に入力されたこと検出する第1検出手段と、

前記部分画像データにおいて前記処理手段が最後に処理する画素データである出力着目画素データを前記処理手段が出力したことを検出する第2検出手段と、

前記処理手段が前記出力着目画素データを出力したことを前記第2検出手段が検出した場合、前記入力着目画素データが前記処理手段に入力されたことを前記第1検出手段が検出するまで、前記処理手段から出力された出力着目画素データを保持し、前記入力着目画素データが前記処理手段に入力されたことを前記第1検出手段が検出した場合に、該保持されている出力着目画素データを出力する出力制御手段と

を備えることを特徴とする画像処理装置。

### 【請求項 16】

処理対象の画像を規定の単位領域ごとに読み出し、該読み出した単位領域内のそれぞれの画素を順次、入力する入力手段と、

着目単位領域から前記入力手段が入力した1以上の画素の画素値を用いて該着目単位領域内の画像に対して画像処理を行うことで該画像中の各画素の画素値を確定させ、該確定した画素値を順次、規定の出力先に出力する画像処理手段と

を備え、

前記画像処理手段は、

入力された画素値を処理して処理済みの画素値を確定する処理手段と、

前記処理手段が確定した画素値が、前記着目単位領域について出力する着目画素の画素値であるか否かを判断する判断手段と、

前記判断手段により前記処理手段が確定した画素値が前記着目単位領域について出力する着目画素の画素値であると判断されると、前記入力手段によって前記着目単位領域内の全ての画素が入力されるまでその出力を待機させ、前記入力手段によって前記全ての画素が入力されると、待機させた画素値の出力を許可する制御手段と

を備えることを特徴とする画像処理装置。

### 【請求項 17】

前記規定の出力先は、前記画像処理手段から出力された画素値を外部に出力すると、前記着目単位領域の次の単位領域に対する読み出し指示を前記入力手段に対して行うこととする特徴とする請求項16に記載の画像処理装置。

### 【請求項 18】

部分画像データに含まれている画素データを逐次的に入力する入力手段と、前記入力手段から入力される画素データを処理して処理済画素データを出力する処理手段と、を備える画像処理装置の制御方法であって、

前記入力手段が前記部分画像データに含まれる入力着目画素データを前記処理手段に入力することに応じて、前記処理済画素データのうち後段のブロックと同期をとるための出力着目画素データを出力することを特徴とする画像処理装置の制御方法。

### 【請求項 19】

部分画像データに含まれている画素データを順次入力する入力手段と、

前記入力手段から入力される画素データを処理して処理済画素データを出力する処理手段と

を有する画像処理装置が行う画像処理方法であって、

前記画像処理装置の第1検出手段が、前記部分画像データにおいて前記入力手段に最後に入力される画素データである入力着目画素データが前記処理手段に入力されたこと検出する第1検出工程と、

10

20

30

40

50

前記画像処理装置の第2検出手段が、前記部分画像データにおいて前記処理手段が最後に処理する画素データである出力着目画素データを前記処理手段がOutputしたことを検出する第2検出工程と、

前記画像処理装置の出力制御手段が、前記処理手段が前記Output着目画素データをOutputしたことを前記第2検出工程で検出した場合、前記入力着目画素データが前記処理手段に入力されたことを前記第1検出工程で検出するまで、前記処理手段からOutputされた出力着目画素データを保持し、前記入力着目画素データが前記処理手段に入力されたことを前記第1検出工程で検出した場合に、該保持されている出力着目画素データをOutputする出力制御工程と

を備えることを特徴とする画像処理方法。

10

【請求項20】

画像処理装置が行う画像処理方法であって、

前記画像処理装置の入力手段が、処理対象の画像を規定の単位領域ごとに読み出し、該読み出した単位領域内のそれぞれの画素を順次、入力する入力工程と、

前記画像処理装置の画像処理手段が、着目単位領域から前記入力工程で入力した1以上の画素の画素値を用いて該着目単位領域内の画像に対して画像処理を行うことで該画像中の各画素の画素値を確定させ、該確定した画素値を順次、規定の出力先に出力する画像処理工程と

を備え、

前記画像処理工程は、

20

入力された画素値を処理して処理済みの画素値を確定する処理工程と、

前記処理工程で確定した画素値が、前記着目単位領域について出力する着目画素の画素値であるか否かを判断する判断工程と、

前記判断工程において前記処理工程で確定した画素値が前記着目単位領域について出力する着目画素の画素値であると判断されると、前記入力工程で前記着目単位領域内の全ての画素が入力されるまでその出力を待機させ、前記入力工程で前記全ての画素が入力されると、待機させた画素値の出力を許可する制御工程と

を備えることを特徴とする画像処理方法。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、画像を部分領域ごとに処理する画像処理技術に関する。

【背景技術】

【0002】

従来、画像処理モジュールにおいては、CPUが入力部へ開始信号を送り、これに応じて入力部がメモリに保存された画像データを画像処理部へ入力し、出力部が処理済みのデータをメモリに出力する。そして、所定の領域の処理が終了すると、出力部がCPUへ終了信号を送るといったシーケンスで画像処理が行われていた。

【0003】

通常、上記画像処理は、所定の領域単位で行われる。所定の領域単位とは、例えばページ、バンド、ブロック等である。以下、所定の領域単位が、バンド(1ページの画像データを帯状に複数の領域に分割した場合の1つの帯状の領域)の場合で説明する。

40

【0004】

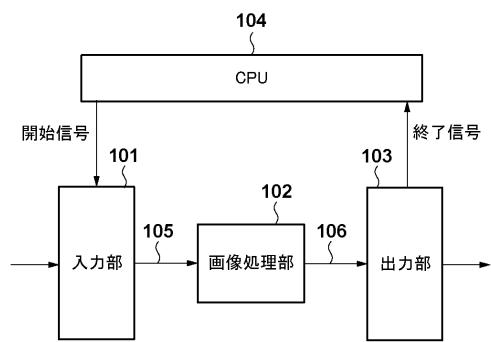

図1は、上記画像処理モジュールの概略構成を示すブロック図である。図1において、入力部101は、図示しないメモリに保存されている画像データを、信号線105を介してバンド単位で画像処理部102へ入力する。画像処理部102は、入力部101から入力されたデータに対してバンド単位で画像処理を行い、信号線106を介して画像処理済みのデータを出力部103へ送る。出力部103は、画像処理済みのデータを図示しないメモリへ出力していく、1バンドの処理が終了すると、終了信号をCPU104へ送る。このため、出力部103は、1バンドの処理の終了を検出する必要がある。

50

**【0005】**

そこで、画像処理部102において、出力データが1バンドの最後の出力画素である時に、バンド終了の識別情報を付加していた。以下、このバンド終了の識別情報を出力バンドエンド信号と記す。

**【0006】**

同様に入力部101においても、出力データが1バンドの最後の出力画素である時に、バンド終了の識別情報を付加していた。以下、このバンド終了の識別情報を入力バンドエンド信号と記す。

**【0007】**

出力部103は、画像処理部102から出力バンドエンド信号を受け取ると、1バンドの画像処理が終了したと認識し、CPU104へ終了信号を送る。CPU104は、出力部103から終了信号を受け取ると、1バンドの処理が終了したと判断し、次のバンドの処理を開始するために、入力部101へ開始信号を送る。そして、CPU104から開始信号を受け取った入力部101は、次のバンドのデータをメモリから画像処理部102へ入力し、画像処理部102は次のバンドのデータの処理を開始する。以降、バンド単位で上記画像処理を繰り返し行っていくことで、1ページ分の画像データに対して所定の画像処理が行われる。

**【先行技術文献】****【特許文献】****【0008】**

【特許文献1】特開2002-150281号公報

20

**【発明の概要】****【発明が解決しようとする課題】****【0009】**

しかし、上記の画像処理では、画像処理部102が、入力部101からの入力バンドエンド信号を受け取る前に、出力部103へ出力バンドエンド信号を送ってしまう場合があった。例えば、トリミング処理において入力画像の後半を切取る場合、入力画像の前半の最後の画素データ（最後の出力データ）に上記出力バンドエンド信号を附加して送っていた。

**【0010】**

30

そのため、入力部101にて1バンド分のデータ出力が終了する前にCPU104は現バンドの処理が終了したと判断し、次のバンドの処理を開始するために上記の開始信号を送るため、入力部101において誤動作するという問題があった。また、複数の画像処理部を数珠状に接続してパイプライン処理する場合は、途中の画像処理部においても同様の問題が発生する。特に、この場合はレイテンシ（遅延量）が大きくなるため、問題が発生し易い。

**【0011】**

本発明はこのような問題に鑑みてなされたものであり、画像を規定の単位領域ごとに処理する場合における誤動作を防止するための技術を提供することを目的とする。

**【課題を解決するための手段】**

40

**【0012】**

上述の目的を達成するために、本発明にかかる画像処理装置は、部分画像データに含まれている画素データを逐次的に入力する入力手段と、前記入力手段から入力される画素データを処理して処理済画素データを出力する処理手段と、前記入力手段が前記部分画像データに含まれる入力着目画素データを前記処理手段に入力することに応じて、前記処理済画素データのうち後段のブロックと同期をとるための出力着目画素データを出力する出力制御手段とを有することを特徴とする。

**【発明の効果】****【0013】**

本発明の構成によれば、画像を規定の単位領域ごとに処理する場合における誤動作を効

50

率的に抑制することができる。

【図面の簡単な説明】

【0014】

【図1】画像処理装置の機能構成例を示すブロック図である。

【図2】画像処理部102の機能構成例を示すブロック図である。

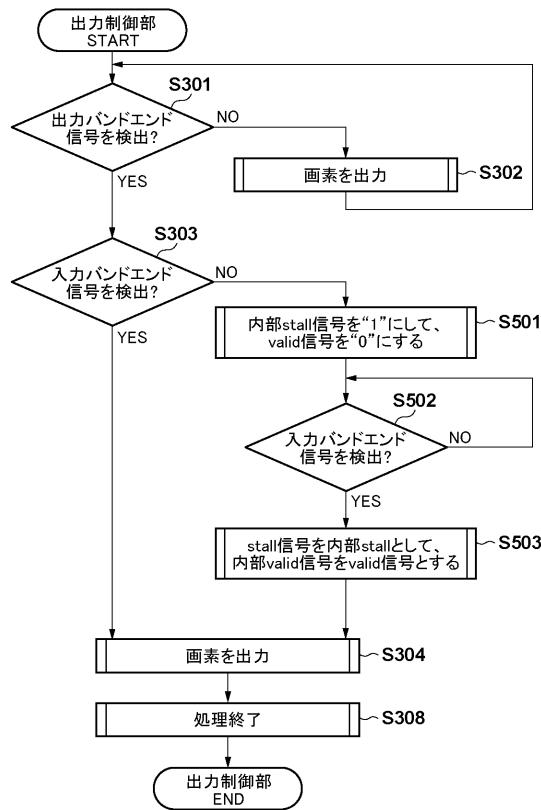

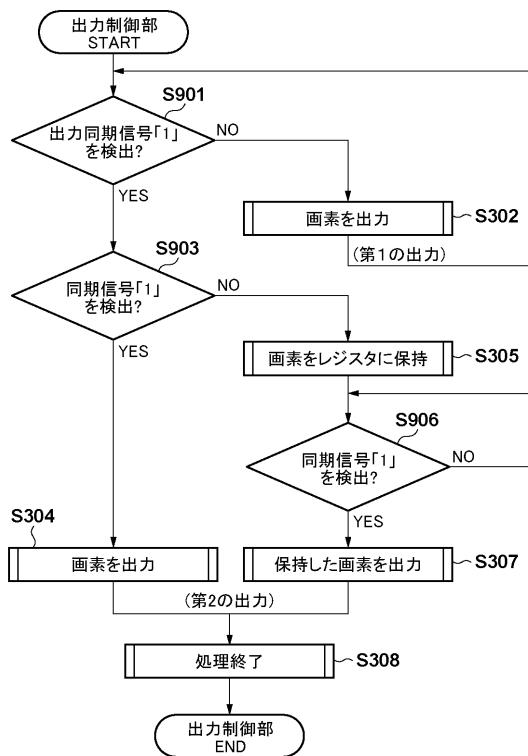

【図3】出力制御部204が行う処理のフローチャートである。

【図4】出力制御部204の機能構成例を示すブロック図である。

【図5】出力制御部204が行う処理のフローチャートである。

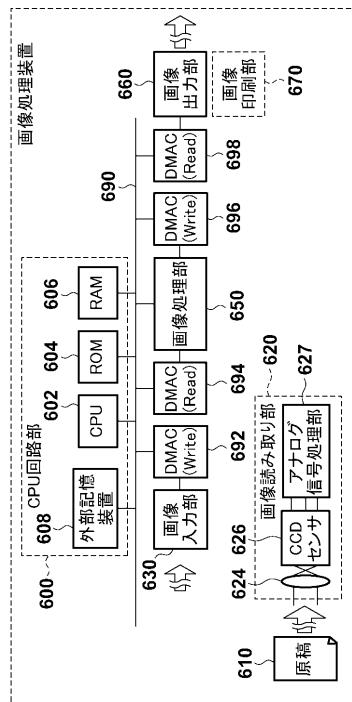

【図6】画像処理装置の機能構成例を示すブロック図である。

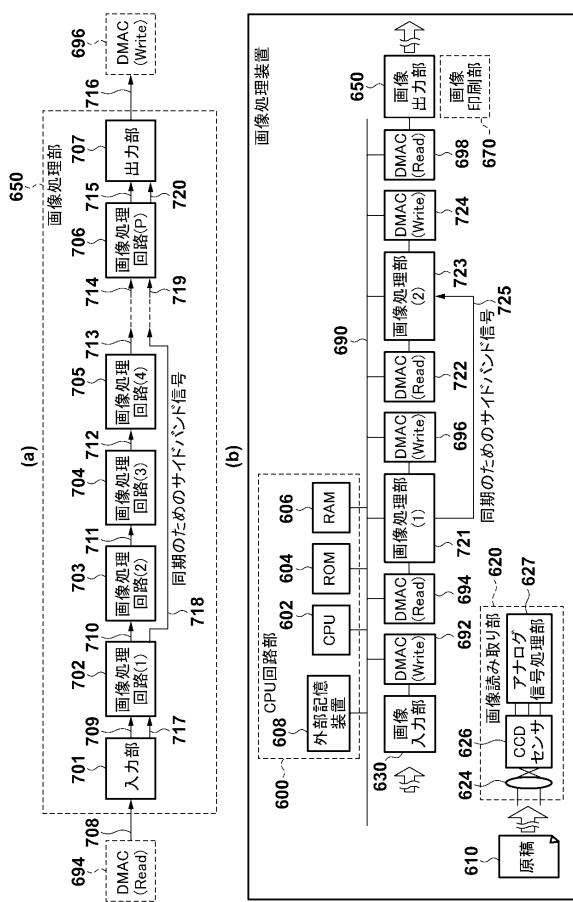

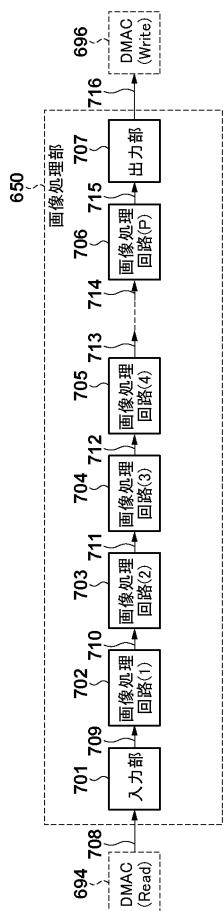

【図7】画像処理部650と画像処理装置の機能構成例を示すブロック図。 10

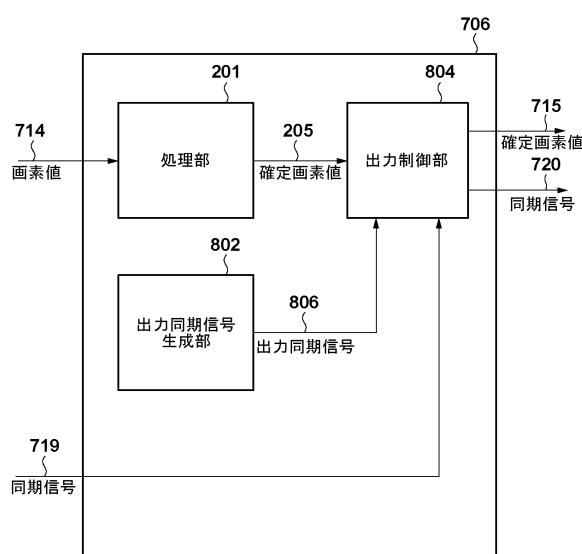

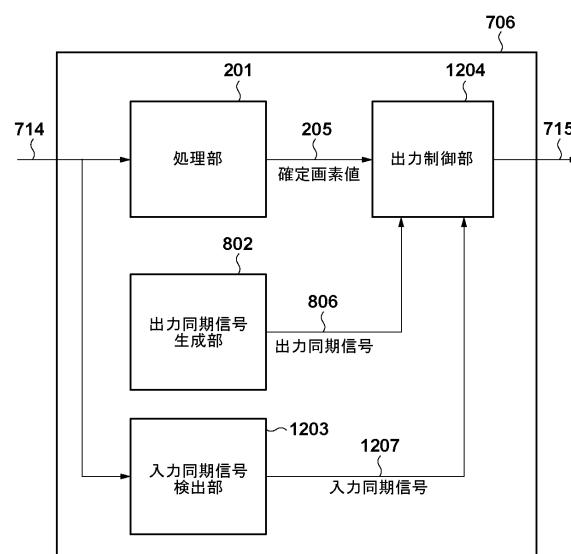

【図8】画像処理回路706の機能構成例を示すブロック図である。

【図9】出力制御部804が行う処理のフローチャートである。

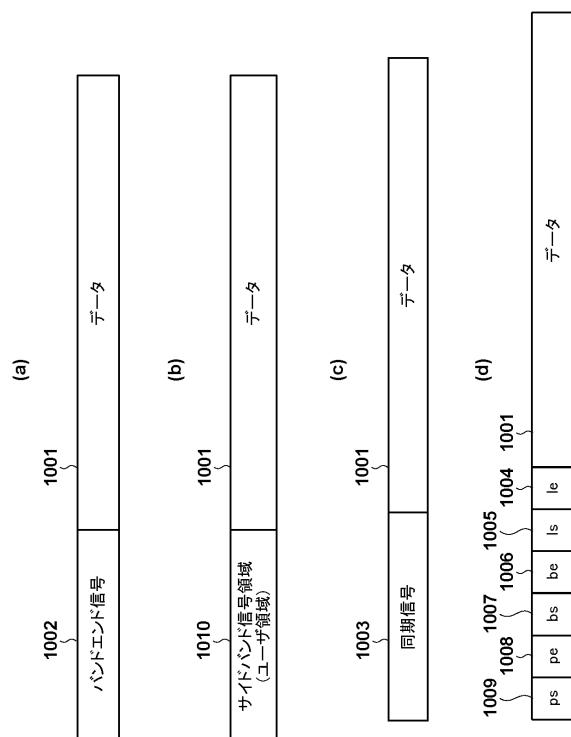

【図10】データパケット構造の一例を示す図である。

【図11】画像処理部650の機能構成例を示すブロック図である。

【図12】画像処理回路706の機能構成例を示すブロック図である。

【発明を実施するための形態】

【0015】

以下、添付図面を参照し、本発明の好適な実施形態について説明する。なお、以下説明する実施形態は、本発明を具体的に実施した場合の一例を示すもので、特許請求の範囲に記載の構成の具体的な実施例の1つである。 20

【0016】

【第1の実施形態】

本実施形態に係る画像処理装置は、図1に示した機能構成例を有するものの、画像処理部102の構成が図2の構成を有する。然るに、画像処理装置の構成は、図1に示した構成に限るものではなく、図2に示した機能構成例を有する画像処理部102が適用可能な構成であれば、如何なる構成であってもよい。

【0017】

入力部101は、不図示のメモリに格納されている処理対象画像を規定の単位領域ごとに読み出し、該読み出した単位領域内のそれぞれの画素データ（画素値）を順次、信号線105を介して画像処理部102に対して供給する。 30

【0018】

本実施形態では、この「規定の単位領域」は上記の「バンド（バンド画像）」であるものとする。然るに本実施形態では入力部101は、不図示のメモリに格納されている処理対象画像をバンドごとに読み出し、該読み出したバンド内のそれぞれの画素データ（画素値）を順次、信号線105を介して画像処理部102に対して供給する。

【0019】

また、本実施形態では、入力部101は、1つのバンド内の各画素を画像処理部102に入力する場合、該バンド内の左上隅から右下隅までの各位置をラスタスキヤ順に参照し、参照した位置における画素の画素値を画像処理部102に入力する。しかし、画像処理部102への画素入力順はこれに限るものではない。 40

【0020】

また、入力部101は、1つのバンド内の各画素の画素値を画像処理部102に送出すると、CPU104（プロセッサ）からの開始信号を待機し、開始信号を受けると、次のバンド内の各画素の画素値を画像処理部102に送出する。即ち入力部101は、開始信号を受けるたびに（読み出し指示を受けるたびに）、次のバンド内の各画素の画素値を画像処理部102に供給する。

【0021】

なお、バンドとは画像を副走査方向について短冊状に分割した部分画像である。しかし、規定の単位領域はバンドに限るものではなく、単に処理対象画像を複数の矩形領域に分割した場合の1つの矩形領域を「規定の単位領域」としてもよいし、何らかの分割方法で 50

処理対象画像を分割した場合の 1 つの領域を「規定の単位領域」としてもよい。

【 0 0 2 2 】

画像処理部 102 は、入力部 101 からバンドごとに、該バンド内のそれぞれの画素の画素値を順次受けるので、受けた画素値を用いて、該バンドに対する画像処理を行うことで、該バンド内の各画素の画素値を確定させる。ここで、画像処理部 102 は、処理の内容によっては、入力部 101 から入力されたバンド内の全ての画素の画素値を用いて該バンド内の各画素の画素値を確定させるわけではなく、1 以上の画素の画素値を用いて該バンド内の各画素の画素値を確定させる。換言すれば、着目単位領域から入力部 101 が入力した 1 以上の画素の画素値を用いて、該着目単位領域内の画像に対して画像処理を行うことで、該画像中の各画素の画素値を確定させる。

10

【 0 0 2 3 】

そして画像処理部 102 は、バンドごとに、該バンド内の各画素の確定画素値を、信号線 106 を介して出力部 103 に対して送出する。画像処理部 102 について詳しくは後述する。

【 0 0 2 4 】

出力部 103 は、画像処理部 102 からバンドごとに送出される、該バンド内の各画素の確定画素値を受けると、この確定画素値を外部（例えば不図示のメモリや外部装置）に対して送出する。また出力部 103 は、1 つのバンドについて確定画素値群を送出するたびに、終了信号を C P U 104 に対して送出する。

20

【 0 0 2 5 】

C P U 104 は出力部 103 から終了信号を受けると、入力部 101 に対し、上記メモリに格納されている処理対象画像から次のバンドの画像を読み出し、該読み出した画像内のそれぞれの画素を順次、画像処理部 102 に入力する為の開始信号を送出する。これにより入力部 101 は、次のバンドの画像を読み出し、該読み出した画像内のそれぞれの画素を順次、画像処理部 102 に供給し、画像処理部 102 は、次のバンドの画像に対して画像処理を行う。このようにして、バンドごとに画像処理を行う。

【 0 0 2 6 】

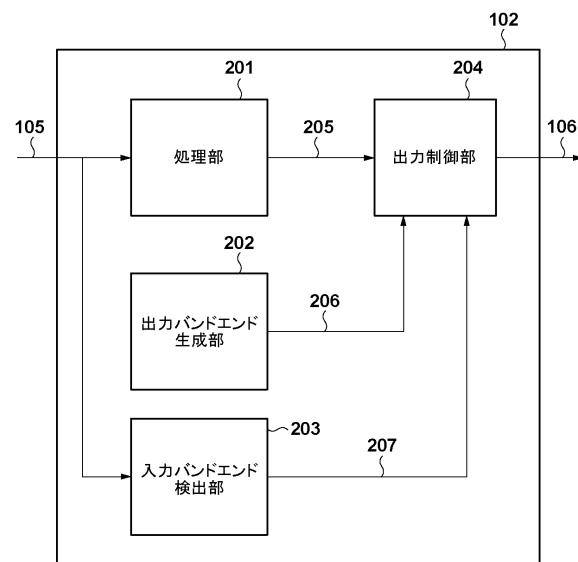

次に、画像処理部 102 の機能構成例について、図 2 のブロック図を用いて説明する。以下では、入力部 101 から着目バンド内の各画素（各画素値）が信号線 105 を介して画像処理部 102 に入力された場合における画像処理部 102 の動作について説明する。しかるに画像処理部 102 は、以下に説明する処理を、各バンドについて行うことになる。

30

【 0 0 2 7 】

着目バンド内の各画素の画素値は順次処理部 201 に入力されるので、処理部 201 は、着目バンドにおける 1 以上の画素の画素値を用いて、該着目バンド内の画像に対して画像処理を行うことで、該画像中の各画素の画素値を確定させる。そして処理部 201 は、各画素の確定画素値を順次、出力制御部 204 に対して送出する。

【 0 0 2 8 】

ここで、処理部 201 が、トリミング処理を行って入力画像の後半を切取る場合、処理部 201 が出力する着目バンドの大きさは、処理部 201 へ入力される着目バンドの大きさより小さくなる。従って、「処理部 201 が着目バンドの最後の画素値を出力する」タイミングは、「処理部 201 へ着目バンドの最後の画素値が入力される」タイミングより早くくなってしまう。このため、実際の処理の終了のタイミングより早くに終了を判定してしまう現象が発生してしまっていた。以降、「処理部 201 が着目バンドの最後の画素値を出力する」タイミングを出力タイミングとし、「処理部 201 へ着目バンドの最後の画素値が入力される」タイミングを入力タイミングとする。

40

【 0 0 2 9 】

次に、本実施形態の処理を簡単に説明する。まず、出力バンドエンド生成部 202 が出力タイミングを検知し、入力バンドエンド検出部 203 が入力タイミングを検知する。そして出力制御部 204 が、検出した出力タイミングと入力タイミングに基づいて「処理部

50

201へ着目バンドの最後の画素の画素値が入力される」のを待ってから、「処理部201によって処理した着目バンドの最後の画素の画素値を出力する」ように制御する。なお、トリミングや変倍処理、フィルタ処理のように処理部201が出力画素数と入力画素数とが異なる画像処理を実施する場合は、「処理部201へ入力する着目バンドの最後の画素」と「処理部201から出力する着目バンドの最後の画素」は異なる。

#### 【0030】

次に、出力バンドエンド生成部202と入力バンドエンド検出部203と出力制御部204が行う動作について詳細に説明する。最初に、出力バンドエンド生成部202が出力タイミングを検知する動作について説明する。出力バンドエンド生成部202は、処理部201が送出した確定画素値が、着目バンドについて出力する最後の画素（ここでは、出力着目画素）の画素値であるか否か、即ち、処理部201が出力着目画素（出力着目画素データ）を出力したか否かを識別する。

10

#### 【0031】

この処理部201が出力着目画素を出力したか否かの判断は、例えば、次のようにして行えよ。先ず、処理部201が着目バンドについて処理を開始する前にカウンタを0にリセットしておき、処理部201から確定画素値が出力されるたびにカウンタの値を1つインクリメントする。そして、このカウンタの値が「出力する1バンド内の画素数」に達した場合に、「処理部201が出力着目画素を出力した」と判断する。即ち、「処理部201がトリミング処理を行って出力する1バンドの画素数」にカウンタ値が達した場合に、「処理部201がトリミング処理を行って出力する1バンドの最後の画素を出力した」と判断する。もちろん、処理部201が出力着目画素を出力したか否かの判断方法は、このような方法に限るものではない。

20

#### 【0032】

そして出力バンドエンド生成部202は、「処理部201が出力着目画素を出力した」と判断した場合には、出力バンドエンド信号を、信号線206を介して出力制御部204に対して送出する。もちろん、出力バンドエンド生成部202は、「処理部201はまだ出力着目画素を出力していない」と判断した場合には、出力バンドエンド信号の送出を待機する。

#### 【0033】

次に、入力バンドエンド検出部203が入力タイミングを検知する動作について説明する。入力バンドエンド検出部203は、着目バンド内の全ての画素が信号線105を介して処理部201に入力されたことを検知した場合に、入力バンドエンド信号を、信号線207を介して出力制御部204に対して送出する。この検知方法は特定の方法に限るものではない。例えば、入力部101が、最後の画素に入力バンドエンド信号を示す情報（バンドエンドフラグ）を附加したとする。この場合、入力バンドエンド検出部203は、信号線105を介して入力された画素に入力バンドエンド信号を示す情報が附加されれば、着目バンド内の全ての画素が信号線105を介して処理部201に入力された、と判断する。

30

#### 【0034】

次に、出力制御部204の動作について説明する。出力制御部204は、処理部201から送出された確定画素値をそのまま信号線106を介して出力部103に送出する。この送出は、出力バンドエンド生成部202から出力バンドエンド信号を受けるまで続けられる。そして出力制御部204は、出力バンドエンド生成部202から出力バンドエンド信号を受けると、この送出を一旦停止する。この時点では、出力着目画素以外の画素の画素値については送出し、出力着目画素についてはまだ送出していない状態となっている。そして出力制御部204は、この時点で入力バンドエンド検出部203から入力バンドエンド信号を受けているか否かを判断する。そしてこの判断の結果、この時点で入力バンドエンド信号を受けている場合には、出力着目画素を、信号線106を介して出力部103に送出する。一方、この判断の結果、この時点で入力バンドエンド信号を受けていない場合には、入力バンドエンド信号を受けるまでこの出力着目画素を保持しておき、入力バン

40

50

ドエンド信号を受けると、出力着目画素を、信号線 106 を介して出力部 103 に送出する。即ち出力制御部 204 は、これから出力しようとする画素値が着目バンドについて出力する最後の画素値である場合、着目バンド内の全ての画素が入力されるまでその出力を待機させ、全ての画素が入力されると、待機させた画素値の出力を許可する。この待機 / 許可の制御は出力制御部 204 が行っても良いし、不図示の制御部が行っても良い。何れの場合でも出力制御部 204 は、出力着目画素に対しては、出力バンドエンド信号を示す情報を附加して送出する。出力バンドエンド信号を示す情報は、画素データ（ピクセルデータ）に附加されるものとする。図 10 (a) は、本実施形態におけるデータパケットの構造の一例を示す図である。フィールド 1001 は処理されるデータを格納する。フィールド 1002 は処理部 201 が送出した画素の画素値が、最後の画素の画素値であるかどうかを示す出力バンドエンド信号を格納する。

【0035】

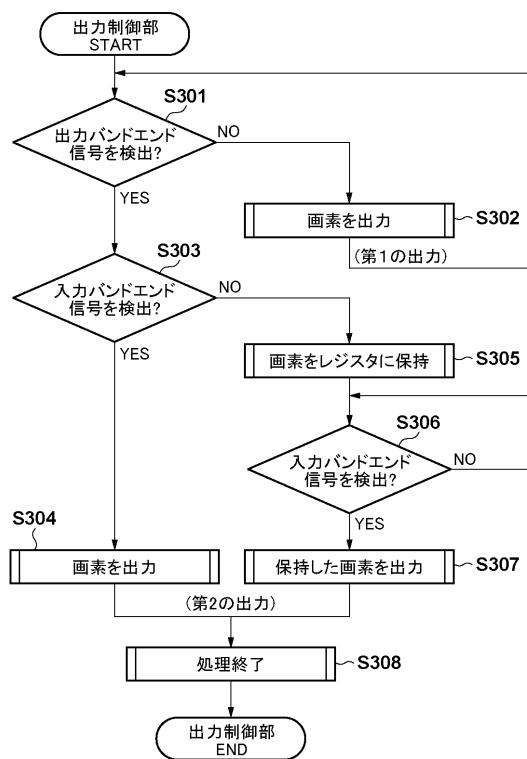

次に、出力制御部 204 が行う処理について、同処理のフローチャートを示す図 3 を用いて説明する。

【0036】

ステップ S301 では、出力制御部 204 は、信号線 206 を介して出力バンドエンド生成部 202 から出力バンドエンド信号を受信したか否かを判断する。この判断の結果、受信していない場合は、処理はステップ S302 に進み、受信した場合は、処理はステップ S303 に進む。

【0037】

ステップ S302 では、出力制御部 204 は、処理部 201 から送出されることが確定した画素の画素値を、信号線 106 を介して、規定の出力先としての出力部 103 に送出する（第 1 の出力）。

【0038】

ステップ S303 では、出力制御部 204 は、入力バンドエンド検出部 203 から入力バンドエンド信号を受信したか否かを判断する。受信していないと判断される場合は処理はステップ S305 に進み、受信していると判断される場合はステップ S304 に進む。ステップ S304 では、出力制御部 204 は、出力着目画素を、信号線 106 を介して、規定の出力先としての出力部 103 に送出する（第 2 の出力）。

【0039】

一方、ステップ S305 では、出力制御部 204 は、出力着目画素を、画像処理部 102 内若しくは画像処理装置内のメモリ（レジスタ）に格納する。そしてステップ S306 では出力制御部 204 は、入力バンドエンド検出部 203 から入力バンドエンド信号を受信したか否かを判断する。この判断の結果、受信していない場合はステップ S306 に戻り、受信している場合はステップ S307 に進む。

【0040】

ステップ S307 では、出力制御部 204 は、ステップ S305 でメモリに格納した出力着目画素を、信号線 106 を介して出力部 103 に送出する（第 2 の出力）。そしてステップ S308 では、出力制御部 204 は、適当な終了処理を行う。

【0041】

以上の説明により本実施形態によれば、入力バンドエンド信号を検出するまで出力着目画素を保持し、入力バンドエンド信号を検出してから出力するようにしたので、入力バンドエンド信号を受け取る前に出力バンドエンド信号を出力してしまうことがなくなる。そのため、バンド単位の画像処理を誤動作なく連続して行うことが可能となる。

【0042】

[第 2 の実施形態]

本実施形態では、第 1 の実施形態で説明した出力制御部 204 に適用可能な構成について説明する。本実施形態で説明する出力制御部 204 は、valid 信号と stall 信号を用いた公知の 2 線式ハンドシェークを用いてデータの受け渡しを行う。

【0043】

10

20

30

40

50

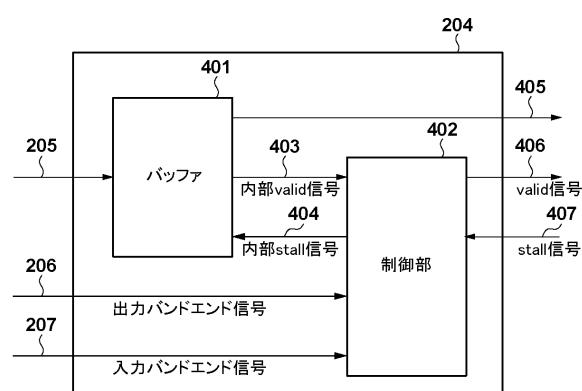

本実施形態に係る出力制御部 204 の機能構成例を図 4 に示す。

最初に、図 4 に示した内部 valid 信号（信号線 403）、内部 stall 信号（信号線 404）、valid 信号（信号線 406）、stall 信号（信号線 407）について説明する。

【0044】

内部 valid 信号は、バッファ 401 が、信号線 403 を介して制御部 402 に送出する信号であり、バッファ 401 に出力することが確定している画素の画素値（以降、単に確定画素値と称す）が格納されているか否かを示す信号である。例えば、バッファ 401 に確定画素値が格納されていない状態では、バッファ 401 は、信号線 403 を介して内部 valid 信号「0」を制御部 402 に対して送出する。

10

【0045】

一方、バッファ 401 に確定画素値が格納されると、バッファ 401 は、信号線 403 を介して内部 valid 信号「1」を制御部 402 に対して送出し、確定画素値を格納していることを通知する。

【0046】

内部 stall 信号は、制御部 402 が信号線 404 を介してバッファ 401 へ送出する信号であり、バッファ 401 によるデータ出力を停止させるか否かを示す信号である。例えば、制御部 402 が内部 stall 信号「1」をバッファ 401 に送出した場合に、制御部 402 からデータ出力の停止の依頼があったものとしてバッファ 401 がデータ出力を停止する。一方で、制御部 402 が内部 stall 信号「0」をバッファ 401 に送出した場合に、制御部 402 からデータ出力の停止の依頼がないものとしてバッファ 401 がデータ出力を継続する。

20

【0047】

stall 信号は、後段の出力部 103 が信号線 407 を介して制御部 402 へ送出する信号であり、後段の出力部 103 がデータを受付可能であるか否かを示すものである。例えば、出力部 103 は、データを受け付け可能である場合には stall 信号「0」を出し、データを受け付け不可能である場合には stall 信号「1」を送出する。

【0048】

valid 信号は、制御部 402 が信号線 406 を介して後段の出力部 103 へ送出する信号であり、出力制御部 204 から出力されたデータが有効であるか否かを示す信号である。例えば、出力制御部 204 から出力されたデータが有効である場合、制御部 402 は valid 信号「1」を出力部 103 へ送出する。一方、出力制御部 204 から出力されたデータが有効でない場合、制御部 402 は valid 信号「0」を出力部 103 へ送出する。

30

【0049】

次に、出力バンドエンド生成部 202 が信号線 206 を介して制御部 402 へ送出する出力バンドエンド信号と、入力バンドエンド検出部 203 が信号線 207 を介して制御部 402 へ送出する入力バンドエンド信号について説明する。なお、以降の説明では信号名称に信号線の符号を用いて簡略的に説明する。

【0050】

40

本実施形態では、出力バンドエンド生成部 202、入力バンドエンド検出部 203 のそれぞれは常に出力バンドエンド信号（信号線 206）、入力バンドエンド信号（信号線 207）を送出している。出力バンドエンド生成部 202 は処理部 201 が出力着目画素を出力した場合、有効値（= 1）を有する出力バンドエンド信号（信号線 206）を送出する。また出力バンドエンド生成部 202 は、処理部 201 がまだ出力着目画素を出力していない場合は、無効値（= 0）を有する出力バンドエンド信号（信号線 206）を送出する。入力バンドエンド検出部 203 は、着目バンド内の全ての画素が信号線 105 を介して処理部 201 に入力されたことを検知した場合は、有効値（= 1）を有する入力バンドエンド信号を出力する。一方、着目バンド内の全ての画素が信号線 105 を介して処理部 201 に入力されたことを検知していない場合、入力バンドエンド検出部 203 は、無効

50

値(=0)を有する入力バンドエンド信号を出力する。なお、厳密には、正論理において低電圧を無効値とする構成において、無効値を発行する際には信号線の電圧を0にしてもよいが、説明の簡便上、電圧を0にすることによって無効値を示す信号を出力しているものとして扱う。

#### 【0051】

次に、バッファ401について説明する。バッファ401には、処理部201から着目バンド内の各画素の確定画素値205が入力され、入力された各画素の確定画素値が格納される。

#### 【0052】

次に、制御部402について説明する。制御部402は、出力バンドエンド信号(信号線206)、入力バンドエンド信号(信号線207)、*stall*信号(信号線407)の値に応じて、バッファ401に送信する内部*stall*信号(信号線404)、出力部103に送出する出力*valid*信号(信号線406)の値を制御する。例えば、出力バンドエンド信号(信号線206)が有効値(=1)を有し、且つ入力バンドエンド信号(信号線207)が無効値(=0)を有する際に、制御部402は、内部*stall*信号(信号線404)として有効値(=1)をバッファ401に送出する。またこの場合、制御部402は、*valid*信号として無効値(=0)を出力部103に送出する。

#### 【0053】

また、内部*stall*信号(信号線404)として有効値(=1)を受信したバッファ401は、自身に保持している画素値の出力を停止する。また、*valid*信号(信号線406)として無効値(=0)を受信した出力部103は、バッファ401からの送信を無視する(信号線のデータをラッチしない)。

#### 【0054】

一方、出力バンドエンド信号が有効値でない場合(=0)、制御部402は、*stall*信号(信号線407)を内部*stall*信号(信号線404)としてバッファ401に伝達する。そして、内部*valid*信号(信号線403)を*valid*信号(信号線406)として出力部103に送出する。

#### 【0055】

次に、本実施形態に係る出力制御部204が行う処理について、同処理のフローチャートを示す図5を用いて説明する。なお、図5のフローチャートの処理を実際に行うのは、出力制御部204内の制御部402である。また、図5において、図3に示した処理と変わらないステップには同じ参照番号を付しており、その説明は省略する。

#### 【0056】

なお、ステップS302で行う処理は基本的には、第1の実施形態で説明したとおりである。しかし本実施形態では制御部402が、*stall*信号(信号線407)を内部*stall*信号(信号線404)としてバッファ401に伝達し、内部*valid*信号(信号線403)を*valid*信号(信号線406)として出力部103に送出する。これにより、第1の実施形態で説明したステップS302と同様の処理を実現している。

#### 【0057】

ステップS501で、制御部402は、内部*stall*信号(信号線404)として有効値(=1)をバッファ401に送出し、*valid*信号(信号線406)として無効値(=0)を出力部103に送出する。

#### 【0058】

ステップS502では、制御部402は、有効値(=1)を有する入力バンドエンド信号(信号線207)を受信したか否かを判断し、受信していない場合はステップS502に戻り、受信している場合はステップS503に進む。

#### 【0059】

ステップS503では制御部402は、*stall*信号(信号線407)を内部*stall*信号(信号線404)としてバッファ401に伝達する。また、内部*valid*信号(信号線403)を*valid*信号(信号線406)として出力部103に送出する。こ

10

20

30

40

50

れにより、2線式ハンドシェークと同様の手続きを用いてバッファ401から画素値を出力できる。

#### 【0060】

以上の説明により、本実施形態によれば、画像処理部102の出力制御部204が後段の出力部103とハンドシェーク制御することで、入力バンドエンド信号を検出するまで出力着目画素を保持し、入力バンドエンド信号を検出してから出力するようにした。そのため、入力バンドエンド信号を受け取る前に、出力バンドエンド信号を出力してしまうことがなくなる。そのため、バンド単位の画像処理を誤動作なく連続して行うことが可能となる。また、第1の実施形態のように入力バンドエンド信号を検出できない場合に画素を保持するためのレジスタを、確定画素値を保持する構成とは別途に追加せずに済む。なお、上記の実施形態においては、バンドエンド信号を例に説明したが、これに限らず、同期を取る必要のある信号であれば同様に適用可能である。

#### 【0061】

##### 【第3の実施形態】

第1の実施形態では、着目バンドの最後の画素に関して画像処理部102からの出力を制御していたのに対し、本実施形態は、着目バンド内の途中の特定領域あるいは特定画素（以降、着目画素と称す）に関して、画像処理回路からの出力を制御するものである。なお、本実施形態では複数段で第1、第2実施形態の入力バンドエンドと出力バンドエンドの判定と同様の処理を行う。そして、前段からの同期信号を入力着目画素（入力着目画素データ）、自身の段から出力する同期信号を出力着目画素とする。

#### 【0062】

画像処理部102は、着目バンド内の途中の出力着目画素を後段のブロックに出力する際に、同期信号を後段のブロックに出力する。この同期信号は、画像処理回路の単位領域（バンド）内のデータの入出力の同期をとるための信号であって、画像処理部102から出力される画素値が着目画素の画素値であるかどうかを判断するための着目情報に相当する。

#### 【0063】

例えば、同期信号が有効値を示す“1”的場合に、画像処理部102から送出されたデータが、着目バンド内の出力着目画素の画素値である。同期信号が無効値を示す“0”的場合は、画像処理部102から送出されたデータは、着目バンド内の出力着目画素の画素値ではない。そして、画像処理部102は、同期信号に基づいてデータ出力を制御する。

#### 【0064】

これにより、第1の実施形態や第2の実施形態のようにバンドの最後の画素でなくても、バンド内の途中の画素に関して画像処理部102の入出力の同期をとることができ、画像処理を誤動作なく連続して行うことが可能となる。以下、本実施形態について、詳細に説明する。

#### 【0065】

図6は、本実施形態を説明するための画像処理装置のブロック図である。図6において、CPU回路部600は、演算制御用のCPU602、固定データやプログラムを格納するROM604、データの一時保存やプログラムのロードに使用されるRAM606、及び外部記憶装置608等を備える。CPU回路部600は、画像入力部630、画像処理部650、及び画像出力部660等を制御し、本実施形態の画像処理装置のシーケンスを統括的に制御する。なお、外部記憶装置608は、本実施形態の画像処理装置が使用するパラメータやプログラムや補正データを記憶するディスク等の記憶媒体であり、RAM606に入力するデータやプログラム等は、外部記憶装置608からロードされる構成としても良い。

#### 【0066】

画像入力部630は、画像データを入力可能な構成であり、例えばケーブルを介して撮像画像を入力する構成や、インターネット等を介して画像データをダウンロードする構成等を備える。以下の説明では画像入力部630として、原稿610を読み取ってその画像

10

20

30

40

50

データを生成する画像読み取り部 620 を例として説明する。画像読み取り部 620 は、レンズ 624、CCD センサ 626、及びアナログ信号処理部 627 等を有する。画像読み取り部 620において、原稿 610 の画像情報がレンズ 624 を介し CCD センサ 626 に結像され、R (Red)、G (Green)、B (Blue) のアナログ電気信号に変換される。アナログ電気信号に変換された画像情報は、アナログ信号処理部 627 に入力され、R、G、B の色毎に補正等が施された後に、アナログ / デジタル変換 (A / D 変換) される。これにより、デジタル化されたフルカラー信号 (デジタル画像信号という) が生成される。

#### 【0067】

画像読み取り部 620 で生成されたデジタル画像信号は、予め動作が設定されている DMA (Direct Memory Access Controller) 692 により、共有バス 690 を介して CPU 回路部 600 の RAM 606 に格納される。なお、DMA 692 は CPU 602 によって制御される。

#### 【0068】

次に CPU 602 は DMA 694 を制御することにより、RAM 606 に格納されたデジタル画像信号を読み出して画像処理部 650 に入力する。画像処理部 650 は、入力されたデジタル画像信号に対し、例えばスキャナなどのセンサ・デバイスの読み取り素子の個体差の補正や入力ガンマ補正などの色補正を行い、読み取り画像を正規化して一定水準のデジタル画像信号を作成する。そして該処理後のデジタル画像信号を、予め書き込み動作の設定がなされた DMA 696 により、RAM 606 に再度、格納させる。

#### 【0069】

画像処理部 650 はまた、入力されたデジタル画像信号に対し、入力色補正処理、空間フィルタ処理、色空間変換、濃度補正処理、及び中間調処理などの印刷のための各種画像処理を施して、印刷可能なデジタル画像信号を作成する。作成された印刷可能なデジタル画像信号は、やはり DMA 696 によって RAM 606 に格納される。すると CPU 602 は DMA 698 を制御して、RAM 606 に格納された画像処理済みのデジタル画像信号を読み出して画像印刷部 670 へ出力する。この画像印刷部 670 としては、例えばインクジェットヘッドやサーマルヘッド等を使用したラスタプロッタ等の印刷出力部 (図示せず) を備えたプリンタとして構成され、入力されたデジタル画像信号に基づく画像を記録用紙上に形成する。

#### 【0070】

図 7 (a) に、本実施形態の画像処理部 650 が有する主要な回路構成の一例を示す。なお、画像処理回路は P 個 (P は 2 以上の整数) あるものとし、信号線 708 ~ 716 は、後段のブロックへデジタル画像信号の各画素の画素値を送出するためのデータ信号線である。信号線 717 ~ 720 は、同期信号を後段のブロックへ送出するためのサイドバンド信号線である。以下の説明では、デジタル画像信号の各画素値を単に画素値と記す。

入力部 701 は、DMA 694 からの画素値を受け取る。入力部 701 は、DMA 694 から受け取った画素値を画像処理回路 702 へ送出する。また、入力部 701 は、同期信号を画像処理回路へ送出する。

#### 【0071】

そして、入力部 701 から送られた画素値は、画像処理回路 702 ~ 画像処理回路 706 に送られ、各種補正処理もしくは画像処理が施される。

#### 【0072】

その後、出力部 707 が、補正処理済みの画素値 (確定画素値、処理済画素データ) を、DMA 696 に送り、DMA 696 が RAM 606 に補正処理済みの画素値 (確定画素値) として書き戻す。

#### 【0073】

画像処理回路 (画像処理モジュール) 702 ~ 706 では、そのいずれかにおいて入力色補正処理、空間フィルタ処理、色空間変換処理、濃度補正処理、及び中間調処理、等の画像処理をそれぞれ行っている。各画像処理回路 702 ~ 706 では、例えば 1 色 (1 ブ

10

20

30

40

50

レーン)に対する処理を行うとしても良いし、RGBやCMYKのように数色をセットとした処理を行うとしても良い。

【0074】

本実施形態では、バンド(1ページの画像データを帯状に複数の領域に分割した場合の1つの帯状の領域)毎に逐次的に画像処理を行う。

【0075】

図8に、本実施形態に係る画像処理回路706の機能構成例を示す。図8に示す構成は画像処理回路706に限らず、画像処理回路702～706において同様の構成である。

【0076】

本実施形態では、出力同期信号生成部802が出力タイミングを検知し、出力制御部804が入力タイミングを検知する。そして、出力制御部804が、入力タイミングと出力タイミングに基づいて、「処理部201へ、着目バンド内の入力着目画素の画素値が入力される」のを待ってから、「着目バンド内の出力着目画素の画素値を後段に出力する」ように制御する。次に、出力同期信号生成部802と出力制御部804が行う動作について詳細に説明する。

【0077】

まず、出力同期信号生成部802について説明する。出力同期信号生成部802は、処理部201が送出した確定画素値が、着目バンドについて出力する画素値のうち予め同期を行う画素として定めた画素(出力着目画素)の画素値であるか否かを判断する。なお、複数の段のあるステージにおける出力着目画素は、その次の段からみると入力着目画素に相当する。出力同期信号生成部802は、「処理部201が送出した確定画素値が着目バンドの出力着目画素の画素値である」と判断した場合、出力同期信号806を有効値である“1”にして、出力制御部804に送出する。そうでない場合は出力同期信号806を無効値である“0”にして、出力制御部804に送出する。この出力着目画素であるかどうかの判断は、処理部201が出力する確定画素値の数をカウントしていく、カウント値が、出力着目画素までの所定数に達したかどうかで判断すればよい。

【0078】

例えば、処理部201が着目バンドについて処理を開始する前にカウンタを0にリセットしておき、処理部201から確定画素値が出力されるたびにカウンタの値を1つインクリメントする。そして、このカウンタの値が「出力着目画素までの所定数」に達した場合に、「処理部201が、出力着目画素の画素値を出力した」と判断する。もちろん、処理部201が予め定めた同期を行う画素値を出力したか否かの判断方法は、このような方法に限るものではない。

【0079】

次に、出力制御部804について説明する。出力制御部804は、処理部201からの確定画素値205をそのまま確定画素値715として後段へ送出する。この送出は、出力同期信号生成部802から有効(=「1」)な出力同期信号806を受けるまで続けられる。そして出力制御部804は、出力同期信号生成部802から有効な出力同期信号806を受けると、確定画素値715の送出を一旦停止する。この時点では、着目バンドについて出力着目画素より前に処理部201から出力される確定画素値205については後段へ送出し、出力着目画素の画素値についてはまだ送出していない状態となっている。そして出力制御部804は、この時点で、前段のブロックから入力された同期信号719が有効な“1”であるか否かを判断する。そしてこの判断の結果、この時点で同期信号が有効である場合には、出力着目画素の画素値を確定画素値715として後段のブロックに送出する。一方、この判断の結果、この時点で同期信号719が有効でない場合には、有効な同期信号719を受けるまで出力着目画素の画素値を保持したままにする。

【0080】

即ち、出力制御部804は、自身がこれから後段へ出力しようとする画素値が出力着目画素の画素値である場合、前段の出力画素値714として入力着目画素の画素値が入力されるまで出力着目画素の画素値の出力を待機させる。そして、入力着目画素の画素値が入

10

20

30

40

50

力されると、待機させていた出力着目画素の画素値の出力を許可する。この待機／許可の制御は出力制御部 804 が行っても良いし、不図示の制御部が行っても良い。

【0081】

出力制御部 804 は、出力着目画素の画素値を確定画素値 715 として後段のブロックへ送出する際に、同期信号 720 を有効「1」にして後段のブロックへ送出する。

【0082】

次に、出力制御部 804 が行う処理について図9を用いて説明する。図9において、第1の実施形態で説明した図3に示す処理と内容が変わらないものには同じ参照番号を付してあり、その詳細な説明を省略する。

【0083】

ステップ S901 では、出力制御部 804 は、出力同期信号生成部 802 から有効な出力同期信号 806 を受信したか否かを判断する。この判断の結果、受信していない場合は、処理はステップ S302 に進み、受信した場合には、処理はステップ S903 に進む。

【0084】

ステップ S903 では、出力制御部 804 は、前段のブロックから有効な同期信号 719 を受信したか否かを判断する。受信していない場合はステップ S305 に進み、受信している場合は、処理はステップ S304 へ進む。

【0085】

ステップ S906 では、出力制御部 804 は、前段のブロックから有効な同期信号 719 を受信したか否かを判断する。受信していない場合はステップ S906 に戻り、受信している場合は、処理はステップ S307 へ進む。

【0086】

以上の説明により、本実施形態によれば、バンド内の途中の領域（画素）であっても画像処理部の入出力の同期をとることができ、画像処理を誤動作なく連続して行うことが可能となる。これにより、バンド内の特定領域に対する適応処理や計測（特定領域のヒストグラム生成、特定画素までの処理時間等）が可能となる。また、各段の出力画素の判断のためのカウント値を異ならせることで、変倍やトリミング処理を含んでいても好ましく入出力の同期制御をすることができる。

【0087】

【第4の実施形態】

第3の実施形態では、出力着目画素を出力する際の同期信号がサイドバンド信号で後段のブロックへ伝送されていたが、本実施形態では、同期信号は部分画像データに付加されてデータパケットとして後段のブロックへ伝送されるものである。

【0088】

データパケットは、例えば図10（b）に示すように、伝送すべきデータ領域と、ユーザが自由に定義した拡張のためのサイドバンド信号領域（ユーザ領域）を持つ。フィールド 1001 は処理されるデータを格納する。フィールド 1010 はユーザが自由に定義した拡張のためのサイドバンド信号の情報を格納する。

【0089】

本実施形態では、ユーザ領域に同期信号を格納した場合について説明する。図10（c）は、ユーザ領域に同期信号を格納した場合のデータパケットの図である。フィールド 1001 は処理されるデータを格納する。フィールド 1003 は同期信号を格納する。

【0090】

この場合の画像処理部の構成を図11に示す。本実施形態では、画像処理回路は、図10（c）に示すように、同期信号を部分画像データに付加してデータパケットとして後段のブロックへ伝送する。そのため、図11の画像処理部の構成では、第3の実施形態で説明した図7（a）に示す構成と比べて、各画像処理回路間で同期信号を伝送するための信号線が必要なくなる。

【0091】

また、この場合の画像処理回路の構成を図12に示す。以下で、図12に示した画像処理回路の構成について説明する。

10

20

30

40

50

理回路の構成について説明する。図12において、図8の構成と機能的に変わらない構成については同じ参照番号を付し、その説明は省略する。

#### 【0092】

まず、入力同期信号検出部1203の動作について説明する。入力同期信号検出部1203は、前段から処理部201に入力されるデータパケット(714)について、データパケットに格納されている部分画像データに入力着目画素が含まれていると、入力同期信号1207を有効“1”にして出力制御部1204に送出する。

#### 【0093】

一方で、入力同期信号検出部1203は、前段から処理部201に入力されるデータパケットについて、データパケットに格納されている部分画像データに入力着目画素が含まれていない場合には、入力同期信号1207を無効“0”にして送出する。前段のブロックにおいて出力着目画素に入力同期信号1207に対応する情報(前段における出力同期信号に対応する同期用フラグ)を付加しておけばよく、データパケットに入力着目画素が含まれていることを効率的に検出できる。次に、出力制御部1204の動作について説明する。

10

#### 【0094】

出力制御部1204は、処理部201から送出された確定画素値205をそのまま確定画素値715として後段のブロックに送出する。この送出は、出力同期信号生成部802からの出力同期信号806が有効値(=1)に変わるまで続けられる。そして出力制御部1204は、出力同期信号生成部802からの出力同期信号806が有効値(=1)に変わると、この送出を一旦停止する。この時点では、出力着目画素より前に処理部201によって出力された確定画素値205についてはそのまま確定画素値715として送出し、出力着目画素の画素値についてはまだ後段へ送出していない状態となっている。

20

#### 【0095】

次に、出力制御部1204は、入力同期信号検出部1203からの入力同期信号1207が有効値(=1)であるか否かを判断する。そしてこの判断の結果、この時点で入力同期信号1207として有効値(=1)を受けている場合には、出力着目画素を含むデータパケット(715)を後段のブロックに送出する。一方、この時点で入力同期信号1207が有効値(=1)でない場合には、入力同期信号1207が有効値(=1)となるまで出力着目画素を含むデータパケットを保持しておく。そして、有効な入力同期信号1207を受けると、出力着目画素と同期用フラグ(同期信号(フィールド1003)が“1”)を含むデータパケット(715)を後段のブロックへ送出する。

30

#### 【0096】

即ち、出力制御部1204は、これから出力しようとするデータパケットが出力着目画素を含む場合、同期用フラグを含むデータパケットが入力されるまで出力着目画素を含むデータパケットの出力を待機させる。

#### 【0097】

そして、同期用フラグを含むデータパケットが入力されると、出力用着目画素を含むデータパケットの出力を許可する。この待機/許可の制御は出力制御部1204が行っても良いし、不図示の制御部が行っても良い。

40

#### 【0098】

また、本実施形態の同期信号は、図10(d)に示すような信号としても実現される。1e(ラインエンド)1004は、データ(フィールド1001)が1ラインの最後の画素であることを示す信号である。1s(ラインスタート)1005は、データ(フィールド1001)が1ラインの最初の画素であることを示す信号である。be(バンドエンド)1006は、データ(フィールド1001)が1バンドの最後の画素であることを示す信号である。bs(バンドスタート)1007は、データ(フィールド1001)が1バンドの最初の画素であることを示す信号である。pe(ページエンド)1008は、データ(フィールド1001)が1ページの最後の画素であることを示す信号である。ps(ページスタート)1009は、データ(フィールド1001)が1ページの最初の画素で

50

あることを示す信号である。なお、ページは複数のバンドを有するものとし、バンドは複数のラインを含むものとする。

【0099】

このように同期信号を設定して、各同期信号に基づいて画像処理回路がデータの出力を制御することで、1ページ内の各位置(1e、1s、bs、be、ps、pe)において、画像処理回路のデータの入出力の同期をとることもできる。

【0100】

なお、本実施形態は複数の画像処理モジュールをリングバスによって接続した形態においても適用できる。リングバスはコマンドパケットとデータパケットを共通的に一方向に巡回できるものとする。コマンドパケットは各画像処理モジュールの画像処理の内容を規定するパラメータを送付する。

10

【0101】

[第5の実施形態]

また、同期信号が複数の画像処理部間でサイドバンド信号線により転送される場合について説明する。図7(b)は、同期信号が複数の画像処理部間でサイドバンド信号線により転送される場合の画像処理装置の概略構成を示すブロック図である。図7(b)において、図6の構成と同様の構成については同じ参照番号を付すとともに、機能的に変わらないものについてはその説明を省略する。

【0102】

CPU602はDMAC694を制御することにより、RAM606に格納されたデジタル画像信号を読み出して画像処理部721に入力する。そして、画像処理部721で所定の画像処理が行われた処理後のデジタル画像信号を、予め書き込み動作の設定がなされたDMAC696により、RAM606に再度、格納させる。

20

【0103】

次に、CPU602はDMAC722を制御することにより、RAM606に格納されたデジタル画像信号を読み出して画像処理部723に入力する。そして、画像処理部723で所定の画像処理が行われた処理後のデジタル画像信号を、予め書き込み動作の設定がなされたDMAC724により、RAM606に再度、格納させる。

【0104】

画像処理部721は、出力着目画素を出力する際に、出力着目画素であることを示す同期信号「1」をサイドバンド信号725として画像処理部723へ送出する。

30

【0105】

画像処理部723は、これから出力しようとする画素値が出力着目画素である場合、画像処理部721から同期信号「1」が入力されるまでその出力を待機させる。そして、同期信号「1」が入力されたことに応じて、待機させた出力着目画素の出力を許可する。

【0106】

このように、画像処理部が同期信号に基づいてデータの出力を制御することで、同期信号が複数の画像処理部間でサイドバンド信号線によって転送される場合においても、複数の画像処理部間のデータの入出力の同期をとることが可能となる。

【0107】

また、上述の実施形態では正論理(ハイ・アクティブ)で説明しているが、負論理(ロー・アクティブ)であっても本発明を適用することができることは言うまでもない。

40

【0108】

(その他の実施例)

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【 図 7 】

【 図 8 】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(72)発明者 正阿弥 晃司

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 石川 尚

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 伊藤 忠幸

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 佐田 宏史

(56)参考文献 特開2000-163388 (JP, A)

特開2010-277429 (JP, A)

特開2010-171622 (JP, A)

特開2005-109708 (JP, A)

特開平7-099592 (JP, A)

特開2008-042321 (JP, A)

特開平5-199404 (JP, A)

籠谷 裕人、外3名，“長方形動画像のための1アフィン変換法”，電子情報通信学会論文誌，日本，社団法人電子情報通信学会，1998年 1月25日，Vol.J81-D-1, No.1, pp.11-20

(58)調査した分野(Int.Cl., DB名)

G 06 T 1 / 20

G 06 F 9 / 46, 15 / 16