(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl. <sup>7</sup>

H03F 3/19

(45) 공고일자 2001년04월16일

(11) 등록번호 10-0285915

(24) 등록일자 2001년01월08일

|            |                 |               |                |

|------------|-----------------|---------------|----------------|

| (21) 출원번호  | 10-1993-0700501 | (65) 공개번호     | 특 1993-0701863 |

| (22) 출원일자  | 1993년 02월 20일   | (43) 공개일자     | 1993년 06월 12일  |

| (30) 우선권주장 | 7/725,966       | 1991년 07월 05일 | 미국(US)         |

(73) 특허권자 실리콘 시스템즈, 인크. 월리엄 비. 캠블러

미국 캘리포니아주 92781-2020 터스틴 마이포드 로드 1435

(72) 발명자 화이트, 버트

미합중국, 캘리포니아 92715, 어빈 5세달리지

(74) 대리인 이건주

심사관 : 인치복

#### (54) 자장샘플 훌드 및 오토제로를 갖는 연산증폭기

요약

본 발명의 스위칭캐패시터 증폭기회로는 빌트-인 샘플과 훌드와 입력 오토 제로를 갖는 단일 증폭기를 사용한다. 본 발명의 빌트-인 샘플과 훌드는 다중 위상 시스템에 연속적 유효출력을 제공한다. 본 발명은 새로운 오토제로구조와 새로운 증폭기를 포함한다. 새로운 증폭기는 AZAMP로서 언급된다. 본 발명의 AZAMP의 회로구성은 샘플 및 훌드기능을 제공하기 위해 회로에 부가되는 스위치들을 갖는 2단계증폭기를 포함한다. 훌드모드 동안 제 2단을 분리함으로써 출력전압이 AZAMP내의 캐패시터에 저장된 전압에 의해 변화되지 않고 유지될 것이다. 전하재거회로는 스위치가 터-오프될 때 상기 캐패시터로 주입되는 전하를 제거하기 위해 샘플 및 훌드회로에 연결된다. 본 발명의 AZAMP는 또한 자장오토제로기능을 갖는다. 결과적인 잇점들은 축소된 면적소모와 낮은 입력등가오피셋이다.

대표도

명세서

## [발명의 명칭]

자장 샘플홀드 및 오토제로를 갖는 연산증폭기

## [도면의 간단한 설명]

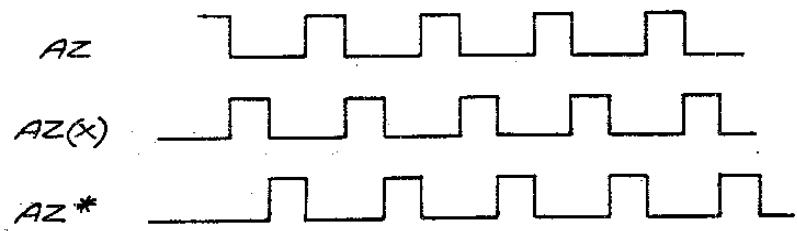

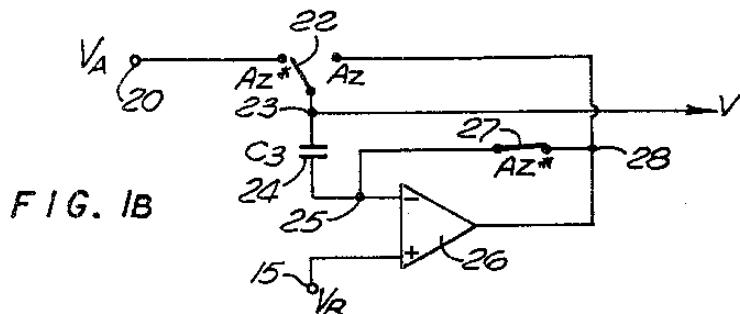

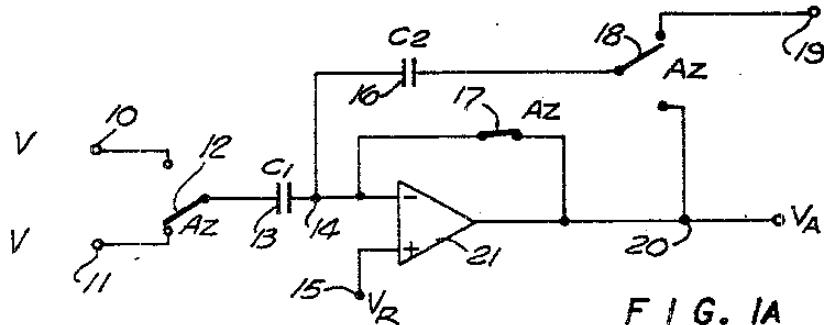

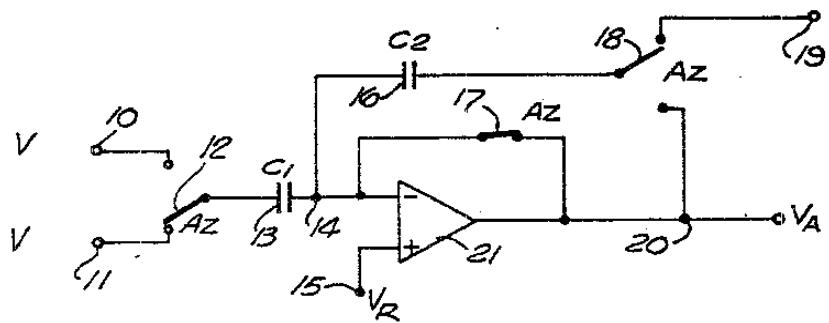

제1a도와 제1b도는 그 출력이 연속적으로 유효한 오토-제로증폭기에 대한 선행 기술의 예시도.

제2도는 본 발명에 따른 오토-제로구조의 예시도.

제3도는 본 발명의 바람직한 실시예에 관한 예시도.

제4도는 본 발명의 바람직한 실시예의 블록도.

제5a도와 제5b도는 본 발명의 오토-제로구조를 제어하기 위한 바람직하고 교호적인 타이밍구조에 관한 예시도.

#### [발명의 상세한 설명]

본 발명은 스위칭 캐패시터 차동증폭기의 기술분야에 관한 것이다.

연산증폭기를 집적회로(IC)화한 상태로 구현할 때, 이상적인 특성들을 이루기가 어렵다. 이상적으로, 제로전압(zero voltage)이 연산증폭기의 입력들 사이에 인가될 때, 출력전압은 제로이다. 그러나 실질적인 증폭기들 있어서, 증폭기 내의 구성요소들의 불완전한 매칭(matching)을 야기하는 처리(process) 변화들은 입력들이 제로 상태로 될 때 양이나 음의 출력전압을 야기한다. 출력전압의 크기는 증폭기의 개방루프 이득에 직접 비례하며, 이를 출력오프셋(offset)전압이라 한다.

오프셋전압의 효과를 제거하기 위해, '오토-제로화 (auto-zeroing)'로 불리는 구성이 활용된다. 오토-제로에서, 2위상 스위칭 구성이 사용된다. 제 1위상 동안 입력전압  $V_{IN}$ 이 캐패시터를 통해 연산증폭기의 한 입력단에 연결되며, 이 연상증폭기의 다른 입력단은 기준전압(전형적으로 접지)에 연결된다. 제 2위상 동안, 두 입력단은 오프셋전압의 효과를 보상하기 위해 접지에 연결되며 증폭기를 자동적으로 제로화한다. 그러므로 입력전압신호들은 동작중에서 단지 제 1위상 동안만 유효하다.

입력이 오토제로화되고, 출력이 연속적으로 유효한 스위칭 캐패시터 증폭기회로를 설계할 필요가 종종 있다. 선행기술에 있어서 이러한 설계는 스위치들과 캐패시터들로 된 세트를 각각 갖는 두개의 증폭기회로들을 필요로 한다.

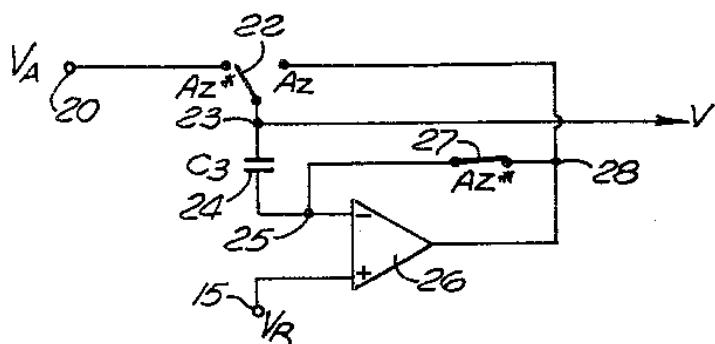

오토-제로증폭기의 전형적인 선행기술 설계는 제 1a도와 제 1b도에 도시된다. 제 1a도는 1보다 큰 이득을 갖는 오토제로 구성이며 그 출력이 단지 제 1위상(AZ<sup>\*</sup>위상)에서만 유효한 제 1증폭기를 도시한다. 제 1a도는 입력전압  $V_{IN}$  10이 AZ<sup>\*</sup>위상 동안 스위치 12에 의해 캐패시터 C1에 연결되는 반면, 입력전압  $V_{ZERO}$  11은 AZ위상 동안 스위치 12에 의해 캐패시터 C1에 연결됨을 보여준다. 캐패시터 C1은 또한 노드 14에서 연산증폭기 21의 반전 입력단에 연결된다. 노드 14는 스위치 17에 연결되는 것은 물론 캐패시터 C2에도 연결된다. 캐패시터 C2는 스위치 18에 연결된다. AZ위상 동안 스위치 18은 출력기준전압 OUTREF 19에 연결되며, AZ<sup>\*</sup>위상 동안 스위치 18은 증폭기 21의 출력에 연결된다. 스위치 17은 AZ위상 동안 노드 20에서 증폭기 21의 출력에 연결된다. 스위치 17은 AZ<sup>\*</sup>위상 동안 개방회로가 된다. 기준전압  $V_R$  15는 증폭기 21의 비반전 입력단자에 연결된다.

제 1a도의 회로는 제어신호 AZ와 AZ<sup>\*</sup>에 따라 스위칭한다. 이 신호들은 교호(交互)의 비중첩(non-overlapping) 타이밍신호들을 의미한다. AZ가 하이상태일 때 고 위상(AZ위상) 동안, 신호  $V_{ZERO}$  11은 연산증폭기 21의 반전입력단에 연결되어지는 캐패시터 C1에 제공된다. 연산증폭기 21의 출력은 피드백을 제공하기 위해 스위치 17을 통해 연산증폭기 21의 반전입력단에 연결된다. 증폭기의 입력오프셋이 이러한 간격 동안 저장되므로, 증폭기는 오토제로화된다.

AZ<sup>\*</sup>가 하이일 때 그 위상(AZ<sup>\*</sup>위상) 동안 직접 피드백은 컷오프되며, AZ위상동안 출력기준신호 19와 증폭기의 입력오프셋을 합한 값까지 충전되었던 캐패시터 C2는 이제 피드백 루프에 연결된다. 이때 노드 20에서 검출할 수 있는 출력전압  $V_A$ 는 캐패시터 C2로부터 방전되는 출력기준전압이 될 것이다. 신호  $V_{IN}$  10이 캐패시터 C1에 제공되는 까닭에 증폭기의 반전입력단에 신호  $V_{ZERO}$ 와  $V_{IN}$  사이의 차에 상응하는 전위 변화를 야기한다. 증폭기의 반전입력단에서의 전위변화는 또한 캐패시터 C2에 걸리는 전압을 변화되지 않은 상태로 유지하기 위해 노드 20에서 증폭기의 출력단에 전위변화를 야기한다. 이상적인 증폭기를 가정하고, 노드 14에서 노드 분석을 사용하면, 출력전압  $V_A$ 에서의 전위는 다음과 같이 주어진다.

$$V_A = (V_{ZERO} - V_{IN})C1/C2 + V_{OUTREF} \quad \text{AZ}^* \text{위상}$$

여기서  $V_A$ 는 증폭기의 반전입력단의 전압이다.

이 회로에 대한 유효출력은 단지 AZ<sup>\*</sup>가 하이상태일 때의 위상 동안만 유효하다. AZ가 하이상태일 때, 증폭기는 오토-제로가 되고, 출력은 증폭기의 입력 오프셋과 동일하다.

이러한 회로는 AZ위상 동안 캐패시터 C1과 C2에 그 오프셋을 저장함에 의해 낮은 입력오프셋을 이룬다. 만약 두 위상들에서 출력을 발생하는 것이 바람직하다면, 샘플홀드회로가 제 1b도에 도시된 것과 같이 부가되어야만 한다. 제 1b도의 회로는 단위이득 샘플홀드 구성이다. 제 1b도에서 노드 20의 전압신호  $V_A$ 는 AZ<sup>\*</sup>위상 동안 스위치 22에 연결된다. 스위치 22는 또한 출력전압  $V_{OUT}$ 를 검출할 수 있는 노드 23에서 캐패시터 C3에 연결된다. 캐패시터 C3은 노드 25에서 연산증폭기 26의 반전입력단에 연결된다. 노드 25는 AZ<sup>\*</sup>위상 동안 닫히고, AZ위상 동안 개방되는 스위치 27을 통해 연산증폭기 26의 출력단에 연결된다. AZ위상 동안 스위치 22는 노드 28에서 연산증폭기 26의 출력단에 연결된다. 기준전압  $V_R$  15는 연산증폭기 26의 비반전 입력단자에 연결된다.

AZ<sup>\*</sup>위상 동안 스위치 22는 유효 출력전압  $V_A$ 가 노드 23에서 출력전압  $V_{OUT}$ 으로 직접 검출될 수 있도록 연결한다. 이 위상 동안 증폭기 26은 스위치 27이 직접 음의 피드백을 증폭기 26의 반전입력단자에 제공함으로서 오토-제로가 된다. 또한 캐패시터 C3은 전압  $V_A$ 를 샘플링한다. AZ위상 동안 스위치 22는 노드 20의 전압  $V_A$ 로 부터 노드 28의 증폭기 26의 출력전압으로 스위칭된다. 또한 스위치 27은 개방회로가 되며, 그래서 증폭기 26은 더 이상 직접 피드백을 하지 않는다. 제 1b도의 샘플 및 훌드회로의 설계 때문에, 캐패시터 C3의 양단이 각각 접속된 노드 23과 25에서의 전압 레벨들은 AZ<sup>\*</sup>위상에 있는 AZ위상의 시작에서와 같은 값들로 유지된다. 그러므로 노드 23의 출력전압  $V_{OUT}$ 은 위상 AZ동안 여전히 전압  $V_A$ 와 동일하다. 제 1a도와 제 1b도의 각 오토-제로회로는 연산증폭기들의 오프셋과 독립적인 출력을 갖는다. 그러나 출력오프셋은 스위치들로부터 주입되는 전하 때문에 제로가 아니다.

비록 제 1a도와 제 1b도의 결합회로가 오토-제로가 되는 입력과 두 위상들에서 유효한 출력을 갖는 회로를 설명할지라도, 상기 회로는 몇 가지 결점들을 갖는다. 한 결점은 선행기술회로는 두 개의 분리된 증폭기를 필요로 함으로써, 불필요하게 넓은 면적을 소모한다는 것이다. 선행기술 회로의 다른 결점은 회로가 두 회로 오프셋들의 합인 오프셋에 기인한 큰 입력등가오프셋을 나타낸다는 것이다. 게다가 증폭기가 그 오토-제로전압으로부터 그 출력전압으로 바뀌므로, 글리치(glitch)가 각 클럭 위상의 시작에서 출력에 나타난다는 것이다.

오토-제로기능과 샘플 및 훌드기능 양자를 결합한 회로를 갖는 것이 바람직하다. 스위치들로부터 주입되는 전하에 보다 면역(immunity)을 갖는 회로를 갖는 것이 또한 바람직하다. 입력오프셋을 줄이는 것이 더욱 바람직하다.

본 발명의 스위칭캐패시터 증폭기회로는 빌트-인 샘플과 훌드와 입력 오토제로를 갖는 단일 증폭기를 사용한다. 본 발명의 빌트-인 샘플과 훌드는 다중 위상 시스템에 연속적 유효출력을 제공한다. 본 발명은 새로운 오토제로구조와 새로운 증폭기를 포함한다. 새로운 증폭기는 AZAMP로서 언급된다. 본 발명의 AZAMP의 회로구성은 샘플 및 훌드기능을 제공하기 위해 회로에 부가되는 스위치들을 갖는 2단계증폭기를 포함한다. 훌드모드 동안 제 2단을 분리함으로써 출력전압이 AZAMP내의 캐패시터에 저장된 전압에 의해 변화되지 않고 유지될 것이다. 전하제거회로는 스위치가 터-오프될 때 상기 캐패시터로 주입되는 전하를 제거하기 위해 샘플 및 훌드회로에 연결된다. 본 발명의 AZAMP는 또한 자장오토제로기능을 갖는다. 결과적인 잇점들은 축소된 면적소모와 낮은 입력등가오프셋이다.

이하 본 발명에 따른 자장(self-contained)오토제로와 샘플 및 훌드기능을 갖는 증폭기를 설명한다. 다음의 설명에서 전력공급 값들, 바이어스 전압들 등등과 같은 다수의 특정한 상술(詳述)들이 본 발명의 보다 철저한 설명을 제공하기 위해 상세히 설명된다. 그러나 당해 기술분야에서 숙련된 자들에게는 본 발명이 그러한 특정한 상술(詳述)들이 없이도 실시될 수 있다는 것이 명백할 것이다. 다른 경우들에서 잘 알려진 특징들은 본 발명을 불필요하게 모호하게 하지 않도록 하기 위해 상세히 설명되지 않는다.

본 발명에 있어서 다중 위상처리에서 동작하는 스위칭-캐패시터 차동증폭기 구성은 모든 동작단계에서 유효한 출력들을 가능하게 하는 오토제로기능과 샘플 및 훌드기능 양자를 제공하는 단일 증폭기를 사용한다. 그 결과적인 잇점들은 감소된 면적소모와 낮은 입력등가오프셋이다.

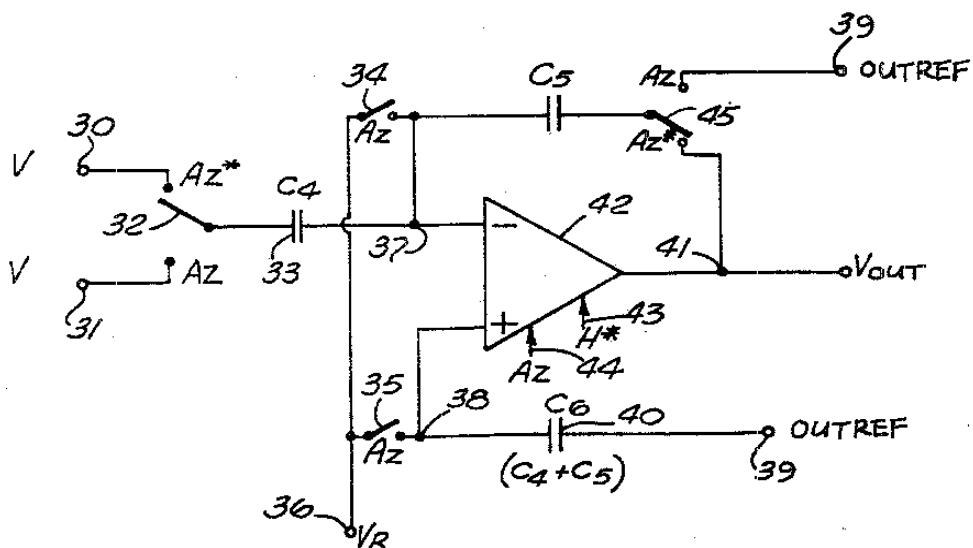

본 발명의 AZAMP증폭기를 사용하는 스위칭-캐패시터 차동증폭기회로는 제2도에 설명된다. 제 2도에서 스위치 32의 한 단자는 AZ<sup>\*</sup>위상 동안 입력신호  $V_{IN}$  30에 연결되며, AZ위상 동안 신호  $V_{ZERO}$  31에 연결된다. 스위치 32의 다른 단자는 캐패시터 C4에 연결된다. 캐패시터 C4는 또한 노드 37에서 AZAMP 42의 반전 입력단자에 연결된다. 스위치 34와 캐패시터 C5도 노드 37에 연결된다. 스위치 34는 AZ위상 동안 닫히며, AZ<sup>\*</sup>위상 동안 개방된다. 기준전압  $V_R$  36은 스위치 34와 35에 연결된다. AZ위상 동안 스위치 35는 닫히며, 노드 38에서 AZAMP 42의 비반전입력단자에 연결된다. AZ<sup>\*</sup>위상 동안 캐패시터 C5는 스위치 45를 통해 노드 41에서 AZAMP 42의 출력단에 연결된다. AZ위상 동안 캐패시터 C5는 스위치 45를 통해 기준전압 OUTREF 36에 연결된다. 신호 AZ 44와 H<sup>\*</sup> 43은 AZAMP 42의 내부 회로에 연결된다. 노드 38은 또한 캐패시터 C6을 통해 기준전압 OUTREF 39에 연결된다.

제 2도의 회로의 동작에 있어서, AZ위상 동안 모든 캐패시터들이 초기화된다. 이러한 위상에서 AZAMP 42의 두 입력이 기준전압  $V_R$  36에 연결된다.  $V_R$ 은 약 2.5볼트(전력공급 범위의 거의 중간)의 DC전압이다. 또한 AZ위상 동안 AZAMP 42는 내부 캐패시터에 입력오프셋을 저장한다. 이러한 방법으로 증폭기는 오프셋을 영(zero)으로 하며 오토 제로화된다.

AZ<sup>\*</sup>위상 동안 캐패시터 C4와 아랫판은 입력전압  $V_{IN}$  30에 연결되며, 캐패시터 C5의 아랫판은 노드 41에서  $V_{OUT}$ 에 연결된다. AZ<sup>\*</sup>위상은 제 2도의  $V_{OUT}$ 에 전압을 야기한다.

$$V_{OUT} = (V_{ZERO} - V_{IN})C4/C5 + OUTREF$$

AZ<sup>\*</sup>위상 동안 언젠가(예를 들면 후반부, 여기서 상기 후반부는 임의의 주기를 갖는 파형의 반주기를 다시 반으로 나누었을 때 상대적으로 시간상 더 늦은 1/4주기를 의미한다.) 훌드신호 43 H<sup>\*</sup>는 AZAMP 42의 출력전압  $V_{OUT}$ 가 새로운 값이 될 수 있도록 상승한다. 훌드신호 43 H<sup>\*</sup>가 로우상태일 때, 출력은 이전의 AZ<sup>\*</sup>위상 동안 발생된  $V_{OUT}$ 의 이전의 값을 훌드한다. 훌드신호 H<sup>\*</sup> 43은 AZAMP 42안쪽의 스위치를 제어하며, 이는 제 3도에서 상세히 설명된다.

AZ스위치 34와 35가 터-오프일 때, 일부 전하가 노드 36으로 주입될 것이다. 만약 동일한 양이 각 스위치에 의해 주입된다면, 오프셋은 C6의 값이 C4 + C5일 때 제거될 것이다.

AZAMP 42로 입력되는 AZ신호 44가 AZ클럭신호가 로우상태로 천이한 후 그리고 AZ<sup>\*</sup>클럭신호가 하이상태로 천이하기 전에 턴-온되는 경우에 제 2도의 2-위상 타이밍 구조의 변화는 3위상 구조를 사용하는 것이다. 이러한 교호의 타이밍 구조는 세개의 교호인 비-중첩 클럭신호들로 구성된다. 다른 위상을 그러한 타이밍 구조에 삽입함으로써 AZAMP가 AZ스위치 34와 35로 부터 전하 주입의 부정합(mismatch)에 의해 야기된 오프셋을 보상하도록 한다.

타이밍구조의 제 2독립변화는 신호 H<sup>\*</sup>의 타이밍을 조정하는 것이다. 제 2도의 회로는 만약 신호 H<sup>\*</sup> 43이 신호 AZ<sup>\*</sup>와 같은 타이밍 패턴을 따른다면 역시 적절하게 동작할 것이다. 그러나 만약 H<sup>\*</sup>이 AZ<sup>\*</sup>이 턴-온된 후에 턴온된다면 전압 V<sub>OUT</sub>의 과도현상 안정화 시간이 작을 것이다.

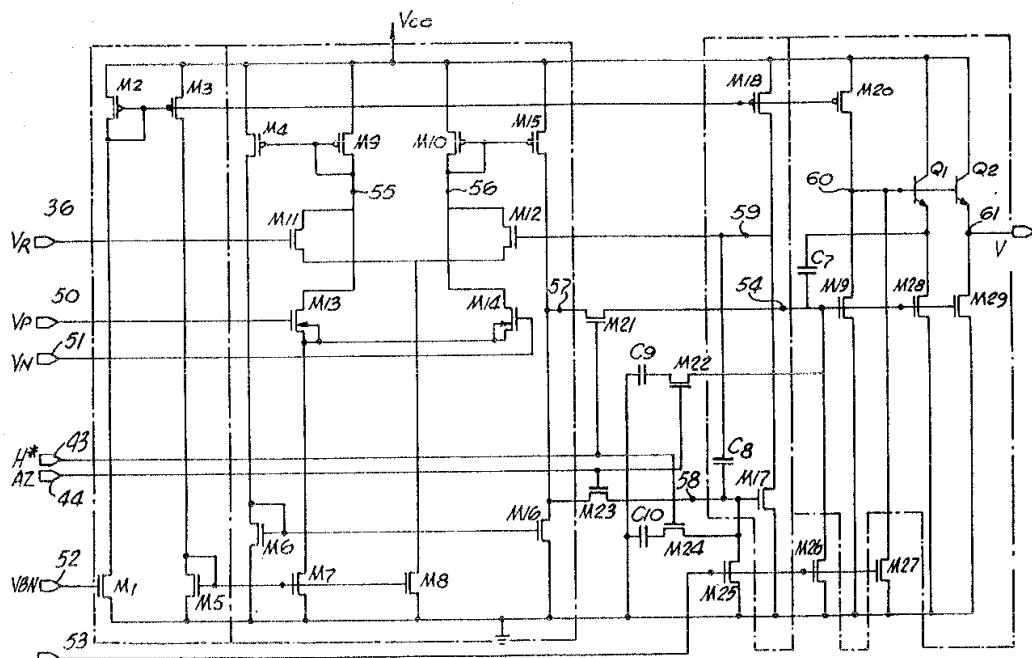

제 2도에 도시된 AZAMP 42의 회로는 제 3도에서 설명된다. 제 3도에서 기준전압신호 36은 MNOS 트랜지스터 M11의 게이트에 입력된다. AZAMP의 양의 입력노드에 연결되는 전압신호인 신호 VP 50은 NMOS 트랜지스터 M13의 게이트에 연결된다. AZAMP의 음의 입력단자로의 전압입력신호인 신호 VN 51은 NMOS 트랜지스터 M14의 게이트에 연결된다. 신호 H<sup>\*</sup> 43은 NMOS 트랜지스터 M21과 M24의 게이트에 연결된다. AZ신호 44는 트랜지스터 M22와 M23의 게이트에 연결된다. 신호 VBN 52는 NMOS 트랜지스터 M1의 게이트에 연결된다. 슬립신호(sleep signal) 53은 NMOS 트랜지스터 M25, M26, M27의 게이트에 연결된다.

NMOS 트랜지스터 M1의 드레인은 PMOS 트랜지스터 M2의 드레인에 연결된다. 트랜지스터 M2의 드레인은 PMOS 트랜지스터 M3의 게이트에 연결됨은 물론 그 자신의 게이트에 연결된다. 트랜지스터 M2의 소오스는 전력공급단 V<sub>CC</sub>에 연결된다. 트랜지스터 M1의 소오스는 접지에 연결된다. PMOS 트랜지스터 M3의 드레인은 NMOS 트랜지스터 M5의 드레인에 연결되며, 또한 트랜지스터 M5의 게이트에 연결된다. 트랜지스터 M5의 게이트는 또한 NMOS 트랜지스터 M7과 M8의 게이트들에 연결된다. 트랜지스터 M5, M7, M8의 소오스들은 접지에 연결된다.

PMOS 트랜지스터 M3의 게이트는 PMOS 트랜지스터 M18과 M20의 게이트에 연결된다. 트랜지스터 M3, M18, M20의 소오스들은 전력공급단 V<sub>CC</sub>에 연결된다. 트랜지스터 M18의 드레인은 노드 59에서 NMOS 트랜지스터 M12의 게이트에 연결되는 것은 물론 NMOS 트랜지스터 M17의 드레인에 연결된다. 캐패시터 C8의 아랫판은 또한 노드 59에 연결된다. 캐패시터 C8의 윗판은 노드 58에서 NMOS 트랜지스터 M23의 소오스에 연결됨은 물론 트랜지스터 M17의 게이트에 연결된다. NMOS 트랜지스터 M24의 드레인과 NMOS 트랜지스터 M25의 드레인은 또한 노드 58에 연결된다. 트랜지스터 M25, M17, M26, M27의 소오스들은 접지에 연결된다.

트랜지스터 M24의 소오스는 캐패시터 C10의 윗판에 연결된다. 캐패시터 C10의 아랫판은 접지에 연결된다. 트랜지스터 M23의 드레인은 노드 57에서 NMOS 트랜지스터 M16의 드레인에 연결된다. PMOS 트랜지스터 M15의 드레인은 물론 NMOS 트랜지스터 M21의 드레인은 또한 노드 57에 연결된다. 트랜지스터 M21의 소오스는 노드 54에서 NMOS 트랜지스터 M19, M28, M29의 게이트들에 연결된다. 캐패시터 C7의 윗판과 NMOS 트랜지스터 M22의 드레인은 또한 노드 54에 연결된다. NMOS 트랜지스터 M26의 드레인은 노드 54에 연결된다. 트랜지스터 M22의 소오스는 캐패시터 C9의 윗판에 연결되며, 캐패시터 C9의 아랫판은 접지에 연결된다. 캐패시터 C7의 아랫판은 NMOS 트랜지스터 M28의 드레인에 연결됨은 물론 바이폴라-접합(bipolar junction) 트랜지스터 Q1의 에미터에 연결된다. 트랜지스터 Q1의 베이스는 노드 60에서 바이폴라-접합트랜지스터 Q2의 베이스와 NMOS 트랜지스터 M27의 드레인에 연결된다. 트랜지스터 M20의 드레인과 트랜지스터 M19의 드레인은 또한 노드 60에 연결된다. 트랜지스터 Q1과 Q2의 콜렉터들은 전력공급단 V<sub>CC</sub>에 연결된다.

트랜지스터 M19, M28, M29의 소오스들은 접지에 연결된다. 트랜지스터 Q2의 에미터는 출력전압을 제공하는 노드 61에서 트랜지스터 M29의 드레인에 연결된다. PMOS 트랜지스터 M15의 게이트는 노드 56에서 PMOS 트랜지스터 M10의 게이트와 드레인에 연결된다. NMOS 트랜지스터 M12와 M14의 드레인들은 또한 노드 56에 연결된다. 트랜지스터 M12의 소오스는 NMOS 트랜지스터 M8의 드레인에 연결됨은 물론 트랜지스터 M11의 소오스에 연결된다. 트랜지스터 M14의 소오스는 트랜지스터 M7의 드레인에 연결됨은 물론 트랜지스터 M13의 소오스에 연결된다. 트랜지스터 M13의 드레인은 노드 55에서 PMOS 트랜지스터 M9의 드레인에 연결됨은 물론 트랜지스터 M11의 드레인에 연결된다. PMOS 트랜지스터 M4의 게이트는 물론 트랜지스터 M9의 게이트가 또한 노드 55에 연결된다. 트랜지스터 M4, M9, M10, M15의 소오스들은 전력공급단 V<sub>CC</sub>에 연결된다. 트랜지스터 M4의 드레인은 트랜지스터 M16의 게이트에 연결됨은 물론 NMOS 트랜지스터 M6의 드레인과 게이트에 연결된다. 트랜지스터 M6의 소오스와 트랜지스터 M16의 소오스는 접지에 연결된다.

신호 VP 50과 VN51은 AZAMP로의 차동 입력신호들을 나타낸다. 신호 VR 36은 기준DC전압(이러한 경우에 2.25볼트)이다. 신호 VBN 52는 트랜지스터 M1의 전류를 약 20 마이크로-암페어로 세트시키기 위한 DC전압이다. 슬립신호 53은 하이상태일 때 증폭기를 디스에이블시키며 그것의 공급전류를 감소시키는 선택적인 입력신호이다. 정규의 동작 동안에 슬립신호는 접지된다.

제 3도는 바이어스단으로 명명(命名)된 트랜지스터들 M1-M3과 M5를 갖는 복개의 블록들로 나뉘는 것으로 볼 수 있다. 트랜지스터 M4와 M6-M16은 제 1단을 포함한다. 트랜지스터 M17과 M18과 캐패시터 C8은 불균형 감지단을 포함한다. 트랜지스터 M19, M20, M28, M29, Q1, Q2 및 캐패시터 C7은 제 2단을 포함한다. 제 3도에 도시된 AZAMP의 단계들의 설계는 단지 한 예에 불과하다. 이 단들은 그러한 설계에 독점적으로 제한되지 않는다.

신호 AZ 44가 로우(비활성)상태이고 신호 H<sup>\*</sup> 43은 하이상태일 때 AZAMP는 제 3도에 도시된 바와 같이 푸쉬-풀(push-pull) 입력단을 갖는 2-단증폭기를 포함한다. 신호 AZ가 하이상태이고 신호 H<sup>\*</sup>이 로우상태일 때 AZAMP는 또한 오토-제로기능을 제공하기 위한 제 3단(불균형감지단)을 포함한다. 신호들 AZ 44와 H<sup>\*</sup> 43은 AZAMP의 적절한 동작을 위해 비-겹침이어야 한다. 스위치들이 샘플 및 훌드기능을 제공하기 위해 이러한 구성에 부가된다. 그 목적은 훌드모드(H<sup>\*</sup> 로우상태) 동안 노드 54에서 제 2단을 분리하는 것이다. 훌드모드 동안 제 2단을 분리함으로써 AZAMP의 출력전압은 캐패시터 C7에 저장된(H<sup>\*</sup> 가 하이상태인 샘플모드 동

안 축적된) 전압으로 인하여 변화되지 않고 유지된다.

이러한 예에서 훌드모드는  $H^*$  가 로우상태일 때 발생하며, 샘플모드는  $H^*$  가 하이상태일 때 발생한다. 스위치를 구현하는 제 3도의 회로는 트랜지스터 M21이다. 트랜지스터 스위치 M21의 턴-온과 턴-오프는 신호  $H^*$  43에 의해 제어된다. 신호  $H^*$  가 하이상태일 때 스위치 M21은 닫히며, 신호  $H^*$  가 로우상태일 때 스위치 M21이 개방된다. 게다가 트랜지스터 M22와 캐패시터 C9은 트랜지스터 M21이 턴-오프일 때 캐패시터 C7로 주입된 전하를 제거한다. (다른 전하제거스위치 설계들을 구현할 수도 있다는 것을 인지해야 할 것이다.)

제 1단에 존재하는 어떤 불균형을 감지하기 위해 불균형감지단을 사용함으로써 오토제로기능이 이 회로에 부가되어진다. 더우기 소량 차동전류가 노드 55와 56에 도입된다. 오토제로화 동안 신호들 VP 50과 VN 51은 둘 다 제로기준들에 묶인다. 이러한 상황에서 만약 제 1단에 불균형이 존재하면 오프셋이 발생한다. 이러한 불균형은 불균형감지단에 의해 감지되어진다.

오토제로(AZ신호 44가 하이상태)인 동안 불균형감지단은 노드 57에서 제 1단 출력에 연결된다. 만약 제 1단이 균형적이면 노드 59에서 불균형감지단의 출력은 공급전력의 거의 중앙값에 있게 된다. 제 1단에서 불균형은 불균형감지단의 노드 59를 제 1단의 차동쌍(differential pair)의 한쪽에 연결함에 의해 조정된다. 차동쌍의 다른쪽이 공급의 중심부 근처의 바이어스 전압 위치에 연결되므로, 차동쌍은 노드 55와 56에서의 전류가 불균형에 대립되도록 한다.

AZ신호 44가 턴-오프일 때 노드 57은 노드 58로 부터 분리되어 교정전압이 캐패시터 C8에 저장된다. 노드 57과 58을 분리하는 스위치는 트랜지스터 M23이다. 트랜지스터 스위치 M23의 턴-온과 턴-오프는 신호 AZ 44에 의해 제어된다. AZ가 하이상태일 때 오토제로스위치 M23은 닫히며, 샘플 및 훌드스위치 M21을 위한 전하제거회로의 스위치 M22가 또한 닫힌다. AZ 44는 AZ 44가 하이상태일 때 샘플 및 훌드스위치 M21이 개방되고 샘플 및 훌드캐패시터 C7로부터의 전하를 제거하기 위해 트랜지스터 M22가 턴-온되므로 샘플 및 훌드스위치 M21을 위한 전하제거회로를 제어한다.  $H^*$  4301 오토제로스위치 M23에 대한 전하제거트랜지스터 M24를 제어하는 것도 이와 마찬가지로 생각해 볼 수 있을 것이다.  $H^*$  4301 하이상태일 때 AZ 44는 로우상태이며 그 결과 오토-제로스위치 M23가 개방된다. 트랜지스터 M24와 캐패시터 C10은 트랜지스터 M23에 대한 전하제거를 수행한다.

스위치 트랜지스터 M23에 의해 교정전압캐패시터 C8로 주입되는 전하는 오프셋 애러를 야기한다. 이러한 애러는 트랜지스터 M13과 M14에 대한 트랜지스터 M11과 M12의 트랜스컨덕턴스(transconductance) 비율에 의해 증폭된다. 이러한 비율은 전형적으로  $1/8 - 1/10$ 의 범위에 있다. 신호 VR 36으로 선택된 실질적 전압은 몇가지 방법으로 전개될 수 있다. 실질적인 AZAMP 응용에 있어서 단일 밴드캡 기준이 사용된다. 출력이 점지에 있을 때 노드 60에서와 같은 전압으로 신호 VR 36을 설정함으로써 성능을 개선할 수 있다. 이러한 전압에 트랜지스터 Q1과 Q2에 의해 얻어진 베이스 전류를 보상함으로써 다른 개선들을 이를 수 있다.

슬립모드에서 AZAMP의 전력은 다운될 수 있다. 그 밖에 회로는 대부분의 바이어스 전류를 턴-오프하기 위해 신호 VBN 52를 점지로 이끈다. 부가적인 풀-다운 트랜지스터 M25, M26, M27은 남아있는 부동(floating)노드들을 풀-다운(pull down)한다.

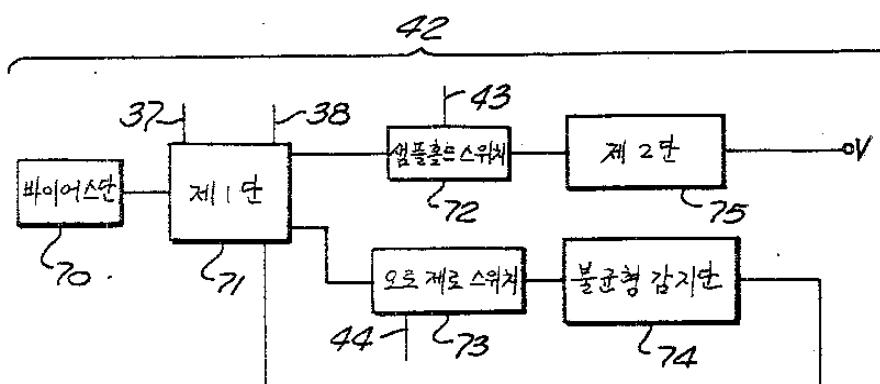

본 발명의 증폭기 AZAMP의 블록도가 제 4도에 도시된다. 제 4도에서 바이어스단 70은 제 1단 71에 연결된다. 제 1단 71은 샘플 및 훌드스위치 72와 오토제로스위치 73에 연결된다. 오토제로스위치 73은 불균형감지단 74에 연결되는 한편, 샘플 및 훌드스위치 72는 제 2단 75에 연결된다. 불균형감지단 74는 제 1단 71의 뒤에 연결된다. 제 2단 75는 증폭기의 출력전압을 제공한다. 불균형감지단은 제 1단의 오프셋을 조정한다. 제 4도는 본 발명의 증폭기내의 기능 블록들의 단순한 개관을 보여준다. 제 4도는 증폭기내의 샘플 및 훌드스위치가 모든 동작단계에서 유효출력이 가능하게 하는 동안, 증폭기 내에서 입력오프셋의 오토제로화가 발생함을 보여준다. 오프셋은 불균형감지단 74 내의 캐패시터에 저장된다. 샘플 및 훌드스위치와 오토-제로스위치를 위한 전하제거회로가 또한 제 4도에 부가될 수 있다.

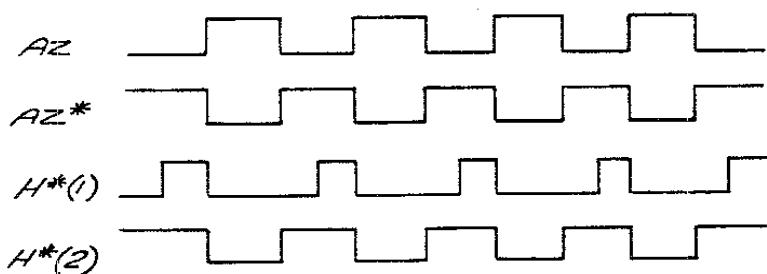

제 5a도와 제 5b도는 본 발명의 오토-제로 구조와 AZAMP를 제어하기에 바람직하고 교호적인 타이밍구조들이다. 제 5a도에서 신호 AZ와  $AZ^*$  가 비-종첩 클럭신호들임을 볼 수 있다. 앞서 언급된 바와 같이 이러한 신호들은 AZAMP에 연결된 오토-제로구성회로에서 사용되는 스위칭수단을 제어한다. 제 5a도는 또한 훌드신호  $H^*$  43에 대한 두개의 다른 타이밍 구조들을 도시한다. 훌드신호  $H^*$  의 제 1버전(version)은 AZ $^*$  클럭신호를 따르며, 만약 이러한 타이밍구조가 제공된다면 회로는 적절하게 동작할 것이다. 그러나 만약 AZ $^*$  가 턴-온된 후에 훌드신호  $H^*$  가 턴-온된다면 AZAMP의 출력에서 과도현상 안정화 시간이 작아지므로 훌드신호의 제 1버전은 바람직한 타이밍구조이다. 제 3도를 언급하면, 훌드신호  $H^*$  는 제 3도의 제 1단의 출력을 샘플링하기 위해 사용되는 트랜지스터 스위치 M21의 턴-온과 턴-오프를 제어하며, 이러한 출력은 노드 54에 접속된 캐패시터 C7에 의해 보유되어진다. 제 3도의 회로가 적절하게 동작하기 위해 클럭신호  $AZ^*$  는 신호  $H^*$  가 하이상태일 때는 언제나 하이상태라야 한다.

제 5b도는 본 발명을 위하여 검토된 2-위상 타이밍구조와 대비하여 교호의 3-위상 타이밍구조를 도시한다. 제 5b도는 AZAMP 42에 입력되는 신호 AZ 44가 AZ 클럭신호가 턴-오프된 후 그리고  $AZ^*$  클럭신호가 턴-온되기 전에 턴-온되는 지점에 세 교호의 비-종첩 클럭신호들을 도시한다. 이러한 교호의 타이밍구조는 AZAMP가 부정함에 의해 야기된 오프셋과 AZ 클럭신호에 의해 제어되는 스위치들로부터의 전하주입을 보상하도록 하다. 앞서 논의된 예에서, AZ신호 44는 AZ 비-종첩 클럭신호와 동일한 타이밍구조를 따른다.

이상 자장 샘플 훌드 및 오토제로를 갖는 연산증폭기에 관하여 설명하였다.

#### (57) 청구의 범위

**청구항 1**

차동증폭기에 있어서, 차동입력신호를 수신하기 위한 제1단과, 상기 제1단에 연결되는 제1 바이어스수단과, 상기 제1단과 불균형감지단의 출력에 연결되는 제1 스위칭수단과, 상기 제1 스위칭수단에 연결되는 제1 전하제거수단과, 상기 제1 스위칭수단에 연결되며, 상기 제1단의 오프셋을 감지 및 교정하고, 상기 제1 스위칭수단이 턴-오프될 때 오프셋 교정을 유지하기에 적절한 교정전압을 저장하는 상기 불균형감지단과, 상기 제1단과 제2단에 연결되는 제2 스위칭수단과, 상기 제2 스위칭수단에 연결되는 제2 전하제거수단과, 다수 동작 단계들의 각 단계동안 상기 차동증폭기로부터 유효출력을 제공하기 위한 상기 제2단을 포함하는 차동증폭기.

**청구항 2**

제1항에 있어서, 상기 제1 전하제거수단이, 제1 캐패시터에 연결되는 제1 모스트랜지스터를 포함하는 차동증폭기.

**청구항 3**

제1항에 있어서, 상기 제2 전하제거수단이, 제2 캐패시터와 연결되는 제2 모스트랜지스터를 포함하는 차동증폭기.

**청구항 4**

제3항에 있어서, 상기 불균형감지단에 의해 제공되는 상기 교정전압이 제3 캐패시터에 저장되는 차동증폭기.

**청구항 5**

제4항에 있어서, 훌딩신호에 의해 제어되는 상기 제2 스위칭수단이 상기 제2단으로부터 상기 제1단을 분리하며, 상기 훌딩신호가 하이상태일 때 상기 제2단이 상기 제1단으로부터의 상기 출력을 제4 캐패시터에 저장된 전압의 상태로 저장하는 차동증폭기.

**청구항 6**

차동증폭기에 있어서, 차동입력신호를 수신하기 위한 제1단과, 상기 제1단과 아날로그 불균형감지단의 출력에 연결되는 제1 스위칭수단과, 상기 제1 스위칭수단에 연결되며, 상기 제1단의 오프셋을 감지 및 교정하고, 상기 제1 스위칭수단이 턴-오프될 때 오프셋 교정을 유지하기에 적절한 교정전압을 제1 캐패시터에 저장하는 상기 아날로그 불균형감지단과, 제2 캐패시터에 접속되며 제1 모스트랜지스터로 이루어지는 상기 제1 스위칭수단에 연결된 제1 전하제거수단과, 상기 제1단과 제2단에 연결되는 제2 스위칭수단과, 다수 동작 단계들의 각 단계동안 상기 차동증폭기로부터 유효출력을 제공하기 위한 상기 제2단을 포함하는 차동증폭기.

**청구항 7**

제6항에 있어서, 제2 캐패시터와 연결되는 제1 모스트랜지스터를 포함하는 제1 전하제거수단이 상기 제1 스위칭수단의 스위칭 동안 과도현상을 막기 위해 상기 제1 스위칭수단에 연결되는 차동증폭기.

**청구항 8**

제6항에 있어서, 제3 캐패시터와 연결되는 제2 모스트랜지스터를 포함하는 제2 전하제거수단이 상기 제2 스위칭수단에 연결되는 차동증폭기.

**청구항 9**

오토-제로 구조 회로에 있어서, 사용자 입력 전압과 입력 기준 전압에 연결되는 제1 스위칭수단과, 상기 제1 스위칭수단에 연결되는 제1 캐패시터와, 상기 제1 캐패시터에 연결되는 차동증폭기와, 각각 상기 차동증폭기의 음과 양의 입력에 연결되며 제1 기준전압에 연결되고, 상기 음의 입력이 상기 제1 캐패시터에 연결되는 제2 및 제3 스위칭수단과, 각각 상기 차동증폭기의 상기 음과 양의 입력들에 연결되는 제2 및 제3 캐패시터와, 상기 제2 캐패시터에 연결되며, 또한 상기 차동증폭기의 출력과 제2 기준전압에 연결되는 제4 스위칭수단을 포함하며, 상기 제1, 제2, 제3, 그리고 제4 스위칭수단이 제1 및 제2 비중첩클럭신호들에 의해 제어되어며, 상기 제1 비-중첩클럭신호 동안 상기 제1 스위칭수단이 입력기준전압을 상기 제1 캐패시터에 연결하고, 상기 제2 및 제3 스위칭수단이 상기 제1 기준전압을 상기 음과 양의 입력들에 각기 전달하며, 상기 제4 스위칭수단이 상기 제2 기준전압을 상기 제2 캐패시터에 연결하는 오토-제로 구조 회로.

**청구항 10**

제9항에 있어서, 상기 제1, 제2, 제3 및 제4 스위칭수단이 제1 및 제2 비중첩클럭신호들에 의해 제어되고, 상기 제1 비중첩클럭신호 동안 상기 제1 스위칭수단이 입력기준전압에 연결되며 상기 제2 및 제3 스위칭수단은 기준전압에 연결되고 상기 제4 스위칭수단이 출력기준전압에 연결되는 오토-제로 구조 회로.

**청구항 11**

제9항에 있어서, 상기 제1 기준전압이 공급전력의 약 1/2인 오토-제로 구조 회로.

**청구항 12**

제9항에 있어서, 상기 차동증폭기가, 제1단과, 상기 제1단에 연결되는 제1 바이어스수단과, 상기 제1단과

불균형감지단의 출력에 연결되는 제5 스위칭수단과, 상기 제5 스위칭수단에 연결되며, 상기 제5 스위칭수단의 스위칭 동안 과도현상을 막기 위한 제1 전하제거수단과, 상기 제1단의 오프셋을 감지 및 교정하고, 상기 제5 스위칭수단이 턴-오프될 때 오프셋 교정을 유지하기에 적절한 교정전압을 저장하는 상기 불균형감지단과, 상기 제1단과 제2단에 연결되는 제6 스위칭수단과, 상기 제6 스위칭수단에 연결되며, 상기 제6 스위칭수단의 스위칭 동안 과도현상을 막기 위한 제2 전하제거수단과, 다수 동작 단계들의 각 단계동안 상기 차동증폭기로부터 유효출력을 제공하기 위한 상기 제2단을 포함하는 오토-제로 구조 회로.

### 청구항 13

제12항에 있어서, 훌드신호가 상기 제6 스위칭수단을 제어하고, 상기 훌드신호가 상기 제2 비중첩 클럭신호가 하이상태일 때의 후반부 동안에는 인가되지 않는 오토-제로 구조 회로.

### 청구항 14

제12항에 있어서, 훌드신호가 상기 제6 스위칭수단을 제어하고, 상기 훌드신호가 상기 제2 비중첩 클럭신호가 하이상태인 동안에는 인가되지 않는 오토-제로 구조 회로.

### 청구항 15

제12항에 있어서, 제1 제어신호가 상기 제6 스위칭수단의 상기 스위칭을 제어하고, 상기 제1 제어신호가 상기 제1 비중첩 클럭신호가 하이상태일 때는 언제나 인가되는 오토-제로 구조 회로.

### 청구항 16

제12항에 있어서, 상기 제1 및 제2 비중첩 클럭신호들의 비중첩신호인 제2 제어신호가 상기 제5 스위칭수단의 상기 스위칭을 제어하며, 상기 제2 제어신호가 상기 제1 비중첩 클럭신호가 하이상태로 된 후 그리고 상기 제2 비중첩 클럭신호가 하이상태이기 전에 인가되는 오토-제로 구조 회로.

### 청구항 17

오토-제로 구조 회로에 있어서, 사용자 입력 전압에 연결되는 제1 스위칭수단과, 차동입력신호를 수신하기 위한 제1단, 상기 제1단에 연결되는 제1 바이어스수단, 상기 제1단과 불균형감지단의 출력에 연결되는 제2 스위칭수단, 상기 제2 스위칭수단에 연결되어 상기 제2 스위칭수단의 스위칭 동안 과도현상을 막기 위한 제1 전하제거수단, 상기 제2 스위칭수단에 연결되어 상기 제2 스위칭수단이 턴-오프일 때 상기 제1 단의 오프셋을 감지 및 교정하고 오프셋 교정을 유지하기에 적합한 교정전압을 저장하는 상기 불균형감지단, 상기 제1단과 제2단에 연결되는 제3 스위칭수단, 상기 제3 스위칭수단에 연결되어 상기 제3 스위칭수단의 스위칭 동안 과도현상을 막기 위한 제2 전하제거수단, 다수 동작 단계들의 각 단계동안 상기 차동증폭기로 부터 유효출력을 제공하는 상기 제2단, 상기 차동증폭기의 음과 양의 입력들에 각기 연결되는 제4 및 제5 스위칭수단, 상기 차동증폭기의 음과 양의 입력들에 각기 연결되며 제1 기준전압에도 연결되는 제2 및 제3 캐패시터, 상기 차동증폭기의 출력과 상기 제2 캐패시터 및 제2 기준전압에 연결되는 제6 스위칭수단을 포함하는 차동증폭기와 상기 제1 스위칭수단에 연결되는 제1 캐패시터를 포함하는 오토-제로 구조 회로.

### 청구항 18

제17항에 있어서, 상기 제1, 제4, 제5 및 제6 스위칭수단이 제1 및 제2 비중첩 클럭신호들에 의해 제어되며, 상기 제1 비-중첩 클럭신호 동안 상기 제1 스위칭수단이 입력기준전압을 상기 제1 캐패시터에 전달하고, 상기 제4 및 제5 스위칭수단이 상기 제1 기준전압을 상기 음과 양의 입력들에 각기 전달하며, 상기 제6 스위칭수단이 상기 제2 기준전압을 상기 제2 캐패시터에 전달하는 오토-제로 구조 회로.

### 청구항 19

제18항에 있어서, 상기 제1 기준전압이 공급전력의 약 1/2인 오토-제로 구조 회로.

### 청구항 20

제19항에 있어서, 훌딩신호가 상기 제3 스위칭수단을 제어하며, 상기 훌딩신호가 상기 제2 비중첩 클럭신호가 하이상태일 때의 후반부 동안 인가되는 오토-제로 구조 회로.

### 청구항 21

제19항에 있어서, 훌딩신호가 상기 제3 스위칭수단을 제어하며, 상기 훌딩신호가 상기 제2 비중첩 클럭신호가 하이상태인 시간 동안 인가되는 오토-제로 구조 회로.

### 청구항 22

제19항에 있어서, 제1 제어신호가 상기 제2 스위칭수단의 상기 스위칭을 제어하며, 상기 제1 비중첩 클럭신호가 하이상태일 때는 상기 제1 제어신호가 언제나 인가되는 오토-제로 구조 회로.

### 청구항 23

제19항에 있어서, 상기 제1 및 제2 비중첩 클럭신호인 비중첩신호인 제2 제어신호가 상기 제2 스위칭수단의 상기 스위칭을 제어하며, 상기 제2 제어신호가 상기 제1 비중첩 클럭신호가 하이상태로 된 후 그리고 상기 제2 비중첩 클럭신호가 하이상태가 되기 전에 하이상태가 되는 오토-제로 구조 회로.

### 청구항 24

차동증폭기에 있어서, 제1 및 제2 트랜지스터들을 포함하여, 차동입력신호를 수신하는 쌍 접속 제1 소오소와, 제3 트랜지스터의 드레인, 제4 트랜지스터의 드레인과 게이트 및 제8 트랜지스터의 게이트에 연결

되는 상기 제1 트랜지스터의 드레인과, 제5 트랜지스터의 드레인, 제6 트랜지스터의 드레인과 게이트 및 제9 트랜지스터게이트에 연결되는 상기 제2 트랜지스터의 드레인과, 제7 트랜지스터의 드레인에 연결되는 상기 쌍 접속 제1 소오스의 상기 소오스들과, 쌍 접속 제2 소오스를 형성하며, 상기 쌍 접속 제2 소오스의 상기 소오스들이 제10 트랜지스터의 드레인에 연결되는 상기 제3 및 제5 트랜지스터와, 제11 트랜지스터의 드레인과 게이트 및 제12 트랜지스터의 게이트에 연결되는 상기 제8 트랜지스터의 드레인과, 제13, 제14 및 상기 제12 트랜지스터의 드레인들에 연결되는 상기 제9 트랜지스터의 드레인과, 전력공급단에 연결되는 상기 제4, 제6, 제8 및 제9 트랜지스터의 소오스들과, 기준전압에 연결되는 상기 제3 트랜지스터의 게이트와, 제15 트랜지스터의 게이트와 드레인 및 제16 트랜지스터의 드레인에 연결되는 상기 제7 및 제10 트랜지스터들의 게이트들과, 상기 제17 및 제18 트랜지스터의 드레인들에 연결되는 상기 제16, 제17, 제19 및 제20 트랜지스터의 게이트들과, 상기 전력공급단에 연결되는 상기 제16 및 제17 트랜지스터들의 소오스들과, 접지에 연결되는 상기 제7, 제10, 제11, 제12, 제15 및 제18 트랜지스터들의 소오스들과, 상기 제18 트랜지스터의 게이트에 연결되는 바이어스전압과, 상기 제13 트랜지스터와 제21 트랜지스터의 게이트들에 연결되는 제1 제어신호와, 상기 제14 트랜지스터와 제22 트랜지스터의 게이트들에 연결되는 제2 제어신호와, 제1 캐패시터의 제1판과 상기 제19 트랜지스터와 제23 트랜지스터의 드레인들에 연결되는 상기 제5 트랜지스터의 게이트와, 제2 캐패시터의 제1판과 제24, 제25 및 제26 트랜지스터의 게이트들과 상기 제22, 제28 트랜지스터의 드레인들에 연결되는 상기 제13 트랜지스터의 소오스와, 상기 제1 캐패시터의 제2판과 상기 제23 트랜지스터의 게이트와 상기 제21 트랜지스터의 드레인과 제27 트랜지스터의 드레인에 연결되는 상기 제14 트랜지스터의 소오스와, 제3 캐패시터의 제1판에 연결되는 상기 제22 트랜지스터의 소오스와, 제4 캐패시터의 제1판에 연결되는 상기 제21 트랜지스터의 소오스와, 접지에 연결되는 상기 제3 및 제4 캐패시터들의 제2판과, 상기 제24 트랜지스터와 제29 트랜지스터의 드레인들과 제30, 제31 트랜지스터들의 베이스들에 연결되는 상기 제20 트랜지스터의 드레인과, 상기 제2 캐패시터의 제2판과 상기 제25 트랜지스터의 드레인에 연결되는 상기 제30 트랜지스터의 에미터와, 상기 제26 트랜지스터의 드레인에 연결되는 출력전압을 제공하는 상기 제31 트랜지스터의 에미터와, 상기 전력공급단에 연결되는 상기 제19 및 제20 트랜지스터들의 소오스들과 상기 제30 및 제31 트랜지스터들의 콜렉터들와 접지에 연결되는 상기 제27, 제23, 제28, 제24, 제25, 제26 및 제29 트랜지스터들의 소오스들과, 제3 제어신호에 연결되는 상기 제27, 제28 및 제29 트랜지스터들의 게이트들을 포함하는 차동증폭기.

## 청구항 25

차동증폭기에 있어서, 제1 및 제2 트랜지스터들을 포함하며, 차동입력신호를 수신하는 쌍 접속 제1 소오스와, 제3 트랜지스터의 드레인 그리고 제4 트랜지스터의 드레인과 게이트 및 제8 트랜지스터의 게이트에 연결되는 상기 제1 트랜지스터의 드레인과, 제5 트랜지스터의 드레인 그리고 제6 트랜지스터의 드레인과 게이트 및 제9 트랜지스터의 게이트에 연결되는 상기 제2 트랜지스터의 드레인과, 제7 트랜지스터의 드레인에 연결되는 상기 쌍 접속 제1 소오스의 상기 소오스들과, 쌍 접속 제2 소오스를 형성하며, 상기 쌍 접속 제2 소오스의 상기 소오스들이 제10 트랜지스터의 드레인에 연결되는 상기 제3 및 제5 트랜지스터와, 제11 트랜지스터의 드레인과 게이트 및 제12 트랜지스터의 게이트에 연결되는 상기 제8 트랜지스터의 드레인과, 제1 및 제2 스위칭수단의 제1단자와 상기 제12 트랜지스터의 드레인에 연결되는 상기 제9 트랜지스터의 드레인과, 전력공급단에 연결되는 상기 제4, 제6, 제8 및 제9 트랜지스터의 소오스들과, 기준전압에 연결되는 상기 제3 트랜지스터의 게이트와, 제15 트랜지스터의 게이트와 드레인 및 제16 트랜지스터의 드레인에 연결되는 상기 제7 및 제10 트랜지스터들의 게이트들과, 상기 제17 트랜지스터와 제18 트랜지스터의 드레인들에 연결되는 상기 제16, 제17, 제19 및 제20 트랜지스터의 게이트들과, 상기 전력공급단에 연결되는 상기 제16 및 제17 트랜지스터의 소오스들과, 접지에 연결되는 상기 제7, 제10, 제11, 제12, 제15 및 제18 트랜지스터들의 소오스들과, 상기 제18 트랜지스터의 게이트에 연결되는 바이어스전압과, 상기 제2 스위칭수단의 제2단자에 연결되는 제1 제어신호와, 상기 제1 스위칭수단의 제2단자에 연결되는 제2 제어신호와, 제1 캐패시터의 제1판과 상기 제19, 제23 트랜지스터의 드레인들에 연결되는 상기 제5 트랜지스터의 게이트와, 제2 캐패시터의 제1판과 제24, 제25 및 제26 트랜지스터의 게이트들과 제28 트랜지스터의 드레인 연결되는 상기 제2 스위칭수단의 제3단자와, 상기 제1 캐패시터의 제2판과 상기 제23 트랜지스터의 게이트와 제27 트랜지스터의 드레인에 연결되는 상기 제2 스위칭수단의 제3단자와, 상기 제24, 제29 트랜지스터의 드레인들과 제30 및 제31 트랜지스터들의 베이스들에 연결되는 상기 제20 트랜지스터의 드레인과, 상기 제2 캐패시터의 제2판과 상기 제25 트랜지스터의 드레인에 연결되는 상기 제30 트랜지스터의 에미터와, 상기 제26 트랜지스터의 드레인에 연결되는 출력전압을 제공하는 상기 제31 트랜지스터의 에미터와, 상기 전력공급단에 연결되는 상기 제19 및 제20 트랜지스터들의 소오스들과 상기 제30 및 제31 트랜지스터들의 콜렉터들과, 접지에 연결되는 상기 제27, 제23, 제28, 제24, 제25, 제26 및 제29 트랜지스터들의 소오스들과, 제3 제어신호에 연결되는 상기 제27, 제28 및 제29 트랜지스터들의 게이트들을 포함하는 차동증폭기.

## 청구항 26

제25항에 있어서, 상기 제1 스위칭수단이 제1 엔-채널 전계효과트랜지스터를 포함하는 차동증폭기.

## 청구항 27

제25항에 있어서, 상기 제2 스위칭수단이 제2 엔-채널 전계효과트랜지스터를 포함하는 차동증폭기.

## 청구항 28

제25항에 있어서, 상기 차동증폭기가, 제3 캐패시터에 연결되는 제3 엔-채널 전계효과트랜지스터를 구비하는 상기 제1 스위칭수단에 연결되는 제1 전하제거수단을 더 포함하는 차동증폭기.

## 청구항 29

제25항에 있어서, 상기 차동증폭기가, 제4 캐패시터에 연결되는 제4 엔-채널 전계효과트랜지스터를 구비하는 상기 제2 스위칭수단에 연결되는 제2 전하제거수단을 더 포함하는 차동증폭기.

도면

도면 1a

도면 1b

도면2

도면3

도면4

도면5a

도면5b