(12) 发明专利

(10) 授权公告号 CN 110808288 B

(45) 授权公告日 2023.11.14

(21) 申请号 201911111690.7

(74) 专利代理机构 北京纪凯知识产权代理有限公司 11245

(22) 申请日 2014.09.26

专利代理人 魏利娜

(65) 同一申请的已公布的文献号

申请公布号 CN 110808288 A

(51) Int.CI.

H01L 29/78 (2006.01)

(43) 申请公布日 2020.02.18

H01L 29/423 (2006.01)

(30) 优先权数据

H01L 29/40 (2006.01)

14/044,909 2013.10.03 US

H01L 29/08 (2006.01)

(62) 分案原申请数据

H01L 29/06 (2006.01)

201480065667.8 2014.09.26

H01L 21/336 (2006.01)

(73) 专利权人 德克萨斯仪器股份有限公司

(56) 对比文件

地址 美国德克萨斯州

JP 特開平6-104446 A, 1994.04.15

(72) 发明人 M·丹尼森 S·彭德哈卡尔

US 2009/0140327 A1, 2009.06.04

G·马图尔

CN 1342332 A, 2002.03.27

US 2013/0137230 A1, 2013.05.30

审查员 卢振宇

权利要求书1页 说明书6页 附图12页

(54) 发明名称

沟槽栅极沟槽场板半垂直半横向MOSFET

(57) 摘要

本申请公开沟槽栅极沟槽场板半垂直半横向MOSFET。在描述的示例中，半导体器件具有带有深沟槽结构的垂直漏极延伸MOS晶体管以限定垂直漂移区和至少一个垂直漏极接触区，所述垂直漏极接触区通过深沟槽结构的至少一个实例与垂直漂移区分开。掺杂剂被植入至垂直漏极接触区，并且半导体器件被退火，使得植入的掺杂剂扩散接近深沟槽结构的底部。垂直漏极接触区在介于中间的深沟槽结构的底部处电接触至最近的垂直漂移区。至少一个栅极、主体区和源极区形成在漂移区之上且在半导体器件的衬底的顶部表面处或接近半导体器件的衬底的顶部表面处。深沟槽结构被隔开以形成漂移区的RESURF区域。

1. 一种垂直MOS晶体管,其包括:

半导体衬底;

在所述半导体衬底中形成的多个晶体管结构,

每个所述晶体管结构包括:

栅极沟槽,其具有侧壁和底部部分并且在第一方向上延伸,其中栅极介电层形成在所述栅极沟槽的所述侧壁和所述底部部分上,并且栅极形成在所述栅极介电层上;

沟槽对,其布置成将所述栅极沟槽置于其间并且定位成与所述栅极沟槽间隔开,所述沟槽对中的每个沟槽在所述第一方向上延伸并且在垂直于所述第一方向的第二方向与所述栅极沟槽间隔开,其中所述沟槽对中的每个沟槽具有侧壁和底部部分,并且具有形成在所述侧壁和所述底部部分上的介电内衬以及形成在所述介电内衬上的导电材料;

第一导电类型的源极区,其形成在所述半导体衬底的表面处并且在所述第二方向上延伸通过所述栅极沟槽和所述沟槽对的两个沟槽之间的区域;

第二导电类型的主体区,其形成在所述半导体衬底中并且在所述源极区之下,并且邻近所述栅极沟槽的所述侧壁和所述沟槽对的每个沟槽的所述侧壁;以及

所述第一导电类型的漂移区,其形成在所述半导体衬底中并且在所述主体区之下,

其中所述多个晶体管结构在所述第二方向上以预定距离布置,并且所述半导体衬底的对应于所述预定距离的区域是具有所述第一导电类型的杂质的掺杂区域。

2. 根据权利要求1所述的垂直MOS晶体管,其中在所述沟槽对的每个沟槽中的所述导电材料电耦合到所述源极区。

3. 根据权利要求1所述的垂直MOS晶体管,其中所述沟槽对中的每个沟槽的宽度在0.5微米和1.5微米之间。

4. 根据权利要求1所述的垂直MOS晶体管,其中所述预定距离在0.5微米和2.5微米之间。

5. 根据权利要求1所述的垂直MOS晶体管,其中所述介电内衬包括氮化硅。

6. 根据权利要求1所述的垂直MOS晶体管,其中所述介电内衬包括氮氧化硅。

7. 根据权利要求1所述的垂直MOS晶体管,其中所述半导体衬底的对应于所述预定距离的所述区域形成所述垂直MOS晶体管的漏极接触。

8. 根据权利要求1所述的垂直MOS晶体管,进一步包括:

所述半导体衬底中的沟槽隔离结构,所述沟槽隔离结构具有闭合环路配置,其中所述沟槽隔离结构围绕所述多个晶体管结构。

9. 根据权利要求1所述的垂直MOS晶体管,其中所述掺杂区域是所述垂直MOS晶体管的漏极接触区域,并且在所述沟槽对的所述底部部分下方延伸。

10. 根据权利要求1所述的垂直MOS晶体管,其中所述半导体衬底的对应于所述预定距离的所述区域包括所述垂直MOS晶体管的另一源极区域。

11. 根据权利要求1所述的垂直MOS晶体管,其中所述沟槽对中的每个沟槽具有带有内部区域的闭合环路配置,所述内部区域包括所述垂直MOS晶体管的漏极接触。

## 沟槽栅极沟槽场板半垂直半横向MOSFET

[0001] 本申请是国际申请日为2014年09月26日、进入国家阶段日为2016年06月01日的名称为“沟槽栅极沟槽场板半垂直半横向MOSFET”的中国专利申请201480065667.8 (PCT/US2014/057790) 的分案申请。

### 技术领域

[0002] 本发明总体涉及半导体器件，并且具体涉及在半导体器件中的漏极延伸晶体管。

### 背景技术

[0003] 延伸漏极金属氧化物半导体 (MOS) 晶体管可以由在导通状态下晶体管的电阻、晶体管在包含晶体管的衬底的顶部表面处占据的横向面积以及限制晶体管的最大工作电势的在晶体管的漏极节点和源极节点之间的击穿电势来表征。可以期待的是，减少对于给定导通状态电阻和击穿电势的值的晶体管的面积。一种减少面积的技术是在延伸漏极中以垂直方向配置漂移区，使得漂移区中的漏极电流垂直地流至衬底的顶部表面。使用平面处理来将垂直取向漂移区集成在半导体器件中同时将制造成本和复杂性限制到所期待水平可能是有问题的。

### 发明内容

[0004] 在描述的示例中，具有垂直漏极延伸MOS晶体管的半导体器件可以通过形成深沟槽结构以限定晶体管的垂直漂移区并限定接近漂移区的至少一个垂直漏极接触区而形成，所述垂直漏极接触区通过深沟槽结构的至少一个实例与垂直漂移区分开。掺杂剂被植入至垂直漏极接触区，并且半导体器件被退火，使得植入的掺杂剂扩散接近深沟槽结构的底部。垂直漏极接触区在介于中间的深沟槽结构的底部处电接触至最近的垂直漂移区。至少一个栅极、主体区以及源极区形成在漂移区之上 (above) 且在半导体器件的衬底的顶部表面处或接近半导体器件的衬底的顶部表面处。深沟槽结构被隔开以形成漂移区的RESURF区域。

### 附图说明

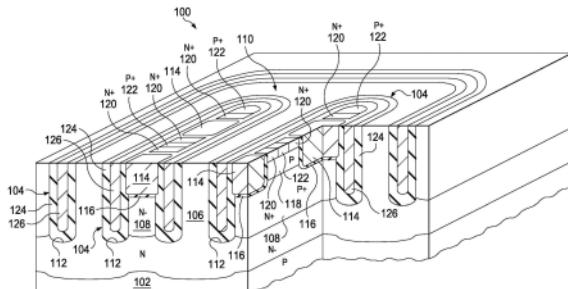

- [0005] 图1是具有垂直漏极延伸MOS晶体管的半导体器件的横截面图。

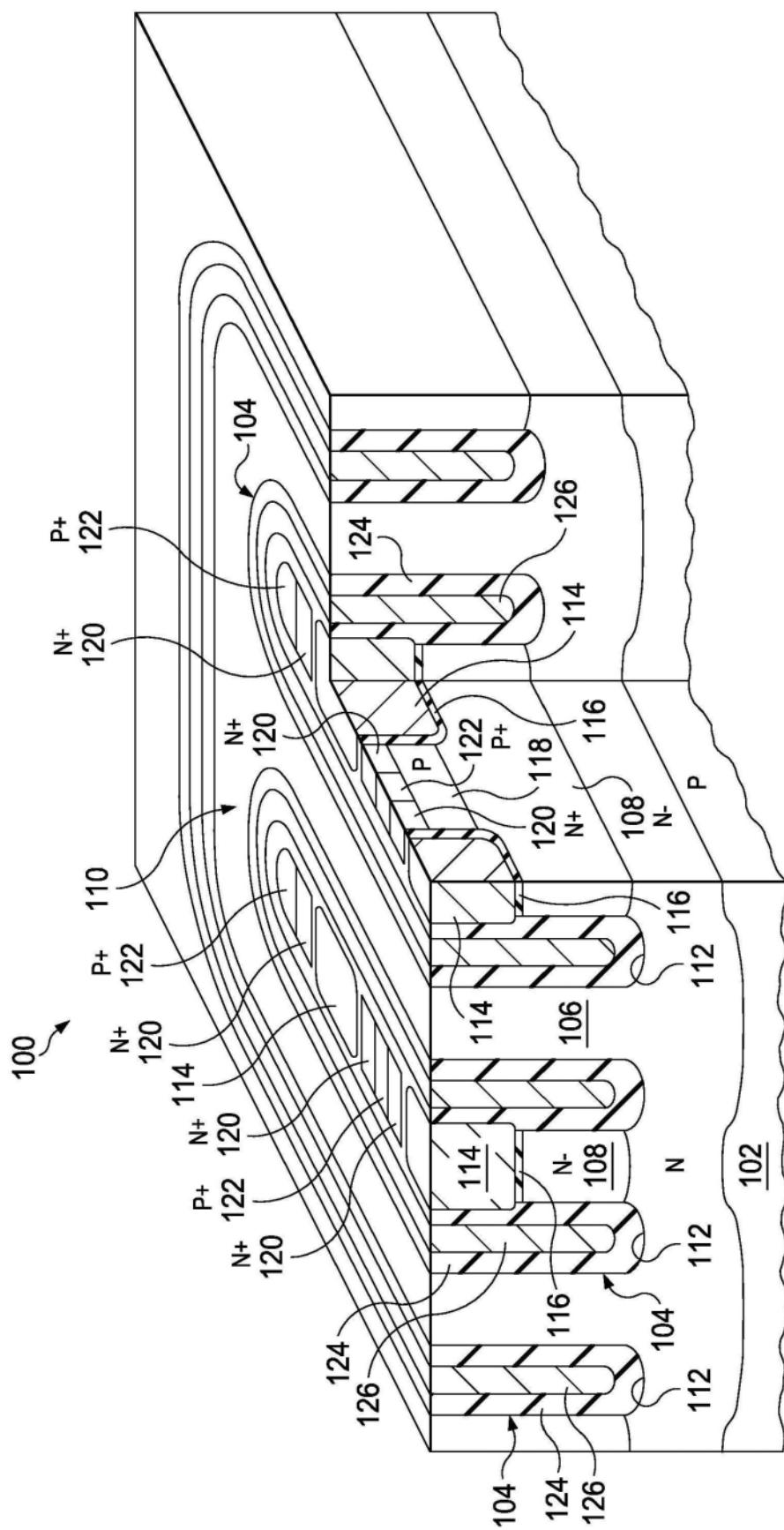

- [0006] 图2是具有垂直漏极延伸MOS晶体管的另一半导体器件的横截面图。

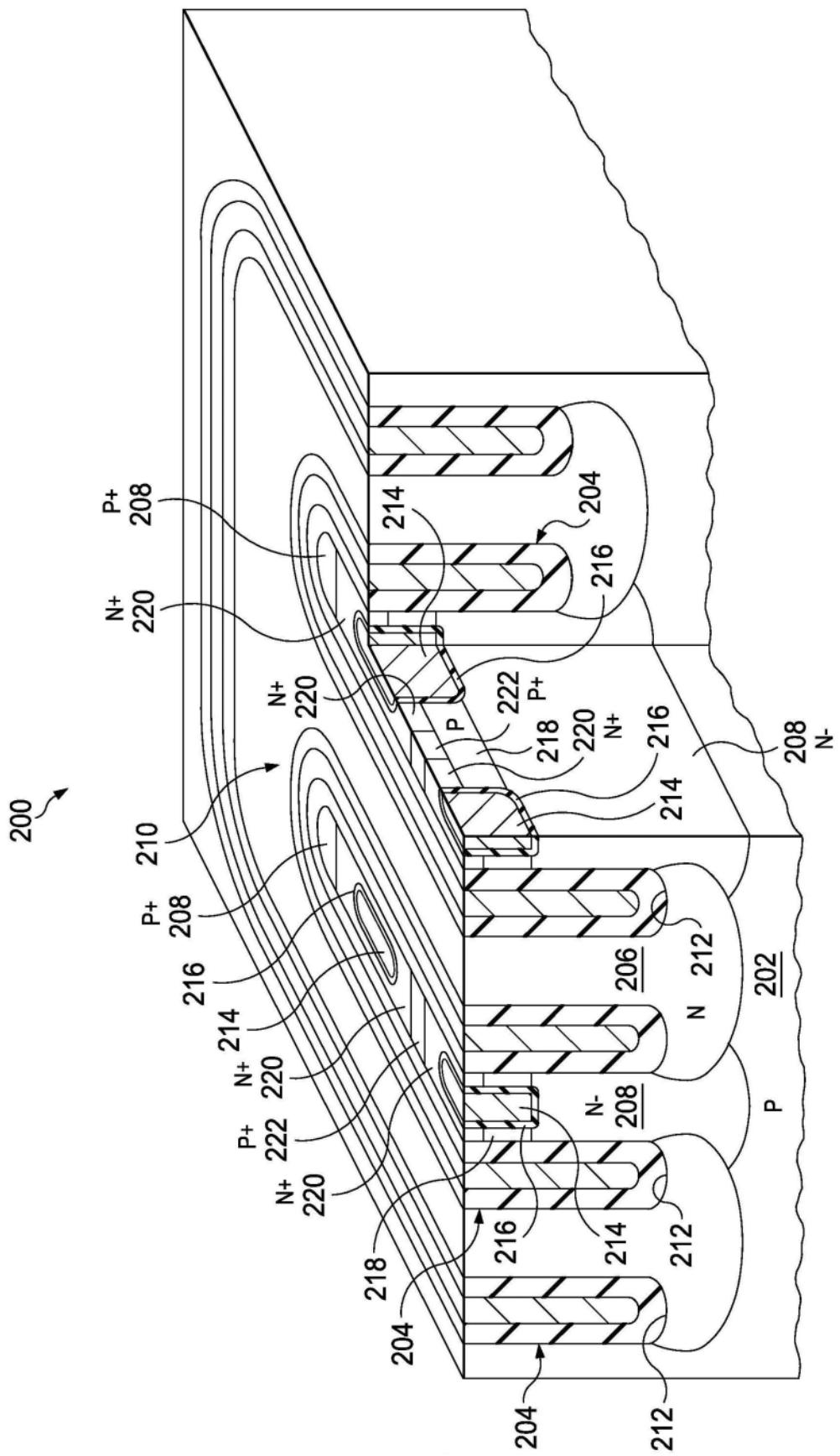

- [0007] 图3是具有垂直漏极延伸MOS晶体管的进一步的半导体器件的横截面图。

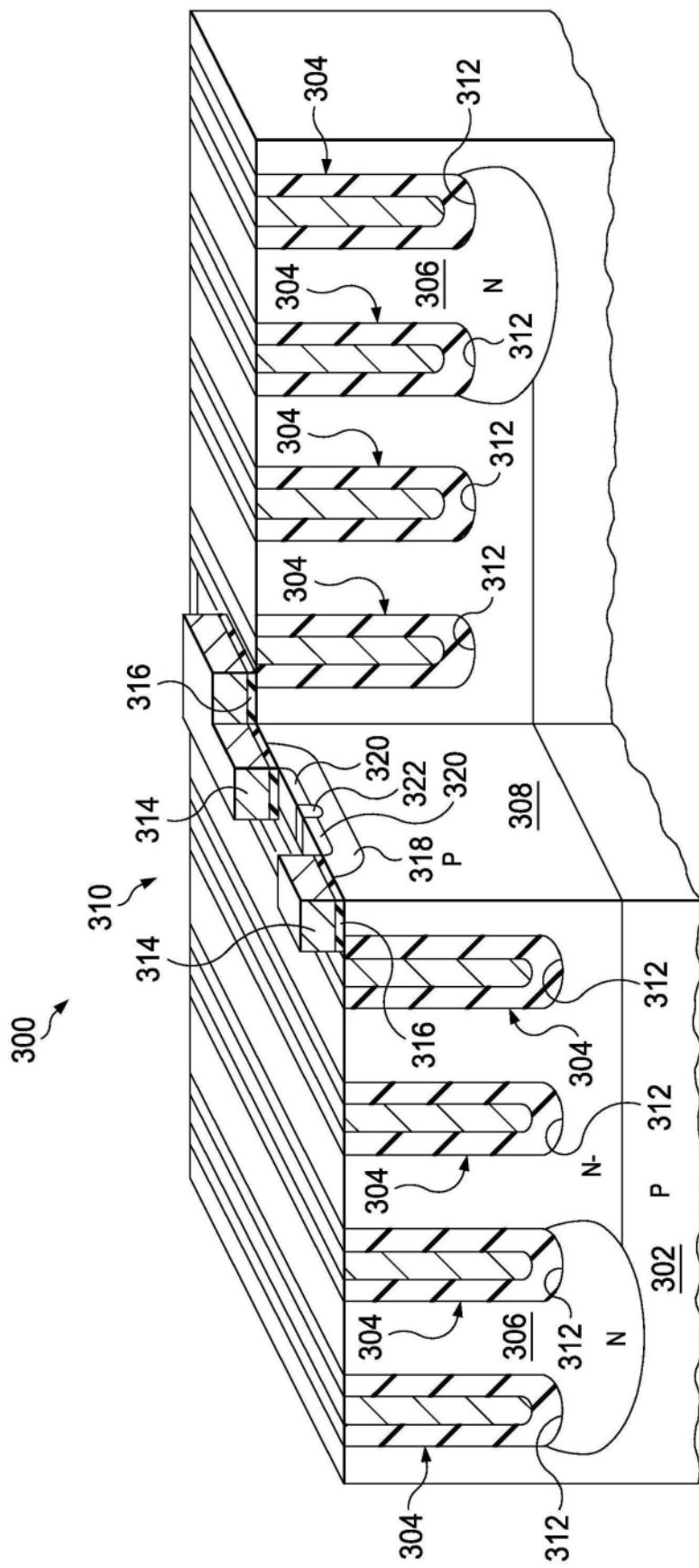

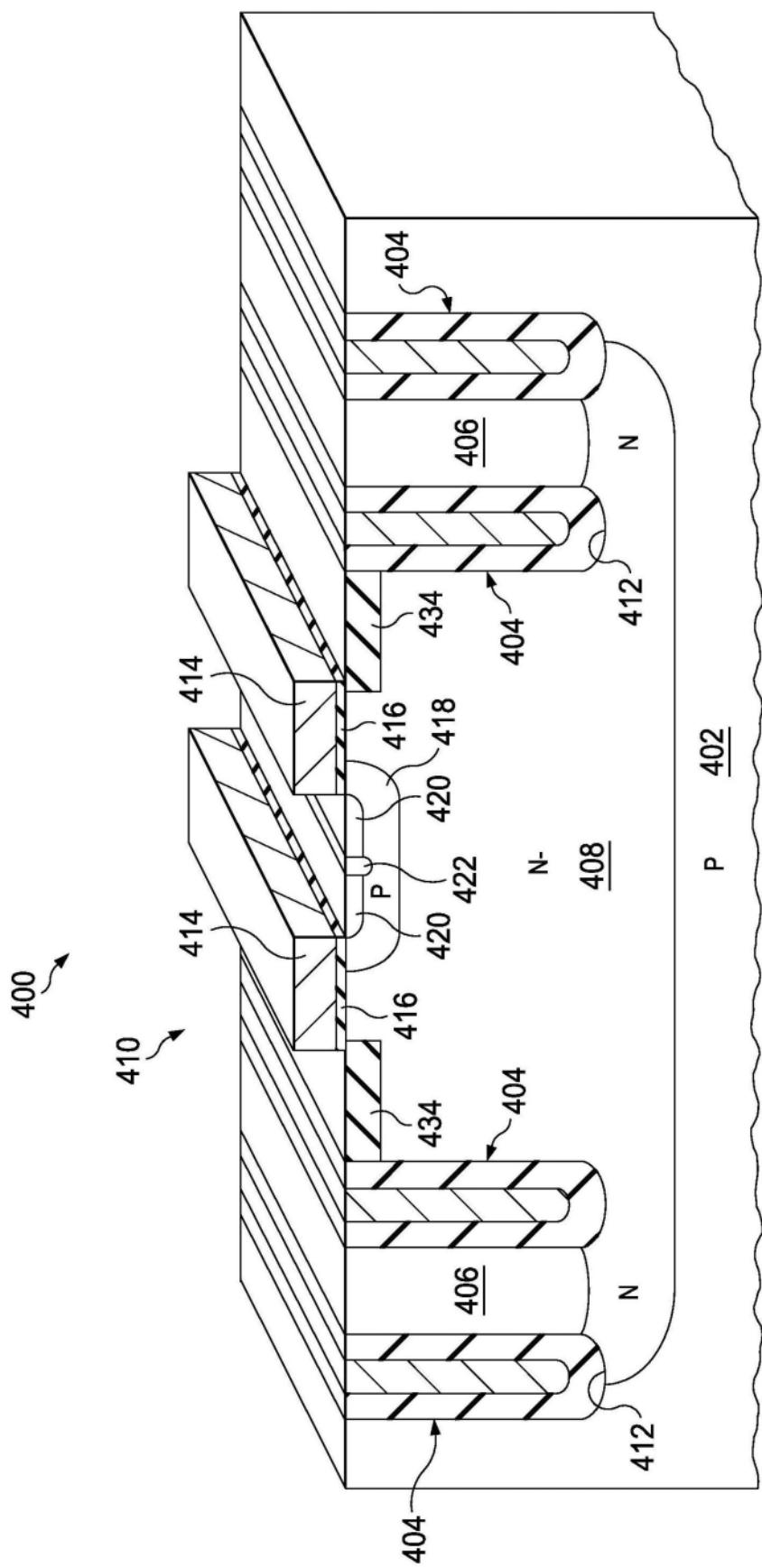

- [0008] 图4是具有垂直漏极延伸MOS晶体管的另一半导体器件的横截面图。

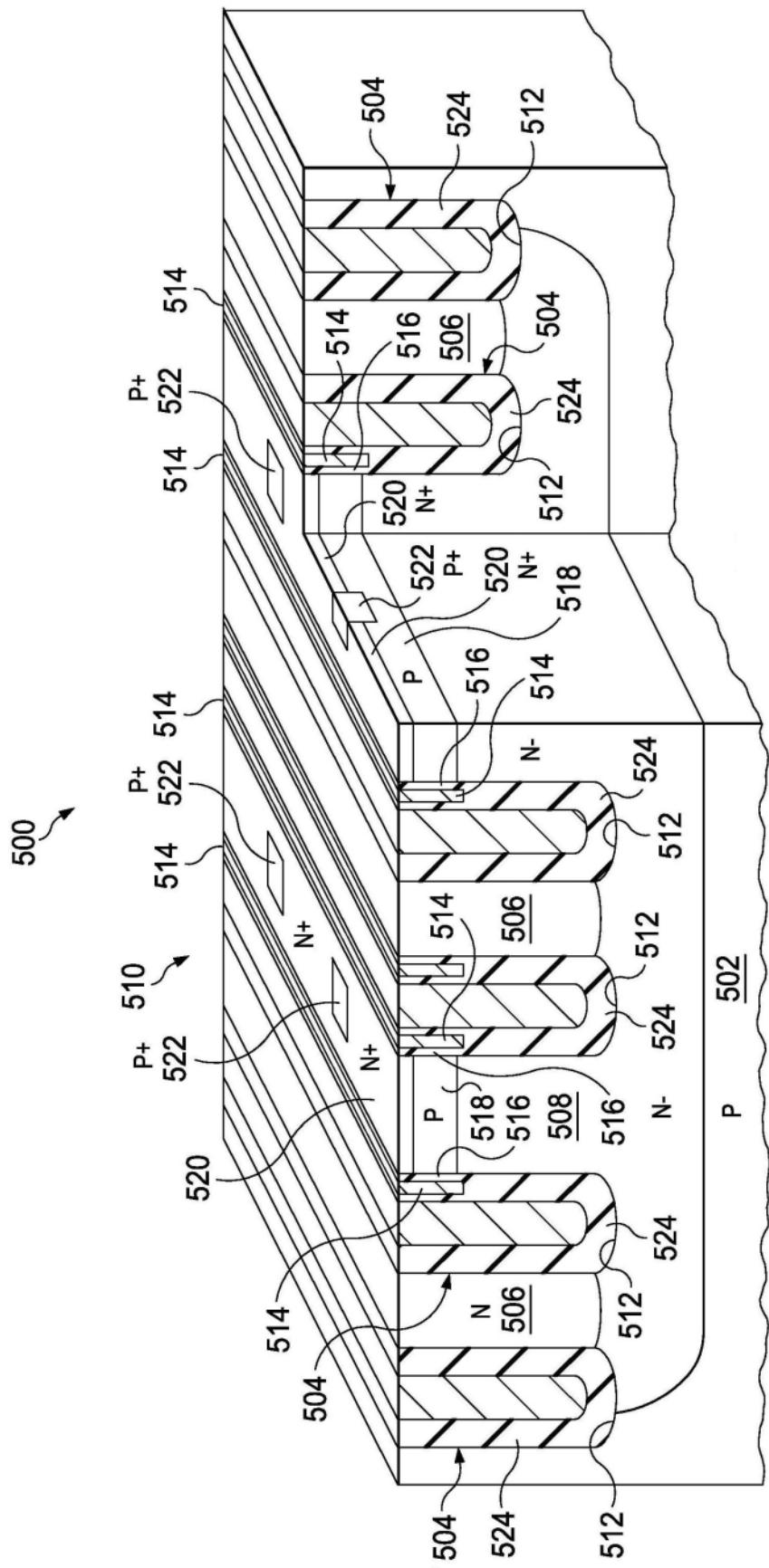

- [0009] 图5是具有垂直漏极延伸MOS晶体管的进一步的半导体器件的横截面图。

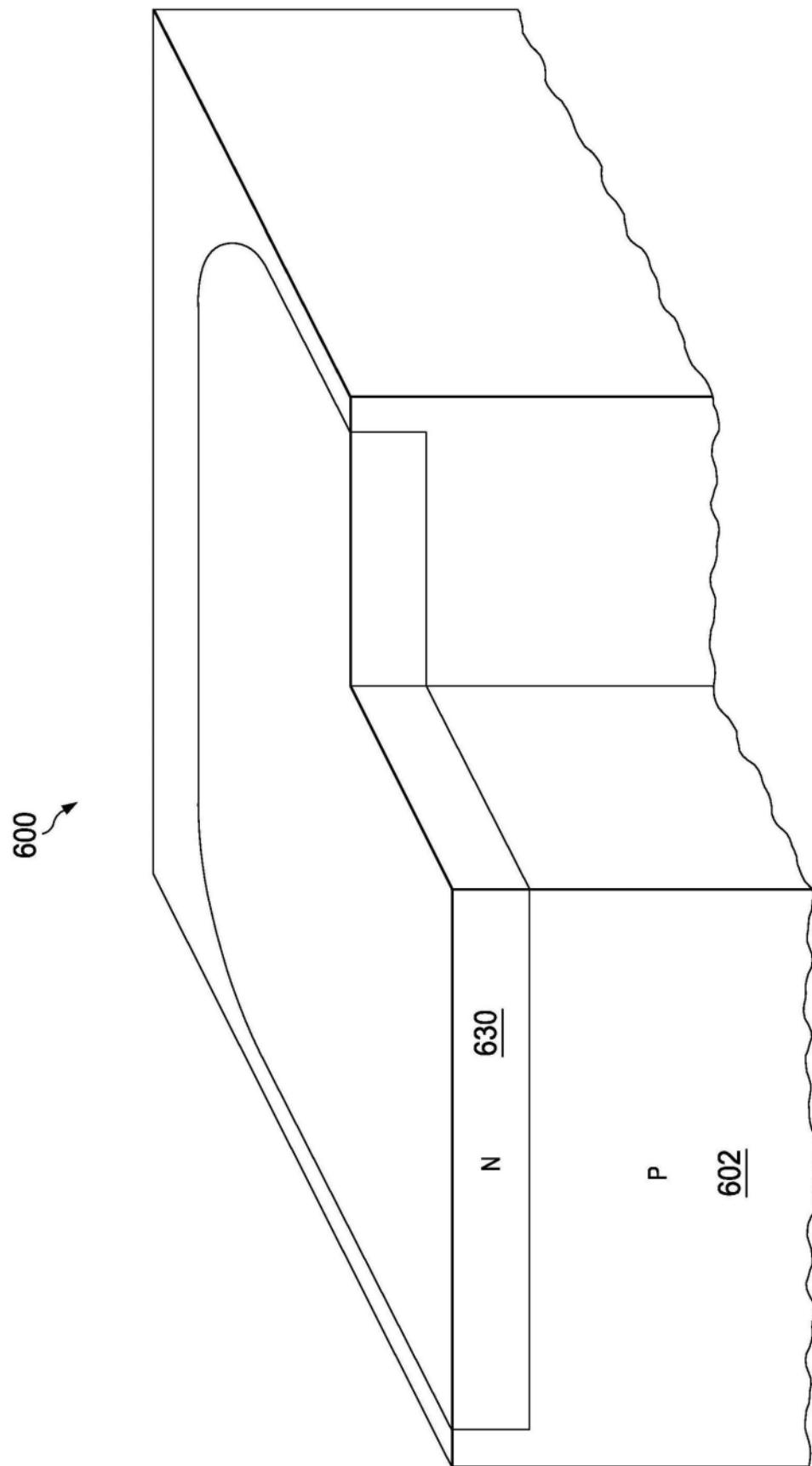

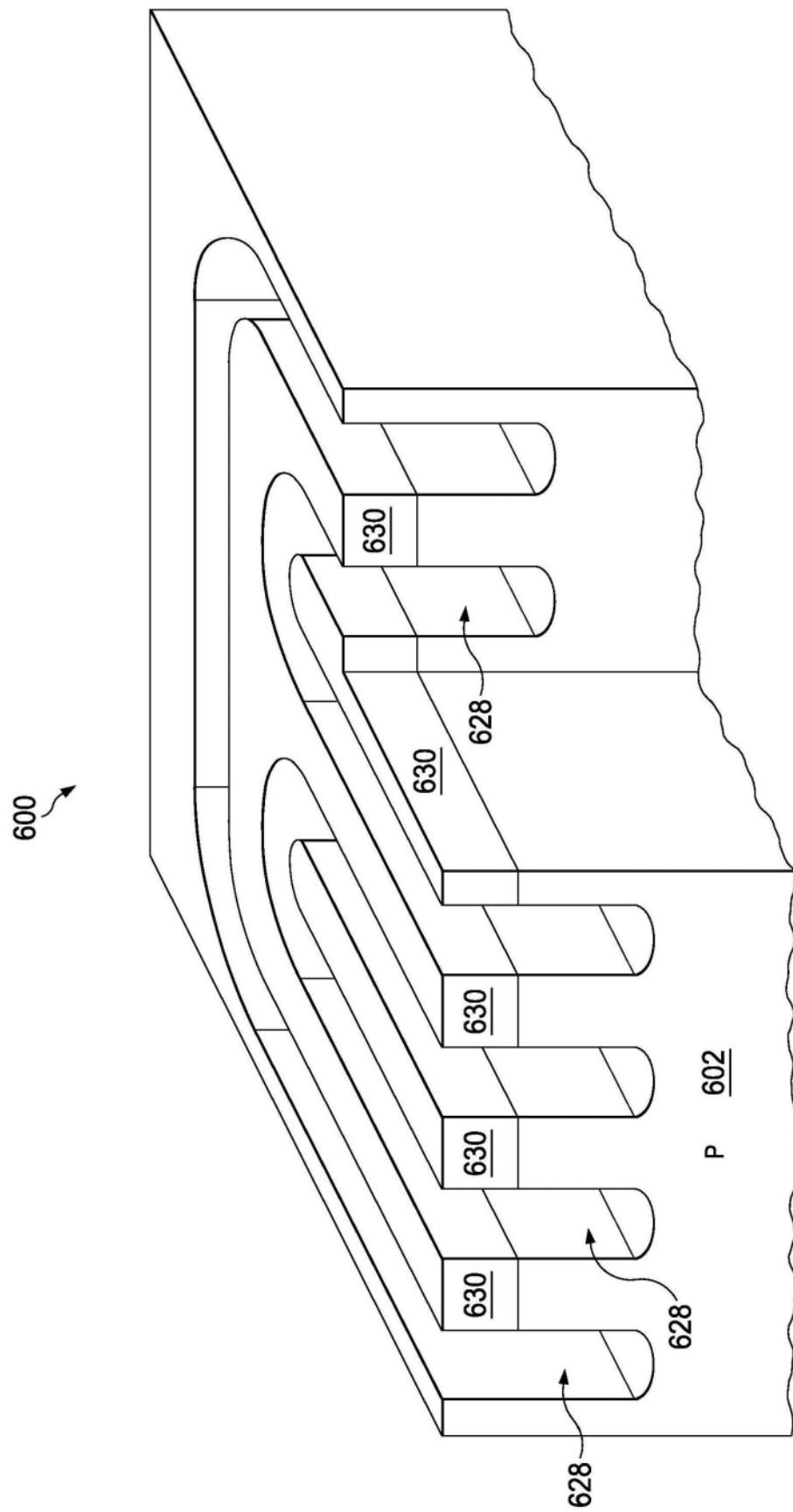

- [0010] 图6A至图6E是在连续的制造阶段中半导体器件的横截面图。

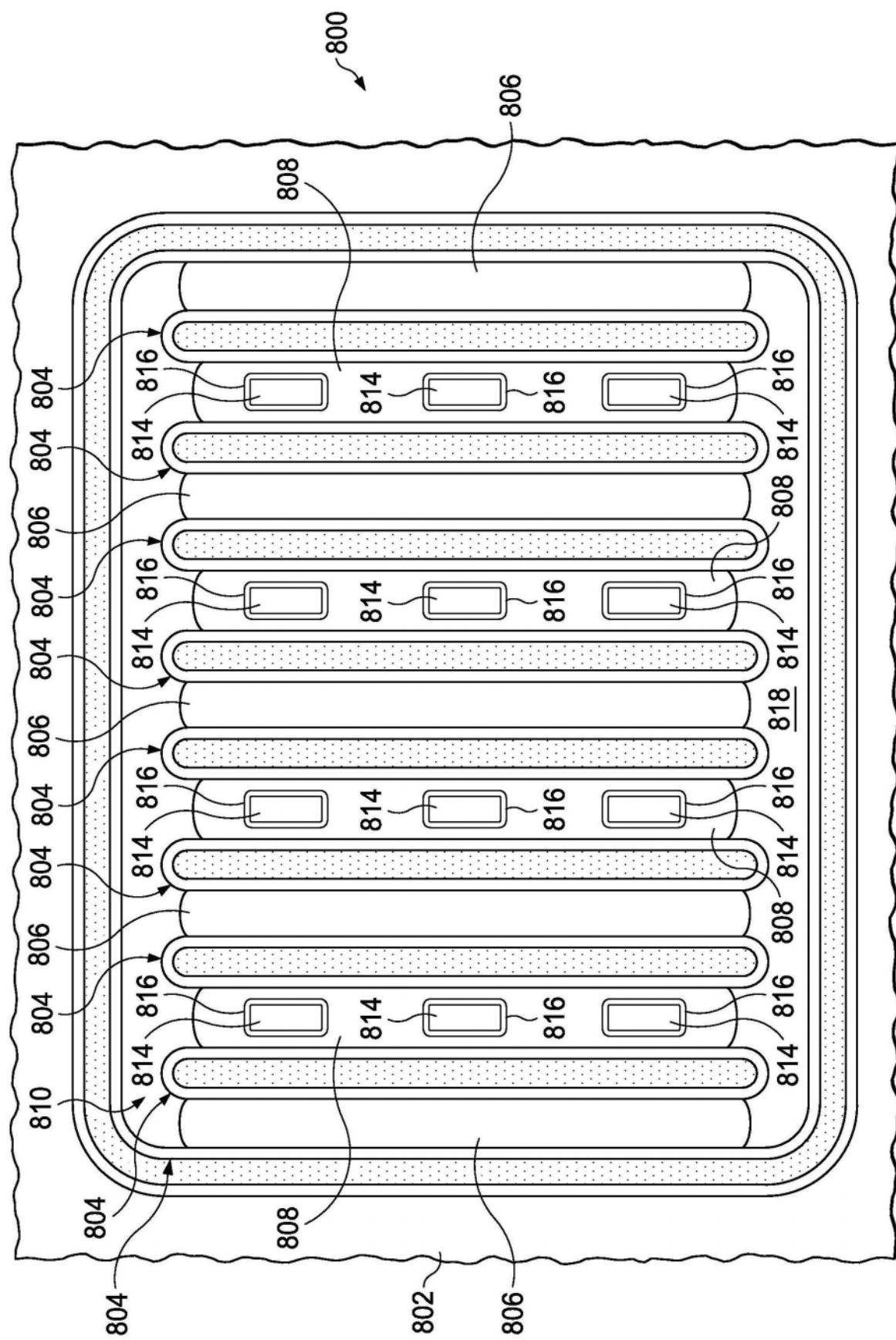

- [0011] 图7和图8是具有垂直漏极延伸MOS晶体管的半导体器件的顶视图。

### 具体实施方式

[0012] 以下共同待审的专利申请在此以引用的方式并入本文中：申请No.US14/044,915；

以及申请No.US 14/044,926。

[0013] 在至少一个示例中,半导体器件可以是包含垂直漏极延伸MOS晶体管和至少一个其它晶体管的集成电路。在另一个示例中,半导体器件可以是垂直漏极延伸MOS晶体管是仅有的晶体管的分立器件。

[0014] 为了该描述的目的,关于晶体管的术语“电阻率”是晶体管在晶体管形成的衬底的顶部表面处占据的面积乘以当晶体管完全导通时晶体管的电阻的积。

[0015] 为了该描述的目的,术语“RESURF”指的是减少在邻近的半导体区域中的电场的材料。例如,RESURF区域可以是具有与邻近的半导体区域相反的导电类型的半导体区域。RESURF结构在Appels等人的“Thin Layer High Voltage Devices”(Philips J,Res.35 1-13,1980)中被描述。

[0016] 在本公开中描述的示例描述n沟道器件。对应的p沟道器件可以通过对掺杂极性作适当改变而形成。图1为具有垂直漏极延伸MOS晶体管的半导体器件的横截面图。半导体器件100在p型半导体衬底102中和在p型半导体衬底102上形成。深沟槽结构104被布置在衬底102中以限定垂直漏极延伸MOS晶体管110的至少一个n型垂直漏极接触区106和至少一个n型垂直取向漂移区108。垂直漏极接触区106由深沟槽结构104界定在至少两个相对侧上。在该示例中,垂直漏极接触区106是n型并且在深沟槽结构104的底部112之下(below)延伸。垂直漏极接触区106可以在深沟槽结构104的底部112的下方横向延伸,以将垂直取向漂移区108与如图1所示的衬底102的p型底部区域分开。在其它示例中,垂直漏极接触区106可以具有更有限的横向范围。垂直取向漂移区108为n型并在接近深沟槽结构104的底部电连接至垂直漏极接触区106。在该示例中,电连接至垂直漏极接触区106在衬底102的顶部表面处进行。

[0017] 至少一个栅极114和对应的栅极介电层116被布置在垂直取向漂移区108的上方。在该示例中,栅极114被布置在衬底102中的沟槽中并且在深沟槽结构104的邻近实例之间延伸。至少一个p型主体区118被布置在邻近栅极114和垂直取向漂移区108的衬底102中。至少一个n型源极区120被布置在邻近栅极114的衬底中。一个或多个可选p型主体接触区122可以在邻接主体区118的衬底102中被布置。在该示例中,电连接至源极区120和主体接触区122在衬底102的顶部表面处进行。其它的栅极配置可以在具有如图1所示的深沟槽结构104、垂直漏极接触区106以及垂直取向漂移区108的配置的垂直漏极延伸MOS晶体管110中被使用。

[0018] 深沟槽结构104可以是1微米至5微米深并且0.5微米至1.5微米宽。例如,2.5微米深的深沟槽结构104可以为垂直漏极延伸MOS晶体管110提供30伏特操作。4微米深的深沟槽结构104可以为垂直漏极延伸MOS晶体管110提供50伏特操作。深沟槽结构104具有介电内衬124并且可以具有可选的导电中心构件126。邻接垂直取向漂移区108的深沟槽结构104的实例可以间隔0.5微米至2微米以为垂直取向漂移区108提供RESURF区域。邻接垂直漏极接触区106的深沟槽结构104的实例可以间隔0.5微米至2.5微米。在垂直漏极延伸MOS晶体管110的操作期间,可以电偏置导电中心构件126(如果有的话)以减少垂直取向漂移区108中的峰值电场。例如,导电中心构件126可以连接至源极区120、栅极114或具有期望电势的偏置源。

[0019] 垂直取向漂移区108的实例邻近垂直漏极接触区106被布置。例如,如图1所示,垂直取向漂移区108的实例可以与垂直漏极接触区106交替。如图1所示,深沟槽结构104可以

围绕垂直取向漂移区108。如图1所示,垂直漏极接触区106可以是连续的。以下讨论深沟槽结构104的可替代配置。形成垂直漏极延伸MOS晶体管110,使得深沟槽结构104为垂直取向漂移区108提供RESURF区域,这可以为垂直漏极延伸MOS晶体管110提供在操作电压和电阻率之间的期望的平衡。形成垂直漏极接触区106以将垂直取向漂移区108与衬底102的底部区域隔离可以期望地减少垂直漏极延伸MOS晶体管110的电阻。

[0020] 图2是具有垂直漏极延伸MOS晶体管的另一个半导体器件的横截面图。半导体器件200被形成在p型半导体衬底202中和p型半导体衬底202上。如参考图1所描述的,深沟槽结构204被布置在衬底202中,以限定垂直漏极延伸MOS晶体管210的至少一个n型垂直漏极接触区206和至少一个n型垂直取向漂移区208。垂直漏极接触区206由深沟槽结构204界定在至少两个相对侧上。该示例中,垂直漏极接触区206是n型并且在深沟槽结构204的底部212之下延伸。垂直漏极接触区206可以横向延伸穿过深沟槽结构204的底部212,但是不足以将垂直取向漂移区208与衬底202的底部区域隔离,如图2所示。在其它示例中,垂直漏极接触区206可以具有更有限的垂直和/或横向范围。垂直取向漂移区208是n型并且在接近深沟槽结构204的底部电连接至垂直漏极接触区206。在该示例中,电连接至垂直漏极接触区206在衬底202的顶部表面处进行。

[0021] 至少一个栅极214和对应的栅极介电层216被布置在垂直取向漂移区208上方。在该示例中,栅极214被布置在衬底202中的沟槽中并且不邻接深沟槽结构204的邻近实例。至少一个p型主体区218被布置在邻近栅极214和垂直取向漂移区208的衬底202中。至少一个n型源极区220被布置在邻近栅极214的衬底中。一个或多个可选p型主体接触区222可以被布置在邻接主体区218的衬底202中。在该示例中,电连接至源极区220和主体接触区222在衬底202的顶部表面处进行。其它的栅极配置可以被使用在具有如图2所示的深沟槽结构204、垂直漏极接触区206以及垂直取向漂移区208的配置的垂直漏极延伸MOS晶体管210中。

[0022] 垂直取向漂移区208的实例邻近垂直漏极接触区206被布置。例如,如图2所示,垂直取向漂移区208的实例可以与垂直漏极接触区206交替。如图2所示,深沟槽结构204可以围绕垂直取向漂移区108。如图2所示,垂直漏极接触区106可以是连续的。形成垂直漏极延伸MOS晶体管210,使得深沟槽结构204为垂直取向漂移区208提供RESURF区域,这可以为垂直漏极延伸MOS晶体管210提供在操作电压和电阻率之间的期望的平衡。形成垂直漏极接触区206以横向延伸穿过深沟槽结构204的底部212,但是不足以将垂直取向漂移区208与衬底202的底部区域隔离,这允许垂直取向漂移区208沿着更长垂直距离的损耗,并且期望地允许在更高电压下的操作。

[0023] 图3具有垂直漏极延伸MOS晶体管的进一步的半导体器件的横截面图。半导体器件300在p型半导体衬底302中和p型半导体衬底302上形成。如参考图1描述的,深沟槽结构304被布置在衬底302中,以限定垂直漏极延伸MOS晶体管310的至少一个n型垂直漏极接触区306和至少一个n型垂直取向漂移区308。垂直漏极接触区306通过深沟槽结构304被界定在至少两个相对侧上。垂直漏极接触区306是n型并可以如图3所示在深沟槽结构304的底部312之下延伸。在该示例中,垂直取向漂移区308从垂直漏极接触区306被横向移位至少两个深沟槽结构304的实例,将水平漂移部件提供至垂直漏极延伸MOS晶体管310的延伸漏极。在该示例中,电连接至垂直漏极接触区306在衬底302的顶部表面处进行。

[0024] 至少一个栅极314和对应的栅极介电层316被布置在垂直取向漂移区308上方。在

该示例中,栅极314被布置在p型主体区318和n型源极区320上方的衬底302之上。一个或多个可选p型主体接触区322可以被布置在邻接主体区318的衬底302中。在该示例中,电连接至源极区320和主体接触区322在衬底302的顶部表面处进行。其它的栅极配置可以被使用在具有如图3所示的深沟槽结构304、垂直漏极接触区306以及横向移位的垂直取向漂移区308的配置的垂直漏极延伸MOS晶体管310中。形成从垂直漏极接触区306横向移位的垂直取向漂移区308可以允许垂直取向漂移区308的横向损耗,并且可以有利地增加垂直漏极延伸MOS晶体管310的操作电压而不需要深沟槽结构304的更深的实例。

[0025] 图4为具有垂直漏极延伸MOS晶体管的另一个半导体器件的横截面图。半导体器件400在p型半导体衬底402中和p型半导体衬底402上形成。如参考图1描述的,深沟槽结构404被布置在衬底402中,以限定垂直漏极延伸MOS晶体管410的至少一个垂直漏极接触区406和至少一个垂直取向漂移区408。垂直漏极接触区406由深沟槽结构404在至少两个相对侧上被界定。垂直漏极接触区406为n型并且在该示例中延伸接近深沟槽结构404的底部412但不在所述底部412之下。垂直取向漂移区408为n型并且在接近深沟槽结构404的底部412电连接至垂直漏极接触区406。

[0026] 至少一个栅极414和对应的栅极介电层416被布置在垂直取向漂移区408上方。在该示例中,栅极414被布置在p型主体区418和n型源极区420上方的衬底402之上。一个或多个可选p型主体接触区422可以被布置在邻接主体区418的衬底402中。在该示例中,直接在栅极414下方的垂直取向漂移区408的部分通过介电材料434(诸如场氧化层434)与深沟槽结构404的最近实例横向分开。此种配置可以将水平漂移部件添加至垂直漏极延伸MOS晶体管410,并且可以有利地增加垂直漏极延伸MOS晶体管410的操作电压。直接在栅极414下方的垂直取向漂移区408的部分也可能通过深沟槽结构404的至少两个实例与垂直漏极接触区406的最近实例中分开,如图3所示。栅极的其它配置可以在具有如图4所示的深沟槽结构404、垂直漏极接触区406以及垂直取向漂移区408的配置的垂直漏极延伸MOS晶体管410中使用。形成从垂直漏极接触区406横向移位的垂直取向漂移区408可以允许垂直取向漂移区408的横向损耗,并且可以有利地增加垂直漏极延伸MOS晶体管410的操作电压,而不需要深沟槽结构404的更深的实例或额外的实例。

[0027] 图5为具有垂直漏极延伸MOS晶体管的进一步的半导体器件的横截面图。如参考图1描述的,半导体器件500在p型半导体衬底502中和p型半导体衬底502上形成。如参考图1描述的,深沟槽结构504被布置在衬底502中,以限定垂直漏极延伸MOS晶体管510的至少一个垂直漏极接触区506和至少一个垂直取向漂移区508的垂直部分。垂直漏极接触区506由深沟槽结构504在至少两个相对侧上被界定。垂直漏极接触区506为n型并且在该示例中延伸接近深沟槽结构504的底部512并可能在深沟槽结构504的底部512之下。在该示例中,垂直取向漂移区508在深沟槽结构504的底部512之下延伸并且横向延伸以形成连续的n型区。垂直取向漂移区508为n型并且电连接至垂直漏极接触区506。此种配置可以有利地减小垂直漏极延伸MOS晶体管510的导通状态电阻。

[0028] 至少一个栅极514和对应的栅极介电层516被布置在垂直取向漂移区508之上。在该示例中,栅极514被布置在深沟槽结构504的介电内衬524中设置,邻近p型主体区518和n型源极区520。一个或多个可选p型主体接触区522可以被布置在邻接主体区518的衬底502中。栅极的其它配置可以在具有图5所示的深沟槽结构504、垂直漏极接触区506以及垂直取

向漂移区508的配置的垂直漏极延伸MOS晶体管510中被使用。

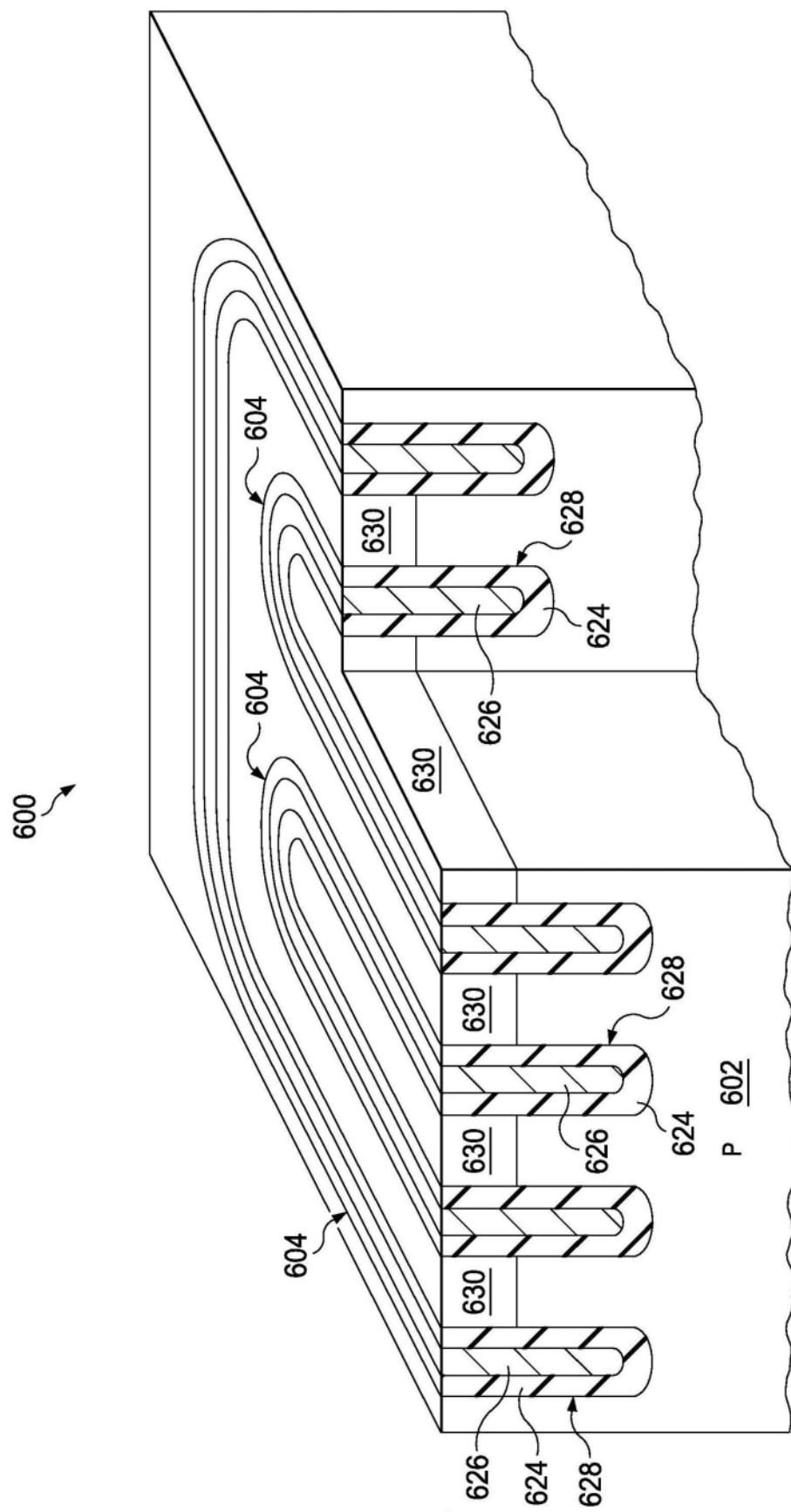

[0029] 图6A至图6E是在连续制造阶段中半导体器件的横截面图。参考图6A, 半导体器件600在p型半导体衬底602中和p型半导体衬底602上形成, 诸如单晶硅晶片。执行漂移区离子植入工艺(将诸如磷的n型掺杂剂植入到为垂直取向漂移区所限定的区域中的衬底602中)以形成漂移植入区630。例如, 漂移区离子植入工艺的剂量可以是 $1 \times 10^{12} \text{ cm}^{-2}$ 至 $1 \times 10^{13} \text{ cm}^{-2}$ 。在本实施例的至少一个版本中, 如图6A所示, 漂移植入区630可以在为垂直漏极接触区限定的区域上方延伸。在可替代版本中, 漂移植入区630可以被限制到在为垂直取向漂移区限定的衬底的区域。

[0030] 参考图6B, 深隔离沟槽628在衬底602中形成, 诸如通过在衬底602的顶部表面上方形成硬掩模材料层而开始的工艺。硬掩模可以通过以下方法形成: 通过光刻法形成蚀刻掩模, 接着使用反应性离子蚀刻(RIE)工艺移除在为深隔离沟槽628限定的区域上方的硬掩模材料。在图案化硬掩模之后, 使用各向异性蚀刻工艺(诸如Bosch深RIE工艺或连续深RIE工艺)将材料从深隔离沟槽628中的衬底602中移除。

[0031] 参考图6C, 介电内衬624在深隔离沟槽628中形成, 使得介电内衬624邻接衬底602。例如, 介电内衬624可以包括热生长的二氧化硅。介电内衬624也可以包括一个或多个介电材料层, 诸如由化学气相沉积(CVD)工艺形成的二氧化硅、氮化硅和/或氮氧化硅。

[0032] 可选导电中心构件626可以在介电内衬624上形成。例如, 导电中心构件626可以包括在580 °C至650 °C的温度下热分解低压反应器内的SiH<sub>4</sub>气体而形成的多晶硅(polycrystalline silicon), 通常被称为多晶硅(polysilicon)。多晶硅可以在形成期间被掺杂以提供期望的导电性。用介电内衬624填充的深隔离沟槽628和导电中心构件626(如果有的话)形成深沟槽结构604。可以诸如通过使用回蚀和/或化学机械抛光(CMP)工艺来移除来自形成介电内衬624的在衬底602的顶部表面上方的不需要的介电材料和来自形成导电中心构件626的在衬底602的顶部表面上方的不需要的导电材料。

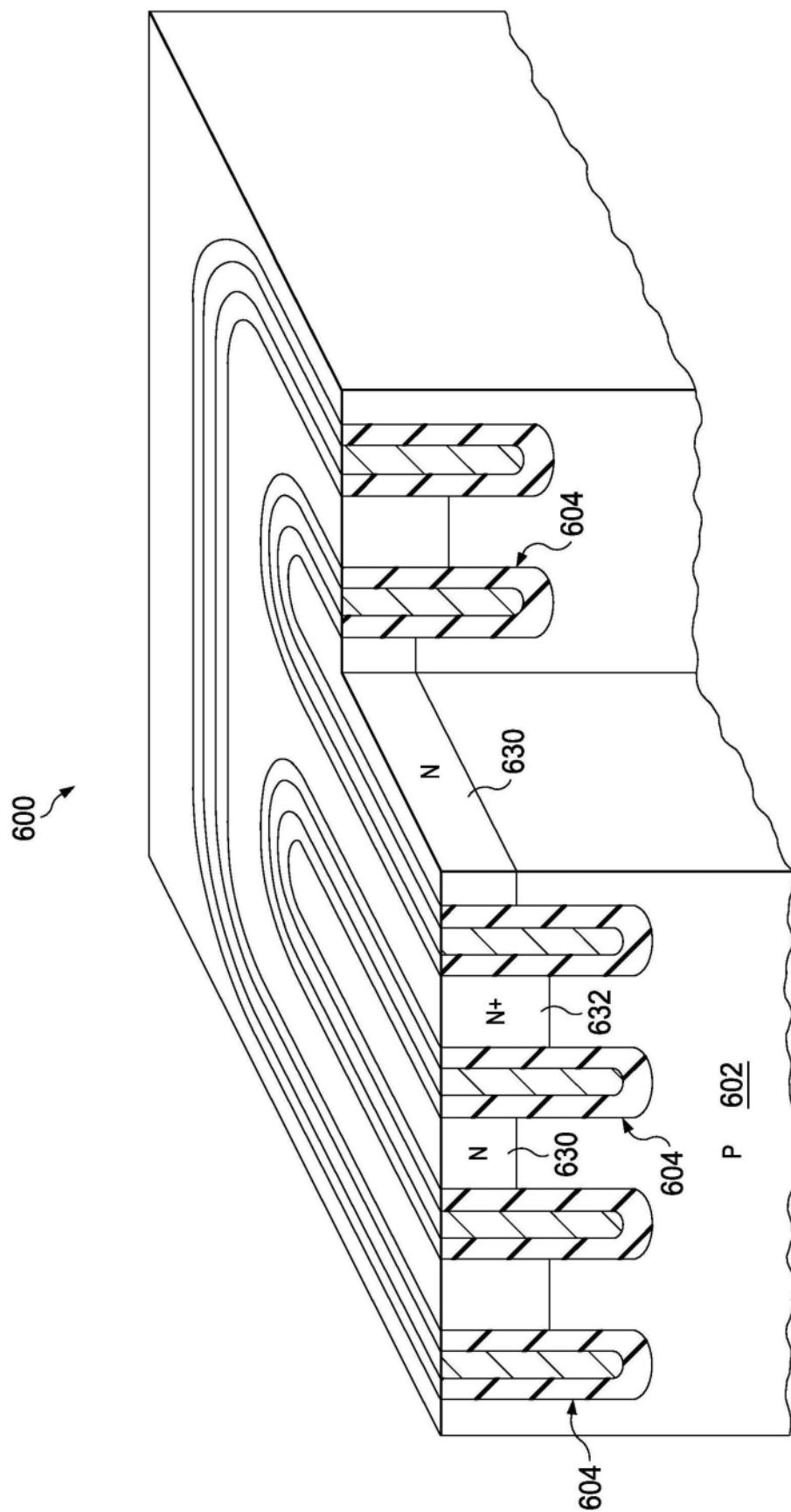

[0033] 参考图6D, 执行漏极接触离子植入工艺(将n型掺杂剂诸如磷植入为垂直漏极接触区限定的区域中的衬底602)以形成漏极接触植入区632。漂移区离子植入工艺的剂量至少是漂移区离子植入剂量的十倍, 并且例如可以是 $1 \times 10^{16} \text{ cm}^{-2}$ 至 $3 \times 10^{16} \text{ cm}^{-2}$ 。漏极接触离子植入工艺可以将掺杂剂提供至导电中心构件626的多晶硅版本, 以获得期望的导电性。

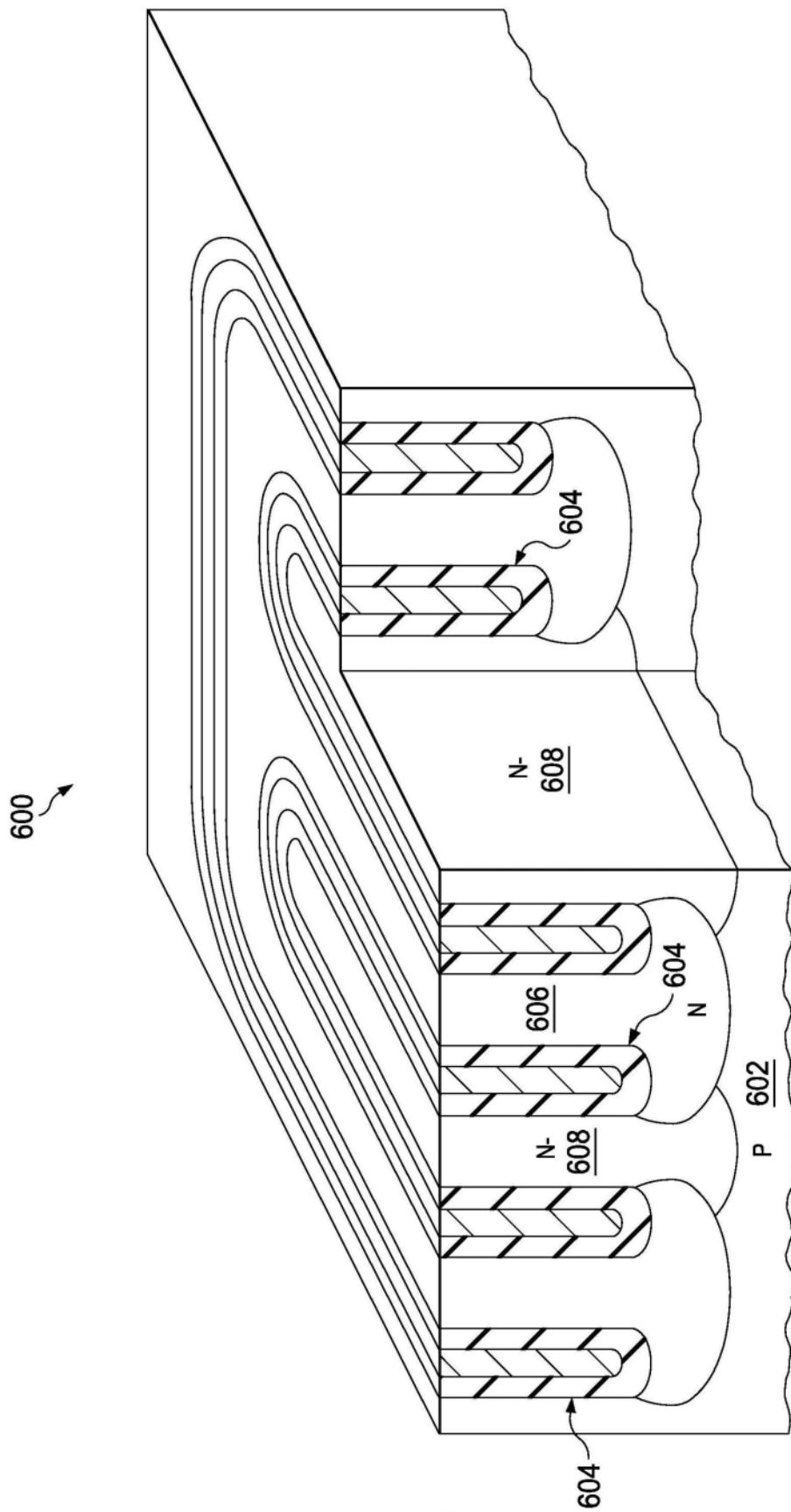

[0034] 参考图6E, 执行热驱动操作, 其加热衬底602以激活并扩散在漂移植入区630和漏极接触植入区632中植入的掺杂剂, 并从而分别形成垂直取向漂移区608和垂直漏极接触区606。热驱动操作的条件取决于深沟槽结构604的深度和在深沟槽结构604的底部处的垂直漏极接触区606的期望的横向范围。例如, 具有2.5微米深的深沟槽结构604的垂直漏极延伸MOS晶体管可以具有热驱动操作, 所述热驱动操作在1100 °C下加热衬底602达3.5小时至4小时, 或在等效的退火条件诸如1125 °C下达2小时, 或1050 °C下达12小时。

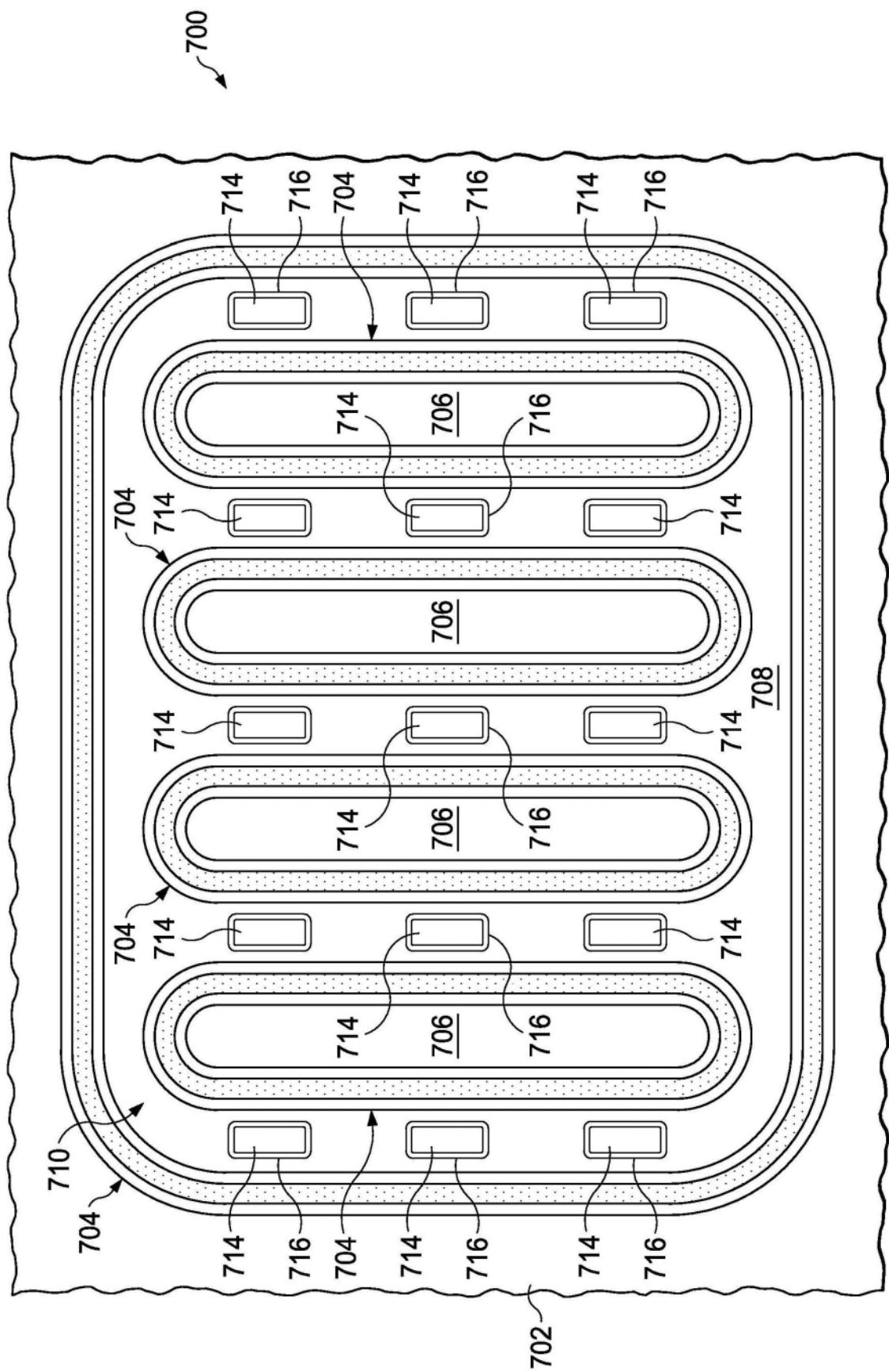

[0035] 图7和图8是具有垂直漏极延伸MOS晶体管的半导体器件的顶视图。图7和图8中所示的栅极如参考图2讨论的被布置在沟槽中, 但栅极的其它配置可以使用在这些示例中。参考图7, 如参考图6A描述的, 半导体器件700在半导体衬底702中和半导体衬底702上形成。具有闭合环路配置的深沟槽结构704被布置在衬底702中。深沟槽结构704的实例横向围绕垂直漏极接触区706。垂直漏极延伸MOS晶体管710的栅极714和栅极介电层716被布置在横向围绕垂直漏极接触区706的深沟槽结构704之间。垂直漂移区708被布置在围绕垂直漏极接

触区706的深沟槽结构704之间。垂直漏极延伸MOS晶体管710的主体区、源极区以及主体接触区未在图7中显示以更清楚地显示垂直漂移区708和垂直漏极接触区706的布置。深沟槽结构704的实例横向围绕垂直漏极延伸MOS晶体管710。电连接至垂直漏极接触区706在衬底702的顶部表面处进行。用深沟槽结构704围绕垂直漏极接触区706可以防止垂直漏极延伸MOS晶体管710的漏极接触和主体区之间的击穿电场，并且可以有利地允许垂直漏极延伸MOS晶体管710在比其它更高的电压下操作。

[0036] 参考图8,如参考图6A描述的,半导体器件800在半导体衬底802中和半导体衬底802上形成。具有线性配置的深沟槽结构804被布置在衬底802中。垂直漏极接触区806被布置在线性深沟槽结构804的相邻对之间。栅极814和栅极介电层816被布置在与垂直漏极接触区806交替的深沟槽结构804的相邻对之间。垂直漂移区808被布置在具有栅极814的深沟槽结构804的可交替对之间。主体区818在线性深沟槽结构804周围被布置并且在垂直漂移区808上方延伸以邻接栅极814;在垂直漂移区808上方延伸的主体区818的部分以及垂直漏极延伸MOS晶体管810的源极区和主体接触区未在图8中显示,以更清楚地显示垂直漂移区808和垂直漏极接触区806的布置。深沟槽结构804的实例横向围绕垂直漏极延伸MOS晶体管810。电连接至垂直漏极接触区806在衬底802的顶部表面处进行。将垂直漏极接触区806布置在线性深沟槽结构804之间可以有利地减小垂直漏极延伸MOS晶体管810所需要的面积,从而减少半导体器件800的制造成本。

[0037] 在权利要求的范围内,在描述的实施例中的修改是可能的,并且其它实施例也是可能的。

图1

图2

图3

图4

图5

图6A

图6B

图6C

图6D

图6E

图7

图8