(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5951808号

(P5951808)

(45) 発行日 平成28年7月13日(2016.7.13)

(24) 登録日 平成28年6月17日(2016.6.17)

(51) Int.Cl.

H04B 1/50 (2006.01)

F 1

H04B 1/50

請求項の数 47 (全 31 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-560053 (P2014-560053)  |

| (86) (22) 出願日 | 平成25年2月28日 (2013.2.28)        |

| (65) 公表番号     | 特表2015-508982 (P2015-508982A) |

| (43) 公表日      | 平成27年3月23日 (2015.3.23)        |

| (86) 國際出願番号   | PCT/US2013/028398             |

| (87) 國際公開番号   | W02013/130866                 |

| (87) 國際公開日    | 平成25年9月6日 (2013.9.6)          |

| 審査請求日         | 平成27年11月4日 (2015.11.4)        |

| (31) 優先権主張番号  | 61/605,285                    |

| (32) 優先日      | 平成24年3月1日 (2012.3.1)          |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 13/765,992                    |

| (32) 優先日      | 平成25年2月13日 (2013.2.13)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人  | 100103034<br>弁理士 野河 信久                                                                                        |

| (74) 代理人  | 100075672<br>弁理士 峰 隆司                                                                                         |

最終頁に続く

(54) 【発明の名称】無線装置のための時分割複信モードでの周波数合成器アーキテクチャー

## (57) 【特許請求の範囲】

## 【請求項 1】

無線通信のための装置であって、受信機のための LO 周波数で第 1 の局部発振器 (LO) 信号を生成するために使用される第 1 の発振器信号を生成するように構成された第 1 の周波数合成器と、送信機のための前記 LO 周波数で第 2 の LO 信号を生成するために使用される第 2 の発振器信号を生成するように構成された第 2 の周波数合成器と、を備え、

ここにおいて、前記第 1 および第 2 の周波数合成器は、前記装置が時分割モードで動作している場合、同じ LO 周波数で前記第 1 および第 2 の LO 信号を得るために前記第 1 および第 2 の発振器信号を生成するように構成され、前記第 1 および第 2 の周波数合成器の少なくとも 1 つは、データ・スロットのミッドアンブル内で有効にされ、前記データ・スロットの他の部分で使用される変調の速度より低い速度が使用される、

装置。

## 【請求項 2】

前記時分割モードにおいて、前記受信機は第 1 の時間間隔の間、有効にされ、前記送信機は第 2 の時間間隔の間、有効にされる、請求項 1 に記載の装置。

## 【請求項 3】

前記時分割モードは、時分割複信 (TDD) モードおよび時間分割同期コード分割多元接続 (TD-SCDMA) モードのいずれかである、請求項 1 に記載の装置。

**【請求項 4】**

前記 T D D モードは、ロング・ターム・エボリューション（ L T E ） T D D モードである、請求項 3 に記載の装置。

**【請求項 5】**

前記第 1 および第 2 の周波数合成器は、同じ発振器周波数で前記第 1 および第 2 の発振器信号を生成するように構成された、請求項 1 に記載の装置。

**【請求項 6】**

前記第 1 の周波数合成器は、第 1 の発振器周波数で前記第 1 の発振器信号を生成するように構成され、前記第 2 の周波数合成器は、前記第 1 の発振器周波数とは異なる第 2 の発振器周波数で前記第 2 の発振器信号を生成するように構成された、請求項 1 に記載の装置

10

。

**【請求項 7】**

前記第 1 の発振器周波数は前記 L O 周波数の整数倍で、前記第 2 の発振器周波数は前記 L O 周波数の非整数倍である、請求項 6 に記載の装置。

**【請求項 8】**

前記第 1 の発振器周波数は前記 L O 周波数の非整数倍で、前記第 2 の発振器周波数は前記 L O 周波数の整数倍である、請求項 6 に記載の装置。

**【請求項 9】**

前記第 1 の周波数合成器は、前記受信機が有効にされる前に有効にされ、前記受信機が無効にされる時または後に無効にされ、前記第 2 の周波数合成器は、前記送信機が有効にされる前に有効にされ、前記送信機が無効にされる時または後に無効にされる、請求項 1 に記載の装置。

20

**【請求項 10】**

前記第 1 および第 2 の周波数合成器は、前記受信機が有効にされる前に有効にされ、前記第 1 の周波数合成器は、前記受信機が無効にされる時または後に無効にされ、前記第 2 の周波数合成器は、前記送信機が無効にされる時または後に無効にされる、請求項 1 に記載の装置。

**【請求項 11】**

前記第 1 および第 2 の周波数合成器は、前記送信機が有効にされる前に有効にされる、

30

請求項 1 に記載の装置。

**【請求項 12】**

前記第 1 および第 2 の周波数合成器は、前記受信機が有効にされる前に、有効にされ、前記受信機が無効にされる時または後に無効にされる、請求項 1 に記載の装置。

**【請求項 13】**

前記第 1 および第 2 の周波数合成器は、前記送信機が有効にされる前に、有効にされ、前記第 1 および第 2 の周波数合成器は、前記送信機が無効にされる時または後に無効にされる、請求項 1 に記載の装置。

**【請求項 14】**

前記第 1 の周波数合成器は、前記受信機が有効にされる場合、ターゲット発信器周波数で前記第 1 の発振器信号を、および前記送信機が有効にされる場合、前記ターゲット発信器周波数からずれたものを生成するように構成された、請求項 1 に記載の装置。

40

**【請求項 15】**

前記第 1 の周波数合成器は、位相同期ループ（ P L L ）を備え、前記ターゲット発信器周波数からの前記ずれは前記 P L L 内の周波数分周器比を変更することによって得られる、請求項 1 4 に記載の装置。

**【請求項 16】**

前記第 2 の周波数合成器は、前記送信機が有効にされる場合、ターゲット発信器周波数で前記第 2 の発振器信号を、および前記受信機が有効にされる場合、前記ターゲット発信器周波数からのずれたものを生成するように構成された、請求項 1 に記載の装置。

**【請求項 17】**

10

20

30

40

50

局部発振器（L.O.）信号を生成するための方法であって、

第1の周波数合成器により第1の発振器周波数で第1の発振器信号を生成することと、

前記第1の発振器信号に基づき受信機のためにL.O.周波数で第1のL.O.信号を生成することと、

第2の周波数合成器により第2の発振器周波数で第2の発振器信号を生成し、ここにおいて、前記第2の発振器信号の周波数は、時分割モードで動作している場合に前記第1の発振器周波数とは異なることと、

前記第2の発振器信号に基づき送信機のために前記L.O.周波数で第2のL.O.信号を生成することと、

データ・スロットのミッドアンブル内で前記第1および第2の周波数合成器の少なくとも1つを有効にすることと、

前記データ・スロットの他の部分で使用される変調の速度より低い速度を使用することと、

を備える方法。

#### 【請求項18】

前記時分割モードは、時分割複信（TDD）モードおよび時間分割同期コード分割多元接続（TDS-SCDMA）モードのいずれかである、請求項17に記載の方法。

#### 【請求項19】

前記TDDモードは、ロング・ターム・エボリューション（LTE）TDDモードである、請求項18に記載の方法。

#### 【請求項20】

前記TDDモードの第1の時間間隔の間、前記受信機を有効にすることと、

前記TDDモードの第2の時間間隔の間、前記送信機を有効にすることと、

をさらに備える請求項18に記載の方法。

#### 【請求項21】

前記第1の発振器周波数は前記L.O.周波数の整数倍で、前記第2の発振器周波数は前記L.O.周波数の非整数倍である、請求項17に記載の方法。

#### 【請求項22】

前記第1の発振器周波数は前記L.O.周波数の非整数倍で、前記第2の発振器周波数は前記L.O.周波数の整数倍である、請求項17に記載の方法。

#### 【請求項23】

前記受信機が有効にされる前に前記第1の周波数合成器を有効にすることと、

前記受信機が無効にされる時または後に前記第1の周波数合成器を無効にすることと、

前記送信機が有効にされる前に前記第2の周波数合成器を有効にすることと、

前記送信機が無効にされる時または後に前記第2の周波数合成器を無効にすることと、

をさらに備える請求項17に記載の方法。

#### 【請求項24】

前記受信機が有効にされる前に前記第1および第2の周波数合成器を有効にすることと、

前記受信機が無効にされる時または後に前記第1の周波数合成器を無効にすることと、

前記送信機が無効にされる時または後に前記第2の周波数合成器を無効にすることと、

をさらに備える請求項17に記載の方法。

#### 【請求項25】

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にすることと、

をさらに備える請求項17に記載の方法。

#### 【請求項26】

前記受信機が有効にされる前に前記第1および第2の周波数合成器を有効にすることと、

前記受信機が無効にされる時または後に前記第1および第2の周波数合成器を無効にすることと、

10

20

30

40

50

をさらに備える請求項 17 に記載の方法。

**【請求項 27】**

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にすることと、

前記送信機が無効にされる時または後に前記第1および第2の周波数合成器を無効にすることと、

をさらに備える請求項 17 に記載の方法。

**【請求項 28】**

前記第1の発振器信号の生成は、

前記受信機が有効にされる場合、ターゲット発信器周波数で前記第1の発振器信号を生成することと、10

前記送信機が有効にされる場合、前記ターゲット発信器周波数からずれたところで前記第1の発振器信号を生成することと、

を備える請求項 17 に記載の方法。

**【請求項 29】**

無線通信のための装置であって、

第1の発振器周波数で第1の発振器信号を生成するための手段と、

前記第1の発振器信号に基づき受信機のために LO 周波数で第1の局部発振器 (LO) 信号を生成するための手段と、

時分割モードで動作している場合に前記第1の発振器周波数とは異なる第2の発振器周波数で第2の発振器信号を生成するための手段と、20

前記第2の発振器信号に基づき送信機のために前記 LO 周波数で第2の LO 信号を生成するための手段と、

データ・スロットのミッドアンブル内で前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段の少なくとも1つを有効にするための手段と、

前記データ・スロットの他の部分で使用される変調の速度より低い速度を使用するための手段と、

を備える装置。

**【請求項 30】**

前記時分割モードは、時分割複信 (TDD) モードおよび時間分割同期コード分割多元接続 (TD-SCDMA) モードのいずれかである、請求項 29 に記載の装置。30

**【請求項 31】**

前記 TDD モードは、ロング・ターム・エボリューション (LTE) TDD モードである、請求項 30 に記載の装置。

**【請求項 32】**

前記 TDD モードの第1の時間間隔の間、前記受信機を有効にするための手段と、

前記 TDD モードの第2の時間間隔の間、前記送信機を有効にするための手段と、

をさらに備える請求項 30 に記載の装置。

**【請求項 33】**

前記第1の発振器周波数は前記 LO 周波数の整数倍で、前記第2の発振器周波数は前記 LO 周波数の非整数倍である、請求項 29 に記載の装置。40

**【請求項 34】**

前記第1の発振器周波数は前記 LO 周波数の非整数倍で、前記第2の発振器周波数は前記 LO 周波数の整数倍である、請求項 29 に記載の装置。

**【請求項 35】**

前記受信機が有効にされる前に前記第1の発振器信号を生成するための前記手段を有効にするための手段と、

前記受信機が無効にされる時または後に前記第1の発振器信号を生成するための前記手段を無効にするための手段と、50

前記送信機が有効にされる前に前記第2の発振器信号を生成するための前記手段を有効にするための手段と、

前記送信機が無効にされる時または後に前記第2の発振器信号を生成するための前記手段を無効にするための手段と、

をさらに備える請求項29に記載の装置。

【請求項36】

前記受信機が有効にされる前に前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段を有効にするための手段と、

前記受信機が無効にされる時または後に前記第1の発振器信号を生成するための前記手段を無効にするための手段と、

前記送信機が無効にされる時または後に前記第2の発振器信号を生成するための前記手段を無効にするための手段と、

をさらに備える請求項29に記載の装置。

【請求項37】

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にするための手段をさらに備える請求項29に記載の装置。

【請求項38】

前記受信機が有効にされる前に前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段を有効にするための手段と、

前記受信機が無効にされる時または後に前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段を無効にするための手段と、

をさらに備える請求項29に記載の装置。

【請求項39】

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にするための手段と、

前記送信機が無効にされる時または後に前記第1および第2の周波数合成器を無効にするための手段と、

をさらに備える請求項29に記載の装置。

【請求項40】

前記第1の発振器信号を生成するための前記手段は、

前記受信機が有効にされる場合、ターゲット発信器周波数で前記第1の発振器信号を生成するための手段と、

前記送信機が有効にされる場合、前記ターゲット発信器周波数からずれたところで前記第1の発振器信号を生成するための手段と、

を備える請求項29に記載の装置。

【請求項41】

コンピュータ読み取可能な記録媒体であって、

少なくとも1つのプロセッサーに第1の周波数合成器により第1の発振器周波数で第1の発振器信号の生成を誘導させるためのコードで、前記第1の発振器信号は受信機のためのLO周波数で第1の局部発振器(LO)信号を生成するために使用されるコードと、

前記少なくとも1つのプロセッサーに第2の周波数合成器により第2の発振器周波数で第2の発振器信号の生成を誘導させるためのコードで、前記第2の発振器信号は送信機のための前記LO周波数で第2のLO信号を生成するために使用され、ここにおいて、前記第2の発振器信号の周波数は、時分割モードで動作している場合、前記第1の発振器周波数とは異なるコードと、

少なくとも1つのプロセッサーにデータ・スロットのミッドアンプル内で前記第1および第2の周波数合成器の少なくとも1つを有効にさせるためのコードと、

少なくとも1つのプロセッサーに前記データ・スロットの他の部分で使用される変調の速度より低い速度を使用させるためのコードと、

を備えるコンピュータ読み取可能な記録媒体。

10

20

30

40

50

**【請求項 4 2】**

前記時分割モードは、時分割複信（TDD）モードおよび時間分割同期コード分割多元接続（TDS-CDMA）モードのいずれかである、請求項41に記載のコンピュータ読取可能な記録媒体。

**【請求項 4 3】**

前記TDDモードの第1の時間間隔の間、少なくとも1つのプロセッサーに前記受信機を有効にさせるためのコードと、

前記TDDモードの第2の時間間隔の間、少なくとも1つのプロセッサーに前記送信機を有効にさせるためのコードと、

をさらに備える請求項42に記載のコンピュータ読取可能な記録媒体。

10

**【請求項 4 4】**

前記TDDモードは、ロング・ターム・エボリューション（LTE）TDDモードである、請求項42に記載のコンピュータ読取可能な記録媒体。

**【請求項 4 5】**

前記受信機が有効にされる前に、少なくとも1つのプロセッサーに前記第1の周波数合成器を有効にさせるためのコードと、

前記受信機が無効にされる時または後に、少なくとも1つのプロセッサーに前記第1の周波数合成器を無効にさせるためのコードと、

前記送信機が有効にされる前に、少なくとも1つのプロセッサーに前記第2の周波数合成器を有効にさせるためのコードと、

20

前記送信機が無効にされる時または後に、少なくとも1つのプロセッサーに前記第2の周波数合成器を無効にさせるためのコードと、

をさらに備える請求項41に記載のコンピュータ読取可能な記録媒体。

**【請求項 4 6】**

前記送信機が有効にされる前に、少なくとも1つのプロセッサーに前記第1および第2の周波数合成器を有効にさせるためのコードをさらに備える請求項41に記載のコンピュータ読取可能な記録媒体。

**【請求項 4 7】**

前記送信機が有効にされる前に、少なくとも1つのプロセッサーに前記第1および第2の周波数合成器を有効にさせるためのコードと、

30

前記送信機が無効にされる時または後に、少なくとも1つのプロセッサーに前記第1および第2の周波数合成器を無効にさせるためのコードと、

をさらに備える請求項41に記載のコンピュータ読取可能な記録媒体。

**【発明の詳細な説明】****【技術分野】****【0001】****関連出願**

[0001]本出願は、「無線装置のための周波数合成器アーキテクチャー（FREQUENCY SYNTHESIZER ARCHITECTURE FOR A WIRELESS DEVICE）」に関し、2012年3月1日に出願された米国仮特許出願第61/605,285号に関連しており、優先権を主張するものである。

40

**【背景技術】****【0002】**

[0002]本開示は、一般にエレクトロニクス、より詳細には、無線装置のための周波数合成器アーキテクチャーに関する。

**【0003】**

[0003]無線装置（例えば、携帯電話またはスマートフォン）は、無線通信システムで双方通信のためのデータを送受信することができる。無線装置には、データ送信のための送信機およびデータ受信のための受信機を含めることができる。データ送信の場合、送信機は変調された無線周波数（RF）信号を得るために、データで送信用局部発振器（LO）

50

) 信号を変調し、適切な出力電力レベルを有する出力 R F 信号を得るために、変調された R F 信号を増幅し、アンテナを介して基地局に出力 R F 信号を送信することができる。データ受信の場合、受信機はアンテナを介して受信された R F 信号を取得し、受信用 L O 信号で受信された R F 信号を増幅およびダウンコンバートし、基地局から送信されたデータを受信するために、ダウンコンバートされた信号を処理する。

#### 【 0 0 0 4 】

[0004] 無線装置には、受信機のための受信用 L O 信号および送信機のための送信用 L O 信号を生成するための周波数合成器を含むことができる。周波数合成器は受信機および送信機の性能に大きな影響を有する場合がある。

#### 【 発明の概要 】

10

#### 【 0 0 0 5 】

[0005] 時分割複信 ( T D D ) モードで動作する無線装置の複式周波数合成器アーキテクチャーが本明細書で開示されている。複式周波数合成器アーキテクチャーはさらに、周波数分割複信 ( F D D ) モードにも使用される場合がある。T D D の場合、ダウンリンクとアップリンクが同じ周波数を共有し、2つの周波数合成器が、受信機と送信機のために同じ周波数で2つの L O 信号を生成するために使用されうる。F D D の場合、ダウンリンクとアップリンクで異なる周波数が割り当てられ、2つの周波数合成器が、受信機と送信機のために異なる周波数で2つの L O 信号を生成するために使用されうる。

#### 【 0 0 0 6 】

20

[0006] 例示的設計では、無線装置には、第1および第2の周波数合成器が含まれる。第1の周波数合成器は、受信機のために L O 周波数で第1の / 受信用 L O 信号を生成するために使用される、第1の発振器信号を生成する。第2の周波数合成器は、送信機のために L O 周波数で第2の / 送信用 L O 信号を生成するために使用される、第2の発振器信号を生成する。例えば、各発振器信号は、分周器によって周波数で分割され、対応する L O 信号を得るためにバッファされうる。第1および第2の周波数合成器は、無線装置が T D D モードで動作する場合、同じ L O 周波数で受信用および送信用 L O 信号を得るために発振器信号を生成する。第1および第2の周波数合成器は、無線装置が F D D モードで動作する場合、異なる L O 周波数で受信用および送信用信号 L O を得るために発振器信号を生成する。

#### 【 0 0 0 7 】

30

[0007] 一設計では、第1および第2の周波数合成器は、T D D モードで同じ発振器周波数の第1および第2の発振器信号を生成し、同じ周波数分周器比が、同じ L O 周波数の受信用および送信用 L O 信号を得るために、第1および第2の発振器信号で使用することができる。別の設計では、第1および第2の周波数合成器は、T D D モードで異なる発振器周波数の第1および第2の発振器信号を生成し、異なる周波数分周器比が、同じ L O 周波数の受信用および送信用 L O 信号を得るために、第1および第2の発振器信号で使用することができる。

#### 【 0 0 0 8 】

40

[0008] 一設計では、第1および第2の周波数合成器は、常時、ターゲット発信器周波数で動作することができる。別の設計では、各周波数合成器は、( i ) 関連受信機または送信機が有効な場合には、ターゲット発信器周波数で動作でき、( i i ) 他の周波数合成器への妨害を減らすために、関連受信機または送信機が無効の場合には、ターゲット発信器周波数から離れて動作することができる。第1および第2の周波数合成器は、以下で記述するように、種々のやり方で有効および無効にされうる。

#### 【 0 0 0 9 】

[0009] T D D モードで受信機および送信機のための別々の周波数合成器を使用すると、以下で記述するように、より少ないおよび / またはより小さいバッファ、低電力消費、複雑な信号ルーティングの緩和、向上する性能などの種々の利点を提供することができる。

#### 【 0 0 1 0 】

[0010] 本開示の種々の態様および特徴は、以下で、より詳細に記述される。

50

## 【図面の簡単な説明】

## 【0011】

【図1】[0011] 図1は、異なる無線通信システムで通信可能な無線装置を示す。

【図2】[0012] 図2は、図1の無線装置のブロック図を示す。

【図3】[0013] 図3は、1つの周波数合成器を備える送受信装置のブロック図を示す。

【図4】[0014] 図4は、2つの周波数合成器を備える送受信装置のブロック図を示す。

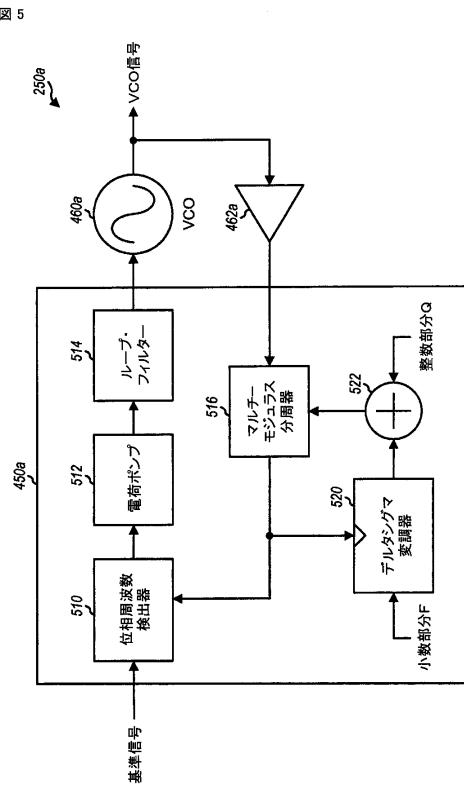

【図5】[0015] 図5は、周波数合成器のブロック図を示す。

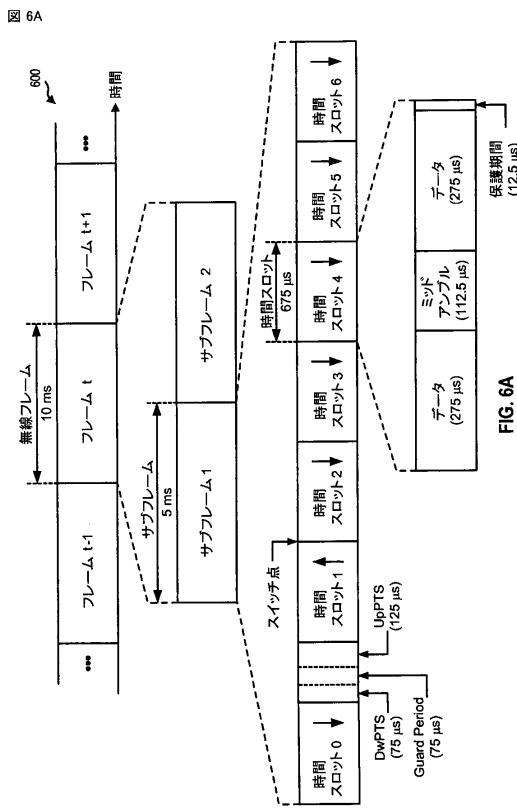

【図6A】[0016] 図6Aは、2つの無線システムのフレーム構造を示す。

【図6B】図6Bは、2つの無線システムのフレーム構造を示す。

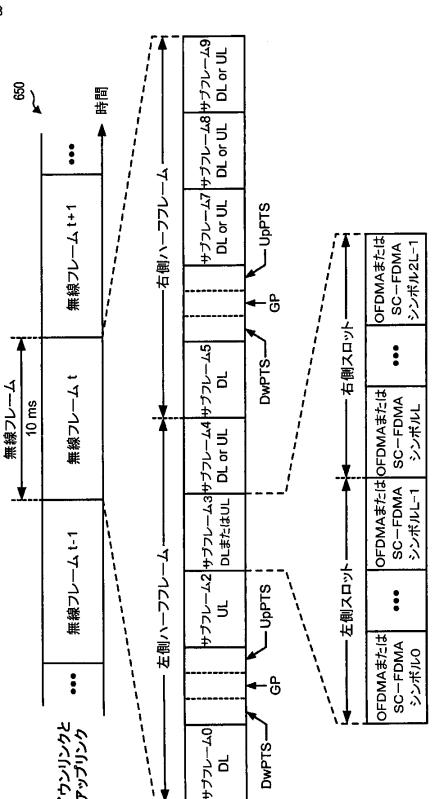

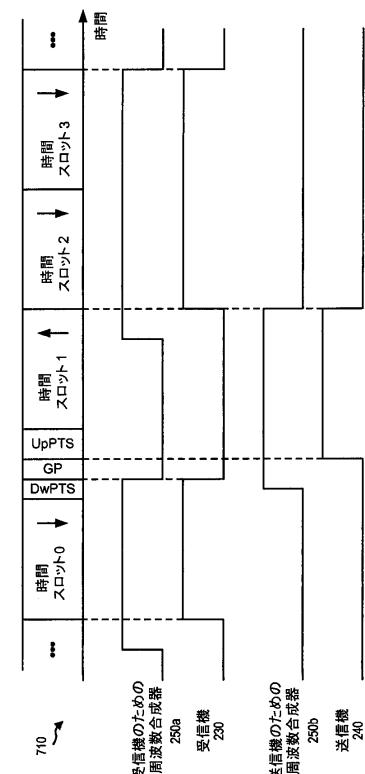

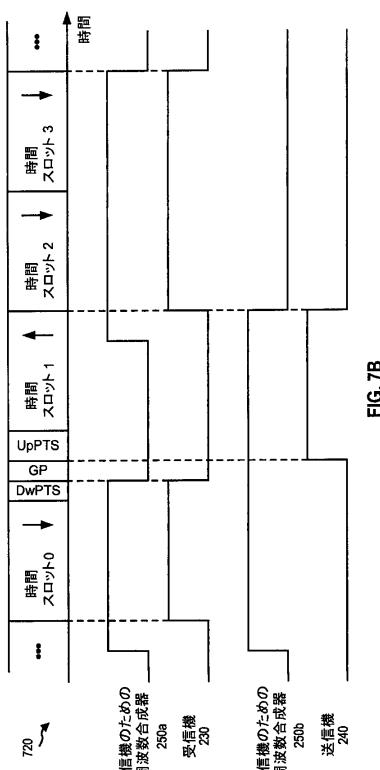

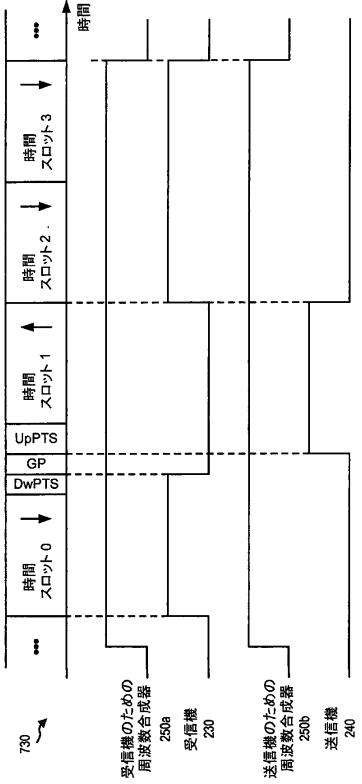

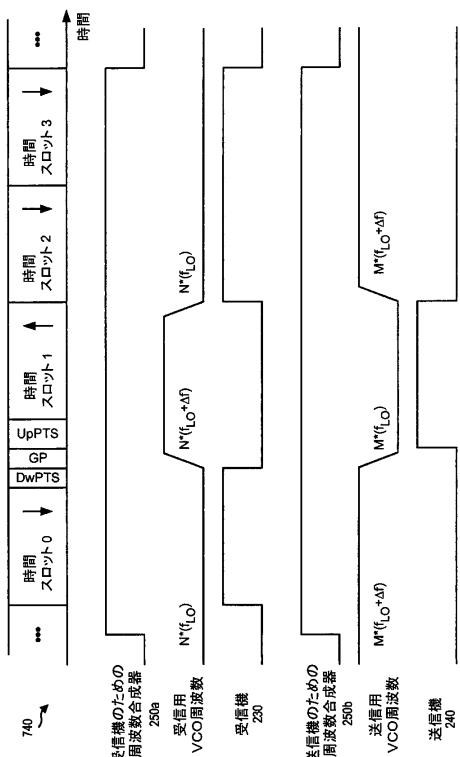

【図7A】[0017] 図7Aは、2つの周波数合成器の4つのパワーオン・シーケンスを示す。

10

【図7B】図7Bは、2つの周波数合成器の4つのパワーオン・シーケンスを示す。

【図7C】図7Cは、2つの周波数合成器の4つのパワーオン・シーケンスを示す。

【図7D】図7Dは、2つの周波数合成器の4つのパワーオン・シーケンスを示す。

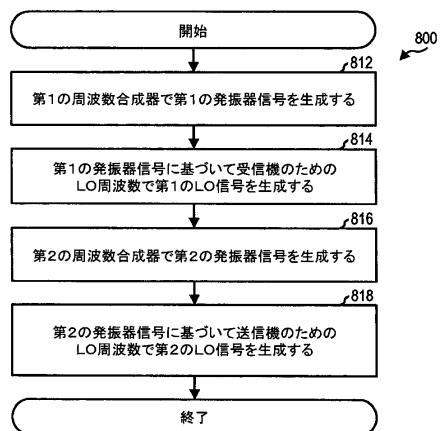

【図8】[0018] 図8は、LO信号を生成するためのプロセスを示す。

## 【発明を実施するための形態】

## 【0012】

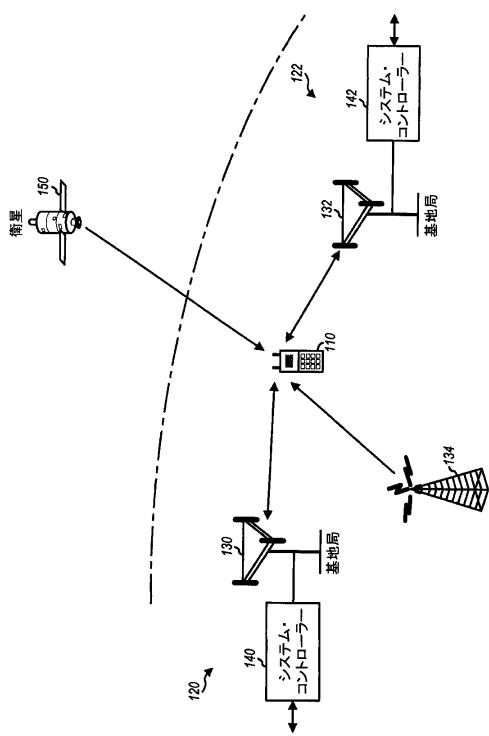

[0019] 図1は、異なる無線通信システム120および122で通信可能な無線装置110を示す。無線システム120および122は、それぞれ符号分割多元接続(CDMA)システム、グローバル・システム・フォン・モバイル・コミュニケーションズ(GSM(登録商標))システム、ロング・ターム・エボリューション(LTE)システム、無線ローカル・エリア・ネットワーク(WLAN)システム、または他の無線システムとすることができます。例えば、無線システム120および122はLTEシステムとすることができます、LTE周波数分割複信(FDD)またはLTE時分割複信(TDD)を含めることができます。例として、システムはLTE TDDシステムとすることができます。CDMAシステムでは、時間分割同期コード分割多元接続(Time Division Synchronous Code Division Multiple Access)(TDS-SCDMA)、広帯域符号分割多元接続(WCDMA(登録商標))、CDMA2000、またはCDMAの他の何らかのバージョンを実装することができます。TD-SCDMAは、ユニバーサル地上波無線接続(Universal Terrestrial Radio Access)(UTRA)時分割複信(TDD)1.28Mcpsオプションまたは低チップ・レート(Low Chip Rate)(LCR)とも呼ばれる。簡単にするために、図1は、1つの基地局130および1つのシステム・コントローラー140を含む無線システム120、ならびに1つの基地局132および1つのシステム・コントローラー142を含む無線システム122を示している。一般に、各無線システムには、任意の数の基地局と任意の組のネットワーク・エンティティを含めることができます。

## 【0013】

[0020] 無線装置110は、ユーザー機器(UE)、モバイル・ステーション、端末、アクセス端末、加入者ユニット、ステーションなどとも呼ばれる場合がある。無線装置110は、携帯電話、スマートフォン、タブレット、無線モデム、携帯情報端末(PDA)、携帯端末、ラップトップ・コンピュータ、スマートブック、ネットブック、コードレス・フォン、無線ローカル・ループ(WLL)ステーション、ブルートゥース装置などとすることができます。無線装置110は、無線システム120および/または122との通信が可能である。無線装置110はさらに、放送局(例えば、放送局134)からの信号を受信することも可能である。無線装置110はさらに、1または複数の全地球的航法衛星システム(GNSS)の衛星(例えば、衛星150)からの信号も受信することが可能である。無線装置110は、LTE、TD-SCDMA、WCDMA、CDMA2000、GSM、802.11などの無線通信のための1または複数の無線技術をサポートすることができます。

## 【0014】

[0021]無線装置110は、ダウンリンクおよびアップリンクを介して無線システム120で、基地局130、132と通信することができる。ダウンリンク（または送信リンク）は基地局から無線装置への通信リンクで、アップリンク（または逆方向リンク）は無線装置から基地局への通信リンクを意味している。

## 【0015】

[0022]無線システムでは、TDDまたはFDDを利用することができる。TDDの場合、ダウンリンクとアップリンクは同じ周波数を共有し、ダウンリンク送信とアップリンク送信は異なる時間期間の同じ周波数で送信されうる。FDDの場合、ダウンリンクとアップリンクは別々の周波数が割り当てられる。ダウンリンク送信は1つの周波数で送信されうるもので、アップリンク送信は別の周波数で送信されうる。TDDをサポートする無線技術の一部の例は、LTE、TDD、TD-SCDMA、GSMなどを含む。FDDをサポートする無線技術の一部の例は、LTE、FDD、WCDMA、CDMA2000などを含む。10

## 【0016】

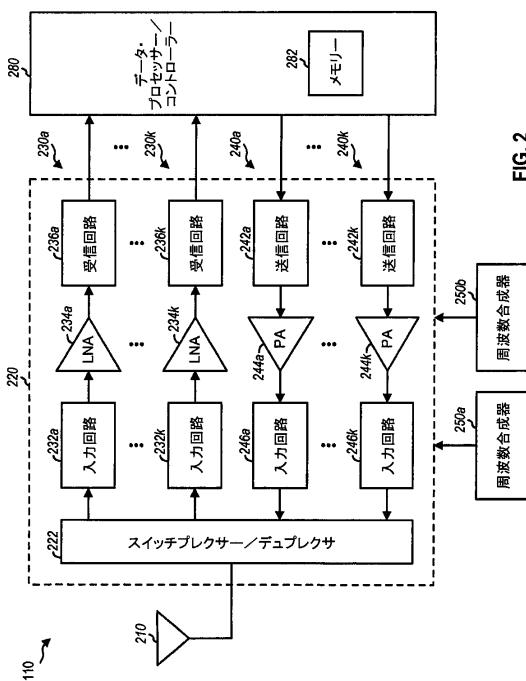

[0023]図2は、図1の無線装置110の例示的設計のブロック図を示す。この例示的設計では、無線装置110は、アンテナ210と結合された送受信装置220、周波数合成器250aおよび250b、およびデータ・プロセッサー／コントローラー280を含む。送受信装置220は、多数の周波数帯、多数の無線技術などをサポートするために、多数の（K）受信機230aから230kおよび多数の（K）送信機240aから240kを含む。20

## 【0017】

[0024]図2に示された例示的設計では、各受信機230は、入力回路232、低雑音増幅器（LNA）234、および受信回路236を含む。データ受信の場合、アンテナ210では基地局および／または例えば送信局からの信号を受信し、受信されたRF信号を提供する、そして、それはスイッチプレクサ／デュプレクサ（duplexer）222を通して配線され、選択された受信機に提供される。以下の説明では、受信機230aが選択された受信機であることを想定している。受信機230a内で、受信されたRF信号は入力回路232aを通過して、LNA234aに提供される。入力回路232aには、受信フィルター、インピーダンス・マッチング回路などを含めることができる。LNA234aは入力回路232aからの受信されたRF信号を増幅し、増幅されたRF信号を提供する。受信回路236aは、RFからベースバンドに増幅されたRF信号を増幅、フィルター処理、およびダウンコンバートし、アナログ入力信号をプロセッサー280に提供する。受信回路236aは、増幅器、フィルター、ミキサー、インピーダンス・マッチング回路を含みうる。送受信装置220の残りの各受信機230も受信機230aと同様の仕方で動作しうる。30

## 【0018】

[0025]図2に示された例示的設計では、各送信機240は、送信回路242a～k、電力増幅器（PA）244a～k、および出力回路246a～kを含む。データ送信の場合、データ・プロセッサー280は送信されるデータを処理（例えば、符号化および変調）し、選択された送信機にアナログ出力信号を提供する。以下の説明では、送信機240aが選択された送信機であることを想定している。送信機240a内で、送信回路242aは、ベースバンドからRFにアナログ出力信号を増幅、フィルター処理、およびアップコンバートし、変調されたRF信号を提供する。送信回路242aには、増幅器、フィルター、ミキサー、インピーダンス・マッチング回路などを含めることができる。電力増幅器244aは変調されたRF信号を受信して増幅し、適切な出力電力レベルを有する増幅された信号を提供する。増幅された信号は出力回路246aを通過し、スイッチプレクサ／送受信切換器222を通して配線され、アンテナ210を介して送信される。出力回路246aには、送信フィルター、インピーダンス・マッチング回路、方向性結合器、デュプレクサなどを含めることができる。40

## 【0019】

[0026]周波数合成器 250a および 250b は、受信機 230 と送信機 240 のための LO 信号を生成する。各周波数合成器 250 には、電圧制御発振器 (VCO)、位相同期ループ (PLL)、バッファなどを含めることができる。

## 【0020】

[0027]図 2 は、受信機 230 と送信機 240 の例示的設計を示している。受信機と送信機にはさらに、フィルター、インピーダンス・マッチング回路などの、図 2 に示されていない他の回路も含めることができる。送受信装置 220 の全部または一部は、1 または複数のアナログ集積回路 (IC)、RF IC (RFIC)、ミックスドシグナル IC (mixed signal IC) などに実装されうる。例えば、LNA 234、受信回路 236a ~ k、および送信回路 242 は、RFIC などとすることができます、1 つの回路モジュールに実装されうる。スイッチプレクサ / デュプレクサ 222、入力回路 232a ~ k、出力回路 246a ~ k、および電力増幅器 244a ~ k は、ハイブリッド・モジュールとすることができます、別の回路モジュールに実装されうる。受信機 230 と送信機 240 の回路も他の仕方で実装されうる。

10

## 【0021】

[0028]データ・プロセッサー / コントローラー 280 は、無線装置 110 のために種々の機能を行うことができる。例えば、データ・プロセッサー 280 は受信機 230 を介して受信されたデータおよび送信機 240 を介して送信されたデータの処理を行うことができる。コントローラー 280 は、スイッチプレクサ / デュプレクサ 222、入力回路 232、LNA 234、受信回路 236、送信回路 242、電力増幅器 244、出力回路 246、周波数合成器 250、またはこれらの組み合わせの動作を制御することができます。メモリー 282 は、データ・プロセッサー / コントローラー 280 のプログラム・コードとデータを保存することができます。データ・プロセッサー / コントローラー 280 は、1 または複数の特定用途向け集積回路 (ASIC) および / または他の IC に実装されうる。

20

## 【0022】

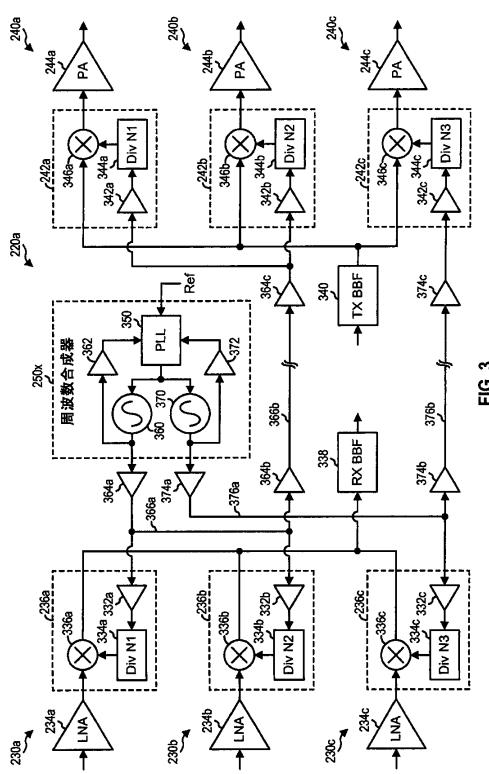

[0029]図 3 は、単一の周波数合成器 250x により TDD をサポートする、送受信装置 220a のブロック図を示す。送受信装置 220a は、図 2 の送受信装置 220 の一例示的設計である。送受信装置 220a には、(i) 低帯域のための受信機 230a と送信機 240a、(ii) 中帯域のための受信機 230b と送信機 240b、(iii) 高帯域のための受信機 230c と送信機 240c が含まれる。各帯域では、周波数の特定の範囲を網羅している。

30

## 【0023】

[0030]各受信機 230 は、受信回路 236 に結合された LNA 234 を含む。受信回路 236 は、バッファ 332、周波数分周器 334、およびダウンコンバーター 336 を含む。低帯域の場合、バッファ 332a は低帯域の VCO 信号を受信しバッファして、バッファされた VCO 信号を提供する。分周器 334a は、バッファされた VCO 信号の周波数を N 分周して、低帯域のための受信用 LO 信号を提供し、ここで、N は任意の値とすることができます（例えば、整数または小数値）。N の値は、各受信回路 236 に対して異なるものとすることができます。例えば、分周器 334a は N1 分周されうるもので、分周器 334b は N2 分周されうるもので、分周器 334c は N3 分周されうる。ダウンコンバーター 336 は、分周器 334a からの受信用 LO 信号で LNA 234a からの入力 RF 信号をダウンコンバートし、ダウンコンバートされた信号を提供する。受信ベースバンド・フィルター (RX BBF) 338 はダウンコンバートされた信号をフィルター処理して、アナログ入力信号を提供する。一部の構成では、受信ベースバンド・フィルター 338 は、ローパス・フィルター (LPF) を含む。中帯域および高帯域のための受信回路 236b および 236c は、低帯域のための受信回路 236a と同様の仕方で動作する。ベースバンド・フィルター 338 は、受信回路 236a、236b、および 236c の出力と結合され、これらの受信回路 230 によって共有される。

40

## 【0024】

50

[0031]各送信機 240 は、電力増幅器 244 に結合された送信回路 242 を含む。送信回路 242 は、バッファ 342、周波数分周器 344、およびアップコンバーター 346 を含む。送信ベースバンド・フィルター (TX\_BBF) 340 は、送信回路 242a、242b、および 242c の入力に結合され、これらの送信回路により共有されている。一部の構成では、送信ベースバンド・フィルター 340 には、ローパス・フィルター (LPF) が含まれる。ベースバンド・フィルター 340 はアナログ出力信号を受信しフィルター処理する。低帯域の場合、バッファ 342a は低帯域の VCO 信号を受信しバッファして、バッファされた VCO 信号を提供する。分周器 344a は、バッファされた VCO 信号の周波数を N 分周し、低帯域の送信用 LO 信号を提供する。N の値は、各送信回路 242 に対して異なるものとすることができます。例えば、分周器 344a は N1 分周されるもので、分周器 344b は N2 分周されるもので、分周器 344c は N3 分周される。アップコンバーター 346a は、分周器 344a からの送信用 LO 信号でベースバンド・フィルター 340 からのフィルター処理された信号をアップコンバートし、変調された RF 信号を提供する。電力増幅器 244a は変調された RF 信号を増幅し、低帯域のための増幅された RF 信号を提供する。中帯域および高帯域のための送信回路 242b および 242c は、低帯域のための送信回路 242a と同様の仕方で動作する。

10

#### 【0025】

[0032]図 3 に示された例示的設計では、単一の周波数合成器 250x が受信機 230 と送信機 240 の両方のための VCO 信号を生成する。周波数合成器 250x 内で、VCO 360 は低帯域または中帯域のいずれかのための第 1 の VCO 信号を生成し、バッファ 362 は第 1 の VCO 信号をバッファする。VCO 370 は高帯域のための第 2 の VCO を生成し、バッファ 372 は第 2 の VCO 信号をバッファする。PLL 350 はバッファ 362 からバッファされた第 1 の VCO 信号、バッファ 372 からバッファされた第 2 の VCO 信号、および基準周波数で基準信号 (Ref) を受信する。PLL 350 は、第 1 の VCO 信号が低または中帯域の対象の VCO 周波数となるように、VCO 360 のための第 1 の制御信号を生成する。PLL 350 はさらに、第 2 の VCO 信号が高帯域のターゲット VCO 周波数となるように、VCO 370 のための第 2 の制御信号を生成する。PLL 350 によって生成される制御信号は同時に発生しない場合がある。言い換えれば、ターゲット周波数が低 / 中帯域の場合、第 1 の制御信号のみが生成される場合がある。ターゲット周波数が高帯域の場合、第 2 の制御信号のみが生成される場合がある。バッファ 364 は低帯域と中帯域のための第 1 の VCO 信号をバッファしドライブして、第 1 の VCO 信号のための配線 366 に沿って配置されうる。バッファ 374 は高帯域のための第 2 の VCO 信号をバッファしドライブして、第 2 の VCO 信号のための配線 376 に沿って配置されうる。

20

30

#### 【0026】

[0033]図 3 は、周波数合成器 250x の例示的設計を示している。周波数合成器は、他の仕方でも実装されうる。例えば、各帯域に別々の VCO が使用されうる。VCO 360 および 370 はさらに、電流制御発振器 (ICO)、数値制御発振器 (NCO) などに置き換えられうる。

40

#### 【0027】

[0034]図 3 に示された例示的設計では、単一の周波数合成器 250x が受信機 230 と送信機 240 の両方のための VCO 信号を生成するために使用される。低帯域または中帯域が選択される場合、VCO 360 は受信機 230a または 230b および送信機 240a または 240b のために第 1 の VCO 信号を生成する。高帯域が選択される場合、VCO 370 は受信機 230c と送信機 240c のために第 2 の VCO 信号を生成する。

#### 【0028】

[0035]受信機 230 のための回路は、送信機 240 から受信機 230 へのカップリングを減らすために、送信機 240 のための回路から可能な限り遠くに配置されうる。周波数合成器 250x は、受信機 230 に近く、送信機 240 からは比較的遠くに配置されうる。VCO 360 および 370 からの VCO 信号は、長い配線 366 および 376 を介して

50

送信機 240 に提供されうる。バッファ 364 および 374 は配線 366 および 376 に沿い一定の間隔で置かれ、VCO 信号のための信号のドライブ (drive) を提供するため使用されうる。

#### 【0029】

[0036]受信機 230 と送信機 240 の両方のための単一の周波数合成器 250x の使用は、種々の欠点を有する場合がある。第 1 に、VCO 信号のための配線 366 および 376 が複雑化され長くなる場合がある。バッファ 364 および 374 は、これらの配線に沿って VCO 信号をドライブするために配線 366 および 376 に沿って置かれる場合がある。バッファ 364 および 374 は受信機 230 と送信機 240 の両方のための VCO 信号の信号忠実度を保持するために大きくなる場合があり、この結果、ダウンコンバーター 336 とアップコンバーター 346 での LO 信号がかなりの波形を有する場合がある。大きなバッファ 364 および 374 は大量の電流を消費する場合があり、さらに、広い領域を占める場合もあり、この両方は望ましいものではない。その上、バッファ 364 および 374 の電源網は複雑化される場合があり、付随現象も大きくなる場合がある。これは、FDD モードの場合でも、受信機 230 と送信機 240 間のカップリングが増大する結果となる場合がある。10

#### 【0030】

[0037]第 2 に、送信機 240 の性能が、受信機 230 と送信機 240 の両方のための単一の周波数合成器 250x の使用により、劣化する場合がある。送信機 240 の VCO 信号のための長い配線 366 および 376 が不適切な組み合わせを起こしやすくする場合がある。送信機 240 の残留側波帯 (RSB) が、長い配線 366 および 376 の適合不足により、不十分なものになる場合がある。周波数合成器 250x の受信機 230 により近い配置も、周波数合成器 250x が、分周器 334 が有効 / 無効にされる場合の VCO の引きのために分周器 334 によってより容易に妨害されるという結果になりうる。この妨害は、例えば、TDD モードで、受信用 LO 回路が無効にされる場合、アップリンク間隔の最初で、送信用 LO 信号のより大きな位相誤差という結果になりうる。20

#### 【0031】

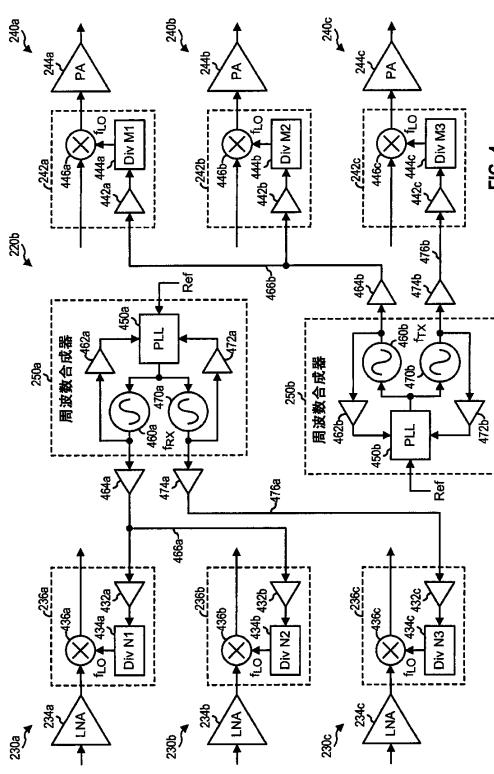

[0038]図 4 は、2 つの周波数合成器 250a および 250b により TDD をサポートする、送受信装置 220b のブロック図を示す。送受信装置 220b は、図 2 の送受信装置 220 の別の例示的設計である。送受信装置 220b は、(i) 低帯域のための受信機 230a と送信機 240a、(ii) 中帯域のための受信機 230b と送信機 240b、(iii) 高帯域のための受信機 230c と送信機 240c を含む。各受信機 230 は、受信回路 236 に結合された LNA 234 を含む。受信回路 236 は、バッファ 432、周波数分周器 434、およびダウンコンバーター 436 を含み、図 3 のバッファ 332a、周波数分周器 334a、およびダウンコンバーター 336a について、上述のとおりに動作することができる。各送信機 240 は、電力增幅器 244 に結合された送信回路 242 を含む。送信回路 244 は、バッファ 442、周波数分周器 444、およびアップコンバーター 446 を含み、図 3 のバッファ 342a、周波数分周器 344a、およびアップコンバーター 346a について、上述のとおりに動作することができる。30

#### 【0032】

[0039]図 4 に示された例示的設計では、周波数合成器 250a が受信機 230 のための受信用 VCO 信号を生成し、周波数合成器 250b が送信機 240 のための送信用 VCO 信号を生成する。周波数合成器 250a は、低帯域または中帯域のための受信用 VCO 信号を生成する VCO 460a、高帯域のための受信用 VCO 信号を生成する VCO 470a、VCO 460a および 470a のための制御信号を生成する PLL 450a、ならびにバッファ 462a および 472a を含み、図 3 の VCO 360 および 370、PLL 350、ならびにバッファ 362 および 372 について、上述と同じ仕方で動作することができる。周波数合成器 250b は、低帯域または中帯域のための送信用 VCO 信号を生成する VCO 460b、高帯域のための送信用 VCO 信号を生成する VCO 470b、VCO 460b および 470b のための制御信号を生成する PLL 450b、ならびにバッフ4050

ア 4 6 2 b および 4 7 2 b を含み、図 3 の V C O 3 6 0 および 3 7 0 、 P L L 3 5 0 、ならびにバッファ 3 6 2 および 3 7 2 について、上述と同じ仕方で動作することができる。

#### 【 0 0 3 3 】

[0040] バッファ 4 6 4 a は、 V C O 4 6 0 a からの低帯域または中帯域のための第 1 の受信用 V C O 信号をバッファしドライブする。バッファ 4 7 4 a は、 V C O 4 7 0 a からの高帯域のための第 2 の受信用 V C O 信号をバッファしドライブする。バッファ 4 6 4 b は、 V C O 4 6 0 b からの低帯域または中帯域のための第 1 の送信用 V C O 信号をバッファしドライブする。バッファ 4 7 4 b は、 V C O 4 7 0 b からの高帯域のための第 2 の送信用をバッファしドライブする。

#### 【 0 0 3 4 】

[0041] 図 4 は、周波数合成器 2 5 0 a および 2 5 0 b の例示的設計を示している。周波数合成器は、上述のとおり、他の仕方で実装されることもできる。

#### 【 0 0 3 5 】

[0042] 周波数合成器 2 5 0 a 内で、 V C O 4 6 0 a または 4 7 0 a のいずれかはいつでも有効にされうる。低帯域または中帯域で動作している場合、 P L L 4 5 0 a は、第 1 の受信用 V C O 信号が低帯域または中帯域でターゲット V C O 周波数になるように、 V C O 4 6 0 a のための制御信号を生成することができる。高帯域で動作している場合、 P L L 4 5 0 a は、第 2 の受信用 V C O 信号が高帯域でターゲット V C O 周波数になるように、 V C O 4 7 0 a のための制御信号を生成することができる。各分周器 4 3 4 は受信用 V C O 信号の周波数を N 分周することができ、これは任意の適切な値とすることができる。N の値は、各受信回路 2 3 6 に対して異なるものとすることができます。例えば、分周器 4 3 4 a は N 1 分周されうるもので、分周器 4 3 4 b は N 2 分周されうるもので、分周器 4 3 4 c は N 3 分周されうる。受信用 V C O 信号の周波数は次のように表しうる。

#### 【 0 0 3 6 】

$$f_{R_X} = N * f_{L_O}$$

ここで、  $f_{R_X}$  は受信用 V C O 信号の周波数で、  $f_{L_O}$  は L O 周波数、例えば、受信された R F 信号の中心周波数である。

#### 【 0 0 3 7 】

[0043] 周波数合成器 2 5 0 b 内で、 V C O 4 6 0 b または 4 7 0 b のいずれかはいつでも有効にされることが可能である。低帯域または中帯域で動作している場合、 P L L 4 5 0 b は、第 1 の送信用 V C O 信号が低帯域または中帯域でターゲット V C O 周波数になるように、 V C O 4 6 0 b のための制御信号を生成することができる。高帯域で動作している場合、 P L L 4 5 0 b は、第 2 の送信用 V C O 信号が高帯域でターゲット V C O 周波数になるように、 V C O 4 7 0 b のための制御信号を生成することができる。各分周器 4 3 4 は送信用 V C O 信号の周波数を M 分周することができ、これは任意の適切な値とすることができる。送信用 V C O 信号の周波数は次のように表しうる。

#### 【 0 0 3 8 】

$$f_{T_X} = M * f_{L_O}$$

ここで、  $f_{T_X}$  は送信用 V C O 信号の周波数である。

#### 【 0 0 3 9 】

[0044] 式 (1) および (2) に示されているように、同じ L O 周波数  $f_{L_O}$  の L O 信号が、 T D D モードの受信機 2 3 0 と送信機 2 4 0 に提供されうる。しかし、式 (1) の受信機 2 3 0 に対する分周器比 N は、式 (2) の送信機 2 4 0 に対する分周器比 M に等しい場合もあれば、等しくない場合もある。受信機 2 3 0 と送信機 2 4 0 のための別々の周波数合成器 2 5 0 a および 2 5 0 b の使用によって、受信機 2 3 0 と送信機 2 4 0 に対して同じまたは異なる周波数分周器比 N および M を使用するための柔軟性が可能になる。以下で記述されるように、受信機 2 3 0 と送信機 2 4 0 に対して異なる周波数分周器比を使用することによって、特定の利点が得られうる。

#### 【 0 0 4 0 】

[0045] 受信機 2 3 0 のための回路は、送信機 2 4 0 から受信機 2 3 0 へのカップリング

10

20

30

40

50

を減らすために、送信機 240 のための回路から可能な限り遠くに配置されうる。周波数合成器 250a は受信機 230 の近くに配置されうるもので、周波数合成器 250b は送信機 240 の近くに配置されうる。VCO 460a および 470a からの受信用 VCO 信号は、比較的短い配線 466a および 476a を介して受信機 230 に提供されうる。同様に、VCO 360b および 370b からの送信用 VCO 信号は、比較的短い配線 466b および 476b を介して送信機 240 に提供されうる。

#### 【0041】

[0046]無線装置 110 は TDD および FDD モードの両方をサポートすることができる。無線装置 110 には、FDD モードで受信機 230 と送信機 240 のために異なる LO 周波数で受信および送信用 LO 信号を生成するための周波数合成器 250a および 250b を含めることができる。周波数合成器 250a および 250b は再使用されうるもので、TDD モードで両方ともが有効にされうるもので、回路および領域の不利益がないという結果になる。10

#### 【0042】

[0047]図 5 は、図 4 の周波数合成器 250a の例示的設計のブロック図を示す。簡単にするために、図には VCO 460a とバッファ 462a のみが示されており、VCO 470a とバッファ 472a は簡単にするために省かれている。PLL 450a 内で、位相周波数検出器 510 は  $f_{REF}$  の正確な周波数およびマルチモジュラス分周器 (multi modulus divider) 516 からのフィードバック信号を有する基準信号を受信する。検出器 510 は基準信号の位相に対してフィードバック信号の位相を比較し、2つの入力信号間で位相の相違 / 誤差を示す誤差信号を提供する。電荷ポンプ 512 は誤差信号を受信して、誤差信号に比例する電流（または電荷）を生成する。ループ・フィルター 514 は電流信号をフィルター処理して、制御信号を提供する。VCO 460a は制御信号を受信し、制御信号によって決定される、 $f_{RX}$  の周波数を有する VCO 信号を生成する。バッファ 462a は VCO 信号をバッファして、バッファされた VCO 信号を提供する。分周器 516 は L の分周器比による周波数でバッファされた VCO 信号を分周し、位相周波数検出器 510 にフィードバック信号を提供する。20

#### 【0043】

[0048]分周器比 L は非整数値とすることができる、整数部分 Q と小数部分 F に分解されうるもので、ここで、 $L = Q + F$ 、 $Q \geq 1$  および  $1 > F > 0$  である。デルタシグマ変調器 520 は小数部分 F を受信して、1（「1」）とゼロ（「0」）のビット列を生成し、ここでの 1 の割合は小数部分 F に依存している。しかし、量子化ノイズの大部分が高周波で出現するように定められ、およびループ・フィルター 514 によってより容易にフィルター処理されうるように、1 とゼロはビット列に分散される。加算器 522 は、デルタシグマ変調器 520 からのビット列と整数部分 Q を加算し、分周器 516 に瞬間の (instantaneous) 分周器比を提供する。瞬間の分周器比は、Q または  $Q + 1$  に等しく、デルタシグマ変調器 520 によってゼロまたは 1 のいずれかが提供されるかに依存している。30

#### 【0044】

[0049]周波数合成器 250a は小数 L の周波数合成器として動作されうる。小数分周器比 L は基準周波数のレートで Q および  $Q + 1$  の整数値間の瞬間の分周器比の変更 / ディザリングによって得られうるもので、ここで、Q は L 未満の最大整数値である。瞬間の分周器比は基準信号のサイクルごとに一度、変更することができる。瞬間の分周器比の平均は小数分周器比 L に等しい。整数分周器比 Q および  $Q + 1$  の列で小数分周比を近似する結果の量子化ノイズは、周波数合成器 250a の閉ループ帯域幅の外側の高周波数に集めるためにデルタシグマ変調器 520 により成形されうる。次いで、量子化ノイズは周波数合成器 250a のロー・パス応答によってフィルター処理されうる。40

#### 【0045】

[0050]周波数合成器 250a はさらに、整数 L の周波数合成器として動作されうる。この場合、デルタシグマ変調器 520 は除去されうる。分周器 516 は固定された整数分周器比による周波数でバッファされた VCO を分周することができ、VCO 周波数は基準周50

波数の整数倍、すなわち  $f_{VCO} = L^* f_{REF}$  とすることができます。

#### 【0046】

[0051]周波数合成器 250a および 250b は、TDD モードで受信機 230 と送信機 240 のための VCO 信号を生成することができる。TDD モードでは、ダウンリンクの受信機 230 のための LO 周波数は、式(1)および(2)に示されているように、所定のフレームにおけるアップリンクの送信機 240 のための LO 周波数と同じである。

#### 【0047】

[0052]一例示的設計では、周波数合成器 250a および 250b は同じ VCO 周波数で VCO 信号を生成することができ、この結果、式(1)および(2)では  $f_{RX} = f_{TX}$  および  $N = M$  である。この設計は、送受信装置が優れた送受信隔離を有する場合に、使用されうる。10

#### 【0048】

[0053]別の例示的設計では、周波数合成器 250a および 250b は異なる VCO 周波数で VCO 信号を生成することができ、この結果、式(1)および(2)では  $f_{RX} \neq f_{TX}$  および  $N \neq M$  である。この設計は、送受信装置が VCO の引きを軽減するために不十分な送受信隔離を有する場合、使用されうるもので、これは、送信および受信用 VCO (例えば、VCO 360 および VCO 370) が同じまたは似た周波数で発振する場合に、重大なものになる場合がある。受信機 230 は残留側波帯でより厳しい要件を有する場合があるので、受信機 230 のための分周器 434 には整数分周器比が使用されうるもので、送信機 240 のための分周器 444 には非整数分周器比が使用されうる。例えば、2 の分周比を使う分周器はより単純なので、より優れた残留側波帯性能という結果になりうる。例として、受信機 230 には 2 の分周器比 ( $N = 2$ ) が使用されうるもので、送信機 240 には 1.5 の分周器比 ( $N = 1.5$ ) が使用されうる。この場合、受信用 VCO 信号は  $f_{RX} = 2^* f_{LO}$  の周波数を有し、送信用 VCO 信号は  $f_{TX} = 1.5^* f_{LO}$  の周波数を有するはずである。送信用 VCO 信号のために 1.5 (および他の整数または非整数分周器比) の分周器比を使用することによって、多数の帯域のための VCO 信号が、広い同調範囲を網羅するための注意深い周波数計画により 1VCO で生成されうる。整数または非整数分周器比は、図 5 の PLL 450a によりサポートされうる。20

#### 【0049】

[0054]複式周波数合成器 250a および 250b は、TDD を利用する種々の無線システムとの通信のために受信機 230 と送信機 240 で使用されうる。例えば、複式周波数合成器 250a および 250b は、LTE TDD システム、TD-SCDMA システムなどとの通信のために使用されうる。30

#### 【0050】

[0055]図 6A は、TD-SCDMA のためのフレーム構造 600 を示す。送信時間行はフレームに分割され、各フレームはシステム・フレーム番号 (SFN) によって識別される。各フレームは 10 ミリ秒 (ms) の継続時間を有し、2 つのサブフレーム 1 および 2 に分割される。各サブフレームは 5 ms の継続時間を有し、7 つの時間スロット 0 から 6 、ダウンリンク・パイラット時間スロット (DWPTS) 、アップリンク・パイラット時間スロット (UPPTS) 、および保護期間 (GP) に分割される。DWPTS、保護期間、および UPPTS は、時間スロット 0 の後に配置される。時間スロット 0 はダウンリンクのために使用され、時間スロット 1 はアップリンクのために使用され、時間スロット 2 から 6 はスイッチ点によって決定されるとおり、ダウンリンクおよび / またはアップリンクのために使用されうる。図 6A に示されている例では、時間スロット 2 から 6 はダウンリンクのために使用される。各時間スロットは 675 マイクロ秒 ( $\mu s$ ) の継続時間をしており、864 チップを網羅する。DWPTS は 75  $\mu s$  の継続時間を有し、96 チップを網羅する。UPPTS は 125  $\mu s$  の継続時間を有し、160 チップを網羅する。DWPTS と UPPTS 間の保護期間は 75  $\mu s$  の継続時間を有し、96 チップを網羅する。40

#### 【0051】

[0056]各時間スロットは、第 1 のデータ部分、ミッドアンブル、第 2 のデータ部分、お50

より保護期間を含む。各データ部分は  $275 \mu s$  の継続時間を有し、352チップを網羅する。ミッドアンブルは  $112.5 \mu s$  の継続時間を有し、144チップを網羅する。時間スロットの終端の保護期間は  $12.5 \mu s$  の継続時間を有し、16チップを網羅する。各時間スロットは、データ送信のために1人または複数のユーザーに割り当てられる。

#### 【0052】

[0057] 図6Bは、LTE-TDDのためのフレーム構造650を示す。送信時間行は無線フレームのユニットに分割され、各無線ユニットは  $10ms$  の継続時間を有している。各無線フレームは10のサブフレームに分割され、0から9の添え字が付いている。LTEは、TDDのいくつかのアップリンク・ダウンリンク構成をサポートしている。すべてのアップリンク・ダウンリンク構成で、サブフレーム0および5はダウンリンク(DL)のために使用され、サブフレーム2はアップリンク(UL)のために使用される。サブフレーム3、4、7、8、および9のそれぞれは、アップリンク・ダウンリンク構成に応じて、ダウンリンクまたはアップリンクのために使用されうる。サブフレーム1は、ダウンリンク制御チャネルやデータ送信のために使用されるダウンリンク・パイロット時間スロット(DwPTS)、無送信の保護期間(GP)、およびランダム・アクセス・チャネル(RACH)またはサウンディング参照信号(SRS)のいずれかのために使用されるアップリンク・パイロット時間スロット(UpPTS)からなる3つの特別なフィールドを含んでいる。サブフレーム6は、アップリンク・ダウンリンク構成に応じて、DwPTSのみ、または3つのすべての特別フィールド、またはダウンリンク・サブフレームを含むことができる。DwPTS、保護期間、およびUpPTSは、異なるサブフレーム構成に対して異なる継続時間を持つことができる。DwPTSは  $214$  と  $857 \mu s$  の間の継続時間を有することができる。UpPTSは  $71$  と  $142 \mu s$  の間の継続時間を有することができる。保護期間は  $71$  と  $714 \mu s$  の間の継続時間を有することができる。

10

20

#### 【0053】

[0058] 図6Aおよび図6Bで示されているように、LTE-TDDシステムおよびTDS-SCDMAシステムはダウンリンクの時間スロットとアップリンクの時間スロット間で高速スイッチングを有している。図6Aの例では、TDS-SCDMAシステムのサブフレーム内で、ダウンリンクからアップリンクへの移行は  $75 \mu s$  内の保護期間で起こり、アップリンクからダウンリンクへの移行は時間スロットの最後の  $12.5 \mu s$  内の保護期間で起こる。

30

#### 【0054】

[0059] 図6Aおよび図6Bで示されているように、受信機は一部の時間間隔でのみアクティブにすることができる、送信機はTDDを利用する無線システムと通信するための他の一部の時間期間でアクティブにすることができる。電池残量を温存し、性能をできるだけ向上させるために、周波数合成器250aは、受信機がアクティブな場合に有効にされうるもので、他の時には無効にされうる。同様に、周波数合成器250bは、送信機がアクティブな場合に有効にされうるもので、他の時には無効にされうる。周波数合成器250aおよび250bは、パワーオン・シーケンスに基づいて有効および無効にされうる。

#### 【0055】

[0060] 図7Aから図7Dは、TDS-SCDMAシステムと通信するための周波数合成器250aおよび250bの例示的なパワーオン・シーケンスを示している。図7Aから図7Dに示されている例では、無線装置110はダウンリンクのためには時間スロット0、2、および3が割り当てられており、アップリンクのためには時間スロット1が割り当てられている。1つの帯域のために1つの受信機230と1つの送信機240がTDS-SCDMAシステムと通信するために選択される。図7Aに示されているように、選択された受信機230は、(i)時間スロット0とDwPTSの間は有効にされ、(ii)保護期間、UpPTS、および時間スロット1の間は無効にされ、(iii)時間スロット2および3の間は有効にされ、(iv)時間スロット4から6の間は無効にされる。選択された送信機240は、(i)時間スロット0、DwPTS、および保護期間の間は無効にされ、(ii)UpPTS、および時間スロット1の間は有効にされ、(iii)時間スロ

40

50

ット 2 から 6 の間は無効にされる。

#### 【 0 0 5 6 】

[0061] 図 7 A は、周波数合成器 250 a および 250 b のための例示的なパワーオン・シーケンス 710 を示しており、電源消費を減らすために設計されている。パワーオン・シーケンス 710 では、受信機 230 が有効にされる少し前に、周波数合成器 250 a は有効にされ、受信機 230 が無効にされる時に無効にされる。同様に、送信機 240 が有効にされる少し前に、周波数合成器 250 b は有効にされ、送信機 240 が無効にされる時に無効にされる。周波数合成器 250 a および 250 b は、VCO 信号が受信機 230 と送信機 240 により必要とされる時の前に、ターゲット VCO 周波数をウォームアップして同期するため、十分早く有効にされる。周波数合成器 250 a および 250 b は、電源消費を減らす必要がない時には、無効され電源はオフにされうる。

10

#### 【 0 0 5 7 】

[0062] 図 7 B は、周波数合成器 250 a および 250 b のための例示的なパワーオン・シーケンス 720 を示しており、受信機 230 への妨害を減らすために設計されている。高い変調順がダウンリンクのデータ送信のためにサポートされうる。受信機 230 は、例えば、64 直交振幅変調 (QAM) などの高い変調順の変調シンボルを備えるダウンリンク信号の復調時に、優れた性能を達成するため、受信用 VCO 信号における小さな位相誤差（例えば、5 度未満）という結果になる妨害のみを許容することができる場合がある。周波数合成器 250 a の受信用 VCO 信号の位相は、周波数合成器 250 b が電源が投入される場合はいつでも突然変更することができる。したがって、周波数合成器 250 b は、受信機 230 が有効にされる時間間隔ではない、十分に早く電源が投入されうる。図 7 B に示される例では、周波数合成器 250 b は、時間スロット 0 の前、例えば、周波数合成器 250 a が有効にされるのと同時に、有効にされる。したがって、周波数合成器 250 b は、時間スロット 0 および D W P T S の間に周波数合成器 250 a の受信用 VCO 信号の位相を妨害することはない。周波数合成器 250 b は時間スロット 1 の後に無効にされ、これは、アップリンクのための無線装置 110 に割り当てられた最後の時間スロットである。同様に、周波数合成器 250 a は、送信機 240 が有効にされる期間の間ではない、十分に早く電源が投入されうる。

20

#### 【 0 0 5 8 】

[0063] 一部のパワーオン・シーケンス構成（図示せず）では、送信または受信機周波数合成器 250 a および 250 b は、時間スロットのミッドアンブル内で有効にされうる。例えば、送信または受信機周波数合成器 250 a および 250 b は、データ・スロットの任意の部分内で有効にされうる。ミッドアンブルは、例えば、64 QAM など、データ・スロットの他の部分で使用される変調より厳しさが少ない変調（例えば、変調の速度がより低い）、例えば、四位相偏移変調 (QPSK) を使用することができる。ミッドアンブル間の送信周波数合成器 250 a および受信機周波数合成器 250 b の有効化は、妨害がより少なく、したがって、性能の劣化がより少なくなる場合がある。例えば、QPSK では、受信機 230 または送信機 240 は、周波数合成器 250 b の電源投入によってより大きな妨害を許容することができる。例えば、ダウンリンクおよび / またはアップリンクでは、64 QAM が使用されうる。送信周波数合成器 250 b はさらに、誘導された妨害を最小限にするためにダウンリンクのミッドアンブル間に有効にされうる。

30

40

#### 【 0 0 5 9 】

[0064] 図 7 C は、周波数合成器 250 a および 250 b のための例示的なパワーオン・シーケンス 730 を示しており、VCO の引きを減らすために設計されている。周波数合成器 250 a および 250 b 間の隔離および信号バスは、送信機 220 の全領域、レイアウト、およびフロアプランなどの種々の要因に依存しうる。送受信装置 220 が不十分な受信 送信分離を有する場合がある。この場合、VCO の引きが発生し、1 つの周波数合成器に電源を投入することは、他の周波数合成器の周波数 / 位相を乱す場合がある。不十分な受信 送信分離による VCO の引きを減らすために、周波数合成器 250 a および 250 b は共に有効にされうる。図 7 C に示されている例では、周波数合成器 250 a およ

50

び 250b は両方とも、時間スロット 0 の前に有効にされ、時間スロット 3 の終わりに無効にされる。受信機 230 は、時間スロット 0、DwPTS、時間スロット 2 および 3 の間のみ有効にされる。送信機 240 は、UpPTS および時間スロット 1 の間のみ有効にされる。周波数合成器 250a および 250b は、関連された受信機 230 および送信機 240 より長く有効にされ、より高い電力消費という結果になる場合がある。しかし、VCO 信号のための長い配線および大きなバッファは、複式周波数合成器 250a および 250b を使用することによって回避されうるもので、受信機 230 と送信機 240 の両方に対して、より低い電力消費およびより優れた性能（例えば、より優れた残留側波帯）という結果になる場合がある。

## 【0060】

10

[0065] 図 7D は、周波数合成器 250a および 250b のための例示的なパワーオン・シーケンス 740 を示しており、位相ノイズの劣化を軽減するために設計されている。送受信装置 220 内の受信 送信隔離が不十分な場合、周波数合成器 250a の受信用 VCO および周波数合成器 250b の送信用 VCO 間のカップリングが互いの位相ノイズを悪化させうる。その上、受信用 VCO と送信用 VCO の周波数が互いに近すぎる場合、注入同期 (injection lock) が発生する場合がある。注入同期はもう一方の VCO（例えば、送信用 VCO）の位相ノイズを圧倒する一方の VCO 位相ノイズ（例えば、受信用 VCO）の原因となる場合があり、悪化する結果になる。言い換えれば、注入同期は、一方の VCO の位相ノイズがもう一方の VCO の位相ノイズを圧倒するので、問題である。

## 【0061】

20

[0066] 位相ノイズの悪化を軽減する 1 つの設計において、受信用 VCO と送信用 VCO は、上述のように、異なる周波数で動作しうる。そして、必要な LO 周波数で受信および送信用 LO 信号を得るために、異なる分周器比が受信および送信用 VCO 信号に対して使用されうる。例えば、 $N = 2$  の分周器比が周波数合成器 250a からの受信用 VCO 信号に対して使用されうるもので、 $M = 1.5$  の分周器比が周波数合成器 250b からの送信用 VCO 信号に対して使用されうる。

## 【0062】

[0067] 位相ノイズの悪化を軽減する別の設計では、受信用 VCO 周波数は、(i) いかなる時も受信用 VCO と送信用 VCO が同じ周波数で動作せず、(ii) いかなる時も受信用 VCO あるいは送信用 VCO のみがターゲット VCO 周波数で動作する、ように、送信用 VCO 周波数からわずかにずらされうる。図 7D に示されている例では、周波数合成器 250a および 250b は両方とも、時間スロット 0 の前に有効にされ、両方とも時間スロット 3 の終わりに無効にされる。周波数合成器 250a 内の受信用 VCO は、受信機 230 が有効にされる場合、時間スロット 0、DwPTS、時間スロット 2 および 3 の間、 $N^* f_{LO}$  のターゲット VCO 周波数で動作する。受信用 VCO は、受信機 230 が無効にされる場合、保護期間、UpPTS、および時間スロット 1 の間、 $N^*(f_{LO} + f)$  のずらされた VCO 周波数で動作する。周波数合成器 250b 内の送信用 VCO は、送信機 240 が有効にされる場合、UpPTS および時間スロット 1 の間、 $M^* f_{LO}$  のターゲット VCO 周波数で動作する。送信用 VCO は、送信機 240 が無効にされる場合、時間スロット 0、DwPTS、時間スロット 2 および 3 の間、 $M^*(f_{LO} + f)$  のずらされた VCO 周波数で動作する。受信用 VCO と送信用 VCO は同時（例えば、図 7D に示されているとおり）または異なる時（図 7D に図示せず）に周波数を切り換えることができる。

30

## 【0063】

40

[0068] 受信および送信用 VCO 周波数は、各種やり方でずらされうる。例示的一例では、VCO 周波数は、PLL をリセットすることなく、少量だけ PLL（すなわち、合成器周波数語）の周波数分周器比を動的に調整することによってずらされうる。例えば、図 5 の少部分 F は、VCO 周波数でわずかな変更を得るために、小さな値に設定されうる。実行している周波数合成器の限られた周波数ダイナミック・レンジのために、VCO 周波数のわずかなずれのみが、達成しうる。VCO 周波数の整定時間は、VCO 周波数のわず

50

かな変更の結果、比較的短くすることができる。別の例示的設計では、VCO周波数は、周波数合成器のハード・リセットを介してずらされうる。ハード・リセットは、PLLの電源を一時的にオフにすることによって達成されうる。ハード・リセットは、PLLを初期状態（すなわち、PLLが最初を同期する前の最初に電源を投入した時の状態）にリセットする。一部の例示的設計では、VCO周波数は、周波数合成器のソフト・リセットを介してずらされうる。ソフト・リセットでは、分周比がその場で変更され、PLLは周波数の変更に適応するが、電源の切断は必要ない。VCO周波数の大きなずれは、VCO周波数のためのより長い整定時間を伴う場合でも、達成可能なことがある。

#### 【0064】

[0069]図7Aから図7Dは、TDDモードの受信機と送信機のための2つの周波数合成器の4つの例示的パワーオン・シーケンスを示している。2つの周波数合成器はさらに他の仕方で、有効および無効にされうる。例えば、一方の周波数合成器（例えば、周波数合成器250a）はいつでも有効にされうるもので、もう一方の周波数合成器は必要に応じて、有効または無効にされうる。10

#### 【0065】

[0070]TDDモードの受信機230と送信機240に対して別々の周波数合成器250aおよび250bを使用すると、種々の利点を提供することができる。第1に、より少ないおよび／またはより小さいバッファ464および474がより少ない負荷のより短い距離を介してVCO信号をドライブするために使用されうる。より少ないおよび／またはより小さいバッファ464および474は回路領域を節約し、電源消費を削減することができる。VCO信号のための配線466および476は、より短く、より複雑化されず、よりカップリングされにくいものとすることができます。20

#### 【0066】

[0071]第2に、VCO信号のためのより短い配線466および476により、受信機230と送信機240に対して、より優れた性能（例えば、より優れた残留側波帯）が達成されうる。受信機230と送信機240に対する位相妨害のより優れた抑制は、以下に記述されるとおり、周波数合成器250aおよび250bの適切なLO周波数計画およびパワーオン・シーケンスで達成されうる。より優れた受信 送信隔離はさらに、図4に示されているように、送受信装置の受信部分と送信部分間にスイッチまたはバッファが接続されていないので、TDDおよびFDDモードの両方でも達成されうる。より優れた受信送信隔離はさらに、周波数合成器250aおよび250bに対して、より少ない妨害、VCOの引き、およびより高速なスイッチング時間という結果にもなりうる。30

#### 【0067】

[0072]他の利点はさらに、TDDモードの受信機230と送信機240のための2つの周波数合成器を使用することによっても得られる。例えば、LO周波数はTDDモードの所定のフレームの受信機230と送信機240の両方で同じなので、VCO周波数を再同期するための時間は必要ない。この結果が起き得るのは、例えば、受信機230と送信機240の周波数合成器が両方とも、同じフレームのアップリンクおよびダウンリンク内に有効にされるからである。受信機230と送信機240に対して、異なる分周器比が使用される場合には、より小さいVCO同調範囲が可能な場合がある。40

#### 【0068】

[0073]例示的設計では、装置（例えば、無線装置、IC、回路モジュールなど）は、第1および第2周波数合成器を備えることができる。第1の周波数合成器（例えば、図4の周波数合成器250a）は、第1の発振器信号（例えば、受信用VCO信号）を生成でき、受信機のためのLO周波数で第1のLO信号（例えば、受信用LO信号）を生成するために使用されうる。第2の周波数合成器（例えば、周波数合成器250b）は、第2の発振器信号（例えば、送信用VCO信号）を生成でき、送信機のための同じLO周波数で第2のLO信号（例えば、送信用LO信号）を生成するために使用されうる。

#### 【0069】

[0074]第1および第2の周波数合成器は、装置がTDDモードで動作する場合、同じLO50

O周波数で第1および第2のLO信号を得るために第1および第2の発振器信号を生成する。TDDモードでは、受信機は第1の時間間隔の間、有効にされうるもので、送信機は第2の時間間隔の間、有効にされうる。装置はさらに、FDDモードでも動作することができる。この場合、第1および第2の周波数合成器は、異なるLO周波数で第1および第2のLO信号を得るために第1および第2の発振器信号を生成する。

#### 【0070】

[0075]一設計では、第1および第2の周波数合成器は、同じ発振器 / VCO周波数で第1および第2の発振器信号を生成することができる。この設計では、第1および第2の発振器信号は、同じLO周波数で第1および第2のLO信号を得るために、同じ分周器比による周波数で分周されうる。別の設計では、第1および第2の周波数合成器は、異なる発振器 / VCO周波数で第1および第2の発振器信号を生成することができる。第1の発振器信号は第1の発振器周波数とすることができる、これはLO周波数の整数倍である。第2の発振器信号は第2の発振器周波数とできることができる、これは、第1の発振器周波数とは異なるものとすることができる、LO周波数の比整数倍とすることができる。10

#### 【0071】

[0076]第1および第2の周波数合成器は、種々のやり方で有効および無効にすることができる。図7Aに示されている一設計では、第1の周波数合成器は、受信機が有効にされる前に、有効にされうるもので、受信機が無効にされる時または後に、無効にされうる。第2の周波数合成器は、送信機が有効にされる前に、有効にされうるもので、送信機が無効にされる時または後に、無効にされうる。図7Bに示されている別の設計では、第1および第2の周波数合成器は、受信機が有効にされる前に、有効にされうる。第1の周波数合成器は、受信機が無効にされた時または後に、無効にされうる。第2の周波数合成器は、送信機が無効にされた時または後に、無効にされうる。図7Cに示されているさらに別の設計では、第1および第2の周波数合成器は、受信機が有効にされる前に、有効にされうるもので、受信機が無効にされる時または後に、無効にされうる。第1および第2の周波数合成器はさらに、他のやり方でも有効および無効にされうる。20

#### 【0072】

[0077]一設計では、第1の周波数合成器は、受信機が有効にされる場合、ターゲット発信器周波数（例えば、 $N^* f_{LO}$ ）で第1の発振器信号を、および送信機が有効にされる場合、ターゲット発信器周波数からのずれたもの（例えば、 $N^*(f_{LO} + f)$ ）を生成することができる。第1の周波数合成器はPLLを備えることができ、ターゲット発信器周波数からずれたものは、PLL内の周波数分周器比を変更することによって得られる。一設計では、第2の周波数合成器は、送信機が有効にされる場合、ターゲット発信器周波数（例えば、 $M^* f_{LO}$ ）で第2の発振器信号を、および受信機が有効にされる場合、ターゲット発信器周波数からのずれたもの（例えば、 $M^*(f_{LO} + f)$ ）を生成することができる。30

#### 【0073】

[0078]図8は、LO信号を生成するためのプロセス800の例示的設計を示している。第1の発振器信号は、第1の周波数合成器で生成されうる812。受信機のためのLO周波数で第1のLO信号が第1の発振器信号に基づいて生成されうる814。第2の発振器信号は、第2の周波数合成器で生成されうる816。送信機のためのLO周波数で第2のLO信号が第2の発振器信号に基づいて生成されうる818。40

#### 【0074】

[0079]第1の周波数合成器は、第1の発振器周波数で第1の発振器信号を生成することができる。第2の周波数合成器は、第2の発振器周波数で第2の発振器信号を生成することができる。一設計では、第1の発振器周波数は第2の発振器周波数と同じで、同じ周波数分周器比が、第1および第2のLO信号を生成するために、第1および第2の発振器信号のために使用されうる。別の設計では、第1の発振器周波数は第2の発振器周波数と異なることができる。この設計では、第1の発振器周波数はLO周波数の整数倍（例えば、2倍）で、第2の発振器周波数はLO周波数の非整数倍（例えば、1.5倍）とすること50

ができる。

【0075】

[0080]第1および第2の周波数合成器は、上述のとおり、種々のやり方で有効および無効にされうる。第1および第2の周波数合成器は、種々のやり方で第1および第2の発振器信号を生成することができる。一設計では、第1および第2の発振器信号は、常時、ターゲット発信器周波数とすることができる。別の設計では、例えば、図7Dに示されるとおり、第1の発振器信号は、受信機が有効にされる場合、ターゲット発信器周波数とすることができる、送信機が有効にされる場合、ターゲット発振器周波数からはずれたものとすることができる。例えば、さらに図7Dに示されるとおり、第2の発振器信号は、送信機が有効にされる場合、ターゲット発信器周波数とすることができ、受信機が有効にされる場合、ターゲット発振器周波数からはずれたものとすることができる。10

【0076】

[0081]当業者ならば、情報および信号は多様な異なるテクノロジーおよび技術のいずれかを使用して表現されうることを理解するはずである。例えば、上述全体で参照される場合のあるデータ、命令、コマンド、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または粉、光場または粉、あるいはこれらのいずれかの組み合わせにより表現されうる。

【0077】

[0082]当業者はさらに、本明細書の開示に関連して記述された種々の例示的論理ブロック、モジュール、回路、およびアルゴリズム・ステップは電子機器、コンピュータ・ソフトウェア、または両方の組み合わせとして実装されうることを認識するはずである。ハードウェアとソフトウェアのこの互換性を明確に例示するために、各種の例示的コンポーネント、ブロック、モジュール、回路、およびステップが一般的に、機能の観点で上述されてきた。このような機能がハードウェアまたはソフトウェアとして実装されるかどうかは、システム全体に課せられる特定の用途および設計制約に左右される。熟練工は各特定の用途に対してさまざまなやり方で記述された機能を実装することができるが、このような実装の決定は本開示の範囲の逸脱もたらすものとして解釈されるべきではない。20

【0078】

[0083]本明細書の開示に関連して記述された種々の例示的論理ブロック、モジュール、および回路は、汎用目的プロセッサー、デジタル信号プロセッサー(DSP)、特定用途向け集積回路(ASIC)、フィールド・プログラマブル・ゲート・アレイ(FPGA)または他のプログラム可能な論理デバイス、ディスクリート・ゲートまたはトランジスター・ゲート、ディスクリート・ハードウェア・コンポーネント、あるいは本明細書に記述された機能を行うために設計されたこれらの組み合わせを使って実装または実行されうる。汎用目的プロセッサーはマイクロプロセッサーとすることができますが、代替として、プロセッサーは従来の任意のプロセッサー、コントローラー、マイクロコントローラー、または状態機械とすることができます。プロセッサーはさらに、例えば、DSPとマイクロプロセッサーの組み合わせ、複数のマイクロプロセッサー、DSPコアと併用する1または複数のマイクロプロセッサー、またはいずれか他のこののような構成などのコンピューティング・デバイスの組み合わせとして実装されうる。30

【0079】

[0084]本明細書の開示に関連して記述された方法またはアルゴリズムの各ステップは、ハードウェア、プロセッサーによって実行されるソフトウェア・モジュール、または2つの組み合わせに直接、具現化されうる。ソフトウェア・モジュールは、ランダム・アクセス・メモリー(RAM)、フラッシュ・メモリ、読み出し専用メモリー(ROM)、消去可能プログラム可能読み出し専用メモリー(EPRROM)、電気的消去可能書き込み可能読み出し専用メモリー(EEPROM)、レジスター、ハード・ディスク、リムーバブル・ディスク、CD-ROMまたは当技術分野で知られている他の何らかの形の記憶媒体に常駐することができる。例示的な記憶媒体は、プロセッサーが、記憶媒体からの情報の読み取りおよび情報の書き込みを行うことができるようなプロセッサーと結合されている。40

代替として、記憶媒体はプロセッサーに内蔵することができる。プロセッサーと記憶媒体は A S I C に常駐することができる。A S I C はユーザー端末に常駐することができる。代替として、プロセッサーと記憶媒体は、ユーザー端末のディスクリート・コンポーネントとして常駐することができる。

#### 【0080】

[0085] 1 または複数の例示的設計では、記述された機能は、ハードウェア、ソフトウェア、ファームウェア、またはこれらの任意の組み合わせで実現されうる。ソフトウェアで実現されるのであれば、これら機能は、コンピュータ読取可能な媒体におけるコードまたは 1 または複数の命令群で送信されるか格納されうる。コンピュータ読取可能な媒体は、1 つの場所から別ヘコンピュータ・プログラムの転送を容易にするいずれかの媒体を含む、コンピュータ記憶媒体と通信媒体の両方を含む。記憶媒体は、汎用目的または特殊目的コンピュータによりアクセスされうる使用可能ないずれかの媒体とされうる。限定する訳ではなく、例として、このようなコンピュータ読取可能な媒体は、R A M、R O M、E E P R O M、C D R O M、またはその他の光ディスク記憶装置、磁気ディスク記憶装置、またはその他の磁気記憶デバイス、フラッシュ・メモリ、または、命令群またはデータ構造の形式でかつ汎用目的または特殊目的コンピュータ、あるいは汎用目的または特殊目的プロセッサーによってアクセスされうる所望のプログラム・コード手段を搬送し格納するために使用されうるその他任意の媒体を備えうる。さらに、いかなる接続も、コンピュータ読取可能な媒体として適切に称される。例えば、同軸ケーブル、光ファイバ・ケーブル、対より線・ペア、デジタル加入者線 (D S L)、または、例えば赤外線や無線やマイクロ波のような無線技術を用いて、ウェブサイト、サーバ、またはその他の遠隔ソースからソフトウェアが送信されるのであれば、同軸ケーブル、光ファイバ・ケーブル、対より線、D S L、あるいは、赤外線や無線やマイクロ波のような無線技術が、媒体の定義に含まれる。本明細書で使用されるディスク (d i s k および d i s c ) は、コンパクト・ディスク (d i s c ) (C D)、レーザ・ディスク (d i s c )、光ディスク (d i s c )、デジタル多用途ディスク (d i s c ) (D V D)、フロッピー (登録商標) ディスク (d i s k )、およびブルー・レイ・ディスク (d i s c ) を含む。これら d i s c は、レーザを用いてデータを光学的に再生する。それに対して、d i s k は、通常、データを磁的に再生する。上記の組み合わせもまた、コンピュータ読取可能な媒体の範囲内に含まれるべきである。

#### 【0081】

[0086] 本開示の以前の記述は、当業者が本開示の作成または使用をできるように提供される。本開示への種々の変形態は当業者には直ぐに明らかにない、そして、本明細書で定義された一般原理は本開示の趣旨または範囲を逸脱することなく、他の変形形態に適用されうる。したがって、本開示は本明細書に記述された例および設計に限定されることを意図するものではなく、本明細書で開示された原理および新規な特徴と調和した最も広い範囲に従うことを意図するものである。

以下に、出願当初の特許請求の範囲に記載された発明を付記する。

#### [ C 1 ]

無線通信のための装置であつて、

受信機のためのL O周波数で第1の局部発振器 (L O) 信号を生成するために使用される第1の発振器信号を生成するように構成された第1の周波数合成器と、

送信機のためのL O周波数で第2のL O信号を生成するために使用される第2の発振器信号を生成するように構成された第2の周波数合成器と、

を備え、

ここにおいて、前記第1および第2の周波数合成器は、前記装置が時分割モードで動作している場合、前記同じL O周波数で前記第1および第2のL O信号を得るために前記第1および第2の発振器信号を生成するように構成された装置。

#### [ C 2 ]

前記時分割モードにおいて、前記受信機は第1の時間間隔の間、有効にされ、前記送信

10

20

30

40

50

機は第 2 の時間間隔の間、有効にされる、C 1 に記載の装置。

[ C 3 ]

前記時分割モードは、時分割複信（TDD）モードおよび時間分割同期コード分割多元接続（TDS CDMA）モードのいずれかである、C 1 に記載の装置。

[ C 4 ]

前記TDDモードは、ロング・ターム・エボリューション（LTE）TDDモードである、C 3 に記載の装置。

[ C 5 ]

前記第 1 および第 2 の周波数合成器は、同じ発振器周波数で前記第 1 および第 2 の発振器信号を生成するように構成された、C 1 に記載の装置。

10

[ C 6 ]

前記第 1 の周波数合成器は、第 1 の発振器周波数で前記第 1 の発振器信号を生成するように構成され、前記第 2 の周波数合成器は、前記第 1 の発振器周波数とは異なる第 2 の発振器周波数で前記第 2 の発振器信号を生成するように構成された、C 1 に記載の装置。

[ C 7 ]

前記第 1 の発振器周波数は前記 LO 周波数の整数倍で、前記第 2 の発振器周波数は前記 LO 周波数の非整数倍である、C 6 に記載の装置。

[ C 8 ]

前記第 1 の発振器周波数は前記 LO 周波数の非整数倍で、前記第 2 の発振器周波数は前記 LO 周波数の整数倍である、C 6 に記載の装置。

20

[ C 9 ]

前記第 1 の周波数合成器は、前記受信機が有効にされる前に有効にされ、前記受信機が無効にされる時または後に無効にされ、前記第 2 の周波数合成器は、前記送信機が有効にされる前に有効にされ、前記送信機が無効にされる時または後に無効にされる、C 1 に記載の装置。

[ C 10 ]

前記第 1 および第 2 の周波数合成器は、前記受信機が有効にされる前に有効にされ、前記第 1 の周波数合成器は、前記受信機が無効にされる時または後に無効にされ、前記第 2 の周波数合成器は、前記送信機が無効にされる時または後に無効にされる、C 1 に記載の装置。

30

[ C 11 ]

前記第 1 および第 2 の周波数合成器は、前記送信機が有効にされる前に有効にされる、C 1 に記載の装置。

[ C 12 ]

前記第 1 および第 2 の周波数合成器の少なくとも 1 つは、データ・スロットのミッドアンブル内で有効にされ、変調のより低い速度が使用される、C 1 に記載の装置。

[ C 13 ]

前記第 1 および第 2 の周波数合成器は、前記受信機が有効にされる前に、有効にされ、前記受信機が無効にされる時または後に無効にされる、C 1 に記載の装置。

[ C 14 ]

前記第 1 および第 2 の周波数合成器は、前記送信機が有効にされる前に、有効にされ、前記第 1 および第 2 の周波数は、前記送信機が無効にされる時または後に無効にされる、C 1 に記載の装置。

40

[ C 15 ]

前記第 1 の周波数合成器は、前記受信機が有効にされる場合、ターゲット発信器周波数で前記第 1 の発振器信号を、および前記送信機が有効にされる場合、前記ターゲット発信器周波数からずれたものを生成するように構成された、C 1 に記載の装置。

[ C 16 ]

前記第 1 の周波数合成器は、位相同期ループ（PLL）を備え、前記ターゲット発信器周波数からの前記ずれは前記 PLL 内の周波数分周器比を変更することによって得られる

50

、C 1 5 に記載の装置。

[ C 1 7 ]

前記第2の周波数合成器は、前記送信機が有効にされる場合、ターゲット発信器周波数で前記第2の発振器信号を、および前記受信機が有効にされる場合、前記ターゲット発信器周波数からの中間のものを生成するように構成された、C 1 に記載の装置。

[ C 1 8 ]

局部発振器（L O）信号を生成するための方法であって、

第1の周波数合成器により第1の発振器周波数で第1の発振器信号を生成することと、

前記第1の発振器信号に基づき受信機のためにL O周波数で第1のL O信号を生成することと、

10

第2の周波数合成器により第2の発振器周波数で第2の発振器信号を生成し、ここにおいて、前記第2の発振器信号周波数は、時分割モードで動作している場合に前記第1の発振器周波数とは異なることと、

前記第2の発振器信号に基づき送信機のために前記L O周波数で第2のL O信号を生成することと、

を備える方法。

[ C 1 9 ]

前記時分割モードは、時分割複信（T D D）モードおよび時間分割同期コード分割多元接続（T D S C D M A）モードのいずれかである、C 1 8 に記載の方法。

[ C 2 0 ]

前記T D Dモードは、ロング・ターム・エボリューション（L T E）T D Dモードである、C 1 9 に記載の方法。

20

[ C 2 1 ]

T D Dモードの第1の時間間隔の間、前記受信機を有効にすることと、

T D Dモードの第2の時間間隔の間、前記送信機を有効にすることと、

をさらに備えるC 1 9 に記載の方法。

[ C 2 2 ]

前記第1の発振器周波数は前記L O周波数の整数倍で、前記第2の発振器周波数は前記L O周波数の非整数倍である、C 1 8 に記載の方法。

[ C 2 3 ]

前記第1の発振器周波数は前記L O周波数の非整数倍で、前記第2の発振器周波数は前記L O周波数の整数倍である、C 1 8 に記載の方法。

30

[ C 2 4 ]

前記受信機が有効にされる前に前記第1の周波数合成器を有効にすることと、

前記受信機が無効にされる時または後に前記第1の周波数合成器を無効にすることと、

前記送信機が有効にされる前に前記第2の周波数合成器を有効にすることと、

前記送信機が無効にされる時または後に前記第2の周波数合成器を無効にすることと、

をさらに備えるC 1 8 に記載の方法。

[ C 2 5 ]

前記受信機が有効にされる前に前記第1および第2の周波数合成器を有効にすることと、

前記受信機が無効にされる時または後に前記第1の周波数合成器を無効にすることと、

前記送信機が無効にされる時または後に前記第2の周波数合成器を無効にすることと、

をさらに備えるC 1 8 に記載の方法。

40

[ C 2 6 ]

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にすることを

さらに備えるC 1 8 に記載の方法。

[ C 2 7 ]

データ・スロットのミッドアンブル内で前記第1および第2の周波数合成器の少なくとも1つを有効にすることと、

50

変調のより低い速度を使用することと、

をさらに備える C 1 8 に記載の方法。

## [ C 2 8 ]

前記受信機が有効にされる前に前記第 1 および第 2 の周波数合成器を有効にすることと、

前記受信機が無効にされる時または後に前記第 1 および第 2 の周波数合成器を無効にす

ることと、

をさらに備える C 1 8 に記載の方法。

## [ C 2 9 ]

前記送信機が有効にされる前に前記第 1 および第 2 の周波数合成器を有効にすることと、

前記送信機が無効にされる時または後に前記第 1 および第 2 の周波数合成器を無効にす

ることと、

をさらに備える C 1 8 に記載の方法。

## [ C 3 0 ]

前記第 1 の発振器信号の生成は、

前記受信機が有効にされる場合、ターゲット発信器周波数で前記第 1 の発振器信号を生

成することと、

前記送信機が有効にされる場合、前記ターゲット発信器周波数からずれたところで前記

第 1 の発振器信号を生成することと、

を備える C 1 8 に記載の方法。

## [ C 3 1 ]

無線通信のための装置であって、

第 1 の発振器周波数で第 1 の発振器信号を生成するための手段と、

前記第 1 の発振器信号に基づき受信機のために LO 周波数で第 1 の局部発振器 (LO)

信号を生成するための手段と、

時分割モードで動作している場合に前記第 1 の発振器周波数とは異なる第 2 の発振器周

波数で第 2 の発振器信号を生成するための手段と、

前記第 2 の発振器信号に基づき送信機のために前記 LO 周波数で第 2 の LO 信号を生成

するための手段と、

を備える装置。

## [ C 3 2 ]

前記時分割モードは、時分割複信 (TDD) モードおよび時間分割同期コード分割多元

接続 (TD SCDMA) モードのいずれかである、C 3 1 に記載の装置。

## [ C 3 3 ]

前記 TDD モードは、ロング・ターム・エボリューション (LTE) TDD モードであ

る、C 3 2 に記載の装置。

## [ C 3 4 ]

TDD モードの第 1 の時間間隔の間、前記受信機を有効にするための手段と、

TDD モードの第 2 の時間間隔の間、前記送信機を有効にするための手段と、

をさらに備える C 3 2 に記載の装置。

## [ C 3 5 ]

前記第 1 の発振器周波数は前記 LO 周波数の整数倍で、前記第 2 の発振器周波数は前記

LO 周波数の非整数倍である、C 3 1 に記載の装置。

## [ C 3 6 ]

前記第 1 の発振器周波数は前記 LO 周波数の非整数倍で、前記第 2 の発振器周波数は前

記 LO 周波数の整数倍である、C 3 1 に記載の装置。

## [ C 3 7 ]

前記受信機が有効にされる前に前記第 1 の発振器信号を生成するための前記手段を有効

にするための手段と、

10

20

30

40

50

前記受信機が無効にされる時または後に前記第1の発振器信号を生成するための前記手段を無効にするための手段と、

前記送信機が有効にされる前に前記第2の発振器信号を生成するための前記手段を有効にするための手段と、

前記送信機が無効にされる時または後に前記第2の発振器信号を生成するための前記手段を無効にするための手段と、

をさらに備えるC31に記載の装置。

[ C 3 8 ]

前記受信機が有効にされる前に前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段を有効にするための手段と、

10

前記受信機が無効にされる時または後に前記第1の発振器信号を生成するための前記手段を無効にするための手段と、

前記送信機が無効にされる時または後に前記第2の発振器信号を生成するための前記手段を無効にするための手段と、

をさらに備えるC31に記載の装置。

[ C 3 9 ]

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にするための手段をさらに備えるC31に記載の装置。

[ C 4 0 ]

データ・スロットのミッドアンプル内で前記第1および第2の周波数合成器の少なくとも1つを有効にするための手段と、

20

変調のより低い速度を使用するための手段と、

をさらに備えるC31に記載の装置。

[ C 4 1 ]

前記受信機が有効にされる前に前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段を有効にするための手段と、

前記受信機が無効にされる時または後に前記第1の発振器信号を生成するための前記手段および前記第2の発振器信号を生成するための前記手段を無効にするための手段と、

をさらに備えるC31に記載の装置。

[ C 4 2 ]

30

前記送信機が有効にされる前に前記第1および第2の周波数合成器を有効にするための手段と、

前記送信機が無効にされる時または後に前記第1および第2の周波数を無効にするための手段と、

をさらに備えるC31に記載の装置。

[ C 4 3 ]

前記第1の発振器信号を生成するための前記手段は、

前記受信機が有効にされる場合、ターゲット発信器周波数で前記第1の発振器信号を生成するための手段と、

前記送信機が有効にされる場合、前記ターゲット発信器周波数からずれたところで前記第1の発振器信号を生成するための手段と、

40

を備えるC31に記載の装置。

[ C 4 4 ]

コンピュータ・プログラム製品であって、

非一時的コンピュータ読取可能な媒体で、

少なくとも1つのプロセッサーが第1の周波数合成器により第1の発振器周波数で第1の発振器信号の生成を誘導するためのコードで、前記第1の発振器信号は受信機のためのLO周波数で第1の局部発振器（LO）信号を生成するために使用されるコードと、

少なくとも1つのプロセッサーが第2の周波数合成器により第2の発振器周波数で第2の発振器信号の生成を誘導するためのコードで、前記第2の発振器信号は送信機のための

50

L O 周波数で第 2 の L O 信号を生成するために使用され、ここにおいて、前記第 2 の発振器信号周波数は、時分割モードで動作している場合、前記第 1 の発振器周波数とは異なるコードと、

を備える非一時的コンピュータ読取可能な媒体を備えるコンピュータ・プログラム製品。

[ C 4 5 ]

前記時分割モードは、時分割複信（T D D）モードおよび時間分割同期コード分割多元接続（T D S C D M A）モードのいずれかである、C 4 4 に記載のコンピュータ・プログラム製品。

[ C 4 6 ]

T D D モードの第 1 の時間間隔の間、少なくとも 1 つのプロセッサーに前記受信機を有効にさせるためのコードと、

T D D モードの第 2 の時間間隔の間、少なくとも 1 つのプロセッサーに前記送信機を有効にさせるためのコードと、

をさらに備える C 4 5 に記載のコンピュータ・プログラム製品。

[ C 4 7 ]

前記 T D D モードは、ロング・ターム・エボリューション（L T E）T D D モードである、C 4 5 に記載のコンピュータ・プログラム製品。

[ C 4 8 ]

前記受信機が有効にされる前に、少なくとも 1 つのプロセッサーに前記第 1 の周波数合成器を有効にさせるためのコードと、

前記受信機が無効にされる時または後に、少なくとも 1 つのプロセッサーに前記第 1 の周波数合成器を無効にさせるためのコードと、

前記送信機が有効にされる前に、少なくとも 1 つのプロセッサーに前記第 2 の周波数合成器を有効にさせるためのコードと、

前記送信機が無効にされる時または後に、少なくとも 1 つのプロセッサーに前記第 2 の周波数合成器を無効にさせるためのコードと、

をさらに備える C 4 4 に記載のコンピュータ・プログラム製品。

[ C 4 9 ]

前記送信機が有効にされる前に、少なくとも 1 つのプロセッサーに前記第 1 および第 2 の周波数合成器を有効にさせるためのコードをさらに備える C 4 4 に記載の装置。

[ C 5 0 ]

少なくとも 1 つのプロセッサーにデータ・スロットのミッドアンブル内で前記第 1 および第 2 の周波数合成器の少なくとも 1 つを有効にさせるためのコードと、

少なくとも 1 つのプロセッサーに変調のより低い速度を使用させるためのコードと、

をさらに備える C 4 4 に記載の装置。

[ C 5 1 ]

前記送信機が有効にされる前に、少なくとも 1 つのプロセッサーに前記第 1 および第 2 の周波数合成器を有効にさせるためのコードと、

前記送信機が無効にされる時または後に、少なくとも 1 つのプロセッサーに前記第 1 および第 2 の周波数を無効にさせるためのコードと、

をさらに備える C 4 4 に記載の装置。

10

20

30

40

【図1】

図1

FIG. 1

【図2】

図2

FIG. 2

【図3】

図3

FIG. 3

【図4】

図4

FIG. 4

【図5】

FIG. 5

【図 6 A】

FIG. 6A

【図 6 B】

EIG 6B

【図 7 A】

FIG. 7A

【図 7B】

図 7B

FIG. 7B

【図 7C】

図 7C

FIG. 7C

【図 7D】

図 7D

FIG. 7D

【図 8】

図 8

FIG. 8

---

フロントページの続き

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(72)発明者 ナラソング、チューチャーン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 レウン、ライ・カン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775

(72)発明者 ラウ、ソン - セン

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775

(72)発明者 パテル、シュレニク

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドラ

イブ 5775

審査官 石川 雄太郎

(56)参考文献 特表2015-508982(JP,A)

米国特許出願公開第2012/0263215(US,A1)

米国特許出願公開第2005/0078615(US,A1)

米国特許出願公開第2005/0239417(US,A1)

(58)調査した分野(Int.Cl., DB名)

H04B 1 / 50