(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5517725号

(P5517725)

(45) 発行日 平成26年6月11日(2014.6.11)

(24) 登録日 平成26年4月11日(2014.4.11)

(51) Int.Cl.

HO3F 3/45 (2006.01)

F 1

HO3F 3/45

Z

請求項の数 5 (全 17 頁)

(21) 出願番号 特願2010-99067 (P2010-99067)

(22) 出願日 平成22年4月22日 (2010.4.22)

(65) 公開番号 特開2010-288266 (P2010-288266A)

(43) 公開日 平成22年12月24日 (2010.12.24)

審査請求日 平成25年4月19日 (2013.4.19)

(31) 優先権主張番号 特願2009-119076 (P2009-119076)

(32) 優先日 平成21年5月15日 (2009.5.15)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】全差動増幅回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入力差動対を成す第1の入力信号及び第2の入力信号を差動増幅して、対を成す第1の中間信号及び第2の中間信号を生成する差動増幅部と、

前記第1の中間信号を増幅して第1の出力信号を生成する第1のA B級増幅部と、

前記第2の中間信号を増幅して第2の出力信号を生成する第2のA B級増幅部とを備え、

前記差動増幅部は、前記第1の入力信号を受ける第1の入力トランジスタと、前記第2の入力信号を受ける第2の入力トランジスタと、前記第1の入力トランジスタと直列に接続された第1の負荷素子と、前記第2の入力トランジスタと直列に接続された第2の負荷素子と、前記第1の入力トランジスタおよび前記第2の入力トランジスタに対して共通に設けられた電流源とを含み、

10

前記第1の出力信号及び前記第2の出力信号は、出力差動対を成し、

前記第1のA B級増幅部は、前記第1の出力信号及び前記第2の出力信号のコモンモード成分である第1のフィードバック信号によって調整された基準電圧と前記第1の中間信号との差分がゲートに入力される第1のトランジスタを含み、前記第1のフィードバック信号によって調整された前記基準電圧を基準として前記第1の中間信号を増幅し、

前記第2のA B級増幅部は、前記第1の出力信号及び前記第2の出力信号のコモンモード成分である第2のフィードバック信号によって調整された基準電圧と前記第2の中間信号との差分がゲートに入力される第2のトランジスタを含み、前記第2のフィードバック

20

信号によって調整された前記基準電圧を基準として前記第2の中間信号を増幅する、ことを特徴とする全差動増幅回路。

【請求項2】

入力差動対を成す第1の入力信号及び第2の入力信号を差動増幅して、対を成す第1の中間信号及び第2の中間信号を生成する差動増幅部と、

前記第1の中間信号を増幅して第1の出力信号を生成する第1のA B級増幅部と、

前記第2の中間信号を増幅して第2の出力信号を生成する第2のA B級増幅部とを備え、

前記第1の出力信号及び前記第2の出力信号は、出力差動対を成し、

前記第1のA B級増幅部は、前記第1の出力信号及び前記第2の出力信号のコモンモード成分である第1のフィードバック信号によって調整された基準電圧を基準として前記第1の中間信号を増幅し、

前記第2のA B級増幅部は、前記第1の出力信号及び前記第2の出力信号のコモンモード成分である第2のフィードバック信号によって調整された基準電圧を基準として前記第2の中間信号を増幅し、

前記第1のA B級増幅部は、

ソースが電源電位に接続され、ドレインから前記第1の出力信号を出力する第1のPMOSトランジスタと、

ソースがグランド電位に接続され、ドレインが前記第1のPMOSトランジスタのドレインに接続された第1のNMOSトランジスタと、

第1の基準信号に対する前記第1の中間信号の差分である第1の信号を前記第1のPMOSトランジスタのゲートへ伝達する第1の伝達部と、

第2の基準信号に対する前記第1の中間信号の差分である第2の信号を前記第1のNMOSトランジスタのゲートへ伝達する第2の伝達部と、

前記第1の出力信号及び前記第2の出力信号を受けて、前記第1のフィードバック信号を用いて前記第1の基準信号又は前記第2の基準信号を調整する第1の調整部とを含み、

前記第2のA B級増幅部は、

ソースが電源電位に接続され、ドレインから前記第2の出力信号を出力する第2のPMOSトランジスタと、

ソースがグランド電位に接続され、ドレインが前記第2のPMOSトランジスタのドレインに接続された第2のNMOSトランジスタと、

第3の基準信号に対する前記第2の中間信号の差分である第3の信号を前記第2のPMOSトランジスタのゲートへ伝達する第3の伝達部と、

第4の基準信号に対する前記第2の中間信号の差分である第4の信号を前記第2のNMOSトランジスタのゲートへ伝達する第4の伝達部と、

前記第1の出力信号及び前記第2の出力信号を受けて、前記第2のフィードバック信号を用いて前記第3の基準信号又は前記第4の基準信号を調整する第2の調整部とを含む、ことを特徴とする全差動増幅回路。

【請求項3】

前記第1の調整部は、

前記第1の出力信号を一端で受ける第1のコンデンサと、

前記第2の出力信号を一端で受ける第2のコンデンサと、

を含み、

前記第1のコンデンサの他端と前記第2のコンデンサの他端とは、互いに接続されるとともに前記第1の基準信号又は前記第2の基準信号が保持されるべきノードに接続されており、

前記第2の調整部は、

前記第1の出力信号を一端で受ける第3のコンデンサと、

前記第2の出力信号を一端で受ける第4のコンデンサと、

を含み、

10

20

30

40

50

前記第3のコンデンサの他端と前記第4のコンデンサの他端とは、互いに接続されるとともに前記第3の基準信号又は前記第4の基準信号が保持されるべきノードに接続されている

ことを特徴とする請求項2に記載の全差動增幅回路。

【請求項4】

前記第1の調整部は、

前記第1の中間信号をサンプリングする期間に前記第1のコンデンサと並列に接続される第5のコンデンサと、

前記第1の中間信号をサンプリングする期間に前記第2のコンデンサと並列に接続される第6のコンデンサとを含み、

前記第5のコンデンサの一端と前記第6のコンデンサの一端とは、互いに接続されるとともに、前記第1の中間信号をホールドする期間に、前記第1の基準信号が供給されるノード又は前記第2の基準信号が供給されるノードに接続されて、

前記第5のコンデンサの他端と前記第6のコンデンサの他端とは、前記第1の中間信号をホールドする期間に前記第1の出力信号及び前記第2の出力信号のコモンレベルを目標値にするために設定されるコモンレベル基準信号に接続され、

前記第2の調整部は、

前記第2の中間信号をサンプリングする期間に前記第3のコンデンサと並列に接続される第7のコンデンサと、

前記第2の中間信号をサンプリングする期間に前記第4のコンデンサと並列に接続される第8のコンデンサとを含み、

前記第7のコンデンサの一端と前記第8のコンデンサの一端とは、互いに接続されるとともに、前記第2の中間信号をホールドする期間に、前記第3の基準信号が供給されるノード又は前記第4の基準信号が供給されるノードに接続され、

前記第7のコンデンサの他端と前記第8のコンデンサの他端とは、前記第2の中間信号をホールドする期間に前記コモンレベル基準信号に接続されていることを特徴とする請求項3に記載の全差動增幅回路。

【請求項5】

前記第1の調整部は、

前記第1の中間信号をホールドする期間に前記第1のコンデンサと並列に接続される第5のコンデンサと、

前記第1の中間信号をホールドする期間に前記第2のコンデンサと並列に接続される第6のコンデンサとを含み、

前記第5のコンデンサの一端と前記第6のコンデンサの一端とは、互いに接続されるとともに、前記第1の中間信号をサンプリングする期間に、前記第1の基準信号が供給されるノード又は前記第2の基準信号が供給されるノードに接続され、

前記第5のコンデンサの他端と前記第6のコンデンサの他端とは、前記第1の中間信号をサンプリングする期間に、前記第1の出力信号及び前記第2の出力信号のコモンレベルを目標値にするために設定されるコモンレベル基準信号に接続され、

前記第2の調整部は、

前記第2の中間信号をホールドする期間に前記第3のコンデンサと並列に接続される第7のコンデンサと、

前記第2の中間信号をホールドする期間に前記第4のコンデンサと並列に接続される第8のコンデンサとを含み、

前記第7のコンデンサの一端と前記第8のコンデンサの一端とは、互いに接続されるとともに、前記第2の中間信号をサンプリングする期間に、前記第3の基準信号が供給されるノード又は前記第4の基準信号が供給されるノードに接続され、

前記第7のコンデンサの他端と前記第8のコンデンサの他端とは、前記第2の中間信号をサンプリングする期間に前記コモンレベル基準信号に接続されていることを特徴とする請求項3に記載の全差動增幅回路。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、全差動増幅回路に関する。

**【背景技術】****【0002】**

S / H のようなスイッチトキャパシタ回路に適用する 2 段増幅構成の広帯域全差動アンプにおいて、1 段目を高いカットオフ周波数を持つ A 級アンプとし、2 段目をソース接地 A B 級アンプとすることで、位相補償を不要とし低消費電力化することが可能である。

**【0003】**

10

さらに、2 段目のソース接地 A B 級アンプのバイアス回路を、連続時間動作型ではなくクロック動作するダイナミックバイアス回路で構成すると、回路の簡素化が可能となりさらなる低消費電力化が見込まれる（非特許文献 1 参照）。

**【0004】**

全差動アンプでは、出力同相電位を信号コモンモード電圧（以下 V cm ）など所望の基準信号に設定する必要がある。この機能は、全出力信号の同相成分を検出し、検出結果と V cm との差に応じて、全差動アンプにフィードバック信号を提供するコモンモードフィードバック回路（以下 CMFB 回路）で実現する。

**【0005】**

20

特許文献 1 の図 1 には、差動増幅器 20 において、同相モード・フィードバック回路 50 が差動部 30 の複数の出力信号の同相成分を検出し、検出した差に比例したフィードバック信号を差動部 30 へ帰還することが記載されている。これにより、特許文献 1 によれば、同相モード電圧が所定の基準電圧からドリフトするのを防止できるとされている。

**【先行技術文献】****【特許文献】****【0006】**

【特許文献 1】特開平 6 - 29761 号公報

**【非特許文献】****【0007】**

【非特許文献 1】「A 14b 74MS/s CMOS AFE for True High-Definition Camcorders」(2006 ISSCC)

30

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

特許文献 1 に記載された差動増幅器では、同相モード・フィードバック回路 50 がフィードバック信号を帰還する先が差動部 30 であるため、フィードバック信号を反転するための反転アンプ 54 が別途必要となり、消費電力が増大する可能性がある。また、同相モード・フィードバック回路 50 における経路に 3 つの位相遅れ要因（3 組の容量素子及び抵抗素子）が存在することにより、フィードバック動作の安定性を満たすための設計負荷が増大するとともに消費電力が増大する可能性がある。加えて、1 段目の増幅器のフリッカノイズを除去する場合にはオートゼロ技術が必要となるが、安定性確保の為に消費電力の増大を伴う。

40

**【0009】**

本発明の目的は、全差動増幅回路において、コモンモードフィードバック動作を行う際における消費電力を低減することにある。或いは、本発明の目的は、オートゼロ技術を用いずに 1 段目の増幅器のフリッカノイズを除去することで、ノイズ除去の際の消費電力を低減することにある。

**【課題を解決するための手段】****【0010】**

本発明の 1 つの側面に係る全差動増幅回路は、入力差動対を成す第 1 の入力信号及び第

50

2 の入力信号を差動増幅して、対を成す第 1 の中間信号及び第 2 の中間信号を生成する差動増幅部と、前記第 1 の中間信号を増幅して第 1 の出力信号を生成する第 1 の A B 級増幅部と、前記第 2 の中間信号を増幅して第 2 の出力信号を生成する第 2 の A B 級増幅部とを備え、前記差動増幅部は、前記第 1 の入力信号を受ける第 1 の入力トランジスタと、前記第 2 の入力信号を受ける第 2 の入力トランジスタと、前記第 1 の入力トランジスタと直列に接続された第 1 の負荷素子と、前記第 2 の入力トランジスタと直列に接続された第 2 の負荷素子と、前記第 1 の入力トランジスタおよび前記第 2 の入力トランジスタに対して共通に設けられた電流源とを含み、前記第 1 の出力信号及び前記第 2 の出力信号は、出力差動対を成し、前記第 1 の A B 級増幅部は、前記第 1 の出力信号及び前記第 2 の出力信号のコモンモード成分である第 1 のフィードバック信号によって調整された基準電圧と前記第 1 の中間信号との差分がゲートに入力される第 1 のトランジスタを含み、前記第 1 のフィードバック信号によって調整された前記基準電圧を基準として前記第 1 の中間信号を増幅し、前記第 2 の A B 級増幅部は、前記第 1 の出力信号及び前記第 2 の出力信号のコモンモード成分である第 2 のフィードバック信号によって調整された基準電圧と前記第 1 の中間信号との差分がゲートに入力される第 1 のトランジスタを含み、前記第 1 のフィードバック信号によって調整された前記基準電圧を基準として前記第 2 の中間信号を増幅する。

**【発明の効果】**

**【0011】**

本発明によれば、全差動増幅回路において、コモンモードフィードバック動作を行う際における消費電力を低減することができる。或いは、オートゼロ技術を用いずに 1 段目の増幅器のフリッカノイズを除去することで、ノイズ除去の際の消費電力を低減することができる。

**【図面の簡単な説明】**

**【0012】**

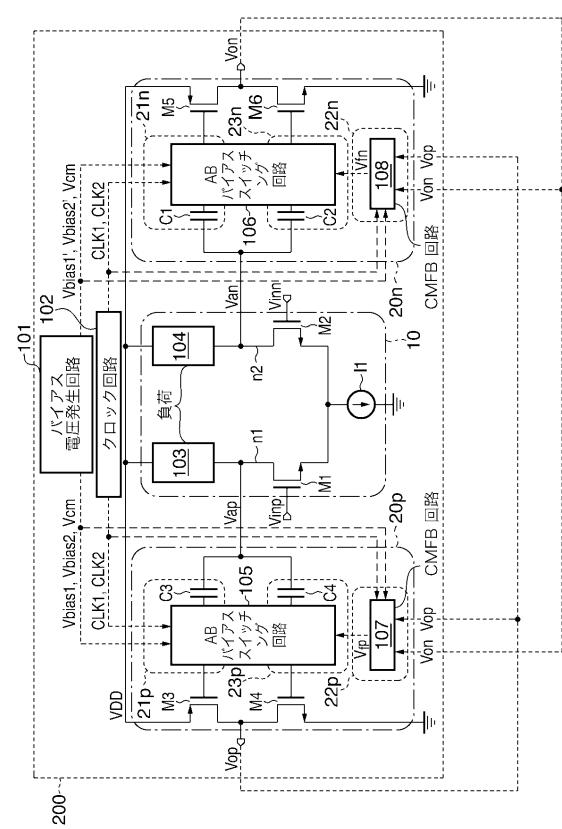

【図 1】本発明の実施形態に係る全差動増幅回路 200 の構成を示す図。

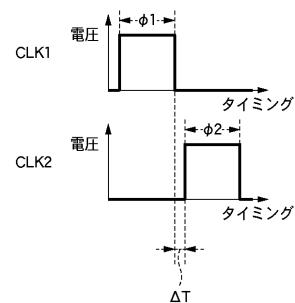

【図 2】本発明の実施形態におけるクロック信号の波形を示すタイミングチャート。

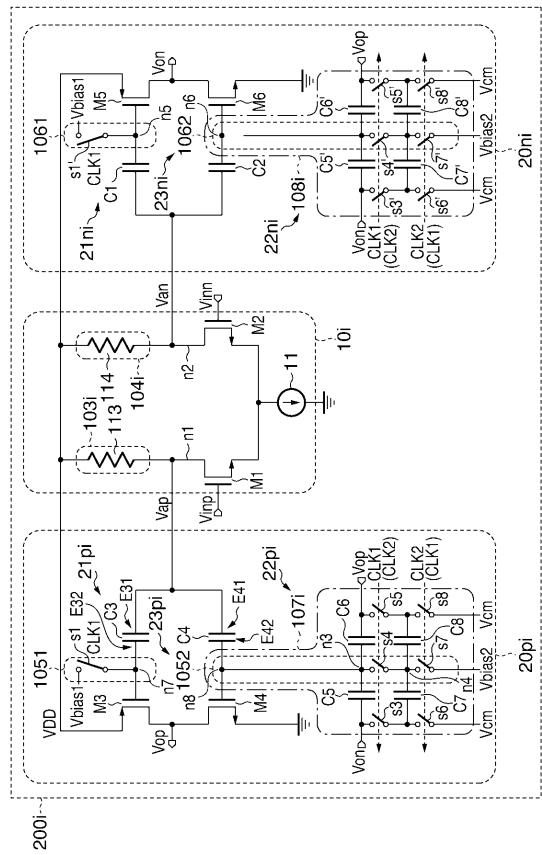

【図 3】本発明の第 1 実施例に係る全差動増幅回路 200i の回路構成例を示す図。

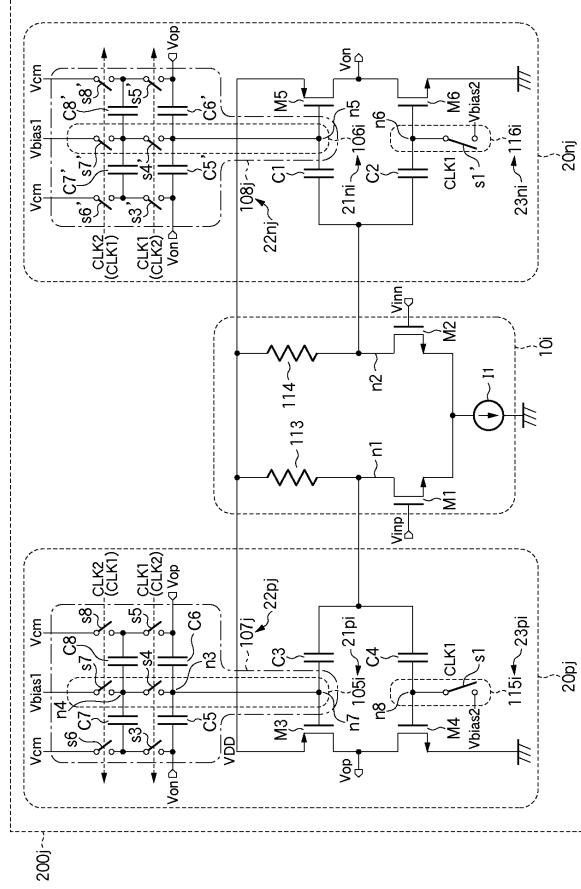

【図 4】本発明の第 2 実施例に係る全差動増幅回路 200j の回路構成例を示す図。

【図 5】本発明の実施形態に係る全差動増幅回路 200 を適用した S / H アプリケーションの回路図。

**【発明を実施するための形態】**

**【0013】**

本発明の実施形態に係る全差動増幅回路 200 を、図 1、3 を用いて説明する。図 1 は、本発明の実施形態に係る全差動増幅回路 200 の構成を示す図である。図 3 は、全差動増幅回路 200 を具体化した第 1 実施例の全差動増幅回路 200i の構成を示す図である。

**【0014】**

全差動増幅回路 200 は、2 段増幅型の増幅回路である。全差動増幅回路 200 は、入力差動対を成す 2 つの入力信号（第 1 の入力信号、第 2 の入力信号） $V_{in\,p}$ 、 $V_{in\,n}$  を受けて、出力差動対を成す 2 つの出力信号（第 1 の出力信号、第 2 の出力信号） $V_{o\,p}$ 、 $V_{o\,n}$  を出力する。全差動増幅回路 200 は、クロック回路 102、バイアス電圧発生回路（供給部）101、差動増幅部 10、及び 2 つの A B 級増幅部 20p, 20n を備える。

**【0015】**

クロック回路 102 は、2 つの A B 級増幅部 20p, 20n のそれぞれへ、第 1 のクロック信号 C L K 1 及び第 2 のクロック信号 C L K 2 を供給する。全差動増幅回路 200 が S / H 等の離散時間信号処理に適用される事を前提としているので、クロック回路 102 は、後述する図 2 に示す第 1 のクロック信号 C L K 1 と第 2 のクロック信号 C L K 2 とのような 2 相ノンオーバーラップクロックを発生する。第 1 のクロック信号 C L K 1 が H レベルになる期間 1 と第 2 のクロック信号 C L K 2 が H レベルになる期間 2 とは、互い

10

20

30

40

50

に重ならず、ノンオーバーラップ期間  $T$  の間隔を有する。

【0016】

バイアス電圧発生回路 101 は、2つのAB級増幅部 20p, 20n のそれぞれへバイアス電圧を供給する。バイアス電圧発生回路 101 が output するバイアス電圧は、第1のバイアス電圧  $V_{bias1}$ 、第2バイアス電圧  $V_{bias2}$ 、第3のバイアス電圧  $V_{bias1}'$ 、第4のバイアス電圧  $V_{bias2}'$ 、及びコモンレベル基準信号（同相電圧） $V_{cm}$ を含みうる。第1のバイアス電圧  $V_{bias1}$  及び第2のバイアス電圧  $V_{bias2}$  は、AB級増幅部 20p におけるAB級バイアスに必要な電圧である。第3のバイアス電圧  $V_{bias1}'$  及び第4のバイアス電圧  $V_{bias2}'$  は、AB級増幅部 20n におけるAB級バイアスに必要な電圧である。第1のバイアス電圧  $V_{bias1}$  と第3のバイアス電圧  $V_{bias1}'$  とは同一の電圧でありうる。第2のバイアス電圧  $V_{bias2}$  と第4のバイアス電圧  $V_{bias2}'$  とは同一の信号でありうる。コモンレベル基準信号  $V_{cm}$  は、コモンモードフィードバック（以下、CMFB）動作に必要な電圧である。

10

【0017】

差動増幅部 10 は、1段目の増幅を行う。差動増幅部 10 は、対を成す2つの入力信号  $V_{inp}, V_{inn}$  の差動増幅を行う。これにより、差動増幅部 10 は、対を成す2つの中間信号（第1の中間信号、第2の中間信号） $V_{ap}, V_{an}$  を生成して出力する。差動増幅部 10 は、中間信号  $V_{ap}$  をAB級増幅部 20p へ出力し、中間信号  $V_{an}$  をAB級増幅部 20n へ出力する。差動増幅部 10 は、入力トランジスタ M1、入力トランジスタ M2、負荷素子 103、負荷素子 104、及び電流源 I1 を含む。

20

【0018】

AB級増幅部（第1のAB級増幅部）20p は、中間信号  $V_{ap}$  を増幅する。AB級増幅部 20p は、第1の出力信号  $V_{op}$  及び第2の出力信号  $V_{on}$  のコモンモード成分であるフィードバック信号（第1のフィードバック信号） $V_{fp}$  によって調整された基準電圧を基準として中間信号  $V_{ap}$  を増幅する。具体的には、AB級増幅部 20p は、中間信号  $V_{ap}$  をサンプリングする期間に、フィードバック信号  $V_{fp}$  を用いて第1の基準信号又は第2の基準信号を調整する。そして、AB級増幅部 20p は、中間信号  $V_{ap}$  をホールドする期間に、第1の基準信号及び第2の基準信号を基準として中間信号  $V_{ap}$  を増幅する。これにより、AB級増幅部 20p は、出力信号  $V_{op}$  を生成して出力する。AB級増幅部 20p は、PMOSトランジスタ（第1のPMOSトランジスタ）M3、NMOSトランジスタ（第1のNMOSトランジスタ）M4、第1の伝達部 21p、第2の伝達部 23p、及び調整部（第1の調整部）22p を含む。

30

【0019】

PMOSトランジスタ M3 は、ソースが電源電位  $V_{DD}$  に接続され、ドレインがNMOSトランジスタ M4 のドレインに接続され、ゲートが第1の伝達部 21p に接続されている。PMOSトランジスタ M3 は、ドレインから出力信号  $V_{op}$  を出力する。

【0020】

NMOSトランジスタ M4 は、ソースがグランド電位に接続され、ドレインがPMOSトランジスタ M3 のドレインに接続され、ゲートが第2の伝達部 23p に接続されている。NMOSトランジスタ M4 は、PMOSトランジスタ M3 と共にドレインから出力信号  $V_{op}$  を出力する。

40

【0021】

第1の伝達部 21p は、第1のクロック信号  $C_{LK1}$  に同期して、第1の基準ノード n7（図3）に保持された第1の基準信号に対する中間信号  $V_{ap}$  の差分をとることにより第1の信号を生成してPMOSトランジスタ M3 のゲートへ伝達する。第1の伝達部 21p は、コンデンサ C3、及びAB級バイアススイッチング回路 105 の一部を含む。

【0022】

第2の伝達部 23p は、第1のクロック信号  $C_{LK1}$  に同期して、第2の基準ノード n8（図3）に保持された第2の基準信号に対する中間信号  $V_{ap}$  の差分をとることにより第2の信号を生成してNMOSトランジスタ M4 のゲートへ伝達する。第2の伝達部 23p は、コンデンサ C4、及びAB級バイアススイッチング回路 105 の一部を含む。

50

p は、コンデンサ C 4、及び A B 級バイアススイッチング回路 105 の他の一部を含む。

【 0023 】

第 1 の伝達部 21p 及び第 2 の伝達部 23p は、PMOS トランジスタ M3 及び NMOS トランジスタ M4 を A B 級バイアスする。これにより、低消費電力動作を実現する。A B 級バイアス手法は、例えば、次のようにして実現される。第 1 のクロック信号 CLK1 が H レベルの期間においてコンデンサ C3, C4 に適切な電荷がサンプリングされた後、第 1 のクロック信号 CLK1 が L レベルの期間においてコンデンサ C3, C4 がオフセット電圧源として動作する事によって実現される。

【 0024 】

調整部 22p は、第 1 のクロック信号 CLK1 及び第 2 のクロック信号 CLK2 の一方のクロック信号に同期して、フィードバック信号 Vfp を用いて第 1 の基準信号又は第 2 の基準信号を調整する。フィードバック信号 Vfp は、対を成す 2 つの出力信号 Vop, Von のコモンモード成分に応じた信号である。調整部 22p は、CMFB 回路 107 を含む。CMFB 回路 107 は、対を成す 2 つの出力信号 Von, Vop、コモンレベル基準信号 Vcm、第 1 のクロック信号 CLK1、及び第 2 のクロック信号 CLK2 を受ける。CMFB 回路 107 は、2 つの出力信号 Vop, Von のコモンモード成分を適正な値に保つようにフィードバック信号 Vfp を第 1 の基準ノード n7 又は第 2 の基準ノード n8 へ供給する。すなわち、CMFB 回路 107 は、第 1 のクロック信号 CLK1 又は第 2 のクロック信号 CLK2 に同期して、コモンレベル基準信号 Vcm に対する 2 つの出力信号 Vop, Von のコモンモード成分の差分をとることによりフィードバック信号 Vfp を生成する。CMFB 回路 107 は、生成したフィードバック信号 Vfp を第 1 の基準ノード n7 又は第 2 の基準ノード n8 へ供給することにより、PMOS トランジスタ又は NMOS トランジスタのゲートのバイアス電圧（基準信号）をコントロール（調整）する。

【 0025 】

図 3 に示すように、調整部 22p がフィードバック信号 Vfp を第 2 の基準ノード n8 へ供給する場合、第 1 の伝達部 21p 及び第 2 の伝達部 23p は次のような動作を行う。第 1 の基準ノード n7 には、第 1 のバイアス電圧 Vbias1 が第 1 基準信号として保持される。第 1 の伝達部 21p は、第 1 のクロック信号 CLK1 に同期して、第 1 の基準信号に対する中間信号 Vap の差分をとることにより第 1 の信号を生成して PMOS トランジスタ M3 のゲートへ伝達する。第 2 の基準ノード n8 には、第 2 の伝達部 23p により、第 2 のバイアス電圧 Vbias2 にフィードバック信号 Vfp を加算した電圧が第 2 の基準信号として保持される。即ち、第 2 の伝達部 23p は、調整前の第 2 の基準信号として第 2 のバイアス電圧 Vbias2 を受けて、第 2 のバイアス電圧 Vbias2 をフィードバック信号 Vfp によって調整し、調整された第 2 の基準信号を得る。第 2 の伝達部 23p は、その調整された第 2 の基準信号に対する中間信号 Vap の差分をとることにより第 2 の信号を生成する。第 2 の伝達部 23p は、生成した第 2 の信号を NMOS トランジスタ M4 のゲートへ伝達する。これにより、PMOS トランジスタ M3 及び NMOS トランジスタ M4 は、対を成す 2 つの出力信号 Vop, Von のコモンモード成分が基準値（コモンレベル基準信号 Vcm）になるように増幅動作を行うことにより、出力信号 Vop を生成して出力する。

【 0026 】

再び図 3 に注目して説明を行う。A B 級増幅部（第 2 の A B 級増幅部）20n は、中間信号 Van を増幅する。A B 級増幅部 20n は、第 1 の出力信号 Vop 及び第 2 の出力信号 Von のコモンモード成分であるフィードバック信号（第 2 のフィードバック信号）Vfn によって調整された基準電圧を基準として中間信号 Van を増幅する。具体的には、A B 級増幅部 20n は、中間信号 Van をサンプリングする期間に、フィードバック信号 Vfn を用いて第 3 の基準信号又は第 4 の基準信号を調整する。そして、A B 級増幅部 20n は、中間信号 Van をホールドする期間に、第 3 の基準信号及び第 4 の基準信号を基準として中間信号 Van を増幅する。これにより、A B 級増幅部 20n は、出力信号 Von を生成して出力する。A B 級増幅部 20n は、PMOS トランジスタ（第 2 の PMOS

10

20

30

40

50

トランジスタ) M 5、NMOSトランジスタ(第2のNMOSトランジスタ) M 6、第3の伝達部 21n、第4の伝達部 23n、及び調整部(第2の調整部) 22nを含む。

【0027】

PMOSトランジスタ M 5 は、ソースが電源電位 VDD に接続され、ドレインが NMOSトランジスタ M 6 のドレインに接続され、ゲートが第3の伝達部 21n に接続されている。PMOSトランジスタ M 5 は、ドレインから 2 つの出力信号の一方の出力信号 V<sub>on</sub> を出力する。

【0028】

NMOSトランジスタ M 6 は、ソースがグランド電位に接続され、ドレインが PMOSトランジスタ M 5 のドレインに接続され、ゲートが第4の伝達部 23n に接続されている。NMOSトランジスタ M 6 は、PMOSトランジスタ M 5 と共にドレインから出力信号 V<sub>on</sub> を出力する。

10

【0029】

第3の伝達部 21n は、第1のクロック信号 CLK1 に同期して、第3の基準ノード n 5 に保持された第3の基準信号に対する中間信号 V<sub>an</sub> の差分をとることにより第3の信号を生成して PMOSトランジスタ M 5 のゲートへ伝達する。第3の伝達部 21n は、コンデンサ C1、及び A B 級バイアスイッチング回路 106 の一部を含む。

【0030】

第4の伝達部 23n は、第1のクロック信号 CLK1 に同期して、第4の基準ノード n 6 に保持された第4の基準信号に対する中間信号 V<sub>an</sub> の差分をとることにより第4の信号を生成して NMOSトランジスタ M 6 のゲートへ伝達する。第4の伝達部 23n は、コンデンサ C2、及び A B 級バイアスイッチング回路 106 の他の一部を含む。

20

【0031】

第3の伝達部 21n 及び第4の伝達部 23n は、PMOSトランジスタ M 5 及び NMOSトランジスタ M 6 を A B 級バイアスする。これにより、低消費電力動作を実現する。A B 級バイアス手法は、例えば、次のようにして実現される。第1のクロック信号 CLK1 が H レベルの期間においてコンデンサ C1, C2 に適切な電荷がサンプリングされた後、第1のクロック信号 CLK1 が L レベルの期間においてコンデンサ C1, C2 がオフセット電圧源として動作する事によって実現される。

【0032】

30

調整部 22n は、第1のクロック信号 CLK1 及び第2のクロック信号 CLK2 の一方のクロック信号に同期して、フィードバック信号 V<sub>fn</sub> を用いて第3の基準信号又は第4の基準信号を調整する。フィードバック信号 V<sub>fn</sub> は、対を成す 2 つの出力信号 V<sub>on</sub>, V<sub>op</sub> のコモンモード成分に応じた信号である。調整部 22n は、CMFB回路 108 を含む。CMFB回路 108 は、対を成す 2 つの出力信号 V<sub>on</sub>, V<sub>op</sub>、コモンレベル基準信号 V<sub>cm</sub>、第1のクロック信号 CLK1、及び第2のクロック信号 CLK2 を受ける。CMFB回路 108 は、2 つの出力信号 V<sub>on</sub>, V<sub>op</sub> のコモンモード成分を適正な値に保つようにフィードバック信号 V<sub>fn</sub> を第3の基準ノード n 5 又は第4の基準ノード n 6 へ供給する。すなわち、CMFB回路 108 は、第1のクロック信号 CLK1 又は第2のクロック信号 CLK2 に同期して、コモンレベル基準信号 V<sub>cm</sub> に対する 2 つの出力信号 V<sub>op</sub>, V<sub>on</sub> のコモンモード成分の差分をとることによりフィードバック信号 V<sub>fn</sub> を生成する。CMFB回路 108 は、生成したフィードバック信号 V<sub>fn</sub> を第3の基準ノード n 5 又は第4の基準ノード n 6 へ供給することにより、PMOSトランジスタ又は NMOSトランジスタのゲートのバイアス電圧(基準信号)をコントロールする。

40

【0033】

図 3 に示すように、調整部 22n がフィードバック信号 V<sub>fn</sub> を第4の基準ノード n 6 へ供給する場合、第3の伝達部 21n 及び第4の伝達部 23n は次のような動作を行う。第3の基準ノード n 5 には、第3のバイアス電圧 V<sub>bias1</sub> が第3の基準信号として保持される。第3の伝達部 21n は、第1のクロック信号 CLK1 に同期して、第3の基準信号に対する中間信号 V<sub>an</sub> の差分をとることにより第3の信号を生成して PMOSト

50

ランジスタM5のゲートへ伝達する。第4の基準ノードn6には、第4の伝達部23nにより、第4のバイアス電圧Vbias2'にフィードバック信号Vfnを加算した電圧が第4の基準信号として保持される。即ち、第4の伝達部23nは、調整前の第4の基準信号として第4のバイアス電圧Vbias2'を受けて、第4のバイアス電圧Vbias2'をフィードバック信号Vfnによって調整し、調整された第4の基準信号を得る。第4の伝達部23nは、その第4の基準信号に対する中間信号Vanの差分をとることにより第4の信号を生成する。第4の伝達部23nは、生成した第4の信号をNMOSトランジスタM6のゲートへ伝達する。これにより、PMOSトランジスタM5及びNMOSトランジスタM6は、対を成す2つの出力信号Vop, Vonのコモンモード成分が基準値(コモンレベル基準信号Vcm)になるように増幅動作を行うことにより、出力信号Vonを生成して出力する。図3においては、対を成す2つの出力信号のコモンモード成分に応じたフィードバック信号を、第2の基準ノードn8および第4の基準ノードn6に帰還する例を示した。しかし、第2実施形態で説明するように、第1の基準ノードn7および第3の基準ノードn5に帰還しても良い。

#### 【0034】

このように、本実施形態では、対を成す2つの出力信号のコモンモード成分に応じたフィードバック信号を2つのAB級増幅部のそれぞれにおける2つの基準ノードの一方へ帰還することによって2つの基準信号の一方を調整する。第1の伝達部及び第3の伝達部は、それぞれ、2つの基準信号に対する中間信号の差分をとることにより第1の信号及び第3の信号を生成してPMOSトランジスタのゲートへ伝達する。また、第2の伝達部及び第4の伝達部のそれぞれは、それぞれ、2つの基準信号に対する中間信号の差分をとることにより第2の信号及び第4の信号を生成してNMOSトランジスタのゲートへ伝達する。これにより、フィードバック信号を帰還するために反転アンプを設ける必要がないので、消費電力を低減できる。

#### 【0035】

また、仮に、CMFBループ内に、位相遅れ要因である極が複数個発生すると、CMFB動作の安定性が損なわれる。それに対して、本実施形態では、極の発生は本質的に2段目(AB級増幅部)の出力ノードに限定されているので、安定性確保に要する消費電力を低減できる。

#### 【0036】

したがって、全差動増幅回路において、コモンモードフィードバック(CMFB)動作を行う際ににおける消費電力を低減することができる。

#### 【0037】

次に、本発明の実施形態に係る全差動増幅回路200の動作を、図2をさらに用いて説明する。図2は、本発明の実施形態におけるクロック信号の波形を示すタイミングチャートである。

#### 【0038】

第1のクロック信号CLK1がHレベルの期間T1において、コンデンサC1～C4に電荷がサンプリングされる。この際、入力トランジスタM1及び入力トランジスタM2で発生するフリッカノイズは、電圧出力となってノードn1及びノードn2に伝達される。

#### 【0039】

第2のクロック信号CLK2がHレベルの期間において、コンデンサC1～C4により電荷がホールドされる。これにより、コンデンサC1～C4がオフセット電圧源として動作し、PMOSトランジスタM3, M5及びNMOSトランジスタM4, M6が増幅動作を行う。期間T1の完了からノンオーバラップ期間T経過した後に始まる期間T2において、オフセット電圧源の電圧値は、このフリッカノイズを含んだ値となっている。

#### 【0040】

第1のクロック信号CLK1及び第2のクロック信号CLK2の周波数がフリッカノイズの存在する周波数帯域より高い値に設定されるため、フリッカノイズ電圧の期間T1から期間T2に至る間の変動は殆ど無い。従って、期間T2で増幅動作を行う際、期間T1

10

20

30

40

50

でオフセット電圧源に吸収された差動対（入力トランジスタM 1 及び入力トランジスタM 2）のフリッカノイズの殆どはトランジスタM 3～M 6に伝達されない。すなわち、一般的の増幅器で行われるようなオートゼロ技術は不要である。従って、安定性確保の為に消費電力増大を伴うネガティブフィードバックを掛けることなく、フリッカノイズを除去することができる。

#### 【0041】

次に、本発明の第1実施例に係る全差動増幅回路200iの回路構成例を、図3を用いて説明する。図3は、本発明の第1実施例に係る全差動増幅回路200iの回路構成例を示す図である。以下では、実施形態における具体化した部分を中心に説明する。なお、図3において、末尾にiを有する符号が付された構成要素は、図1において、当該符号からiを取り除いた符号が付された構成要素に対応する。また、図3において、'を有する符号が付された構成要素は、当該符号から'を取り除いた符号が付された構成要素と実質的に同一である。

10

#### 【0042】

全差動増幅回路200iは、差動増幅部10i、及び2つのAB級増幅部20pi, 20niを備える。差動増幅部10iは、負荷素子103i及び負荷素子104iを含む。負荷素子103iは、ノードn1の定常電圧を適切に決めるための素子であり、例えば、抵抗器113を含む。負荷素子104iは、ノードn2の定常電圧を適切に決めるための素子であり、例えば、抵抗器114を含む。

20

#### 【0043】

AB級増幅部20piは、第1の伝達部21pi、第2の伝達部23pi、及び調整部22piを含む。調整部22piは、フィードバック信号Vfpを第2の伝達部23piへフィードバックする。具体的には、第1の伝達部21piは、AB級バイアススイッチング回路105の一部を構成する第1の部分1051を含む。第1の部分1051は、第1のクロック信号CLK1がアクティブルーベルになると、第1の基準ノードn7へ第1のバイアス電圧Vbias1を第1の基準信号として供給する。このとき、コンデンサC3の基準電極E32は、第1の基準ノードn7を介して第1の基準信号としての第1のバイアス電圧Vbias1を受ける。次いで、コンデンサC3の基準電極E32には、第1のクロック信号CLK1がインアクティブルーベルになると、第1の基準信号としての第1のバイアス電圧Vbias1に対する中間信号Vapの差分である第1の信号が生成される。このとき、コンデンサC3の信号電極E31へは、中間信号Vapが供給されている。第1の信号は、PMOSトランジスタM3のゲートに供給される。ここで、第1の基準信号としての第1のバイアス電圧Vbias1は、PMOSトランジスタM3の定常時のドレイン電流を決定する電圧である。

30

#### 【0044】

第2の伝達部23piは、AB級バイアススイッチング回路105の一部を構成する第2の部分1052を含む。第2の部分1052は、第1のクロック信号CLK1がアクティブルーベルになると、コンデンサC7およびC8に保持された電荷がコンデンサC5およびC6に分配されることによって生じた電圧を第2の基準信号として供給する。コンデンサC4の基準電極E42は、第2の基準ノードn8を介して第2の基準信号を受ける。また、調整部22piは、第1のクロック信号CLK1がアクティブルーベルになると、第2の基準ノードn8へフィードバック信号Vfpを供給する。コンデンサC4の基準電極E42は、第2の基準ノードn8を介してフィードバック信号Vfpを受ける。よって、コンデンサC4の基準電極E42には、第1のクロック信号CLK1がアクティブルーベルになると、第2の基準信号にフィードバック信号Vfpが加算された信号である調整された第2の基準信号に対する中間信号Vapの差分である第2の信号が生成される。このとき、コンデンサC4の信号電極E41へは、中間信号Vapが供給されている。第2の信号は、NMOSトランジスタM4のゲートに供給される。第2のバイアス電圧Vbias2は、NMOSトランジスタM4の定常時のドレイン電流を決定する電圧である。

40

#### 【0045】

50

以下、さらに具体的に説明する。第1の部分1051は、スイッチs1を含む。スイッチs1は、第1のクロックCLK1がHレベル(アクティブルベル)の期間(サンプリング期間)にオンすることにより、第1のバイアス電圧Vbias1を第1の基準信号として第1の基準ノードn7へ供給する。これにより、コンデンサC3は、第1の基準信号としての第1のバイアス電圧Vbias1を基準とした中間信号Vapをサンプリングする。その後、第1のクロックCLK1がLレベルの期間(ホールド期間)では、スイッチs1にオフする。これにより、コンデンサC3は、第1の基準信号としての第1のバイアス電圧Vbias1に対する中間信号Vapの差分である第1の信号を生成して保持するとともにPMOSトランジスタM3のゲートへ伝達する。

## 【0046】

10

スイッチs7は、第2のクロックCLK2がHレベル(アクティブルベル)の期間にオンすることにより、第2のバイアス電圧Vbias2を調整前の第2の基準信号としてノードn4へ供給する。これにより、ノードn4の電圧は、第2のバイアス電圧Vbias2になる。その後、スイッチs7は、第2のクロックCLK2がLレベルになるとオフする。これにより、ノードn4は、調整前の第2の基準信号としての第2のバイアス電圧Vbias2を保持する。

## 【0047】

スイッチs4は、第1のクロックCLK1がHレベルの期間(サンプリングする期間)にオンすることにより、ノードn4に保持された調整前の第2の基準信号をノードn3を介して第2の基準ノードn8へ供給する。また、調整部22piは、CMFB回路107iを含む。CMFB回路107iは、第1のクロック信号CLK1に同期して、調整された第2の基準信号を第2の基準ノードn8へ供給する。これにより、コンデンサC4は、信号(Vbias2 + Vfp)を基準とした中間信号Vapをサンプリングする。その後、第1のクロック信号CLK1がLレベルの期間(ホールド期間)では、スイッチs4がオフする。これにより、コンデンサC4は、信号(Vbias2 + Vfp)に対する中間信号Vapの差分である第2の信号を生成して保持するとともにNMOSトランジスタM4のゲートへ伝達する。

20

## 【0048】

具体的には、CMFB回路107iは、第1のコンデンサC6、第2のコンデンサC5、第5のコンデンサC8、第6のコンデンサC7を含む。CMFB回路107iは、第2のスイッチ群(s6、s8)、及び第1のスイッチ群(s3、s5)を含む。図3に示すように、第5のコンデンサC8は、サンプリング期間(CLK1がHになる期間)において、スイッチs4、s5を介して第1のコンデンサC6と並列に接続される。第6のコンデンサC7は、サンプリング期間において、スイッチs3、s4を介して第2のコンデンサC5と並列に接続される。第5のコンデンサC8の一端と第6のコンデンサC7の一端とは、互いに接続されるとともにホールド期間(CLK2がHになる期間)においてスイッチs7を介して第2のバイアス電圧Vbias2に接続されている。第5のコンデンサC8の他端と第6のコンデンサC7の他端とには、ホールド期間は、スイッチs6、s8を介してコモンレベル基準信号Vcmが供給される。コモンレベル基準信号Vcmは、第1の出力信号Vop及び第2の出力信号Vonのコモンレベルを目標値にするためにバイアス電圧発生回路101によって設定される信号である。CMFB回路108iにおいては、CMFB回路107iにおける第1、第2、第5および第6のコンデンサが、第3のコンデンサC6'、第4のコンデンサC5'、第7のコンデンサC8'および第8のコンデンサC7'に置き換わる。

30

## 【0049】

40

第1のコンデンサC6は、対を成す2つの出力信号Vop、Vonにおける第1の出力信号Vopを一端で受ける。第1のコンデンサC6は、その一端がスイッチs5に接続されている。第2のコンデンサC5は、対を成す2つの出力信号Vop、Vonにおける第2の出力信号Vonを一端で受ける。第2のコンデンサC5は、その一端がスイッチs3に接続されている。第1のコンデンサC6の他端と第2のコンデンサC5の他端とは、ノ

50

ード n 3 で互いに接続されるとともに、ノード n 3 を介して第 2 の基準ノード n 8 に接続されている。

【 0 0 5 0 】

第 5 のコンデンサ C 8 は、その一端がスイッチ s 5 及びスイッチ s 8 に接続されている。第 6 のコンデンサ C 7 は、その一端がスイッチ s 3 及びスイッチ s 6 に接続されている。第 5 のコンデンサ C 8 の他端と第 6 のコンデンサ C 7 の他端とは、ノード n 4 で互いに接続されるとともに、ノード n 4 を介してスイッチ s 4 及びスイッチ s 7 に接続されている。

【 0 0 5 1 】

第 2 のスイッチ群 ( s 6, s 8 ) は、第 2 のクロック信号 C L K 2 に同期して、第 5 のコンデンサ C 8 の一端及び第 6 のコンデンサ C 7 の一端をバイアス電圧発生回路 101 ( 図 1 参照 ) へ接続する。これにより、第 5 のコンデンサ C 8 の一端及び第 6 のコンデンサ C 7 の一端には、それぞれ、 C M F B 動作の基準信号となるコモンレベル基準信号 V c m が供給される。

10

【 0 0 5 2 】

第 1 のスイッチ群 ( s 3, s 5 ) は、第 1 のクロック信号 C L K 1 に同期して、第 1 のコンデンサ C 6 の一端を第 5 のコンデンサ C 8 の一端へ接続するとともに、第 2 のコンデンサ C 5 の一端を第 6 のコンデンサ C 7 の一端へ接続する。これにより、第 1 のコンデンサ C 6 の一端及び第 2 のコンデンサ C 5 の一端には、それぞれ、コモンレベル基準信号 V c m が伝達される。この結果、第 1 のコンデンサ C 6 及び第 2 のコンデンサ C 5 は、コモンレベル基準信号 V c m に対する対を成す 2 つの出力信号 V o p, V o n のコモンモード成分の差分であるフィードバック信号 V f p を生成してノード n 3 へ供給する。

20

【 0 0 5 3 】

なお、 A B 級增幅部 20 n i の構成は A B 級增幅部 20 p i の構成と同様であるので、 A B 級增幅部 20 n i についての説明を省略する。

【 0 0 5 4 】

また、図 3 に括弧で示されるように、第 1 のスイッチ群 ( s 3, s 5 ) が第 2 のクロック信号 C L K 2 に同期してオンし、第 2 のスイッチ群 ( s 6, s 8 ) が第 1 のクロック信号 C L K 1 に同期してオンしても良い。この場合、スイッチ s 7 は、第 1 のクロック C L K 1 が H レベルの期間にオンし、スイッチ s 4 は、第 2 のクロック C L K 2 が H レベルの期間にオンする。第 2 の部分 1052 は、第 2 のクロック信号 C L K 2 に同期して、コンデンサ C 4 の基準電極 E 42 へ調整された第 2 の基準信号を供給する。すなわち、第 2 の伝達部 22 p i は、第 2 のクロック信号 C L K 2 に同期して、第 2 の基準信号 V b i a s 2 及びフィードバック信号 V f p に対する中間信号 V a p の差分である第 2 の信号を生成して N M O S トランジスタ M 4 のゲートへ伝達する。

30

【 0 0 5 5 】

次に、本発明の第 1 実施例に係る全差動增幅回路 200 i における C M F B 動作の詳細な説明を行う。第 2 のクロック信号 C L K 2 が H レベルになる期間 2 において、コンデンサ C 7, C 8 に「 V c m - V b i a s 2 」なる電圧がスイッチ s 6 ~ s 8 を通して蓄えられる。次に、第 1 のクロック信号 C L K 1 が H レベルになる期間 1 において、この電圧の電荷がコンデンサ C 5, C 6 にスイッチ s 3 ~ s 5 を通して再分配される。従って、この繰り返しシーケンスが数回行われた結果、出力信号 V o n, V o p の中点電位は設定されたコモンレベル基準信号 V c m とほぼ等しくなり、ノード n 3 の電位はノード n 4 の電位とほぼ等しくなる。従って、 N M O S トランジスタ M 4 の定常時のドレイン電流は第 2 の基準信号によって定まる値となる。

40

【 0 0 5 6 】

期間 1 において、 P M O S トランジスタ M 3 のゲートは、スイッチ s 1 を通じて第 1 の基準信号である第 1 のバイアス電圧 V b i a s 1 にバイアスされている。これにより、 P M O S トランジスタ M 3 の定常時のドレイン電流は、第 1 の基準信号である第 1 のバイアス電圧 V b i a s 1 によって定まる値となる。従って、第 1 のバイアス電圧 V b i a s

50

1 及び第 2 のバイアス電圧  $V_{bias}$  2 を適切に設定することで、ソース接地段を A B 級バイアスし、定常時の消費電力低減が可能となる。

【 0 0 5 7 】

ここで、何らかの要因で出力  $V_{op}$ ,  $V_{on}$  の同相電圧が上昇した場合を考える。同相電圧の上昇分は、第 2 のコンデンサ C 5 及び第 1 のコンデンサ C 6 を通じてノード n 3 に伝達される。あるいは、図 3 に括弧で示されるように、第 1 のスイッチ群 ( s 3, s 5 ) が第 2 のクロック信号 C L K 2 に同期してオンし、第 2 のスイッチ群 ( s 6, s 8 ) が第 1 のクロック信号 C L K 1 に同期してオンする。この場合には、同相電圧の上昇分は、コンデンサ C 5 とコンデンサ C 7 及びコンデンサ C 6 とコンデンサ C 8 を通じてノード n 3 に伝達される。ノード n 3 の電圧が上昇することで、N M O S トランジスタ M 4 のドレイン電流が増加し、出力信号  $V_{op}$  の電位が低下する。このとき、A B 級増幅部 2 0 n i においても同様の現象が起こり、出力信号  $V_{on}$  の電位が低下する。この様に、出力信号  $V_{op}$ ,  $V_{on}$  のコモンモード成分の上昇に対して、出力信号  $V_{op}$ ,  $V_{on}$  の両方の電位が低下するようフィードバックされる機構になっており、C M F B 機能が実現する。また、コモンモード成分が低下した場合においても、同様のメカニズムでN M O S トランジスタ M 4, M 6 のドレイン電流が減少することにより、C M F B 機能が実現する。

【 0 0 5 8 】

一方、出力の差動信号が変化した場合、例えば出力信号  $V_{op}$  が V 上昇し、出力信号  $V_{on}$  が V 減少した場合を考える。この場合、第 2 のコンデンサ C 5 ( あるいは C 5 + C 7 ) 及び第 1 のコンデンサ C 6 ( あるいは C 6 + C 8 ) の静電容量値がほぼ等しい値であるとすると、ノード n 3 の電位はほぼ変動しない。従って、N M O S トランジスタ M 4 のドレイン電流は変化しない。このことは A B 級増幅部 2 0 n i においても同様であるから、N M O S トランジスタ M 6 のドレイン電流の変化もない。つまり、差動出力信号に対しては、第 2 のコンデンサ C 5 、第 1 のコンデンサ C 6 、第 4 のコンデンサ C 5 ' 、第 3 のコンデンサ C 6 ' を通した出力電圧への関与はない。

【 0 0 5 9 】

次に、本発明の第 2 実施例に係る全差動増幅回路 2 0 0 j の回路構成例を、図 4 を用いて説明する。図 4 は、本発明の第 2 実施例に係る全差動増幅回路 2 0 0 j の回路構成例を示す図である。以下では、第 1 実施例と異なる部分を中心に説明する。なお、図 4 において、末尾に j を有する符号が付された構成要素は、図 1 において、当該符号から j を取り除いた符号が付された構成要素に対応する。また、図 4 において、' を有する符号が付された構成要素は、当該符号から ' を取り除いた符号が付された構成要素と実質的に同一である。

【 0 0 6 0 】

図 4 に示すように、調整部 2 2 p がフィードバック信号  $V_{fp}$  を第 1 の基準ノード n 7 へ供給する場合、第 1 の伝達部 2 1 p 及び第 2 の伝達部 2 3 p は次のような動作を行う。第 2 の基準ノード n 8 には、第 2 のバイアス電圧  $V_{bias}$  2 が第 2 基準信号として保持される。第 2 の伝達部 2 3 p は、第 1 のクロック信号 C L K 1 に同期して、第 2 の基準信号に対する中間信号  $V_{ap}$  の差分をとることにより第 2 の信号を生成してN M O S トランジスタ M 4 のゲートへ伝達する。第 1 の基準ノード n 7 には、第 1 の伝達部 2 1 p により、第 1 のバイアス電圧  $V_{bias}$  1 にフィードバック信号  $V_{fp}$  を加算した電圧が第 1 の基準信号として保持される。即ち、第 1 の伝達部 2 1 p は、調整前の第 1 の基準信号として第 1 のバイアス電圧  $V_{bias}$  1 を受けて、第 1 のバイアス電圧  $V_{bias}$  1 をフィードバック信号  $V_{fp}$  によって調整し、調整された第 1 の基準信号を得る。第 1 の伝達部 2 1 p は、その調整された第 1 の基準信号に対する中間信号  $V_{ap}$  の差分をとることにより第 1 の信号を生成する。第 1 の伝達部 2 1 p は、生成した第 1 の信号をP M O S トランジスタ M 3 及びN M O S トランジスタ M 4 は、対を成す 2 つの出力信号  $V_{op}$ ,  $V_{on}$  のコモンモード成分が基準値 ( コモンレベル基準信号  $V_{cm}$  ) になるように増幅動作を行うことにより、出力信号  $V_{op}$  を生成して出力する。

10

20

30

40

50

## 【0061】

図4に示すように、調整部22nがフィードバック信号Vfnを第3の基準ノードn5へ供給する場合、第3の伝達部21n及び第4の伝達部23nは次のような動作を行う。第4の基準ノードn6には、第4のバイアス電圧Vbias2が第4の基準信号として保持される。第4の伝達部23nは、第1のクロック信号CLK1に同期して、第4の基準信号に対する中間信号Vanの差分をとることにより第4の信号を生成してNMOSトランジスタM6のゲートへ伝達する。第3の基準ノードn5には、第3の伝達部21nにより、第3のバイアス電圧Vbias1'にフィードバック信号Vfnを加算した電圧が第3の基準信号として保持される。即ち、第3の伝達部21nは、調整前の第3の基準信号として第3のバイアス電圧Vbias1'を受けて、第3のバイアス電圧Vbias1'をフィードバック信号Vfnによって調整し、調整された第3の基準信号を得る。第3の伝達部21nは、その第3の基準信号に対する中間信号Vanの差分をとることにより第3の信号を生成する。第3の伝達部21nは、生成した第3の信号をPMOSトランジスタM5のゲートへ伝達する。これにより、PMOSトランジスタM5及びNMOSトランジスタM6は、対を成す2つの出力信号Vop, Vonのコモンモード成分が基準値(コモンレベル基準信号Vcm)になるように増幅動作を行うことにより、出力信号Vonを生成して出力する。

## 【0062】

全差動増幅回路200jは、2つのAB級増幅部20pj, 20njを備える。AB級増幅部20pjは、第1の伝達部21pj及び調整部22pjを含む。調整部22pjは、フィードバック信号Vfpを第1の基準ノードn7へ供給する。調整部22pjは、CMFB回路107jを含む。CMFB回路107jは、第1のクロック信号CLK1に同期して、フィードバック信号Vfpを第1の基準ノードn7へ供給する。コンデンサC3の基準電極E32は、第1の基準ノードn7を介してフィードバック信号Vfpを受ける。これにより、コンデンサC3は、第1のクロック信号CLK1に同期して第1の信号を生成する。ここで、第1の信号は、調整前の第1の基準信号である第1のバイアス電圧Vbias1にフィードバック信号Vfpが加算された信号である調整された第1の基準信号に対する中間信号Vapの差分である。このとき、コンデンサC3の信号電極E31へは、中間信号Vapが供給されている。コンデンサC3は、生成した第1の信号をPMOSトランジスタM3のゲートへ伝達する。従って、出力Vop, Vonのコモンレベル基準信号Vcmの変動は、PMOSトランジスタM3, M5のそれぞれのドレイン電流が変化する事で抑制される。

## 【0063】

以上の実施形態及び実施例に示したように、CMFB回路によるフィードバック信号の帰還先はソース接地のNMOSトランジスタ及びPMOSトランジスタのどちらのゲートに設定しても良い。また、2つのAB級増幅部20pj, 20njそれぞれにおけるCMFB回路によるフィードバック信号の帰還先を、一方はNMOSトランジスタのゲートとし、他方はPMOSトランジスタのゲートに設定した場合でも、CMFB効果が得られる。

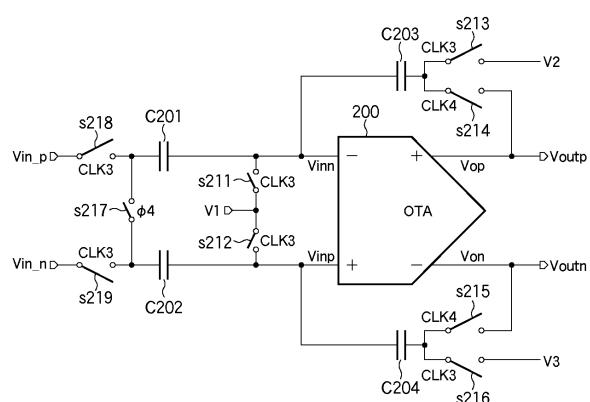

## 【0064】

次に、本発明の全差動増幅回路200を適用したS/Hアプリケーションの一例を図5に示す。図5は、本発明の実施形態に係る全差動増幅回路200を適用したS/Hアプリケーションの回路図である。

## 【0065】

図5中のOTA200が本発明に該当する全差動増幅回路である。ここで、クロック信号CLK3, CLK4は、図2に示す1, 2とほぼ同じ期間である3, 4において、それぞれHレベルとなる2相ノンオーバーラップクロック信号である。また、V1は任意に設定するOTA200の入力コモンモード電圧である。

## 【0066】

以下、この回路の動作の説明を行う。期間3において、入力Vin\_pと任意の電圧

10

20

30

40

40

50

V1との差電圧がスイッチs218, s211を通してコンデンサC201にサンプリングされる。同時に、入力Vin\_nと任意の電圧V1との差電圧がスイッチs219, s212を通してコンデンサC202にサンプリングされる。同時に、任意の電圧V2及びV1の差電圧がスイッチs213, s211を通してコンデンサC203にサンプリングされ、任意の電圧V3及びV1の差電圧がスイッチs216, s212を通してコンデンサC204にサンプリングされる。OTA200はサンプリング状態となる。

### 【0067】

次に、期間4において、スイッチs217, s214, s215が短絡する。OTA入力Vin\_n, Vin\_pは仮想短絡となるため、期間3におけるコンデンサC201, C202に蓄えられた電荷がそれぞれコンデンサC203, C204に転送され、OTA200はホールド状態となる。

10

【図1】

【図2】

【 义 3 】

【 図 4 】

【 図 5 】

---

フロントページの続き

(72)発明者 磯田 尚希

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 高橋 義昭

(56)参考文献 特開2008-011051(JP, A)

再公表特許第2006/132315(JP, A1)

特開2009-060376(JP, A)

特開2008-211535(JP, A)

特開平08-316746(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03F 3/45