(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5090451号

(P5090451)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

H01L 21/205 (2006.01)

F 1

H01L 21/205

請求項の数 15 (全 13 頁)

(21) 出願番号 特願2009-522864 (P2009-522864)

(86) (22) 出願日 平成19年7月31日 (2007.7.31)

(65) 公表番号 特表2009-545886 (P2009-545886A)

(43) 公表日 平成21年12月24日 (2009.12.24)

(86) 國際出願番号 PCT/US2007/017193

(87) 國際公開番号 WO2008/016650

(87) 國際公開日 平成20年2月7日 (2008.2.7)

審査請求日 平成22年7月16日 (2010.7.16)

(31) 優先権主張番号 60/834,773

(32) 優先日 平成18年7月31日 (2006.7.31)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 390040660

アプライド マテリアルズ インコーポレイテッド

APPPLIED MATERIALS, INCORPORATED

アメリカ合衆国 カリフォルニア州 95054 サンタクララ バウアーズ アベニュー 3050

(74) 代理人 100109726

弁理士 園田 吉隆

(74) 代理人 100101199

弁理士 小林 義教

(74) 代理人 100088155

弁理士 長谷川 芳樹

最終頁に続く

(54) 【発明の名称】炭素含有シリコンエピタキシャル層の形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、望ましい厚さとターゲット炭素濃度を有するエピタキシャル層スタックを形成する方法であって、

- (a) 該基板上に、炭素含有シリコンを含む第一シリコン層を形成するステップと、

- (b) 該第一シリコン層上に、炭素を含有しないシリコンを含む第二シリコン層を形成するステップと、

- (c) 該第一シリコン層からの炭素を該第二シリコン層に分布させるステップと、

- (d) 該エピタキシャル層スタックをエッティングして、該第二シリコン層の一部を除去するステップと、

(e) 該エッティングされたエピタキシャル層スタックが望ましい厚さになるまで、(a)から(d)のステップを繰り返すステップと、

(f) 該第一シリコン層の(i)初期炭素濃度、(ii)厚さ、(iii)堆積時間の一つ以上を制御して、該エッティングされたエピタキシャル層スタックのターゲット炭素濃度を達成するステップと、

を含む、前記方法。

## 【請求項 2】

該ターゲット炭素濃度が、200 ppm ~ 5 原子%である、請求項1に記載の方法。

## 【請求項 3】

該初期炭素濃度が、0.5 原子% ~ 10 原子%である、請求項1に記載の方法。

10

20

**【請求項 4】**

該第一シリコン層と該基板との間に炭素を含有しないエピタキシャル層を形成するステップを更に含む、請求項 1 に記載の方法。

**【請求項 5】**

該望ましい厚さが、10 オングストローム～2000 オングストロームである、請求項 1 に記載の方法。

**【請求項 6】**

該初期炭素濃度が、該ターゲット炭素濃度より大きい、請求項 1 に記載の方法。

**【請求項 7】**

該エピタキシャル層スタックをエッチングするステップが、C<sub>12</sub> を含むエッチャントガス中で該エピタキシャル層スタックをエッチングする工程を含む、請求項 1 に記載の方法。 10

**【請求項 8】**

該第二シリコン層が、該エッチャントガスと該第一シリコン層との間に反応が生じるのを防ぐ厚さを有する、請求項 7 に記載の方法。

**【請求項 9】**

該第一シリコン層及び該第二シリコン層の少なくとも 1 つの形成が、700 以下の温度で行われる、請求項 1 に記載の方法。

**【請求項 10】**

基板上に形成されたエピタキシャル層スタックの炭素濃度を制御する方法であって、

20

該エピタキシャル層スタックの望ましい炭素濃度を決定するステップと、

エピタキシャル層スタックを、

- (a) 該基板上に、炭素を含む第一エピタキシャル層を形成し、

- (b) 該第一エピタキシャル層上に、炭素を含有しないキャップ層を形成し、

- (c) 該第一エピタキシャル層からの炭素を該キャップ層に分布させ、

- (d) エッチングして該キャップ層の一部を除去し、

- (e) 該エッチングされたエピタキシャル層スタックが望ましい厚さになるまで、(a) から (d) のステップを繰り返し、

(f) 該第一エピタキシャル層の (i) 初期炭素濃度、(ii) 厚さ、(iii) 堆積時間の一つ以上を制御して、該エッチングされたエピタキシャル層スタックのターゲット炭素濃度を達成する 30

30

ことによって形成するステップと、

を含む、前記方法。

**【請求項 11】**

該第一エピタキシャル層と該基板との間にシードエピタキシャル層を形成するステップを更に含む、請求項 10 に記載の方法。

**【請求項 12】**

該ターゲット炭素濃度が、200 ppm～5 原子%である、請求項 10 に記載の方法。

**【請求項 13】**

各第一エピタキシャル層が、2 オングストローム～100 オングストロームの厚さを有する、請求項 10 に記載の方法。 40

40

**【請求項 14】**

該エッチャントが、C<sub>12</sub> を用いて該エピタキシャル層スタックをエッチャントする工程を含む、請求項 10 に記載の方法。

**【請求項 15】**

該エピタキシャル層スタックとして第一エピタキシャル層とキャップ層を更に交互に形成するステップを更に含む、請求項 10 に記載の方法。

**【発明の詳細な説明】****【関連出願の相互参照】****【0001】**

50

本願は、2006年7月31日に出願された、発明の名称が“METHOD OF FORMING CARBON-CONTAINING SILICON EPITAXIAL LAYERS”（代理人整理番号1-0595/L）とされた、米国仮特許出願第60/834,773号の優先権を主張し、この開示内容は本明細書に全体で援用されている。

#### 【0002】

本願は、以下の同時係属出願に関連し、これらの開示内容の各々は、本明細書に全体で援用されている。

#### 【0003】

2004年12月1日に出願された米国特許出願第11/001,774号（整理番号9618）10

2005年9月14日に出願された米国特許出願第11/227,974号（整理番号9618/P01）

#### 【発明の分野】

#### 【0004】

本発明は、半導体デバイスの製造、より詳細には、炭素含有シリコンエピタキシャル層の形成方法に関する。

#### 背景

より小さいトランジスタが製造されるにつれて、極浅ソース／ドレイン接合を作るのがより難しくなってきている。一般的に、100nm以下の(sub-100nm)CMOS（相補型金属酸化物半導体）デバイスは、30nm未満の接合深さを必要とする。シリコン含有材料（例えば、Si、SiGe、SiC）のエピ層を接合中に形成するのに、選択的エピタキシャル堆積がしばしば利用される。一般的に、選択的エピタキシャル堆積は、エピ層を誘電領域に成長させることなく、シリコンモート（moats）上に成長させることができる。選択的エピタキシーは、隆起したソース／ドレイン、ソース／ドレイン拡大部、コンタクトプラグ又はバイポーラデバイスのベース層堆積のような半導体デバイス内で用いることができる。20

#### 【0005】

一般的に、選択的エピタキシープロセスは、堆積反応とエッチング反応とを含む。堆積反応とエッチング反応は、エピタキシャル層に対するのと、多結晶層に対するのとで相対的に異なる反応速度で同時に生じる。堆積プロセス中、エピタキシャル層が単結晶層上に形成され、一方、多結晶層は、既存の多結晶層及び／又はアモルファス層のような、少なくとも第二層上に堆積される。しかしながら、堆積された多結晶層は、一般的にエピタキシャル層よりも速い速度でエッチングされる。それ故、エッチャントガスの濃度を変えることによって、正味の選択的プロセスは、エピタキシー材料の堆積と、限られた多結晶材料の堆積又は多結晶材料は堆積しない結果となる。例えば、選択的エピタキシープロセスは、スペーサ上に堆積を残さずに、単結晶シリコン表面上のシリコン含有材料のエピ層の形成を生じる場合がある。30

#### 【0006】

隆起したソース／ドレイン特徴部やソース／ドレイン拡大部の特徴部の形成中、例えば、シリコン含有MOSFET（金属酸化物半導体電界効果トランジスタ）デバイスの形成中、シリコン含有材料の選択的エピタキシー堆積は、有益な技術になってきている。ソース／ドレイン拡大部の特徴部は、シリコン表面をエッチングして、凹んだソース／ドレイン特徴部を作り、続いて、エッチングされた表面を、選択的成长エピ層(epilayer)、例えば、シリコングルマニウム(SiGe)材料で充填することによって製造する。選択的エピタキシーは、インサイチュドーピングで完全に近いドーパント活性化を可能にするので、その後のアニールプロセスが省略される。それ故、接合深さを、シリコンエッチングと選択的エピタキシーによって正確に画成することができる。他方で、超浅ソース／ドレイン接合は、直列抵抗の増加を必然的に生じる。40

#### 【0007】

また、シリサイド形成中の接合消失により、直列抵抗が更に増加する。接合消失を補償

50

するために、隆起したソース／ドレインを、接合上に選択的にエピタキシャル成長させる。典型的には、隆起したソース／ドレイン層は、ドープされていないシリコンである。

#### 【0008】

しかしながら、現在の選択的エピタキシープロセスは、いくつかの欠点を有する。現在のエピタキシープロセス中、選択性を維持するために、前駆物質の化学的濃度と、反応温度を堆積プロセス全体を通して調節、調整しなければならない。十分なシリコン前駆物質が与えられない場合には、エッチング反応が支配的になり、全体のプロセスが減速する。また、基板特徴部の有害なオーバーエッチングが起こることがある。十分なエッチャンント前駆物質が与えられない場合には、堆積反応が支配的になり、基板表面にわたって単結晶及び多結晶材料を形成させる選択性を減少することがある。また、現在の選択的エピタキシープロセスは、通常、約800、1,000又はそれより高い反応温度を要求する。このような高温は、熱量上の理由と基板表面の制御できない窒化物形成反応の可能性により、製造プロセス中は望ましくない。更に、いくつかのエピタキシャル膜及び／又はプロセスは、膜中のピッチング或いは表面粗さのような形態的な欠陥を生じる傾向がある。10

#### 【0009】

それ故、シリコンやシリコン含有化合物を選択的にエピタキシャル堆積するためのプロセスの必要がある。更に、このプロセスは、速い堆積速度を有し、約800以下のようなプロセス温度を維持しながら、様々な元素濃度を有するシリコン含有化合物を形成する用途にも用いることができなければならない。最後に、プロセスは、低欠陥膜或いは膜スタック（例えば、ピッチング、転位、粗さ、点欠陥等が殆どない）を生じることができなければならない。20

#### 【発明の概要】

#### 【0010】

本発明の第一態様では、基板上にエピタキシャル層スタックを形成する方法が提供される。本方法は、(1)エピタキシャル層スタックのためのターゲット炭素濃度を選択するステップと、(2)基板上に炭素含有シリコン層を形成するステップであって、炭素含有シリコン層が、選択されたターゲット炭素濃度に基づいて選択される初期炭素濃度、厚さ及び堆積時間の少なくとも一つを有する、前記ステップと、(3)エッチングの前に、炭素含有シリコン層上に炭素を含有しないシリコン層を形成するステップと、を含む。30

#### 【0011】

本発明の第二態様では、エピタキシャル層スタックを形成する方法が提供される。この方法は、(1)エピタキシャル層スタックのためのターゲット炭素濃度を選択するステップと、(2)交互の炭素含有シリコン層と炭素を含有しないシリコン層を堆積させることによって、エピタキシャル層スタックを形成するステップとを含む。ターゲット炭素濃度は、全体の厚さ、初期炭素濃度、及び炭素含有シリコン層の堆積時間の少なくとも1つに基づいて達成される。40

#### 【0012】

本発明の第三態様では、基板上に形成されたエピタキシャル層スタックの炭素濃度を制御するための方法が提供される。この方法は、(1)エピタキシャル層スタックの望ましい炭素濃度を決定するステップと、(2)(a)基板上に炭素含有エピタキシャル層を形成し、(b)炭素含有エピタキシャル層上に炭素を含有しないエピタキシャル層を形成することによって、エピタキシャル層スタックを形成するステップと、を含む。炭素含有エピタキシャル層の厚さは、エピタキシャル層スタックの望ましい炭素濃度に基づいて選択される。多数の他の態様も提供される。40

#### 【0013】

本発明の他の特徴及び態様は以下の詳細な説明、添付した特許請求の範囲、添付図面からより十分に明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0014】

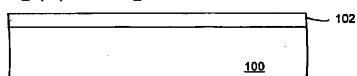

【図1A】図1Aは、本発明によるエピタキシャル層スタックの形成中の基板を示す断面50

図である。

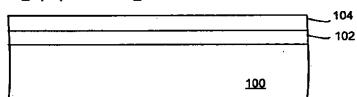

【図1B】図1Bは、本発明によるエピタキシャル層スタックの形成中の基板を示す断面図である。

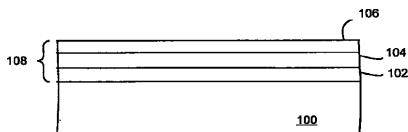

【図1C】図1Cは、本発明によるエピタキシャル層スタックの形成中の基板を示す断面図である。

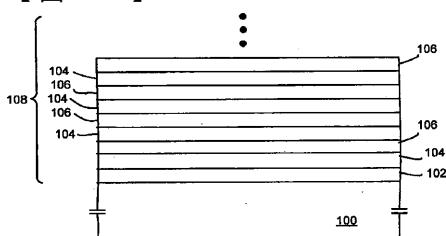

【図1D】図1Dは、本発明によるエピタキシャル層スタックの形成中の基板を示す断面図である。

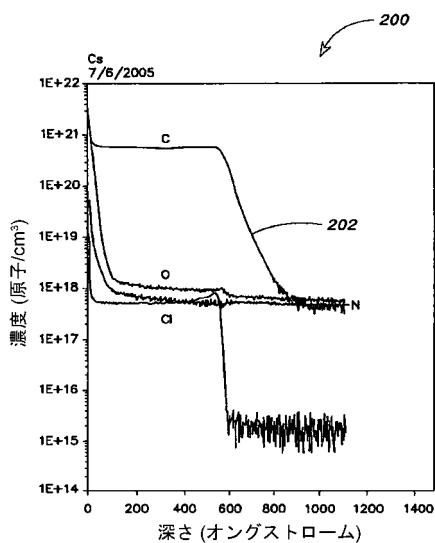

【図2】図2は、本発明により形成された、炭素を含有しないエピタキシャルシード層と炭素含有エピタキシャル層と炭素を含有しないエピタキシャルキャップ層の積層全体の炭素の濃度を示すグラフである。

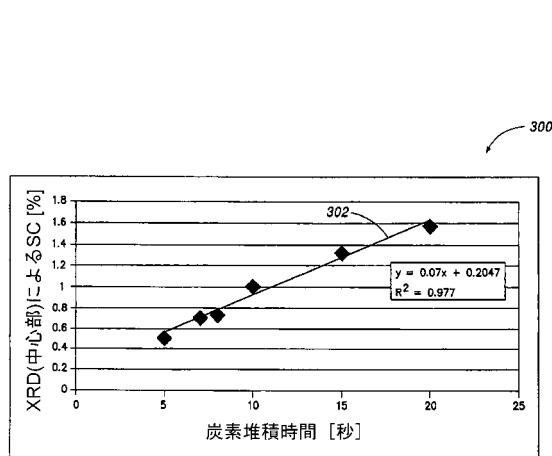

【図3】図3は、本発明によるエピタキシャルシード層とキャップ層の一定の堆積時間の間の炭素含有エピタキシャル層の堆積時間に対する置換炭素(SC)濃度の依存性を示すグラフである。

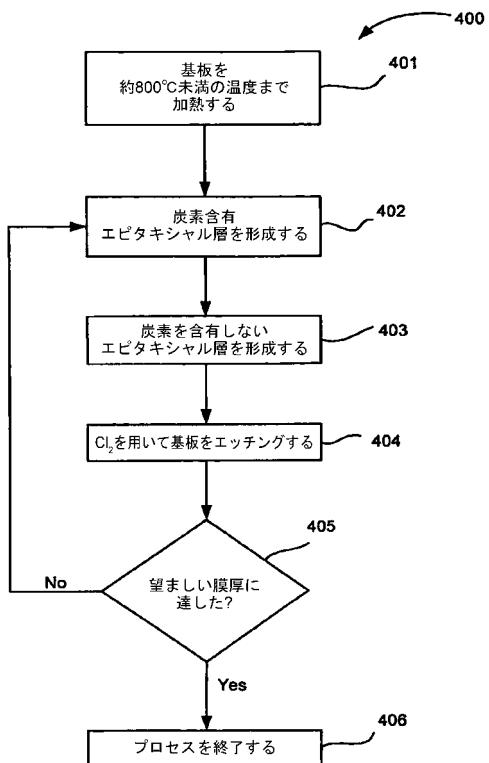

【図4】図4は、本発明によるターゲット炭素濃度を有するエピタキシャル層スタックを形成するための例示的な方法のフローチャートである。

#### 【詳細な説明】

##### 【0015】

誘電膜でパターン形成されたシリコン基板上の選択的エピタキシャル成長プロセス中、単結晶半導体の形成は、露出したシリコン表面上（例えば、誘電表面上ではなく）でのみ生じる。選択的エピタキシャル成長プロセスは、同時に起こるエッチング堆積プロセスと、交互のガス供給プロセスを含むことがある。同時に起こるエッチング堆積プロセスでは、エッチャント化学種と堆積化学種の両方が、同時に流される。このようにして、エピタキシャル層は、その形成中、同時に堆積され且つエッチングされる。

##### 【0016】

一方、先に援用した、2004年12月1日に出願された米国特許出願第11/001,774号（整理番号9618）は、基板上にエピタキシャル層を形成するための交互のガス供給（AGS）プロセスを記載する。AGSプロセス中、エピタキシャル堆積プロセスが基板上で行われ、次いで、エッチングプロセスが基板上で行われる。エピタキシャル層の望ましい厚さが形成されるまで、エピタキシャル堆積プロセスの後にエッチングプロセスが続くサイクルが繰り返される。

##### 【0017】

堆積プロセスは、基板表面を少なくともシリコン源とキャリアガスを含有する堆積ガスに曝すステップを含んでもよい。堆積ガスは、また、ゲルマニウム及び／又は炭素源だけでなく、ドーパント源を含んでもよい。一般的なドーパントとしては、ヒ素、ホウ素、リン、アンチモン、ガリウム、アルミニウム、他の元素を挙げることができる。

##### 【0018】

堆積プロセス中、エピタキシャル層は、一つ又は複数の基板の単結晶表面上に形成され、一方、多結晶層が、アモルファス及び／又は多結晶表面のような二次表面上に形成される。続いて、基板がエッチングガスに曝される。エッチングガスは、キャリアガスとエッチャントとを含む。エッチングガスは、堆積中に堆積されたシリコン含有材料を除去する。エッチングプロセス中、多結晶層が、エピタキシャル層よりも速い速度で除去される。それ故、堆積とエッチングプロセスの最終結果は、単結晶表面上のシリコン含有材料のエピタキシャル成長を形成し、もしあったとしても、二次表面上の多結晶シリコン含有材料の成長は最小限である。堆積することができる例示的なシリコン含有材料としては、シリコン、シリコンゲルマニウム、シリコン炭素、シリコンゲルマニウム炭素、これらのドーパント変形例等が挙げられる。

##### 【0019】

従来のシリコンエピタキシャル膜形成プロセスは、水素(H<sub>2</sub>)、塩化水素(HCl)、ジクロロシランのようなシリコン源を用いて、（例えば、HCl及び／又はシリコン源を解離させるために）約700より高い基板温度で行われる。C<sub>1</sub><sub>2</sub>はより低い温度（

10

20

30

40

50

例えば、約 600 以下)で効率的に解離するので、エピタキシャル膜形成温度を下げる一つの方法は、H C l の代わりに塩素 (C l<sub>2</sub>) を用いることである。水素とC l<sub>2</sub>は非相溶性であることから、水素以外の、例えば、窒素のようなキャリアガスをC l<sub>2</sub>と用いるのがよい。同様に、より低い解離温度を有するシリコン源を用いるのがよい(例えば、シラン (S i H<sub>4</sub>)、ジシラン (S i<sub>2</sub> H<sub>6</sub>) 等)。

#### 【0020】

シリコンエピタキシャル膜形成プロセスのエッチャントガスとしてC l<sub>2</sub>を用いることにより、生じるシリコンエピタキシャル膜の表面形態が悪くなる場合がある。いかなる特定の理論に縛られることは望まないが、C l<sub>2</sub>は、シリコンエピタキシャル膜表面を過度に激しく攻撃して、ピッチング等を生じるのであろうと考えられる。シリコンエピタキシャル膜が炭素を含有するときに、C l<sub>2</sub>を用いると特に問題があることが分かってきた。

10

#### 【0021】

本発明は、エピタキシャル膜表面形態を改善することができるシリコンエピタキシャル膜形成プロセス中、エッチャントガスとしてC l<sub>2</sub>を用いる方法を提供する。本発明の方法は、例えば、2004年12月1日に出願された米国特許出願第11/001,774号(整理番号9618)に記載された交互のガス供給 (A G S) プロセスとともに用いることもできる。

#### 【0022】

ある実施形態では、エッチング段階中、C l<sub>2</sub>に曝される前に、いかなる炭素含有シリコンエピタキシャル膜をも“封入”されるのがよい。炭素含有シリコンエピタキシャル膜は、例えば、炭素源なしに形成されたシリコンエピタキシャル膜(“炭素を含有しないシリコンエピタキシャル膜”)によって、封入することができる。

20

#### 【0023】

例示として、本発明による、A G S プロセスを用いた、炭素含有シリコンエピタキシャル層スタックの形成を図1 A - 図1 D を参照して以下に記載する。図1 A を参照すると、基板100 上にエピタキシャルシード層102(例えば、シリコン (S i) エピタキシャル層)が形成された基板100 の断面図を示す。ある実施形態では、エピタキシャルシード層102は、除かれる。

#### 【0024】

エピタキシャルシード層102を形成するために、基板100をプロセスチャンバ内に配置し、望ましい基板及び/又はプロセス温度まで加熱する。例示的なエピタキシャル膜チャンバは、カリフォルニア州サンタクララにある Applied Materials 社の E p i C e n t u r e (登録商標) システムや P o l y G e n (登録商標) システムに見られるが、他のエピタキシャル膜チャンバ及び/又はシステムを用いることができる。本発明の少なくとも1つの実施形態では、プロセスチャンバ内でいかなるシリコンエピタキシャル層中にも炭素が混入することを改善するために、約700 未満の基板及び/又はプロセス温度を用いるのがよい。特定の実施形態では、約550 ~ 650 の基板及び/又はプロセス温度範囲を用いるのがよく、更に他の実施形態では、約600 未満の基板及び/又はプロセス温度を用いるのがよい。700 より高い基板及び/又はプロセス温度を含む、他の基板及び/又はプロセス温度を用いてもよい。

30

#### 【0025】

望ましい基板及び/又はプロセス温度に達した後、基板100を、少なくともシリコン源(炭素源なしで)に曝して、エピタキシャルシード層102を形成する。例えば、基板100をシラン或いはジシランのようなシリコン源と、窒素のようなキャリアガスに曝すのがよい。リン或いはホウ素のようなドーパント源、ゲルマニウム源等も(いかなる他の適当なソース及び/又はガスであってもよいように)用いることができる。エピタキシャル膜形成プロセス中、基板100のいかなる単結晶表面上にもエピタキシャル層102が形成され、一方、(前述したように)基板100上に存在するいかなる多結晶層及び/又はいかなるアモルファス層上にも多結晶層が形成される。

#### 【0026】

10

20

30

40

50

エピタキシャルシード層102は、例えば、シランを約50-150sccmの流量で(或いはジシランを約10-40sccmの流量で)シリコン源を流し、約20-25s1mの流量で窒素キャリアガスを流すことによって(より大きい或いは小さいシリコン源及び/又はキャリアガス流量を用いてもよいが)形成される。必要に応じてHClを流してもよい。

#### 【0027】

少なくとも一つの実施形態では、エピタキシャルシード層102は、約2オングストローム～約10オングストロームの厚さを有するのがよいが、他の厚さが用いられてもよい。例えば、約1秒～約100秒の堆積時間を、一つ以上の実施形態においては約5秒を、用いることができる。

10

#### 【0028】

エピタキシャルシード層102(少しでも用いた場合には)を形成した後、基板100を少なくともシリコン源と炭素源に曝して、炭素含有シリコンエピタキシャル層104(図1B)を基板100上にエピタキシャルシード層102の上に形成する。例えば、基板100をシラン或いはジシランのようなシリコン源、メタンのような炭素源と、窒素のようなキャリアガスに曝すのがよい。リン或いはホウ素のようなドーパント源、ゲルマニウム源等も(いかなる他の適当なソース及び/又はガスでもよいように)用いることができる。エピタキシャル膜形成プロセス中、炭素含有エピタキシャル層が、基板100のいかなる単結晶表面上にも形成され、一方、(前述したように)基板100上に存在するいかなる多結晶層及び/又はいかなるアモルファス層上にも多結晶層が形成される。

20

#### 【0029】

少なくとも一つの実施形態では、メタンの約1-5sccmの炭素源流量を、シランの約50-150sccm(或いはジシランの約10-40sccm)のシリコン源流量と約20-25s1mの流量の窒素キャリアガスとともに用いるのがよい(より大きい或いは小さいシリコン源及び/又はキャリアガス流量を用いてもよい)。必要に応じてHClを流してもよい。

#### 【0030】

炭素含有エピタキシャル層104は、例えば、約2オングストローム～100オングストロームの厚さを有するのがよいが、他の厚さが用いられてもよい。例えば、約1秒～約50秒の堆積時間を、一つ以上の実施形態においては約10秒を、用いることができる。

30

#### 【0031】

炭素含有シリコンエピタキシャル層104を形成した後、基板100を少なくともシリコン源(炭素源なしに)曝して、第二シリコンエピタキシャル層106(例えば、図1Cに示すようなキャッピング層)を基板100上に炭素含有シリコンエピタキシャル層104の上に形成する。例えば、基板100をシラン或いはジシランのようなシリコン源と、窒素のようなキャリアガスに曝すのがよい。リン或いはホウ素のようなドーパント源、ゲルマニウム源等も(いかなる他の適当なソース及び/又はガスでもよいように)用いることができる。炭素含有シリコンエピタキシャル層104上に第二シリコンエピタキシャル層106が存在することにより、炭素含有シリコンエピタキシャル層104中の塩素と炭素(及び/又は水素)との相互作用を減らすことができる。前述したように、HClを流してもよい。

40

#### 【0032】

第二シリコンエピタキシャル層106は、例えば、シランの約50-150sccmの流量(或いはジシランの約10-40sccmの流量)でシリコン源を流し、約20-25s1mの流量で窒素キャリアガスを流すことによって(より大きい或いは小さいシリコン源及び/又はキャリアガス流量を用いてもよいが)、形成することができる。HClを流してもよい。

#### 【0033】

少なくとも一つの実施形態では、第二シリコンエピタキシャル層106は、約2オングストローム～100オングストロームの厚さを有するのがよいが、他の厚さが用いられて

50

もよい。例えば、約1秒～約100秒の堆積時間を、一つ以上の実施形態において約5秒を、用いることができる。

**【0034】**

これによって、炭素含有エピタキシャル層104が、炭素を含有しないエピタキシャル層102、206（例えば、意図的な炭素源なしに形成されたエピタキシャル層）の間に封入された、エピタキシャル層スタック108が形成される。

**【0035】**

第二シリコンエピタキシャル層106の形成後、基板100をC<sub>1,2</sub>及び／又は他のエッチャントに曝して、少なくとも第二シリコンエピタキシャル層106及び／又は基板100上に形成された他の膜（例えば、基板100上に存在する多結晶及び／又はアモルファス層上に形成された多結晶シリコン及び／又は炭素含有シリコンエピタキシャル層104上に形成された単結晶シリコン）をエッチングする。例えば、少なくとも一つの実施形態では、基板100を約30-50 sccmの流量のC<sub>1,2</sub>と20 s1mの流量の窒素キャリアガスに曝す。HClを流してもよい（より大きい或いは小さいC<sub>1,2</sub>及び／又はキャリアガス流量を用いてもよい）。

10

**【0036】**

エッチングの後、（例えば、窒素及び／又は他の不活性ガスで、約20秒或いは他の適当な時間中）使用されているプロセスチャンバがバージされ、いかなるC<sub>1,2</sub>及び／又はいかなる他の望ましくない化学種／副生成物をチャンバから除去するのがよい。

**【0037】**

20

エピタキシャルキャップ層106及び／又はシード層102は、エッチャントと炭素含有エピタキシャル層104の炭素との間で反応が生じるのを妨げる。このようなものとして、エッチング中、下にある炭素含有層はC<sub>1,2</sub>に曝されないので、C<sub>1,2</sub>をエッチャントして用いるのがよい。従って、炭素含有エピタキシャル層102は、ピッチングを有する表面形態ではなく平滑な表面形態を有する。

**【0038】**

例えば、図1Dに示されるように、望ましい全体のエピタキシャル層スタック厚さが達成されるまで、堆積とエッチングの順番を繰り返すのがよい。例えば、炭素を含有しないシリコン層堆積／炭素含有シリコン層堆積／炭素を含有しないシリコン層堆積／エッチングの順番を約80回繰り返して、約600オングストロームの全体のエピタキシャル層スタック厚さを生じるのがよい。他の実施形態では、下に横たわるシード層の堆積は除去されるので、形成の順番は、望ましい全体のエピタキシャル層スタック厚さを生じるために多数回繰り返される、炭素含有シリコン層堆積／炭素を含有しないシリコン層堆積／エッチングであるのがよい。

30

**【0039】**

上述の例示は、特定の実施形態を示すが、一般的には、エピタキシャル層スタック（炭素含有エピタキシャル層と炭素を含有しないエピタキシャル層を含む）は、約10オングストローム～約2000オングストローム、好ましくは約100オングストローム～約1500オングストローム、より好ましくは約300オングストローム～約1000オングストロームの範囲の厚さを有する。一つの特定の実施形態では、約600オングストロームの層スタックを用いるのがよい。

40

**【0040】**

(1)炭素を含有しないエピタキシャル材料に対するカプセル被覆された炭素含有エピタキシャル層の膜厚と、(2)炭素含有エピタキシャル層の炭素濃度を制御することによって、最終的なエピタキシャル層スタックの平均炭素濃度を制御及び／又は決定することができる。例えば、ある実施形態では、炭素が炭素含有エピタキシャル層形成ステップ中に堆積されるのみであっても、一つ又は複数の炭素含有エピタキシャル層の炭素は、スタックされた層（例えば、シード層、炭素含有層、キャップ層）の深さに層って素早く且つ均一に拡散する。

**【0041】**

50

図2は、本発明により形成された（図1Cのような）炭素を含有しないエピタキシャルシード層と、炭素含有エピタキシャル層と、炭素を含有しないエピタキシャルキャップ層のスタックされた層全体の炭素濃度を示すグラフ200である。図2を参照して分かるように、（X軸は、スタックされた層の深さを表し、Y軸は、スタックされた層全体の炭素分布を示す）全体として線202で示される炭素濃度は、スタックされた層の深さ全体に均一に分布する。このようなものとして、本発明のある実施形態によれば、スタックされた層内の炭素濃度は、炭素含有層及び／又はシード層及び／又はキャップ層の相対的な厚さと、炭素含有層内の初期炭素濃度と、を制御することによって、制御することができる。

## 【0042】

10

ある実施形態では、最終的な炭素濃度は、炭素を含有しないエピタキシャル層に対する炭素含有エピタキシャル層の相対的な厚さから推定することができる。例えば、図3は、（例えば、図1Cの）シード層とキャップ層の一定の堆積時間の炭素含有エピタキシャル層の堆積時間に対する置換炭素（SC）濃度の依存を示すグラフ300である。図3の線302を参照して分かるように、スタック層内の炭素濃度は、炭素含有エピタキシャル層の堆積時間に比例する。かくして、本発明のある実施形態によれば、シード層／炭素含有層／キャップ層スタック或いは“サンドイッチ”内の炭素濃度は、炭素含有エピタキシャル層の堆積時間を制御することによって制御することができる。

## 【0043】

20

一つ或いはそれ以上の実施形態では、エピタキシャル層スタックのターゲット炭素濃度は、約200パーツ・パー・ミリオン（ppm）～約5原子パーセント（at%）、好ましくは約0.5at%～約2at%の範囲、例えば、約1.5at%であるのがよい。他のターゲット濃度を用いてもよい。ある実施形態では、炭素濃度は、（図1A-図1Dの層104のような）エピタキシャル層で、勾配を有していてもよい。

## 【0044】

30

炭素含有シリコン層に組み込まれる炭素は、シリコン含有層の堆積の直後に、一般的に、結晶格子の格子間位置に配置される。初期炭素濃度は、或いは言い換えれば炭素含有層の堆積されたままの炭素含有量は、約10at%以下、好ましくは約5at%未満、より好ましくは約0.5at%～約3at%、例えば、約2at%がよい。（連続する）プロセスステップ中のアニーリング（後述する）或いは自然拡散によって、エピタキシャル層は、少なくとも一部、もしそうでないなら全ての格子間炭素が結晶格子の置換位置に組み込まれる。エピタキシャル層スタックの全体の炭素濃度は、格子間或いは置換位置に組み込まれた全ての炭素を含む。高分解能X線回折（XRD）を用いて、置換炭素濃度と厚さを決定することができる。二次イオン質量分析装置（SIMS）を用いて、エピタキシャル層スタックの全体の（置換及び格子間）炭素濃度を決定することができる。置換炭素濃度は、全体の炭素濃度と等しいか或いは低い場合がある。適したアニーリングプロセスは、酸素、窒素、水素、アルゴン、ヘリウム或いはこれらの組み合わせのようなガス雰囲気での高速熱処理（ RTP）、レーザアニーリング、或いは熱アニーリングのようなスパイクアニールを含むのがよい。ある実施形態では、アニーリングプロセスは、約800～約1,200、好ましくは約1,050～1,100の温度で行うのがよい。このようなアニーリングプロセスは、炭素を含有しないキャップ層106が堆積された直後、或いは、他の様々なプロセスステップ（例えば、全体の膜スタックが堆積された後）の直後に行うのがよい。

40

## 【0045】

図4は、本発明によるターゲット炭素濃度を有するエピタキシャル層スタックを形成するための例示的な方法400のフローチャートである。図4を参照して、ステップ401では、基板をプロセスチャンバ内に装填し、約800以下の温度まで加熱する。ある実施形態では、750未満、700未満、或いは650未満のような、より低い温度範囲をエピタキシャル膜形成中に用いてもよい。

## 【0046】

50

ステップ402では、炭素含有エピタキシャル層を基板上に形成する。初期炭素濃度、厚さ及び／又は炭素含有エピタキシャル層の堆積時間は、エピタキシャル層スタックのターゲット炭素濃度に基づいて選択すればよい。その後、ステップ403では、炭素を含有しないエピタキシャル層を、炭素含有エピタキシャル層上に形成する。ある実施形態では、炭素を含有しないエピタキシャル層は、下に横たわる炭素含有層をその後のエッティングから保護するのに十分な厚さである。

#### 【0047】

ステップ404では、H C 1 及び／又はC 1<sub>2</sub>のようなエッチャントガスを用いて基板をエッティングする。述べたように、炭素を含有しないエピタキシャル層は、下に横たわる炭素含有層をエッチャントガスから保護する。バージステップ(図示せず)を、エッティングの後に行って、いかなるエッチャントガス及び／又は他の望ましくないガスをも使用中のプロセスチャンバから取り除くのがよい。

10

#### 【0048】

ステップ405では、所望のエピタキシャル層スタック厚さに達しているか決定される。もしそうであれば、ステップ406でプロセスは終了し、さもなければ、プロセスはステップ402に戻り、基板上にエピタキシャル材料を更に堆積させる。

#### 【0049】

他の例示的な実施形態では、プロセスサイクルは、(1)炭素を含有しないシリコン(Si)層堆積ステップ、(2)炭素含有シリコン(SiC)層堆積ステップ、(3)炭素を含有しないシリコン(Si)層堆積ステップ、(4)エッティングステップ、(5)バージステップを含むのがよい。プロセスサイクルを多数回繰り返して、全体のエピタキシャル層スタック厚さを達成することができる。特定の一実施形態では、プロセスサイクルを、約80回繰り返して、エピタキシャル層スタックの約600オングストロームのエピタキシャル材料を得ることができる。この場合、Si或いはSiCの各堆積は、約5～30オングストロームのエピタキシャル材料を生じ、それらの一部(例えば、約15-25オングストローム)が、後のエッティングステップでエッティング除去される。約80回の繰り返しの後、(例えば、Siモート上に)残存するエピタキシャル材料は、約600オングストロームである場合がある(基板の誘電領域上には殆ど或いは全く堆積していない)。他の実施形態では、約30～100ナノメートルのエピタキシャル層スタック厚さ範囲を用いるのがよい。

20

#### 【0050】

ある実施形態では、エピタキシャル層スタック及び／又は堆積したままのSi:C層の置換炭素濃度範囲は、約0.5-2.0at%である。Si:C層がSi層の間に挟まれているとき、全体のスタック炭素濃度は、Si:C層の厚さと比較したSi層の厚さに依存して減少する。プロセス条件に依存して、置換炭素濃度は、全体の炭素濃度と等しいか或いは低くなる。

30

#### 【0051】

例示的なガス流量範囲は、ジクロロシラン、シラン、ジシラン、或いは高級シランの約5-500sccmのシリコン源流量、H<sub>2</sub>或いはN<sub>2</sub>の約3-30slmのキャリアガス流量を含む。エッティング中、H C 1 の例示的な流量は、約20-1000sccm、C 1<sub>2</sub>は約10-500sccmである。

40

#### 【0052】

特定の一実施形態では、(バージステップを除く)各プロセスステップ中、ほぼ同じ流量(例えば、約300sccm或いは他の適当な流量)でH C 1 を流すのがよく、エッティングステップ中のみC 1<sub>2</sub>を(例えば、約30sccm或いは他の適当な流速で)流すのがよい。各堆積ステップ中、ジシランを(例えば、約7sccm或いは他の適当な流量で)流すのがよく、Si:C堆積ステップ中メチルシランを(例えば、約2.2sccm或いは他の適当な流量で)流すのがよい。各プロセスサイクルステップ中、N<sub>2</sub>キャリアガスは、約20slm或いは他の適当な流量で流すのがよく、各バージステップ中、約30slm或いは他の適当な流量まで増加させるのがよい。ある実施形態では、約5オングス

50

トロームの S i を第一 S i 堆積ステップ中（例えば、約 4 秒で堆積）堆積させ、約 9 オンゲストロームの S i : C を S i : C 堆積ステップ中堆積（例えば、約 7 秒で堆積）させるのがよく、約 13 オンゲストロームの S i を第二 S i 堆積ステップ中に堆積（例えば、約 10 秒で堆積）させるのがよく、約 19 オンゲストロームのエピタキシャル材料をエッチングステップ中除去するのがよい（例えば、約 13 秒のエッチング）。適当なバージ時間用いることができる（例えば、約 10 秒）。約 600 のプロセス温度と、堆積とバージ中、約 10 トール、エッチング中、約 13 トールのチャンバ圧を用いるのがよい。述べたように、他のプロセス条件を用いてもよい。

## 【 0053 】

前述の記載は、本発明の例示的実施形態のみを開示するものである。本発明の範囲内にある上記で開示した装置及び方法の変更は、当業者に容易に明らかであろう。従って、本発明は、その例示的実施形態に関連して開示され、添付した特許請求の範囲によって定められるように、他の実施形態が本発明の精神及び範囲内であることが理解されるべきである。10

## 【 符号の説明 】

## 【 0054 】

100 … 基板、 102 … エピタキシャル層、 104 … エピタキシャル層、 106 … エピタキシャル層、 108 … エピタキシャル層スタック。

【 図 1 A 】

FIG. 1A

【 図 1 B 】

FIG. 1B

【 図 1 C 】

FIG. 1C

【 図 1 D 】

FIG. 1D

【 図 2 】

【図3】

【図4】

---

フロントページの続き

(72)発明者 キム， イワン

アメリカ合衆国， カリフォルニア州， ミルピタス， ヘブンリー プレイス 825

(72)発明者 イー， ツアイヤン

アメリカ合衆国， カリフォルニア州， クパーテイーノ， アパートメント655， ヴァリー

グリーン ドライブ 20990

(72)発明者 ゾジャジ， アリ

アメリカ合衆国， カリフォルニア州， サンタ クララ， パート ストリート 662

審査官 大塚 徹

(56)参考文献 国際公開第2006/060543 (WO, A1)

特開平10-223537 (JP, A)

特開平05-175141 (JP, A)

特開昭62-243144 (JP, A)

特開2000-269476 (JP, A)

特開平08-288215 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/205