(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5598876号

(P5598876)

(45) 発行日 平成26年10月1日(2014.10.1)

(24) 登録日 平成26年8月22日(2014.8.22)

(51) Int.Cl.

G 11 C 11/413 (2006.01)

F 1

G 11 C 11/34 335 A

請求項の数 2 (全 11 頁)

|              |                                                                    |

|--------------|--------------------------------------------------------------------|

| (21) 出願番号    | 特願2012-274485 (P2012-274485)                                       |

| (22) 出願日     | 平成24年12月17日 (2012.12.17)                                           |

| (62) 分割の表示   | 特願2009-518412 (P2009-518412)<br>の分割<br>原出願日 平成19年4月19日 (2007.4.19) |

| (65) 公開番号    | 特開2013-54818 (P2013-54818A)                                        |

| (43) 公開日     | 平成25年3月21日 (2013.3.21)                                             |

| 審査請求日        | 平成24年12月17日 (2012.12.17)                                           |

| (31) 優先権主張番号 | 11/427,610                                                         |

| (32) 優先日     | 平成18年6月29日 (2006.6.29)                                             |

| (33) 優先権主張国  | 米国(US)                                                             |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100142907<br>弁理士 本田 淳                                                                                      |

| (72) 発明者  | ケンカレ、プラシャント ュー.<br>アメリカ合衆国 78735 テキサス州<br>オースティン オセロ コーブ 711<br>2                                          |

最終頁に続く

(54) 【発明の名称】低電圧で読み出／書き動作を行うメモリを有する集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサと、

それぞれが、メモリセル電力供給電圧を受け取るための電力供給電圧ノードを含む行および列の形に配置され、前記プロセッサと結合しているメモリの一部である複数のメモリセルであって、メモリセルの行が、ワード線、および前記ワード線と結合しているメモリセルのすべてを含み、メモリセルの列が、ビット線、および前記ビット線と結合しているメモリセルのすべてを含む複数のメモリセルと、

前記複数のメモリセルのそれぞれの前記電力供給電圧ノードと結合し、書き動作の第1の部分中に、選択した複数のメモリセルの電力供給電圧ノード上の電圧を第1の電力供給電圧から前記第1の電力供給電圧より低い所定の電圧に変更するための放電回路と、

前記複数の各メモリセルの前記電力供給電圧ノードと結合し、第1の電力供給電圧を、前記書き動作中にメモリセルの選択した列の前記電力供給電圧ノードに供給するためのものであって、前記第1の電力供給電圧より高い第2の電力供給電圧を、前記書き動作中にすべての選択しなかった列の前記電力供給電圧ノードに供給するメモリセル電力供給多重化回路と、を備え、

前記第1の電力供給電圧は前記プロセッサに電力を供給するためのものであり、前記複数のメモリセルの読み出動作中に、前記第2の電力供給電圧が前記複数のメモリセルのすべてに供給される、集積回路。

## 【請求項 2】

10

20

集積回路メモリにアクセスするための方法であって、

それぞれが、電力供給電圧ノード、および記憶ノードとビット線の間に結合しているアクセス・トランジスタを有し、プロセッサと結合しているメモリの一部である複数のメモリセルを提供するステップと、

第1の電力供給電圧を受け取るステップであって、前記第1の電力供給電圧は前記プロセッサに電力を供給するためのものである、前記ステップと、

前記第1の電力供給電圧より高い第2の電力供給電圧を受け取るステップと、

読み動作中、前記第2の電力供給電圧を前記複数のメモリセルのすべてに供給するステップと、

書込動作中、メモリセルの選択した列の前記電力供給電圧ノードに供給するための前記第1の電力供給電圧を選択するステップと、

前記書込動作中、メモリセルの選択しなかった列の前記電力供給電圧ノードに供給するために、前記第2の電力供給電圧を選択するステップと、

前記書込動作の第1の部分中に、メモリセルの前記選択した列の前記電力供給電圧ノードを、前記第1の電力供給電圧から前記第1の電力供給電圧より低い所定の電圧に放電するステップと、からなる方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、概して、回路に関し、特に、低電圧で読み出/書き込動作を行うメモリを有する集積回路に関する。

##### 【背景技術】

##### 【0002】

新しい世代の集積回路は、電力消費を低減するために、ますますより低い供給電圧を使用するようになっている。しかし、集積回路に内蔵されているメモリに読み出/書き込を行うためにより低い供給電圧を使用すると、メモリ・ビットセルの性能が劣化する。例を挙げて説明すると、より低い供給電圧を使用すると、ビットセルの読み出/書き込マージンが低減する。読み出/書き込マージンを維持するために、従来、回路の設計者はより高い供給電圧をどうしても使用しなければならなかった。すなわち、許容できる読み出/書き込マージンを有するために、ビットセルが必要とする最低供給電圧は全集積回路の供給電圧となり、その結果、電力消費が大きくなる。

##### 【0003】

ビットセルの読み出/書き込マージンを改善することができれば、集積回路に対してより低い供給電圧を使用することができる。通常、ビットセルの読み出/書き込マージンは、ビットセルのサイズを増大することにより改善することができる。しかし、そうすると、ビットセルの占有する面積が増大し、メモリが占有する面積も増大することになる。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

それ故、ビットセルのサイズを増大することなしに、低電圧読み出/書き込動作を行うメモリを有する集積回路が求められている。

##### 【課題を解決するための手段】

##### 【0005】

添付の図面を参照すれば、本発明をよりよく理解することができるし、当業者には、その多数の目的、機能および利点をよりよく理解することができるだろう。

当業者であれば、図の要素は図を分かりやすく、見やすくするためのものであり、縮尺は必ずしも正確なものでないことを理解することができるだろう。例えば、本発明の実施形態を分かりやすくするために、図面のある要素の寸法は、他の要素より誇張してある。

##### 【0006】

本発明を実行するためのモードについては、以下にさらに詳細に説明する。この説明は

10

20

30

40

50

、本発明を制限するものではない。

一態様においては、本発明は、複数の各メモリセルが、メモリセル電力供給電圧を受け取るための電力供給電圧ノードを含んでいる行および列の形に配置されている複数のメモリセルを含む集積回路を提供する。この場合、メモリセルの行は、ワード線、およびワード線と結合しているすべてのメモリセルを含んでいる。メモリセルの列は、真のおよび／または補足のビット線、およびビット線と結合しているすべてのメモリセルを含む。この集積回路は、さらに、複数の各メモリセルの電力供給電圧ノードと結合しているメモリセル電力供給多重化回路、書き動作中メモリセルの選択した列の電力供給電圧ノードに、第1の電力供給電圧を供給するためのメモリセル電力供給多重化回路、書き動作中にすべての選択されなかった列の電力供給電圧ノードに第1の電力供給電圧より高い第2の電力供給電圧を供給するためのメモリセル電力供給多重化回路を含むことができる。集積回路は、さらに、複数の各メモリセルの電力供給電圧ノードに結合している放電回路を含むことができる。この放電回路は、書き動作の第1の部分中に、メモリセルの選択した列のメモリセル供給電圧端末上の電圧を、第1の電力供給電圧から第1の電力供給電圧より低い所定の電圧に変更するためのものである。

#### 【0007】

さらに他の態様においては、本発明は、集積回路メモリにアクセスするための方法を提供する。この方法は、それぞれが、電力供給電圧ノード、および記憶ノードとビット線の間に結合しているアクセス・トランジスタを有する複数のメモリセルを提供するステップを含むことができる。この方法は、さらに、第1の電力供給電圧を受け取るステップを含むことができる。この方法は、さらに、第1の電力供給電圧より高い第2の電力供給電圧を受け取るステップを含むことができる。この方法は、さらに、書き動作中メモリセルの選択した列の電力供給電圧ノードに供給するために、第1の電力供給電圧を選択するステップを含むことができる。この方法は、さらに、書き動作中メモリセルの選択しなかった列の電力供給電圧ノードに供給するために、第2の電力供給電圧を選択するステップを含むことができる。この方法は、さらに、書き動作の最初の部分中にメモリセルの選択した列の電力供給電圧ノードを、第1の電力供給電圧から第1の電力供給電圧より低い所定の電圧に放電するステップを含むことができる。

#### 【図面の簡単な説明】

#### 【0008】

【図1】本発明の一実施形態によるメモリを有する例示としての集積回路図。

【図2】本発明の一実施形態による図1のメモリの例示としての一部の図面。

【図3】本発明の一実施形態によるビットセルの例示としての実施態様の図面。

【図4】本発明の一実施形態によるビットセル電圧マルチプレクサの例示としての実施態様の図面。

【図5】本発明の一実施形態による図3のビットセルの読み出動作のための例示としてのタイミング図。

【図6】本発明の一実施形態による図3のビットセルの書き動作のための例示としてのタイミング図。

【図7】本発明の一実施形態によるビットセルの書きマージンを改善するための例示としての回路図。

#### 【発明を実施するための形態】

#### 【0009】

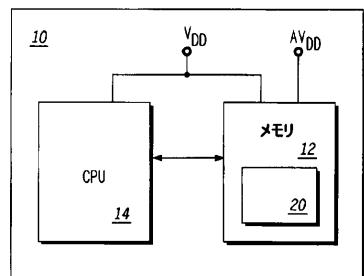

図1を参照すると、この図は、本発明の一実施形態によるメモリを含む例示としての集積回路の図を示す。例を挙げて説明すると、集積回路10は、CPU14と結合しているメモリ12を含むことができる。メモリ12およびCPU14は、V<sub>DD</sub>電圧端子を介して電圧の供給を受けることができる。さらに、メモリ12は、AV<sub>DD</sub>電圧端子を介して他の電圧の供給を受けることができる。それ故、V<sub>DD</sub>電圧端子は、CPUに対する動作電圧を供給するために使用することができる。AV<sub>DD</sub>電圧端子は、メモリ12のビットセル・アレイのようなメモリ12の少なくとも一部に電圧を供給するために使用すること

10

20

30

40

50

ができる。各ビットセルは、書込マージンおよび読出マージンを有することができ、書込マージンは、読出マージンよりもかなり大きいものであってもよい。例を挙げて説明すると、ビットセルは、スタティック・ランダム・アクセス・メモリセルであってもよい。 $V_{DD}$ 電圧端子は、集積回路10に対する外部ピンまたは接続部であってもよい。 $A V_{DD}$ 電圧端子は、また、集積回路10に対するもう1つの外部ピンまたは接続部であってもよい。別の方針としては、 $A V_{DD}$ 電圧端子は、集積回路10内に位置するものであってもよい。それ故、この端子に供給される電圧は、集積回路10内で発生することができる。 $A V_{DD}$ 電圧端子に供給される電圧は、例えば、充電ポンプにより発生することができる。 $A V_{DD}$ 電圧端子に供給される電圧は、また、RCネットワークと接続している位相オフセット・ループ( $PLL$ )電圧から発生することもできる。これら電圧を発生するための他の手段も使用することもできる。さらに、図1は、1つのメモリおよび1つのCPUしか図示していないが、集積回路10は、追加のメモリおよび/またはCPUを含むことができる。さらに、集積回路10は、集積回路10の動作のために必要な追加の構成要素を含むことができる。メモリ12は、キャッシュとして実施することができる。メモリ12は、また、スタティックRAMのようなスタンダードアロン・メモリとして実施することもできる。

#### 【0010】

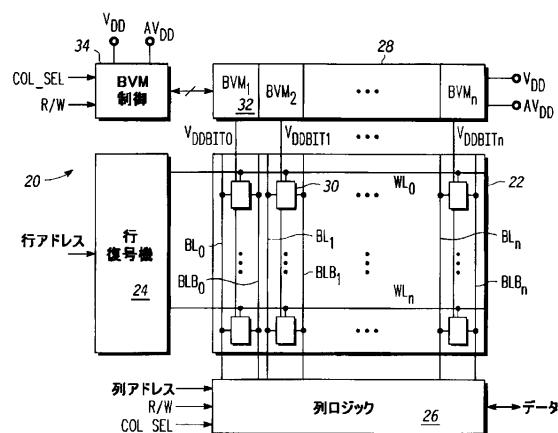

図2は、本発明の一実施形態による図1のメモリの例示としての一部の図面を示す。メモリ12の一部20は、ビットセル・アレイ22、行デコーダ24および列論理ブロック26を含むことができる。行デコーダ24および列論理ブロック26は、ビットセル・アレイ22のビットセル30のようなビットセルから/へデータの読出/書込を行うために使用することができる。行デコーダ24は、例えば、CPU14から行アドレス( $ROW\_ADDR$ )信号を受信することができる。列論理ブロック26は、列アドレス( $COL\_ADDR$ )信号、読出/書込( $R/W$ )信号、および列選択( $COL\_SEL$ )信号のような種々の信号を受信することができる。行デコーダ24および列論理ブロック26は、追加の信号を含むことができる。列論理ブロック26は、例えば、CPU14からデータ( $DATA$ )を提供することもできるし、および/またはデータ( $DATA$ )を受信することもできる。メモリの一部20のビットセル30および他の類似のビットセルには、ワード線 $WL_0 \sim WL_n$ およびビット線 $BL_0 \sim BL_n$ および $B LB_0 \sim B LB_n$ を使用してアクセスすることができる。例を挙げて説明すると、ビットセル30のようなビットセルは、メモリの一部20の一部として行および列の形に配列される。ビットセルの各列は、列論理ブロック26と結合することができる。ビットセルの各列は、さらに、ビットセル電圧マルチプレクサ( $B VM$ )32と結合することができる。それ故、メモリの一部20内の列と同じ数の $B VM$ 28を含むことができる。各 $B VM$ 32は、ビットセルの対応する列に電圧を結合することができる。それ故、例えば、 $B VM_S$ 、 $B VM_0$ 、 $B VM_1$ および $B VM_n$ は、それぞれ電圧端子 $V_{DDB1T0}$ 、 $V_{DDB1T1}$ および $V_{DDB1Tn}$ に電圧を結合することができる。各 $B VM$ 32は、さらに、 $V_{DD}$ 電圧端子および $A V_{DD}$ 電圧端子に対応する電圧を受け取ることができる。制御信号をベースとする各 $B VM$ 32は、 $V_{DD}$ 電圧端子に結合している電圧またはその対応する $V_{DDB1T}$ 端子への $A V_{DD}$ 電圧端子と結合している電圧を結合することができる。それ故、 $B VM_S$ 28を使用して、(書込動作のような)特定の動作中に、特定の列を $V_{DD}$ 電圧端子と結合することができ、一方、他の列を $A V_{DD}$ 電圧端子と結合することができる。各 $B VM$ 32は、 $B VM$ 制御ブロック34から制御信号を受信することができる。 $B VM$ 制御ブロック34は、また、 $V_{DD}$ 電圧端子および $A V_{DD}$ 電圧端子に対応する電圧、読出/書込( $R/W$ )信号、および列選択( $COL\_SEL$ )信号を受信することもできる。

#### 【0011】

書込動作中、 $B VM_S$ 28は、書込中の列に対応する $V_{DDB1T}$ 端子が、プロセッサに供給している電圧とほぼ等しい電圧、すなわち、 $V_{DD}$ 電圧端子に供給中の電圧から、ダイオードと接続しているp-MOSトランジスタに対応するしきい値電圧を差し引いた電圧に切り替わるように、 $B VM$ 制御装置34により制御することができる。一方、ビッ

10

20

30

40

50

トセル・アレイ 22 の書込が行われていない他の列の  $V_{DDBI_T}$  端子は、 $A_{VDD}$  電圧端子に供給中の電圧に結合される。別の方針としては、書込中の列に対応する  $V_{DDBI_T}$  端子は、 $V_{DD}$  電圧端子に供給中の電圧に維持することができる。一方、ビットセル・アレイ 22 の書込が行われていない他の列の  $V_{DDBI_T}$  端子は、 $A_{VDD}$  電圧端子に供給中の電圧に切り替わることができる。書込のために選択されなかつた列は、アサートしたワード線と結合しているビットセルを含むことに留意されたい。実際には、これらのビットセルの記憶ノードは、予め充電したビット線に曝され、それにより疑似読出動作を誘起する。それ故、 $V_{DDBI_T}$  端子がより高い  $A_{VDD}$  に切り替わることにより、これらのビットセルの読出マージンおよびその堅牢性が改善される。何故なら、プロセッサ電圧供給  $V_{DD}$  が低くなるからである。読出動作中、ビットセル・アレイ 22 のすべての列に 10 対応する  $V_{DDBI_T}$  端子を、 $V_{DD}$  電圧端子に供給中の電圧から  $A_{VDD}$  電圧端子へ供給中の電圧に切り替えることができる。スタンバイ・モード中、ビットセル・アレイ 22 のすべての列に対応する  $V_{DDBI_T}$  端子を、 $V_{DD}$  電圧に供給中の電圧からダイオードに接続している p-MOS ドラッグ・レジスタのしきい値電圧を差し引いたものに切り替えることができる。当業者であれば、BVM 制御装置 34 を、本明細書に記載する明細とは異なる方法で、BVMs 28 の行動を修正する追加の入力信号を受信するように、さらに構成することができます。 20 することを理解することができるだろう。例えば、 $V_{DDBI_T}$  端子の  $A_{VDD}$  電圧端子への切替を、プロセッサ  $V_{DD}$  電圧が、あるレベル以上である場合には、ビットセルが、その  $V_{DDBI_T}$  端子のところでもっと高い  $A_{VDD}$  電圧を必要としないよう、十分堅牢なものになるように動作不能にすることができる。別の方針としては、ビットセルの堅牢性をもっと完全なものにすることができるよう、この切替をできないよう 20 にすることができる。

### 【0012】

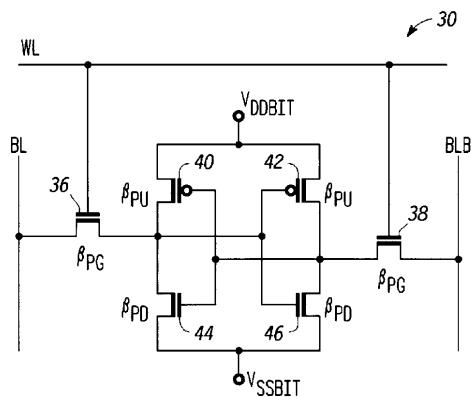

図 3 は、本発明の一実施形態によるビットセルの例示としての実施態様の図面を示す。例示としてのビットセル 30 は、6 つのトランジスタ・セルとして実施することができる。例を挙げて説明すると、図 3 に示すように、ビットセル 30 は、その電流端子のうちの 1 つがビット線 BL に結合し、またその制御端子がワード線 WL に結合しているバス・トランジスタ 36 を含むことができる。ビットセル 30 は、さらに、その電流端子のうちの 1 つがビット線 BLB に結合し、またその制御端子がワード線 WL に結合している他のバス・トランジスタ 38 を含むことができる。ビットセル 30 は、さらに、 $V_{DDBI_T}$  電圧端子と結合しているその電流端子のうちの 1 つを含むプルダウン・トランジスタ 40 を含むことができる ( $V_{DDBI_T}$  端子は、 $V_{DDBI_{T0}}$ 、 $V_{DDBI_{T1}}$ 、および  $V_{DDBI_{Tn}}$  のような  $V_{DDBI_T}$  端子のうちの任意のものであってもよい)。ビットセル 30 は、さらに、 $V_{DDBI_T}$  電圧端子と結合しているその電流端子のうちの 1 つを含む他のプルアップ・トランジスタ 42 を含むことができる。ビット・セル 30 は、さらに、接地電圧  $V_{SSBI_T}$  端子と結合しているその電流端子のうちの 1 つを含むプルダウン・トランジスタ 44 を含むことができる。ビット・セル 30 は、さらに、電圧  $V_{SSBI_T}$  端子と結合しているその電流端子のうちの 1 つを含む他のプルダウン・トランジスタ 46 を含むことができる。図 3 の場合には、ビットセル 30 は、6 つのトランジスタを使用して実施されているが、ビットセル 30 は、例えば、8 つのトランジスタのようなもっと多くのトランジスタを使用して実施することもできる。 40

### 【0013】

ビットセル 30 は、ビットセル 30 に書込が行われているのかまたはビットセル 30 から読出が行われているのかにより、 $V_{DDBI_T}$  電圧端子および  $V_{SSBI_T}$  電圧端子を介して異なる供給電圧を受け取ることができるので、ビットセル 30 を含むトランジスタのコンダクタンスをよりよい性能を發揮することができるように調整することができる。例を挙げて説明すると、ビットセルの読出動作中、 $V_{DDBI_T}$  電圧端子は、 $A_{VDD}$  電圧端子に供給中の電圧と結合され、ビットセルの書込動作中は、 $V_{DDBI_T}$  電圧端子は、 $V_{DD}$  端子に供給中の電圧またはこの電圧より低いしきい値電圧と結合される。例を挙げて説明すると、バス・トランジスタ 36 のコンダクタンス  $P_G$  は、ビットセル 30 が 50

、書込動作中、 $V_{DD}$ 電圧端子と結合している電圧またはこの電圧より低いしきい値電圧を受け取ることができるように構成されているか否かにより、プルアップ・トランジスタ40のコンダクタンス $P_U$ に対して異なるように設定することができる。例えば、コンダクタンス比 $P_G / P_U$ は、ビットセル30が書込動作中、 $V_{DD}$ 電圧端子と結合している電圧を受け取ることができるように構成されている場合には、増大することができる。同様に、バス・トランジスタ38およびプルアップ・トランジスタ42に対応するコンダクタンス比 $P_G / P_U$ も増大することができる。プルダウン・トランジスタ44および46のような他のトランジスタのコンダクタンスも、必要に応じて調整することができる。例えば、プルダウン・トランジスタ44および46のコンダクタンス $P_D$ を、書込マージンを改善するために低減することができる。しかし、このことは、読出マージンにも悪影響を与えない。何故なら、読出動作中、より高い $A_{VDD}$ 電圧端子に $V_{DBIT}$ 電圧端子が結合しているので、読出マージンが改善されるからである。すなわち、読出動作中、より高い $A_{VDD}$ 電圧端子に $V_{DBIT}$ 電圧端子が結合するために読出マージンが改善されるので、ビットセルの設計者が、書込マージンも同様に改善することができるからである。他の利点を達成するために、トランジスタのコンダクタンス値を他の方法で設定することができる。例を挙げて説明すると、トランジスタのコンダクタンス値を設定することにより、場合によっては、メモリセルの書込マージンを、読出マージンよりかなり大きくすることができる。例えば、書込マージンを、書込マージンと読出マージンとのバランスがとれている場合より少なくとも20%大きくなるようにすることができる。このことは、メモリセル・プルアップ・トランジスタに対するメモリセル・アクセス・トランジスタのコンダクタンス比を設定することにより達成することができる。別 の方法としては、場合によっては、メモリセルの読出マージンを書込マージンよりかなり大きくすることができる。

#### 【0014】

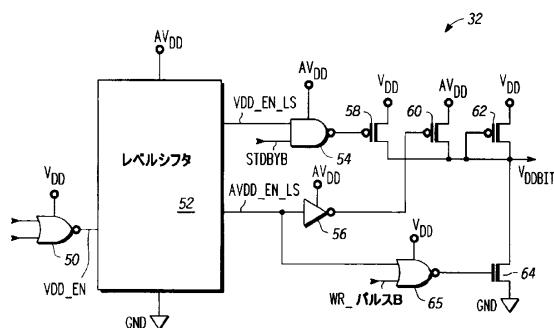

図4は、本発明の一実施形態によるビットセル電圧マルチプレクサの例示としての実施態様の図面を示す。例を挙げて説明すると、ビットセル電圧マルチプレクサ(BVM)32は、NORゲート50、レベル・シフタ52、NANDゲート54、インバータ56、p-MOSトランジスタ58、60、62、n-MOSトランジスタ64、およびNORゲート65を使用して実施することができる。 $V_{DD}$ 電圧端子と結合しているNORゲート50は、列選択(COLSELB)信号、および書込イネーブル(WREN)信号を受信することができる。 $A_{VDD}$ 電圧端子と結合しているレベル・シフタ52は、NORゲート50の出力を $VDD$ 電圧レベルから $A_{VDD}$ 電圧レベルにシフトするために使用することができる。信号処理のこの段階ではレベルをシフトする必要はない。何故なら、このシフトは、例えば、BVM制御装置34の一部である他の段階で行うことができるからである。書込動作中、書込中の列に対応する $V_{DBIT}$ 端子を $V_{DD}$ 電圧端子と結合することができ、一方、ビットセル・アレイ22の書込が行われていない他の列の $V_{DBIT}$ 端子を $A_{VDD}$ 電圧端子に切り替えることができる。BVM32の動作の場合、書込動作中、信号COLSELBおよびWRENは両方とも、書込を行う列を選択するために論理ローになっている。この場合、NORゲート50は、高 $VDD\_EN$ 信号を発生する。レベル・シフタ52は、2つの出力、すなわち $VDD\_EN$ 信号のレベルをシフトすることにより発生した $VDD\_EN\_LS$ 、および $VDD\_EN$ 信号を反転し、レベル・シフトすることにより発生した $A_{VDD\_EN\_LS}$ 信号を発生する。 $VDD\_EN\_LS$ 信号は、NANDゲート54に供給された場合に、p-MOSトランジスタ58のゲートのところで低レベル信号を発生するので、対応する $V_{DBIT}$ 端子は、 $V_{DD}$ 電圧端子に接続する。信号COLSELBは、書込が行われていないこれらの列に対して、論理ハイである。そのため、NORゲート50の出力は、低 $VDD\_EN$ 信号を発生する。それ故、これらの列に対応する $V_{DBIT}$ 端子は、 $V_{DD}$ 電圧端子から $A_{VDD}$ 電圧端子へと切り替わる。

#### 【0015】

別 の方法としては、書込動作中、書込中の列に対応する $V_{DBIT}$ 端子は、 $V_{DD}$ 電

10

20

30

40

50

圧端子のところの電圧からダイオードに接続している p - M O S トランジスタ 6 2 に対応するしきい値電圧を差し引いたものにほぼ等しい電圧に切り替わり、一方、ビットセル・アレイ 2 2 の他の列の V<sub>DDBIT</sub> 端子は、 A V<sub>DD</sub> 電圧端子と結合する。このことは、トランジスタ 5 8 をオフにする N A N D ゲート 5 4 の出力のところのハイ信号となる N A N D ゲート 5 4 の他の入力のところの低いスタンバイ S T D B Y B 信号をアサートすることにより達成することができる。書込動作の一部としての図 4 について引き続き説明すると、書込中の列に対応する V<sub>DDBIT</sub> 端子が V<sub>DD</sub> 電圧端子と結合している電圧から、ダイオードと接続している p - M O S トランジスタ 6 2 に対応するしきい値電圧を差し引いたものとほぼ等しい電圧に切り替わると、アースと結合している n - M O S トランジスタ 6 4 がオンになり、 V<sub>DDBIT</sub> 端子のところの電圧が放電され、そのため、元の電圧（プロセッサおよびメモリの他の列と結合している電圧）から、 V<sub>DD</sub> 電圧端子と結合している電圧からダイオードと接続している p - M O S トランジスタ 6 2 に対応するしきい値電圧を差し引いたものに等しい電圧への遷移が、ビットセル漏洩により行われる遷移より迅速に行われる。例を挙げて説明すると、 n - M O S トランジスタ 6 4 は、 N O R ゲート 6 5 の出力からそのゲート信号を受信することができ、 N O R ゲート 6 5 は、 A V D D \_ E N \_ L S 信号および書込パルス（ W R \_ P U L S E B ）信号を受信することができる。N O R ゲート 6 5 の出力は、 n - M O S トランジスタ 6 4 が導通状態のままでいる所定の時間の間アサートされたままである。当業者であれば、 N O R ゲート 6 5 の出力の正確な電圧レベルが、 V<sub>DDBIT</sub> 端子がプルダウンされる速度を決定し、出力のパルス幅が、 V<sub>DDBIT</sub> 電圧が低減する大きさを決定することを理解することができるだろう。それ故、電圧レベルまたは n - M O S トランジスタ 6 4 のゲートに信号が結合されている時間を、本発明の上記実施形態により変更することができる。N O R ゲート 6 5 がアサートされたままでいなければならない時間は、 V<sub>DDBIT</sub> 端子のキャパシタンスおよび n - M O S トランジスタ 6 4 のコンダクタンスのような特性に依存する。これらの特性は、製造プロセスの変動の影響を受けるので、ある実施形態は、集積回路が製造された後でパルス幅を調整することができる追加の外部トリミング信号を含む。

10

20

#### 【 0 0 1 6 】

図 4 について引き続き説明すると、読出動作中、ビットセル・アレイ 2 2 のすべての列に対応する V<sub>DDBIT</sub> 端子を、 V<sub>DD</sub> 電圧端子と結合している電圧から、 A V<sub>DD</sub> 電圧端子と結合している電圧に切り替えることができる。例を挙げて説明すると、このことは、信号 W R E N B を（読出動作に対応する）ハイにし、それ故、 N O R ゲート 5 0 に低 V<sub>DD\_E\_N</sub> 信号を発生させ、それ故、 A V D D \_ E N \_ L S 信号をハイにすることにより達成することができる。高 A V D D \_ E N \_ L S 信号は、インバータ 5 6 により反転した場合、トランジスタ 6 0 をオンにし、その結果、対応する V<sub>DDBIT</sub> 端子は、 A V<sub>DD</sub> 電圧端子と結合している電圧に切り替えられる。それ故、トランジスタ 6 0 は、特定の列と結合している電圧をブーストするためのブースト回路として機能することができる。各 B V M 3 2 は、読出動作中、 B V M のうちの 1 つを参照しながら説明するように、このブースト動作を行うことができる。

30

#### 【 0 0 1 7 】

スタンバイ・モード中、ビットセル・アレイ 2 2 のすべての列に対応する V<sub>DDBIT</sub> 端子は、 V<sub>DD</sub> 電圧端子と結合している電圧からダイオードと接続している p - M O S トランジスタ 6 2 のしきい値電圧を差し引いたものに切り替えることができる。それは、 N A N D ゲート 5 4 の他の入力のところでスタンバイ S T A N B Y 信号をアサートすることにより、トランジスタ 5 8 をオフにする N A N D ゲート 5 4 の出力のところの信号がハイになるからであり、トランジスタ 6 0 がオフになり、 V<sub>DDBIT</sub> 端子が、 V<sub>DD</sub> 電圧端子と結合している電圧から、ダイオードに接続している p - M O S トランジスタ 6 2 に対応するしきい値電圧を差し引いたものとほぼ等しい電圧に切り替わるからである。別の方 40 法としては、および / または追加として、スタンバイ・モード中、 V<sub>DD</sub> 電圧端子と結合している電源とは異なる電源および A V<sub>DD</sub> 電圧端子を使用することができる。図 4 は、 V<sub>DDBIT</sub> 端子のところで異なる電圧入手するための構成要素の特定の配置を示して

50

いるが、同様に、 $V_{DDBI_T}$  端子のところで異なる電圧を入手するために構成要素の他の配置を使用することもできる。当業者であれば、さらに、図4は、メモリ・アレイに対する動作の読み出、書き込みおよびスタンバイ・モードを含む完全な電圧切替の解決方法を示していることを理解することができるだろう。しかし、図4の要素の一部だけを含む他の電圧切替解決方法も、本発明のある実施形態により実施することができることも理解されたい。

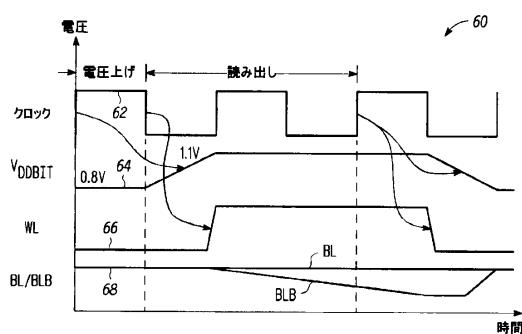

### 【0018】

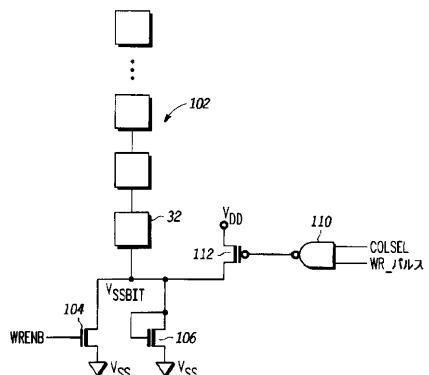

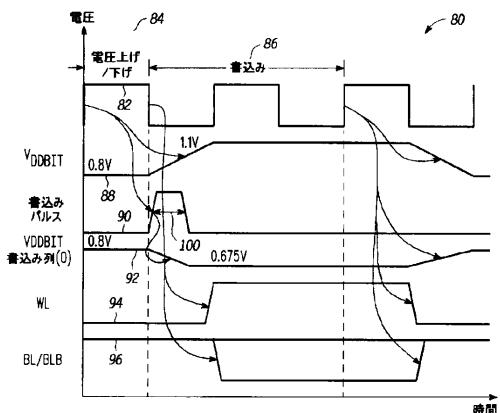

図5は、本発明の一実施形態による図3のピットセルの読み出動作のための（電圧対時間）の例示としてのタイミング図60を示す。例を挙げて説明すると、ピットセル30の動作の一部として、 $V_{DDBI_T}$  端子と結合している電圧を、 $V_{DD}$  電圧端子と結合している電圧から、 $AV_{DD}$  電圧端子と結合している電圧に切り替えるためにクロック62の半サイクルを使用することができる。クロック・サイクルのこの部分は、クロック・スキームの電圧ブースト部分として図示してある。それ故、例えば、 $V_{DDBI_T}$  端子と結合している電圧を、（ $V_{DD}$  電圧端子と結合している電圧が0.8ボルトに設定されたものと仮定して）0.8ボルトから、（ $AV_{DD}$  電圧端子と結合している電圧が1.1ボルトに設定されたものと仮定して）1.1ボルトに切り替えることができる。図5に示すように、クロック62の立ち上がり縁部を、 $V_{DDBI_T}$  端子のところの電圧64を、 $V_{DD}$  電圧端子と結合している電圧から、 $AV_{DD}$  電圧端子と結合している電圧への切替をトリガるために使用することができる。クロック62の立ち下がり縁部を、読み出動作を行う目的でワード線信号WL66をアサートするために使用することもできる。BL/BLB信号68は、それに応じて応答することができる。図6は、本発明の一実施形態による図3のピットセルの書き込み動作のための例示としてのタイミング図80（電圧対時間）を示す。ピットセル30の動作の一部として、 $V_{DDBI_T}$  端子と結合している電圧を、 $V_{DD}$  電圧端子と結合している電圧から、 $AV_{DD}$  電圧端子と結合している電圧に切り替えるために、クロック82の半サイクルを使用することができる。クロック・サイクルのこの部分は、クロック・スキームの電圧ブースト／低減部分84として図示してある。書き込みのために選択した列は、 $V_{DD}$  電圧端子と同じ電圧またはそれより低い電圧と結合しているその $V_{DDBI_T}$  端子を有する。選択しなかった列は、 $AV_{DD}$  電圧端子にブーストしたその $V_{DDBI_T}$  端子を有する。それ故、例えば、 $V_{DDBI_T}$  端子と結合している電圧88を、（ $V_{DD}$  電圧端子と結合している電圧が0.8ボルトに設定されたものと仮定して）0.8ボルトから、（ $AV_{DD}$  電圧端子と結合している電圧が1.1ボルトに設定されたものと仮定して）1.1ボルトに切り替えることができる。書き込み動作中、クロック82の立ち上がり縁部は、また、書き込みパルス（WRITEPULSE）信号90をトリガする。アサートしたWRITEPULSE信号90は、 $V_{DDBI_T}$  電圧端子と結合している電圧を、 $V_{DD}$  電圧端子と結合している電圧から、 $V_{DD}$  電圧端子と結合している電圧から、ダイオードと接続しているp-MOSトランジスタ（例えば、図4のp-MOSトランジスタ62など）のしきい値電圧を差し引いたものに切り替える。例を挙げて説明すると、 $V_{DDBI_T}$  端子のところの電圧は、0.8ボルトから0.675ボルトに切り替えることができる。クロック82の立ち下がり縁部も、ピットセル30に論理0が書き込まれているのか、論理1が書き込まれているのかに基づいて、アサートされているワード線WL信号94、およびアサート解除中のBLまたはBLB信号96になることができる。

### 【0019】

図7に示すように、ピットセル30の書き込みマージンも、 $V_{SSBI_T}$  端子に修正した接地供給電圧を供給することにより改善することができる。例を挙げて説明すると、ピットセルの列102に対応する書き込み動作中、書き込みネーブル信号（WREN）信号は、n-MOSトランジスタ104をオフにすることができる。これにより、 $V_{SSBI_T}$  端子のところの電圧は、n-MOSトランジスタ106のしきい値電圧に変化する。 $V_{SSBI_T}$  端子のところの電圧は、NANDゲート110を使用して、p-MOSトランジスタ112をオンにすることにより、n-MOSトランジスタ106のしきい値電圧に迅速にブ

10

20

30

40

50

ルすることができる。図では、NANDゲートは、COLSELおよびWR\_PULSEを受信している。信号COLSELおよびWR\_PULSEをアサートすると、p-MOSトランジスタ112がオンになり、それにより、そうでない場合にはビットセル漏洩により行うよりは、迅速にV<sub>SSBT</sub>端子をn-MOSトランジスタ106のしきい値電圧にプルアップすることができる。NANDゲート110の出力は、p-MOSトランジスタ112が導通状態のままである所定の時間の間アサート解除されたままである。当業者であれば、NANDゲート110の出力の正確な電圧レベルが、V<sub>SSBT</sub>端子がプルダウンされる速度を決定し、出力のパルス幅が、V<sub>SSBT</sub>電圧が増大する大きさを決定することを理解することができるだろう。それ故、本発明の実施形態によれば、電圧レベルまたはp-MOSトランジスタ112のゲートに信号が結合されている時間を変更することができる。NANDゲート110がアサート解除されたままでいなければならぬ時間は、V<sub>SSBT</sub>端子のキャパシタンスおよびp-MOSトランジスタ112のコンダクタンスのような特性に依存する。これらの特性は、製造プロセスの変動の影響を受けるので、一実施形態は、集積回路が製造された後でパルス幅を調整することができる追加の外部トリミング信号を含む。図7は、V<sub>SSBT</sub>端子のところで（実質的にゼロ電圧である）アースより高い電圧を入手するための構成要素の特定の配置を示しているが、V<sub>SSBT</sub>端子のところでもっと高い電圧を入手するために構成要素の他の配置を使用することもできる。図7の信号WRENBは、列102内のビットセルの漏洩が削減されるようにスタンバイ・モード中にアサート解除することに留意されたい。

#### 【0020】

今まで特定の実施形態を参照しながら本発明を説明してきたが、通常の当業者であれば、添付の特許請求の範囲に記載する本発明の範囲から逸脱することなしに、種々の修正および変更を行うことができることを理解することができるだろう。それ故、本明細書および図面は、例示としてのものであって、本発明を制限するものでないと解釈すべきであり、すべてのこののような修正は、本発明の範囲に含まれる。

#### 【0021】

特定の実施形態を参照しながら、今まで利益、他の利点および問題の解決方法を説明してきた。しかし、利益、利点、問題の解決方法、および利益、利点、または問題の解決方法をもたらす、またはより顕著なものにする任意の要素を、任意のまたはすべての請求項の重要な、必要な、または本質的な機能または要素であると解釈すべきではない。本明細書で使用する場合、「備える」「備えている」またはその任意の他の派生語は、非排他的に内容物をカバーするためのものであるので、要素のリストを含むプロセス、方法、物品または装置は、これらの要素だけを含んでいるのではなく、リストに明示されていないまたはこのようなプロセス、方法、物品または装置に固有な他の要素を含むことができる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

---

フロントページの続き

(72)発明者 ラッセル、アンドリュー シー。

アメリカ合衆国 78735 テキサス州 オースティン エスダブリュ パークウェイ 560

4 ナンバー 2633

(72)発明者 バーデン、デイビッド アール。

アメリカ合衆国 78739 テキサス州 オースティン デッドハム レーン 6203

(72)発明者 バーネット、ジェームズ デイ。

アメリカ合衆国 78731 テキサス州 オースティン ローレル レッジ レーン 3804

(72)発明者 クーパー、トロイ エル。

アメリカ合衆国 78704 テキサス州 オースティン ピクトリー ドライブ 4017 ナ

ンバー 125

(72)発明者 チャン、シャヤン

アメリカ合衆国 78750 テキサス州 オースティン スコティッシュ パスチャーズ コー

ブ 9111

審査官 小林 紀和

(56)参考文献 特開2006-085786(JP,A)

特開2002-197867(JP,A)

特開2003-060077(JP,A)

特開2004-241021(JP,A)

特開2003-022677(JP,A)

特開2003-016786(JP,A)

特開昭58-211391(JP,A)

特開2003-059273(JP,A)

特開2005-025907(JP,A)

特表2005-512261(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11 / 413