# (19) World Intellectual Property Organization

International Bureau

# (43) International Publication Date

17 August 2006 (17.08.2006)

(51) International Patent Classification:

H04B 1/02 (2006.01) H04B 1/66 (2006.01)

H04B 1/04 (2006.01)

(21) International Application Number:

PCT/US2006/002973

(22) International Filing Date: 26 January 2006 (26.01.2006)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

11/055,525

9 February 2005 (09.02.2005)

- (71) Applicant (for all designated States except US): PULSE-LINK, INC. [US/US]; 1969 Kellogg Avenue, Carlsbad, CA 92008 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): LAKKIS, Ismail [LB/US]; 10131 Prairie Springs Road, San Diego, CA 92127 (US). BAHREINI, Yasaman [US/US]; 11271 Carmel Creek Road, San Diego, CA 92130 (US). SAN-THOFF, John [US/US]; 6434 Kinglet Way, Carlsbad, CA 92009 (US).

- (74) Agent: MARTINEZ, Peter, R.; Pulse-Link, Inc., 1969 Kellogg Avenue, Carlsbad, CA 92008 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

(10) International Publication Number WO 2006/086168 A2

AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: HIGH DATA RATE TRANSMITTER AND RECEIVER

(57) Abstract: A high-speed tansmitter and receiver are provided. In one embodiment, a transmitter comprises a baseband processor structured to receive data and to convert the data into a multiplicity of high and low signal values, with each high and low signal value having a first timing interval. A local oscillator generates a clock signal at a second timing interval and a digital circuit combines the high and low signal values with the clock signal to produce a transmission signal directly at a transmission frequency. A receiver is configured to receive the signal. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules that allow a reader to quickly ascertain the subject matter of the disclosure contained herein. This Abstract is submitted with the explicit understanding that will not be used to interpret or to limit the scope or the meaning of the claims.

## HIGH DATA RATE TRANSMITTER AND RECEIVER

#### 1. Field of the Invention

The invention relates generally to communications, and more particularly to systems and methods for high data rate communications.

#### 2. Background

Wireless communication systems are proliferating at the Wide Area Network (WAN), Local Area Network (LAN), and Personal Area Network (PAN) levels. These wireless communication systems use a variety of techniques to allow simultaneous access to multiple users. The most common of these techniques are Frequency Division Multiple Access (FDMA), which assigns specific frequencies to each user, Time Division Multiple Access (TDMA), which assigns particular time slots to each user, and Code Division Multiple Access (CDMA), which assigns specific codes to each user. But these wireless communication systems and various modulation techniques are afflicted by a host of problems that limit the capacity and the quality of service provided to the users. The following paragraphs briefly describe a few of these problems for the purpose of illustration.

One problem that can exist in a wireless communication system is multipath interference. Multipath interference, or multipath, occurs because some of the energy in a transmitted wireless signal bounces off of obstacles, such as buildings or mountains, as it travels from source to destination. The obstacles in effect create reflections of the transmitted signal and the more obstacles there are, the more reflections they generate. The reflections then travel along their own transmission paths to the destination (or receiver). The reflections will contain the same information as the original signal; however, because of the differing transmission path lengths, the reflected signals will be out of phase with the original signal. As a result, they will often combine destructively with the original signal in the receiver. This is referred to as fading. To combat fading, current systems typically try to estimate the multipath effects and then compensate for them in the receiver using an equalizer. In practice, however, it is very difficult to achieve effective multipath compensation.

A second problem that can affect the operation of wireless communication systems is interference from adjacent communication cells within the system. In FDMA/TDMA systems, this type of interference is prevent through a frequency reuse plan. Under a frequency reuse plan, available communication frequencies are allocated to communication cells within the communication system such that the same frequency will not be used in adjacent cells. Essentially, the available frequencies are split into groups. The number of groups is termed the reuse factor. Then the communication cells are grouped into clusters, each cluster containing the same number of cells as there are frequency groups. Each frequency group is then assigned to a cell in each cluster. Thus, if a frequency reuse factor of 7 is used, for example, then a particular communication frequency will be used only once in every seven communication cells. Thus, in any group of seven communication cells, each cell can only use  $1/7^{th}$  of the available frequencies, i.e., each cell is only able to use  $1/7^{th}$  of the available bandwidth.

In a CDMA communication system, each cell uses the same wideband communication channel. In order to avoid interference with adjacent cells, each communication cell uses a particular set of spread spectrum codes to differentiate

communications within the cell from those originating outside of the cell. Thus, CDMA systems preserve the bandwidth in the sense that they avoid reuse planning. But as will be discussed, there are other issues that limit the bandwidth in CDMA systems as well. Thus, in overcoming interference, system bandwidth is often sacrificed. Bandwidth is becoming a very valuable commodity as wireless communication systems continue to expand by adding more and more users. Therefore, trading off bandwidth for system performance is a costly, albeit necessary, proposition that is inherent in all wireless communication systems.

The foregoing are just two examples of the types of problems that can affect conventional wireless communication systems. The examples also illustrate that there are many aspects of wireless communication system performance that can be improved through systems and methods that, for example, reduce interference, increase bandwidth, or both. Not only are conventional wireless communication systems effected by problems, such as those described in the preceding paragraphs, but also different types of systems are effected in different ways and to different degrees. Wireless communication systems can be split into three types: 1) line-of-sight systems, which can include point-to-point or point-to-multipoint systems; 2) indoor non-line of sight systems; and 3) outdoor systems such as wireless WANs. Line-of-sight systems are least affected by the problems described above, while indoor systems are more affected, due for example to signals bouncing off of building walls. Outdoor systems are by far the most affected of the three systems. Because these types of problems are limiting factors in the design of wireless transmitters and receivers, such designs must be tailored to the specific types of system in which it will operate. In practice, each type of system implements unique communication standards that address the issues unique to the particular type of system. Even if an indoor system used the same communication protocols and modulation techniques as an outdoor system, for example, the receiver designs would still be different because multipath and other problems are unique to a given type of system and must be addressed with unique solutions. This would not necessarily be the case if cost efficient and effective methodologies can be developed to combat such problems as described above that build in programmability so that a device can be reconfigured for different types of systems and still maintain superior performance.

## **SUMMARY OF THE INVENTION**

In order to combat the above problems, a high data rate transmitter and receiver are provided. In one embodiment, a transmitter comprises a baseband processor structured to receive data and to convert the data into a multiplicity of high and low signal values, with each high and low signal value having a first timing interval. A local oscillator generates a clock signal at a second timing interval and a digital circuit combines the high and low signal values with the clock signal to produce a transmission signal directly at a transmission frequency.

The radio frequency used for transmission may range up to 11 Giga-Hertz, and production of the transmission signal directly at the transmission frequency is possible by use of a high-speed oscillator.

A receiver is structured to receive the communication signal, which in one embodiment, may have a fractional bandwidth that may range between approximately 20 percent and approximately 200 percent. The receiver includes a high-speed analog to digital converter configured to directly convert the radio frequency signal into a data signal. These and other features and advantages of the present invention will be appreciated from review of the following Detailed Description of the

Preferred Embodiments, along with the accompanying figures in which like reference numerals are used to describe the same, similar or corresponding parts in the several views of the drawings.

## BRIEF DESCRIPTION OF THE DRAWINGS

Preferred embodiments of the present inventions taught herein are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings, in which:

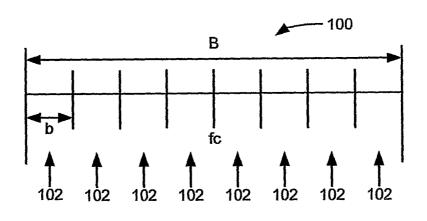

- FIG. 1A is a diagram illustrating an example embodiment of a wideband channel divided into a plurality of subchannels in accordance with the invention;

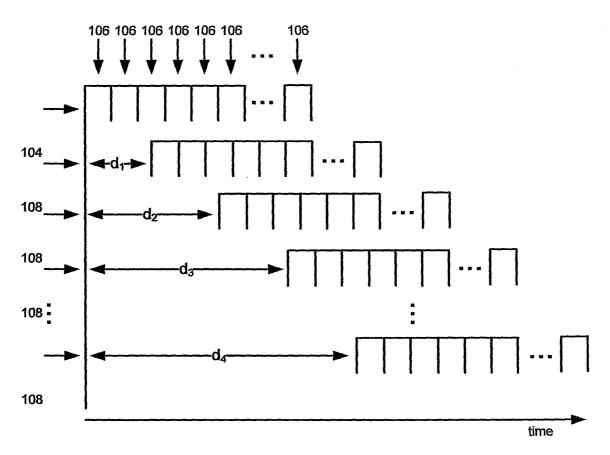

- FIG. 1B is a diagram illustrating the effects of multipath in a wireless communication system;

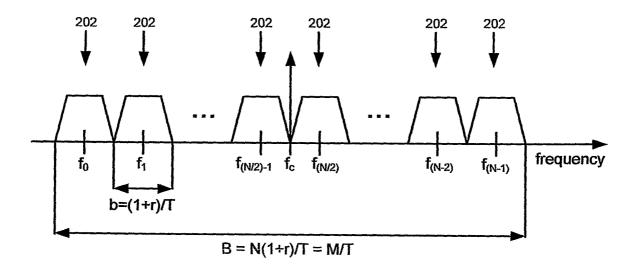

- FIG. 2 is a diagram illustrating another example embodiment of a wideband communication channel divided into a plurality of sub-channels in accordance with the invention;

- FIG. 3 is a diagram illustrating the application of a roll-off factor to the sub-channels of figures 1 and 2;

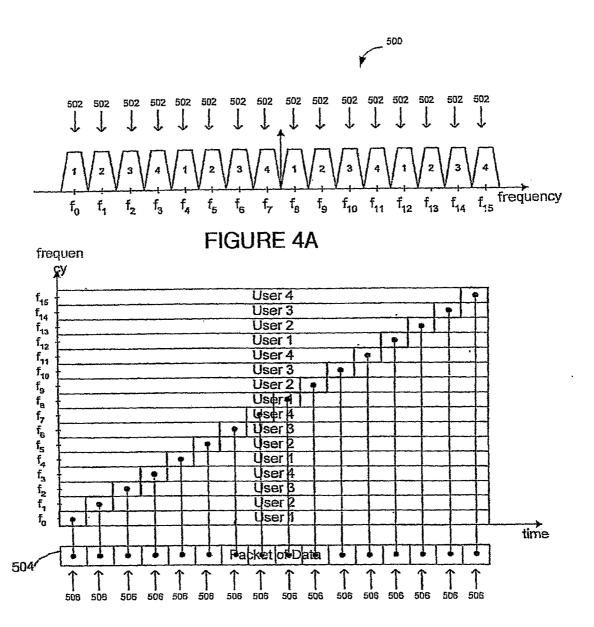

- FIG. 4A is a diagram illustrating the assignment of sub-channels for a wideband communication channel in accordance with the invention;

- FIG. 4B is a diagram illustrating the assignment of time slots for a wideband communication channel in accordance with the invention:

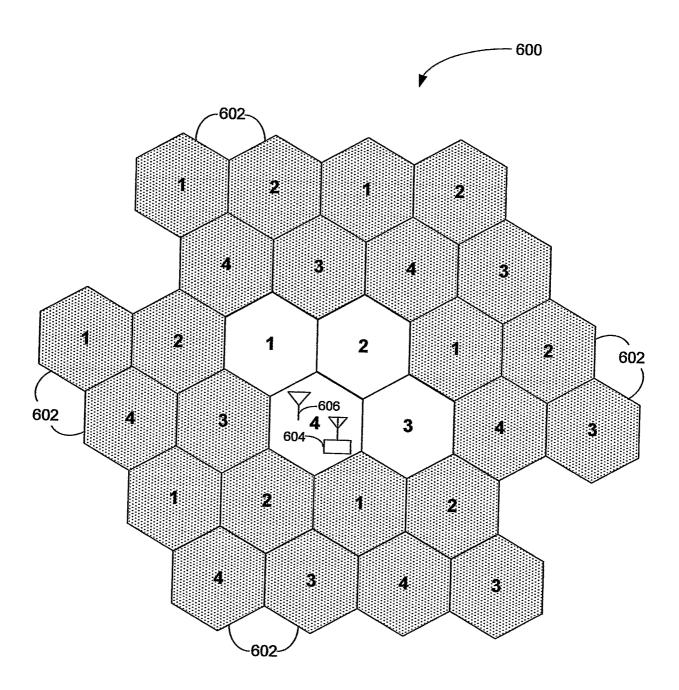

- FIG. 5 is a diagram illustrating an example embodiment of a wireless communication in accordance with the invention;

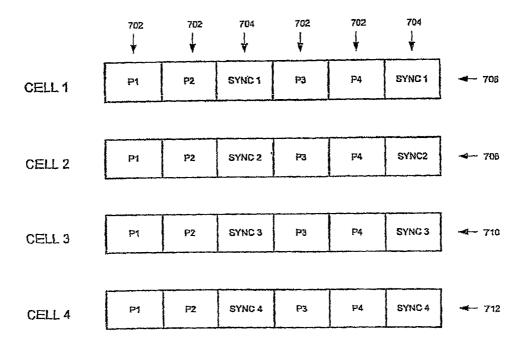

- FIG. 6 is a diagram illustrating the use of synchronization codes in the wireless communication system of figure 5 in accordance with the invention;

- FIG. 7 is a diagram illustrating a correlator that can be used to correlate synchronization codes in the wireless communication system of figure 5;

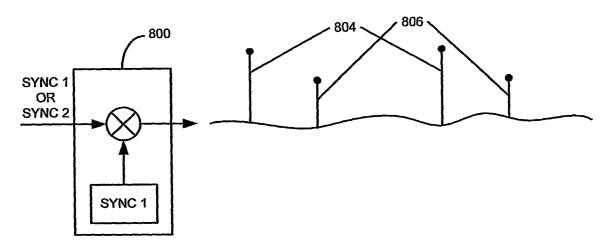

- FIG. 8 is a diagram illustrating synchronization code correlation in accordance with the invention;

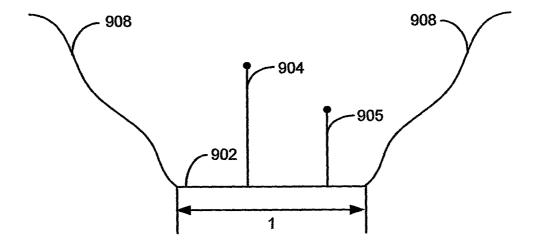

- FIG. 9 is a diagram illustrating the cross-correlation properties of synchronization codes configured in accordance with the invention;

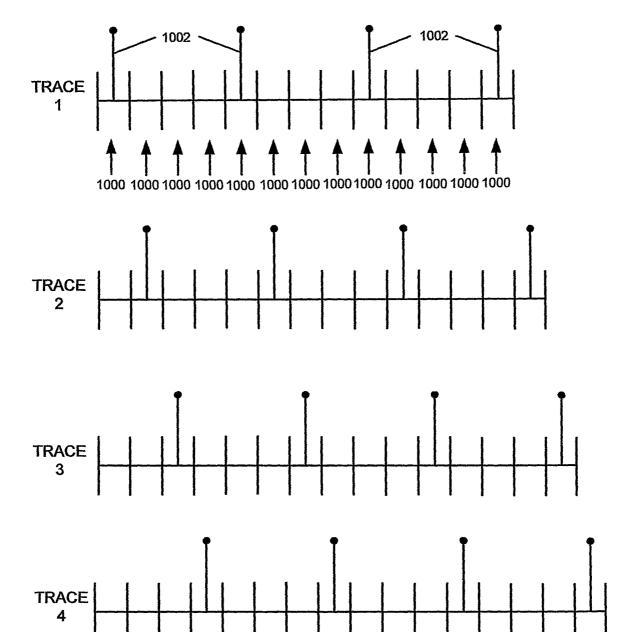

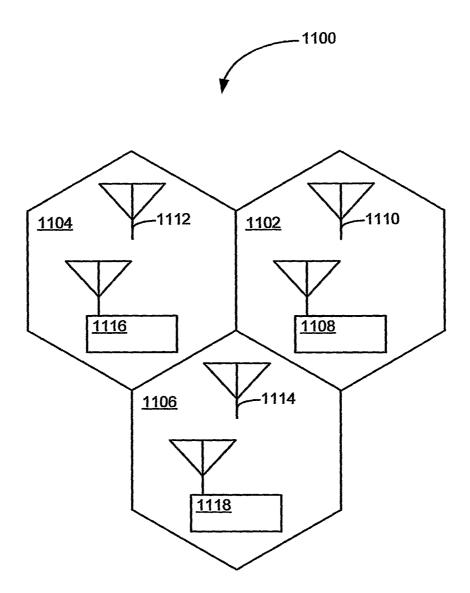

- FIG. 10 is a diagram illustrating another example embodiment of a wireless communication system in accordance with the invention;

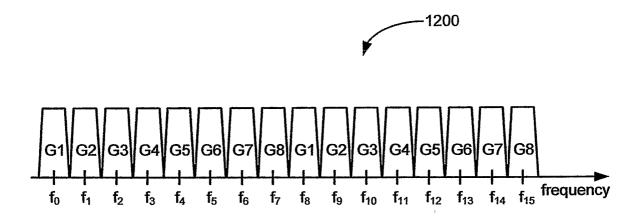

- FIG. 11A is a diagram illustrating how sub-channels of a wideband communication channel according to the present invention can be grouped in accordance with the present invention;

- FIG. 11B is a diagram illustrating the assignment of the groups of sub-channels of figure 11A in accordance with the invention;

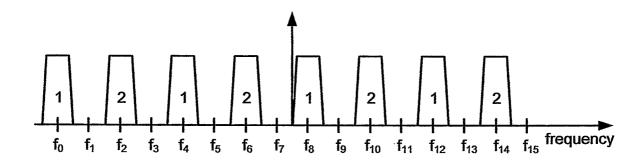

- FIG. 12 is a diagram illustrating the group assignments of figure 11B in the time domain;

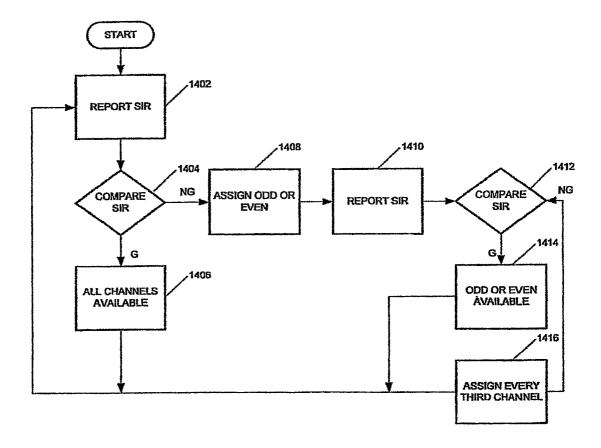

- FIG. 13 is a flow chart illustrating the assignment of sub-channels based on SIR measurements in the wireless communication system of figure 10 in accordance with the invention;

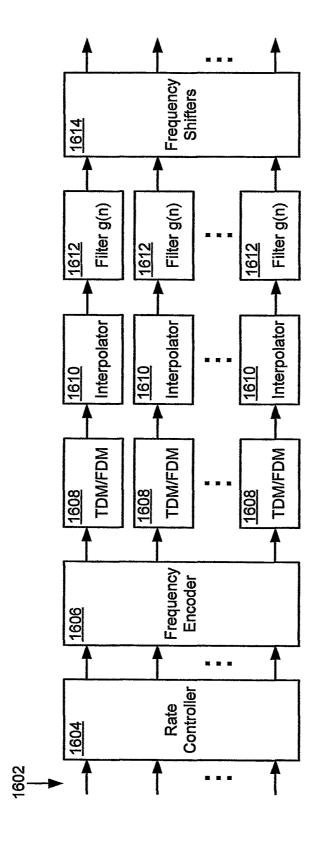

- FIG. 14 is a logical block diagram of an example embodiment of transmitter configured in accordance with the

invention;

FIG. 15 is a logical block diagram of an example embodiment of a modulator configured in accordance with the present invention for use in the transmitter of figure 14;

- FIG. 16 is a diagram illustrating an example embodiment of a rate controller configured in accordance with the invention for use in the modulator of figure 15;

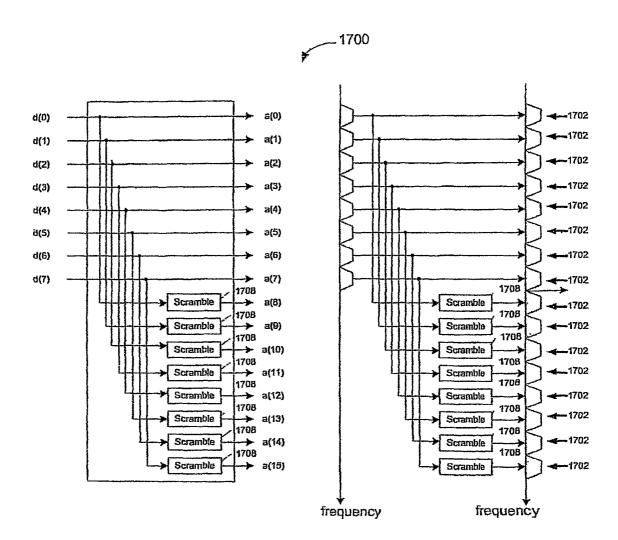

- FIG. 17 is a diagram illustrating another example embodiment of a rate controller configured in accordance with the invention for use in the modulator of figure 15;

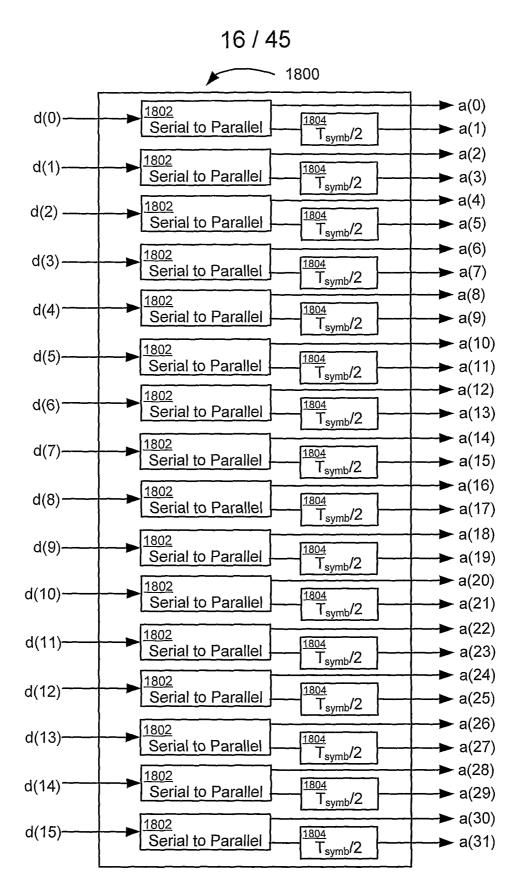

- FIG. 18 is a diagram illustrating an example embodiment of a frequency encoder configured in accordance with the invention for use in the modulator of figure 15;

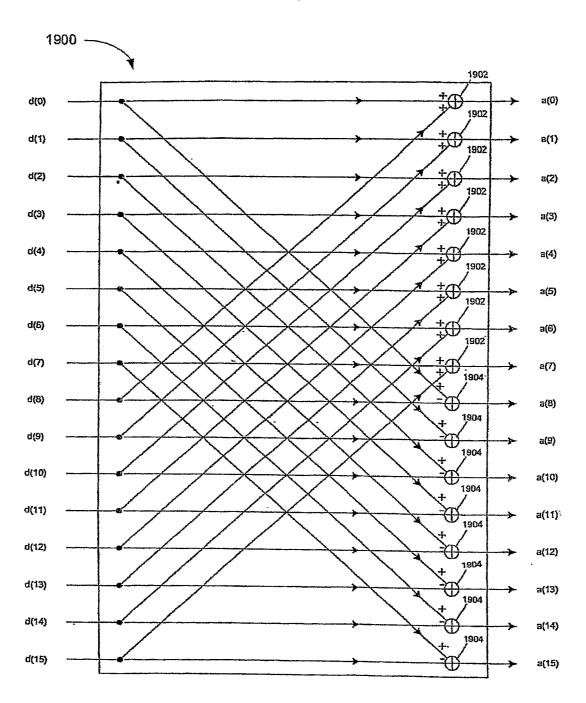

- FIG. 19 is a logical block diagram of an example embodiment of a TDM/FDM block configured in accordance with the invention for use in the modulator of figure 15;

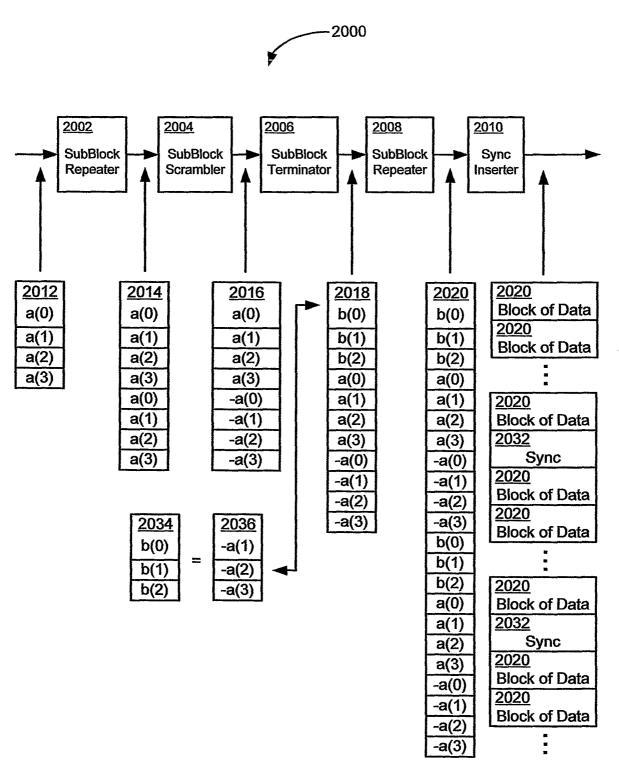

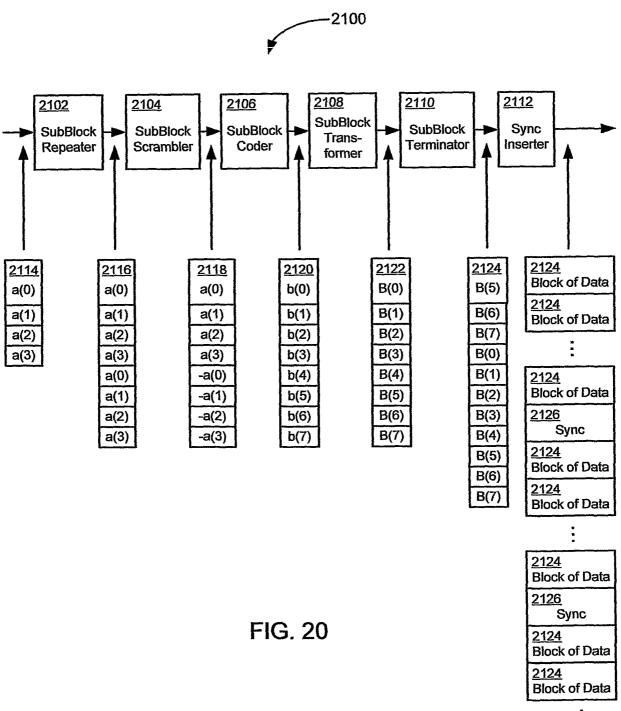

- FIG. 20 is a logical block diagram of another example embodiment of a TDM/FDM block configured in accordance with the invention for use in the modulator of figure 15;

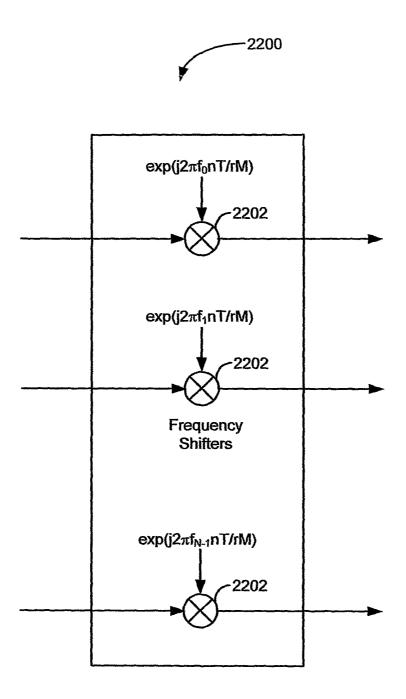

- FIG. 21 is a logical block diagram of an example embodiment of a frequency shifter configured in accordance with the invention for use in the modulator of figure 15;

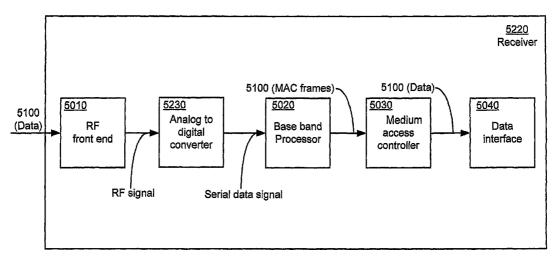

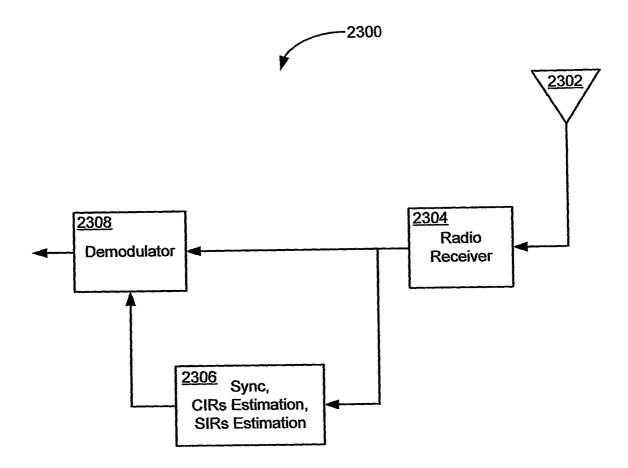

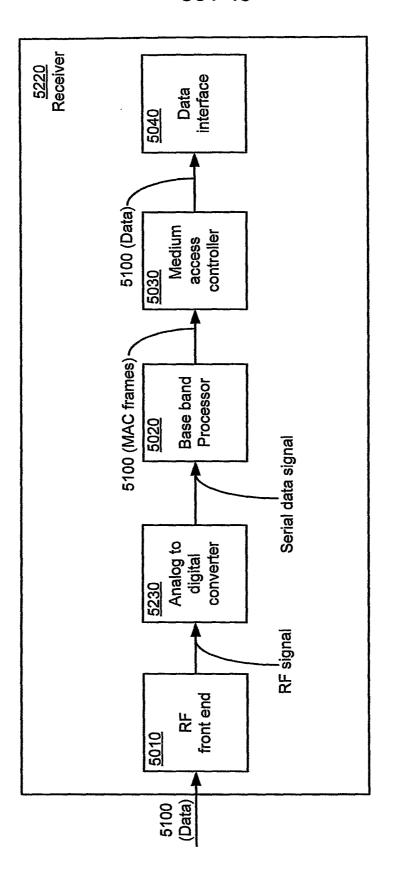

- FIG. 22 is a logical block diagram of a receiver configured in accordance with the invention;

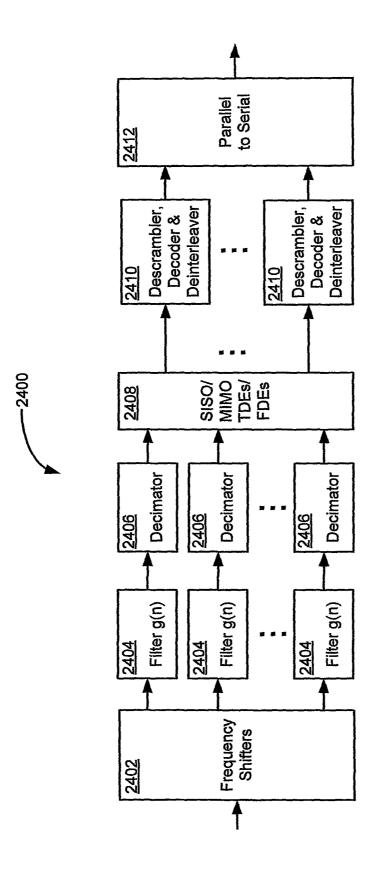

- FIG. 23 is a logical block diagram of an example embodiment of a demodulator configured in accordance with the invention for use in the receiver of figure 22;

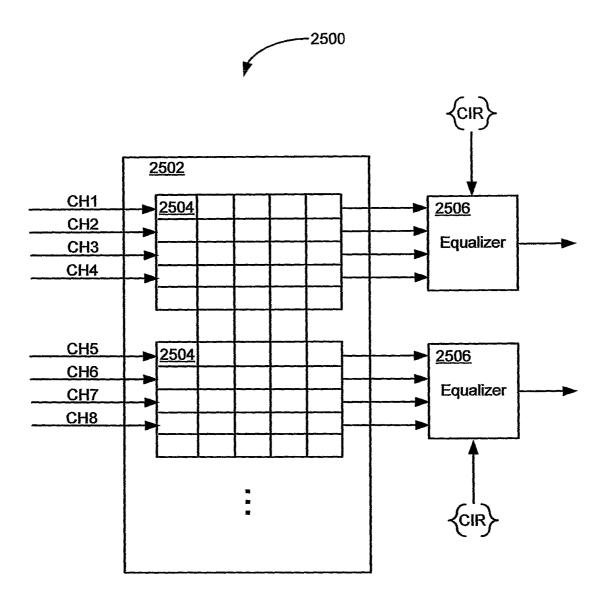

- FIG. 24 is a logical block diagram of an example embodiment of an equalizer configured in accordance with the present invention for use in the demodulator of figure 23;

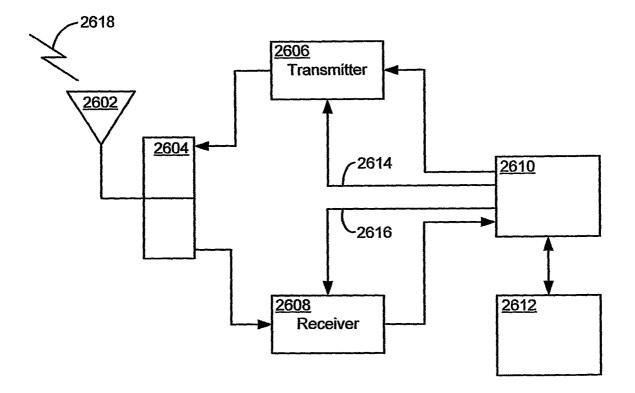

- FIG. 25 is a logical block diagram of an example embodiment of a wireless communication device configured in accordance with the invention;

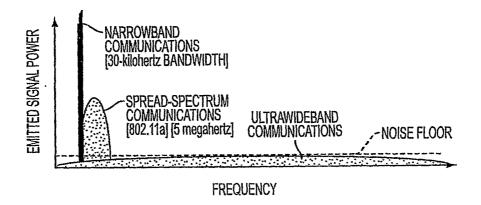

- FIG. 26 is an illustration of different communication methods;

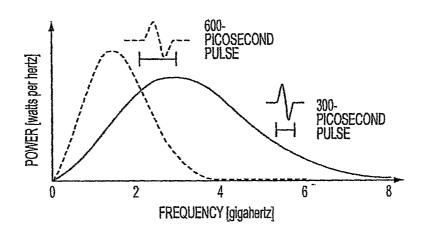

- FIG. 27 is an illustration of two ultra-wideband pulses;

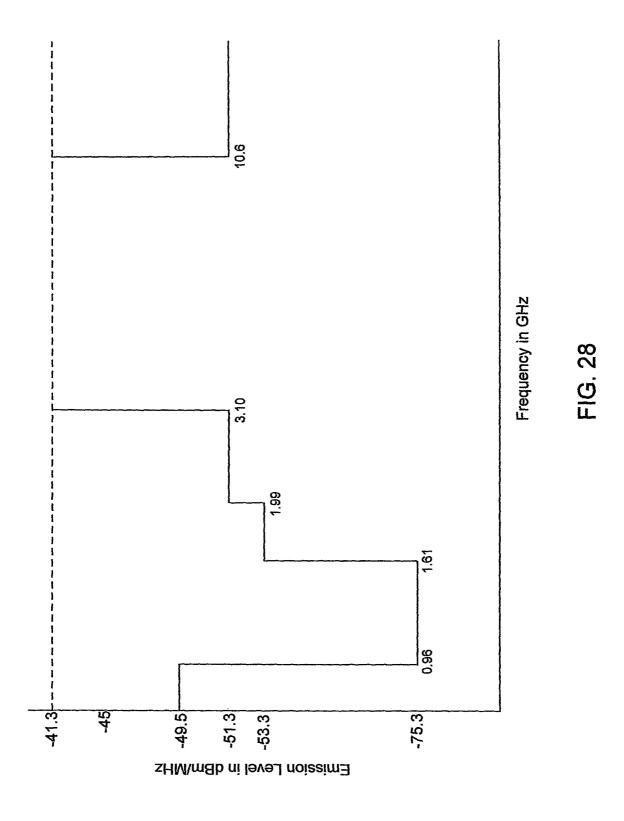

- FIG. 28 is a chart of ultra-wideband emission limits as established by the Federal Communications Commission on April 22, 2002;

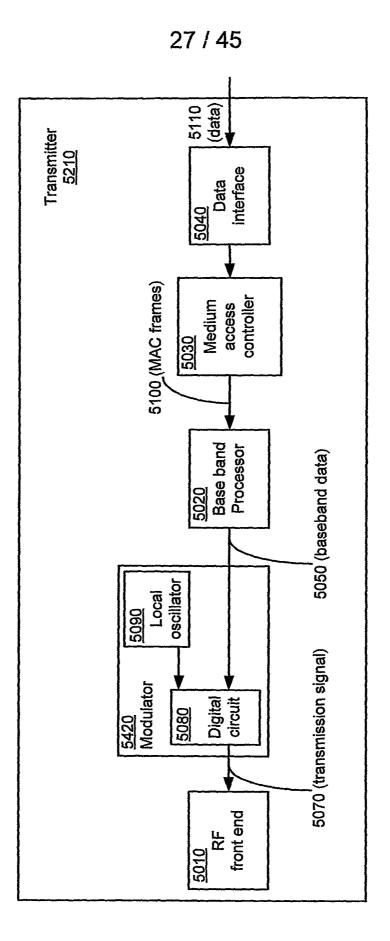

- FIG. 29 illustrates a transmitter consistent with one embodiment of the present invention;

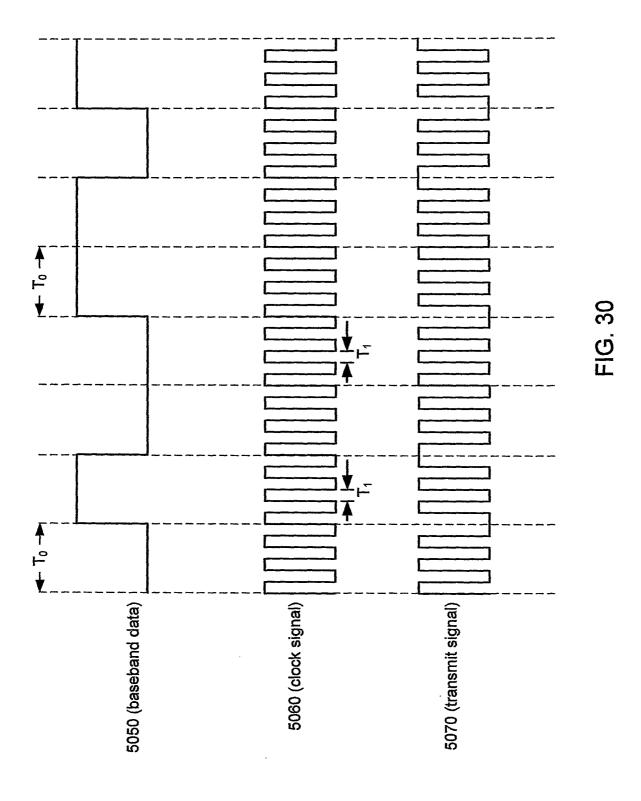

- FIG. 30 illustrates a timing diagram of various signals;

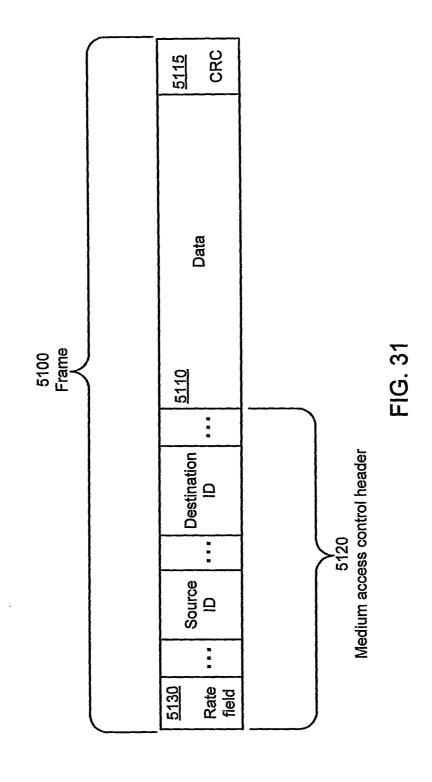

- FIG. 31 illustrates a frame consistent with one embodiment of the present invention;

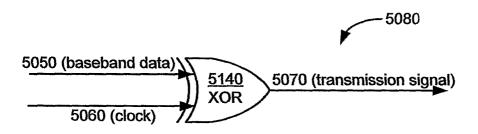

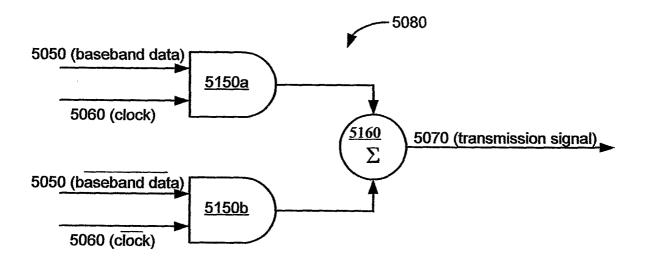

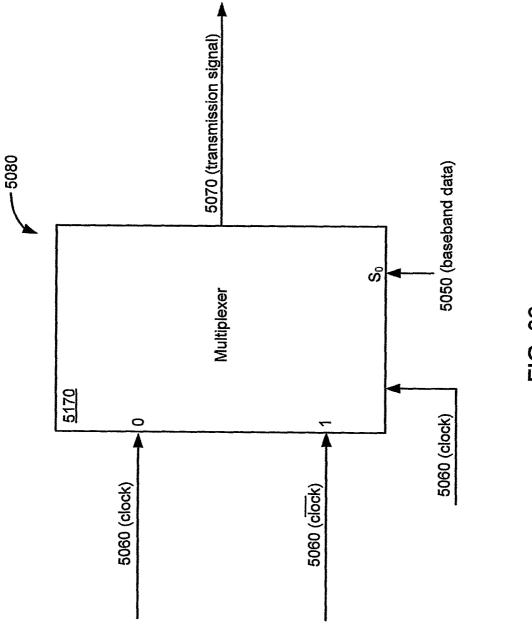

- FIG. 32a illustrates one embodiment of a digital circuit employed in the transmitter of FIG. 29;

- FIG. 32b illustrates a second embodiment of a digital circuit employed in the transmitter of FIG. 29;

- FIG. 32c illustrates a third embodiment of a digital circuit employed in the transmitter of FIG. 29;

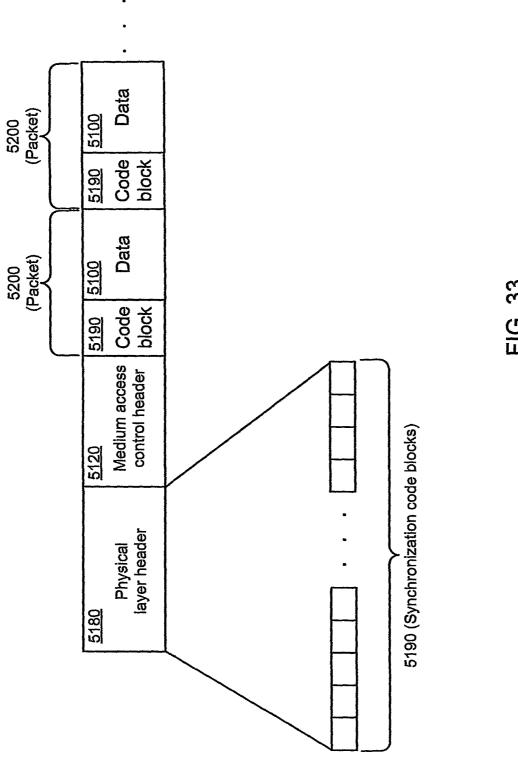

- FIG. 33 illustrates a data stream consistent with one embodiment of the present invention;

- FIG. 34 illustrates a receiver consistent with one embodiment of the present invention;

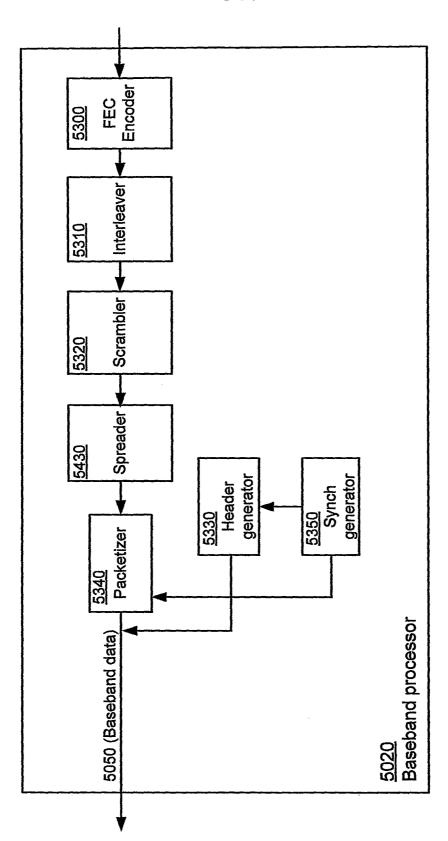

FIG. 35 illustrates a schematic of a first portion of a baseband processor employed in the transmitter of FIG. 29;

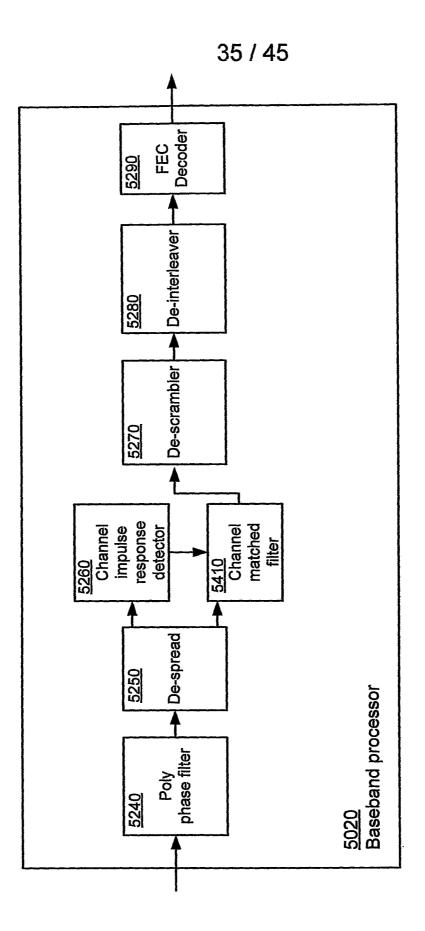

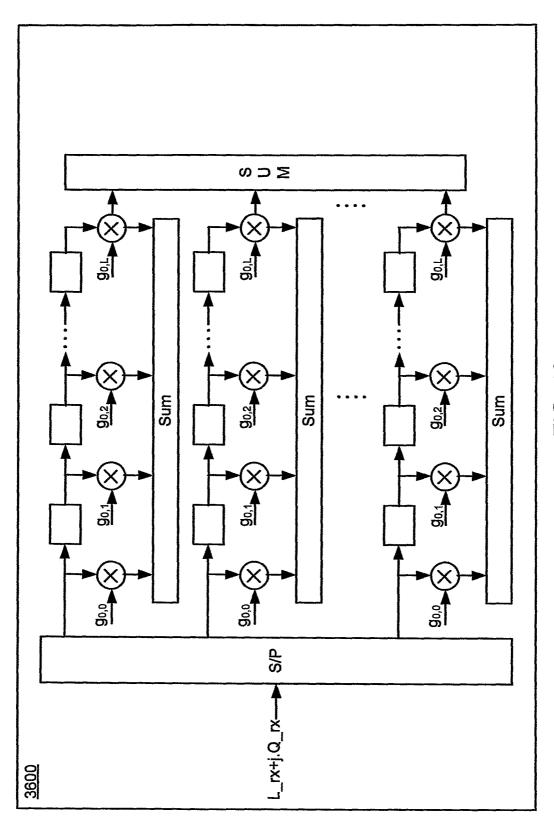

- FIG. 36 illustrates a schematic of a second portion of a baseband processor employed in the receiver of FIG. 34;

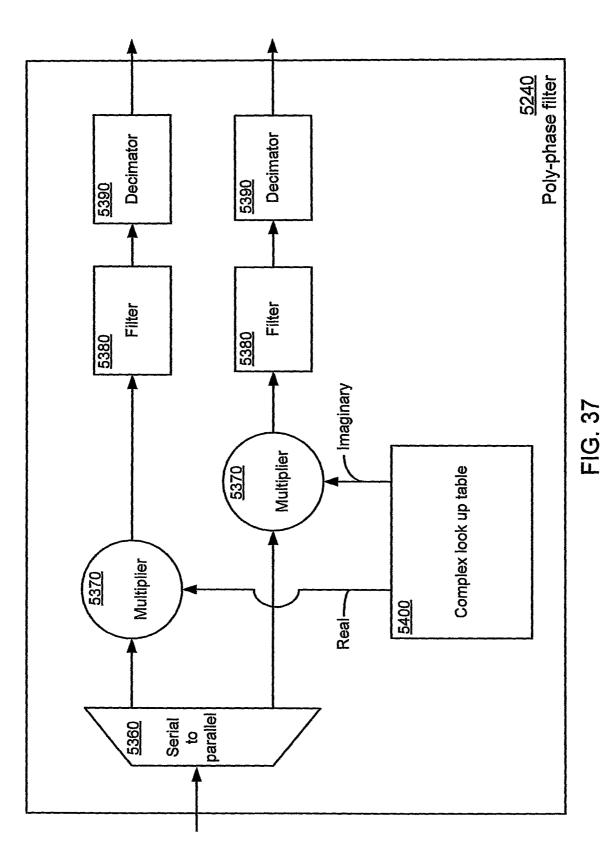

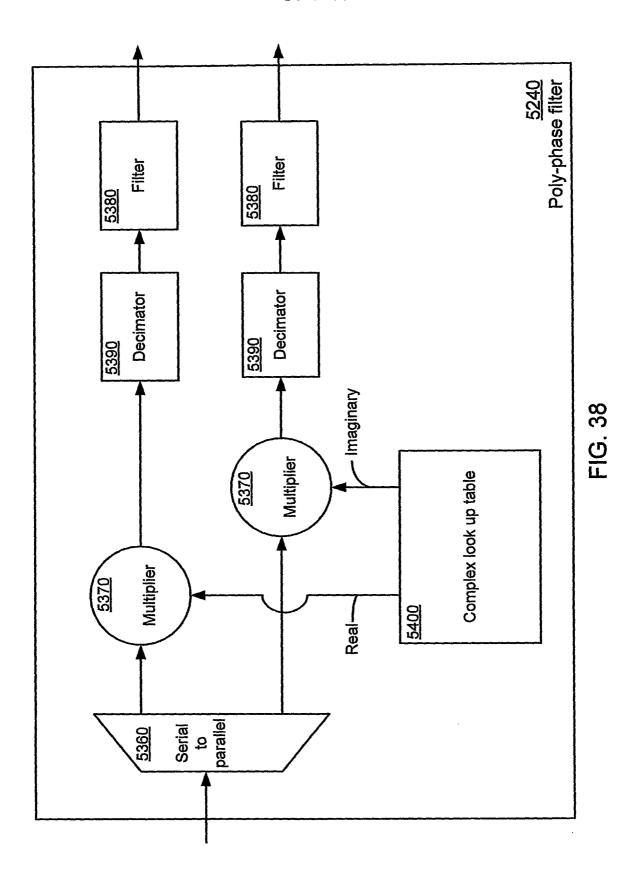

- FIG. 37 illustrates one embodiment of a poly-phase filter employed in the baseband processor of FIG. 36;

- FIG. 38 illustrates another embodiment of a poly-phase filter employed in the baseband processor of FIG. 36;

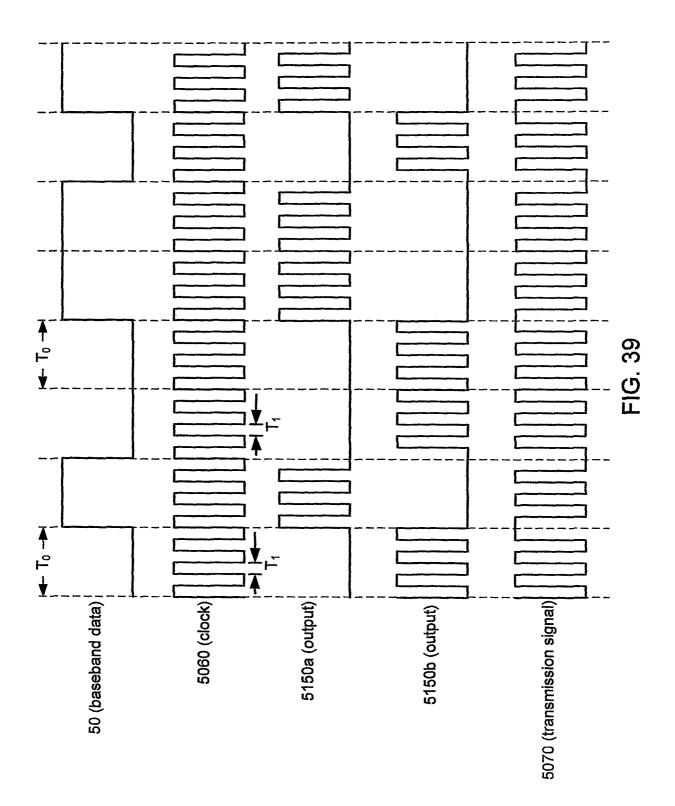

- FIG. 39 illustrates another timing diagram of signals consistent with the present invention.

- FIG. 40 illustrates one embodiment of an equalizer consistent with the present invention;

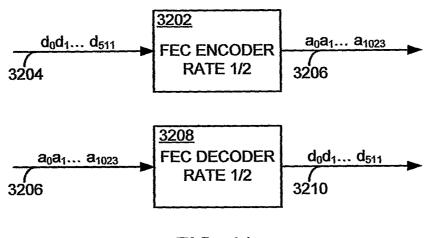

- FIG. 41 illustrates an exemplary FEC encoder and exemplary FEC decoder;

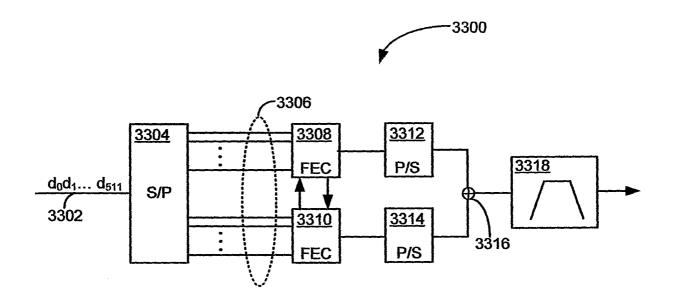

- FIG. 42 illustrates an example FEC encoder configured in accordance with one embodiment of the present invention;

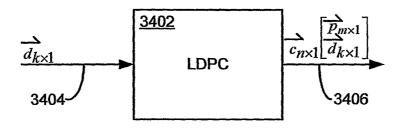

- FIG. 43 illustrates a FEC encoder configured to generate a code word from input data in accordance with one embodiment;

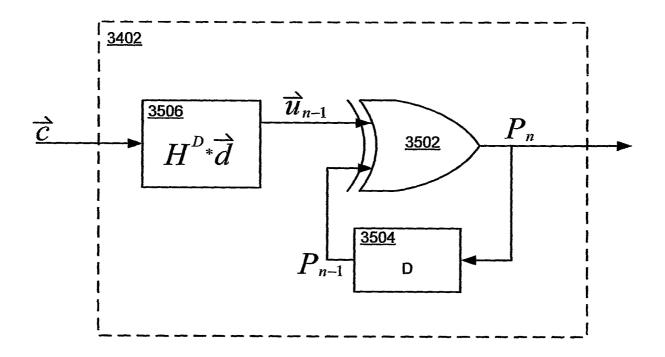

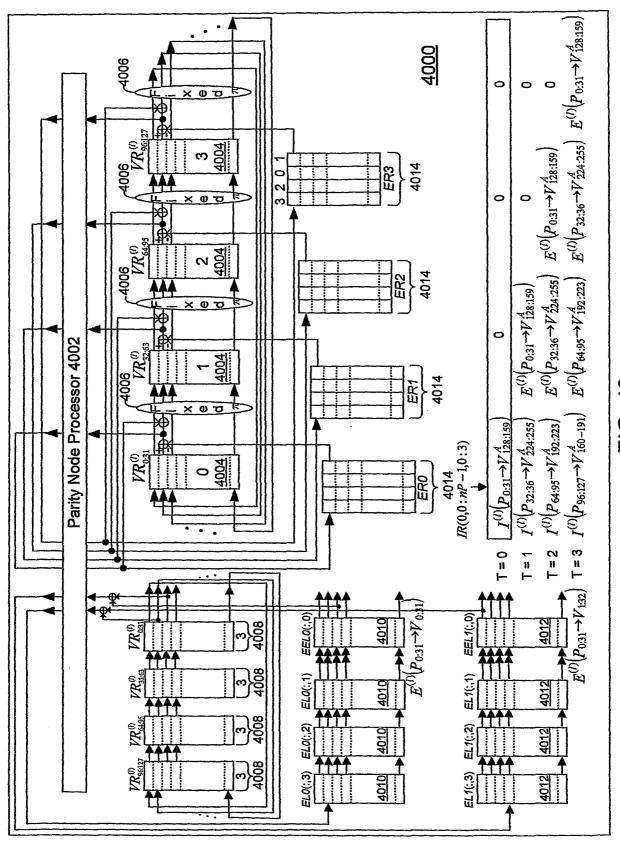

- FIG. 44 illustrates the encoder of FIG. 42 in more detail;

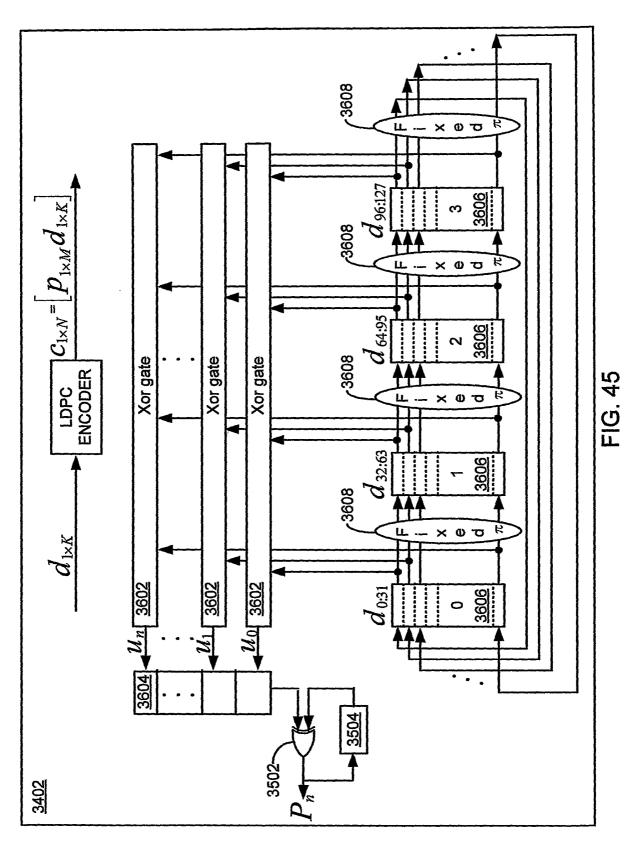

- FIG. 45 illustrates further detail for the encoder of FIG. 42;

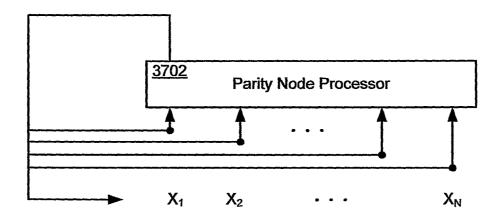

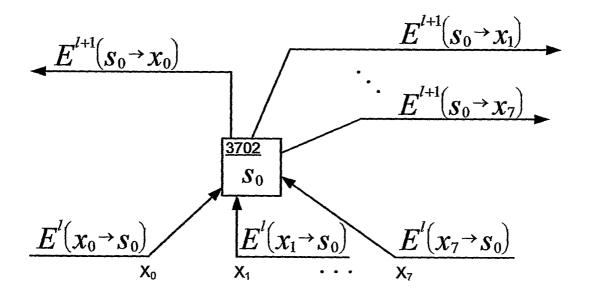

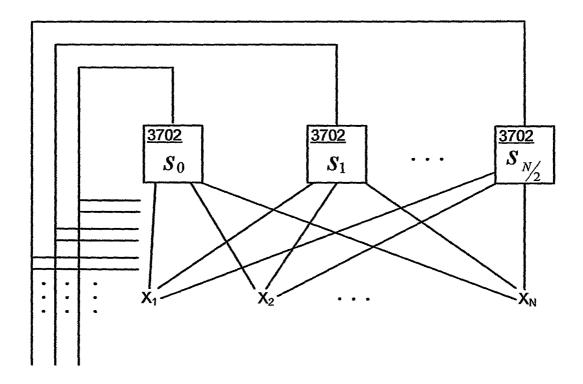

- FIG. 46 illustrates an example parity node processor that can be included in a decoder in accordance with one embodiment;

- FIG. 47 illustrates one node of the parity node processor of FIG. 45;

- FIG. 48 illustrates the parity node processor of FIG. 45 in more detail; and

- FIG. 49 illustrates a parity node processor configured in accordance with one embodiment.

It will be recognized that some or all of the Figures are schematic representations for purposes of illustration and do not necessarily depict the actual relative sizes or locations of the elements shown. The Figures are provided for the purpose of illustrating one or more embodiments of the invention with the explicit understanding that they will not be used to limit the scope or the meaning of the claims.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

#### 1. Introduction

In the following paragraphs, the present invention will be described in detail by way of example with reference to the attached drawings. While this invention is capable of embodiment in many different forms, there is shown in the drawings and will herein be described in detail specific embodiments, with the understanding that the present disclosure is to be considered as an example of the principles of the invention and not intended to limit the invention to the specific embodiments shown and described. That is, throughout this description, the embodiments and examples shown should be considered as exemplars, rather than as limitations on the present invention. As used herein, the "present invention" refers to any one of the embodiments of the invention described herein, and any equivalents. Furthermore, reference to various

feature(s) of the "present invention" throughout this document does not mean that all claimed embodiments or methods must include the referenced feature(s).

In order to improve wireless communication system performance and allow a single device to move from one type of system to another, while still maintaining superior performance, the systems and methods described herein provide various communication methodologies that enhance performance of transmitters and receivers with regard to various common problems that afflict such systems and that allow the transmitters and/or receivers to be reconfigured for optimal performance in a variety of systems. Accordingly, the systems and methods described herein define a channel access protocol that uses a common wideband communication channel for all communication cells. The wideband channel, however, is then divided into a plurality of sub-channels. Different sub-channels are then assigned to one or more users within each cell. But the base station, or service access point, within each cell transmits one message that occupies the entire bandwidth of the wideband channel. Each user's communication device receives the entire message, but only decodes those portions of the message that reside in sub-channels assigned to the user. For a point-to-point system, for example, a single user may be assigned all sub-channels and, therefore, has the full wide band channel available to them. In a wireless WAN, on the other hand, the sub-channels may be divided among a plurality of users.

In the descriptions of example embodiments that follow, implementation differences, or unique concerns, relating to different types of systems will be pointed out to the extent possible. But it should be understood that the systems and methods described herein are applicable to any type of communication systems. In addition, terms such as communication cell, base station, service access point, etc. are used interchangeably to refer to the common aspects of networks at these different levels. To begin illustrating the advantages of the systems and methods described herein, one can start by looking at the multipath effects for a single wideband communication channel 100 of bandwidth B as shown in figure 1A. Communications sent over channel 100 in a traditional wireless communication system will comprise digital data bits, or symbols, that are encoded and modulated onto a RF carrier that is centered at frequency  $f_c$  and occupies bandwidth B. Generally, the width of the symbols (or the symbol duration) T is defined as I/B. Thus, if the bandwidth B is equal to 100MHz, then the symbol duration T is defined by the following equation: T = I/B = I/100 megahertz (MHZ) = 10 nanoseconds (ns).

When a receiver receives the communication, demodulates it, and then decodes it, it will recreate a stream 104 of data symbols 106 as illustrated in figure 1B. But the receiver will also receive multipath versions 108 of the same data stream. Because multipath data streams 108 are delayed in time relative to the data stream 104 by delays d1, d2, d3, and d4, for example, they may combine destructively with data stream 104.

A delay spread  $d_s$  is defined as the delay from reception of data stream 104 to the reception of the last multipath data stream 108 that interferes with the reception of data stream 104. Thus, in the example illustrated in figure 1B, the delay spread  $d_s$  is equal to delay d4. The delay spread  $d_s$  will vary for different environments. An environment with a lot of obstacles will create a lot of multipath reflections. Thus, the delay spread  $d_s$  will be longer. Experiments have shown that for outdoor WAN type environments, the delay spread  $d_s$  can be as long as 20 microseconds. Using the 10ns symbol duration of equation (1),

this translates to 2000 symbols. Thus, with a very large bandwidth, such as 100MHz, multipath interference can cause a significant amount of interference at the symbol level for which adequate compensation is difficult to achieve. This is true even for indoor environments. For indoor LAN type systems, the delay spread  $d_s$  is significantly shorter, typically about 1 microsecond. For a 10ns symbol duration, this is equivalent to 100 symbols, which is more manageable but still significant. By segmenting the bandwidth B into a plurality of sub-channels 202, as illustrated in figure 2, and generating a distinct data stream for each sub-channel, the multipath effect can be reduced to a much more manageable level. For example, if the bandwidth B of each sub-channel B02 is B00KHz, then the symbol duration is B1 microseconds. Thus, the delay spread B2 for each sub-channel is equivalent to only B3 symbols (outdoor) or half a symbol (indoor). Thus, by breaking up a message that occupies the entire bandwidth B3 into discrete messages, each occupying the bandwidth B3 of sub-channels B3 a very wideband signal that suffers from relatively minor multipath effects is created.

Before discussing further features and advantages of using a wideband communication channel segmented into a plurality of sub-channels as described, certain aspects of the sub-channels will be explained in more detail. Referring back to figure 2, the overall bandwidth B is segmented into N sub-channels center at frequencies  $f_0$  to  $f_{NJ}$ . Thus, the sub-channel 202 that is immediately to the right of  $f_0$  is offset from  $f_0$  by  $f_0$ 2, where  $f_0$  is the bandwidth of each sub-channel 202. The next sub-channel 202 is offset by  $f_0$ 2, the next by  $f_0$ 5, and so on. To the left of  $f_0$ 6, each sub-channel 202 is offset by  $f_0$ 6, etc. Preferably, sub-channels 202 are non-overlapping as this allows each sub-channel to be processed independently in the receiver. To accomplish this, a roll-off factor is preferably applied to the signals in each sub-channel in a pulse-shaping step. The effect of such a pulse-shaping step is illustrated in figure 2 by the non-rectangular shape of the pulses in each sub-channel 202. Thus, the bandwidth  $f_0$ 6 of each sub-channel can be represented by an equation such as the following:  $f_0$ 6 beautiful to the signal of the pulses in each sub-channel 202. Thus, the bandwidth  $f_0$ 6 each sub-channel can be represented by an equation such as the following:  $f_0$ 6 beautiful to the signal of the pulses in each sub-channel 202. Thus, the bandwidth  $f_0$ 6 each sub-channel can be represented by an equation such as the following:  $f_0$ 7 beautiful to the signal of the pulses in each sub-channel 202.

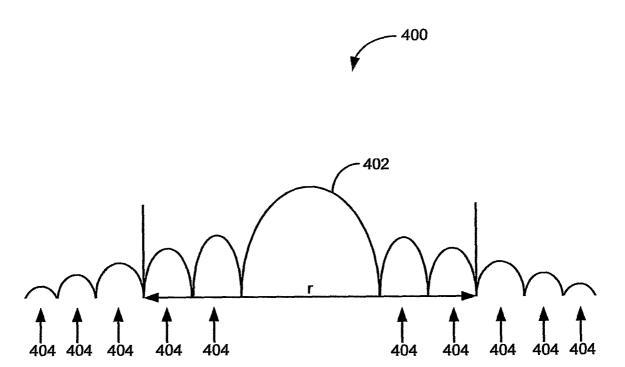

Where r=the roll-off factor; and T= the symbol duration. Without the roll-off factor, i.e., b = 1/T, the pulse shape would be rectangular in the frequency domain, which corresponds to a  $(sin \ x)/x$  function in the time domain. The time domain signal for a  $(sin \ x)/x$  signal 400 is shown in figure 3 in order to illustrate the problems associated with a rectangular pulse shape and the need to use a roll-off factor. As can be seen, main lobe 402 comprises almost all of signal 400. But some of the signal also resides in side lobes 404, which stretch out indefinitely in both directions from main lobe 402. Side lobes 404 make processing signal 400 much more difficult, which increases the complexity of the receiver. Applying a roll-off factor r; as in equation (2), causes signal 400 to decay faster, reducing the number of side lobes 404. Thus, increasing the roll-off factor decreases the length of signal 400, i.e., signal 400 becomes shorter in time. But including the roll-off factor also decreases the available bandwidth in each sub-channel 202. Therefore, r must be selected so as to reduce the number of side lobes 404 to a sufficient number, e.g., 15, while still maximizing the available bandwidth in each sub-channel 202. Thus, the overall bandwidth B for communication channel 200 is given by the following equation:  $B = N(1+r)/T; \qquad (3)$

or

$$B=MT$$

; (4)

Where

$$M=(1+r)N$$

. (5)

For efficiency purposes related to transmitter design, it is preferable that r is chosen so that M in equation (5) is an integer. Choosing r so that M is an integer allows for more efficient transmitters designs using, for example, Inverse Fast Fourier Transform (IFFT) techniques. Since M = N + N(r), and N is always an integer, this means that r must be chosen so that N(r) is an integer. Generally, it is preferable for r to be between 0.1 and 0.5. Therefore, if N is 16, for example, then 0.5 could be selected for r so that N(r) is an integer. Alternatively, if a value for r is chosen in the above example so that N(r) is not an integer, B can be made slightly wider than M/T to compensate. In this case, it is still preferable that r be chosen so that N(r) is approximately an integer.

## 2. Example Embodiment of a Wireless Communication System

With the above in mind, figure 5 illustrates an example communication system 600 comprising a plurality of cells 602 that each use a common wideband communication channel to communicate with communication devices 604 within each cell 602. The common communication channel is a wideband communication channel as described above. Each communication cell 602 is defined as the coverage area of a base station, or service access point, 606 within the cell. One such base station 606 is shown for illustration in figure 5. For purposes of this specification and the claims that follow, the term base station will be used generically to refer to a device that provides wireless access to the wireless communication system for a plurality of communication devices, whether the system is a line of sight, indoor, or outdoor system. Because each cell 602 uses the same communication channel, signals in one cell 602 must be distinguishable from signals in adjacent cells 602. To differentiate signals from one cell 602 to another, adjacent base stations 606 use different synchronization codes according to a code reuse plan. In figure 6, system 600 uses a synchronization code reuse factor of 4, although the reuse factor can vary depending on the application. Preferably, the synchronization code is periodically inserted into a communication from a base station 606 to a communication device 604 as illustrated in figure 6. After a predetermined number of data packets 702, in this case two, the particular synchronization code 704 is inserted into the information being transmitted by each base station 606. A synchronization code is a sequence of data bits known to both the base station 606 and any communication devices 604 with which it is communicating. The synchronization code allows such a communication device 604 to synchronize its timing to that of base station 606, which, in turn, allows device 604 to decode the data properly. Thus, in cell 1 (see lightly shaded cells 602 in figure 6), for example, synchronization code 1 (SYNC1) is inserted into data stream 706, which is generated by base station 606 in cell 1, after every two packets 702; in cell 2 SYNC2 is inserted after every two packets 702; in cell 3 SYNC3 is inserted; and in cell 4 SYNC4 is inserted. Use of the synchronization codes is discussed in more detail below.

In figure 4A, an example wideband communication channel 500 for use in communication system 600 is divided into 16 sub-channels 502, centered at frequencies fo to  $f_{15}$ . A base station 606 at the center of each communication cell 602 transmits a single packet occupying the whole bandwidth B of wideband channel 500. Such a packet is illustrated by packet 504 in figure 4B. Packet 504 comprises sub-packets 506 that are encoded with a frequency offset corresponding to one of sub-channels 502. Sub-packets 506 in effect define available time slots in packet 504. Similarly, sub-channels 502 can be

said to define available frequency bins in communication channel 500. Therefore, the resources available in communication cell 602 are time slots 506 and frequency bins 502, which can be assigned to different communication devices 604 within each cell 602. Thus, for example, frequency bins 502 and time slots 506 can be assigned to 4 different communication devices 604 within a cell 602 as shown in figure 5. Each communication device 604 receives the entire packet 504, but only processes those frequency bins 502 and/or timeslots 506 that are assigned to it. Preferably, each device 604 is assigned non-adjacent frequency bins 502, as in figure 4A. This way, if interference corrupts the information in a portion of communication channel 500, then the effects are spread across all devices 604 within a cell 602. Hopefully, by spreading out the effects of interference in this manner the effects are minimized and the entire information sent to each device 604 can still be recreated from the unaffected information received in other frequency bins. For example, if interference, such as fading, corrupted the information in bins  $f_0f_0$ , then each user 1-4 loses one packet of data. But each user potentially receives three unaffected packets from the other bins assigned to them. Hopefully, the unaffected data in the other three bins provides enough information to recreate the entire message for each user. Thus, frequency diversity can be achieved by assigning non-adjacent bins to each of multiple users.

Ensuring that the bins assigned to one user are separated by more than the coherence bandwidth ensures frequency diversity. As discussed above, the coherence bandwidth is approximately equal to  $1/d_s$  For outdoor systems, where ds is typically 1 microsecond,  $1/d_s = 1/1$  microsecond = 1 Mega Hertz (MHz). Thus, the non-adjacent frequency bands assigned to a user are preferably separated by at least 1 MHz. It is even more preferable, however, if the coherence bandwidth plus some guard band to ensure sufficient frequency diversity separate the non-adjacent bins assigned to each user. For example, it is preferable in certain implementations to ensure that at least 5 times the coherence bandwidth, or 5 MHz in the above example, separates the non-adjacent bins. Another way to provide frequency diversity is to repeat blocks of data in frequency bins assigned to a particular user that are separated by more than the coherence bandwidth. In other words, if 4 sub-channels 202 are assigned to a user, then data block a can be repeated in the first and third sub-channels 202 and data block b can be repeated in the second and fourth sub-channels 202, provided the sub-channels are sufficiently separated in frequency. In this case, the system can be said to be using a diversity length factor of 2. The system can similarly be configured to implement other diversity lengths, e.g., 3, 4,..., 1.

It should be noted that spatial diversity can also be included depending on the embodiment. Spatial diversity can comprise transmit spatial diversity, receive spatial diversity, or both. In transmit spatial diversity, the transmitter uses a plurality of separate transmitters and a plurality of separate antennas to transmit each message. In other words, each transmitter transmits the same message in parallel. The messages are then received from the transmitters and combined in the receiver. Because the parallel transmissions travel different paths, if one is affected by fading, the others will likely not be affected. Thus, when they are combined in the receiver, the message should be recoverable even if one or more of the other transmission paths experienced severe fading. Receive spatial diversity uses a plurality of separate receivers and a plurality of separate antennas to receive a single message. If an adequate distance separates the antennas, then the transmission path for the signals received by the antennas will be different. Again, this difference in the transmission paths will provide

imperviousness to fading when the signals from the receivers are combined. Transmit and receive spatial diversity can also be combined within a system such as system 600 so that two antennas are used to transmit and two antennas are used to receive. Thus, each base station 606 transmitter can include two antennas, for transmit spatial diversity, and each communication device 604 receiver can include two antennas, for receive spatial diversity. If only transmit spatial diversity is implemented in system 600, then it can be implemented in base stations 606 or in communication devices 604. Similarly, if only receive spatial diversity is included in system 600, then it can be implemented in base stations 606 or communication devices 604. The number of communication devices 604 assigned frequency bins 502 and/or time slots 506 in each cell 602 is preferably programmable in real time. In other words, the resource allocation within a communication cell 602 is preferably programmable in the face of varying external conditions, i.e., multipath or adjacent cell interference, and varying requirements, i.e., bandwidth requirements for various users within the cell. Thus, if user 1 requires the whole bandwidth to download a large video file, for example, then the allocation of bins 502 can be adjust to provide user 1 with more, or even all, of bins 502. Once user 1 no longer requires such large amounts of bandwidth, the allocation of bins 502 can be readjusted among all of users 1-4. It should also be noted that all of the bins assigned to a particular user can be used for both the forward and reverse link. Alternatively, some bins 502 can be assigned as the forward link and some can be assigned for use on the reverse link, depending on the implementation. To increase capacity, the entire bandwidth B is preferably reused in each communication cell 602, with each cell 602 being differentiated by a unique synchronization code (see discussion below). Thus, system 600 provides increased immunity to multipath and fading as well as increased bandwidth due to the elimination of frequency reuse requirements.

#### 3. Synchronization

Figure 6 illustrates an example embodiment of a synchronization code correlator 800 (shown in figure 7). When a device 604 in cell 1 (see figure 5), for example, receives an incoming communication from the cell 1 base station 606, it compares the incoming data with SYNCl in correlator 800. Essentially, the device scans the incoming data trying to correlate the data with the known synchronization code, in this case SYNCl. Once correlator 800 matches the incoming data to SYNCl it generates a correlation peak 804 at the output. Multipath versions of the data will also generate correlation peaks 806, although these peaks 806 are generally smaller than correlation peak 804. The device can then use the correlation peaks to perform channel estimation, which allows the device to adjust for the multipath using an equalizer. Thus, in cell 1, if correlator 800 receives a data stream comprising SYNC1, it will generate correlation peaks 804 and 806. If, on the other hand, the data stream comprises SYNC2, for example, then no peaks will be generated and the device will essentially ignore the incoming communication.

Even though a data stream that comprises SYNC2 will not create any correlation peaks, it can create noise in correlator 800 that can prevent detection of correlation peaks 804 and 806. Several steps can be taken to prevent this from occurring. One way to minimize the noise created in correlator 800 by signals from adjacent cells 602, is to configure system 600 so that each base station 606 transmits at the same time. This way, the synchronization codes can preferably be generated in such a manner that only the synchronization codes 704 of adjacent cell data streams, e.g., streams 708, 710, and 712, as

opposed to packets 702 within those streams, will interfere with detection of the correct synchronization code 704, e.g., SYNC1. The synchronization codes can then be further configured to eliminate or reduce the interference. For example, the noise or interference caused by an incorrect synchronization code is a function of the cross correlation of that synchronization code with respect to the correct code. The better the cross correlation between the two, the lower the noise level. When the cross correlation is ideal, then the noise level will be virtually zero as illustrated in figure 8 by noise level 902. Therefore, a preferred embodiment of system 600 uses synchronization codes that exhibit ideal cross correlation, i.e., zero. Preferably, the ideal cross correlation of the synchronization codes covers a period l that is sufficient to allow accurate detection of multipath 906 as well as multipath correlation peaks 904. This is important so that accurate channel estimation and equalization can take place. Outside of period I, the noise level 908 goes up, because the data in packets 702 is random and will exhibit low cross correlation with the synchronization code, e.g., SYNC1. Preferably, period l is actually slightly longer then the multipath length in order to ensure that the multipath can be detected.

#### Synchronization code generation a.

Conventional systems use orthogonal codes to achieve cross correlation in correlator 800. In system 600 for example, SYNC1, SYNC2, SYNC3, and SYNC4, corresponding to cells 1-4 (see lightly shaded cells 602 of figure 5) respectively, will all need to be generated in such a manner that they will have ideal cross correlation with each other. In one embodiment, if the data streams involved comprise high and low data bits, then the value "1" can be assigned to the high data bits and "-1" to the low data bits. Orthogonal data sequences are then those that produce a "0" output when they are exclusively ORed (XORed) together in correlator 800. The following example illustrates this point for orthogonal sequences 1 and 2:

> sequence 1: 11-11 sequence 2: 111-1

Thus, when the results of XORing each bit pair are added, the result is "O".

But in system 600, for example, each code must have ideal, or zero, cross correlation with each of the other codes used in adjacent cells 602. Therefore, in one example embodiment of a method for generating synchronization codes exhibiting the properties described above, the process begins by selecting a "perfect sequence" to be used as the basis for the codes. A perfect sequence is one that when correlated with itself produces a number equal to the number of bits in the sequence. For example:

> Perfect sequence 1: 11-11 1111=4

But each time a perfect sequence is cyclically shifted by one bit, the new sequence is orthogonal with the original sequence. Thus, for example, if perfect sequence 1 is cyclically shifted by one bit and then correlated with the original, the correlation produces a "O" as in the following example;

Perfect sequence 1: 11-11

111-1

$$11-1-1=0$$

If the perfect sequence 1 is again cyclically shifted by one bit, and again correlated with the original, then it will produce a "0". In general, you can cyclically shift a perfect sequence by any number of bits up to its length and correlate the shifted sequence with the original to obtain a "0". Once a perfect sequence of the correct length is selected, the first synchronization code is preferably generated in one embodiment by repeating the sequence 4 times. Thus, if perfect sequence 1 is being used, then a first synchronization code y would be the following:

Or in generic form: y=x(0)x(1)x(2)x(3)x(0)x(1)x(2)x(3)x(0)x(1)x(2)x(3)x(0)x(1)x(2)x(3). For a sequence of length L: y=x(0)x(1)...x(L)x(0)x(1)...x(L)x(0)x(1)...x(L)

Repeating the perfect sequence allows correlator 800 a better opportunity to detect the synchronization code and allows generation of other uncorrelated frequencies as well. Repeating has the effect of sampling in the frequency domain. This effect is illustrated by the graphs in figure 9. Thus, in TRACE 1, which corresponds to synchronization code y, a sample 1002 is generated every fourth sample bin 1000. Each sample bin is separated by 1/(4LxT), where T is the symbol duration. Thus, in the above example, where L=4, each sample bin is separated by 1/(16xT) in the frequency domain. TRACES 2-4 illustrate the next three synchronization codes. As can be seen, the samples for each subsequent synchronization code are shifted by one sample bin relative to the samples for the previous sequence. Therefore, none of the sequences interfere with each other. To generate the subsequent sequences, corresponding to TRACES 2-4, sequence y must be shifted in frequency. This can be accomplished using the following equation:  $z'(m) = y(m) *exp(j*2 *\pi*r*m/(n*L))$ ,

16

for r=1 to L (# of sequences) and m=0 to 4\*L-1 (time); and where: Z'(m)= each subsequent sequence; y(m)= the first sequence; and n= the number of times the sequence is repeated. It will be understood that multiplying by an  $\exp(j2\pi(r*m/N))$  factor, where N is equal to the number of times the sequence is repeated n multiplied by the length of the underlying perfect sequence L, in the time domain results in a shift in the frequency domain. Equation (6) results in the desired shift as illustrated in figure 9 for each of synchronization codes 2-4, relative to synchronization code 1. The final step in generating each synchronization code is to append the copies of the last M samples, where M is the length of the multipath, to the front of each code. This is done to make the convolution with the multipath cyclic and to allow easier detection of the multipath. It should be noted that synchronization codes can be generated from more than one perfect sequence using the same methodology. For example, a perfect sequence can be generated four times and then a second perfect sequence can be generated and repeated four times and then a second perfect sequence can be generated and repeated four times to get a n factor equal to eight. The resulting sequence can then be shifted as described above to create the synchronization codes.

## b. <u>Signal Measurements Using Synchronization Codes</u>

Therefore, when a communication device is at the edge of a cell, it will receive signals from multiple base stations and, therefore, will be decoding several synchronization codes at the same time. This can be illustrated with the help of figure 10, which illustrates another example embodiment of a wireless communication system 1100 comprising communication

cells 1102, 1104, and 1106 as well as communication device 1108, which is in communication with base station 1110 of cell 1102 but also receiving communication from base stations 1112 and 1114 of cells 1104 and 1106, respectively. If communications from base station 1110 comprise synchronization code SYNC1 and communications from base station 1112 and 1114 comprise SYNC2 and SYNC3 respectively, then device 1108 will effectively receive the sum of these three synchronization codes. This is because, as explained above, base stations 1110, 1112, and 1114 are configured to transmit at the same time. Also, the synchronization codes arrive at device 1108 at almost the same time because they are generated in accordance with the description above. Again as described above, the synchronization codes SYNC1, SYNC2, and SYNC3 exhibit ideal cross correlation. Therefore, when device 1108 correlates the sum x of codes SYNC1, SYNC2, and SYNC3, the latter two will not interfere with proper detection of SYNC1 by device 1108. Importantly, the sum x can also be used to determine important signal characteristics, because the sum x is equal to the sum of the synchronization code signal in accordance with the following equation: x = SYNC1 + SYNC2 + SYNC3.

Therefore, when SYNC1 is removed, the sum of SYNC2 and SYNC3 is left, as shown in the following:

$$x-SYNC1 = SYNC2 + SYNC3. (8)$$

The energy computed from the sum (SYNC2+SYNC3) is equal to the noise or interference seen by device 1108. Since the purpose of correlating the synchronization code in device 1106 is to extract the energy in SYNC 1, device 1108 also has the energy in the signal from base station 1110, i.e., the energy represented by SYNC1. Therefore, device 1106 can use the energy of SYNC1 and of (SYNC2 + SYNC3) to perform a signal-to-interference measurement for the communication channel over which it is communicating with base station 1110. The result of the measurement is preferably a signal-to-interference ratio (SIR). The SIR measurement can then be communicated back to base station 1110 for purposes that will be discussed below.

The ideal cross correlation of the synchronization codes, also allows device 1108 to perform extremely accurate determinations of the Channel Impulse Response (CIR), or channel estimation, from the correlation produced by correlator 800. This allows for highly accurate equalization using low cost, low complexity equalizers, thus overcoming a significant draw back of conventional systems.

#### 4. Sub-Channel Assignments

As mentioned, the SIR as determined by device 1108 can be communicated back to base station 1110 for use in the assignment of channels 502. In one embodiment, due to the fact that each sub-channel 502 is processed independently, the SIR for each sub-channel 502 can be measured and communicated back to base station 1110. In such an embodiment, therefore, sub-channels 502 can be divided into groups and a SIR measurement for each group can be sent to base station 1110. This is illustrated in figure 11A, which shows a wideband communication channel 1200 segmented into sub-channels fo to  $f_{15}$  Sub-channels fo to  $f_{15}$  are then grouped into 8 groups GI to G8. Thus, in one embodiment, device 1108 and base station 1110 communicate over a channel such as channel 1200.

Sub-channels in the same group are preferably separated by as many sub-channels as possible to ensure diversity. In figure 11A for example, sub-channels within the same group are 7 sub-channels apart, e.g., group Gl comprises  $f_0$  and  $f_8$ . Device 1102 reports a SIR measurement for each of the groups G1 to G8. These SIR measurements are preferably

compared with a threshold value to determine which sub-channels groups are useable by device 1108. This comparison can occur in device 1108 or base station 1110. If it occurs in device 1108, then device 1108 can simply report to base station 1110 which sub-channels groups are useable by device 1108.

SIR reporting will be simultaneously occurring for a plurality of devices within cell 1102. Thus, figure 11B illustrates the situation where two communication devices corresponding to User 1 and User 2 report SIR levels above the threshold for groups GI, G3, G5, and G7. Base station 1110 preferably then assigns sub-channel groups to User 1 and User 2 based on the SIR reporting as illustrated in Figure 11B. When assigning the "good" sub-channel groups to User 1 and User 2, base station 1110 also preferably assigns them based on the principles of frequency diversity. In figure 11B, therefore, User 1 and User 2 are alternately assigned every other "good" sub-channel. The assignment of sub-channels in the frequency domain is equivalent to the assignment of time slots in the time domain. Therefore, as illustrated in figure 12, two users, User 1 and User 2, receive packet 1302 transmitted over communication channel 1200. Figure 12 also illustrated the sub-channel assignment of figure 11B. While figures 11 and 12 illustrate sub-channel/time slot assignment based on SIR for two users, the principles illustrated can be extended for any number of users. Thus, a packet within cell 1102 can be received by 3 or more users. Although, as the number of available subchannels is reduced due to high SIR, so is the available bandwidth. In other words, as available channels are reduced, the number of users that can gain access to communication channel 1200 is also reduced.

Poor SIR can be caused for a variety of reasons, but frequently it results from a device at the edge of a cell receiving communication signals from adjacent cells. Because each cell is using the same bandwidth *B*, the adjacent cell signals will eventually raise the noise level and degrade SIR for certain sub-channels. In certain embodiments, therefore, sub-channel assignment can be coordinated between cells, such as cells 1102, 1104, and 1106 in figure 10, in order to prevent interference from adjacent cells. Thus, if communication device 1108 is near the edge of cell 1102, and device 1118 is near the edge of cell 1106, then the two can interfere with each other. As a result, the SIR measurements that device 1108 and 1118 report back to base stations 1110 and 1114, respectively, will indicate that the interference level is too high. Base station 1110 can then be configured to assign only the odd groups, i.e., Gl, G3, G5, etc., to device 1108, while base station 1114 can be configured to assign the even groups to device 1118. The two devices 1108 and 1118 will then not interfere with each other due to the coordinated assignment of sub-channel groups.

Assigning the sub-channels in this manner reduces the overall bandwidth available to devices 1108 and 1118, respectively. In this case the bandwidth is reduced by a factor of two. But it should be remembered that devices operating closer to each base station 1110 and 1114, respectively, will still be able to use all channels if needed. Thus, it is only devices, such as device 1108, that are near the edge of a cell that will have the available bandwidth reduced. Contrast this with a CDMA system, for example, in which the bandwidth for all users is reduced, due to the spreading techniques used in such systems, by approximately a factor of 10 at all times. It can be seen, therefore, that the systems and methods for wireless communication over a wide bandwidth channel using a plurality of sub-channels not only improves the quality of service, but can also increase the available bandwidth significantly. When there are three devices 1108, 1118, and 1116 near the edge

of their respective adjacent cells 1102, 1104, and 1106, the sub-channels can be divided by three. Thus, device 1108, for example, can be assigned groups G1, G4, etc., device 1118 can be assigned groups G2, G5, etc., and device 1116 can be assigned groups G3, G6, etc. In this case the available bandwidth for these devices, i.e., devices near the edges of cells 1102, 1104, and 1106, is reduced by a factor of 3, but this is still better than a CDMA system, for example.

The manner in which such a coordinated assignment of sub-channels can work is illustrated by the flow chart in figure 13. First in step 1402, a communication device, such as device 1108, reports the SIR for all sub-channel groups G1 to G8. The SIRs reported are then compared, in step 1404, to a threshold to determine if the SIR is sufficiently low for each group. Alternatively, device 1108 can make the determination and simply report which groups are above or below the SIR. threshold. If the SIR levels are good for each group, then base station 1110 can make each group available to device 1108, in step 1406. Periodically, device 1108 preferably measures the SIR level and updates base station 1110 in case the SIR as deteriorated. For example, device 1108 may move from near the center of cell 1102 toward the edge, where interference from an adjacent cell may affect the SIR for device 1108. If the comparison in step 1404 reveals that the SIR levels are not good, then base station 1110 can be preprogrammed to assign either the odd groups or the even groups only to device 1108, which it will do in step 1408. Device 1108 then reports the SIR measurements for the odd or even groups it is assigned in step 1410, and they are again compared to a SIR threshold in step 1412. It is assumed that the poor SIR level is due to the fact that device 1108 is operating at the edge of cell 1102 and is therefore being interfered with by a device such as device 1118. But device 1108 will be interfering with device 1118 at the same time. Therefore, the assignment of odd or even groups in step 1408 preferably corresponds with the assignment of the opposite groups to device 1118, by base station 1114. Accordingly, when device 1108 reports the SIR measurements for whichever groups, odd or even, are assigned to it, the comparison in step 1410 should reveal that the SIR levels are now below the threshold level. Thus, base station 1110 makes the assigned groups available to device 1108 in step 1414. Again, device 1108 preferably periodically updates the SIR measurements by returning to step 1402.

It is possible for the comparison of step 1410 to reveal that the SIR levels are still above the threshold, which should indicate that a third device, e.g., device 1116 is still interfering with device 1108. In this case, base station 1110 can be preprogrammed to assign every third group to device 1108 in step 1416. This should correspond with the corresponding assignments of non-interfering channels to devices 1118 and 1116 by base stations 1114 and 1112, respectively. Thus, device 1108 should be able to operate on the sub-channel groups assigned, i.e., G1, G4, etc., without undue interference. Again, device 1108 preferably periodically updates the SIR measurements by returning to step 1402. Optionally, a third comparison step (not shown) can be implemented after step 1416, to ensure that the groups assigned to device 1408 posses an adequate SIR level for proper operation. Moreover, if there are more adjacent cells, i.e., if it is possible for devices in a 4<sup>th</sup> or even a 5<sup>th</sup> adjacent cell to interfere with device 1108, then the process of figure 13 would continue and the sub-channel groups would be divided even further to ensure adequate SIR levels on the sub-channels assigned to device 1108. Even though the process of figure 13 reduces the bandwidth available to devices at the edge of cells 1102, 1104, and 1106, the SIR measurements can be used in such a manner as to increase the data rate and therefore restore or even increase bandwidth. To

accomplish this, the transmitters and receivers used in base stations 1102, 1104, and 1106, and in devices in communication therewith, e.g., devices 1108, 1114, and 1116 respectively, must be capable of dynamically changing the symbol mapping schemes used for some or all of the sub-channel. For example, in some embodiments, the symbol mapping scheme can be dynamically changed among BPSK, QPSK, 8PSK, 16QAM, 32QAM, etc. As the symbol mapping scheme moves higher, i.e., toward 32QAM, the SIR level required for proper operation moves higher, i.e., less and less interference can be withstood. Therefore, once the SIR levels are determined for each group, the base station, e.g., base station 1110, can then determine what symbol mapping scheme can be supported for each sub-channel group and can change the modulation scheme accordingly. Device 1108 must also change the symbol mapping scheme to correspond to that of the base stations. The change can be effected for all groups uniformly, or it can be effected for individual groups. Moreover, the symbol mapping scheme can be changed on just the forward link, just the reverse link, or both, depending on the embodiment. Thus, by maintaining the capability to dynamically assign sub-channels and to dynamically change the symbol mapping scheme used for assigned sub-channels, the systems and methods described herein provide the ability to maintain higher available bandwidths with higher performance levels than conventional systems. To fully realize the benefits described, however, the systems and methods described thus far must be capable of implementation in a cost effect and convenient manner. Moreover, the implementation must include reconfigurability so that a single device can move between different types of communication systems and still maintain optimum performance in accordance with the systems and methods described herein. The following descriptions detail example high level embodiments of hardware implementations configured to operate in accordance with the systems and methods described herein in such a manner as to provide the capability just described above.

## 5. <u>Sample Transmitter Embodiments</u>

Figure 14 is logical block diagram illustrating an example embodiment of a transmitter 1500 configured for wireless communication in accordance with the systems and methods described above. The transmitter could, for example be within a base station, e.g., base station 606, or within a communication device, such as device 604. Transmitter 1500 is provided to illustrate logical components that can be included in a transmitter configured in accordance with the systems and methods described herein. It is not intended to limit the systems and methods for wireless communication over a wide bandwidth channel using a plurality of sub-channels to any particular transmitter configuration or any particular wireless communication system. With this in mind, it can be seen that transmitter 1500 comprises a serial-to-parallel converter 1504 configured to receive a serial data stream 1502 comprising a data rate R. Serial-to-parallel converter 1504 converts data stream 1502 into N parallel data streams 1504, where N is the number of sub-channels 202. It should be noted that while the discussion that follows assumes that a single serial data stream is used, more than one serial data stream can also be used if required or desired. In any case, the data rate of each parallel data stream 1504 is then R/N. Each data stream 1504 is then sent to a scrambler, encoder, and interleaver block 1506. Scrambling, encoding, and interleaving are common techniques implemented in many wireless communication transmitters and help to provide robust, secure communication. Examples of these techniques will be briefly explained for illustrative purposes.

Scrambling breaks up the data to be transmitted in an effort to smooth out the spectral density of the transmitted data. For example, if the data comprises a long string of "I"s, there will be a spike in the spectral density. This spike can cause greater interference within the wireless communication system. By breaking up the data, the spectral density can be smoothed out to avoid any such peaks. Often, scrambling is achieved by XORing the data with a random sequence. Encoding, or coding, the parallel bit streams 1504 can, for example, provide Forward Enor Correction (FEC). The purpose of FEC is to improve the capacity of a communication channel by adding some carefully designed redundant information to the data being transmitted through the channel. The process of adding this redundant information is known as channel coding. Convolutional coding and block coding are the two major forms of channel coding. Convolutional codes operate on serial data, one or a few bits at a time. Block codes operate on relatively large (typically, up to a couple of hundred bytes) message blocks. There are a variety of useful convolutional and block codes, and a variety of algorithms for decoding the received coded information sequences to recover the original data. For example, convolutional encoding or turbo coding with Viterbi decoding is a FEC technique that is particularly suited to a channel in which the transmitted signal is corrupted mainly by additive white gaussian noise (AWGN) or even a channel that simply experiences fading.

Convolutional codes are usually described using two parameters: the code rate and the constraint length. The code rate, k/m, is expressed as a ratio of the number of bits into the convolutional encoder (k) to the number of channel symbols (m) output by the convolutional encoder in a given encoder cycle. A common code rate is 1/2, which means that 2 symbols are produced for every 1-bit input into the coder. The constraint length parameter, K, denotes the "length" of the convolutional encoder, i.e. how many k-bit stages are available to feed the combinatorial logic that produces the output symbols. Closely related to K is the parameter m, which indicates how many encoder cycles an input bit is retained and used for encoding after it first appears at the input to the convolutional encoder. The m parameter can be thought of as the memory length of the encoder. Interleaving is used to reduce the effects of fading. Interleaving mixes up the order of the data so that if a fade interferes with a portion of the transmitted signal, the overall message will not be effected. This is because once the message is de-interleaved and decoded in the receiver, the data lost will comprise non-contiguous portions of the overall message. In other words, the fade will interfere with a contiguous portion of the interleaved message, but when the message is de-interleaved, the interfered with portion is spread throughout the overall message. Using techniques such as FEC, the missing information can then be filled in, or the impact of the lost data may just be negligible.

After blocks 1506, each parallel data stream 1504 is sent to symbol mappers 1508. Symbol mappers 1508 apply the requisite symbol mapping, e.g., BPSK, QPSK, etc., to each parallel data stream 1504. Symbol mappers 1508 are preferably programmable so that the modulation applied to parallel data streams can be changed, for example, in response to the SIR reported for each sub-channel 202. It is also preferable, that each symbol mapper 1508 be separately programmable so that the optimum symbol mapping scheme for each sub-channel can be selected and applied to each parallel data stream 1504. After symbol mappers 1508, parallel data streams 1504 are sent to modulators 1510. Important aspects and features of example embodiments of modulators 1510 are described below. After modulators 1510, parallel data streams 1504 are sent to summer 1512, which is configured to sum the parallel data streams and thereby generate a single serial data stream 1518

comprising each of the individually processed parallel data streams 1504. Serial data stream 1518 is then sent to radio module 1512, where it is modulated with an RF carrier, amplified, and transmitted via antenna 1516 according to known techniques.

The transmitted signal occupies the entire bandwidth *B* of communication channel 100 and comprises each of the discrete parallel data streams 1504 encoded onto their respective sub-channels 102 within bandwidth *B*. Encoding parallel data streams 1504 onto the appropriate sub-channels 102 requires that each parallel data stream 1504 be shifted in frequency by an appropriate offset. This is achieved in modulator 1510. Figure 15 is a logical block diagram of an example embodiment of a modulator 1600 in accordance with the systems and methods described herein. Importantly, modulator 1600 takes parallel data streams 1602 performs Time Division Modulation (TDM) or Frequency Division Modulation (FDM) on each data stream 1602, filters them using filters 1612, and then shifts each data stream in frequency using frequency shifter 1614 so that they occupy the appropriate sub-channel. Filters 1612 apply the required pulse shaping, i.e., they apply the roll-off factor described in section 1. The frequency shifted parallel data streams 1602 are then summed and transmitted. Modulator 1600 can also include rate controller 1604, frequency encoder 1606, and interpolators 1610. All of the components shown in figure 15 are described in more detail in the following paragraphs and in conjunction with figures 16-22.

Figure 16 illustrates one example embodiment of a rate controller 1700 in accordance with the systems and methods described herein. Rate control 1700 is used to control the data rate of each parallel data stream 1602. In rate controller 1700, the data rate is halved by repeating data streams d(0) to d(7), for example, producing streams a(0) to a(15) in which a(0) is the same as a(8), a(1) is the same as a(9), etc. Figure 16 also illustrates that the effect of repeating the data streams in this manner is to take the data streams that are encoded onto the first 8 sub-channels 1702, and duplicate them on the next 8 sub-channels 1702. As can be seen, 7 sub-channels separate sub-channels 1702 comprising the same, or duplicate, data streams. Thus, if fading effects one sub-channel 1702, for example, the other sub-channels 1702 carrying the same data will likely not be effected, i.e., there is frequency diversity between the duplicate data streams. So by sacrificing data rate, in this case half the data rate, more robust transmission is achieved. Moreover, the robustness provided by duplicating the data streams d(0) to d(7) can be further enhanced by applying scrambling to the duplicated data streams via scramblers 1708. It should be noted that the data rate can be reduced by more than half, e.g., by four or more. Alternatively, the data rate can also be reduced by an amount other than half. For example if information from n data stream is encoded onto m sub-channels, where m > n. Thus, to decrease the rate by 2/3, information from one data stream can be encoded on a first sub-channel, information from a second data stream can be encoded on a second data channel, and the sum or difference of the two data streams can be encoded on a third channel. In which case, proper scaling will need to be applied to the power in the third channel. Otherwise, for example, the power in the third channel can be twice the power in the first two. Preferably, rate controller 1700 is programmable so that the data rate can be changed responsive to certain operational factors. For example, if the SIR reported for sub-channels 1702 is low, then rate controller 1700 can be programmed to provide more robust transmission via repetition to ensure that no data is lost due to interference. Additionally, different types of wireless

communication system, e.g., indoor, outdoor, line-of-sight, may require varying degrees of robustness. Thus, rate controller 1700 can be adjusted to provide the minimum required robustness for the particular type of communication system. This type of programmability not only ensures robust communication, it can also be used to allow a single device to move between communication systems and maintain superior performance.

Figure 17 illustrates an alternative example embodiment of a rate controller 1800 in accordance with the systems and methods described. In rate controller 1800 the data rate is increased instead of decreased. This is accomplished using serial-to-parallel converters 1802 to convert each data streams d(0) to d(15), for example, into two data streams. Delay circuits 1804 then delay one of the two data streams generated by each serial-to-parallel converter 1802 by 1/2 a symbol. Thus, data streams d(0) to d(15) are transformed into data streams a(0) to a(31). The data streams generated by a particular serial-to-parallel converter 1802 and associate delay circuit 1804 must then be summed and encoded onto the appropriate sub-channel. For example, data streams a(0) and a(1) must be summed and encoded onto the first sub-channel. Preferably, the data streams are summed subsequent to each data stream being pulsed shaped by a filter 1612. Thus, rate controller 1604 is preferably programmable so that the data rate can be increased, as in rate controller 1800, or decreased, as in rate controller 1700, as required by a particular type of wireless communication system, or as required by the communication channel conditions or sub-channel conditions. In the event that the data rate is increased, filters 1612 are also preferably programmable so that they can be configured to apply pulse shapping to data streams a(0) to a(31), for example, and then sum the appropriate streams to generate the appropriate number of parallel data streams to send to frequency shifter 1614. The advantage of increasing the data rate in the manner illustrated in figure 17 is that higher symbol mapping rates can essentially be achieved, without changing the symbol mapping used in symbol mappers 1508. Once the data streams are summed, the summed streams are shifted in frequency so that they reside in the appropriate sub-channel. But because the number of bits per each symbol has been doubled, the symbol mapping rate has been doubled. Thus, for example, a 4QAM symbol mapping can be converted to a 16QAM symbol mapping, even if the SIR is too high for 16QAM symbol mapping to otherwise be applied. In other words, programming rate controller 1800 to increase the data rate in the manner illustrated in figure 17 can increase the symbol mapping even when channel conditions would otherwise not allow it, which in turn can allow a communication device to maintain adequate or even superior performance regardless of the type of communication system. The draw back to increasing the data rate as illustrated in figure 17 is that interference is increased, as is receiver complexity. The former is due to the increased amount of data. The latter is due to the fact that each symbol cannot be processed independently because of the 1/2 symbol overlap. Thus, these concerns must be balanced against the increase symbol mapping ability when implementing a rate controller such as rate controller 1800.

Figure 18 illustrates one example embodiment of a frequency encoder 1900 in accordance with the systems and methods described herein. Similar to rate encoding, frequency encoding is preferably used to provide increased communication robustness. In frequency encoder 1900 the sum or difference of multiple data streams are encoded onto each sub-channel. This is accomplished using adders 1902 to sum data streams d(0) to d(7) with data streams d(8) to d(15), respectively, while adders 1904 subtract data streams d(0) to d(7) from data streams d(8) to d(15), respectively, as shown.

Thus, data streams a(0) to a(15) generated by adders 1902 and 1904 comprise information related to more than one data streams d(0) to d(15). For example, a(0) comprises the sum of d(0) and d(8), i.e., d(0) + d(8), while a(8) comprises d(8) - d(0). Therefore, if either a(0) or a(8) is not received due to fading, for example, then both of data streams d(0) and d(8) can still be retrieved from data stream a(8).

Essentially, the relationship between data stream d(0) to d(15) and a(0) to a(15) is a matrix relationship. Thus, if the receiver knows the correct matrix to apply, it can recover the sums and differences of d(0) to d(15) from a(0) to a(15). Preferably, frequency encoder 1900 is programmable, so that it can be enabled and disabled in order to provided robustness when required. Preferable, adders 1902 and 1904 are programmable also so that different matrices can be applied to d(0) to d(15). After frequency encoding, if it is included, data streams 1602 are sent to TDM/FDM blocks 1608. TDM/FDM blocks 1608 perform TDM or FDM on the data streams as required by the particular embodiment. Figure 19 illustrates an example embodiment of a TDM/FDM block 2000 configured to perform TDM on a data stream. TDM/FDM block 2000 is provided to illustrate the logical components that can be included in a TDM/FDM block configured to perform TDM on a data stream. Depending on the actual implementation, some of the logical components may or may not be included. TDM/FDM block 2000 comprises a sub-block repeater 2002, a sub-block scrambler 2004, a sub-block terminator 2006, a sub-block repeater 2008, and a sync inserter 2010. Sub-block repeater 2002 is configured to receive a sub-block of data, such as block 2012 comprising bits a(0) to a(3) for example. Sub-block repeater is then configured to repeat block 2012 to provide repetition, which in turn leads to more robust communication. Thus, sub-block repeater 2002 generates block 2014, which comprises 2 blocks 2012. Sub-block scrambler 2004 is then configured to receive block 2014 and to scramble it, thus generating block 2016. One method of scrambling can be to invert half of block 2014 as illustrated in block 2016. But other scrambling methods can also be implemented depending on the embodiment.

Sub-block terminator 2006 takes block 2016 generated by sub-block scrambler 2004 and adds a termination block 2034 to the front of block 2016 to form block 2018. Termination block 2034 ensures that each block can be processed independently in the receiver. Without termination block 2034, some blocks may be delayed due to multipath, for example, and they would therefore overlap part of the next block of data. But by including termination block 2034, the delayed block can be prevented from overlapping any of the actual data in the next block. Termination block 2034 can be a cyclic prefix termination 2036. A cyclic prefix termination 2036 simply repeats the last few symbols of block 2018. Thus, for example, if cyclic prefix termination 2036 is three symbols long, then it would simply repeat the last three symbols of block 2018. Alternatively, termination block 2034 can comprise a sequence of symbols that are known to both the transmitter and receiver. The selection of what type of block termination 2034 to use can impact what type of equalizer is used in the receiver. Therefore, receiver complexity and choice of equalizers must be considered when determining what type of termination block 2034 to use in TDM/FDM block 2000. After sub-block terminator 2006, TDM/FDM block 2010 can include a sub-block repeater 2008 configured to perform a second block repeater to perform a second block scrambling step as well. After sub-block repeater 2008, if included, TDM/FDM block 2000 comprises a sync inserter 210 configured to

periodically insert an appropriate synchronization code 2032 after a predetermined number of blocks 2020 and/or to insert known symbols into each block. The purpose of synchronization code 2032 is discussed in section 3.