## (12)发明专利

(10)授权公告号 CN 106648552 B

(45)授权公告日 2019.02.22

(21)申请号 201611216183.6

(74)专利代理机构 上海专利商标事务所有限公司 31100

(22)申请日 2012.06.29

代理人 黄嵩泉

(65)同一申请的已公布的文献号

申请公布号 CN 106648552 A

(51)Int.Cl.

G06F 9/38(2006.01)

(43)申请公布日 2017.05.10

(56)对比文件

(30)优先权数据

13/193,779 2011.07.29 US

CN 1549964 A, 2004.11.24,

US 2010/0118041 A1, 2010.05.13,

US 2011/0161974 A1, 2011.06.30,

US 7773090 B1, 2010.08.10,

CN 101884029 A, 2010.11.10,

CN 102103567 A, 2011.06.22,

(62)分案原申请数据

201280037791.4 2012.06.29

审查员 刘畅

(73)专利权人 英特尔公司

地址 美国加利福尼亚州

(72)发明人 B·靳兹伯格 E·纳坦森

I·殴萨池依 Y·扎克

权利要求书2页 说明书3页 附图4页

## (54)发明名称

处理设备、异构处理系统和数据处理系统

## (57)摘要

本发明涉及CPU/GPU同步机制。可以使用一个处理器上的线程来使另一个处理器能对互斥上锁或释放。例如，中央处理单元线程可以由图形处理单元使用以保护共享存储器的互斥。

1.一种处理设备,包括:

主中央处理单元CPU,用于执行库的第一线程;

与所述主CPU耦合的图形处理单元GPU,所述主CPU和所述GPU用于共享到共享虚拟地址空间的访问,所述第一线程用于同步到所述共享虚拟地址空间的访问;

其中所述第一线程用于同步第二线程和第三线程之间的访问,所述第二线程用于在所述主CPU上执行,所述第三线程用于在所述GPU上执行;以及

其中所述第一线程用于经由获取操作和释放操作来同步访问,所述获取操作和所述释放操作是响应于从所述第三线程接收的请求而执行的。

2.如权利要求1所述的处理设备,其特征在于,所述第三线程用于经由所述获取操作来访问所述共享虚拟地址空间中的数据并且等待所述数据直到所述第二线程释放所述数据。

3.如权利要求2所述的处理设备,其特征在于,所述第三线程用于经由所述释放操作在所述访问后释放所述数据,所述释放使所述第二线程能访问所述数据。

4.如权利要求1—3的任一项所述的处理设备,其特征在于,所述GPU用于在从所述主CPU接收到信号消息时唤醒所述第三线程。

5.如权利要求4所述的处理设备,其特征在于,所述第一线程用于允许所述主CPU和所述GPU之间的信号消息。

6.如权利要求1所述的处理设备,其特征在于,所述第一线程用于同步所述第三线程和所述第一线程之间的访问。

7.如权利要求1所述的处理设备,其特征在于,所述主CPU和所述GPU集成在一个集成电路内。

8.如权利要求7所述的处理设备,其特征在于,所述主CPU包括多个处理核。

9.如权利要求8所述的处理设备,其特征在于,所述GPU是多线程的多核并行处理器。

10.一种异构处理系统,包括:

多个异构处理器,包括主CPU以及与所述主CPU耦合的GPU;

由所述主CPU和所述GPU共享的存储器,其中所述存储器包括共享虚拟地址空间;以及

用于在所述主CPU上执行的第一线程,用于同步所述主CPU上的第二线程与所述GPU上的第三线程的存储器访问,其中所述第一线程用于经由获取操作和释放操作来同步访问,所述获取操作和所述释放操作是响应于从所述第三线程接收的请求而执行的。

11.如权利要求10所述的异构处理系统,其特征在于,所述GPU上的所述第三线程用于请求获得对所述共享虚拟地址空间中的数据的访问,并且等待获取对所述数据的访问直到所述数据被所述第一线程释放。

12.如权利要求11所述的异构处理系统,其特征在于,所述GPU用于在从所述主CPU接收到信号消息时唤醒所述第三线程,所述信号消息用于使所述第三线程能获取对所述数据的访问。

13.如权利要求10所述的异构处理系统,其特征在于,所述第一线程用于同步所述第三线程和所述第一线程之间的访问。

14.如权利要求10所述的异构处理系统,其特征在于,所述多个异构处理器集成在一个集成电路内。

15.如权利要求10所述的异构处理系统,其特征在于,另外包括与所述GPU相关联的驱

动器,所述驱动器用于在所述主CPU上执行以便在所述第一线程和所述第三线程之间传送同步消息。

16. 如权利要求10—15的任一项所述的异构处理系统,其特征在于,所述主CPU包括多个处理核,且所述GPU是多线程的多核并行处理器。

17. 一种数据处理系统,包括:

多个异构处理器,包括主CPU以及与所述主CPU耦合的GPU,所述多个异构处理器集成在一个集成电路内;

显示设备,用于显示来自所述GPU的输出;

由所述主CPU和所述GPU共享的存储器,其中所述存储器包括共享虚拟地址空间;以及

用于在所述主CPU上执行的第一线程,用于同步所述主CPU上的第二线程和所述GPU上的第三线程的存储器访问,其中所述第一线程用于经由获取操作和释放操作来同步访问,所述获取操作和所述释放操作是响应于从所述第三线程接收的请求而执行的。

18. 如权利要求17所述的数据处理系统,其特征在于,所述GPU上的所述第三线程用于请求获取对所述共享虚拟地址空间中的数据的访问,等待以获取对所述数据的访问直到所述数据被所述第一线程释放,且所述GPU在从所述主CPU接收到信号消息时唤醒所述第三线程,所述信号消息用于使所述第三线程能获取对所述数据的访问,且所述第一线程用于同步所述第三线程和所述第一线程之间的访问。

19. 如权利要求17所述的数据处理系统,其特征在于,另外包括与所述GPU相关联的驱动器,所述驱动器用于在所述主CPU上执行以便在所述第一线程和所述第三线程之间传送同步消息。

20. 如权利要求17—19的任一项所述的数据处理系统,其特征在于,所述主CPU包括多个处理核,且所述GPU是多线程的多核并行处理器。

## 处理设备、异构处理系统和数据处理系统

[0001] 本申请是申请日为2012年6月29日申请号为第201280037791.4号发明名称为“CPU/GPU同步机制”的中国专利申请的分案申请。

### 技术领域

[0002] 本申请一般地涉及具有通用处理器和图形处理单元的计算机。

### 背景技术

[0003] 运行在通用或中央处理单元上由用户应用所使用的存储器和由图形处理单元所使用的处理器通常是分开的。图形处理单元驱动器将数据从用户空间复制到驱动器存储器以在图形处理单元上进行处理。在共享的虚拟存储器模型中，数据没有被复制到图形处理单元，而是相反地，它在图形处理单元和中央处理单元之间共享。

[0004] 当前，在多线程应用中，共享的数据由称为互斥的锁来保护。每个想要访问共享数据的线程都必须首先对相对应的互斥上锁以阻止其它线程访问该互斥。此上锁可以通过锁上的“回旋(spinning)”来进行，但这个技术从功率和性能的角度效率不高。

[0005] 为了优化中央处理单元，操作系统提供允许线程休眠直到有互斥可用、然后当互斥被解锁时通知其它线程的系统调用。但这个机制只对于运行在中央处理单元核上的线程生效。

### 附图说明

[0006] 图1是本发明的一个实施例的示意图；

[0007] 图2是根据本发明的一个实施例的扩展线程和存储器模型；

[0008] 图3是根据本发明的一个实施例的页错误处理的流程图；以及

[0009] 图4是一个实施例的系统图。

### 具体实施方式

[0010] 在一个实施例中，对每个运行在图形处理器上的线程群，可以创建运行在中央处理单元上的辅助影子线程。当运行在图形处理器上的线程想要对互斥上锁时，如果它想要等待直到该线程由其它任务释放，则图形线程向中央处理单元上的影子线程发送请求。中央处理单元上的影子线程向操作系统发出相对应的系统调用。当操作系统将锁给影子线程时，影子线程向图形处理器上的线程发送通知。

[0011] 当在本申请中使用术语图形处理器时，应理解图形处理器可以是或可以不是单独的集成电路。本发明对图形处理器和中央处理单元集成到一个集成电路的情形适用。如此处所使用的，处理器或处理单元可以是处理器、控制器或协处理器。

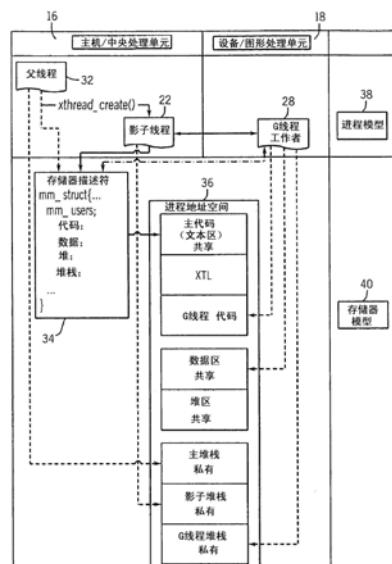

[0012] 参考图1，在基于处理器的系统10中，主/中央处理单元16与图形处理器18通信。主/中央处理单元16可以是包括硬连线或移动设备的任何基于处理器的系统的一部分。举几个示例，移动设备的示例包括蜂窝电话、膝上型计算机、平板计算机和移动因特网设备。

主中央处理单元16包括用户应用20,它向影子线程22提供控制信息。然后影子线程22向图形处理单元驱动器26通信关于同步和控制信息的同步。影子线程也和主操作系统24通信。

[0013] 如图1中所示,用户级别12包括影子线程22和用户应用20,而内核级别14包括主操作系统24和图形处理单元驱动器26。图形处理单元驱动器26是图形处理单元的驱动器,即使该驱动器驻留在中央处理单元16中。

[0014] 在用户级别12中,图形处理单元18包括g线程(gthread)28,它向操作系统(poS)30发送控制和同步消息并从操作系统30接收消息。g线程是运行在图形处理单元上的用户代码,与运行在中央处理单元上的父线程共享虚拟存储器。操作系统30可以是相对小的操作系统,它运行在图形处理单元上,负责图形处理单元异常。作为一个示例,它相对于主操作系统24是小的。

[0015] 用户应用20是运行在中央处理单元16上的任何用户进程。用户应用20派生图形处理单元18上的线程。

[0016] 扩展线程库或XTL是创建和管理图形处理单元上的用户线程的扩展。这个库为每个g线程创建影子线程并具有用于同步的库函数。

[0017] 用户应用使用传统多线程模型的扩展将计算卸载到图形处理单元,扩展诸如:

[0018] `xthread_create(thread,attr,gpu_worker,arg)`。

[0019] 在图形处理单元上创建的g线程或工作者线程与父线程共享虚拟存储器。在可以使用所有标准的过程间同步机制诸如互斥和信号机的意义上,它以与常规线程相同的方式行为。同时,在主中央处理单元16上创建新影子线程。这个影子线程充当异常处理单元的代理和中央处理单元与图形处理单元上的线程之间的同步。

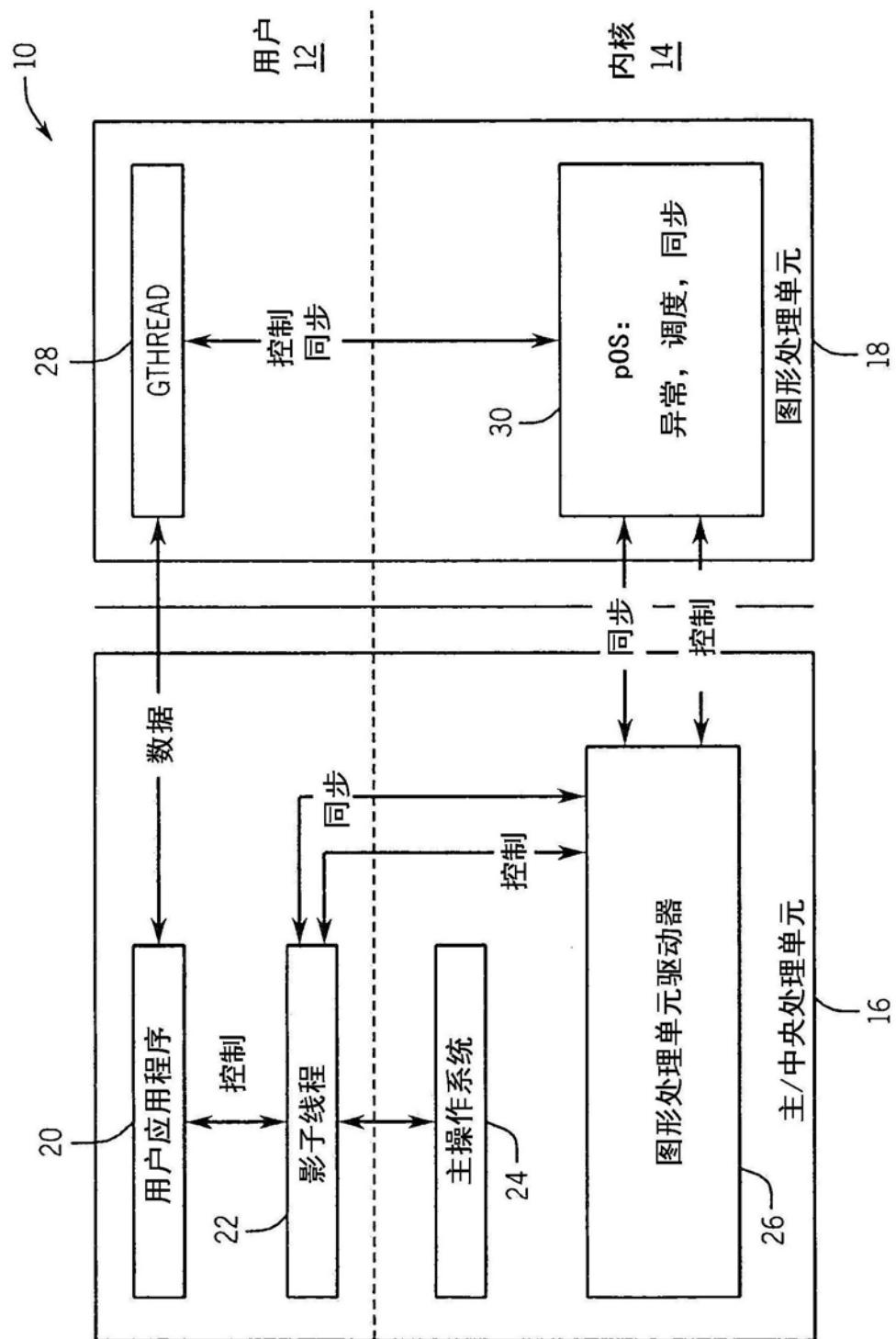

[0020] 在一些实施例中,父线程、主影子线程和图形处理单元工作者线程可以共享虚拟存储器,如图2中所示。主/中央处理单元16包括为影子线程22生成`xthread_create()`的父线程32。影子线程22访问影子堆栈,影子堆栈是进程地址空间36中的私有地址空间。父线程32也访问存储器描述符34和主堆栈,主堆栈是进程地址空间36内的私有地址空间。存储器描述符34也可以与g线程工作者28通信。g线程工作者28可以访问进程空间36内的g线程代码以及共享数据区和私有g线程堆栈。较上的框中的材料对应于进程模型38,并且较下的框相对应于存储器模型40。

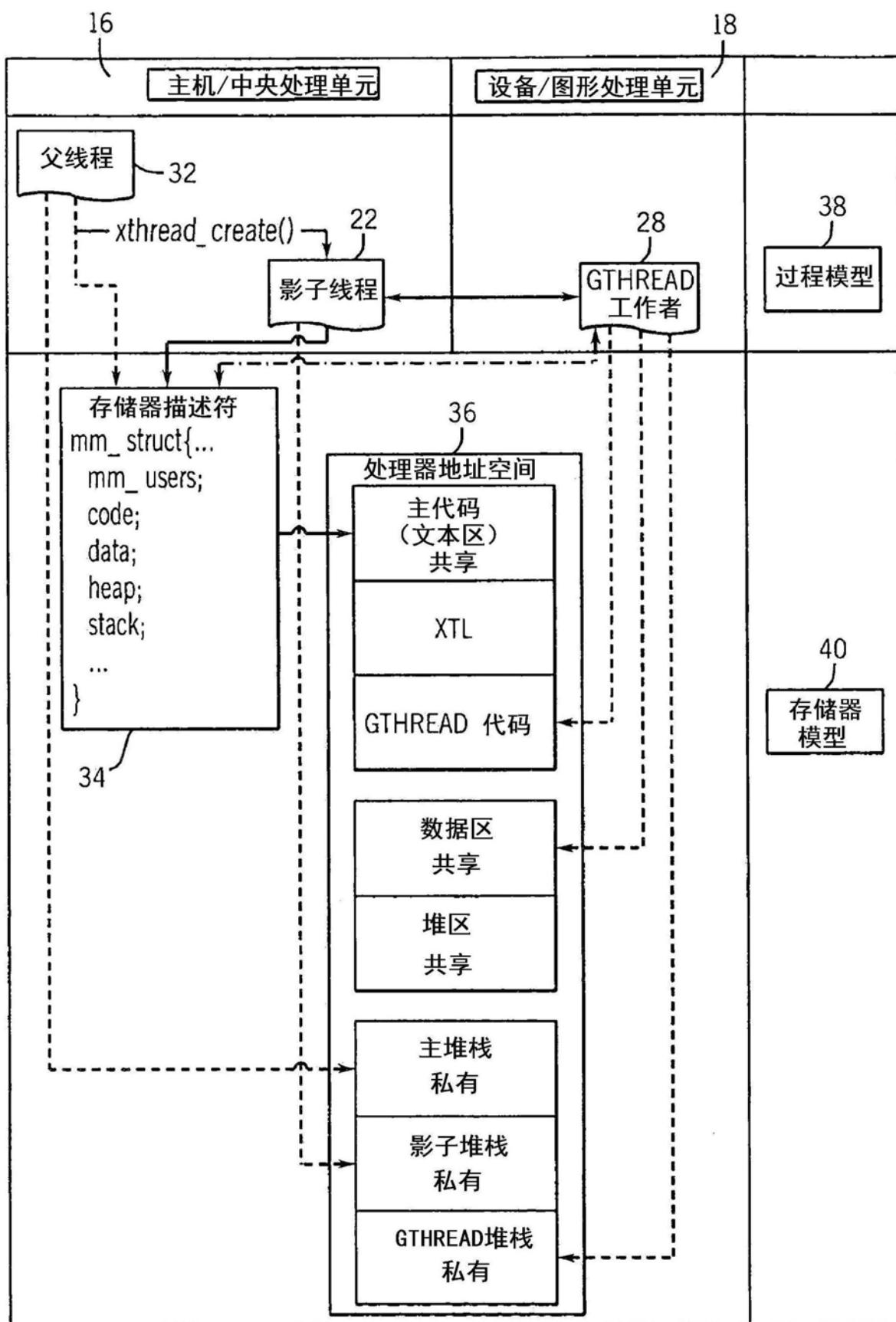

[0021] 参考图3,同步算法可以用硬件、软件和/或固件来实现。在软件实施例中,算法可以作为存储在非瞬态计算机可读介质上的计算机可执行指令来实现,介质诸如光学、半导体或磁存储设备。在图3中,中央处理单元16的主操作系统24、影子线程22、驱动器26和图形处理单元18中的操作系统30和环3 57的流程示为并行的垂直流程路径,且一般由水平箭头指示的它们之间的交互。

[0022] 继续在图3中,在一个实施例中,在环3,g线程28试图通过回旋(spinning)一小段时间来从用户空间获取互斥,如列中的框60中所指示的。如果成功地获取了互斥,如菱形61中所确定的,则程序继续,如框62中所指示的。如果由于互斥已经由另一线程上锁而没有被获取,则用ACQUIRE操作码进行对操作系统30的调用(SYSCALL)。

[0023] 在操作系统30中接收SYSCALL。操作系统30向驱动器发送称为PassHostCommand(通过主机命令)的消息。PassHostCommand包括SYSCALL的操作码和地址加操作的数据,如框50中所指示的。然后操作系统30将调用线程置为休眠,如框54中所指示的。然后调用线程

进入空闲,如框56中所指示的。

[0024] 中央处理单元16中的驱动器26使用传输命令将消息传输给影子线程22。在影子线程22中,接收传输命令。Xthread等待来自驱动器的这个消息,如框44中所指示的。然后Xthread执行对互斥上锁,如框46中所指示的,并可以包括对主操作系统24的SYSCALL。操作系统24等待,直到获取了互斥(即,存在上下文切换),如42处所指示的。在获取了互斥之后,Xthread向驱动器26发送恢复执行命令,然后等待来自驱动器的下一消息,如框48中所指示的。

[0025] 驱动器26接收恢复执行命令并向图形处理单元中的操作系统30发送PassGpuCommand(通过Gpu命令)消息。PassGpuCommand可以包括不带数据的resume\_execution的操作码,如框52中所指示的。

[0026] 操作系统30唤醒线程,如框58中所指示的,并向g线程28发送来自SYSCALL的恢复。结果是,g线程28继续工作,如框62中所指示的。影子线程也可以用来释放互斥。

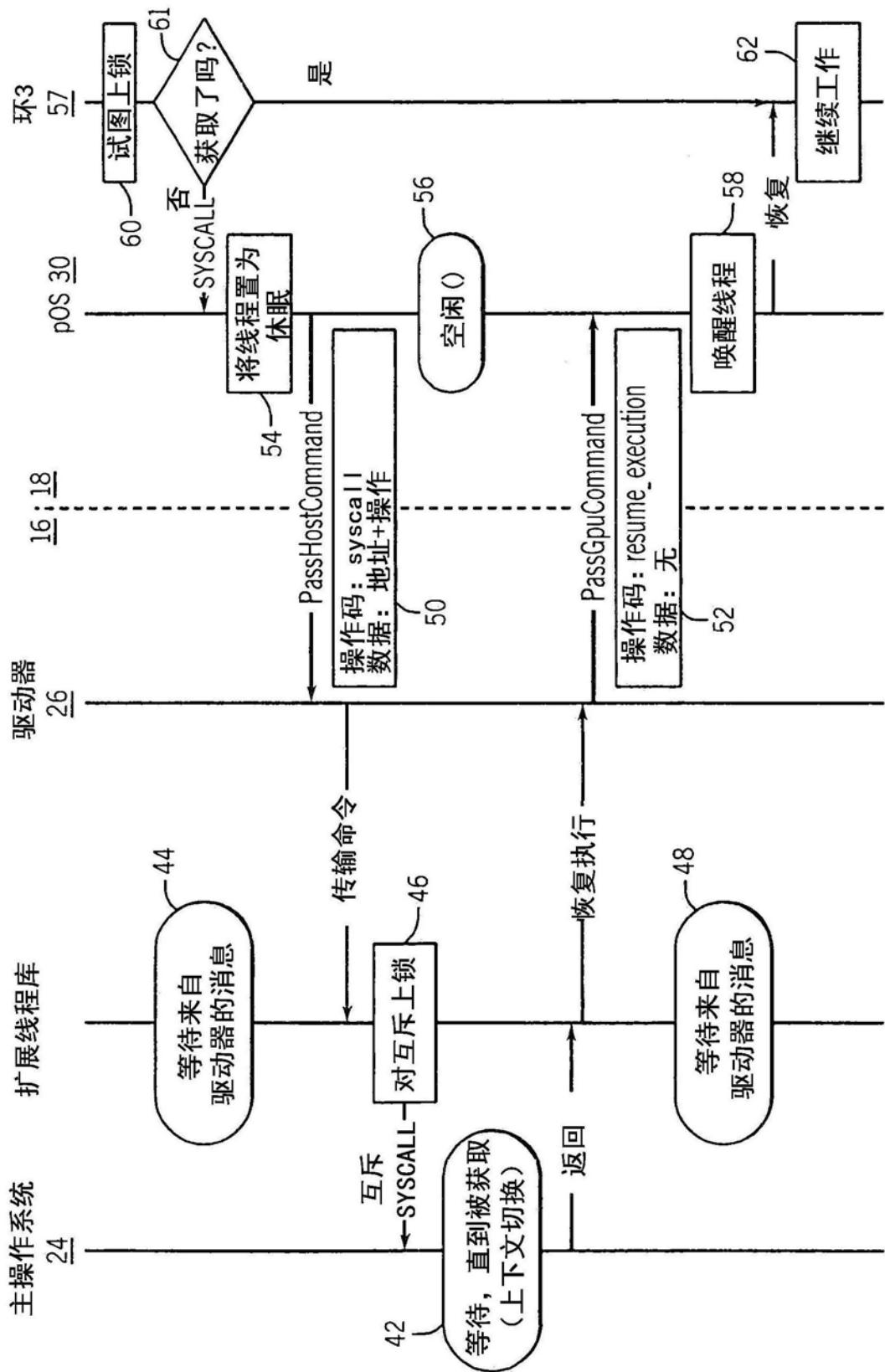

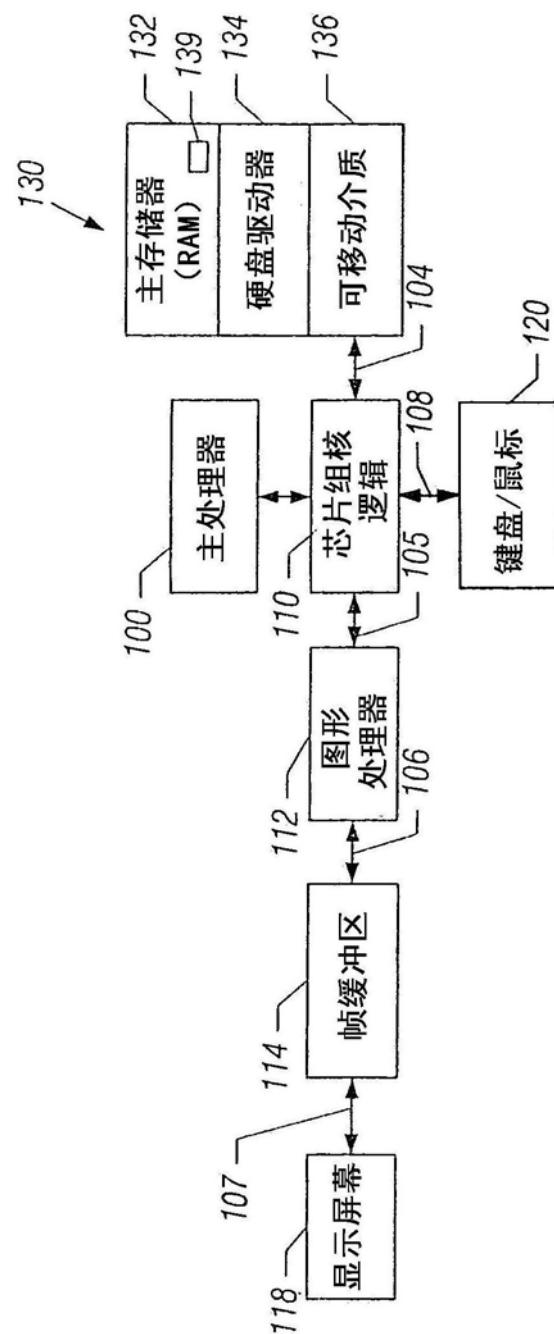

[0027] 图4中所示的计算机系统130可以包括通过总线104耦合到芯片组核逻辑110的硬盘驱动器134和可移动介质136。键盘和鼠标120或其它传统组件可以经由总线108耦合到芯片组核逻辑。在一个实施例中,核逻辑可以经由总线105耦合到图形处理器112,和耦合到主处理器100(例如,中央处理器)。图形处理器112还可以通过总线106耦合到帧缓冲器114。帧缓冲器114可以通过总线107耦合到显示屏幕118。在一个实施例中,图形处理器112可以是使用单指令多数据(SIMD)架构的多线程、多核并行处理器。

[0028] 在软件实现的情况下,相关代码可以存储在任何适合的半导体、磁或光学存储器中,包括主存储器132(如139处所指示的)或图形处理器内任何可用的存储器。因此,在一个实施例中,执行图3的序列的代码可以存储在非瞬态机器或计算机可读介质(诸如存储器132和/或图形处理器112和/或主处理器100)中,并在一个实施例中可以由主处理器100和/或图形处理器112执行。

[0029] 图3是流程图。在一些实施例中,在此流程图中描绘的序列可以用硬件、软件或固件实现。在软件实施例中,非瞬态计算机可读介质,诸如半导体存储器、磁存储器或光学存储器,可以用来存储指令并可以由处理器执行以实现图3中所示的序列。

[0030] 此处描述的图形处理技术可以用各种硬件架构实现。例如,图形功能可以集成在芯片组中。替换性地,可以使用离散图形处理器。如又一实施例,图形功能可以通过通用处理器(包括多核处理器)来实现。

[0031] 贯穿本说明书的对“一个实施例”和“实施例”的引用意味着结合实施例所描述的特定特征、结构或特性包括在涵盖于本发明的至少一个实现中。因此,短语“一个实施例”或“在实施例中”的出现不必全都指的是同一实施例。而且,除了所示的特定实施例之外,特定特征、结构和特性还可以用其它适合的形式建立,且所有这样的形式都可以涵盖于本申请的权利要求书中。

[0032] 尽管参考有限数量的实施例描述了本发明,本领域的技术人员从中可以理解众多修改和变化。所附权利要求书旨在覆盖所有这样落入本发明的真正的精神和范围内的修改和变化。

图1

图2

图3

图4