(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6415192号

(P6415192)

(45) 発行日 平成30年10月31日(2018.10.31)

(24) 登録日 平成30年10月12日(2018.10.12)

(51) Int.Cl.

F 1

**G02F 1/1368 (2006.01)**

**G09F 9/30 (2006.01)**

**H01L 29/786 (2006.01)**

GO2 F 1/1368

GO9 F 9/30 338

H01 L 29/78 612 C

H01 L 29/78 618 B

H01 L 29/78 618 E

請求項の数 6 (全 69 頁)

(21) 出願番号 特願2014-180826 (P2014-180826)

(22) 出願日 平成26年9月5日 (2014.9.5)

(65) 公開番号 特開2016-1292 (P2016-1292A)

(43) 公開日 平成28年1月7日 (2016.1.7)

審査請求日 平成29年9月1日 (2017.9.1)

(31) 優先権主張番号 特願2013-190864 (P2013-190864)

(32) 優先日 平成25年9月13日 (2013.9.13)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2013-249904 (P2013-249904)

(32) 優先日 平成25年12月3日 (2013.12.3)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2014-47241 (P2014-47241)

(32) 優先日 平成26年3月11日 (2014.3.11)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 久保田 大介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 初見 亮

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 佐藤 洋允

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

絶縁表面に、信号線として機能する導電膜、走査線として機能する導電膜、トランジスタ、画素電極、及びコモン電極を有し、

前記トランジスタは、前記信号線として機能する導電膜、前記走査線として機能する導電膜、及び前記画素電極と電気的に接続され、

前記コモン電極は、一部が前記信号線として機能する導電膜と重なる第1の領域と、一部が前記画素電極と重なる第2の領域とを有し、

前記第1の領域及び前記第2の領域は延伸方向が異なり、

前記コモン電極は、平面視において前記信号線として機能する導電膜と前記画素電極の間の領域に、屈曲点を有し、

前記第1の領域及び前記第2の領域が成す角は、平面形状において第1の角度を有し、

前記第1の領域、及び前記信号線として機能する導電膜の垂線が成す角は、平面形状において第2の角度を有し、

前記第1の角度は、90°より大きく180°未満であり、

前記第2の角度は0°より大きく90°未満であり、

前記第1の角度及び前記第2の角度の和は、135°より大きく180°未満であることを特徴とする表示装置。

## 【請求項2】

絶縁表面に、信号線として機能する導電膜、走査線として機能する導電膜、トランジス

10

20

タ、画素電極、コモン電極、及び容量素子を有し、

前記トランジスタは、

前記走査線として機能する導電膜と電気的に接続されるゲート電極と、

前記ゲート電極と重なり、且つ前記信号線として機能する導電膜と電気的に接続される半導体膜と、

前記ゲート電極及び前記半導体膜の間のゲート絶縁膜と、

前記画素電極及び前記半導体膜に接続される導電膜と、を有し、

前記容量素子は、

前記画素電極と、

前記コモン電極と、

前記画素電極及び前記コモン電極の間に設けられる窒化物絶縁膜と、を有し、

前記コモン電極は、一部が前記信号線として機能する導電膜と重なる第1の領域と、一部が前記画素電極と重なる第2の領域とを有し、

前記第1の領域及び前記第2の領域は延伸方向が異なり、

前記コモン電極は、平面視において前記信号線として機能する導電膜と前記画素電極の間の領域に、屈曲点を有し、

前記第1の領域及び前記第2の領域は、平面形状において第1の角度を有し、

前記第1の領域、及び前記信号線として機能する導電膜の垂線は、平面形状において第2の角度を有し、

前記第1の角度は、90°より大きく180°未満であり、

前記第2の角度は0°より大きく90°未満であり、

前記第1の角度及び前記第2の角度の和は、135°より大きく180°未満であることを特徴とする表示装置。

### 【請求項3】

請求項2において、

前記半導体膜及び前記画素電極は、前記ゲート絶縁膜と接することを特徴とする表示装置。

### 【請求項4】

請求項2または請求項3において、

前記半導体膜及び前記画素電極は、In-Ga酸化物膜、In-Zn酸化物膜、またはIn-M-Zn酸化物膜(MはAl、Ga、Y、Zr、Sn、La、Ce、またはNd)を有することを特徴とする表示装置。

### 【請求項5】

請求項2乃至請求項4のいずれか一項において、

前記半導体膜及び前記画素電極は、第1の膜及び第2の膜を含む多層構造であり、

前記第1の膜は、前記第2の膜と金属元素の原子数比が異なることを特徴とする表示装置。

### 【請求項6】

請求項1乃至請求項5のいずれか一項において、

前記コモン電極は、前記走査線として機能する導電膜と交差し、且つ前記第1の領域または前記第2の領域と接続される領域を有することを特徴とする表示装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物(コンポジション・オブ・マター)に関する。特に、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、それらの駆動方法、または、それらの製造方法に関する。特に、本発明の一態様は、表示装置及びその作製方法に関する。

### 【背景技術】

10

20

30

40

50

**【0002】**

近年、液晶は多様なデバイスに利用されており、特に薄型、軽量の特徴を持つ液晶表示装置（液晶ディスプレイ）は、幅広い分野のディスプレイにおいて用いられている。

**【0003】**

液晶表示装置に含まれる液晶に電界を印加する方法として、縦電界方式または横電界方式がある。横電界方式の液晶表示パネルとしては、画素電極及びコモン電極が重ならずに設けられるIPS（In-Plane Switching）モードと、絶縁膜を介して画素電極及びコモン電極が重なるFFS（Fringe Field Switching）モードとがある。

**【0004】**

FFSモードの液晶表示装置は、画素電極にスリット状の開口部を有し、該開口部において画素電極及びコモン電極の間で生じる電界を液晶に印加することで、液晶分子の配向を制御する。

**【0005】**

FFSモードの液晶表示装置は、高開口率であり、広い視野角を得ることができると共に画像コントラストを改善できるという効果があり、近年、多く用いられるようになってきている（特許文献1参照。）。

**【0006】**

また、表示装置では、1秒間に数十回表示される画像が切り換っている。1秒間あたりの画像の切り替え回数はリフレッシュレートと呼ばれている。また、リフレッシュレートを駆動周波数と呼ぶこともある。このような人の目で知覚が困難である高速の画面の切り替えが、目の疲労の原因として考えられている。そこで、非特許文献1、2では、LCDのリフレッシュレートを低下させて、画像の書き換え回数を減らすことが提案されている。また、リフレッシュレートを低下させた駆動により、表示装置の消費電力を低減することが可能である。

**【先行技術文献】****【特許文献】****【0007】**

【特許文献1】特開2000-89255号公報

**【非特許文献】****【0008】**

【非特許文献1】S. Amano et al., "Low Power LC Display Using In-Ga-Zn-Oxide TFTs Based On Variable Frame Frequency", SID International Symposium Digest of Technical Papers, 2010, p. 626-629

【非特許文献2】R. Hatsumi et al., "Driving Method of FFS-Mode OS-LCD for Reducing Eye Strain", SID International Symposium Digest of Technical Papers, 2013, p. 338-341

**【発明の概要】****【発明が解決しようとする課題】****【0009】**

表示装置の一例である液晶表示装置においては、同一の画像を保持する期間中の画素の透過率の変化が少ないことが望ましい。電極間に蓄電された電荷容量を維持することで、表示素子に印加された電圧の変動を低減し、画素の透過率を維持することが可能である。

**【0010】**

さらに、リフレッシュレートを低減する駆動では、画素の透過率の変化が、同一画像における階調値のずれとして許容できる範囲よりも大きくなると、使用者が画像のちらつき（フリッカー）を知覚してしまう。即ち、表示装置の表示品質の低下を招く。

10

20

30

40

50

**【0011】**

そこで、本発明の一態様は、表示品質の優れた表示装置を提供する。または、本発明の一態様は、寄生容量による配線遅延が低減された表示装置を提供する。または、本発明の一態様は、光漏れが少なく、コントラストの優れた表示装置を提供する。または、本発明の一態様は、開口率が高く、且つ電荷容量を増大させることができ可能な容量素子を有する表示装置を提供する。または、本発明の一態様は、消費電力が低減された表示装置を提供する。または、本発明の一態様は、電気特性の優れたトランジスタを有する表示装置を提供する。または、本発明の一態様は、新規な表示装置を提供する。または、本発明の一態様は、少ない工程数で、高開口率であり、広い視野角が得られる表示装置の作製方法を提供する。または、本発明の一態様は、新規な表示装置の作製方法を提供する。

10

**【0012】**

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】****【0013】**

本発明の一態様は、画素において、信号線、走査線、トランジスタ、画素電極、及びコモン電極を有する表示装置において、信号線と重なる領域の延伸方向と、画素電極と重なる領域の延伸方向が、平面形状において異なり、且つ該延伸方向が信号線と画素電極の間で交差する形状のコモン電極を有することを特徴とする。

20

**【0014】**

コモン電極において、信号線と重なる領域の延伸方向と、画素電極と重なる領域の延伸方向とが異なり、且つ該延伸方向が信号線と画素電極の間で交差することで、信号線及びコモン電極の間で発生する電界方位と、画素電極及びコモン電極の間で発生する電界方位が交差する。この結果、信号線と重なる領域に設けられた第1の液晶分子の配向方向と、画素電極と重なる領域に設けられた第2の液晶分子の配向方向が異なるため、第2の液晶分子と、第1の液晶分子との配向は、互いに影響されにくい。

**【0015】**

信号線に異なる電圧が印加されると、電圧の印加ごとに、信号線と重なる領域に設けられた第1の液晶分子の配向方向は変化する。一方、一定電圧が印加された画素電極と重なる領域に設けられた第2の液晶分子は、第1の液晶分子の配向変化の影響を受けず、一定方向に配向する。この結果、画素の透過率の変化を抑制することが可能であり、ちらつきを抑制することができる。

30

**【0016】**

また、本発明の一態様は、絶縁表面に、信号線として機能する導電膜、走査線として機能する導電膜、トランジスタ、画素電極、及びコモン電極を有する。トランジスタは、信号線として機能する導電膜、走査線として機能する導電膜、及び画素電極と電気的に接続される。コモン電極は、信号線として機能する導電膜と重なる第1の領域と、画素電極と重なる第2の領域とを有する。第1の領域及び第2の領域は延伸方向が異なり、第1の領域及び第2の領域が成す角は、上面形状において第1の角度を有し、第1の領域、及び信号線として機能する導電膜の垂線が成す角は、上面形状において第2の角度を有する。第1の角度は、90°より大きく180°未満であり、第2の角度は0°より大きく90°未満であり、第1の角度及び第2の角度の和は、135°より大きく180°未満である。

40

**【0017】**

なお、トランジスタ上の酸化物絶縁膜と、酸化物絶縁膜上に設けられる窒化物絶縁膜とを有し、酸化物絶縁膜は、画素電極の一部を露出する開口部を有してもよい。

**【0018】**

また、画素電極は、マトリクス状に設けられている。

50

## 【0019】

コモン電極は、走査線として機能する導電膜と平行または略平行な方向において、第1の領域及び第2の領域が交互に配置される。また、コモン電極は、走査線として機能する導電膜と交差し、且つ第1の領域または第2の領域と接続される領域を有してもよい。

## 【0020】

半導体膜及び画素電極は、ゲート絶縁膜と接する。また、半導体膜及び画素電極は、In-Ga酸化物膜、In-Zn酸化物膜、またはIn-M-Zn酸化物膜（MはAl、Ga、Y、Zr、Sn、La、Ce、またはNd）を有する。また、半導体膜及び画素電極は、第1の膜及び第2の膜を含む多層構造であり、第1の膜は、第2の膜と金属元素の原子数比が異なってもよい。

10

## 【発明の効果】

## 【0021】

本発明の一態様により、表示品質の優れた表示装置を提供することができる。または、本発明の一態様により、寄生容量による配線遅延が低減された表示装置を提供することができる。または、本発明の一態様により、光漏れが少なく、コントラストの優れた表示装置を提供することができる。または、本発明の一態様により、開口率が高く、且つ電荷容量を増大させることができ容量素子を有する表示装置を提供することができる。または、本発明の一態様により、消費電力が低減された表示装置を提供することができる。本発明の一態様により、電気特性の優れたトランジスタを有する表示装置を提供することができる。または、本発明の一態様により、少ない工程数で、高開口率であり、広い視野角を得られる表示装置を作製することができる。または、本発明の一態様により、新規な表示装置を提供することができる。なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

20

## 【図面の簡単な説明】

## 【0022】

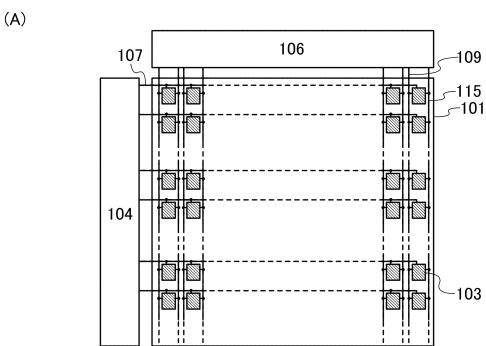

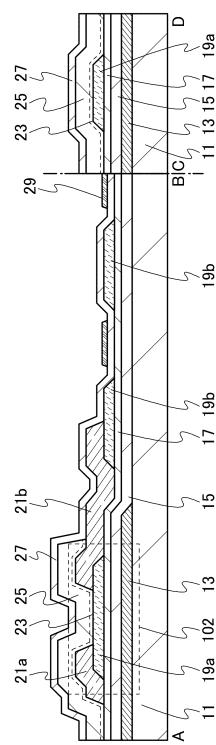

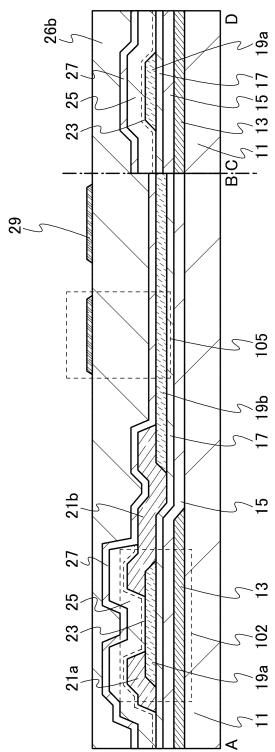

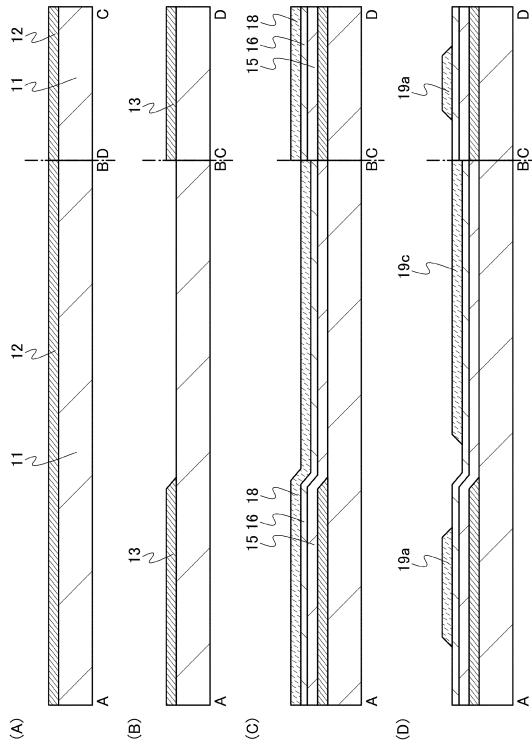

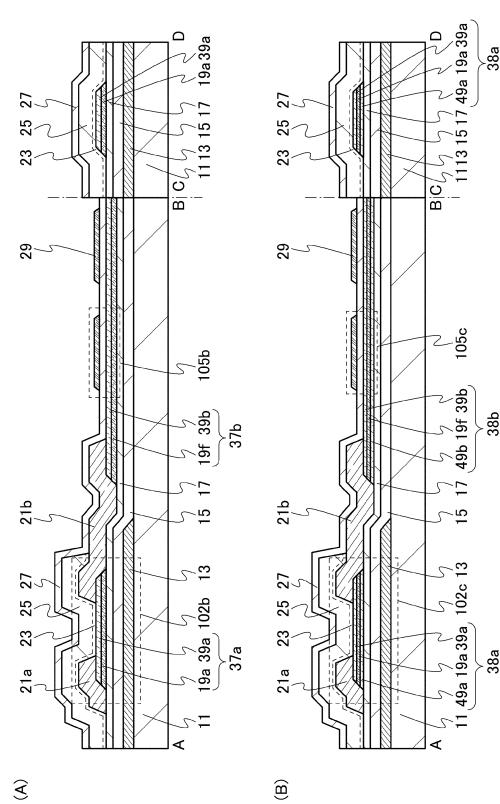

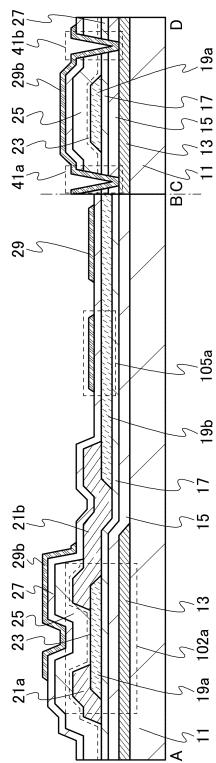

【図1】表示装置の一形態を説明する断面図及び上面図である。

30

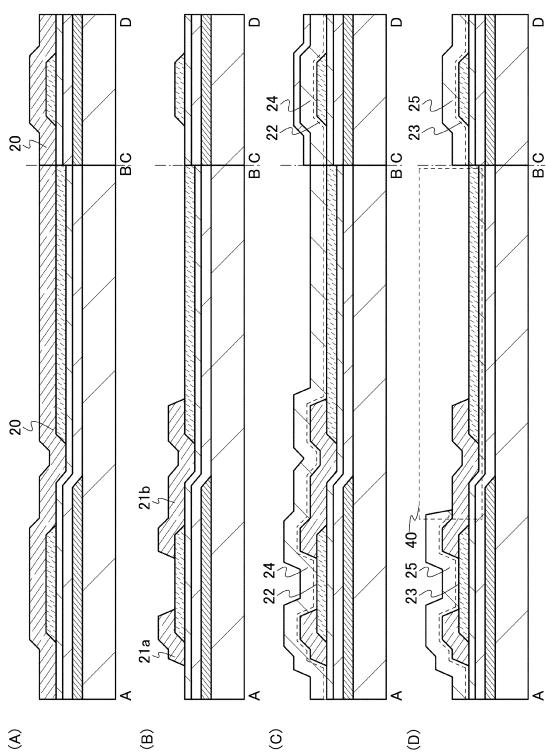

【図2】表示装置の一形態を説明する上面図である。

【図3】表示装置の一形態を説明する上面図である。

【図4】表示装置の一形態を説明する断面図である。

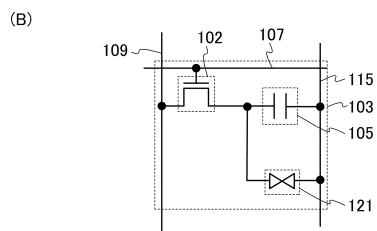

【図5】表示装置の一形態を説明するブロック図及び回路図である。

【図6】表示装置の一形態を説明する上面図である。

【図7】表示装置の一形態を説明する断面図である。

【図8】表示装置の一形態を説明する断面図である。

【図9】表示装置の一形態を説明する断面図である。

【図10】表示装置の作製方法の一形態を説明する断面図である。

【図11】表示装置の作製方法の一形態を説明する断面図である。

【図12】表示装置の作製方法の一形態を説明する断面図である。

40

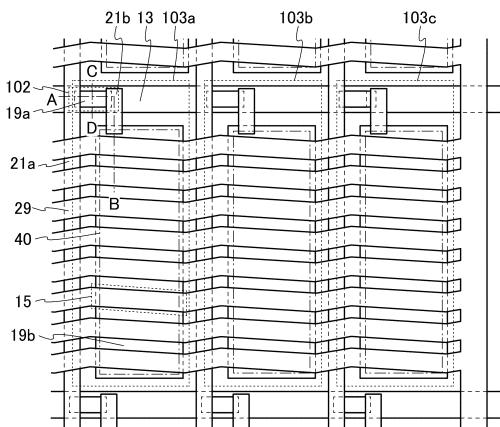

【図13】表示装置の一形態を説明する上面図及び断面図である。

【図14】表示装置の一形態を説明する上面図である。

【図15】表示装置の一形態を説明する上面図である。

【図16】表示装置の一形態を説明する断面図である。

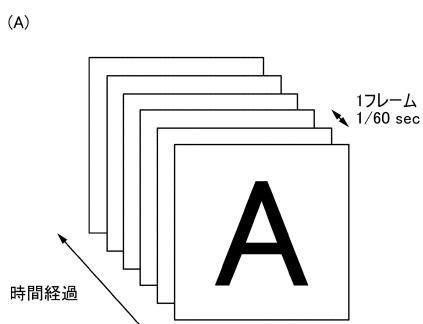

【図17】表示装置の駆動方法の一例を示す概念図である。

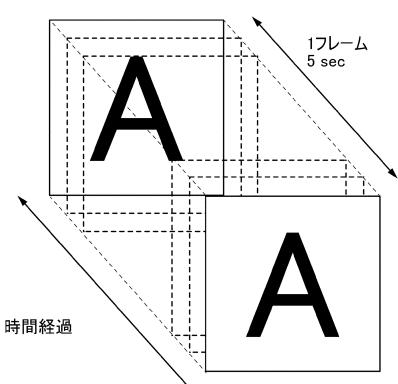

【図18】表示モジュールを説明する図である。

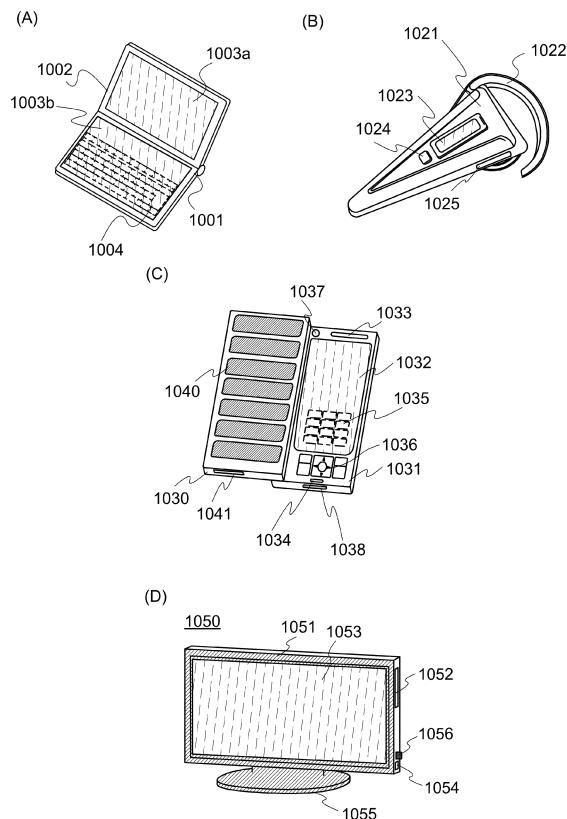

【図19】実施の形態に係る、電子機器の外観図を説明する図である。

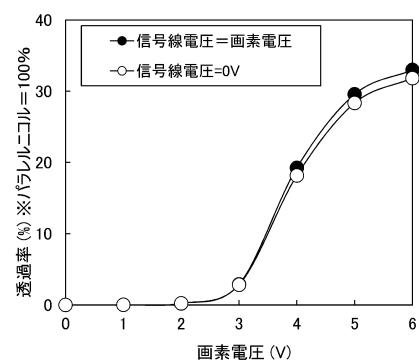

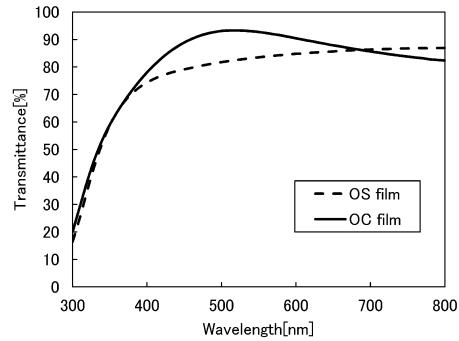

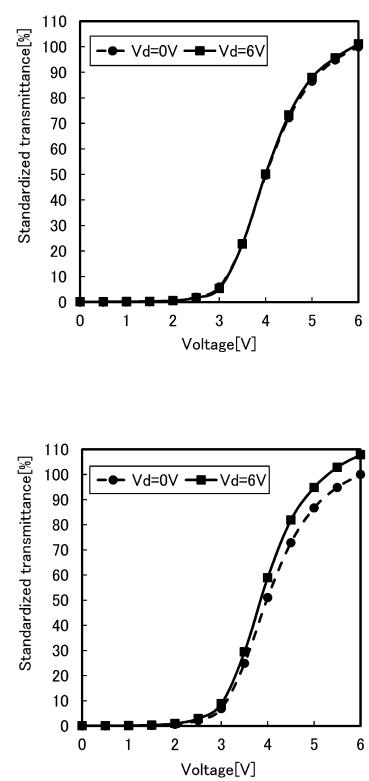

【図20】試料1及び試料2の透過率を示す図である。

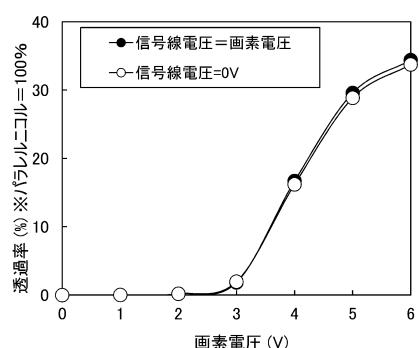

【図21】試料3の透過率を示す図である。

【図22】表示装置の一形態を説明する断面図である。

50

- 【図23】表示装置の一形態を説明する断面図である。

【図24】表示装置の一形態を説明する上面図である。

【図25】表示装置の一形態を説明する上面図である。

【図26】表示装置の一形態を説明する断面図である。

【図27】表示装置の作製方法の一形態を説明する断面図である。

【図28】表示装置の一形態を説明する上面図である。

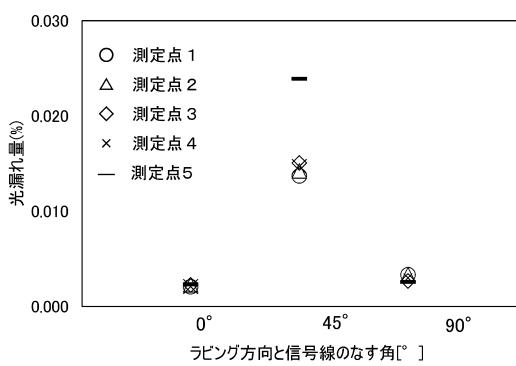

【図29】素子基板におけるラビング角度と光漏れの関係を説明する図である。

- 【図30】液晶表示装置の表示部を観察した結果を説明する図である。

【図31】計算に用いた画素の形状を説明する上面図及び計算結果を説明する図である。

【図32】計算に用いた画素の形状を説明する上面図及び計算結果を説明する図である。 10

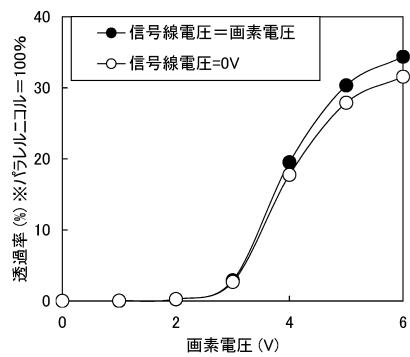

【図33】電圧 - 透過率特性を説明する図である。

- 【図34】液晶表示装置が表示した画像を撮影した図である。

【図35】透過率を測定した結果を説明する図である。

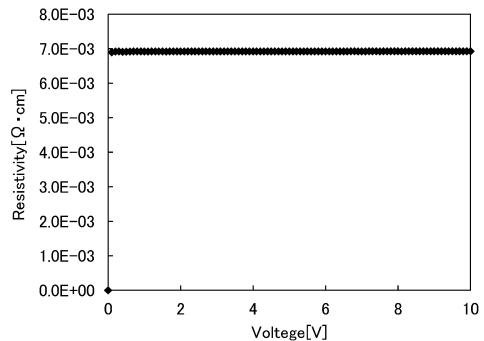

【図36】導電率を測定した結果を説明する図である。

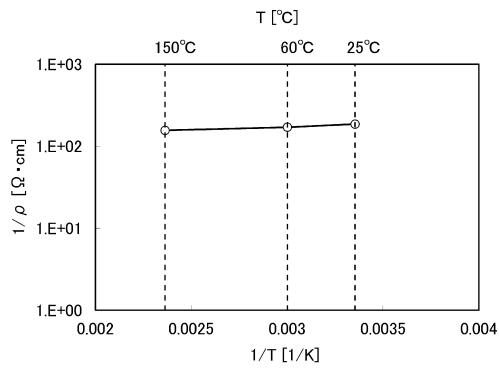

【図37】抵抗率を測定した結果を説明する図である。

【図38】導電率の温度依存性を説明する図。

- 【図39】酸化物導電体膜の形成モデルを説明する図である。

【図40】電圧 - 透過率特性の計算結果を説明する図である。

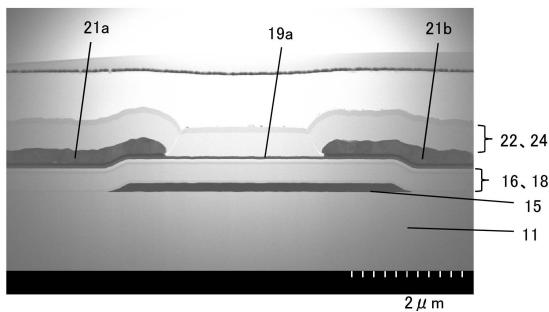

【図41】トランジスタの断面S T E M像を説明する図である。

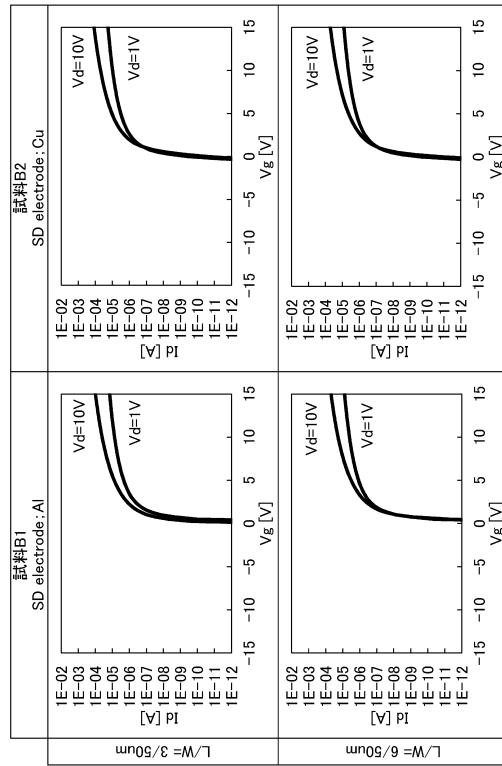

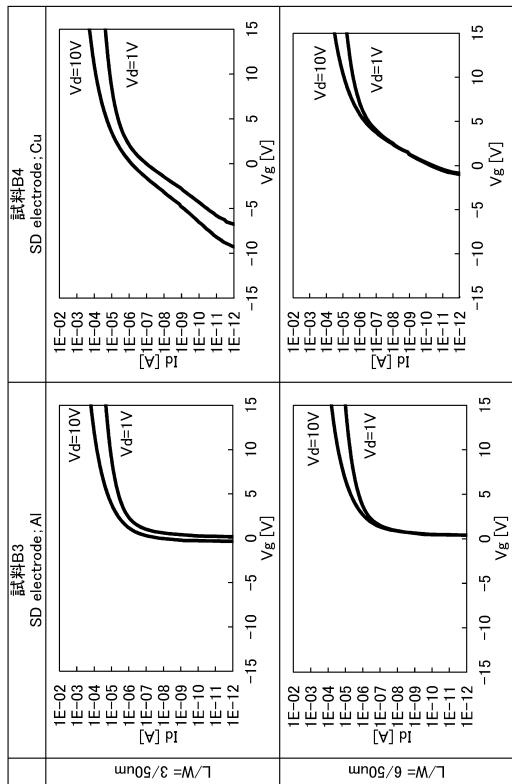

【図42】トランジスタの電気特性を説明する図である。 20

【図43】トランジスタの電気特性を説明する図である。

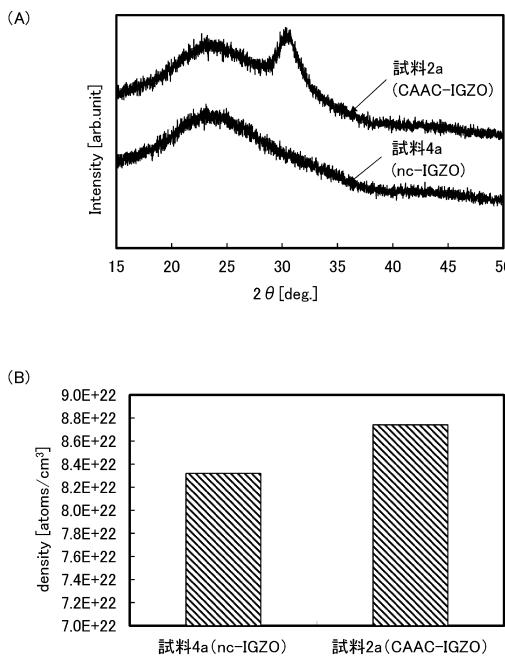

【図44】IGZO膜のXRD及びXRRの測定結果を説明する図である。

**【発明を実施するための形態】**

**【0023】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態及び実施例において、同一部分または同様の機能を有する部分には、同一の符号または同一のハッチパターンを異なる図面間で共通して用い、その繰り返しの説明は省略する。 30

**【0024】**

なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

**【0025】**

また、本明細書にて用いる第1、第2、第3などの用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。

**【0026】**

また、「ソース」や「ドレイン」の機能は、回路動作において電流の方向が変化する場合には入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

**【0027】**

また、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。ただし、一般的に、ある一点における電位と基準となる電位（例えば接地電位）との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、電圧を電位と読み替えてよいこととする。 50

**【0028】**

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

**【0029】****(実施の形態1)**

本実施の形態では、本発明の一態様である表示装置について、図面を用いて説明する。

10

**【0030】**

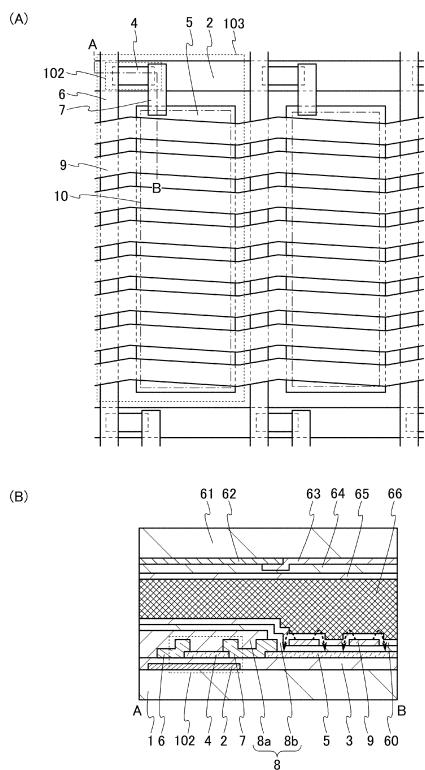

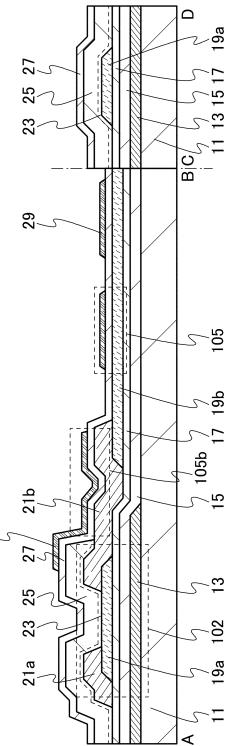

図1(A)は、FFSモードの液晶表示装置に含まれる表示部の一画素103の上面図であり、図1(B)は図1(A)の一点鎖線A-Bの断面図である。また、図1(A)において、基板1、絶縁膜3、絶縁膜8、絶縁膜60、基板61、遮光膜62、着色膜63、絶縁膜64、絶縁膜65、及び液晶層66を省略する。

**【0031】**

図1に示すように、FFSモードの液晶表示装置は、アクティブマトリクス型の液晶表示装置であり、表示部に設けられる画素103ごとにトランジスタ102及び画素電極5を有する。

**【0032】**

20

図1(B)に示すように、液晶表示装置は、基板1上のトランジスタ102と、トランジスタ102に接続される画素電極5と、トランジスタ102及び画素電極5に接する絶縁膜8と、絶縁膜8に接するコモン電極9と、絶縁膜8及びコモン電極9に接し、且つ配向膜として機能する絶縁膜60と、を有する。

**【0033】**

また、基板61に接する遮光膜62及び着色膜63と、基板61、遮光膜62、及び着色膜63に接する絶縁膜64と、絶縁膜64に接し、且つ配向膜として機能する絶縁膜65とを有する。また、絶縁膜60及び絶縁膜65の間に液晶層66を有する。なお、図示しないが、基板1及び基板61の外側に偏光板が設けられる。

**【0034】**

30

トランジスタ102は、順スタガ型、逆スタガ型、コブレナー型等のトランジスタを適宜用いることができる。また、トランジスタ102は、半導体膜をゲート絶縁膜及びゲート電極でコの字型に囲うFin型のトランジスタを用いることができる。また、逆スタガ型の場合、チャネルエッチ構造、チャネル保護構造等を適宜用いることができる。

**【0035】**

本実施の形態に示すトランジスタ102は、逆スタガ型であり、且つチャネルエッチ構造のトランジスタである。トランジスタ102は、基板1上の、ゲート電極として機能する導電膜2と、基板1及び導電膜2上のゲート絶縁膜として機能する絶縁膜3と、絶縁膜3を介して導電膜2と重なる半導体膜4と、半導体膜4と接する導電膜6及び導電膜7と、を有する。なお、導電膜2は、ゲート電極と共に、走査線として機能する導電膜として機能する。即ち、ゲート電極は走査線の一部である。また、導電膜6は、ソース電極極及びドレイン電極の一方と共に、信号線として機能する導電膜として機能する。即ち、ソース電極及びドレイン電極の一方は、信号線の一部である。また、導電膜7はソース電極及びドレイン電極の他方として機能する。これらのため、トランジスタ102は、走査線として機能する導電膜2及び信号線として機能する導電膜6と電気的に接続される。なお、ここでは、導電膜2は、ゲート電極と共に走査線として機能するが、ゲート電極及び走査線を、別々に形成してもよい。また、導電膜6は、ソース電極及びドレイン電極の一方、並びに信号線として機能するが、ソース電極及びドレイン電極の一方、並びに信号線を、別々に形成してもよい。

40

**【0036】**

50

なお、トランジスタ102において、半導体膜4は、シリコン、シリコンゲルマニウム、酸化物半導体等の半導体材料を適宜用いることができる。また、半導体膜4は適宜、非晶質構造、微結晶構造、多結晶構造、単結晶構造等とすることができます。

#### 【0037】

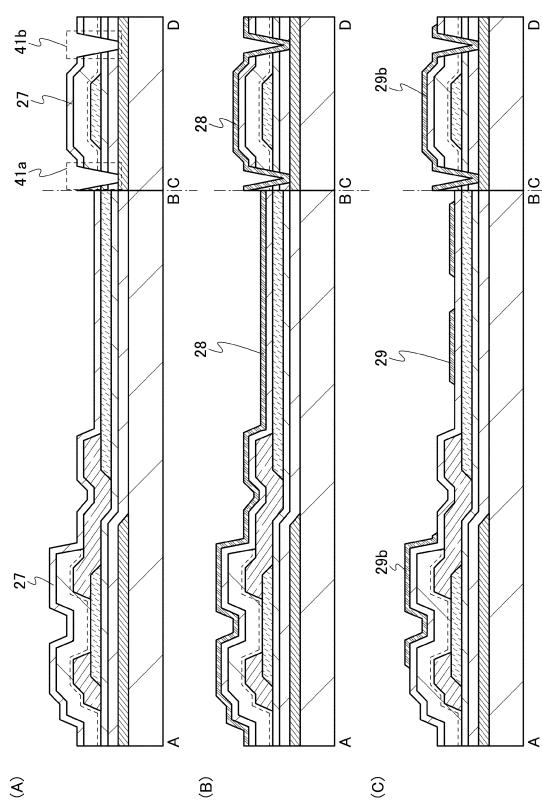

また、ゲート絶縁膜として機能する絶縁膜3上に画素電極5を有する。画素電極は、導電膜7と接続される。すなわち、画素電極5はトランジスタ102と電気的に接続される。

#### 【0038】

図1(A)に示すように、画素電極5は、画素103において、矩形状である。また、本実施の形態に示す表示装置は、アクティブマトリクス型の液晶表示装置であるため、画素電極5がマトリクス状に配置される。画素電極5及びコモン電極9は透光性を有する膜で形成される。

10

#### 【0039】

なお、画素電極5の形状は、矩形状に限定されず、画素103の形状に合わせて適切な形状とすることができます。なお、画素電極5は、画素103において、走査線として機能する導電膜2及び信号線として機能する導電膜6に囲まれる領域において、広く形成されることが好ましい。この結果、画素103における開口率を高めることができる。

#### 【0040】

トランジスタ102及び画素電極5上に絶縁膜8を有する。ここでは、絶縁膜8として、トランジスタ102を覆い、且つ画素電極5の一部を露出する開口部(図1(A)に示す一点鎖線10)を有する絶縁膜8aと、絶縁膜8a及び画素電極5上の絶縁膜8bとを示す。なお、絶縁膜8として、絶縁膜8a及び絶縁膜8bの代わりに、絶縁膜8bのみを設けてもよく、または平坦性を有する絶縁膜を設けてもよい。

20

#### 【0041】

コモン電極9の上面形状は、ジグザグ状であってもよい。また、コモン電極9において、ジグザグ状の繰り返し単位が繰り返す方向をコモン電極9の延伸方向とすると、信号線として機能する導電膜6の延伸方向とコモン電極9の延伸方向が交差する。

#### 【0042】

また、コモン電極9の上面形状は、波状であってもよい。また、コモン電極9において、波状の繰り返し単位が繰り返す方向をコモン電極9の延伸方向とすると、信号線として機能する導電膜6の延伸方向とコモン電極9の延伸方向が交差する。

30

#### 【0043】

コモン電極9の延伸方向及び信号線として機能する導電膜6の延伸方向が交差する角度は、45°以上135°以下が好ましい。上記範囲の角度で交差することで、ちらつきを低減することが可能である。

#### 【0044】

また、一つの画素において、コモン電極9が縞状である。画素電極5に電圧が印加されると、画素電極5及びコモン電極9の間ににおいて、図1(B)の破線矢印で示すように、放物線状の電界が発生する。この結果、液晶層66に含まれる液晶分子を配向させることができる。

40

#### 【0045】

また、m行n列の画素に設けられる画素電極は、n列目の信号線として機能する導電膜、及びn+1列目の信号線として機能する導電膜の間に配置する。該画素電極及びn列目の信号線として機能する導電膜の間、並びに該画素電極及びn+1列目の信号線として機能する導電膜の間、それぞれにおいてコモン電極9の屈曲点を有することが好ましい。この結果、コモン電極9が、各列における信号線として機能する導電膜6と交差する方向が、平行または略平行となる。また、各画素において、コモン電極9が、画素電極5と交差する方向が、平行または略平行となる。この結果、各画素におけるコモン電極9の形状が同じ形状または略同じ形状となるため、画素ごとにおける液晶分子の配向むらを低減することができる。

50

## 【0046】

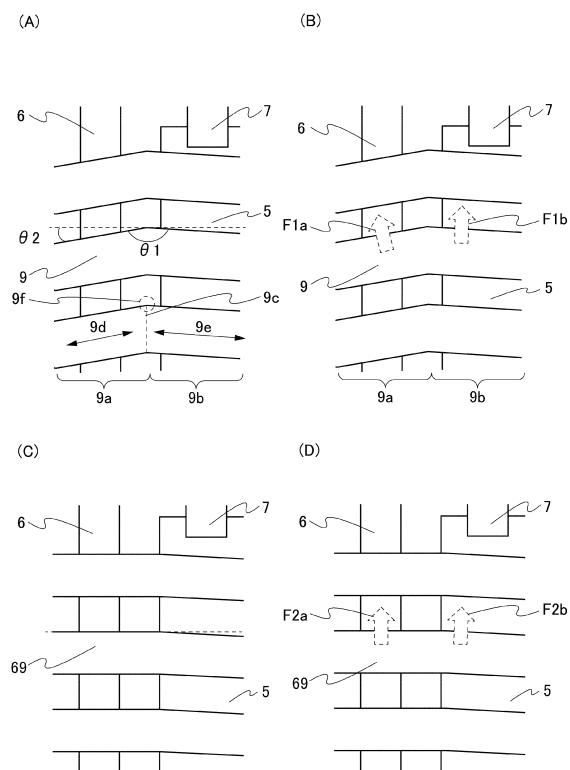

ここで、コモン電極9の平面形状の詳細について、図2(A)を用いて説明する。図2は、信号線として機能する導電膜6及び画素電極5の近傍における上面拡大図である。

## 【0047】

コモン電極9は、第1の領域9a及び第2の領域9bを有する。一つの画素において第1の領域9a及び第2の領域9bはそれぞれ複数設けられる。また、一つの画素において複数の第1の領域9aは平行または略平行である。また、一つの画素において複数の第2の領域9bは平行または略平行である。コモン電極9は、第1の領域9a及び第2の領域9bが接続部9cで接続している。第1の領域9aの一部が、信号線として機能する導電膜6と重なり、第2の領域9bの一部が画素電極5と重なる。また、平面形状において、接続部9cが信号線として機能する導電膜6と画素電極5との間に位置する。なお、接続部9cは、画素電極5の端部及び信号線として機能する導電膜6の端部の一以上と重なってもよい。また、第1の領域9a及び第2の領域9bが、信号線として機能する導電膜6と交差する方向に交互に配置されている。

## 【0048】

また、第1の領域9aは第1の方向9dに延伸し、第2の領域9bは第2の方向9eに延伸する。第1の方向9d及び第2の方向9eは異なる方向であり、交差する。

## 【0049】

また、コモン電極9は、平面形状において、屈曲点9fが信号線として機能する導電膜6と画素電極5の間に位置する。なお、屈曲点9fは、画素電極5の端部及び信号線として機能する導電膜6の端部の一以上と重なってもよい。

## 【0050】

第1の領域9a及び第2の領域9bがなす角度、すなわち第1の方向9d及び第2の方向9eのなす角度、さらに言い換えると屈曲点9fの角度1は、90°より大きく180°未満、好ましく135°より大きく180°未満である。

## 【0051】

また、第1の領域9aと信号線として機能する導電膜6の垂線(図2(A))において破線で示す。)とのなす角度、すなわち第1の領域9aの延伸方向と信号線として機能する導電膜6の垂線とのなす角度、さらに言い換えると、屈曲点9fでの第1の領域9aと信号線として機能する導電膜6の垂線とのなす角度2は、0°より大きく90°未満、好ましくは0°より大きく45°未満である。

## 【0052】

角度1及び2を上記範囲とすることで、第1の領域9aに設けられる液晶分子と、第2の領域9bに設けられる液晶分子のそれぞれの電圧印加時の配向方向を異ならせることが可能である。配向方向が異なることで、配線電位により生じた第1の領域9aの配向状態と、第2の領域9bに生じた配向状態が影響しにくくなる。即ち、第2の領域9bに生じた配向状態は、配線電位により生じた第1の領域9aの配向状態の影響を受けにくい。従って信号線として機能する導電膜6及びコモン電極9の間で発生する電界の影響を、画素電極5が受けにくくすることが可能であり、ちらつきの抑制効果が得られる。

## 【0053】

コモン電極9を縞状とし、且つ角度2を上記範囲とすることで、信号線として機能する導電膜6と交差する方向に、コモン電極9が延伸する。よって、信号線として機能する導電膜6と重なる面積が低減され、コモン電極9と導電膜7との間の寄生容量を低減することができる。また、2を45°以上とすると、コモン電極9の幅が狭くなり、コモン電極9の抵抗が高まるため、2は45°未満であるとより好ましい。

## 【0054】

また、角度1及び角度2の和は135°以上180°未満である。

## 【0055】

角度1及び角度2の和を上記範囲とすることで、コモン電極9の第1の領域9aは、各列における信号線として機能する導電膜6と交差する方向が平行または略平行となる

10

20

30

40

50

。また、各画素において、コモン電極 9 の第 2 の領域 9 b は、画素電極 5 と交差する方向が平行または略平行となる。この結果、各画素におけるコモン電極 9 の形状が同じ形状となるため、画素ごとにおける液晶分子の配向むらを低減することができる。

#### 【 0 0 5 6 】

なお、画素電極 5 及びコモン電極 9 が重なる領域において、画素電極 5 、絶縁膜 8 b 、及びコモン電極 9 が容量素子として機能する。画素電極 5 及びコモン電極 9 は透光性を有する膜で形成されるため、開口率が高まるとともに、容量素子に蓄積される電荷容量を高めることができる。また、画素電極 5 及びコモン電極 9 の間の絶縁膜 8 b を比誘電率の高い材料を用いて形成することで、容量素子において、大きな電荷容量を蓄積させることができある。比誘電率の高い材料としては、窒化シリコン、酸化アルミニウム、酸化ガリウム、酸化イットリウム、酸化ハフニウム、ハフニウムシリケート ( $HfSiO_x$ ) 、窒素が添加されたハフニウムシリケート ( $HfSi_xO_yN_z$ ) 、窒素が添加されたハフニウムアルミネート ( $HfAl_xO_yN_z$ ) 等がある。10

#### 【 0 0 5 7 】

遮光膜 6 2 は、ブラックマトリクスとして機能する。着色膜 6 3 は、カラーフィルタとして機能する。なお、着色膜 6 3 は、必ずしも設ける必要はなく、例えば、液晶表示装置が白黒表示の場合は、着色膜 6 3 を設けない構成としてもよい。

#### 【 0 0 5 8 】

着色膜 6 3 としては、特定の波長帯域の光を透過する着色膜であればよく、例えば、赤色の波長帯域の光を透過する赤色 (R) の膜、緑色の波長帯域の光を透過する緑色 (G) の膜、青色の波長帯域の光を透過する青色 (B) の膜などを用いることができる。20

#### 【 0 0 5 9 】

遮光膜 6 2 としては、特定の波長帯域の光を遮光する機能を有していればよく、金属膜または黒色顔料等を含んだ有機絶縁膜などを用いることができる。

#### 【 0 0 6 0 】

絶縁膜 6 5 は、平坦化層としての機能、または着色膜 6 3 が含有しうる不純物を液晶素子側へ拡散するのを抑制する機能を有する。

#### 【 0 0 6 1 】

なお、図示しないが、基板 1 及び基板 6 1 の間には、シール材が設けられており、基板 1 、基板 6 1 、及びシール材により液晶層 6 6 を封止している。また、絶縁膜 6 0 及び絶縁膜 6 4 の間に液晶層 6 6 の厚さ (セルギャップともいう) を維持するスペーサを設けてもよい。30

#### 【 0 0 6 2 】

次に、本実施の形態に示す液晶表示装置の駆動方法について、図 2 を用いて説明する。

#### 【 0 0 6 3 】

各画素において、初期状態を黒表示とし、画素電極に電圧を印加することで白表示とする画素における表示素子の駆動方法、すなわちノーマリー・ブラックモードの表示素子の駆動方法について説明する。なお、ここで、表示素子とは、画素電極 5 、コモン電極 9 、及び液晶層 6 6 に含まれる液晶分子のことをいう。なお、本実施の形態では、ノーマリー・ブラックモードの駆動方法を用いて説明するが、適宜ノーマリー・ホワイトモードの駆動方法を用いることもできる。40

#### 【 0 0 6 4 】

なお、黒表示の場合は、トランジスタをオン状態とする電圧を走査線として機能する導電膜に印加し、信号線として機能する導電膜及びコモン電極に 0 V 印加する。この結果、画素電極に 0 V 印加される。すなわち、画素電極及びコモン電極の間に電界が発生せず、液晶分子は動作しない。

#### 【 0 0 6 5 】

白表示の場合は、トランジスタをオン状態とする電圧を走査線として機能する導電膜に印加し、信号線として機能する導電膜に液晶分子を動作させる電圧、たとえば 6 V 印加し、コモン電極に 0 V 印加する。この結果、画素電極に 6 V 印加される。すなわち、画素電50

極及びコモン電極の間に電界が発生し、液晶分子が動作する。

#### 【0066】

また、ここでは、ネガ型の液晶材料を用いて説明するため、初期状態において、液晶分子は信号線として機能する導電膜と平行または略平行な方向に配向させる。このように、初期状態における液晶分子の配向を初期配向という。また、画素電極及びコモン電極間に電圧を印加することで、基板に対して平行な面内において、液晶分子を回転動作させる。なお、本実施の形態では、ネガ型の液晶材料を用いて説明するが、適宜ポジ型の液晶材料を用いることもできる。

#### 【0067】

また、図1(B)に示す基板1及び基板61の外側に偏光板が設けられる。基板1の外側に設けられる偏光板に含まれる偏光子と、基板61の外側に設けられる偏光板に含まれる偏光子が互いに直交するように配置されたクロスニコルである。このため、走査線として機能する導電膜2及び信号線として機能する導電膜6と平行な方向に、液晶分子が配向すると、偏光板において光が吸収され、黒表示となる。なお、本実施の形態では、クロスニコルの偏光板を用いて説明するが、適宜パラレルニコルの偏光板を用いることもできる。

10

#### 【0068】

ここで、画素電極5及びコモン電極9に異なる電圧を印加した場合、信号線として機能する導電膜6とコモン電極9との間、及び画素電極5とコモン電極9との間に生じる電界について説明する。コモン電極9の第1の領域9aにおいては、信号線として機能する導電膜6とコモン電極9との間に、図2(B)の破線矢印に示す電界F1aが発生し、コモン電極9の第2の領域9bにおいては、画素電極5とコモン電極9との間に、破線矢印に示す電界F1bが発生する。

20

#### 【0069】

電界F1a及び電界F1bの方位が異なる。すなわち、第1の領域9a及び第2の領域9bにおいて電界方位のずれが生じ、さらに、該電界方位のずれが大きい。この結果、第1の領域9aにおける液晶分子の配向と、第2の領域9bにおける液晶分子の配向は、互いに影響されにくい。

#### 【0070】

一般に、リフレッシュレートが低い液晶表示装置において、保持期間及びリフレッシュ期間を有する。ここでは、図2(D)を用いて説明する。保持期間は、信号線として機能する導電膜6に0Vまたは任意の固定の電位を印加し、画素電極5の電位を保持する期間である。リフレッシュ期間は、信号線として機能する導電膜6に書き込み電圧を印加し、画素電極5の電位を書き換える(リフレッシュする)期間である。このようにリフレッシュ期間と保持期間では、信号線として機能する導電膜6にそれぞれ異なる電圧が印加される。従って、信号線として機能する導電膜6近傍の液晶分子の配向は、リフレッシュ期間と保持期間において異なる。このため、隣接する画素に設けられた画素電極5とコモン電極9との間で生じる電界により発生した第2の領域9bの液晶分子の配向状態は、リフレッシュ期間と保持期間において、信号線として機能する導電膜6近傍の液晶分子から、異なる影響を受ける。この結果、画素の透過率が変化し、ちらつきが生じる。

30

#### 【0071】

しかしながら、本実施の形態に示す形状のコモン電極を用いることで、図2(B)に示すように、第1の領域9a及び第2の領域9bにおいて電界方位のずれが生じるため、信号線として機能する導電膜6近傍の液晶分子の配向状態と、隣接する画素に設けられた画素電極5とコモン電極9との間で生じる電界により生じた画素電極5近傍の液晶分子の配向状態は、互いに影響されにくい。この結果、画素の透過率の変化が抑制される。この結果、画像のちらつきを低減することが可能である。

40

#### 【0072】

ここで、比較例として、図2(C)に、コモン電極69において、信号線として機能する導電膜6と重なる領域では、導電膜7の垂線(図2(C)において破線で示す。)と平

50

行に延伸する例を示す。また、コモン電極 6 9において、画素電極 5 と重なる領域は導電膜 7 の垂線と所定の角度を有する。なお、コモン電極 6 9において、画素電極 5 と重なる領域は導電膜 7 の垂線と平行であってもよい。

#### 【0073】

ここで、図 2 (C) に示す画素電極 5 及びコモン電極 6 9 に異なる電圧を印加した場合、画素電極 5 及びコモン電極 6 9 の間に生じる電界について、図 2 (D) を用いて説明する。コモン電極 6 9において、信号線として機能する導電膜 6 と重なる領域では、信号線として機能する導電膜 6 とコモン電極 6 9 の間に、図 2 (D) の破線矢印に示す電界 F 2 a が発生し、画素電極 5 と重なる領域では、画素電極 5 とコモン電極 6 9 の間に、破線矢印に示す電界 F 2 b が発生する。

10

#### 【0074】

電界 F 2 a 及び電界 F 2 b の方位が異なるが、該電界方位のずれが小さい。この結果、信号線として機能する導電膜 6 と重なる領域における液晶分子は、信号線として機能する導電膜及び隣接する画素の画素電極の電圧の影響を受けやすく、また、モノドメインとなってしまう。この結果、画像のちらつきが発生してしまう。特に、信号線とコモン電極が垂直に交差する場合、液晶分子の回転方向が規定されないため、画素電極近傍の液晶分子との配向状態は、信号線として機能する導電膜 6 近傍の液晶分子の影響を受けやすく、ちらつきを生じやすい。

#### 【0075】

以上のことから、本実施の形態に示すコモン電極 9 のようにジグザグ状のコモン電極を有する表示装置は、ちらつきが少なく、表示品質の優れた表示装置である。

20

#### 【0076】

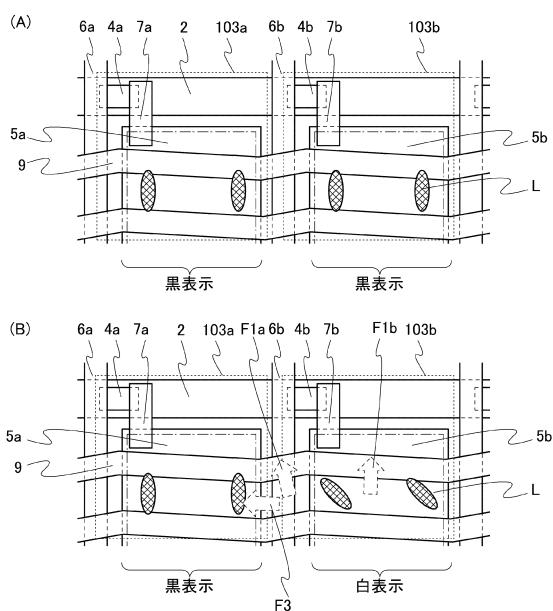

次に、コモン電極 9 が縞状であることの効果について、図 3 を用いて説明する。

#### 【0077】

図 3 は、FFS モードの液晶表示装置の画素部に含まれる画素の上面図であり、隣り合う 2 つの画素 103a、103b を示す。

#### 【0078】

画素 103a は、走査線として機能する導電膜 2、半導体膜 4a、信号線として機能する導電膜 6a、導電膜 7a、画素電極 5a 及びコモン電極 9 を有する。画素 103b は、走査線として機能する導電膜 2、半導体膜 4b、信号線として機能する導電膜 6b、導電膜 7b、画素電極 5b 及びコモン電極 9 を有する。

30

#### 【0079】

図 3 において、コモン電極 9 の上面形状は、ジグザグ状であり、且つ信号線として機能する導電膜 6a、6b と交差する方向に延伸している。すなわち、画素 103a、103b にまたがっている。

#### 【0080】

また、図 3 (A) は初期状態（黒表示）を示し、図 3 (B) は駆動状態を示す。

#### 【0081】

図 3 (A) 及び図 3 (B) に示す画素 103a、103b は、コモン電極 9 が信号線として機能する導電膜 6a、6b と交差する方向に延伸するため、初期状態（黒表示）では、液晶分子 L は、信号線として機能する導電膜 6a、6b と平行または略平行な方向に配向する。

40

#### 【0082】

次に、図 3 (B) に示すように、画素 103a を黒表示、画素 103b を白表示とする場合について説明する。信号線として機能する導電膜 6a 及びコモン電極 9 に 0V 印加する。また、信号線として機能する導電膜 6b に 6V 印加する。この結果、画素 103b において、画素電極 5b に 6V 印加され、信号線として機能する導電膜 6b とコモン電極 9 の間に図 3 (B) の破線矢印に示す電界 F 1a が発生し、画素電極 5 とコモン電極 9 の間に破線矢印に示す電界 F 1b が発生する。また、該電界に合わせて液晶分子 L が配向する。ここでは、液晶分子 L が 45° 回転した状態を示す。

50

## 【0083】

なお、画素 103a において、画素電極 5a が 0V であり、画素電極 5a の近傍に設けられる信号線として機能する導電膜 6b が 6V である。しかしながら、信号線として機能する導電膜 6b 及びコモン電極 9 が交差するため、画素電極 5a 及び信号線として機能する導電膜 6b の間に電界 F3 が生じる。電界 F3 は、液晶分子の初期配向と略垂直な方向である。ここでは、ネガ型液晶材料を用いているため、電界 F3 が発生しても液晶分子 L が動作しにくく、チラツキを抑制することができる。

## 【0084】

以上のことから、本実施の形態に示すコモン電極を有する液晶表示装置において、信号線として機能する導電膜とコモン電極との間で生じる電界と、画素電極とコモン電極との間で生じる電界との間で、方位ずれが生じ、且つそのずれの角度が大きい。このため、信号線として機能する導電膜の近傍に設けられた液晶分子は、隣接する画素の画素電極及び信号線として機能する導電膜の電圧の影響を受けにくく、液晶分子の配向乱れを低減することができる。

## 【0085】

また、リフレッシュレートが低い液晶表示装置において、保持期間であっても、信号線として機能する導電膜 6 近傍の液晶分子の配向は、隣接する画素に設けられた画素電極とコモン電極との間で生じる電界の影響を受けにくい。この結果、保持期間において、画素の透過率を維持することが可能であり、ちらつきを低減することができる。

## 【0086】

また、信号線として機能する導電膜と交差する方向に延伸したコモン電極を設けることで、光漏れが少なく、液晶表示装置のコントラストを高めることができる。

## 【0087】

また、本実施の形態に示すコモン電極は、基板上において全面に形成されない。このため、信号線として機能する導電膜と重なる領域を減らすことが可能であり、信号線として機能する導電膜とコモン電極の間に発生する寄生容量を低減することが可能である。この結果、大面積基板を用いて形成される表示装置において、配線遅延を低減することが可能である。

## 【0088】

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

## 【0089】

## &lt;変形例 1 &gt;

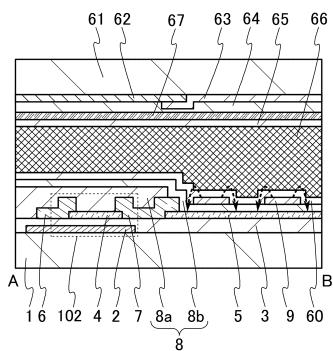

図 1 に示す液晶表示装置の変形例について、図 4 を用いて説明する。図 4 に示す液晶表示装置は、基板 61 において、導電膜 67 を有することを特徴とする。具体的には、絶縁膜 64 及び絶縁膜 65 の間に導電膜 67 を有する。

## 【0090】

導電膜 67 は、透光性を有する導電膜を用いて形成する。また、導電膜 67 は、コモン電極 9 と同電位とすることが好ましい。すなわち、導電膜 67 は共通電位が印加されることが好ましい。

## 【0091】

導電膜 6 に液晶分子を駆動する電圧が印加された場合、導電膜 6 とコモン電極 9 の間に電界が発生してしまう。該電界は縦電界である。FFS モードでは、横電界により基板平行方向において液晶分子が配向する。しかしながら、縦電界が生じると、この電界の影響を受け、導電膜 6 とコモン電極 9 の間の液晶分子が、基板垂直方向に配向してしまい、ちらつきが生じる。

## 【0092】

しかしながら、液晶層 66 を介してコモン電極 9 と対向する側に導電膜 67 を設け、コモン電極 9 及び導電膜 67 を同電位とすることで、導電膜 6 とコモン電極 9 の間における電界による液晶分子の、基板垂直方向の配向変化を抑制することが可能であり、該領域に

10

20

30

40

50

おける液晶分子の配向状態が安定する。この結果、ちらつきを低減できる。

**【0093】**

<変形例2>

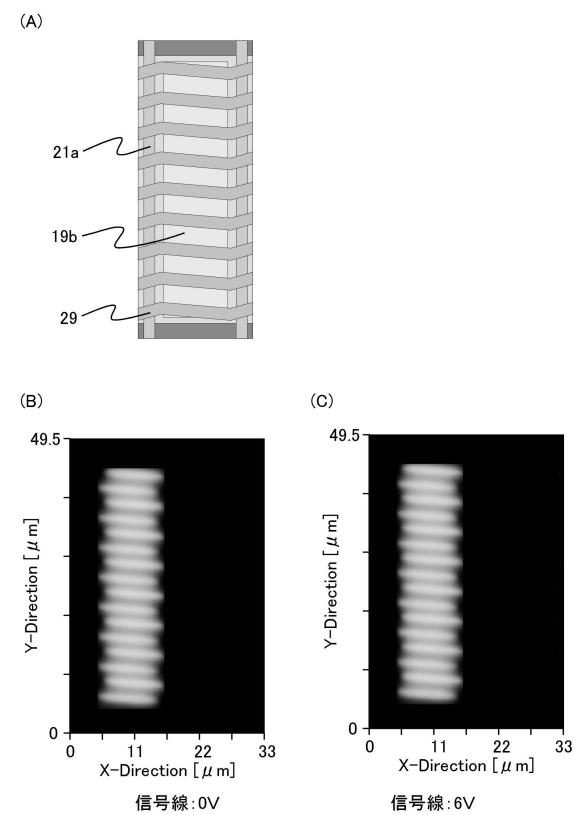

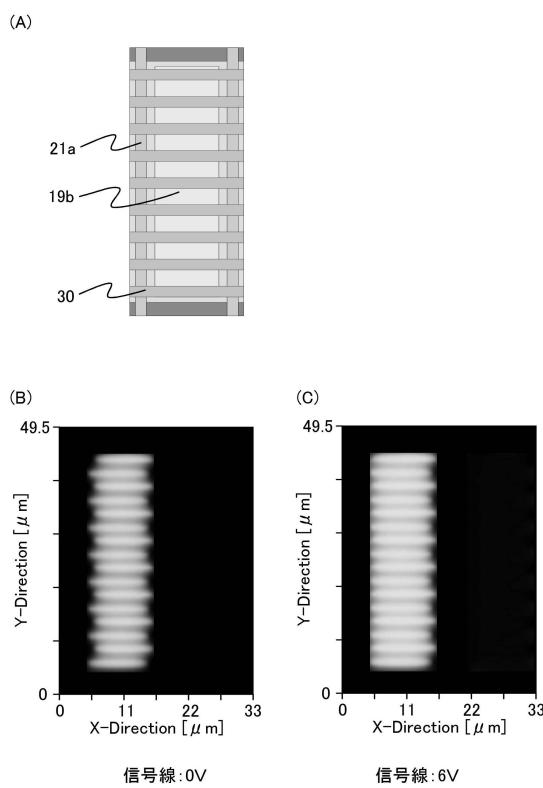

図6に示すコモン電極29は、第1の領域と第2の領域が接続している。第1の領域は、縞状であり、ジグザグ状に屈曲しており、信号線として機能する導電膜21aの延伸方向と交差する領域である。第2の領域は、信号線として機能する導電膜21aと平行または略平行な方向に延伸している領域である。図6に示すコモン電極29は、信号線として機能する導電膜21aと重ならないため、コモン電極29の寄生容量を低減することができる。

**【0094】**

10

しかしながら、第2の領域は、表示領域として寄与しない。このため、画素103a、103b、103cの面積が狭くなり、開口率が低減する。

**【0095】**

そこで、図28に示すコモン電極29のように、第1の領域と接続される第2の領域を信号線として機能する導電膜21a上に設けることで、画素103d、103e、103fの面積を広くすることができる。なお、第2の領域は、信号線として機能する導電膜21aと平行または略平行な方向に延伸せず、導電膜21aの一部と重なる。よって、信号線として機能する導電膜21aとコモン電極29との間に発生する寄生容量を低減しつつ、画素の面積及び画素の開口率を低減することができる。なお、図28に示す画素において、開口率を50%以上、一例としては50.8%とすることができる。

20

**【0096】**

なお、図28に示すコモン電極29において、第2の領域は、規則的に第1の領域と結合しているが、ランダムに第1の領域と結合してもよい。

**【0097】**

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

**【0098】**

(実施の形態2)

本実施の形態では、本発明の一態様である表示装置について、図面を用いて説明する。また、本実施の形態では、トランジスタに含まれる半導体膜として酸化物半導体膜を用いて説明する。

30

**【0099】**

図5(A)に示す表示装置は、画素部101と、走査線駆動回路104と、信号線駆動回路106と、各々が平行または略平行に配設され、且つ走査線駆動回路104によって電位が制御されるm本の走査線として機能する導電膜107と、各々が平行または略平行に配設され、且つ信号線駆動回路106によって電位が制御されるn本の信号線として機能する導電膜109と、を有する。さらに、画素部101はマトリクス状に配設された複数の画素103を有する。また、信号線として機能する導電膜109に沿って、各々が平行または略平行に配設されたコモン線115を有する。また、走査線駆動回路104及び信号線駆動回路106をまとめて駆動回路部という場合がある。

40

**【0100】**

各走査線として機能する導電膜107は、画素部101においてm行n列に配設された画素103のうち、いずれかの行に配設されたn個の画素103と電気的に接続される。また、各信号線として機能する導電膜109は、m行n列に配設された画素103のうち、いずれかの列に配設されたm個の画素103に電気的に接続される。m、nは、ともに1以上の整数である。また、各コモン線115は、m行n列に配設された画素103のうち、いずれかの列に配設されたm個の画素103と電気的に接続される。

**【0101】**

図5(B)は、図5(A)に示す表示装置の画素103に用いることができる回路構成の一例を示している。

50

**【 0 1 0 2 】**

図5(B)に示す画素103は、液晶素子121と、トランジスタ102と、容量素子105と、を有する。

**【 0 1 0 3 】**

液晶素子121の一対の電極の一方は、トランジスタ102と接続し、電位は、画素103の仕様に応じて適宜設定される。液晶素子121の一対の電極の他方は、コモン線115と接続し、電位は共通の電位(コモン電位)が与えられる。液晶素子121は、トランジスタ102に書き込まれるデータにより、液晶分子の配向状態が制御される。

**【 0 1 0 4 】**

なお、液晶素子121は、液晶分子の光学的変調作用によって光の透過または非透過を制御する素子である。なお、液晶分子の光学的変調作用は、液晶分子にかかる電界(横方向の電界、縦方向の電界又は斜め方向の電界を含む)によって制御される。なお、液晶素子121としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、サーモトロピック液晶、ライオトロピック液晶、強誘電液晶、反強誘電液晶等が挙げられる。

10

**【 0 1 0 5 】**

液晶素子121を有する表示装置の駆動方法としては、FFSモードを用いる。

**【 0 1 0 6 】**

また、ブルー相(Blue Phase)を示す液晶材料とカイラル剤とを含む液晶組成物により液晶素子を構成してもよい。ブルー相を示す液晶は、応答速度が1 msec以下と短く、光学的等方性であるため、配向処理が不要であり、かつ視野角依存性が小さい。

20

**【 0 1 0 7 】**

図5(B)に示す画素103の構成において、トランジスタ102のソース電極及びドレイン電極の一方は、信号線として機能する導電膜109に電気的に接続され、他方は液晶素子121の一対の電極の他方に電気的に接続される。また、トランジスタ102のゲート電極は、走査線として機能する導電膜107に電気的に接続される。トランジスタ102は、オン状態またはオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

**【 0 1 0 8 】**

図5(B)に示す画素103の構成において、容量素子105の一対の電極の一方は、トランジスタ102に接続される。容量素子105の一対の電極他方は、コモン線115に電気的に接続される。コモン線115の電位の値は、画素103の仕様に応じて適宜設定される。容量素子105は、書き込まれたデータを保持する保持容量としての機能を有する。なお、本実施の形態において、容量素子105の一対の電極の一方は、液晶素子121の一対の電極の一方の一部または全部である。また、容量素子105の一対の電極の他方は、液晶素子121の一対の電極の他方の一部または全部である。

30

**【 0 1 0 9 】**

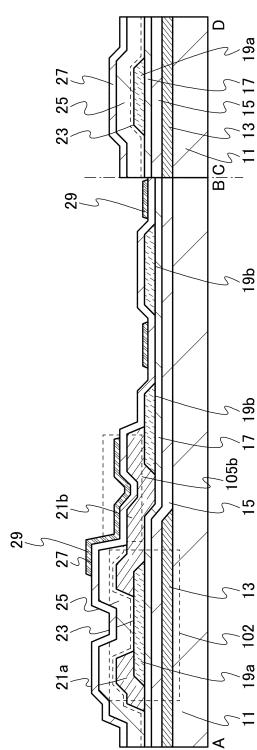

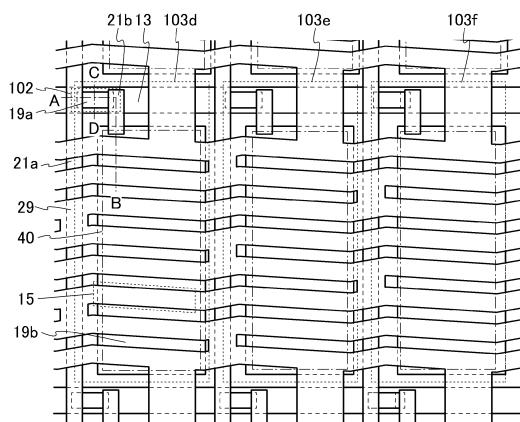

次に、表示装置に含まれる素子基板の具体的な構成について説明する。ここでは、複数の画素103a乃至103cの上面図を図6に示す。

**【 0 1 1 0 】**

40

図6において、走査線として機能する導電膜13は、信号線として機能する導電膜に略直交する方向(図中左右方向)に延伸して設けられている。信号線として機能する導電膜21aは、走査線として機能する導電膜に略直交する方向(図中上下方向)に延伸して設けられている。なお、走査線として機能する導電膜13は、走査線駆動回路104(図5を参照。)と電気的に接続されており、信号線として機能する導電膜21aは、信号線駆動回路106(図5を参照。)に電気的に接続されている。

**【 0 1 1 1 】**

トランジスタ102は、走査線として機能する導電膜及び信号線として機能する導電膜が交差する領域に設けられている。トランジスタ102は、ゲート電極として機能する導電膜13、ゲート絶縁膜(図6に図示せず。)、ゲート絶縁膜上に形成されたチャネル領

50

域が形成される酸化物半導体膜 19a、ソース電極及びドレイン電極として機能する導電膜 21a、21b により構成される。なお、導電膜 13 は、走査線として機能する導電膜としても機能し、酸化物半導体膜 19a と重畳する領域がトランジスタ 102 のゲート電極として機能する。また、導電膜 21a は、信号線として機能する導電膜としても機能し、酸化物半導体膜 19a と重畳する領域がトランジスタ 102 のソース電極またはドレイン電極として機能する。また、図 6 において、走査線として機能する導電膜は、上面形状において端部が酸化物半導体膜 19a の端部より外側に位置する。このため、走査線として機能する導電膜はバックライトなどの光源からの光を遮る遮光膜として機能する。この結果、トランジスタに含まれる酸化物半導体膜 19a に光が照射されず、トランジスタの電気特性の変動を抑制することができる。

10

#### 【0112】

また、導電膜 21b は、画素電極 19b と電気的に接続されている。また、画素電極 19b 上において、絶縁膜を介してコモン電極 29 が設けられている。画素電極 19b 上に設けられる絶縁膜において、一点鎖線で示す開口部 40 が設けられている。開口部 40 において、画素電極 19b は、窒化物絶縁膜（図 6 に図示せず。）と接する。

#### 【0113】

コモン電極 29 は、信号線として機能する導電膜と交差する方向に延伸した縞状の領域（第 1 の領域）を有する。また、該縞状の領域（第 1 の領域）は、信号線として機能する導電膜と平行または略平行な方向に延伸した領域（第 2 の領域）と接続される。このため、画素において、縞状の領域（第 1 の領域）を有するコモン電極 29 は、各領域が同電位である。

20

#### 【0114】

容量素子 105 は、画素電極 19b、及びコモン電極 29 が重なる領域で形成される。画素電極 19b 及びコモン電極 29 は透光性を有する。即ち、容量素子 105 は透光性を有する。

#### 【0115】

図 6 に示すように、本実施の形態に示す液晶表示装置は、FFS モードの液晶表示装置であり、さらに、信号線として機能する導電膜と交差する方向に延伸した縞状の領域を有するコモン電極が設けられるため、コントラストの優れた表示装置を作製することができる。

30

#### 【0116】

また、容量素子 105 は透光性を有するため、画素 103 内に容量素子 105 を大きく（大面積に）形成することができる。従って、開口率を高めつつ、代表的には 50% 以上、好ましくは 60% 以上とすることが可能であると共に、電荷容量を増大させた表示装置を得ることができる。例えば、解像度の高い表示装置、例えば液晶表示装置においては、画素の面積が小さくなり、容量素子の面積も小さくなる。このため、解像度の高い表示装置において、容量素子に蓄積される電荷容量が小さくなる。しかしながら、本実施の形態に示す容量素子 105 は透光性を有するため、当該容量素子を画素に設けることで、各画素において十分な電荷容量を得つつ、開口率を高めることができる。代表的には、画素密度が 200 ppi 以上、さらには 300 ppi 以上、更には 500 ppi 以上である高解像度の表示装置に好適に用いることができる。

40

#### 【0117】

また、液晶表示装置において、容量素子の容量値を大きくするほど、電界を加えた状況において、液晶分子の配向を一定に保つことができる期間を長くすることができる。静止画を表示させる場合、当該期間を長くできるため、画像データを書き換える回数を削減することができ、消費電力を低減することができる。また、本実施の形態に示す構造により、高解像度の表示装置においても、開口率を高めることができるため、バックライトなどの光源の光を効率よく利用することができ、表示装置の消費電力を低減することができる。

#### 【0118】

50

なお、本発明の実施形態の一態様の上面図は、これに限定されない。様々な構成をとることができる。例えば、図28のように、コモン電極29において、接続領域（第2の領域）が各信号線として機能する導電膜上に形成されてもよい。

#### 【0119】

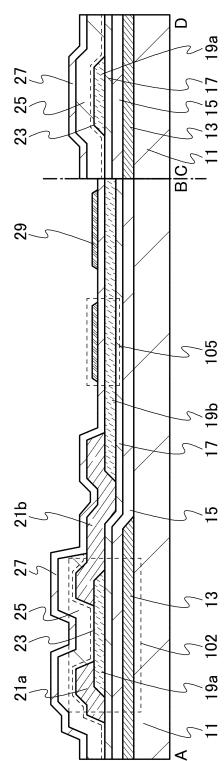

次いで、図6の一点鎖線A-B、C-Dにおける断面図を図7に示す。図7に示すトランジスタ102は、チャネルエッチ型のトランジスタである。なお、一点鎖線A-Bは、トランジスタ102のチャネル長方向、及び容量素子105の断面図であり、C-Dにおける断面図は、トランジスタ102のチャネル幅方向の断面図である。

#### 【0120】

図7に示すトランジスタ102は、シングルゲート構造のトランジスタであり、基板11上に設けられるゲート電極として機能する導電膜13を有する。また、基板11及びゲート電極として機能する導電膜13上に形成される窒化物絶縁膜15と、窒化物絶縁膜15上に形成される酸化物絶縁膜17と、窒化物絶縁膜15及び酸化物絶縁膜17を介して、ゲート電極として機能する導電膜13と重なる酸化物半導体膜19aと、酸化物半導体膜19aに接する、ソース電極及びドレイン電極として機能する導電膜21a、21bとを有する。また、酸化物絶縁膜17、酸化物半導体膜19a、及びソース電極及びドレイン電極として機能する導電膜21a、21b上には、酸化物絶縁膜23が形成され、酸化物絶縁膜23上には酸化物絶縁膜25が形成される。窒化物絶縁膜15、酸化物絶縁膜23、酸化物絶縁膜25、導電膜21b上には窒化物絶縁膜27が形成される。また、画素電極19bが、酸化物絶縁膜17上に形成される。画素電極19bは、ソース電極及びドレイン電極として機能する導電膜21a、21bの一方、ここでは導電膜21bに接続される。また、コモン電極29が、窒化物絶縁膜27上に形成される。

#### 【0121】

また、画素電極19bと、窒化物絶縁膜27と、コモン電極29とが重なる領域が容量素子105として機能する。

#### 【0122】

なお、本発明の実施形態の一態様の断面図は、これに限定されない。様々な構成をとることができる。例えば、画素電極19bは、スリットを有してもよい。または、画素電極19bは櫛歯形状でもよい。その場合の断面図の例を、図8に示す。または、図9に示すように、窒化物絶縁膜27の上に、絶縁膜26bが設けられてもよい。例えば、絶縁膜26bとして、有機樹脂膜を設けてもよい。これにより、絶縁膜26bの表面を平坦にすることができる。つまり、絶縁膜26bは、一例としては、平坦化膜としての機能を有することができる。または、コモン電極29と、導電膜21bとが重なるようにして、容量素子105bを形成してもよい。その場合の断面図の例を、図22、図23に示す。このような構成とすることにより、容量素子105bを画素電極の電位を保持する容量素子として機能させることができる。したがって、このような構成とすることにより、容量素子の電荷容量を増やすことができる。

#### 【0123】

以下に、表示装置の構成の詳細について説明する。

#### 【0124】

基板11の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板11として用いてもよい。また、シリコンや炭化シリコンなどを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板11として用いてもよい。なお、基板11として、ガラス基板を用いる場合、第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)、第9世代(2400mm×2800mm)、第10世代(2950mm×3400mm)等の大面積基板を用いることで、大型の表示装置を作製することができる。

10

20

30

40

50

## 【0125】

また、基板11として、可撓性基板を用い、可撓性基板上に直接、トランジスタ102を形成してもよい。または、基板11とトランジスタ102の間に剥離層を設けてもよい。剥離層は、その上に表示装置を一部あるいは全部完成させた後、基板11より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ102は耐熱性の劣る基板や可撓性の基板にも転載できる。

## 【0126】

ゲート電極として機能する導電膜13は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いてもよい。また、ゲート電極として機能する導電膜13は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタングステン膜を積層する二層構造、窒化タンタル膜または窒化タングステン膜上にタングステン膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

10

20

## 【0127】

また、ゲート電極として機能する導電膜13は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

## 【0128】

窒化物絶縁膜15は、酸素の透過性の低い窒化物絶縁膜を用いることが可能である。更には、酸素、水素、及び水の透過性の低い窒化物絶縁膜を用いることが可能である。酸素の透過性の低い窒化物絶縁膜、酸素、水素、及び水の透過性の低い窒化物絶縁膜としては、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、窒化酸化アルミニウム膜等がある。また、酸素の透過性の低い窒化物絶縁膜、酸素、水素、及び水の透過性の低い窒化物絶縁膜の代わりに、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ガリウム膜、酸化窒化ガリウム膜、酸化イットリウム膜、酸化窒化イットリウム膜、酸化ハフニウム膜、酸化窒化ハフニウム膜等の酸化物絶縁膜を用いることができる。

30

## 【0129】

窒化物絶縁膜15の厚さは、5nm以上100nm以下、より好ましくは20nm以上80nm以下とするとよい。

## 【0130】

40

酸化物絶縁膜17は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物などを用いればよく、積層または単層で設ける。

## 【0131】

また、酸化物絶縁膜17として、ハフニウムシリケート(HfSiO<sub>x</sub>)、窒素が添加されたハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、窒素が添加されたハフニウムアルミニート(HfAl<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、酸化ハフニウム、酸化イットリウムなどの比誘電率の高い材料を用いることでトランジスタのゲートリーアークを低減できる。

## 【0132】

酸化物絶縁膜17の厚さは、5nm以上400nm以下、より好ましくは10nm以上

50

300 nm 以下、より好ましくは 50 nm 以上 250 nm 以下とするとよい。

**【0133】**

酸化物半導体膜 19a は、代表的には、In-Ga 酸化物、In-Zn 酸化物、In-M-Zn 酸化物 (M は Al、Ga、Y、Zr、Sn、La、Ce、または Nd) がある。

**【0134】**

なお、酸化物半導体膜 19a が In-M-Zn 酸化物膜であるとき、In および M の和を 100 atomic % としたとき、In と M の原子数比率は好ましくは In が 25 atomic % より高く、M が 75 atomic % 未満、さらに好ましくは In が 34 atomic % より高く、M が 66 atomic % 未満とする。

**【0135】**

酸化物半導体膜 19a は、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタ 102 のオフ電流を低減することができる。

**【0136】**

酸化物半導体膜 19a の厚さは、3 nm 以上 200 nm 以下、好ましくは 3 nm 以上 100 nm 以下、さらに好ましくは 3 nm 以上 50 nm 以下とする。

**【0137】**

酸化物半導体膜 19a が In-M-Zn 酸化物膜 (M は Al、Ga、Y、Zr、Sn、La、Ce、または Nd) の場合、In-M-Zn 酸化物膜を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In-M-Zn を満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In : M : Zn = 1 : 1 : 1、In : M : Zn = 1 : 1 : 1.2、In : M : Zn = 3 : 1 : 2 が好ましい。なお、成膜される酸化物半導体膜 19a の原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス 40 % の変動を含む。

**【0138】**

酸化物半導体膜 19a としては、キャリア密度の低い酸化物半導体膜を用いる。例えば、酸化物半導体膜 19a は、キャリア密度が  $1 \times 10^{17}$  個 / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  個 / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{13}$  個 / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{11}$  個 / cm<sup>3</sup> 以下の酸化物半導体膜を用いる。

**【0139】**

なお、これらに限られず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体膜 19a のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

**【0140】**

なお、酸化物半導体膜 19a として、不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を用いることで、さらに優れた電気特性を有するトランジスタを作製することができ好ましい。ここでは、不純物濃度が低く、欠陥準位密度の低い（酸素欠損量の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが多い。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が  $1 \times 10^6 \mu m$  でチャネル長 L が  $10 \mu m$  の素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が 1 V から 10 V の範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち  $1 \times 10^{-13} A$  以下という特性を得ることができ

10

20

30

40

50

る。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

#### 【0141】

酸化物半導体膜に含まれる水素は金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子（または酸素が脱離した部分）に酸素欠損が形成される。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。

10

#### 【0142】

このため、酸化物半導体膜19aは酸素欠損と共に、水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜19aにおいて、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られる水素濃度を、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下とする。

20

#### 【0143】

酸化物半導体膜19aにおいて、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体膜19aにおいて酸素欠損が増加し、n型化してしまう。このため、酸化物半導体膜19aにおけるシリコンや炭素の濃度(二次イオン質量分析法により得られる濃度)を、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。

30

#### 【0144】

また、酸化物半導体膜19aにおいて、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms/cm<sup>3</sup>以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜19aのアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

#### 【0145】

また、酸化物半導体膜19aに窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。従って、当該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下にすることが好ましい。

#### 【0146】

また、酸化物半導体膜19aは、例えば非単結晶構造でもよい。非単結晶構造は、例えば、後述するCAAC-O<sub>S</sub>(C Axis Aligned-Crystalline Oxide Semiconductor)、多結晶構造、後述する微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、CAAC-O<sub>S</sub>は最も欠陥準位密度が低い。

40

#### 【0147】

酸化物半導体膜19aは、例えば非晶質構造でもよい。非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

#### 【0148】

なお、酸化物半導体膜19aが、非晶質構造の領域、微結晶構造の領域、多結晶構造の

50

領域、C A A C - O S の領域、単結晶構造の二種以上の領域を有する混合膜であってよい。混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、C A A C - O S の領域、単結晶構造の領域のいずれか二種以上の領域を有する单層構造の場合がある。また、混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、C A A C - O S の領域、単結晶構造の領域のいずれか二種以上の領域の積層構造を有する場合がある。

#### 【0149】

画素電極19bは、酸化物半導体膜19aと同時に形成された酸化物半導体膜を加工して形成される。このため、画素電極19bは、酸化物半導体膜19aと同様の金属元素を有する膜である。また、酸化物半導体膜19aと同様の結晶構造、または異なる結晶構造を有する膜である。しかしながら、酸化物半導体膜19aと同時に形成された酸化物半導体膜に、不純物または酸素欠損を有せしめることで、導電性を有する膜となり、画素電極19bとして機能する。酸化物半導体膜に含まれる不純物としては、水素がある。なお、水素の代わりに不純物として、ホウ素、リン、スズ、アンチモン、希ガス元素、アルカリ金属、アルカリ土類金属等が含まれていてもよい。または、画素電極19bは、酸化物半導体膜19aと同時に形成された膜であり、プラズマダメージ等により酸素欠損が形成され、導電性が高められた膜である。または、画素電極19bは、酸化物半導体膜19aと同時に形成された膜であり、且つ不純物を含むと共に、プラズマダメージ等により酸素欠損が形成され、導電性が高められた膜である。

#### 【0150】

このため、酸化物半導体膜19a及び画素電極19bは共に、酸化物絶縁膜17上に形成されるが、不純物濃度が異なる。具体的には、酸化物半導体膜19aと比較して、画素電極19bの不純物濃度が高い。例えば、酸化物半導体膜19aに含まれる水素濃度は、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$  atoms/cm<sup>3</sup>以下であり、画素電極19b含まれる水素濃度は、 $8 \times 10^{19}$ 以上、好ましくは $1 \times 10^{20}$  atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{20}$ 以上である。また、酸化物半導体膜19aと比較して、画素電極19bに含まれる水素濃度は2倍以上、好ましくは10倍以上である。

#### 【0151】

また、酸化物半導体膜19aと同時に形成された酸化物半導体膜をプラズマに曝すことにより、酸化物半導体膜にダメージを与え、酸素欠損を形成することができる。例えば、酸化物半導体膜上に、プラズマCVD法またはスパッタリング法で膜を成膜すると、酸化物半導体膜がプラズマに曝され、酸素欠損が生成される。または、酸化物絶縁膜23及び酸化物絶縁膜25を形成するためのエッチング処理において酸化物半導体膜がプラズマに曝されることで、酸素欠損が生成される。または、酸化物半導体膜が、酸素及び水素の混合ガス、水素、希ガス、アンモニア等のプラズマに曝されることで、酸素欠損が生成される。この結果、酸化物半導体膜は導電性が高くなり、導電性を有する膜となり、画素電極19bとして機能する。

#### 【0152】

即ち、画素電極19bは、導電性の高い酸化物半導体膜で形成されるともいえる。また、画素電極19bは、導電性の高い金属酸化物膜で形成されるともいえる。

#### 【0153】

また、窒化物絶縁膜27として、窒化シリコン膜を用いる場合、窒化シリコン膜は水素を含む。このため、窒化物絶縁膜27の水素が酸化物半導体膜19aと同時に形成された酸化物半導体膜に拡散すると、該酸化物半導体膜において水素は酸素と結合し、キャリアである電子が生成される。また、窒化シリコン膜をプラズマCVD法またはスパッタリング法で成膜すると、酸化物半導体膜がプラズマに曝され、酸素欠損が生成される。当該酸素欠損に、窒化シリコン膜に含まれる水素が入ることで、キャリアである電子が生成され

10

20

30

40

50

る。これらの結果、酸化物半導体膜は導電性が高くなり、画素電極 19 b となる。

**【0154】**

酸素欠損が形成された酸化物半導体に水素を添加すると、酸素欠損サイトに水素が入り伝導帯近傍にドナー準位が形成される。この結果、酸化物半導体は、導電性が高くなり、導電体化する。導電体化された酸化物半導体を酸化物導電体ということができる。すなわち、画素電極 19 b は、酸化物導電体膜で形成されるということができる。一般に、酸化物半導体は、エネルギーギャップが大きいため、可視光に対して透光性を有する。一方、酸化物導電体は、伝導帯近傍にドナー準位を有する酸化物半導体である。したがって、該ドナー準位による吸収の影響は小さく、可視光に対して酸化物半導体と同程度の透光性を有する。

10

**【0155】**

ここで、酸化物半導体膜が酸化物導電体膜となるモデルの一について、図 39 を用いて説明する。

**【0156】**

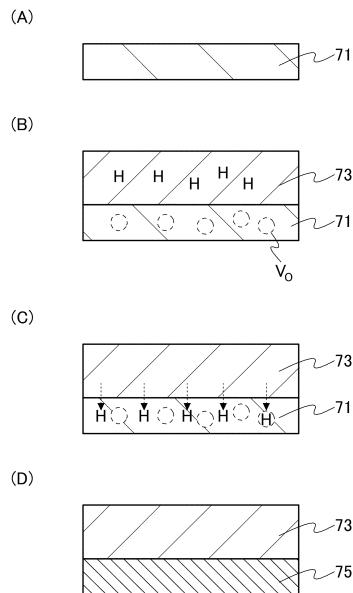

図 39 (A) に示すように、酸化物半導体膜 71 が形成される。

**【0157】**

図 39 (B) に示すように、酸化物半導体膜 71 に窒化物絶縁膜 73 が形成される。窒化物絶縁膜 73 には水素 H が含まれる。窒化物絶縁膜 73 が形成される際に、酸化物半導体膜 71 がプラズマに曝され、酸化物半導体膜 71 に酸素欠損 V<sub>x</sub> が形成される。

20

**【0158】**

図 39 (C) に示すように、窒化物絶縁膜 73 に含まれる水素 H が、酸化物半導体膜 71 に拡散する。酸素欠損 V<sub>x</sub> に水素 H が入り伝導帯近傍にドナー準位が形成される。この結果、図 39 (D) に示すように、酸化物半導体膜は導電性が高くなり、酸化物導電体膜 75 となる。また、酸化物導電体膜 75 が画素電極として機能する。

**【0159】**

画素電極 19 b は、酸化物半導体膜 19 a より抵抗率が低い。画素電極 19 b の抵抗率が、酸化物半導体膜 19 a の抵抗率の  $1 \times 10^{-8}$  倍以上  $1 \times 10^{-1}$  倍未満であることが好ましく、代表的には  $1 \times 10^{-3}$  cm 以上  $1 \times 10^{-4}$  cm 未満、さらに好ましくは、抵抗率が  $1 \times 10^{-3}$  cm 以上  $1 \times 10^{-1}$  cm 未満であるとよい。

30

**【0160】**

ソース電極及びドレイン電極として機能する導電膜 21 a、21 b は、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタングステンからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タングステン膜上にアルミニウム膜を積層する二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

40

**【0161】**

酸化物絶縁膜 23 または酸化物絶縁膜 25 として、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いることが好ましい。ここでは、酸化物絶縁膜 23 として、酸素を透過する酸化物絶縁膜を形成し、酸化物絶縁膜 25 として、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を形成する。

**【0162】**

酸化物絶縁膜 23 は、酸素を透過する酸化物絶縁膜である。このため、酸化物絶縁膜 2

50

3上に設けられる、酸化物絶縁膜25から脱離する酸素を、酸化物絶縁膜23を介して酸化物半導体膜19aに移動させることができる。また、酸化物絶縁膜23は、後に形成する酸化物絶縁膜25を形成する際の、酸化物半導体膜19aへのダメージ緩和膜としても機能する。

#### 【0163】

酸化物絶縁膜23としては、厚さが5nm以上150nm以下、好ましくは5nm以上50nm以下の酸化シリコン膜、酸化窒化シリコン膜等を用いることができる。なお、本明細書中において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。10

#### 【0164】

また、酸化物絶縁膜23は、欠陥量が少ないことが好ましく、代表的には、ESR測定により、 $g = 2.001$ に現れる信号のスピンドル密度が $3 \times 10^{17} \text{ spins/cm}^3$ 以下であることが好ましい。なお、 $g = 2.001$ に現れる信号はシリコンのダンギングボンドに由来する。これは、酸化物絶縁膜23に含まれる欠陥密度が多いと、当該欠陥に酸素が結合してしまい、酸化物絶縁膜23における酸素の透過量が減少してしまうためである。

#### 【0165】

また、酸化物絶縁膜23と酸化物半導体膜19aとの界面における欠陥量が少ないことが好ましく、代表的には、ESR測定により、酸化物半導体膜19aの欠陥に由来するg値が1.89以上1.96以下に現れる信号のスピンドル密度が $1 \times 10^{17} \text{ spins/cm}^3$ 以下、さらには検出下限以下であることが好ましい。20

#### 【0166】

なお、酸化物絶縁膜23においては、外部から酸化物絶縁膜23に入った酸素が全て酸化物絶縁膜23の外部に移動する場合がある。または、外部から酸化物絶縁膜23に入った酸素の一部が、酸化物絶縁膜23にとどまる場合もある。また、外部から酸化物絶縁膜23に酸素が入ると共に、酸化物絶縁膜23に含まれる酸素が酸化物絶縁膜23の外部へ移動することで、酸化物絶縁膜23において酸素の移動が生じる場合もある。

#### 【0167】

酸化物絶縁膜23に接するように酸化物絶縁膜25が形成されている。酸化物絶縁膜25は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、TDS分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18} \text{ atoms/cm}^3$ 以上、好ましくは $3.0 \times 10^{20} \text{ atoms/cm}^3$ 以上である酸化物絶縁膜である。なお、上記TDS分析時における膜の表面温度としては100以上700以下、または100以上500以下の範囲が好ましい。30

#### 【0168】

酸化物絶縁膜25としては、厚さが30nm以上500nm以下、好ましくは50nm以上400nm以下の、酸化シリコン膜、酸化窒化シリコン膜等を用いることができる。40

#### 【0169】

また、酸化物絶縁膜25は、欠陥量が少ないことが好ましく、代表的には、ESR測定により、 $g = 2.001$ に現れる信号のスピンドル密度が $1.5 \times 10^{18} \text{ spins/cm}^3$ 未満、更には $1 \times 10^{18} \text{ spins/cm}^3$ 以下であることが好ましい。なお、酸化物絶縁膜25は、酸化物絶縁膜23と比較して酸化物半導体膜19aから離れているため、酸化物絶縁膜23より、欠陥密度が多くともよい。

#### 【0170】

窒化物絶縁膜27は、窒化物絶縁膜15と同様に酸素の透過性の低い窒化物絶縁膜を用いることが可能である。更には、酸素、水素、及び水の透過性の低い窒化物絶縁膜を用いることが可能である。50

## 【0171】

窒化物絶縁膜27としては、厚さが50nm以上300nm以下、好ましくは100nm以上200nm以下の、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、窒化酸化アルミニウム膜等がある。

## 【0172】

酸化物絶縁膜23または酸化物絶縁膜25において、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜が含まれると、酸化物絶縁膜23または酸化物絶縁膜25に含まれる酸素の一部を酸化物半導体膜19aに移動させ、酸化物半導体膜19aに含まれる酸素欠損量を低減することが可能である。

## 【0173】

酸化物半導体膜中に酸素欠損が含まれている酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナス方向に変動しやすく、ノーマリーオン特性となりやすい。これは、酸化物半導体膜に含まれる酸素欠損に起因して電荷が生じ、低抵抗化するためである。トランジスタがノーマリーオン特性を有すると、動作時に動作不良が発生しやすくなる、または非動作時の消費電力が高くなるなどの、様々な問題が生じる。また、経時変化やストレス試験により、トランジスタの電気特性、代表的にはしきい値電圧の変動量が増大するという問題がある。

## 【0174】

しかしながら、本実施の形態に示すトランジスタ102は、酸化物半導体膜19a上に設けられる酸化物絶縁膜23または酸化物絶縁膜25が、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜である。さらに、酸化物半導体膜19a、酸化物絶縁膜23、及び酸化物絶縁膜25を、窒化物絶縁膜15及び酸化物絶縁膜17で包み込む。この結果、酸化物絶縁膜23または酸化物絶縁膜25に含まれる酸素が、効率よく酸化物半導体膜19aに移動し、酸化物半導体膜19aの酸素欠損量を低減することが可能である。この結果、ノーマリーオフ特性を有するトランジスタとなる。また、経時変化やストレス試験により、トランジスタの電気特性、代表的にはしきい値電圧の変動量を低減することができる。

## 【0175】

コモン電極29は、透光性を有する膜、好ましくは透光性を有する導電膜を用いる。透光性を有する導電膜は、酸化タンゲステンを含むインジウム酸化物膜、酸化タンゲステンを含むインジウム亜鉛酸化物膜、酸化チタンを含むインジウム酸化物膜、酸化チタンを含むインジウム錫酸化物膜、インジウム錫酸化物(以下、ITOと示す。)膜、インジウム亜鉛酸化物膜、酸化ケイ素を添加したインジウム錫酸化物膜等がある。

## 【0176】

コモン電極29は、実施の形態1に示すコモン電極9と同様の形状をしており、信号線として機能する導電膜21aの延伸方向とコモン電極29の延伸方向が交差する。このため、信号線として機能する導電膜21aとコモン電極29との間で生じる電界と、画素電極19bとコモン電極29との間で生じる電界との間で、方位ずれが生じ、且つそのずれの角度が大きい。このため、信号線として機能する導電膜近傍の液晶分子の配向状態と、隣接する画素に設けられた画素電極とコモン電極との間で生じる電界により生じた画素電極近傍の液晶分子の配向状態とは、互いに影響されにくい。この結果、画素の透過率の変化が抑制される。この結果、画像のちらつきを低減することができる。

## 【0177】

また、リフレッシュレートが低い液晶表示装置において、保持期間であっても、信号線として機能する導電膜21a近傍の液晶分子の配向は、隣接する画素に設けられた画素電極とコモン電極29との間で生じる電界による画素電極近傍の液晶分子の配向状態へ影響を与えにくい。この結果、保持期間において、画素の透過率を維持することができあり、ちらつきを低減することができる。

## 【0178】

また、コモン電極29は、信号線として機能する導電膜21aと交差する方向に縞状に

10

20

30

40

50

延伸する領域を有する。このため、画素電極 19 b 及び導電膜 21 a 近傍において、意図しない液晶分子の配向を防ぐことが可能であり、光漏れを抑制することができる。この結果、コントラストの優れた表示装置を作製することができる。

#### 【0179】

また、本実施の形態に示す表示装置の素子基板は、トランジスタの酸化物半導体膜とともに、画素電極が形成される。画素電極は容量素子の一方の電極として機能する。また、コモン電極は容量素子の他方の電極として機能する。これらのため、容量素子を形成するために、新たに導電膜を形成する工程が不要であり、作製工程を削減できる。また、容量素子は透光性を有する。この結果、容量素子の占有面積を大きくしつつ、画素の開口率を高めることができる。

10

#### 【0180】

次に、図 7 に示すトランジスタ 102 及び容量素子 105 の作製方法について、図 10 乃至図 12 を用いて説明する。

#### 【0181】

図 10 (A) に示すように、基板 11 上に導電膜 13 となる導電膜 12 を形成する。導電膜 12 は、スパッタリング法、化学気相堆積 (CVD) 法 (有機金属化学気相堆積 (MOCVD : Metal Organic Chemical Vapor Deposition) 法、メタル化学気相堆積法、原子層成膜 (ALD) 法あるいはプラズマ化学気相堆積 (PECVD) 法を含む。)、蒸着法、パルスレーザー堆積 (PLD) 法等により形成する。有機金属化学気相堆積 (MOCVD) 法、メタル化学気相堆積法、原子層成膜 (ALD) 法を用いることで、プラズマによるダメージの少ない導電膜を形成することができる。

20

#### 【0182】

ここでは、基板 11 としてガラス基板を用いる。また、導電膜 12 として、厚さ 100 nm のタンクステン膜をスパッタリング法により形成する。

#### 【0183】

次に、導電膜 12 上に、第 1 のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜 12 の一部をエッチングして、図 10 (B) に示すように、ゲート電極として機能する導電膜 13 を形成する。この後、マスクを除去する。

30

#### 【0184】

なお、ゲート電極として機能する導電膜 13 は、上記形成方法の代わりに、電解メッキ法、印刷法、インクジェット法等で形成してもよい。

#### 【0185】

ここでは、ドライエッティング法によりタンクステン膜をエッティングして、ゲート電極として機能する導電膜 13 を形成する。

#### 【0186】

次に、図 10 (C) に示すように、ゲート電極として機能する導電膜 13 上に、窒化物絶縁膜 15 と、後に酸化物絶縁膜 17 となる酸化物絶縁膜 16 を形成する。次に、酸化物絶縁膜 16 上に、後に酸化物半導体膜 19 a、画素電極 19 b となる酸化物半導体膜 18 を形成する。

40

#### 【0187】

窒化物絶縁膜 15 及び酸化物絶縁膜 16 は、スパッタリング法、化学気相堆積 (CVD) 法 (有機金属化学気相堆積 (MOCVD) 法、メタル化学気相堆積法、原子層成膜 (ALD) 法あるいはプラズマ化学気相堆積 (PECVD) 法を含む。)、蒸着法、パルスレーザー堆積 (PLD) 法、塗布法、印刷法等により形成する。有機金属化学気相堆積 (MOCVD) 法、原子層成膜 (ALD) 法を用いることで、プラズマによるダメージの少ない窒化物絶縁膜 15 及び酸化物絶縁膜 16 を形成することができる。また、原子層成膜 (ALD) 法を用いることで、窒化物絶縁膜 15 及び酸化物絶縁膜 16 の被覆性を高めることが可能である。

50

## 【0188】

ここでは、シラン、窒素、及びアンモニアを原料ガスとしたプラズマCVD法を用いて、窒化物絶縁膜15として、厚さ300nmの窒化シリコン膜を形成する。

## 【0189】

酸化物絶縁膜16として酸化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜を形成する場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

## 【0190】

酸化物絶縁膜16として酸化ガリウム膜を形成する場合、MOCVD法を用いて形成することができる。

## 【0191】

ここでは、シラン及び一酸化二窒素を原料ガスとしたプラズマCVD法を用いて、酸化物絶縁膜16として、厚さ50nmの酸化窒化シリコン膜を形成する。

## 【0192】

酸化物半導体膜18は、スパッタリング法、化学気相堆積(CVD)法(有機金属化学堆積(MOCVD)法、原子層成膜(ALD)法あるいはプラズマ化学気相堆積(PECVD)法を含む)、パルスレーザー蒸着法、レーザーアブレーション法、塗布法等を用いて形成することができる。有機金属化学堆積(MOCVD)法、メタル化学堆積法、原子層成膜(ALD)法を用いることで、プラズマによるダメージの少ない酸化物半導体膜18を形成することができるとともに、酸化物絶縁膜16へのダメージを低減することができる。また、原子層成膜(ALD)法を用いることで、酸化物半導体膜18の被覆性を高めることが可能である。

## 【0193】

スパッタリング法で酸化物半導体膜を形成する場合、プラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。

## 【0194】

スパッタリングガスは、希ガス(代表的にはアルゴン)、酸素ガス、希ガス及び酸素の混合ガスを適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。

## 【0195】

また、ターゲットは、形成する酸化物半導体膜の組成にあわせて、適宜選択すればよい。

## 【0196】

高純度真性または実質的に高純度真性である酸化物半導体膜を得るためにには、チャンバー内を高真空排氣するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下、より好ましくは-120以下にまで高純度化したガスを用いることで酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。

## 【0197】

ここでは、In-Ga-Zn酸化物ターゲット(In:Ga:Zn=1:1:1)を用いたスパッタリング法により、酸化物半導体膜として厚さ35nmのIn-Ga-Zn酸化物膜を形成する。

## 【0198】

次に、酸化物半導体膜18上に、第2のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成した後、該マスクを用いて酸化物半導体膜の一部をエッチングすることで、図10(D)に示すような、素子分離された酸化物半導体膜19a、19cを形成する。この後、マスクを除去する。

10

20

30

40

50

**【 0 1 9 9 】**

ここでは、酸化物半導体膜18上にマスクを形成し、ウェットエッティング法により酸化物半導体膜18の一部を選択的にエッティングすることで、酸化物半導体膜19a、19cを形成する。

**【 0 2 0 0 】**

次に、図11(A)に示すように、のちに導電膜21a、21bとなる導電膜20を形成する。

**【 0 2 0 1 】**

導電膜20は、導電膜12と同様の方法を適宜用いて形成することができる。

**【 0 2 0 2 】**

ここでは、厚さ50nmのタンゲステン膜及び厚さ300nmの銅膜を順にスパッタリング法により積層する。

**【 0 2 0 3 】**

次に、導電膜20上に第3のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜20をエッティングして、図11(B)に示すように、ソース電極及びドレイン電極として機能する導電膜21a、21bを形成する。この後、マスクを除去する。

**【 0 2 0 4 】**

ここでは、銅膜上にフォトリソグラフィ工程によりマスクを形成する。次に、当該マスクを用いてタンゲステン膜及び銅膜をエッティングして、導電膜21a、21bを形成する。なお、ウェットエッティング法を用いて銅膜をエッティングする。次に、SF<sub>6</sub>を用いたドライエッティング法により、タンゲステン膜をエッティングすることで、該エッティングにおいて、銅膜の表面にフッ化物が形成される。該フッ化物により、銅膜からの銅元素の拡散が低減され、酸化物半導体膜19aにおける銅濃度を低減することができる。

**【 0 2 0 5 】**

次に、図11(C)に示すように、酸化物半導体膜19a、19c、及び導電膜21a、21b上に、後に酸化物絶縁膜23となる酸化物絶縁膜22、及び後に酸化物絶縁膜25となる酸化物絶縁膜24を形成する。酸化物絶縁膜22及び酸化物絶縁膜24は、窒化物絶縁膜15及び酸化物絶縁膜16と同様の方法を適宜用いて形成することができる。

**【 0 2 0 6 】**

なお、酸化物絶縁膜22を形成した後、大気に曝すことなく、連続的に酸化物絶縁膜24を形成することが好ましい。酸化物絶縁膜22を形成した後、大気開放せず、原料ガスの流量、圧力、高周波電力及び基板温度の一以上を調整して、酸化物絶縁膜24を連続的に形成することで、酸化物絶縁膜22及び酸化物絶縁膜24における界面の大気成分由來の不純物濃度を低減することができると共に、酸化物絶縁膜24に含まれる酸素を酸化物半導体膜19aに移動させることができ、酸化物半導体膜19aの酸素欠損量を低減することができる。

**【 0 2 0 7 】**

酸化物絶縁膜22としては、プラズマCVD装置の真空排気された処理室内に載置された基板を280以上400以下に保持し、処理室に原料ガスを導入して処理室内における圧力を20Pa以上250Pa以下、さらに好ましくは100Pa以上250Pa以下とし、処理室内に設けられる電極に高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

**【 0 2 0 8 】**

酸化物絶縁膜22の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

**【 0 2 0 9 】**

上記条件を用いることで、酸化物絶縁膜22として酸素を透過する酸化物絶縁膜を形成

10

20

30

40

50

することができる。また、酸化物絶縁膜22を設けることで、後に形成する酸化物絶縁膜25の形成工程において、酸化物半導体膜19aへのダメージ低減が可能である。

#### 【0210】

なお、酸化物絶縁膜22は、プラズマCVD装置の真空排気された処理室内に載置された基板を280以上400以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下とし、処理室内に設けられる電極に高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

#### 【0211】

当該成膜条件において、基板温度を上記温度とすることで、シリコン及び酸素の結合力が強くなる。この結果、酸化物絶縁膜22として、酸素が透過し、緻密であり、且つ硬い酸化物絶縁膜、代表的には、25において0.5重量%のフッ酸を用いた場合のエッチング速度が10nm/分以下、好ましくは8nm/分以下である酸化シリコン膜または酸化窒化シリコン膜を形成することができる。10

#### 【0212】

また、加熱をしながら酸化物絶縁膜22を形成するため、当該工程において酸化物半導体膜19aに含まれる水素、水等を脱離させることができる。酸化物半導体膜19aに含まれる水素は、プラズマ中で発生した酸素ラジカルと結合し、水となる。酸化物絶縁膜22の成膜工程において基板が加熱されているため、酸素及び水素の結合により生成された水は、酸化物半導体膜から脱離する。即ち、プラズマCVD法によって酸化物絶縁膜22を形成することで、酸化物半導体膜19aに含まれる水及び水素の含有量を低減することができる。20

#### 【0213】

また、酸化物絶縁膜22を形成する工程において加熱するため、酸化物半導体膜19aが露出された状態での加熱時間が少なく、加熱処理による酸化物半導体膜からの酸素の脱離量を低減することができる。即ち、酸化物半導体膜中に含まれる酸素欠損量を低減することができる。

#### 【0214】

なお、シリコンを含む堆積性気体に対する酸化性気体量を100倍以上とすることで、酸化物絶縁膜22に含まれる水素含有量を低減することが可能である。この結果、酸化物半導体膜19aに混入する水素量を低減できるため、トランジスタのしきい値電圧のマイナスシフトを抑制することができる。30

#### 【0215】

ここでは、酸化物絶縁膜22として、流量30sccmのシラン及び流量4000sccmの一酸化二窒素を原料ガスとし、処理室の圧力を200Pa、基板温度を220とし、27.12MHzの高周波電源を用いて150Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ50nmの酸化窒化シリコン膜を形成する。当該条件により、酸素が透過する酸化窒化シリコン膜を形成することができる。

#### 【0216】

酸化物絶縁膜24としては、プラズマCVD装置の真空排気された処理室内に載置された基板を180以上280以下、さらに好ましくは200以上240以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm<sup>2</sup>以上0.5W/cm<sup>2</sup>以下、さらに好ましくは0.25W/cm<sup>2</sup>以上0.35W/cm<sup>2</sup>以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成する。40

#### 【0217】

酸化物絶縁膜24の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素50

、二酸化窒素等がある。

**【0218】**

酸化物絶縁膜24の成膜条件として、上記圧力の処理室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、酸化物絶縁膜24における酸素含有量が化学量論比よりも多くなる。一方、基板温度が、上記温度で形成された膜では、シリコンと酸素の結合力が弱いため、後の工程の加熱処理により膜中の酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化物絶縁膜を形成することができる。また、酸化物半導体膜19a上に酸化物絶縁膜22が設けられている。このため、酸化物絶縁膜24の形成工程において、酸化物絶縁膜22が酸化物半導体膜19aの保護膜となる。この結果、酸化物半導体膜19aへのダメージを低減しつつ、パワー密度の高い高周波電力を用いて酸化物絶縁膜24を形成することができる。

10

**【0219】**

ここでは、酸化物絶縁膜24として、流量200 sccmのシラン及び流量4000 sccmの一酸化二窒素を原料ガスとし、処理室の圧力を200 Pa、基板温度を220とし、27.12 MHzの高周波電源を用いて1500 Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ400 nmの酸化窒化シリコン膜を形成する。なお、プラズマCVD装置は電極面積が6000 cm<sup>2</sup>である平行平板型のプラズマCVD装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると0.25 W/cm<sup>2</sup>である。

20

**【0220】**

また、ソース電極及びドレイン電極として機能する導電膜21a、21bを形成する際、導電膜のエッティングによって、酸化物半導体膜19aはダメージを受け、酸化物半導体膜19aのバックチャネル（酸化物半導体膜19aにおいて、ゲート電極として機能する導電膜13と対向する面と反対側の面）側に酸素欠損が生じる。しかし、酸化物絶縁膜24に化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を適用することで、加熱処理によって当該バックチャネル側に生じた酸素欠損を修復することができる。これにより、酸化物半導体膜19aに含まれる欠陥を低減することができるため、トランジスタ102の信頼性を向上させることができる。

30

**【0221】**

次に、酸化物絶縁膜24上に、第4のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて酸化物絶縁膜22及び酸化物絶縁膜24の一部をエッティングして、図11(D)に示すように、開口部40を有する酸化物絶縁膜23及び酸化物絶縁膜25を形成する。この後、マスクを除去する。

**【0222】**

当該工程において、ドライエッティング法により、酸化物絶縁膜22及び酸化物絶縁膜24をエッティングすることが好ましい。この結果、酸化物半導体膜19cはエッティング処理においてプラズマに曝されるため、酸化物半導体膜19cの酸素欠損量を増加させることができある。

40

**【0223】**

次に、加熱処理を行う。該加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。

**【0224】**

該加熱処理は、電気炉、RTA装置等を用いることができる。RTA装置を用いることで、短時間に限り、基板の歪み点以上の温度で熱処理を行うことができる。そのため加熱処理時間を短縮することができる。

**【0225】**

加熱処理は、窒素、酸素、超乾燥空気（水の含有量が20 ppm以下、好ましくは1 ppm以下、好ましくは10 ppb以下の空気）、または希ガス（アルゴン、ヘリウム等）

50

の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい。

【0226】

当該加熱処理により、酸化物絶縁膜25に含まれる酸素の一部を酸化物半導体膜19aに移動させ、酸化物半導体膜19aに含まれる酸素欠損量を低減することが可能である。

【0227】

また、酸化物絶縁膜23及び酸化物絶縁膜25に水、水素等が含まれる場合であって、窒化物絶縁膜26が、さらに水、水素等に対するバリア性を有する場合、窒化物絶縁膜26を後に形成し、加熱処理を行うと、酸化物絶縁膜23及び酸化物絶縁膜25に含まれる水、水素等が、酸化物半導体膜19aに移動し、酸化物半導体膜19aに欠陥が生じてしまう。しかしながら、当該加熱により、酸化物絶縁膜23及び酸化物絶縁膜25に含まれる水、水素等を脱離させることができ、トランジスタ102の電気特性のばらつきを低減すると共に、しきい値電圧の変動を抑制することができる。10

【0228】

なお、加熱しながら酸化物絶縁膜24を、酸化物絶縁膜22上に形成することで、酸化物半導体膜19aに酸素を移動させ、酸化物半導体膜19aに含まれる酸素欠損量を低減することが可能であるため、当該加熱処理を行わなくともよい。

【0229】

また、当該加熱処理は、酸化物絶縁膜22及び酸化物絶縁膜24を形成した後に行つてもよいが、酸化物絶縁膜23及び酸化物絶縁膜25を形成した後の加熱処理の方が、酸化物半導体膜19cへの酸素の移動が生じないと共に、酸化物半導体膜19cが露出されているため酸化物半導体膜19cから酸素が脱離し、酸素欠損が形成されるため、より導電性を有する膜を形成でき、好ましい。20

【0230】

ここでは、窒素及び酸素雰囲気で、350、1時間の加熱処理を行う。

【0231】

次に、図12(A)に示すように、窒化物絶縁膜26を形成する。

【0232】

窒化物絶縁膜26は、窒化物絶縁膜15及び酸化物絶縁膜16と同様の方法を適宜用いて形成することができる。窒化物絶縁膜26をスパッタリング法、CVD法等により形成することで、酸化物半導体膜19cがプラズマに曝されるため、酸化物半導体膜19cの酸素欠損量を増加させることができる。30

【0233】

また、酸化物半導体膜19cは導電性が向上し、画素電極19bとなる。なお、窒化物絶縁膜26として、プラズマCVD法により窒化シリコン膜を形成すると、窒化シリコン膜に含まれる水素が酸化物半導体膜19cに拡散するため、画素電極19bの導電性を高めることができる。

【0234】

窒化物絶縁膜26としてプラズマCVD法で窒化シリコン膜を形成する場合、プラズマCVD装置の真空排気された処理室内に載置された基板を300以上400以下、さらに好ましくは320以上370以下に保持することで、緻密な窒化シリコン膜を形成できるため好ましい。40

【0235】

窒化シリコン膜を形成する場合、シリコンを含む堆積性気体、窒素、及びアンモニアを原料ガスとして用いることが好ましい。原料ガスとして、窒素と比較して少量のアンモニアを用いることで、プラズマ中でアンモニアが解離し、活性種が発生する。当該活性種が、シリコンを含む堆積性気体に含まれるシリコン及び水素の結合、及び窒素の三重結合を切断する。この結果、シリコン及び窒素の結合が促進され、シリコン及び水素の結合が少なく、欠陥が少なく、緻密な窒化シリコン膜を形成することができる。一方、原料ガスにおいて、窒素に対するアンモニアの量が多いと、シリコンを含む堆積性気体及び窒素それ50

その分解が進まず、シリコン及び水素結合が残存してしまい、欠陥が増大した、且つ粗な窒化シリコン膜が形成されてしまう。これらのため、原料ガスにおいて、アンモニアに対する窒素の流量比を5以上50以下、好ましくは10以上50以下とすることが好ましい。

#### 【0236】

ここでは、プラズマCVD装置の処理室に、流量50sccmのシラン、流量5000sccmの窒素、及び流量100sccmのアンモニアを原料ガスとし、処理室の圧力を100Pa、基板温度を350<sup>o</sup>Cとし、27.12MHzの高周波電源を用いて1000Wの高周波電力を平行平板電極に供給したプラズマCVD法により、窒化物絶縁膜26として、厚さ50nmの窒化シリコン膜を形成する。なお、プラズマCVD装置は電極面積が6000cm<sup>2</sup>である平行平板型のプラズマCVD装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると1.7×10<sup>-1</sup>W/cm<sup>2</sup>である。10

#### 【0237】

次に、加熱処理を行ってもよい。該加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。この結果、しきい値電圧のマイナスシフトを低減することができる。また、しきい値電圧の変動量を低減することができる。

#### 【0238】

次に、図示しないが、第5のフォトマスクを用いたフォトリソグラフィ工程により、マスクを形成する。次に、該マスクを用いて、窒化物絶縁膜15、酸化物絶縁膜16、酸化物絶縁膜23、酸化物絶縁膜25、窒化物絶縁膜26のそれぞれ一部をエッチングして、窒化物絶縁膜27を形成すると共に、導電膜13と一緒に形成された接続端子の一部を露出する開口部を形成する。または、酸化物絶縁膜23、酸化物絶縁膜25、窒化物絶縁膜26のそれぞれ一部をエッチングして、窒化物絶縁膜27を形成すると共に、導電膜21a、21bと一緒に形成された接続端子の一部を露出する開口部を形成する。20

#### 【0239】

次に、図12(B)に示すように、窒化物絶縁膜27上に、後にコモン電極29となる導電膜28を形成する。

#### 【0240】

導電膜28は、スパッタリング法、CVD法、蒸着法等により導電膜を形成する。30

#### 【0241】

次に、導電膜28上に、第6のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜28の一部をエッチングして、図12(C)に示すように、コモン電極29を形成する。なお、図示しないが、コモン電極29は、導電膜13と一緒に形成された接続端子、または導電膜21a、21bと一緒に形成された接続端子と接続される。この後、マスクを除去する。

#### 【0242】

以上の工程により、トランジスタ102を作製すると共に、容量素子105を作製することができる。

#### 【0243】

本実施の形態に示す表示装置の素子基板は、上面形状がジグザグ状であり、且つ信号線として機能する導電膜と交差する方向に縞状に延伸した領域を有するコモン電極が形成される。このため、コントラストの優れた表示装置を作製することができる。また、リフレッシュレートが低い液晶表示装置において、ちらつきを低減することができる。40

#### 【0244】

また、本実施の形態に示す表示装置の素子基板は、トランジスタの酸化物半導体膜とともに、画素電極が形成されるため、6枚のフォトマスクを用いてトランジスタ102及び容量素子105を作製することが可能である。画素電極は容量素子の一方の電極として機能する。また、コモン電極は、容量素子の他方の電極として機能する。これらのため、容量素子を形成するために、新たに導電膜を形成する工程が不要であり、作製工程を削減で50

きる。また、容量素子は透光性を有する。この結果、容量素子の占有面積を大きくしつつ、画素の開口率を高めることができる。また、低消費電力の表示装置を作製することができる。

#### 【0245】

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

#### 【0246】

<変形例1>

実施の形態1に示す表示装置において、コモン電極に接続されるコモン線を設ける構造について、図13を用いて説明する。

10

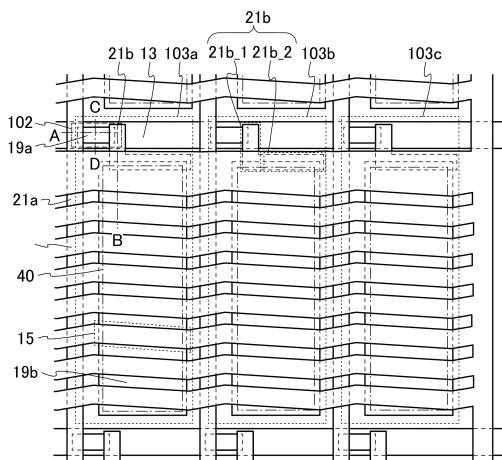

#### 【0247】

図13(A)は、表示装置に含まれる画素103a乃至103cの上面図であり、図13(A)の一点鎖線A-B、C-Dの断面図を図13(B)に示す。

#### 【0248】

図13(A)に示すように、コモン電極29の上面形状は、ジグザグ状であり、信号線として機能する導電膜21aの延伸方向とコモン電極29の延伸方向が交差する。

#### 【0249】

ここで、コモン電極29の構成を分かりやすくするため、ハッチングを用いてコモン電極29の形状を説明する。コモン電極29は、左下がりハッチングで示した領域と、右下がりハッチングで示した領域とを有する。左下がりハッチングで示した領域は、縞状の領域(第1の領域)であり、ジグザグ状であり、信号線として機能する導電膜21aの延伸方向とコモン電極29の延伸方向が交差する。右下がりハッチングで示した領域は、縞状の領域(第1の領域)と接続される接続領域(第2の領域)であり、信号線として機能する導電膜21aと平行または略平行な方向に延伸する。

20

#### 【0250】

また、コモン線21cが、コモン電極29の接続領域(第2の領域)と重なる。

#### 【0251】

コモン線21cは、1画素ごとに設けてもよい。または、コモン線21cは、複数の画素ごとに設けてもよい。たとえば、図13(A)に示すように、3つの画素に対して1本のコモン線21cを設けることで、表示装置の平面においてコモン線の専有面積を低減することが可能である。または、4以上の画素に対して1本のコモン線を設けてもよい。この結果、画素の面積及び画素の開口率を高めることができる。

30

#### 【0252】

また、画素電極19b及びコモン電極29が重なる領域において、画素電極19bと、コモン電極29の接続領域(第2の領域)との間で発生する電界では、液晶分子が駆動されにくい。このため、コモン電極29の接続領域(第2の領域)において、画素電極19bと重なる領域を低減することで、液晶分子が駆動される領域を増加させることができ、開口率を向上させることができる。例えば、図13(A)に示すように、コモン電極29の接続領域(第2の領域)を、画素電極19bと重ならない位置に設けることで、画素電極19bとコモン電極29の接続領域との重なる面積を低減することが可能であり、画素の開口率を高めることができる。

40

#### 【0253】

図13(B)に示すように、コモン線21cは、信号線として機能する導電膜21aと同時に形成することができる。また、コモン電極29は、酸化物絶縁膜23、酸化物絶縁膜25、及び窒化物絶縁膜27に形成される開口部42において、コモン線21cと接続される。

#### 【0254】

コモン電極29を形成する材料と比較して、導電膜21aを形成する材料の抵抗率が低いため、コモン電極29及びコモン線21cの抵抗を低減することが可能である。

#### 【0255】

50

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

#### 【0256】

##### (実施の形態3)

本実施の形態では、実施の形態2と異なる表示装置及びその作製方法について図面を参照して説明する。本実施の形態では、高精細な表示装置に含まれるトランジスタにおいて、光漏れを低減することが可能なソース電極及びドレイン電極を有する点が、実施の形態2と異なる。なお、実施の形態2と重複する構成は説明を省略する。

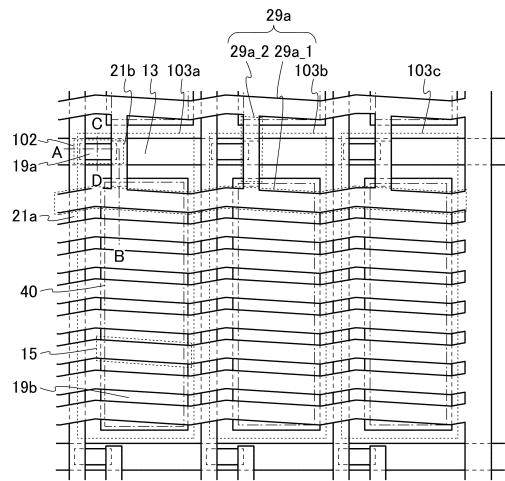

#### 【0257】

図14は、本実施の形態に示す表示装置の上面図である。<sup>10</sup> ソース電極及びドレイン電極の一方として機能する導電膜21bの上面形状がL字であることを特徴とする。すなわち、導電膜21bは、走査線として機能する導電膜13と垂直な方向に延伸する領域21b\_1と、該導電膜13と平行または略平行な方向に延伸する領域21b\_2とが接続した平面形状を有し、且つ該領域21b\_2が、平面において、導電膜13、画素電極19b及びコモン電極29の一以上と重なることを特徴とする。または、導電膜21bは、該導電膜13と平行または略平行な方向に延伸する領域21b\_2を有し、該領域21b\_2が、平面において、導電膜13と、画素電極19bまたはコモン電極29との間に位置することを特徴とする。

#### 【0258】

<sup>20</sup> 高精細な表示装置において、画素の面積が縮小されるため、走査線として機能する導電膜13及びコモン電極29の間隔が狭まる。黒表示の画素において、トランジスタがオン状態となる電圧が、走査線として機能する導電膜13に印加されると、黒表示の画素電極19bにおいて、画素電極及び走査線として機能する導電膜13との間に、電界が発生してしまう。この結果、液晶分子が意図しない方向に回転してしまい、光漏れの原因となる。

#### 【0259】

しかしながら、本実施の形態に示す表示装置に含まれるトランジスタにおいて、ソース電極及びドレイン電極の一方として機能する導電膜21bにおいて、導電膜13、画素電極19b及びコモン電極29の一以上と重なる領域21b\_2を有する、または、平面において、導電膜13と、画素電極19bまたはコモン電極29との間に位置する領域21b\_2を有する。<sup>30</sup> この結果、領域21b\_2が、走査線として機能する導電膜13の電界を遮蔽するため、該導電膜13及び画素電極19bの間に発生する電界を抑制することが可能であり、光漏れを低減することが可能である。

#### 【0260】

なお、導電膜21bとコモン電極29とが、重なるようにしてもよい。その領域は、容量素子として機能させることができる。したがって、このような構成とすることにより、容量素子の電荷容量を増やすことが出来る。その場合の例を、図24に示す。

#### 【0261】

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。<sup>40</sup>

#### 【0262】

##### (実施の形態4)

本実施の形態では、実施の形態2及び実施の形態3と異なる表示装置及びその作製方法について図面を参照して説明する。本実施の形態では、高精細な表示装置において、光漏れを低減することが可能なコモン電極を有する点が実施の形態2と異なる。なお、実施の形態2と重複する構成は説明を省略する。

#### 【0263】

図15は、本実施の形態に示す表示装置の上面図である。コモン電極29aは、信号線として機能する導電膜21aと交差する方向に延伸する縞状の領域29a\_1と、該縞状の領域と接続し、且つ走査線として機能する導電膜13と重なる領域29a\_2を有する

50

50

50

50

50

ことを特徴とする。

**【0264】**

高精細な表示装置において、画素の面積が縮小されるため、走査線として機能する導電膜13及び画素電極19bの間隔が狭まる。走査線として機能する導電膜13に電圧が印加されると、該導電膜13及び画素電極19bの間に電界が発生してしまう。この結果、液晶分子が意図しない方向に動作してしまい、光漏れの原因となる。

**【0265】**

しかしながら、本実施の形態に示す表示装置は、走査線として機能する導電膜13と交差する領域29a\_2を有するコモン電極29aを有する。この結果、走査線として機能する導電膜13とコモン電極29aの間に発生する電界を抑制することが可能であり、光漏れを低減することが可能である。10

**【0266】**

なお、導電膜21bとコモン電極29とが、重なるように形成してもよい。その領域は、容量素子として機能させることができる。したがって、このような構成とすることにより、容量素子の電荷容量を増やすことが出来る。その場合の例を、図25に示す。

**【0267】**

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

**【0268】**

(実施の形態5)

20

本実施の形態では、実施の形態2と異なる表示装置及びその作製方法について図面を参照して説明する。本実施の形態では、トランジスタにおいて異なるゲート電極の間に酸化物半導体膜が設けられている構造、即ちデュアルゲート構造のトランジスタである点が実施の形態2と異なる。なお、実施の形態2と重複する構成は説明を省略する。

**【0269】**

表示装置に含まれる素子基板の具体的な構成について説明する。本実施の形態に示す素子基板は、図26に示すように、ゲート電極として機能する導電膜13、酸化物半導体膜19a、導電膜21a、21b、及び酸化物絶縁膜25それぞれの一部または全部に重なるゲート電極として機能する導電膜29bを有する点が実施の形態2と異なる。ゲート電極として機能する導電膜29bは、開口部41a及び41bにおいて、ゲート電極として機能する導電膜13と接続される。30

**【0270】**

次いで、図26に示すトランジスタ102aは、チャネルエッチ型のトランジスタである。なお、A-Bは、トランジスタ102aのチャネル長方向、及び容量素子105aの断面図であり、C-Dにおける断面図は、トランジスタ102aのチャネル幅方向、及びゲート電極として機能する導電膜13及びゲート電極として機能する導電膜29bの接続部における断面図である。

**【0271】**

図26に示すトランジスタ102aは、デュアルゲート構造のトランジスタであり、基板11上に設けられるゲート電極として機能する導電膜13を有する。また、基板11及びゲート電極として機能する導電膜13上に形成される窒化物絶縁膜15と、窒化物絶縁膜15上に形成される酸化物絶縁膜17と、窒化物絶縁膜15及び酸化物絶縁膜17を介して、ゲート電極として機能する導電膜13と重なる酸化物半導体膜19aと、酸化物半導体膜19aに接する、ソース電極及びドレイン電極として機能する導電膜21a、21bとを有する。また、酸化物絶縁膜17、酸化物半導体膜19a、及びソース電極及びドレイン電極として機能する導電膜21a、21b上には、酸化物絶縁膜23が形成され、酸化物絶縁膜23上には酸化物絶縁膜25が形成される。窒化物絶縁膜15、酸化物絶縁膜23、酸化物絶縁膜25、導電膜21b上には窒化物絶縁膜27が形成される。また、画素電極19bが、酸化物絶縁膜17上に形成される。画素電極19bは、ソース電極及びドレイン電極として機能する導電膜21a、21bの一方、ここでは導電膜21bに接40

50

続される。また、コモン電極 29、及びゲート電極として機能する導電膜 29b が窒化物絶縁膜 27 上に形成される。

#### 【0272】

C-D における断面図に示すように、窒化物絶縁膜 15 及び窒化物絶縁膜 27 に設けられる開口部 41a において、ゲート電極として機能する導電膜 29b は、ゲート電極として機能する導電膜 13 と接続される。即ち、ゲート電極として機能する導電膜 13 及びゲート電極として機能する導電膜 29b は同電位である。

#### 【0273】

このため、トランジスタ 102a の各ゲート電極に同電位の電圧を印加することで、初期特性バラつきの低減、-GBTストレス試験の劣化の抑制及び異なるドレイン電圧におけるオン電流の立ち上がり電圧の変動の抑制が可能である。また、酸化物半導体膜 19a においてキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタ 102a のオン電流が大きくなると共に、電界効果移動度が高くなり、代表的には電界効果移動度が  $20 \text{ cm}^2 / \text{V} \cdot \text{s}$  以上となる。

10

#### 【0274】

本実施の形態に示すトランジスタ 102a 上には分離された酸化物絶縁膜 23、25 が形成される。分離された酸化物絶縁膜 23、25 が酸化物半導体膜 19a と重畠する。また、チャネル幅方向の断面図において、酸化物半導体膜 19a の外側に酸化物絶縁膜 23 及び酸化物絶縁膜 25 の端部が位置する。また、図 26 に示すチャネル幅方向において、ゲート電極として機能する導電膜 29b は、酸化物絶縁膜 23 及び酸化物絶縁膜 25 を介して、酸化物半導体膜 19a の側面と対向する。

20

#### 【0275】

エッティング等で加工された酸化物半導体膜の端部においては、加工におけるダメージにより欠陥が形成されると共に、不純物付着などにより汚染される。このため、酸化物半導体膜の端部は、電界などのストレスが与えられることによって活性化しやすく、それにより n 型（低抵抗）となりやすい。そのため、ゲート電極として機能する導電膜 13 と重なる酸化物半導体膜 19a の端部において、n 型化しやすくなる。当該 n 型化された端部が、ソース電極及びドレイン電極として機能する導電膜 21a、21b の間に設けられるとなれば、n 型化された領域がキャリアのパスとなってしまい、寄生チャネルが形成される。しかしながら、C-D の断面図に示すように、チャネル幅方向において、ゲート電極として機能する導電膜 29b が、酸化物絶縁膜 23、25 を介して、酸化物半導体膜 19a の側面と対向すると、ゲート電極として機能する導電膜 29b の電界の影響により、酸化物半導体膜 19a の側面、または側面及びその近傍を含む領域における寄生チャネルの発生が抑制される。この結果、しきい値電圧におけるドレイン電流の上昇が急峻である、電気特性の優れたトランジスタとなる。

30

#### 【0276】

また、容量素子 105a において、画素電極 19b は、酸化物半導体膜 19a と一緒に形成された膜であり、且つ不純物を含むことにより導電性が高められた膜である。または、画素電極 19b は、酸化物半導体膜 19a と一緒に形成された膜であり、プラズマダメージ等により酸素欠損が形成され、導電性が高められた膜である。または、画素電極 19b は、酸化物半導体膜 19a と一緒に形成された膜であり、且つ不純物を含むと共に、プラズマダメージ等により酸素欠損が形成され、導電性が高められた膜である。

40

#### 【0277】

本実施の形態に示す表示装置の素子基板は、トランジスタの酸化物半導体膜と一緒に、画素電極が形成される。画素電極は容量素子の一方の電極として機能する。また、コモン電極は容量素子の他方の電極として機能する。これらのため、容量素子を形成するために、新たに導電膜を形成する工程が不要であり、作製工程を削減できる。また、容量素子は透光性を有する。この結果、容量素子の占有面積を大きくしつつ、画素の開口率を高めることができる。

#### 【0278】

50

以下に、トランジスタ 102a の構成の詳細について説明する。なお、実施の形態 2 と同じ符号の構成については、説明を省略する。

#### 【0279】

ゲート電極として機能する導電膜 29b は、実施の形態 2 に示すコモン電極 29 と同様の材料を適宜用いることができる。

#### 【0280】

次に、図 26 に示すトランジスタ 102a 及び容量素子 105a の作製方法について、図 10 乃至図 12 (A)、及び図 27 を用いて説明する。

#### 【0281】

実施の形態 2 と同様に、図 10 乃至図 12 (A) の工程を経て、基板 11 上にゲート電極として機能する導電膜 13、窒化物絶縁膜 15、酸化物絶縁膜 16、酸化物半導体膜 19a、画素電極 19b、ソース電極及びドレイン電極として機能する導電膜 21a、21b、酸化物絶縁膜 22、酸化物絶縁膜 24、及び窒化物絶縁膜 26 をそれぞれ形成する。

当該工程においては、第 1 のフォトマスク乃至第 4 のフォトマスクを用いたフォトリソグラフィ工程を行う。

#### 【0282】

次に、窒化物絶縁膜 26 上に第 5 のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成した後、該マスクを用いて窒化物絶縁膜 26 の一部をエッティングして、図 27 (A) に示すように、開口部 41a 及び 41b を有する窒化物絶縁膜 27 を形成する。

20

#### 【0283】

次に、図 27 (B) に示すように、ゲート電極として機能する導電膜 13、導電膜 21b、及び窒化物絶縁膜 27 上に、後にコモン電極 29、ゲート電極として機能する導電膜 29b となる導電膜 28 を形成する。

#### 【0284】

次に、導電膜 28 上に、第 6 のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜 28 の一部をエッティングして、図 27 (C) に示すように、コモン電極 29 及びゲート電極として機能する導電膜 29b を形成する。この後、マスクを除去する。

30

#### 【0285】

以上の工程により、トランジスタ 102a を作製すると共に、容量素子 105a を作製することができる。

#### 【0286】

本実施の形態に示すトランジスタは、チャネル幅方向において、ゲート電極として機能するコモン電極 29 が、酸化物絶縁膜 23、25 を介して、酸化物半導体膜 19a の側面と対向することで、ゲート電極として機能する導電膜 29b の電界の影響により、酸化物半導体膜 19a の側面、または側面及びその近傍を含む領域における寄生チャネルの発生が抑制される。この結果、しきい値電圧におけるドレイン電流の上昇が急峻である、電気特性の優れたトランジスタとなる。

#### 【0287】

本実施の形態に示す表示装置の素子基板は、信号線と交差する方向に縞状に延伸した領域を有するコモン電極が形成される。このため、コントラストの優れた表示装置を作製することができる。

40

#### 【0288】

また、本実施の形態に示す表示装置の素子基板は、トランジスタの酸化物半導体膜と同時に、画素電極が形成される。画素電極は容量素子の一方の電極として機能する。また、コモン電極は、容量素子の他方の電極として機能する。これらのため、容量素子を形成するために、新たに導電膜を形成する工程が不要であり、作製工程を削減できる。また、容量素子は透光性を有する。この結果、容量素子の占有面積を大きくしつつ、画素の開口率を高めることができる。

50

## 【0289】

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

## 【0290】

## (実施の形態6)

本実施の形態では、上記実施の形態と比較して、酸化物半導体膜の欠陥量をさらに低減することが可能なトランジスタを有する表示装置について図面を参照して説明する。本実施の形態で説明するトランジスタは、実施の形態2乃至実施の形態5と比較して、複数の酸化物半導体膜を有する多層膜を有する点が異なる。ここでは、実施の形態2を用いて、トランジスタの詳細を説明する。

10

## 【0291】

図16に、表示装置が有する素子基板の断面図を示す。図16は、図6の一点鎖線A-B、C-D間の断面図に相当する。

## 【0292】

図16(A)に示すトランジスタ102bは、窒化物絶縁膜15及び酸化物絶縁膜17を介して、ゲート電極として機能する導電膜13と重なる多層膜37aと、多層膜37aに接するソース電極及びドレイン電極として機能する導電膜21a、21bとを有する。また、窒化物絶縁膜15及び酸化物絶縁膜17、多層膜37a、及びソース電極及びドレイン電極として機能する導電膜21a、21b上には、酸化物絶縁膜23、酸化物絶縁膜25、及び窒化物絶縁膜27が形成される。

20

## 【0293】

図16(A)に示す容量素子105bは、酸化物絶縁膜17上に形成される多層膜37bと、多層膜37bに接する窒化物絶縁膜27と、窒化物絶縁膜27に接するコモン電極29とを有する。多層膜37bは画素電極として機能する。

## 【0294】

本実施の形態に示すトランジスタ102bにおいて、多層膜37aは、酸化物半導体膜19a及び酸化物半導体膜39aを有する。即ち、多層膜37aは2層構造である。また、酸化物半導体膜19aの一部がチャネル領域として機能する。また、多層膜37aに接するように、酸化物絶縁膜23が形成されており、酸化物絶縁膜23に接するように酸化物絶縁膜25が形成されている。即ち、酸化物半導体膜19aと酸化物絶縁膜23との間に、酸化物半導体膜39aが設けられている。

30

## 【0295】

酸化物半導体膜39aは、酸化物半導体膜19aを構成する元素の一種以上から構成される酸化物膜である。このため、酸化物半導体膜19aと酸化物半導体膜39aとの界面において、界面散乱が起こりにくい。従って、該界面においてはキャリアの動きが阻害されないため、トランジスタの電界効果移動度が高くなる。

## 【0296】

酸化物半導体膜39aは、代表的には、In-Ga酸化物膜、In-Zn酸化物膜、In-M-Zn酸化物膜(Mは、Al、Ga、Y、Zr、Sn、La、Ce、またはNd)であり、且つ酸化物半導体膜19aよりも伝導帯の下端のエネルギーが真空準位に近く、代表的には、酸化物半導体膜39aの伝導帯の下端のエネルギーと、酸化物半導体膜19aの伝導帯の下端のエネルギーとの差が、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上、且つ2eV以下、1eV以下、0.5eV以下、または0.4eV以下である。即ち、酸化物半導体膜39aの電子親和力と、酸化物半導体膜19aの電子親和力との差が、0.05eV以上、0.07eV以上、0.1eV以上、または0.15eV以上、且つ2eV以下、1eV以下、0.5eV以下、または0.4eV以下である。

40

## 【0297】

酸化物半導体膜39aは、Inを含むことで、キャリア移動度(電子移動度)が高くなるため好ましい。

50

## 【0298】

酸化物半導体膜39aとして、Al、Ga、Y、Zr、Sn、La、Ce、またはNdをInより高い原子数比で有することで、以下の効果を有する場合がある。(1)酸化物半導体膜39aのエネルギーギャップを大きくする。(2)酸化物半導体膜39aの電子親和力を小さくする。(3)外部からの不純物の拡散を低減する。(4)酸化物半導体膜19aと比較して、絶縁性が高くなる。(5)Al、Ga、Y、Zr、Sn、La、Ce、またはNdは、酸素との結合力が強い金属元素であるため、酸素欠損が生じにくくなる。

## 【0299】

酸化物半導体膜39aがIn-M-Zn酸化物膜であるとき、InおよびMの和を100atomic%としたとき、InとMの原子数比率は、Inが50atomic%未満、Mが50atomic%より高く、さらに好ましくは、Inが25atomic%未満、Mが75atomic%より高くとする。

## 【0300】

また、酸化物半導体膜19a及び酸化物半導体膜39aが、In-M-Zn酸化物膜(MAl、Ga、Y、Zr、Sn、La、Ce、またはNd)の場合、酸化物半導体膜19aと比較して、酸化物半導体膜39aに含まれるM(Al、Ga、Y、Zr、Sn、La、Ce、またはNd)の原子数比が大きく、代表的には、酸化物半導体膜19aに含まれる上記原子と比較して、1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比である。

## 【0301】

また、酸化物半導体膜19a及び酸化物半導体膜39aが、In-M-Zn酸化物膜(MはAl、Ga、Y、Zr、Sn、La、Ce、またはNd)の場合、酸化物半導体膜39aを $In : M : Zn = x_1 : y_1 : z_1$  [原子数比]、酸化物半導体膜19aを $In : M : Zn = x_2 : y_2 : z_2$  [原子数比]とすると、 $y_1 / x_1$ が $y_2 / x_2$ よりも大きく、好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも1.5倍以上である。さらに好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも2倍以上大きく、より好ましくは、 $y_1 / x_1$ が $y_2 / x_2$ よりも3倍以上大きい。

## 【0302】

酸化物半導体膜19aがIn-M-Zn酸化物膜(Mは、Al、Ga、Y、Zr、Sn、La、Ce、またはNd)の場合、酸化物半導体膜19aを成膜するために用いるターゲットにおいて、金属元素の原子数比を $In : M : Zn = x_1 : y_1 : z_1$ とすると、 $x_1 / y_1$ は、1/3以上6以下、さらには1以上6以下であって、 $z_1 / y_1$ は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、 $z_1 / y_1$ を1以上6以下とすることで、酸化物半導体膜19aとしてCAC-O-S膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $In : M : Zn = 1 : 1 : 1$ 、 $In : M : Zn = 1 : 1 : 1.2$ 、 $In : M : Zn = 3 : 1 : 2$ 等がある。

## 【0303】

酸化物半導体膜39aがIn-M-Zn酸化物膜(Mは、Al、Ga、Y、Zr、Sn、La、Ce、またはNd)の場合、酸化物半導体膜39aを成膜するために用いるターゲットにおいて、金属元素の原子数比を $In : M : Zn = x_2 : y_2 : z_2$ とすると、 $x_2 / y_2 < x_1 / y_1$ であって、 $z_2 / y_2$ は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、 $z_2 / y_2$ を1以上6以下とすることで、酸化物半導体膜39aとしてCAC-O-S膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $In : M : Zn = 1 : 3 : 2$ 、 $In : M : Zn = 1 : 3 : 4$ 、 $In : M : Zn = 1 : 3 : 6$ 、 $In : M : Zn = 1 : 3 : 8$ 、 $In : M : Zn = 1 : 4 : 4$ 、 $In : M : Zn = 1 : 4 : 5$ 、 $In : M : Zn = 1 : 6 : 8$ 等がある。

## 【0304】

なお、酸化物半導体膜19a及び酸化物半導体膜39aの原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス40%の変動を含む。

10

20

30

40

50

**【0305】**

酸化物半導体膜39aは、後に形成する酸化物絶縁膜25を形成する際の、酸化物半導体膜19aへのダメージ緩和膜としても機能する。

**【0306】**

酸化物半導体膜39aの厚さは、3nm以上100nm以下、好ましくは3nm以上50nm以下とする。

**【0307】**

また、酸化物半導体膜39aは、酸化物半導体膜19aと同様に、例えば非単結晶構造でもよい。非単結晶構造は、例えば、後述するCAAC-OS(C Axis Aligned Crystaline Oxide Semiconductor)、多結晶構造、後述する微結晶構造、または非晶質構造を含む。

10

**【0308】**

酸化物半導体膜39aは、例えば非晶質構造でもよい。非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

**【0309】**

なお、酸化物半導体膜19a及び酸化物半導体膜39aそれぞれにおいて、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAC-OSの領域、及び単結晶構造の二種以上の領域を有する混合膜を構成してもよい。混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAC-OSの領域、単結晶構造の領域のいずれか二種以上の領域を有する単層構造の場合がある。また、混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAC-OSの領域、単結晶構造の領域のいずれか二種以上の領域が積層した積層構造を有する場合がある。

20

**【0310】**

ここでは、酸化物半導体膜19a及び酸化物絶縁膜23の間に、酸化物半導体膜39aが設けられている。このため、酸化物半導体膜39aと酸化物絶縁膜23の間ににおいて、不純物及び欠陥によりキャリアトラップが形成されても、当該キャリアトラップと酸化物半導体膜19aとの間には隔たりがある。この結果、酸化物半導体膜19aを流れる電子がキャリアトラップに捕獲されにくく、トランジスタのオン電流を増大させることができると共に、電界効果移動度を高めることができる。また、キャリアトラップに電子が捕獲されると、該電子がマイナスの固定電荷となってしまう。この結果、トランジスタのしきい値電圧が変動してしまう。しかしながら、酸化物半導体膜19aとキャリアトラップとの間に隔たりがあるため、キャリアトラップにおける電子の捕獲を削減することができる、しきい値電圧の変動量を低減することができる。

30

**【0311】**

また、酸化物半導体膜39aは、外部からの不純物を遮蔽することができるため、外部から酸化物半導体膜19aへ移動する不純物量を低減することができる。また、酸化物半導体膜39aは、酸素欠損を形成しにくい。これらのため、酸化物半導体膜19aにおける不純物濃度及び酸素欠損量を低減することができる。

**【0312】**

なお、酸化物半導体膜19a及び酸化物半導体膜39aは、各膜を単に積層するのではなく連続接合(ここで特に伝導帯の下端のエネルギーが各膜の間で連続的に変化する構造)が形成されるように作製する。すなわち、各膜の界面に、トラップ中心や再結合中心のような欠陥準位を形成する不純物が存在しないような積層構造とする。仮に、積層された酸化物半導体膜19a及び酸化物半導体膜39aの間に不純物が混在していると、エネルギー・バンドの連続性が失われ、界面でキャリアがトラップされ、あるいは再結合して、消滅してしまう。

**【0313】**

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置(スパッタリング装置)を用いて各膜を大気に触れさせることなく連続して積層するこ

50

とが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体膜にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa 乃至  $1 \times 10^{-4}$  Pa 程度まで）することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体、特に炭素または水素を含む気体が逆流しないようにしておくことが好ましい。

#### 【0314】

なお、多層膜 37a の代わりに、図 16 (B) に示すトランジスタ 102c のように、多層膜 38a を有してもよい。

#### 【0315】

また、多層膜 37b の代わりに、図 16 (B) に示す容量素子 105c のように、多層膜 38b を有してもよい。

#### 【0316】

多層膜 38a は、酸化物半導体膜 49a、酸化物半導体膜 19a、及び酸化物半導体膜 39a を有する。即ち、多層膜 38a は 3 層構造である。また、酸化物半導体膜 19a がチャネル領域として機能する。

#### 【0317】

酸化物半導体膜 49a は、酸化物半導体膜 39a と同様の材料及び形成方法を適宜用いることができる。

#### 【0318】

多層膜 38b は、酸化物半導体膜 49b、酸化物半導体膜 19f、及び酸化物半導体膜 39b を有する。即ち、多層膜 38b は 3 層構造である。また、多層膜 38b は画素電極として機能する。

#### 【0319】

酸化物半導体膜 19f は、画素電極 19b と同様の材料及び形成方法を適宜用いることができる。酸化物半導体膜 49b は、酸化物半導体膜 39b と同様の材料及び形成方法を適宜用いることができる。

#### 【0320】

また、酸化物絶縁膜 17 及び酸化物半導体膜 49a が接する。即ち、酸化物絶縁膜 17 と酸化物半導体膜 19aとの間に、酸化物半導体膜 49a が設けられている。

#### 【0321】

また、多層膜 38a 及び酸化物絶縁膜 23 が接する。また、酸化物半導体膜 39a 及び酸化物絶縁膜 23 が接する。即ち、酸化物半導体膜 19a と酸化物絶縁膜 23 との間に、酸化物半導体膜 39a が設けられている。

#### 【0322】

酸化物半導体膜 49a は、酸化物半導体膜 19a より膜厚が小さいと好ましい。酸化物半導体膜 49a の厚さを 1 nm 以上 5 nm 以下、好ましくは 1 nm 以上 3 nm 以下とすることで、トランジスタのしきい値電圧の変動量を低減することができる。

#### 【0323】

本実施の形態に示すトランジスタは、酸化物半導体膜 19a 及び酸化物絶縁膜 23 の間に、酸化物半導体膜 39a が設けられている。このため、酸化物半導体膜 39a と酸化物絶縁膜 23 の間ににおいて、不純物及び欠陥によりキャリアトラップが形成されても、当該キャリアトラップと酸化物半導体膜 19aとの間には隔たりがある。この結果、酸化物半導体膜 19a を流れる電子がキャリアトラップに捕獲されにくく、トランジスタのオン電流を増大させることができると共に、電界効果移動度を高めることができる。また、キャリアトラップに電子が捕獲されると、該電子がマイナスの固定電荷となってしまう。この結果、トランジスタのしきい値電圧が変動してしまう。しかしながら、酸化物半導体膜 19a とキャリアトラップとの間に隔たりがあるため、キャリアトラップにおける電子の捕獲を削減することができ、しきい値電圧の変動量を低減することができる。

#### 【0324】

10

20

30

40

50

また、酸化物半導体膜39aは、外部からの不純物を遮蔽することができるため、外部から酸化物半導体膜19aへ移動する不純物量を低減することができる。また、酸化物半導体膜39aは、酸素欠損を形成しにくい。これらのため、酸化物半導体膜19aにおける不純物濃度及び酸素欠損量を低減することができる。

#### 【0325】

また、酸化物絶縁膜17と酸化物半導体膜19aとの間に、酸化物半導体膜49aが設けられており、酸化物半導体膜19aと酸化物絶縁膜23との間に、酸化物半導体膜39aが設けられているため、酸化物半導体膜49aと酸化物半導体膜19aとの界面近傍におけるシリコンや炭素の濃度、酸化物半導体膜19aにおけるシリコンや炭素の濃度、または酸化物半導体膜39aと酸化物半導体膜19aとの界面近傍におけるシリコンや炭素の濃度を低減することができる。これらの結果、多層膜38aにおいて、一定光電流測定法で導出される吸収係数は、 $1 \times 10^{-3} / \text{cm}$ 未満、好ましくは $1 \times 10^{-4} / \text{cm}$ 未満となり、局在準位が極めて少ない。10

#### 【0326】

このような構造を有するトランジスタ102cは、酸化物半導体膜19aを含む多層膜38aにおいて欠陥が極めて少ないと、トランジスタの電気特性を向上させることができ、代表的には、オン電流の増大及び電界効果移動度の向上が可能である。また、ストレス試験の一例であるBTストレス試験及び光BTストレス試験におけるしきい値電圧の変動量が少なく、信頼性が高い。20

#### 【0327】

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

#### 【0328】

##### (実施の形態7)

本実施の形態では、上記実施の形態で説明した表示装置に含まれているトランジスタにおいて、酸化物半導体膜に適用可能な一態様について説明する。

#### 【0329】

酸化物半導体膜は、単結晶構造の酸化物半導体（以下、単結晶酸化物半導体という。）、多結晶構造の酸化物半導体（以下、多結晶酸化物半導体という。）、微結晶構造の酸化物半導体（以下、微結晶酸化物半導体という。）及び非晶質構造の酸化物半導体（以下、非晶質酸化物半導体という。）の一以上で構成されてもよい。また、酸化物半導体膜は、CAAC-OS膜で構成されていてもよい。また、酸化物半導体膜は、非晶質酸化物半導体及び結晶粒を有する酸化物半導体で構成されていてもよい。以下に、代表例として、CAAC-OS及び微結晶酸化物半導体について説明する。30

#### 【0330】

##### <CAAC-OS>

CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つである。また、CAAC-OS膜に含まれる結晶部は、c軸配向性を有する。平面TEM像において、CAAC-OS膜に含まれる結晶部の面積が $2500 \text{ nm}^2$ 以上、さらに好ましくは $5 \mu\text{m}^2$ 以上、さらに好ましくは $1000 \mu\text{m}^2$ 以上である。また、断面TEM像において、該結晶部を50%以上、好ましくは80%以上、さらに好ましくは95%以上有することで、単結晶に近い物性の薄膜となる。40

#### 【0331】

CAAC-OS膜を透過型電子顕微鏡（TEM：Transmission Electron Microscope）によって観察すると、結晶部同士の明確な境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することが困難である。そのため、CAAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0332】

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察（断面TEM観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原50

子の各層は、 C A A C - O S 膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、 C A A C - O S 膜の被形成面または上面と平行に配列する。なお、本明細書において、「平行」とは、二つの直線が - 10° 以上 10° 以下の角度で配置されている状態をいう。従って、 - 5° 以上 5° 以下の場合も含まれる。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。従って、 85° 以上 95° 以下の場合も含まれる。

#### 【 0 3 3 3 】

一方、 C A A C - O S 膜を、試料面と概略垂直な方向から T E M によって観察（平面 T E M 観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

10

#### 【 0 3 3 4 】

なお、 C A A C - O S 膜に対し、電子線回折を行うと、配向性を示すスポット（輝点）が観測される。

#### 【 0 3 3 5 】

断面 T E M 観察及び平面 T E M 観察より、 C A A C - O S 膜の結晶部は配向性を有していることがわかる。

#### 【 0 3 3 6 】

C A A C - O S 膜に対し、X線回折（ X R D : X - R a y D i f f r a c t i o n ）装置を用いて構造解析を行うと、 C A A C - O S 膜の out-of-plane 法による解析では、回折角（ 2θ ）が 31° 近傍にピークが現れる場合がある。このピークは、 I n - G a - Z n 酸化物の結晶の（ 00x ）面（ x は整数）に帰属されることから、 C A A C - O S 膜の結晶が c 軸配向性を有し、 c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

20

#### 【 0 3 3 7 】

一方、 C A A C - O S 膜に対し、 c 軸に概略垂直な方向から X 線を入射させる in - plane 法による解析では、 2θ が 56° 近傍にピークが現れる場合がある。このピークは、 I n - G a - Z n 酸化物の結晶の（ 110 ）面に帰属される。 I n - G a - Z n 酸化物の単結晶酸化物半導体膜であれば、 2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸（ c 軸）として試料を回転させながら分析（スキャン）を行うと、（ 110 ）面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、 C A A C - O S 膜の場合は、 2θ を 56° 近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

30

#### 【 0 3 3 8 】

以上のことから、 C A A C - O S 膜では、異なる結晶部間では a 軸及び b 軸の配向は不規則であるが、 c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 T E M 観察で確認された層状に配列した金属原子の各層は、結晶の a - b 面に平行な面である。

#### 【 0 3 3 9 】

なお、結晶は、 C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、 C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、 C A A C - O S 膜の形状をエッチングなどによって変化させた場合、結晶の c 軸が C A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

40

#### 【 0 3 4 0 】

また、 C A A C - O S 膜中の結晶化度が均一でなくてもよい。例えば、 C A A C - O S 膜の結晶部が、 C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、 C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

#### 【 0 3 4 1 】

10

20

30

40

50

なお、 C A A C - O S 膜の out - of - plane 法による解析では、 2 $\theta$  が 31°。近傍のピークの他に、 2 $\theta$  が 36°。近傍にもピークが現れる場合がある。 2 $\theta$  が 36°。近傍のピークは、 C A A C - O S 膜中の一部に、 c 軸配向性を有さない結晶部が含まれることを示している。 C A A C - O S 膜は、 2 $\theta$  が 31°。近傍にピークを示し、 2 $\theta$  が 36°。近傍にピークを示さないことが好ましい。

#### 【 0342 】

C A A C - O S 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。10

#### 【 0343 】

また、 C A A C - O S 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【 0344 】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損量の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができます。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。2030

#### 【 0345 】

また、 C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【 0346 】

##### < 微結晶酸化物半導体 >

微結晶酸化物半導体膜は、 T E M による観察像では、明確に結晶部を確認することが困難な場合がある。微結晶酸化物半導体膜に含まれる結晶部は、 1 nm 以上 100 nm 以下、または 1 nm 以上 10 nm 以下の大きさであることが多い。特に、 1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の微結晶であるナノ結晶 ( n c : n a n o c r y s t a l ) を有する酸化物半導体膜を、 n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 膜と呼ぶ。また、 n c - O S 膜は、例えば、 T E M による観察像では、結晶粒界を明確に確認することが困難な場合がある。40

#### 【 0347 】

n c - O S 膜は、微小な領域（例えば、 1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、 n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。従って、 n c - O S 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、 n c - O S 膜に対し、結晶部よりも大きい径の X 線を用いる X R D 装置を用いて構造解析を行うと、 out - of - plane 法による解析では、結晶面を示すピークが検出されない。また、 n c - O S 膜に対し、結晶部よりも大きいプローブ径50

(例えば 50 nm 以上) の電子線を用いる電子線回折 (制限視野電子線回折ともいう。) を行うと、ハローパターンのような回折パターンが観測される。一方、n<sub>c</sub>-OS 膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径 (例えば 1 nm 以上 30 nm 以下) の電子線を用いる電子線回折 (ナノビーム電子線回折ともいう。) を行うと、スポットが観測される。また、n<sub>c</sub>-OS 膜に対しナノビーム電子線回折を行うと、円を描くように (リング状に) 輝度の高い領域が観測される場合がある。また、n<sub>c</sub>-OS 膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

#### 【0348】

n<sub>c</sub>-OS 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。

そのため、n<sub>c</sub>-OS 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、n<sub>c</sub>-OS 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n<sub>c</sub>-OS 膜は、CACAC-OS 膜と比べて欠陥準位密度が高くなる。

10

#### 【0349】

<酸化物半導体膜及び酸化物導電体膜>

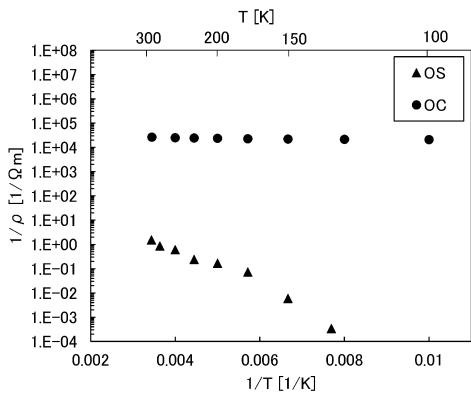

次に、酸化物半導体で形成される膜 (以下、酸化物半導体膜 (OS) という。) 及び画素電極 19b として用いることが可能な酸化物導電体で形成される膜 (以下、酸化物導電体膜 (OC) という。) それぞれにおける、導電率の温度依存性について、図 38 を用いて説明する。図 38 において、横軸に測定温度 (下横軸は 1/T、上横軸は T) を示し、縦軸に導電率 (1/T) を示す。また、酸化物半導体膜 (OS) の測定結果を三角印で示し、酸化物導電体膜 (OC) の測定結果を丸印で示す。

20

#### 【0350】

なお、酸化物半導体膜 (OS) を含む試料は、ガラス基板上に、原子数比が In : Ga : Zn = 1 : 1 : 1.2 のスパッタリングターゲットを用いたスパッタリング法により厚さ 35 nm の In-Ga-Zn 酸化物膜を形成し、原子数比が In : Ga : Zn = 1 : 4 : 5 のスパッタリングターゲットを用いたスパッタリング法により厚さ 20 nm の In-Ga-Zn 酸化物膜を形成し、450 の窒素雰囲気で加熱処理した後、450 の窒素及び酸素の混合ガス雰囲気で加熱処理し、さらにプラズマ CVD 法で酸化窒化シリコン膜を形成して、作製された。

#### 【0351】

また、酸化物導電体膜 (OC) を含む試料は、ガラス基板上に、原子数比が In : Ga : Zn = 1 : 1 : 1 のスパッタリングターゲットを用いたスパッタリング法により厚さ 100 nm の In-Ga-Zn 酸化物膜を形成し、450 の窒素雰囲気で加熱処理した後、450 の窒素及び酸素の混合ガス雰囲気で加熱処理し、プラズマ CVD 法で窒化シリコン膜を形成して、作製された。

30

#### 【0352】

図 38 からわかるように、酸化物導電体膜 (OC) における導電率の温度依存性は、酸化物半導体膜 (OS) における導電率の温度依存性より小さい。代表的には、80 K 以上 290 K 以下における酸化物導電体膜 (OC) の導電率の変化率は、±20% 未満である。または、150 K 以上 250 K 以下における導電率の変化率は、±10% 未満である。即ち、酸化物導電体は、縮退半導体であり、伝導帯端とフェルミ準位とが一致または略一致していると推定される。このため、酸化物導電体膜を、抵抗素子、配線、電極、画素電極、コモン電極等に用いることが可能である。

40

#### 【0353】

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。

#### 【0354】

(実施の形態 8)

実施の形態 2 で述べたように、酸化物半導体膜を用いたトランジスタは、オフ状態における電流値 (オフ電流値) を低く制御することができる。よって、画像信号等の電気信号

50

の保持時間を長くすることができ、書き込み間隔も長く設定できる。

#### 【0355】

本実施の形態の液晶表示装置は、オフ電流値の低いトランジスタを適用することで、少なくとも2つの駆動方法（モード）で表示を行う液晶表示装置とすることができます。第1の駆動モードは、従来の液晶表示装置の駆動方法であり、1フレームごとにデータを逐次書き換える駆動方法である。第2の駆動モードは、データの書き込み処理を実行した後、データの書き換えを停止する駆動方法である。すなわち、リフレッシュレートを低減した駆動モードである。

#### 【0356】

動画の表示は、第1の駆動モードにより行われる。静止画の表示は、フレームごとの画像データに変化がないため、1フレームごとにデータの書き換えを行う必要がない。そこで、静止画を表示する際は、第2の駆動モードで動作させると、画面のちらつきをなくすとともに、電力消費を削減することができる。10

#### 【0357】

また、本実施の形態の液晶表示装置に適用される液晶素子は、面積の大きい容量素子を有し、容量素子で蓄積する電荷容量が大きい。このため、画素電極の電位を保持する時間を長くすることが可能であり、リフレッシュレートを低減する駆動モードを適用できる。さらに、液晶表示装置においてリフレッシュレートを低減する駆動モードを適用した場合であっても、液晶層に印加された電圧の変化を長期間抑制することが可能であるため、使用者による画像のちらつきの知覚をより防止することができる。したがって、低消費電力化と表示品質の向上を図ることができる。20

#### 【0358】

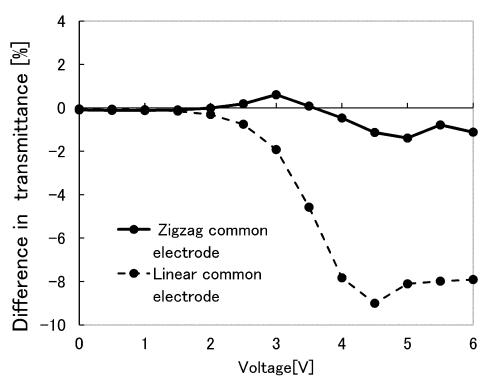

ここで、リフレッシュレートを低減する効果に関して説明する。