## INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

|                                                                                                                                                                                                               |    |                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------|

| (51) International Patent Classification <sup>6</sup> :<br><br>H02M 1/08                                                                                                                                      | A2 | (11) International Publication Number: <b>WO 98/49765</b><br><br>(43) International Publication Date: 5 November 1998 (05.11.98) |

| (21) International Application Number: PCT/IB98/00351                                                                                                                                                         |    | (81) Designated States: JP, European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).                |

| (22) International Filing Date: 16 March 1998 (16.03.98)                                                                                                                                                      |    |                                                                                                                                  |

| (30) Priority Data:<br>08/845,745 25 April 1997 (25.04.97) US                                                                                                                                                 |    | Published<br><i>Without international search report and to be republished upon receipt of that report.</i>                       |

| (71) Applicant: KONINKLIJKE PHILIPS ELECTRONICS N.V.<br>[NL/NL]; Groenewoudseweg 1, NL-5621 BA Eindhoven<br>(NL).                                                                                             |    |                                                                                                                                  |

| (71) Applicant (for SE only): PHILIPS AB [SE/SE]; Kottbygatan 7,<br>Kista, S-164 85 Stockholm (SE).                                                                                                           |    |                                                                                                                                  |

| (72) Inventors: MAJID, Naveed; Prof. Holstlaan 6, NL-5656<br>AA Eindhoven (NL). MELSE, Bram; Prof. Holstlaan<br>6, NL-5656 AA Eindhoven (NL). SEINEN, Erwin; Prof.<br>Holstlaan 6, NL-5656 AA Eindhoven (NL). |    |                                                                                                                                  |

| (74) Agent: HESSELMANN, Gerardus, J., M.; Internationaal<br>Ostrooibureau B.V., P.O. Box 220, NL-5600 AE Eindhoven<br>(NL).                                                                                   |    |                                                                                                                                  |

## (54) Title: OVERVOLTAGE PROTECTION CIRCUIT FOR SMPS BASED ON DEMAGNETIZATION SIGNAL

## (57) Abstract

An overvoltage protection circuit is provided for a switched-mode power supply of the type having a transformer (21) and a switching transistor (64) coupled in series with a primary winding (56) of the transformer (21). The overvoltage protection circuit includes a sensing resistor (74) having a first terminal directly connected to a sensing winding (20) for generating a current proportional to the voltage across the sensing winding (20), with a second terminal of this resistor being coupled to an input of a current mirror (78). The reflected current output of the current mirror (78) is compared to an overvoltage reference current generated by an overvoltage reference current source (88) by means of a current comparator (92), and a circuit (38) is provided to generate a signal to turn off the switching transistor (64) when the reflected current exceeds the overvoltage reference current. Such an overvoltage protection circuit provides fast, efficient and accurate overvoltage protection for the switched-mode power supply.

***FOR THE PURPOSES OF INFORMATION ONLY***

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

|    |                          |    |                                       |    |                                           |    |                          |

|----|--------------------------|----|---------------------------------------|----|-------------------------------------------|----|--------------------------|

| AL | Albania                  | ES | Spain                                 | LS | Lesotho                                   | SI | Slovenia                 |

| AM | Armenia                  | FI | Finland                               | LT | Lithuania                                 | SK | Slovakia                 |

| AT | Austria                  | FR | France                                | LU | Luxembourg                                | SN | Senegal                  |

| AU | Australia                | GA | Gabon                                 | LV | Latvia                                    | SZ | Swaziland                |

| AZ | Azerbaijan               | GB | United Kingdom                        | MC | Monaco                                    | TD | Chad                     |

| BA | Bosnia and Herzegovina   | GE | Georgia                               | MD | Republic of Moldova                       | TG | Togo                     |

| BB | Barbados                 | GH | Ghana                                 | MG | Madagascar                                | TJ | Tajikistan               |

| BE | Belgium                  | GN | Guinea                                | MK | The former Yugoslav Republic of Macedonia | TM | Turkmenistan             |

| BF | Burkina Faso             | GR | Greece                                | ML | Mali                                      | TR | Turkey                   |

| BG | Bulgaria                 | HU | Hungary                               | MN | Mongolia                                  | TT | Trinidad and Tobago      |

| BJ | Benin                    | IE | Ireland                               | MR | Mauritania                                | UA | Ukraine                  |

| BR | Brazil                   | IL | Israel                                | MW | Malawi                                    | UG | Uganda                   |

| BY | Belarus                  | IS | Iceland                               | MX | Mexico                                    | US | United States of America |

| CA | Canada                   | IT | Italy                                 | NE | Niger                                     | UZ | Uzbekistan               |

| CF | Central African Republic | JP | Japan                                 | NL | Netherlands                               | VN | Viet Nam                 |

| CG | Congo                    | KE | Kenya                                 | NO | Norway                                    | YU | Yugoslavia               |

| CH | Switzerland              | KG | Kyrgyzstan                            | NZ | New Zealand                               | ZW | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP | Democratic People's Republic of Korea | PL | Poland                                    |    |                          |

| CM | Cameroon                 | KR | Republic of Korea                     | PT | Portugal                                  |    |                          |

| CN | China                    | KZ | Kazakhstan                            | RO | Romania                                   |    |                          |

| CU | Cuba                     | LC | Saint Lucia                           | RU | Russian Federation                        |    |                          |

| CZ | Czech Republic           | LI | Liechtenstein                         | SD | Sudan                                     |    |                          |

| DE | Germany                  | LK | Sri Lanka                             | SE | Sweden                                    |    |                          |

| DK | Denmark                  | LR | Liberia                               | SG | Singapore                                 |    |                          |

Overvoltage protection circuit for SMPS based on demagnetization signal.

## BACKGROUND OF THE INVENTION

The invention is in the field of power supply protection circuits, and relates more particularly to an overvoltage protection circuit, for a switched-mode power supply of the type having a transformer and a switching transistor coupled in series with a winding of 5 the transformer.

Such an overvoltage protection circuit is known from U.S. Patent No. 5,313,381.

Switched-mode power supplies are well known in the art, and are typically used to obtain good regulation (due to switched feedback) as well as efficient and economical 10 filtering, since smaller-value filtering components can be used because of the typically higher operating frequency of the switched-mode supply.

In switched-mode power supplies, it is desirable to provide overvoltage protection to prevent the power supply output from exceeding a predetermined maximum value, thus preventing circuit malfunction and possible damage to circuitry powered by the 15 switched-mode power supply.

In prior-art overvoltage protection circuits, such as the overvoltage protection circuit incorporated into the Motorola MC44603 power supply controller IC and illustrated in Fig. 44 on page 22 of the Motorola Technical Data Sheet for this device, a filtered DC voltage ( $V_{CC}$ ) is sensed by a resistive divider, then compared to a voltage reference level by 20 a voltage comparator, the output of which is fed to a circuit which generates a signal that serves to turn off a switching transistor within the switched-mode power supply, thus causing the output voltage to drop below the overvoltage protection level. A similar circuit is shown 25 in Fig. 1 of U.S. Patent No. 5,313,381.

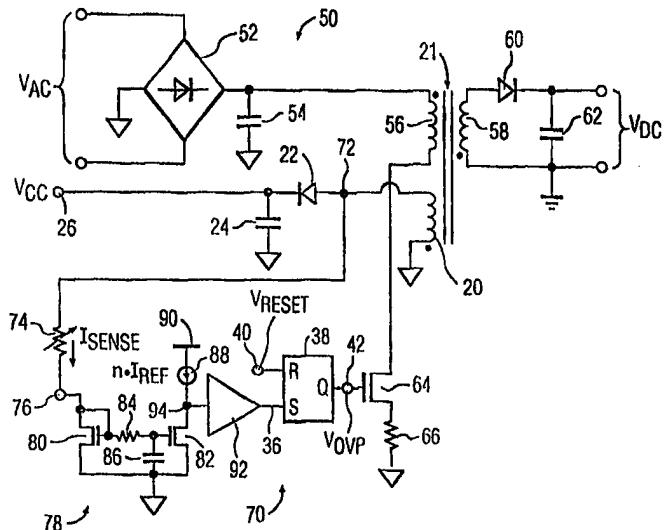

A prior-art overvoltage protection circuit of this general type is shown in 25 simplified form in Fig. 1. In Fig. 1, an overvoltage protection circuit 10 senses an auxiliary power supply voltage  $V_{CC}$  which is generated from an AC voltage taken from an auxiliary winding 20 of a power supply transformer 21, which, in the simplified embodiment shown, is rectified by a diode 22 and filtered by a filter capacitor 24 to produce the voltage  $V_{CC}$  at terminal 26. Voltage  $V_{CC}$  is sensed by a resistive divider composed of resistors 28 and 30,

with a scaled-down voltage proportional to  $V_{CC}$  being coupled to the noninverting (+) input of a voltage comparator 32. The inverting (-) input of voltage comparator 32, at the terminal 34, is provided with a voltage reference signal  $V_{REF}$ . The output of voltage comparator 32, on line 36, is connected to the Set input (S) of a circuit, such as the latch circuit 38 shown 5 here, for providing an overvoltage indicator signal  $V_{OVP}$  at the output (Q) of the latch circuit at terminal 42. In order to restore the power supply circuit to its normal operating condition, a reset signal  $V_{RESET}$  is applied to Reset (R) terminal 40 of the latch circuit 38.

The prior-art circuit of Fig. 1 operates by sensing the rectified, filtered voltage  $V_{CC}$ , stepping this voltage down using a resistive voltage divider composed of resistors 28 and 30, and feeding this stepped-down voltage to the noninverting input of comparator 32. The inverting input 34 of the comparator is provided with a voltage reference signal  $V_{REF}$ , with the attenuation ratio of the resistive voltage divider and the value of the  $V_{REF}$  selected such that the comparator output 36 trips at a voltage which exceeds the nominal value of  $V_{CC}$  by a selected amount. When the comparator 32 trips, latch 38 is set and an overvoltage 15 protection signal  $V_{OVP}$  is generated on terminal 42. This signal is provided to a switching transistor (such as transistor 40 in Fig. 1 of U.S. Patent No. 5,313,381) which is coupled in series with the primary winding of the switched-mode power supply transformer to inhibit switching and thereby reduce the output voltage of the power supply. When the power supply output returns to an acceptable level, latch 38 is reset by a signal  $V_{RESET}$  at reset 20 terminal 40 and the circuit returns to its normal mode of operation.

Although the circuit of Fig. 1 provides adequate overvoltage protection, it suffers from several drawbacks. Since this overvoltage protection circuit senses the voltage across capacitor 24, typically a large capacitor which will charge and discharge relatively slowly, the overvoltage protection circuit will inherently be slow to recognize an overvoltage 25 condition due to increased transformer voltage. Additionally, since  $V_{CC}$  can vary by as much as 30 percent from its nominal value due to such factors as transformer winding ratio tolerances, the voltage fed to the noninverting input of voltage comparator 32, which is a scaled-down version of  $V_{CC}$ , can have a similar percentage variation, thus rendering the circuit relatively inaccurate.

Accordingly, it would be desirable to have an overvoltage protection circuit for 30 a switched-mode power supply which is both faster and more accurate than existing overvoltage protection circuits.

## SUMMARY OF THE INVENTION

It is therefore an object of the invention to provide an overvoltage protection circuit for a switched-mode power supply which is capable of operating faster than prior-art circuits and which also offers improved accuracy with respect to prior-art circuits.

In accordance with the invention, these objects are achieved by a new

5 overvoltage protection circuit for a switched-mode power supply which is characterized in that the overvoltage protection circuit comprises a sensing resistor having a first terminal directly connected to a sensing winding of the transformer for generating a current in said sensing resistor proportional to the voltage across said sensing winding and a second terminal, a current mirror, said second resistor terminal being coupled to an input of said

10 current mirror, an overvoltage reference current source coupled to an output of said current mirror, a current comparator for comparing a reflected current from said current mirror proportional to said sensing current in said sensing resistor to an overvoltage reference current generated by said overvoltage reference current source, and circuit means for generating a signal to turn off said switching transistor when said reflected current exceeds

15 said overvoltage reference current.

In a preferred embodiment of the invention, the sensing resistor is a variable resistor, so that current generated therein can be adjusted to compensate for variations due to such factors as transformer winding ratio tolerances.

In a further preferred embodiment of the invention, the current mirror is

20 provided with a delay circuit so that the overvoltage protection circuit will not be overly sensitive to a highly transient overvoltage condition.

In yet a further preferred embodiment of the invention, the overvoltage reference current source provides an overvoltage reference current which exceeds a nominal current in the sensing resistor by a selected percentage which is approximately equal to the

25 percentage above a nominal voltage of the switched-mode power supply at which the switching transistor is to be turned off.

An overvoltage protection circuit in accordance with the present invention offers a significant improvement in that faster, more efficient and more accurate overvoltage protection is provided for the switched-mode power supply in which such an overvoltage

30 protection circuit is provided.

These and other aspects of the invention will be apparent from and elucidated with reference to the embodiments described hereinafter.

#### BRIEF DESCRIPTION OF THE DRAWING

The invention may be more completely understood with reference to the following description, to be read in conjunction with the accompanying drawing, in which:

Fig. 1 shows a simplified schematic diagram of a prior-art overvoltage protection circuit; and

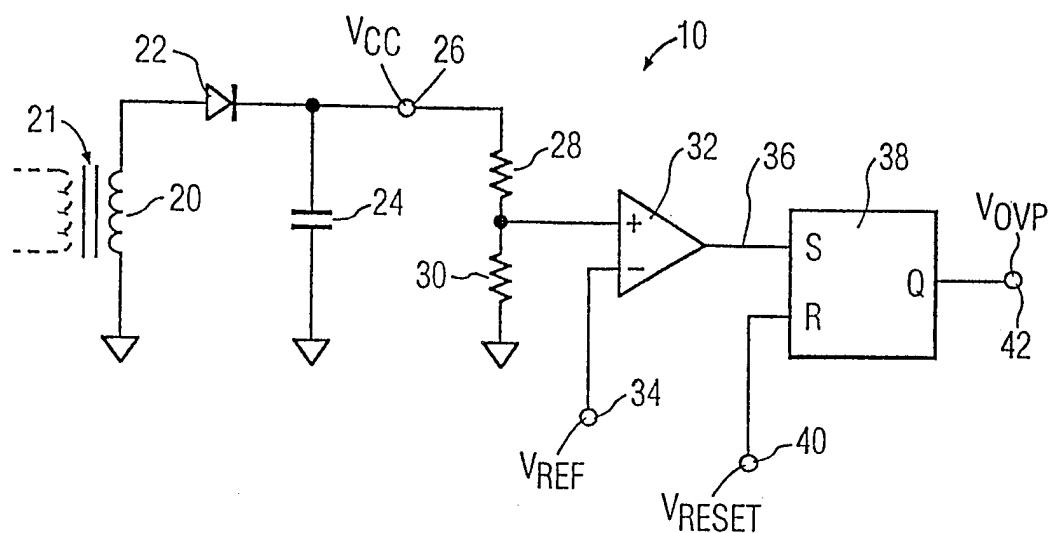

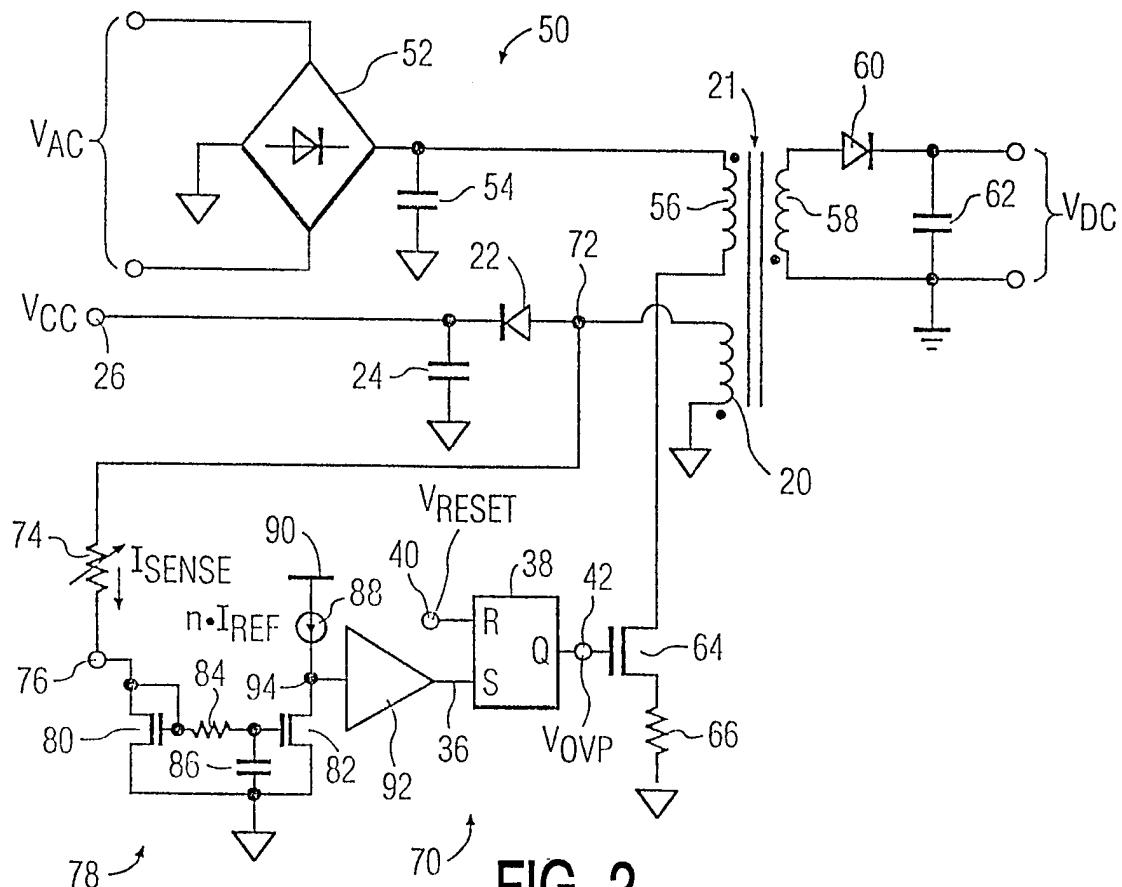

5 Fig. 2 shows a simplified schematic diagram of a switch-mode power supply incorporating an improved overvoltage protection circuit in accordance with the invention.

In the drawing, like components are generally designated by like reference numerals.

## 10 DESCRIPTION OF THE PREFERRED EMBODIMENTS

Fig. 1 shows a simplified schematic diagram of a typical prior-art overvoltage protection circuit, as described above. Since this circuit operates by sensing the rectified, filtered voltage on capacitor 24, circuit operation will inherently be slow, thus not affording optimum overvoltage protection and possibly resulting in circuit malfunction or even

15 permanent damage to sensitive circuit components. Additionally, as noted above, since the voltage across capacitor 24 can vary substantially from its nominal value, the prior-art overvoltage protection circuit, which operates off a fixed-ratio scaled-down version of the capacitor voltage, can have a relatively inaccurate overvoltage trigger level.

These disadvantages are overcome by the overvoltage protection circuit of the 20 present invention, which is shown in a simplified switched-mode power supply 50 in Fig. 2. In the circuit of Fig. 2, an AC input voltage  $V_{AC}$  is applied to a conventional diode bridge rectifier 52, the output of which is coupled to a filter capacitor 54 and a primary winding 56 of transformer 21. The primary winding 56 is coupled to ground through a switching transistor 64 and, optionally, a resistor 66. A secondary winding 58 of transformer 21 has 25 its output coupled through a diode 60 to a filter capacitor 62, with the D.C. output voltage  $V_{DC}$  of the circuit being taken across this capacitor. A sensing or auxiliary winding 20 of the transformer 21 is connected to diode 22 and filter capacitor 24 to generate a D.C. voltage  $V_{CC}$  on terminal 26, which voltage can be used to power the control circuitry of the power supply. The portions of the circuit so far described are essentially similar to those of Fig. 1 30 of U.S. Patent No. 5,313,381, in both configuration and operation, and accordingly will not be described in further detail.

Unlike the prior-art overall voltage protection circuits previously described, in the overvoltage protection circuit 70 of the present invention, as shown in Fig. 2, the protection circuit input is taken directly from the auxiliary winding 20 of the transformer 21,

at junction 72, rather than from terminal 26, at which terminal the auxiliary winding output has been rectified and filtered. This input to the overvoltage protection circuit is coupled through a sensing resistor 74, here a variable resistor, to the input terminal 76 of a current mirror 78 in order to provide an input current  $I_{SENSE}$  proportional to the voltage at junction 5 72 to the input terminal 76 of the current mirror 78. The current mirror 78 includes two MOSFET transistors 80 and 82 in a conventional current mirror configuration. The current mirror 78 may additionally include a delay circuit, in the form of an RC filter composed of resistor 84 and capacitor 86, which may optionally be included for the purpose of avoiding a false overvoltage protection circuit trigger condition due to a transient noise signal of short 10 duration. In practice, the values of resistor 84 and capacitor 86 may be selected in a known manner to provide a delay of about 500 nanoseconds.

The output of current mirror 78 is connected to a current source 88, which is coupled to a power line 90 and which provides a current of  $n \cdot I_{REF}$ . A current comparator 92 has an input coupled to the junction 94 between current source 88 and transistor 82 of the 15 current mirror 78, so that the current comparator changes state and provides a Set (S) input to the latch 38 on line 36 when the current in current mirror transistor 82 exceeds the value  $n \cdot I_{REF}$  of the current source 88. This in turn will generate an overvoltage protection circuit output signal  $V_{OVP}$  from the Q output of the latch 38 at terminal 42, thus disabling switching transistor 64 and reducing the overvoltage condition. When the overvoltage condition ceases, 20 the latch 38 is reset by a signal  $V_{RESET}$  at Reset (R) input 40 of the latch, in the same manner as the prior-art circuit of Fig. 1.

The current source 88 provides a current of  $n \cdot I_{REF}$ , where  $I_{REF}$  is a selected reference current value, with resistor 74 being set such that  $I_{SENSE}$  is equal to  $I_{REF}$  when the voltage at junction 72 is equal to its nominal operating value. Since current mirror 78 is 25 selected to have a 1:1 current ratio, the current in MOSFET 82 will be equal to  $I_{SENSE}$ , which in the nominal case is equal to  $I_{REF}$ . Thus, by selecting the parameter  $n$  to be equal to a value at which overvoltage detection and protection is to occur, a desired overvoltage protection level can be achieved. Thus, for example, if  $n$  is set equal to 1.26, the overvoltage protection circuit will trigger when the voltage level at junction 72 (which is 30 proportional to the output voltage  $V_{DC}$ ) rises above its nominal value by 26 percent. The current source 88, shown schematically in Fig. 2 by a current-source symbol, may be implemented by conventional means, such as a current mirror having its input connected to a source of reference current  $I_{REF}$ , and a current mirror ratio of 1: $n$ .

In operation, the resistance of variable resistor 74 will be set such that  $I_{SENSE}$  is

equal to  $I_{REF}$  under nominal operating conditions. This initial adjustment not only sets the nominal operating conditions of the circuit, but also serves to compensate for voltage variations in a particular circuit due to component tolerances, such as the tolerances in the transformer winding ratios, which can vary by as much as 30 percent, thus causing similar 5 variations in voltages among circuits having nominally identical circuit configurations. In this manner, the drawback of prior-art circuits, such as the one shown in Fig. 1, that voltage variations due to component tolerances can lead to substantial variations in the level of overvoltage that will trigger the overvoltage protection circuit, is eliminated. Additionally, since the input to the overvoltage protection circuit of the invention is taken directly from a 10 transformer winding, at junction 72, rather than from across capacitor 24 as in the prior-art, an overvoltage condition can be detected much more rapidly, since the substantial time delay necessary to charge the capacitor 24 has been eliminated. Thus, overvoltage protection circuits in accordance with the present invention are both faster and more accurate than prior-art circuits.

15 Instead of taking the input for the overvoltage protection circuit from a separate auxiliary winding, the secondary winding or even the primary winding of the transformer can be used as a sensing winding for providing the input.

20 While the invention has been particularly shown and described with reference to several preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and detail may be made without departing from the spirit or scope of the invention.

CLAIMS

1. An overvoltage protection circuit, for a switched-mode power supply of the type having a transformer (21) and a switching transistor (64) coupled in series with a winding (56) of the transformer (21), characterized in that the overvoltage protection circuit comprises a sensing resistor (74) having a first terminal directly connected to a sensing winding (20) of the transformer (21) for generating a current in said sensing resistor (74) proportional to the voltage across said sensing winding (20) and a second terminal, a current mirror (78), said second resistor terminal being coupled to an input (76) of said current mirror (78), an overvoltage reference current source (88) coupled to an output (94) of said current mirror (78), a current comparator (92) for comparing a reflected current from said current mirror (78) proportional to said sensing current in said sensing resistor (74) to an overvoltage reference current generated by said overvoltage reference current source (88), and circuit means (38) for generating a signal to turn off said switching transistor (64) when said reflected current exceeds said overvoltage reference current.

2. An overvoltage protection circuit as in Claim 1, characterized in that said sensing resistor (74) comprises a variable resistor.

3. An overvoltage protection circuit as in Claim 1, characterized in that said current mirror comprises a delay circuit (84,86).

4. An overvoltage protection circuit as in Claim 1, characterized in that said means (38) for generating a signal to turn off said switching transistor (64) comprises a latch circuit.

5. An overvoltage protection circuit as in Claim 1, characterized in that said overvoltage reference current source (88) provides an overvoltage reference current which exceeds a nominal current in said sensing resistor (74) by a selected percentage approximately equal to the percentage above a nominal voltage of said switched-mode power supply at which said switching transistor (64) is to be turned off.

1/1

FIG. 1

FIG. 2