(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4995264号

(P4995264)

(45) 発行日 平成24年8月8日(2012.8.8)

(24) 登録日 平成24年5月18日(2012.5.18)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 16/04 (2006.01)G 11 C 17/00 6 1 1 F

G 11 C 17/00 6 2 2 E

G 11 C 17/00 6 4 1

G 11 C 17/00 6 1 1 A

G 11 C 17/00 6 1 3

請求項の数 18 (全 30 頁)

(21) 出願番号 特願2009-505373 (P2009-505373)

(86) (22) 出願日 平成19年3月22日 (2007.3.22)

(65) 公表番号 特表2009-533794 (P2009-533794A)

(43) 公表日 平成21年9月17日 (2009.9.17)

(86) 國際出願番号 PCT/US2007/007087

(87) 國際公開番号 WO2007/126665

(87) 國際公開日 平成19年11月8日 (2007.11.8)

審査請求日 平成20年11月11日 (2008.11.11)

(31) 優先権主張番号 60/791,365

(32) 優先日 平成18年4月12日 (2006.4.12)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 11/413,951

(32) 優先日 平成18年4月28日 (2006.4.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 592012513

サンディスク コーポレイション

Sandisk Corporation

アメリカ合衆国 95035 カリフォルニア州、ミルピタス、マッカーシー ブールバード 601

(74) 代理人 110000110

特許業務法人快友国際特許事務所

(72) 発明者 ヘミンク ゲルト ヤン

〒231-0862 日本国神奈川県横浜市中区山手町262

審査官 園田 康弘

最終頁に続く

(54) 【発明の名称】読み出し中におけるプログラム外乱による影響の軽減

## (57) 【特許請求の範囲】

## 【請求項 1】

不揮発性メモリアレイを動作させる方法であって、

不揮発性記憶素子の第1集合を、読み出し比較値の第1セットを用いて読み出すこと

、

不揮発性記憶素子の第2集合を、読み出し比較値の第2セットを用いて読み出すことを含んでおり、

前記第1集合は、ソース選択制御線に隣接する第1ワード線に接続されており、

前記第2集合は、ソース選択制御線に隣接しない複数のワード線に接続されており、

前記第1セットは、複数の読み出し比較値を含んでおり、

前記第2セットは、前記第1セットに含まれている複数の読み出し比較値に対応する複数の読み出し比較値を含んでおり、

前記第1セットに含まれている少なくとも1つの読み出し比較値が、前記第2セットに含まれている対応する読み出し比較値と異なることを特徴とする方法。

## 【請求項 2】

前記第1セットに含まれている読み出し比較値のすべてが、前記第2セットに含まれている対応する読み出し比較値と異なることを特徴とする請求項1に記載の方法。

## 【請求項 3】

前記第1セットに含まれている1つの読み出し比較値が、前記第2セットに含まれている対応する読み出し比較値より大きいことを特徴とする請求項1に記載の方法。

10

20

**【請求項 4】**

前記第1セットを用いて読み出すワード線の本数より、前記第2セットを用いて読み出すワード線の本数が多いことを特徴とする請求項1に記載の方法。

**【請求項 5】**

前記第1ワード線に接続されている不揮発性記憶素子の第3集合を、複数個の読み出し比較値を含んでいる第3セットを用いて読み出す工程をさらに含むことを特徴とする請求項1に記載の方法。

**【請求項 6】**

前記第1セットを用いてデータの第1ページを読み出し、前記第3セットを用いてデータの第2ページを読み出すことを特徴とする請求項5に記載の方法。

10

**【請求項 7】**

前記第1集合と、前記第2集合が、マルチステートNANDフラッシュメモリデバイスであることを特徴とする請求項1に記載の方法。

**【請求項 8】**

前記第1セットが、前記第1集合を読み出す際にだけ利用されることを特徴とする請求項1に記載の方法。

**【請求項 9】**

不揮発性メモリアレイシステムであり、

不揮発性記憶素子の第1集合と、

不揮発性記憶素子の第2集合と、

20

前記第1集合を読み出し比較値の第1セットを用いて読み出すとともに、前記第2集合を読み出し比較値の第2セットを用いて読み出す管理回路を備えており、

前記第1集合は、ソース選択制御線に隣接する第1ワード線に接続されており、

前記第2集合は、ソース選択制御線に隣接しない複数のワード線に接続されており、

前記第1セットは、複数の読み出し比較値を含んでおり、

前記第2セットは、前記第1セットに含まれている複数の読み出し比較値に対応する複数の読み出し比較値を含んでおり、

前記第1セットに含まれている少なくとも1つの読み出し比較値が、前記第2セットに含まれている対応する読み出し比較値と異なることを特徴する不揮発性メモリアレイシステム。

30

**【請求項 10】**

前記第1集合と、前記第2集合が、マルチステートNANDフラッシュメモリデバイスであることを特徴する請求項9に記載の不揮発性メモリアレイシステム。

**【請求項 11】**

複数の前記不揮発性記憶素子が複数のブロックに配列されており、各々のブロックがページの集合を含み、前記ページはプログラミング単位を定め、前記ブロックは消去単位を定めており、

前記第1集合の一部と前記第2集合の一部が同じブロック内に配列されており、

そのブロックがビット線の集合を含み、

前記第1集合の前記一部に属する不揮発性記憶素子の各々が、ビット線の前記集合のうちの異なったビット線に接続されていることを特徴とする請求項9に記載の不揮発性メモリアレイシステム。

40

**【請求項 12】**

前記第1セットに含まれている1つの読み出し比較値が、前記第2セットに含まれている対応する読み出し比較値より大きいことを特徴とする請求項9に記載の不揮発性メモリアレイシステム。

**【請求項 13】**

前記管理回路が、前記第1ワード線に接続されている不揮発性記憶素子の第3集合を、複数の読み出し比較値を含んでいる第3セットを用いて読み出すことを特徴とする請求項9に記載の不揮発性メモリアレイシステム。

50

**【請求項 1 4】**

前記管理回路が、前記第 1 セットを用いてデータの第 1 ページを読み出し、前記第 3 セットを用いてデータの第 2 ページを読み出すことを特徴とする請求項 1 3 に記載の不揮発性メモリアレイシステム。

**【請求項 1 5】**

前記第 1 セットに含まれている読み出し比較値のすべてが、前記第 2 セットに含まれている対応する読み出し比較値より大きいことを特徴とする請求項 9 に記載の不揮発性メモリアレイシステム。

**【請求項 1 6】**

前記管理回路が、コントローラ、状態マシン、コマンド回路、制御回路およびデコーダのうちのいずれかの 1 つまたは組み合わせを含むことを特徴とする請求項 9 に記載の不揮発性メモリアレイシステム。 10

**【請求項 1 7】**

前記第 1 セットが前記第 1 集合を読み出す際にだけ利用されることを特徴とする請求項 9 に記載の不揮発性メモリアレイシステム。

**【請求項 1 8】**

前記第 1 セットを用いて読み出すワード線の本数より、前記第 2 セットを用いて読み出すワード線の本数が多いことを特徴とする請求項 9 に記載の不揮発性メモリアレイシステム。

**【発明の詳細な説明】**

20

**【技術分野】****【0001】**

本発明は、不揮発性メモリに関する。

**【背景技術】****【0002】**

半導体メモリデバイスは、さまざまな電子装置内で、ますます多く使用されるようになっている。例えば、不揮発性半導体メモリは、携帯電話、デジタルカメラ、パーソナルデジタルアシスタント、モバイルコンピューティング装置、非モバイルコンピューティング装置、およびその他の装置の中で使用されている。電気的に消去可能でプログラム可能な読み出し専用メモリ（EEPROM）およびフラッシュメモリは、特に普及している不揮発性半導体メモリである。 30

**【0003】**

EEPROMとフラッシュメモリの多くのタイプは、半導体基板中のチャネル領域の上方に位置するとともにチャネル領域から絶縁されている浮遊ゲートを利用している。この浮遊ゲートは、ソース領域とドレイン領域の間に位置している。制御ゲートが、浮遊ゲートの上方に設けられるとともに浮遊ゲートから絶縁されている。トランジスタの閾値電圧は、浮遊ゲートに保持されている電荷の量によって制御される。すなわち、ソースとドレイン間を導通させてトランジスタをオンさせるために制御ゲートに印加しなければならない電圧の最小値は、浮遊ゲートの電荷レベルによって制御される。

**【0004】**

30

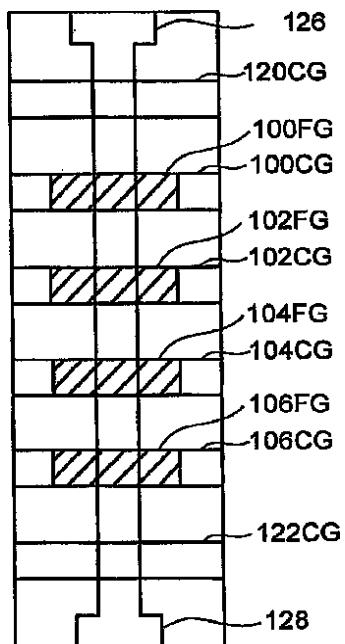

フラッシュメモリシステムの一例では、NAND型の構造を使用する。NAND型フラッシュメモリ構造では、2つの選択ゲートの間に複数のトランジスタが直列に配置されている。直列のトランジスタと選択ゲートは、NANDストリングと呼ばれる。図1は、1つのNANDストリングを示す上面図である。図2は、その等価回路である。図1および図2に示すNANDストリングは、直列の4つのトランジスタ100、102、104、106を備え、第1の（またはドレイン）選択ゲート120と第2の（またはソース）選択ゲート122との間に挟まれている。選択ゲート120は、ビット線コンタクト126を介してNANDストリングをビット線に接続する。選択ゲート122は、NANDストリングをソース線128に接続する。選択ゲート120は、選択線SGDに適切な電圧を印加することによって制御される。選択ゲート122は、選択線SGSに適切な電圧を印 40

40

50

加することによって制御される。トランジスタ100、102、104、106のそれぞれは、制御ゲートと浮遊ゲートを有する。例えば、トランジスタ100は、制御ゲート100CGと浮遊ゲート100FGを有する。トランジスタ102は、制御ゲート102CGと浮遊ゲート102FGとを有する。トランジスタ104は、制御ゲート104CGと浮遊ゲート104FGを有する。トランジスタ106は、制御ゲート106CGと浮遊ゲート106FGを有する。制御ゲート100CGは、ワード線WL3に接続されている。制御ゲート102CGは、ワード線WL2に接続されている。制御ゲート104CGは、ワード線WL1に接続されている。制御ゲート106CGは、ワード線WL0に接続されている。

#### 【0005】

10

図1および図2では、NANDストリング内に4つのメモリセルを示しているが、4つのトランジスタの使用する構成は、一例であることに留意されたい。NANDストリングは、4つ未満のメモリセルを有していてもよく、又は、4つを超えるメモリセルを有していてもよい。例えば、一部のNANDストリングは、8つのメモリセル、16のメモリセル、32のメモリセル、64のメモリセルなどを含むことができる。本明細書における説明では、NANDストリング内のメモリセルの数は、いかなる特定の数にも限定されない。

#### 【0006】

20

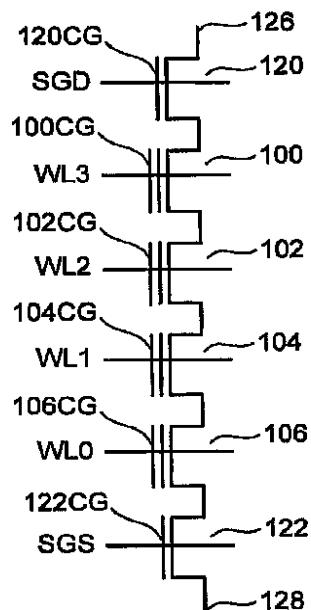

NAND構造を用いたフラッシュメモリシステムの一般的なアーキテクチャは、いくつかのNANDストリングを含んでいる。例えば、図3は、メモリアレイに含まれる多数のNANDストリングのうちの3つのNANDストリング202、204、206を示している。図3の各NANDストリングは、2つの選択トランジスタ（ゲートとも呼ばれる）と4つのメモリセルを含んでいる。例えば、NANDストリング202は、選択トランジスタ220及び230、並びにメモリセル222、224、226及び228を含んでいる。NANDストリング204は、選択トランジスタ240及び250、並びにメモリセル242、244、246及び248を含んでいる。各NANDストリングは、そのソース選択ゲート（例えば選択トランジスタ230、250）によってソース線に接続されている。選択線SGSは、ソース選択ゲート（例えば230と250）を制御するために用いられる。

#### 【0007】

30

さまざまなNANDストリングが、選択線SGDによって制御されている選択トランジスタ220、240などによってそれぞれのビット線に接続されている。それぞれのビット線と、ビット線コンタクトを介してこのビット線に接続されている1つまたはそれぞれのNANDストリングとが、メモリセルのアレイを含む列を構成している。ビット線は、複数のNANDストリングによって共有されている。一般的には、ビット線は、NANDストリングの頂部を、ワード線に対して直交する方向を走行し、また、1つ以上のセンスアンプに接続されている。

#### 【0008】

40

ワード線（WL3、WL2、WL1およびWL0）は、アレイの行を備えている。ワード線WL3は、メモリセル222と242の制御ゲートに接続されている。ワード線WL2は、メモリセル224と244と252の制御ゲートに接続されている。ワード線WL1は、メモリセル226と246の制御ゲートに接続されている。ワード線WL0は、メモリセル228と248の制御ゲートに接続されている。

#### 【0009】

各メモリセルは、データ（アナログデータまたはデジタルデータ）を記憶することができる。1ビットのデジタルデータを記憶する場合（バイナリメモリセルと呼ばれる）には、このメモリセルの可能な閾値電圧の範囲は2つの範囲に分割され、これらの範囲に論理データ「1」と「0」が割り当てられる。NANDタイプのフラッシュメモリの一例では、この閾値電圧は、メモリセルが消去された後では負の値となり、論理「1」と定義される。プログラミング後の閾値電圧は、正の値となり、論理「0」と定義される。閾値

50

電圧が負の状態で制御ゲートに 0 ボルトを印加することによって読み出しが試みられた場合、メモリセルはオンとなり、論理「 1 」が記憶されていることを示す。閾値電圧が正の状態で制御ゲートに 0 ボルトを印加することによって読み出しが試みられた場合、メモリセルはオンにならず、論理「 0 」が記憶されていることを示す。

#### 【 0 0 1 0 】

メモリセルはまた、複数のレベルの情報を記憶することが可能である（マルチステートメモリセルと呼ばれる）。複数のレベルのデータを記憶する場合、可能な閾値電圧の範囲は、このデータのレベルの数に分割される。例えば、4 つのレベルの情報を記憶する場合、4 つの閾値電圧範囲が存在し、これらがデータ値「 1 1 」、「 1 0 」、「 0 1 」、「 0 0 」に割り当てられる。N A N D タイプのメモリの一例では、消去動作の後の閾値電圧は負の値となり、論理「 1 1 」と定義される。正の閾値電圧は「 1 0 」、「 0 1 」、「 0 0 」という状態に対して用いられる。10

#### 【 0 0 1 1 】

N A N D タイプのフラッシュメモリおよびそれらの動作に関連する例は、次の米国出願／特許出願（それらのすべては、それらの全体が参照により本明細書に援用されるものとする）、米国特許第 5 , 5 7 0 , 3 1 5 号、米国特許第 5 , 7 7 4 , 3 9 7 号、米国特許第 6 , 0 4 6 , 9 3 5 号、米国特許第 6 , 4 5 6 , 5 2 8 号、米国特許公報第 U S 2 0 0 3 / 0 0 0 2 3 4 8 号。本明細書の説明はまた、N A N D タイプだけではなく他のタイプのフラッシュメモリ、さらに、他のタイプの不揮発性メモリにも当てはまる。20

#### 【 0 0 1 2 】

フラッシュメモリセルをプログラミングするとき、プログラム電圧を制御ゲートに印加して、ビット線を接地する。このフラッシュメモリセルのチャネルと浮遊ゲートとの電圧差によって、浮遊ゲートの下のチャネル領域から電子が浮遊ゲートに注入される。電子が浮遊ゲートに蓄積されると、浮遊ゲートは負に帯電し、メモリセルの閾値電圧が上昇する。プログラムするセルの制御ゲートにプログラム電圧を印加するためには、このプログラム電圧を適切なワード線に印加する。上記のように、このワード線はまた、同じワード線を利用している他のそれぞれのN A N D ストリング内にある 1 つのメモリセルにも接続されている。例えば、図 3 のメモリセル 2 2 4 をプログラミングするとき、プログラム電圧は、メモリセル 2 4 4 の制御ゲートにも印加されるが、これは、これらメモリセルの双方が同じワード線を共有しているからである。あるワード線上の 1 つのセルを、同じワード線に接続されている他のセルをプログラミングすることなくプログラムしたいとき、例えば、メモリセル 2 2 4 はプログラムしたいが、メモリセル 2 4 4 はプログラムしたくないときに、1 つの問題が発生する。プログラム電圧はあるワード線に接続されているすべてのメモリセルに印加されるため、同じワード線上にある選択されていないメモリセル（プログラムするつもりのないメモリセル）が不用意にプログラムされることがある。例えば、メモリセル 2 4 4 はメモリセル 2 2 4 に隣接しているとする。メモリセル 2 2 4 をプログラミングするとき、メモリセル 2 4 4 が意図しないのにプログラムされるかもしれないという懸念がある。選択されたワード線上にある選択されていないメモリセルが意図しないのにプログラミングされることを、「プログラム外乱」と呼ぶ。30

#### 【 発明の開示 】

#### 【 発明が解決しようとする課題 】

#### 【 0 0 1 3 】

プログラム外乱を防止可能な様々な技術が存在する。「自己昇圧法」として知られている 1 つの方法では、選択されていないN A N D ストリングをこれに対応するビット線から電気的に隔離して、プログラミング中に、バス電圧（例えば 7 ~ 1 0 ボルトであるが、この範囲に限られることはない）を選択されていないワード線に印加する。この選択されていないワード線が選択されていないN A N D ストリングのチャネル領域に結合して、この選択されていないN A N D ストリングのチャネル領域に電圧（たとえば 6 ~ 1 0 ボルト）を発生させ、これによって、プログラム外乱を軽減させる。自己昇圧によって、チャネル内の電圧が上昇し、これによって、トンネル酸化物の両端での電圧差が減少する。その結50

果、プログラム外乱が軽減される。ここで、この昇圧されたチャネル電圧の変動範囲は非常に大きくなることがある。これは、チャネル電圧がどの程度昇圧されるかは、バス電圧の値と、メモリセルの状態にも依存しており、NANDストリング内のメモリセルがすべて消去状態にあるときに昇圧効率がもっとも高い（チャネル電圧がもっとも高い）からである。

#### 【0014】

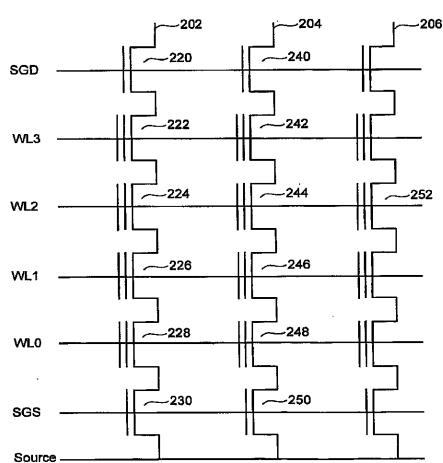

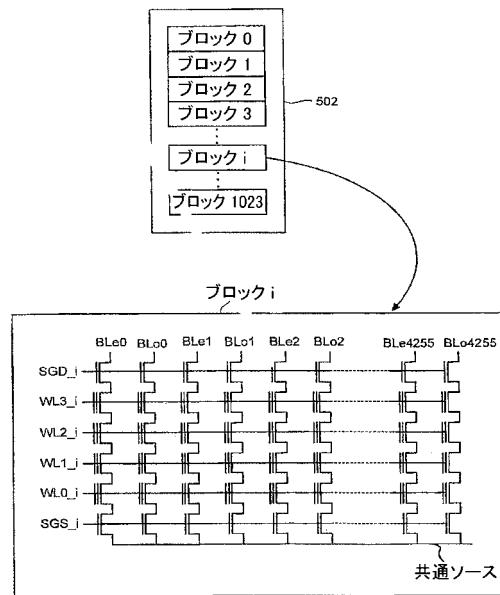

図4と図5に、プログラムされているNANDストリングと自己昇圧法によって抑止されているNANDストリングを示す。図4は、プログラムされているNANDストリングを示す。図4に示すNANDストリングは、8個のメモリセル304、306、308、310、312、314、316、318を含んでいる。これら8個のメモリセルの各々は、浮遊ゲート(FG)と制御ゲート(CG)を含んでいる。浮遊ゲート同士の間には、ソース領域／ドレイン領域330がある。P型基板（たとえばシリコン）があって、基板内部にN-ウェル領域がある、N-ウェル領域内にp-ウェル領域がある実施形態もある（これらをすべて図示しているわけではないが、これは図面をより分かりやすくするためにある）。ここで、p-ウェル領域には、いわゆるチャネルインプランテーションが含まれるが、これは通常はP型インプランテーションであり、これによって、メモリセルの閾値電圧や他の特徴が決定したり、決定の助けになったりする。ソース領域／ドレイン領域330は、p-ウェル領域内に形成されるN+型拡散領域である。

#### 【0015】

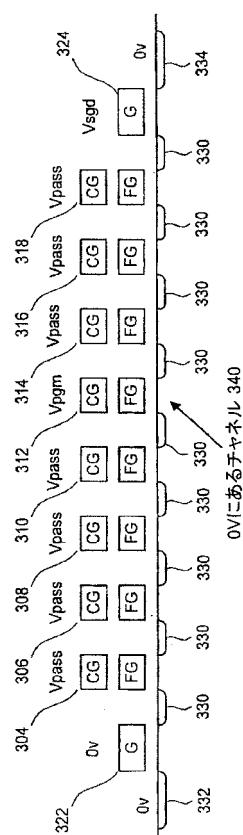

NANDストリングの一方の端はドレイン選択ゲート324である。NANDストリングは、ドレイン選択ゲート324によって、ビット線コンタクト334を介して対応するビット線に接続されている。NANDストリングの他方の端は、ソース選択ゲート322である。ソース選択ゲート322によって、NANDストリングは、共通のソース線332に接続されている。プログラミング中、プログラミング目的で選択されたメモリセル（たとえばメモリセル312）が接続されているワード線にプログラム電圧V<sub>pgm</sub>が印加される。プログラム電圧V<sub>pgm</sub>は、一般的には、12ボルトから24ボルトの範囲で変動し得る。1つの実施形態では、プログラム電圧信号は、新しいパルス毎にその大きさが増加するパルス集合である。約8ボルトのバス電圧V<sub>pass</sub>が、プログラミングするよう選択されていないメモリセルの制御ゲートに印加される。ソース選択ゲート322は隔離状態にあって、そのゲート(G)には0ボルトが印加される。低電圧が共通のソース線332に印加される。この低電圧は0ボルトでもよい。しかしながら、ソース線332に印加される電圧を0ボルトより少し高くして、ソース選択ゲート322の隔離特性を向上させるようにしてもよい。一般的には、電源電圧V<sub>dd</sub>（例えば2.5ボルト）の範囲にある電圧V<sub>sgd</sub>は、ドレイン選択ゲート324に印加される。0ボルトをビット線コンタクト334に対してこれに対応するビット線を介して印加して、選択されたメモリセル312のプログラミングを可能とする。チャネル340は0ボルトないしはこれに近い値にある。メモリセル314のチャネルと浮遊ゲートの間には電圧差があるため、トンネル効果によって、電子がゲート酸化膜（一般にトンネル酸化物とも呼ばれる）を通り抜けて浮遊ゲート内に入る。

#### 【0016】

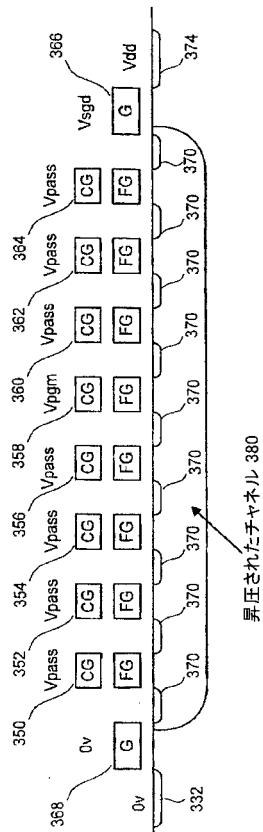

図5のNANDストリングは、プログラミングを抑止しているNANDストリングを示している。このNANDストリングは、8個のメモリセル350、352、354、356、358、360、362、364を含んでいる。このNANDストリングはまた、このNANDストリングを、ビット線コンタクト374を介して対応するビット線に接続しているドレイン選択ゲート366と、このNANDストリングを、共通のソース線332に接続しているソース選択ゲート368をも含んでいる。浮遊ゲートスタック同士の間には、ソース領域／ドレイン領域370が存在する。図5に示すNANDストリングでは、ドレイン選択ゲート366のゲートにV<sub>sgd</sub>が印加され、ソース選択ゲート368のゲートには0ボルトが印加され、共通ソース線332には0ボルト（もしくは0ボルトよりも少し高い電圧）が印加されている。ビット線コンタクト374には対応するビット線

10

20

30

40

50

を介して電源電圧  $V_{dd}$  が印加され、メモリセル 358 のプログラミングを抑止している。

#### 【0017】

$V_{dd}$  が印加されると、ドレイン選択トランジスタ 366 は初期状態においては導電状態となる。したがって、NANDストリングの下のチャネル領域が部分的に充電されて電位が高くなる（0ボルトより高く、一般的には  $V_{dd}$  に等しいないしはほぼ等しい）。この充電は通常、予備充電と呼ばれる。予備充電は、チャネル電位が  $V_{dd}$  はまたは、 $V_{sgd} - V_t$ （ここで、 $V_t$  はドレイン選択ゲート 366 の閾値電圧に等しい）より低い電位に達すると自動的に停止する。一般的に、予備充電中は、 $V_{sgd}$  は  $V_{sgd} - V_t > V_{dd}$  となるように選択する。これによって、NANDストリングの下のチャネル領域を  $V_{dd}$  まで予備充電することが可能となるようになる。チャネルがこの電位にまで到達した後では、選択ゲートトランジスタは非導電状態であるか、または、 $V_{sgd}$  を  $V_{dd}$ （例えば 2.5 ボルト）に近い値にまで下げることによって非導電状態にする。次いで、 $V_{pass}$  と  $V_{pgm}$  の電圧値を 0 ボルトからそれぞれの最終値にまで（必ずしも同時にではなくともよい）上昇させる。ドレイン選択ゲートトランジスタ 366 は非導電状態にあるため、ワード線とチャネル領域間の静電結合によってチャネル電位は上昇し始める。この現象は自己昇圧と呼ばれる。図 5 に示すように、チャネル 380 が、おおよそ均一に昇圧電圧まで昇圧されることが分かる。メモリセル 358 の浮遊ゲートとチャネル 380 の間の電圧差が減少しているため、プログラミングは抑止される。自己昇圧法の技術を含め、NAND型フラッシュメモリのプログラミングに関する更なる情報（それらのすべては、それらの全体が参照により本明細書に援用されるものとする）は、Lutzelaによる米国特許第 6,859,397 号の「Source Side Self Boosting Technique for Non-Volatile Memory」に見受けられる。10 20

#### 【0018】

プログラム外乱を解決しようとする別の試みは、消去領域自己昇圧法（「EASB 法」）である。EASB 法では、すでにプログラムされているセルのチャネルを、抑止されているセルのチャネルから隔離しようとする。EASB 法では、選択された NANDストリングのチャネル領域は 2 つの領域に分割される。一方の領域は、プログラムされた（又は消去された）メモリセルを多く含んでいる可能性のある選択されたワード線のソース側の領域である。他方の領域は、まだ消去状態にある（又は少なくともまだ最終的なプログラム状態ではない）セルを含んでいる選択されたワード線のドレイン側の領域である。これら 2 つの領域は、低電圧、一般的には 0 ボルトに印加されているワード線によって互いに分離されている。このように分離されているため、この 2 つの領域はそれぞれ別の電位に昇圧することが可能である。ほとんどすべての場合に、選択されたワード線のドレイン側の領域は、ソース側の領域より高い電位に昇圧される。最も高く昇圧される領域は消去されたセルを持つ領域であるため、この昇圧方法は、消去領域自己昇圧法（EASB）と呼ばれる。30

#### 【0019】

上記の昇圧方法ではプログラム外乱を軽減するが、この問題を解消したわけではない。ソース選択ゲートに隣接するメモリセル（例えば図 5 においてソース選択ゲート 368 に隣接するメモリセル 350）に発生し得る 1 つの影響として、ゲート誘導ドレイン・リーカ（GIDL）があるが、これはバンド間トンネル効果とも呼ばれる。GIDL によって、NANDストリングの下のチャネルがプログラミングしないように抑止された場合に（高電圧に昇圧された場合に）、ソース選択ゲートのところで電子が発生する。次いで、この発生した電子が、ソース選択ゲートに隣接するメモリセルの浮遊ゲートに向かって、強力な横方向の電場によって加速される。これらの電子の一部は、十分なエネルギーを得て浮遊ゲート下のトンネル酸化膜内に、または、この浮遊ゲート自身の内部に注入される。これによって、対応するメモリセルの閾値電圧が変化する。40

#### 【0020】

図6に、図5のNANDストリングの一部分を示す。図6では、メモリセル350のドレインとチャネルの一部が拡大されている。プログラム抑止動作中（例えば、他のNANDストリングがプログラムされる時）にはNANDストリングが昇圧されるため、この昇圧されたNANDストリングのチャネル領域は高電圧となる（昇圧されたチャネル380を参照）。また、一般的に0ボルトに印加されているソース選択ゲート368とソース選択ゲート368に隣接するメモリセル350の間の接合領域も高電圧となる。この印加状態によって、GIDLが発生する。これによって、電子とホールの対が生成される可能性が生じる。ホールはp-ウェル領域384に移動する。電子は、昇圧されたチャネル領域380に移動する。一般的に、ソース選択ゲートとソース選択ゲートに隣接するメモリセルの間の接合領域には横方向の電場が存在する。これは、この接合（ドレイン／ソース）が、メモリセル下のチャネル領域と選択ゲート下のチャネル領域の間に大きな電圧差があるため、部分的に空乏化するからである。この電場によって電子を加速することが可能であり、この電子が十分なエネルギーを獲得して、ソース選択ゲートに隣接するメモリセルのトンネル酸化膜内に注入されたり、さらに、このメモリセルの浮遊ゲートにまで到達したりしかねない。いずれの場合も、対応するメモリセルの閾値電圧は、注入された電子が存在することによって変化する。このため、ソース選択ゲートに隣接するメモリセルを読み出すときにエラーが発生する可能性がある。

#### 【0021】

したがって、プログラム外乱の影響を軽減するための新たなメカニズムが必要となる。

#### 【課題を解決するための手段】

#### 【0022】

本明細書では、プログラム外乱の影響を軽減する不揮発性記憶素子をプログラミングおよび／または読み出すためのシステムを提案する。実施形態の1つの集合では、プログラミングのプロセス中に、特定のワード線（または他の記憶素子グループ）に対して互いに異なった検証レベルを用いる。マルチステートデバイスを用いる例の1つの集合の場合、1つのプログラム状態、2つのプログラム状態、プログラム状態の別の部分集合またはすべてのプログラム状態に対応する目標レベルを互いに異なったものとすることが可能である。一部の実施形態では、特定のワード線（または他の記憶素子グループ）と関連しているデータのページが異なれば、その目標レベル（1つ、2つ、別の部分集合またはすべてのプログラム状態に対するレベル）も異なるようにすることが可能である。特定のワード線（または他の記憶素子グループ）と接続している記憶素子が異なれば、その目標レベル（1つ、2つ、別の部分集合またはすべてのプログラム状態に対するレベル）も異なるようになることが可能な実施形態もある。1つの実施形態では、それぞれ異なる目標レベルを受信するワード線を、昇圧領域に対する位置に基づいて選択する。

#### 【0023】

1つの実施形態では、目標レベルのグループを用いて不揮発性記憶素子の集合をプログラミングし、特定の目標レベルの集合を用いて特定の不揮発性記憶素子の集合をプログラミングする。これによって、特定の不揮発性記憶素子の集合の閾値分布が、プログラミングプロセスの完了時に不揮発性記憶素子の集合に対応する閾値分布内に含まれるようにする。特定の目標レベルの集合のうちの少なくとも1つが、目標レベルの集合に対応する目標レベル未満である。

#### 【0024】

1つの実施形態では、目標レベルの集合を用いて不揮発性記憶素子の集合をプログラミングし、特定の目標レベルの集合を用いて特定の不揮発性記憶素子の集合をプログラミングする。これによって、特定の不揮発性記憶素子の集合の閾値電圧分布が、プログラミングプロセスの完了時に、不揮発性記憶素子グループに対応する閾値電圧分布からの突出程度が少なくとも減少する（まったく突出しない場合を含む）ようにシフトするようにし、特定の目標レベルの集合のうちの少なくとも1つが、目標レベルの集合に対応する目標レベル未満である。

#### 【0025】

10

20

30

40

50

1つの実施形態では、目標レベルの集合を用いて1つ以上の不揮発性記憶素子の集合をプログラミングし、特定の目標レベルの集合を用いて特定の不揮発性記憶素子をプログラミングする。特定の目標レベル集合のうちの少なくとも1つが、目標レベルの集合の対応する目標レベル未満である。特定の不揮発性記憶素子は、ソース選択ゲートに隣接している。

#### 【0026】

1つの実施形態では、目標レベルの第1の集合を用いて1つ以上の不揮発性記憶素子の第1の集合をプログラミングし、1つ以上の不揮発性記憶素子の第1の集合をプログラミングした後に、目標レベルの第2の集合を用いて1つ以上の不揮発性記憶素子の第2の集合をプログラミングする。1つ以上の不揮発性記憶素子の第1の集合が、最初にプログラミングされる。一連のプログラミング動作中に、1つ以上の不揮発性記憶素子の第1の集合は第1のワード線に接続され、1つ以上の不揮発性記憶素子の第2の集合は、第1のワード線の後でプログラムされたワード線の集合に接続される。第2の目標レベル集合は、第1の目標レベル集合とは異なっている。10

#### 【0027】

別の実施形態では、プログラム外乱の影響を軽減する不揮発性記憶をプログラミングおよび／または読み出すシステムを提案する。実施形態の1つの集合では、読み出しプロセス中に、特定のワード線（または他の記憶素子グループ）に対して互いに異なった読み出し比較値を用いる。この互いに異なる読み出し比較値を受信するワード線は、プログラミングプロセス中に、昇圧領域の位置に対するワード線の位置に基づいて選ばれる。20

#### 【0028】

1つの実施形態では、読み出し比較値の第1の集合を用いて不揮発性記憶素子の第1の集合を読み出し、読み出し比較値の第2の集合を用いて1つ以上の不揮発性記憶素子の第2の集合を読み出す。不揮発性記憶素子の第1の集合が、第1の制御線に接続される。不揮発性記憶素子の第2の集合が、第1の制御線とは異なる制御線の第2の集合に接続される。読み出し比較値の第1の集合のうちの少なくとも1つは、読み出し比較値の第2の集合の対応する比較レベルと異なっている。実施形態（すべての実施形態ではないが）の一例では、第1の制御線は、ソース選択制御線の隣にある。

#### 【0029】

1つの実施形態では、目標レベルの第1の集合を用いて不揮発性記憶素子の第1の集合をプログラミングし、同じ目標レベルの第1の集合を用いて1つ以上の不揮発性記憶素子の第2の集合をプログラミングする。不揮発性記憶素子の第1の集合は、第1の制御線と接続している。第1の制御線は、第2の制御線に隣接している。このプロセスではまた、第1の制御線にプログラミング信号を出力し、第2の制御線に信号を出力して、第2の制御線に接続されている不揮発性記憶素子が信号に応答してオフすることを要求する。1つ以上の不揮発性記憶素子の第2の集合は、制御線の集合と接続している。第1と第2の制御線は、制御線の集合には存在しない。1つ以上の不揮発性記憶素子の第1の集合は、読み出し比較値の第1の集合を用いて読み出される。1つ以上の不揮発性記憶素子の第2の集合は、読み出し比較値の第2の集合を用いて読み出される。読み出し比較値の第1の集合のうちの少なくとも1つは、読み出し比較値の第2の集合のうちの対応する比較レベルとは異なる。3040

#### 【0030】

本明細書に記載する様々な方法は、様々なデバイスによって実行することが可能である。適切な装置の一例は、不揮発性記憶素子と、不揮発性記憶素子と連通している管理回路とを備えている。不揮発性記憶素子には、不揮発性記憶素子の第1の集合と、不揮発性記憶素子の第2の集合がある。管理回路は、不揮発性記憶素子の第1の集合と不揮発性記憶素子の第2の集合に関連して本明細書に記載する様々な方法を実行する。1つの実施形態では、管理回路は、コントローラ、状態マシン、コマンド回路、制御回路およびデコーダのうちのいずれか1つまたは組み合わせを備えている。回路が、特定の実施形態にとって適する他の要素を備えることが可能な実施形態もある。50

【発明を実施するための最良の形態】

【0031】

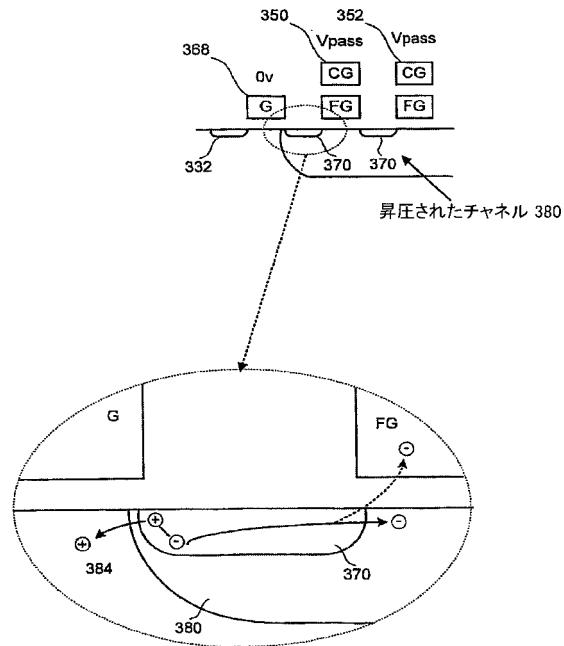

図7は、本明細書に記載される1つ以上の実施形態を実施するために使用できるフラッシュメモリシステムの1つの実施形態のブロック図である。他のシステムや実施形態も使用することができます。メモリセルアレイ502は、列制御回路504と、行制御回路506と、p-ウェル領域制御回路508と、共通ソース制御回路510によって制御される。列制御回路504は、メモリセル内に記憶されたデータを読み出すために、およびプログラム動作中のメモリセルの状態を判定するために、およびビット線の電位レベルを制御してプログラミングや消去を促進又は抑止するために、メモリセルアレイ502のビット線に接続されている。行制御回路306は、ワード線のうちのいずれかを選択するために、および読み出し電圧を印加するために、およびプログラム電圧を印加するために、ワード線に接続されている。行制御回路506はワード線に接続されて、ワード線のうちの1つを選択し、読み出し電圧を印加し、列制御回路504によって制御されるビット線の電位レベルと合成されたプログラム電圧を印加し、消去電圧を印加する。1つの実施形態では、行制御装置306と列制御装置304は、適切なワード線とビット線を選択するデコーダを含んでいる。共通ソース制御回路510は、メモリセルに接続された共通ソース線(図8に「共通ソース」として示す)を制御する。p-ウェル制御回路508は、p-ウェル電圧を制御する。

【0032】

メモリセル内に記憶されたデータは、列制御回路504によって読み出され、データ入力/出力バッファ512を経由して、外部I/O線に出力される。メモリセル内に記憶されるプログラムデータは、外部I/O線を経由してデータ入力/出力バッファ512に入力され、列制御回路504に転送される。外部I/O線は、コントローラ518に接続される。

【0033】

フラッシュメモリデバイスを制御するためのコマンドデータは、コントローラ518に入力される。コマンドデータは、どのような動作が要求されているのかをフラッシュメモリに通知する。入力コマンドは、制御回路515の一部である状態マシン516に転送される。状態マシン516は、列制御回路504と、行制御回路506と、共通ソース制御510と、p-ウェル制御回路508と、データ入力/出力バッファ512とを制御する。状態マシン516は、さらに、レディ/ビジーや、バス/フェイルなどの、フラッシュメモリのステータスデータを出力してもよい。

【0034】

コントローラ518は、パーソナルコンピュータ、デジタルカメラ、パーソナルデジタルアシスタントなどのホストシステムに接続されている、又は、接続可能である。コントローラ518は、ホストと通信する。ホストは、メモリアレイ502に又はメモリアレイ502からデータを記憶又は読み出す、およびそのようなデータを供給又は受信するといったコマンドを起動する。コントローラ518は、そのようなコマンドを、制御回路518の一部であるコマンド回路514が解読して実行可能なコマンド信号に変換する。コマンド回路514は、状態マシン516と通信する。コントローラ518は、通常、メモリアレイに書き込まれる、又はメモリアレイから読み出されるユーザデータのためのバッファメモリを有している。

【0035】

一例のメモリシステムは、コントローラ518を含む1つの集積回路と、1つ以上の集積回路チップ(それぞれがメモリアレイと、関連する制御、入力/出力、および状態マシン回路とを含む)を備える。メモリアレイとシステムのコントローラ回路は、1つ以上の集積回路チップ上に一緒に統合される傾向にある。メモリシステムは、ホストシステムの一部として組み込まれていてもよく、又は、ホストシステムに着脱可能に挿入されるメモリカード(又はその他のパッケージ)内に含まれていてもよい。そのような着脱可能なカードは、メモリシステム全体(例えば、コントローラを含む)を含んでいてもよく、又は

、関連する周辺回路を伴ったメモリアレイのみを含んでいてもよい（コントローラ又は制御機能はホスト内に組み込まれる）。このように、コントローラは、ホスト内に組み込まれることも、又は着脱可能なメモリシステム内に含まれることも可能である。

#### 【0036】

いくつかの実施形態では、図7の構成要素のうちのあるものは、統合することが可能である。さまざまな設計で、図7の構成要素のうちで、メモリセルアレイ502以外の1つ以上の構成要素が（単独、又は統合において）、管理回路と考えることが可能である。たとえば、1つの管理回路は、制御回路515、コマンド回路514、状態マシン516、列制御回路504、行制御回路506、p-ウェル制御回路508、共通ソース制御回路510、およびデータ入／出力回路510のうちのどれか1つまたはこれらを統合したもののを含むことができる。10

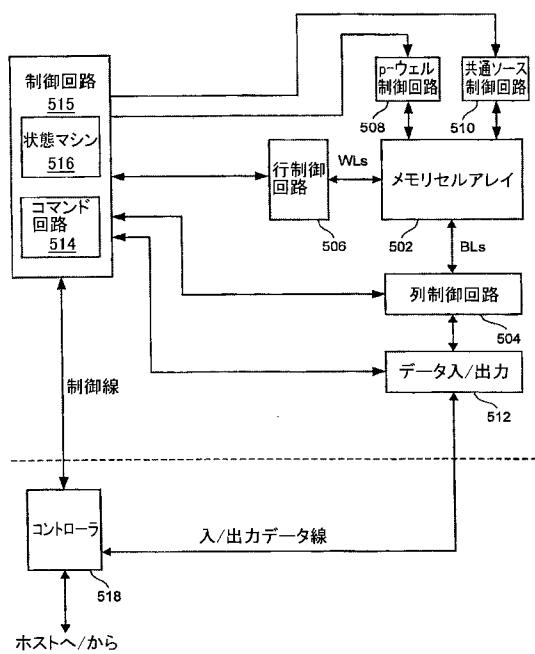

#### 【0037】

図8を参照して、メモリセルアレイ502の構造の一例を説明する。一例として、1,024のブロックに分化されているNAND型フラッシュEEPROMを説明する。それぞれのブロックに記憶されたデータは同時に消去することが可能である。1つの実施形態では、ブロックは、同時に消去されるメモリセルの最小単位である。この例では、それぞれのブロックに8,512の列がある。それぞれのブロックは一般的に、プログラミングの単位となり得る多くのページに分割される。他のデータプログラミング単位も可能である。1つの実施形態では、個々のページはセグメントに分割されてもよいが、このセグメントが含んでいる、基本的なプログラミング動作として一時に書き込まれるセルの数は最小になり得る。一般的には、1ページ以上のデータが、1行のメモリセルに記憶される。20

#### 【0038】

図8に示す各々のブロックには、偶数ビット線（BLE）と奇数ビット線（BLO）に分割される8,512の列がある。偶数／奇数ビット線構造では、共通のワード線に沿っており、奇数ビット線に接続されているメモリセルが、ある時点でプログラムされる。共通のワード線に沿っており、偶数ビット線に接続されているメモリセルが、別の時点でプログラムされる。図8は、NANDストリングを形成するように連続して接続されている4つのメモリセルを示す。図8では、1つのNANDストリングに含まれるセルとして4つのセルを示しているが、4つより多い数又は少ない数でもよい（例えば16個、32個または別の数でもよい）。NANDストリングの一方の端子は、ドレイン選択ゲート（選択ゲートドレイン線SGDに接続されている）を介して対応するビット線に接続されており、もう一方の端子は、ソース選択ゲート（選択ゲートソース線SGSに接続されている）を介して共通ソースに接続されている。30

#### 【0039】

他の実施形態では、ビット線が奇数ビット線と偶数ビット線に分割されていない。このような構造は一般に、全ビット線構造と呼ばれる。全ビット線構造では、あるブロックの全てのビット線を、読み出し動作とプログラム動作中に同時に選択することが可能である。共通のワード線に沿っており、いずれかのビット線に接続されているメモリセルを同時にプログラムすることが可能である。40

#### 【0040】

別の実施形態では、ビット線を平面に分割している。たとえば、左側平面（最も左側の4256個のビット線）と右側平面（最も右側の4256個のビット線）がありえる。各平面は互いに別個にプログラムしたり双方同時にプログラムしたりすることが可能である。一部の実施形態では、3つ以上の平面がありえる。他の配置を用いることも可能である。

#### 【0041】

奇数／偶数ビット線構造を使用する1つの実施形態では、読み出しおよびプログラミング動作中に4,256のメモリセルが同時に選択される。選択されるメモリセルは、同じワード線（例えば、WL2-i）と、同じ種類のビット線（例えば、偶数ビット線）とを50

有する。したがって、532バイトのデータが同時に読み出し又はプログラムされることが可能である。同時に読み出し又はプログラムされるこれらの532バイトのデータは、1つの論理ページを形成する。したがってこの例では、1つのブロックは、少なくとも8つの論理ページを記憶することが可能である。各メモリセルが2ビットのデータ（例えば、マルチステートメモリセル）を記憶する場合、1つのブロックは16のページを記憶する。他のサイズのブロックおよびページも使用されてもよい。さらに、図7および図8に示す構造以外の構造を、実施形態として実施することもできる。

#### 【0042】

読み出し動作と検証動作では、選択されたブロックの選択ゲートを1つ以上の選択電圧に上昇させ、選択されたブロックのうちの選択されていないワード線（たとえばWL0、WL1、WL3）を読み出しバス電圧（たとえば4.5ボルト）に上昇させて、トランジスタをパスゲートとして動作させる。選択されたブロックの選択されたワード線（たとえばWL2）は基準電圧に接続されるが、基準電圧のレベルは、読み出し動作と検証動作のそれぞれに対して指定される。これによって、関連するメモリセルの閾値電圧がこのようなレベルより高いか低いかを判定するようになる。例えば、バイナリメモリセルの読み出し動作では、選択されたワード線WL2を接地し、これによって、閾値電圧が0Vより高いかどうか検出するようになる。バイナリメモリセルの検証動作では、選択されたワード線WL2を、例えば0.8ボルトに接続し、これによって、プログラミングが進行するに連れて、閾値電圧が0.8ボルトという目標レベルに到達したかどうか検証されるようになる。読み出しおよび検証中は、ソースとp-ウェルは0ボルトにある。選択されたビット線（BLe）は、例えば0.7Vというレベルにまで予備充電される。閾値電圧が読み出しレベルまたは検証レベルより高ければ、関連のビット線（BLe）の電位レベルは高レベルを維持するが、これは、関連のメモリセルが非導電性であるからである。一方で、閾値電圧が読み出しレベルまたは検証レベルより低ければ、関連のビット線（BLe）の電位レベルは、例えば0.5ボルト未満という低レベルまで減少するが、これは、関連のメモリセルが導電性であるからである。メモリセルの状態は、ビット線に接続されて、接続された結果としてのこのビット線の電圧を感知するセンスアンプによって検出される。メモリセルがプログラムされたか消去されたかの違いは、正味の負電荷が浮遊ゲートに蓄積されているかどうかで決まる。たとえば、負電荷が浮遊ゲートに蓄積されていれば、閾値電圧は高くなり、トランジスタをエンハンスマントモードで動作可能となる。別の実施形態では、メモリセルは、メモリセル中を導通する電流を検出することによって読み出すことが可能である。

#### 【0043】

一例では、メモリセルをプログラミングするとき、ドレインとp-ウェルは0ボルトを受け、制御ゲートは大きさが漸増する一連のプログラミングパルスを受ける。1つの実施形態では、この一連のパルスの大きさは1.2～2.4ボルトの範囲である。この一連のパルスの範囲が異なりえる実施形態もある。これらパルスの大きさは、パルス毎に所定のステップサイズだけ増加する。複数ビットのデータを記憶するメモリセルを備えている1つの実施形態では、例示のステップサイズは0.2ボルト（または0.4ボルト）である。メモリセルをプログラミングしている間、プログラミングパルス同士間の期間で検証動作を実行する。十分にプログラムされたことが検証されたセルを、ビット線電圧を0からVD（たとえば2.5ボルト）まで上昇させて、例えばNANDセルで、後続のすべてのプログラミングパルスに対してロックアウトして、これらメモリセルに対するプログラミングプロセスを終了させる。

#### 【0044】

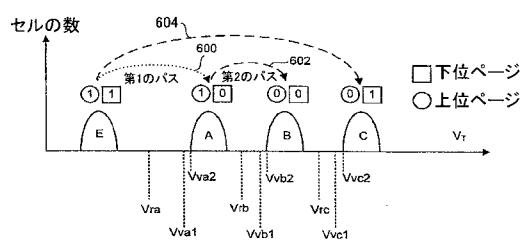

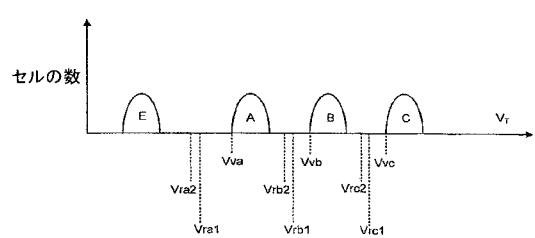

プログラムプロセスが成功裏に終了すれば、メモリセルの閾値電圧は、それぞれ必要に応じて、プログラム済みメモリセルの1つ以上の閾値電圧分布又は消去済みメモリセルの閾値電圧分布に含まれるはずである。図9に、それぞれのメモリセルが2ビットのデータを記憶している場合における、メモリセルアレイの一例の閾値電圧分布を示す。図9は、消去されたメモリセルの第1の閾値電圧分布Eを示している。プログラムされたメモリセ

10

20

30

40

50

ルの 3 つの閾値電圧分布 A、B、C もまた、示されている。1 つの実施形態では、分布 E（物理的状態 E とも呼ばれる）中の閾値電圧は負であり、分布 A、B、C（物理的状態 A、B、C とも呼ばれる）中の閾値電圧は正である。

#### 【0045】

図 9 に示す、異なる閾値電圧範囲はそれぞれが、データビットの集合の所定の値に対応している。メモリセルにプログラムされたデータとこのメモリセルの閾値電圧レベルとの間の具体的な関係は、メモリセルに対して採用されるデータ符号化スキームによって異なる。例えば、その双方を、それらの全体が参照により本明細書に援用されるものとする米国特許第 6,222,762 号と米国特許公報第 2004/0255090 号には、マルチステートフラッシュメモリセルに対するさまざまなデータ符号化方式が解説されている。10 1 つの実施形態では、グレイコード割り当て法を用いて閾値電圧範囲に対してデータ値を割り当て、これで、浮遊ゲートの閾値電圧がその隣の物理的状態に誤ってシフトしても、たった 1 ビットしか影響されないようにする。1 つの例では、「11」を閾値電圧範囲 E（状態 E）に割り当て、「10」を閾値電圧範囲 A（状態 A）に割り当て、「00」を閾値電圧範囲 B（状態 B）に割り当て、「01」を閾値電圧範囲 C（状態 C）に割り当てている。しかしながら、グレイコードを用いない実施形態もある。図 9 では 4 つの状態を示しているが、本発明は、4つより多い状態又は少ない状態を持つ構造を含む他のマルチステート構造でも用いることが可能である。

#### 【0046】

図 9 はまた、メモリセルからデータを読み出すための 3 つの読み出し比較値として、基準電圧  $V_{ra}$ 、 $V_{rb}$ 、 $V_{rc}$  を示している。所与のメモリセルの閾値電圧が  $V_{ra}$ 、 $V_{rb}$  および  $V_{rc}$  より大きいか小さいかをテストすることによって、本システムは、メモリセルがどの状態にあるかを判定することが可能である。20

#### 【0047】

図 9 はまた、3 つの検証レベルとして、電圧  $V_{va2}$ 、 $V_{vb2}$ 、 $V_{vc2}$  を示している。メモリセルを状態 A にプログラミングする際には、本システムは、これらのメモリセルの閾値電圧が  $V_{va2}$  以上であるかどうかテストする。メモリセルを状態 B にプログラミングする際には、本システムは、これらのメモリセルの閾値電圧が  $V_{vb2}$  以上であるかどうかテストする。メモリセルを状態 C にプログラミングする際には、本システムは、これらのメモリセルの閾値電圧が  $V_{vc2}$  以上であるかどうかを決定する。30

#### 【0048】

1 つの実施形態では、総シーケンスプログラミングとして知られているが、メモリセルを、消去状態 E からプログラム済み状態 A、B、C のうちのどれにでも直接的にプログラムすることが可能である。一部のメモリセルが状態 E から状態 A にプログラムされている間に、他のメモリセルを状態 E から状態 B にプログラムしたりおよび / または状態 E から状態 C にプログラムしたりする。

#### 【0049】

上記の総シーケンスプログラミングに加えて、図 9 に、互いに異なった 2 つのページ、すなわち、下位ページと上位ページ分のデータを記憶しているマルチステートメモリセルをプログラミングする 2 パス式技法の例を示す。状態 E の場合、両ページとも「1」を記憶している。状態 A の場合、下位ページは「0」を記憶し、上位ページは「1」を記憶している。状態 B の場合、両ページとも「0」を記憶している。状態 C の場合、下位ページは「1」を記憶し、上位ページは「0」を記憶している。ここで、特定のビットパターンがそれぞれの状態に割り当てられているが、別のビットパターンを割り当ててもよい。40

#### 【0050】

第 1 のプログラミングパスでは、メモリセルの閾値電圧レベルが、下位の論理ページにプログラムされるビットにしたがって設定される。このビットが論理「1」であれば、この閾値電圧は変更されないが、これは、前に消去されている結果として適切な状態にあるからである。しかしながら、このプログラムされるビットが論理「0」であれば、このセルの閾値電圧レベルは、矢印 600 で示すように状態 A にまで引き上げられる。これで、50

第1のプログラミングパスが完結する。

**【0051】**

第2のプログラミングパスでは、メモリセルの閾値電圧レベルが、上位の論理ページにプログラムされるビットにしたがって設定される。この上位論理ページビットが論理「1」を記憶するのであれば、なんらプログラミングされないが、これは、このセルが、双方ともが「1」という上位ページビットを有している、下位ページビットのプログラミングしだいで決まる状態EまたはAのうちの一方の状態にあるからである。上位ページビットが論理「0」となるのであれば、閾値電圧ははずれる。第1のパスの結果、セルが消去状態Eのままであれば、第2のフェーズで、このセルは、閾値電圧が、矢印604で示すように状態C内に来るよう増大されるようにプログラムされる。このセルが、第1のプログラミングパスの結果として状態Aにプログラムされた場合、メモリセルは、矢印602で示すように閾値電圧が状態B内に来るよう、第2のパスでさらにプログラムされる。第2のパスの結果、下位ページのデータを変更することなく、上位ページの論理「0」を記憶するように指定された状態にセルをプログラムすることになる。10

**【0052】**

1つの実施形態では、ページ全体を満たすに十分なデータを書き込まれた場合に、総シーケンス書き込みを実行するようにシステムをセットアップすることが可能である。ページ全体を満たすに十分なデータが書き込まれない場合、プログラミングプロセスは、受信したデータによる下位ページのプログラミングをプログラムすることが可能である。さらにその後にデータが受信されると、本システムは、上位ページをプログラムする。別の実施形態では、このシステムは、ワード線のメモリセルの全部（またはほとんど）を満たすに十分なデータがその後に受信されるのであれば、下位ページをプログラムするモードで書き込みを始めるとともに、総シーケンスプログラミングモードに変換することが可能である。このような実施形態のさらなる詳細が、その全体を参照して本明細書に援用される、発明者Sergy Anatolievich GorobetsとYan Liによる、2004年12月14日に出願された「Pipelined Programming of Non-Volatile Memories Using Early Data」という名称の米国特許出願第11/013,125号に開示されている。20

**【0053】**

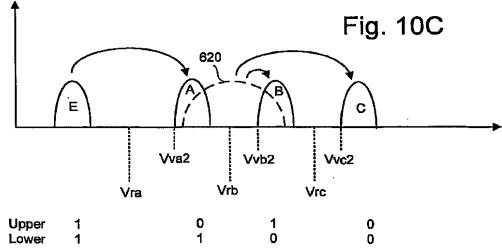

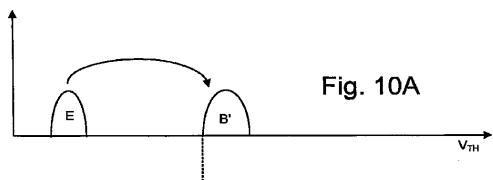

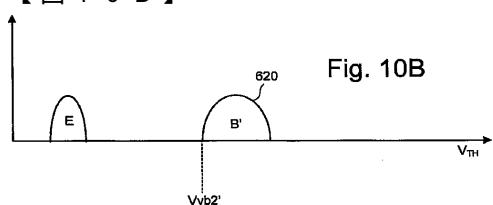

図10A～Cに、前のページの隣接するメモリセルに書き込んだ後に特定のページに関するなんらかの特定のメモリセルに書き込み動作を実行することによって、この特定のメモリセルに対する、浮遊ゲート同士のカップリングの影響を軽減する不揮発性メモリをプログラミングする別のプロセスを示す。図10A～Cに示すこのプロセスの1つの実施形態では、この不揮発性メモリセルのそれぞれが、4つのデータ状態を用いてメモリセル毎に2ビットのデータを記憶する。例えば、状態Eが消去された状態で、状態A、BおよびCがプログラムされた状態と仮定する。状態Eはデータ11を記憶している。状態Aはデータ01を記憶している。状態Bはデータ10を記憶している。状態Cはデータ00を記憶している。隣り合った状態Aと状態Bの間で双方のビットが変化するので、これはノングレイコーディングの例である。データをデータの物理的状態に符号化する他の方法も用いることが可能である。それぞれのメモリセルが2ページ分のデータを記憶している。参考目的で、これらのページのデータを下位ページと上位ページと呼ぶが、別のラベルを付けることも可能である。図10A～Cのプロセスに対する状態Aを参照して、上位ページデータは0、下位ページデータは1とする。状態Bを参照して、上位ページデータは1、下位ページデータは0とする。状態Cを参照して、双方のページはデータ0を記憶する。3040

**【0054】**

図10A～Cのプログラミングプロセスは、2つのステップのプロセスである。第1のステップでは、下位ページをプログラムする。この下位ページがデータ1の状態にとどまることになっている場合、メモリセルの状態は状態Eのままである。このデータが0にプログラムされることになっている場合、メモリセルが状態B'にプログラムされるように、メモリセルの閾値電圧を引き上げる。そこで図10Aに、状態Eから状態B'にメモリ50

セルをプログラミングする様子を示す。図10Aに示す状態B'は中間状態Bである。したがって、検証目標レベルを、Vvb2より低いVvb2'として示す。

#### 【0055】

1つの実施形態では、あるメモリセルが状態Eから状態B'にプログラムされた後では、NANDストリング中のその隣のメモリセルはその下位ページに対してプログラムされる。例えば、図2を見ると、メモリセル106の下位ページがプログラムされた後で、メモリセル104の下位ページがプログラムされる。メモリセル104をプログラミングした後では、メモリセル104の閾値電圧が状態Eから状態B'に上昇していれば、浮遊ゲート同士間の結合による影響のため、メモリセル106の見かけ上の閾値電圧が上昇する。これによって、状態Bの閾値電圧分布の幅を図10Bの閾値電圧分布620として示す分布にまで広げる作用がある。この閾値電圧分布の見かけ上の拡大は、上位ページをプログラミングするときに修正される。

#### 【0056】

図10Cは、上位ページをプログラミングするプロセスを示している。メモリセルが消去された状態Eにあって上位ページが1のままとどまるのであれば、このメモリセルは状態Eのままである。メモリセルが状態Eにあってその上位ページデータを0にプログラミングすることになっているのであれば、このメモリセルの閾値電圧を引き上げて、メモリセルが状態Aとなるようにする。メモリセルが中間閾値電圧分布620中にあって、上位ページデータが1にとどまることになっている場合、このメモリセルは最終状態Bにプログラムされる。メモリセルが中間閾値電圧分布620中にあって、上位ページデータがデータ0になることになっている場合、このメモリセルの閾値電圧を引き上げて、メモリセルが状態Cとなるようにする。図10A～10Cに示すプロセスによって、浮遊ゲート同士間の結合による影響が減少するが、これは、セルが、図9のように状態Eから状態Cにプログラムされるのではなく、状態Eから状態Aに又は状態B'から状態Cにプログラムされると、上位ページをプログラミングしている間に発生する最大のVtシフトが減少し、その結果、隣のメモリセルの上位ページをプログラミングすることによる所与のメモリセルの見かけ上の閾値電圧に対する影響が軽減されるためである。図10A～Cは4つのデータ状態と2つのページに対する一例を示しているが、図10A～Cによって示される概念は、4つ以上又は4つ未満の状態や、2ページ以上又は2ページ未満である他の実施形態にも適用することができる。

#### 【0057】

ここで、さまざまなページをプログラミングするさまざまな順序が存在する。本発明は、特定の実施形態にとって適切なように、さまざまなページをプログラミングするさまざまな多くの順序に用いることが可能である。プログラミングに関するさらなる情報は、その全体を参照して本明細書で援用されるJian Chenによって2005年4月5日に出願された米国特許出願第11/099,133号「Compensating for Coupling During Read Operations of Non-Volatile Memory」に見受けられる。

#### 【0058】

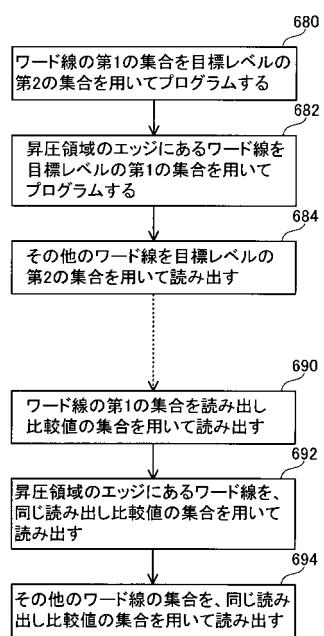

プログラム外乱による影響を軽減するために、プログラミングプロセスの1つ以上の検証ステップ中で特定のワード線（または他の記憶素子グループ）に対してさまざまな目標検証レベルを用いることが可能である。図11に、ソース選択ゲートとソース選択線に隣接するワード線に対する目標レベルの1つの集合と、その他のワード線に対する目標レベルの別の集合とを用いるプロセスの1つの実施形態を説明するフローチャートを示す。図11のステップ650で、最初にプログラムされるワード線であり、また、ソース選択線SGSの隣のワード線であるワード線WL0（図2、3、8を参照）を、目標レベルの第1の集合を用いてプログラムする。すなわち、WL0に接続されているメモリセルのすべてまたは部分集合を目標レベルの第1の集合を用いてプログラムして、それぞれのメモリセルがプログラミングを完了したかどうか検証する。ステップ652で、残りの（または別の部分集合の）ワード線を、目標レベルの第2の集合を用いてプログラムする。すなわ

10

20

30

40

50

ち、例えば、W L 1 ~ W L 4 に接続されているメモリセルのすべてまたは部分集合を目標レベルの第 2 の集合を用いてプログラムして、それぞれのメモリセルがプログラミングを完了したかどうか検証する。図 5 を見ると、ワード線 W L 0 は昇圧領域 380 のエッジのところにある。

#### 【 0 0 5 9 】

1 つの実施形態では、目標レベルの第 1 の集合は V v a 1 、 V v b 1 および V v c 1 を含んでおり、第 2 の目標レベル集合は V v a 2 、 V v b 2 および V v c 2 を含んでいる。1 つの実施形態では、 V v a 1 は対応する V v a 2 より低い 100 ~ 200 mV 台であり、 V v b 1 は対応する V v b 2 より低い 100 ~ 200 mV 台であり、 V v c 1 は対応する V v c 2 より低い 100 ~ 200 mV 台である。

10

#### 【 0 0 6 0 】

目標レベルの第 1 の集合の部分集合が、目標レベルの第 2 の集合の部分集合と同じであり得るような実施形態もある。これは、一部の実施形態では、プログラム外乱が、プログラムされた状態のうちの一部の状態（たとえば状態 A または状態 A と B ）にあるメモリセルにとって問題となるだけの場合があるからである。したがって、一部の実施形態では、目標レベルの第 1 の集合は V v a 1 、 V v b 2 および V v c 2 を含んでおり、目標レベルの第 2 の集合は V v a 2 、 V v b 2 および V v c 2 を含んでいる。目標レベルの第 1 の集合が V v a 1 、 V v b 1 および V v c 2 を含んでおり、目標レベルの第 1 の集合が V v a 2 、 V v b 2 および V v c 2 を含んでいる実施形態もある。他の順列でも実施可能である。

20

#### 【 0 0 6 1 】

第 1 の集合と第 2 の集合の目標レベルに含まれる目標レベルは、あるメモリセルがいつプログラミングを終了したかを判定するためにプログラミングプロセス中で用いられる比較ポイントである。例えば、状態 A にプログラムすることが意図されている W L 0 上のメモリセルは、その閾値電圧が V v a 1 に到達したときにプログラミングプロセスが終了し、状態 B にプログラムすることが意図されている W L 3 上のメモリセルは、その閾値電圧が V v b 2 に到達したときにプログラミングプロセスが終了する。

#### 【 0 0 6 2 】

2 フェーズの粗 / 密プログラミング方法を用いてプログラムするデバイスがいくつか存在する。第 1 のフェーズである粗プログラミングフェースでは、閾値電圧を速く上昇させようとして、緊密な閾値分布を達成することには比較的注意を払わない。第 2 のフェーズである密プログラミングフェースでは、閾値電圧をゆっくりと上昇させて目標の閾値電圧に到達させ、同時に、緊密な閾値分布を達成しようとする。粗 / 密プログラミング方法の例は、その全体を参照して本明細書で援用される次の特許文献に見受けられる。米国特許公報第 2005 / 0162916 号、米国特許第 6,301,161 号、米国特許第 5,712,815 号、米国特許第 5,220,531 号、米国特許第 5,761,222 号。プログラミング中にメモリセルを検証するとき、一部の先行ソリューションでは、最初に、中間検証レベルを用いて粗モードに対する検証プロセスを実行し、次に、検証のための目標レベルを用いて密モードに対する検証プロセスを実行する。目標レベルを変更する本ソリューションでは、密モード中に検証用の目標レベルを印加する。場合によっては、中間検証レベルも変更することが可能である。

30

#### 【 0 0 6 3 】

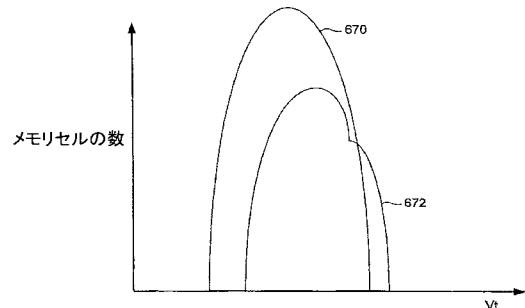

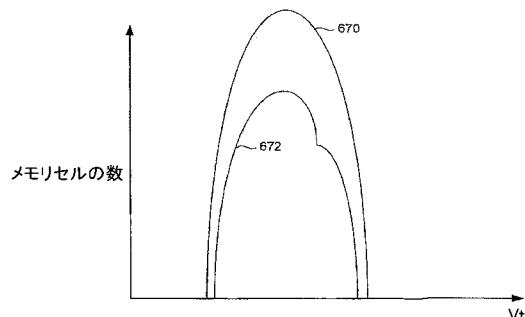

ワード線 W L 0 の目標レベルを下げるによって、 W L 0 に接続されているプログラム済みのメモリセルの閾値電圧は、この目標レベルが下げられなかった場合と比較して、メモリセルの母集団全体に亘って下がるはずである。例えば、図 12A に、1 つのプログラム状態（たとえば状態 A ）の 2 つの閾値分布を示す。分布 670 は、ワード線 W L 0 以外の全てのワード線に接続されているメモリセルの閾値電圧分布（閾値電圧に対するメモリセルの数）の一例を表している。分布 672 は、ワード線のすべてが同じ目標レベルを用いているときのワード線 W L 0 に接続されているメモリセルの閾値電圧分布の一例を表している。上記のプログラム外乱のため、分布 672 は、分布 670 と比較して右側にシフ

40

50

トして広がっている。見れば分かるように、分布 672 の上端は、分布 670 から突出している。

#### 【0064】

ステップ 650 と 652においてワード線 WL0 に対して低い目標レベルの集合を用いることによって、WL0 に接続されているプログラム済みメモリセルの閾値電圧分布は左側にシフトし、これによって、プログラミングプロセスが完了した時点では他のワード線と関連する対応する閾値電圧分布に含まれるようにする例えば、図 12B に、ワード線 WL0 に対して低い目標レベルを用いて、分布 672 が分布 670 の内側に収まるようにした結果、プログラミングプロセスが完了した（デジタル写真や他のファイルなどのデータ集合の保管に対応するために 1 ページや多くのページがプログラムされた）後に左側にシフトした分布 672 を表す。別の実施形態では、分布 672 は、ワード線 WL0 に対して低い目標レベルを用いて、分布 672 の上端が分布 670 から突出する度合いが図 12A に示すそれと比較して少なくとも減少するようにした結果、プログラミングプロセスが完了した（デジタル写真や他のファイルなどのデータ集合の保管に対応するために 1 ページや多くのページがプログラムされた）後に左側にシフトする。分布 672 の上端が分布 670 から突出する度合いが図 12A に示すそれと比較して少なくとも減少すると、読み出しプロセス中に（例えば ECC を利用して）他のどのような誤りでも訂正される。10

#### 【0065】

ここで、分布 672 と分布 670 は 1 つの状態（例えば状態 A、B、C または他の状態）を表している。ある例では、3 つのプログラム状態（と消去状態）があって、分布 672 と 670 に類似した対応する最大で 3 対の閾値電圧分布が存在する。3 ビット以上の情報をメモリセルに記憶することを想定した実施形態では、分布 672 と 670 に類似した 4 対以上の閾値電圧分布が存在し得る。場合によっては、あらゆる状態の分布が WL0 上でシフトするとは限らない。20

#### 【0066】

図 11 を見ると、ステップ 660 で、WL0 に接続されているメモリセルのすべてまたは部分集合が、読み出し比較値の集合を用いて読み出される。例えば、読み出し比較値 Vra、Vrb、Vrc（図 9 を参照）を用いて、メモリセルに記憶されているデータを読み出すことが可能である。ステップ 662 で、WL0 以外のワード線に接続されているメモリセルのすべてまたは部分集合が、ステップ 660 で用いられたと同じ読み出し比較値の集合を用いて読み出される。ここで、ステップ 652 と 660 の間にある矢印を破線として、ステップ 660 が、ステップ 650 や 652 とは異なった時点でおよび / またはステップ 651 や 652 とは関連しない方法で実行され得ることを示している。30

#### 【0067】

図 13 に、昇圧領域のエッジのあるワード線に対しては目標レベルの 1 つの集合を用い、その他のワード線に対しては目標レベルの別の集合を用いるプロセスの実施形態を説明するフローチャートを示す。上述した図 11 のプロセスでは、WL0 は昇圧領域のエッジのあるところにある。しかしながら、昇圧領域のエッジ部分が、他の場所であってもよい実施形態もある。図 13 のステップ 680 で、ワード線の第 1 の集合に接続されているメモリセルを目標レベルの第 2 の集合を用いてプログラムして、それぞれのメモリセルのプログラミングが完了したかどうか検証する。ステップ 682 で、昇圧領域のエッジのあるワード線に接続されているメモリセルを目標レベルの第 1 の集合を用いてプログラムして、それぞれのメモリセルのプログラミングが完了したかどうか検証する。ステップ 684 で、その他のワード線に接続されているメモリセルを目標レベルの第 2 の集合を用いてプログラムして、それぞれのメモリセルのプログラミングが完了したかどうか検証する。ワード線のさらに別の集合とさらに別のエッジのワード線を含むことが可能な実施形態もある。40

#### 【0068】

ステップ 690 で、ワード線の第 1 の集合に接続されているメモリセルを、読み出し比較値の集合（たとえば Vra、Vrb、Vrc）を用いて読み出す。ステップ 692 で、50

プログラミング中に昇圧領域のエッジにあるワード線に接続されているメモリセルを、ステップ 692 で用いたのと同じ読み出し比較値の集合を用いて読み出す。ステップ 694 で、他のワード線の集合に接続されているメモリセルを、ステップ 692 で用いたのと同じ読み出し比較値の集合を用いて読み出す。ここで、ステップ 684 と 690 の間にある矢印を破線として、ステップ 690 が、ステップ 684 とは異なった時点でおよび／またはステップ 684 とは関連しない仕方で実行され得ることを示している。

#### 【0069】

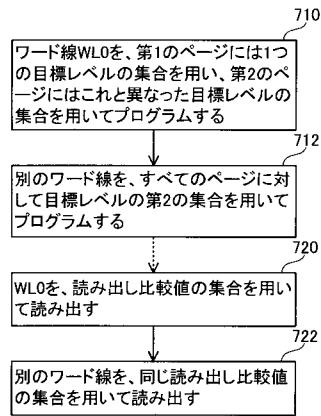

図 14 に、昇圧領域のエッジのところにある（たとえばソース選択線の隣にある）ワード線と接続している互いに異なったデータページに対しては目標レベルの互いに異なった集合を用い、他のワード線に対しては目標レベルの別の集合を用いるプロセスの実施形態を説明するフローチャートを示す。ステップ 710 で、ワード線 WL0（または別のワード線）に接続されているメモリセルを、第1のデータページ用の目標レベルの第1の集合（Vva1、Vvb1、Vvc1）と第2のデータページ用の目標レベルの別の集合を用いてプログラムする。例えば、この目標レベルの別の集合には Vva3、Vvb3、Vvc3 が含まれるが、ここで次式が成立する。

$$(1) Vva3 \quad Vva1, Vvb3 \quad Vvb1, Vvc3 \quad Vvc1 \text{ および,}$$

$$(2) Vva3 < Vva2, Vvb3 < Vvb2, Vvc3 < Vvc2$$

この目標レベルの別の集合に、Vva3、Vvb3、Vvc3 の一部を含み、残りの目標レベルが、目標レベルの第1または第2の集合と同じであることが可能な実施形態もある。

ステップ 712 で、WL0 以外の別のワード線に接続されているメモリセルが、上述したように、目標レベルの第2の集合を用いてプログラムされる。

#### 【0070】

ステップ 720 で、WL0 に接続されているメモリセルのすべてまたは部分集合が、読み出し比較値の集合（例えば、Vra、Vrb、Vrc）を用いて読み出される。ステップ 722 で、WL0 以外のワード線に接続されているメモリセルのすべてまたは部分集合が、ステップ 720 で用いられたのと同じ読み出し比較値の集合を用いて読み出される。ここで、ステップ 712 と 720 の間にある矢印を破線として、ステップ 720 が、ステップ 712 や 710 とは異なった時点でおよび／またはステップ 712 や 710 とは関連しない仕方で実行され得ることを示している。

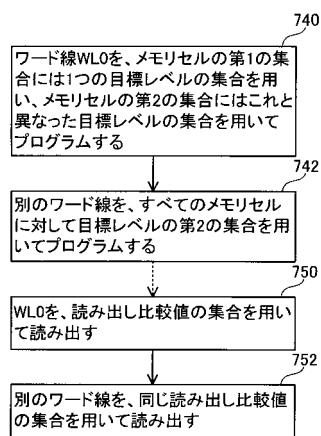

#### 【0071】

図 15 に、昇圧領域のエッジのところにあるワード線（たとえば、WL0 などのソース選択線の隣にあるワード線）と接続している互いに異なった平面（またはセクションもしくはグループ）のメモリセルに対しては目標レベルの互いに異なった集合を用い、他のワード線に対しては目標レベルの別の集合を用いるプロセスの実施形態を説明するフローチャートを示す。ステップ 740 で、ワード線 WL0（または別のワード線）に接続されているメモリセルを、メモリセルの第1の集合用の目標レベルの第1の集合とメモリセルの第2の集合用の目標レベルの別の集合を用いてプログラムする。ステップ 742 で、WL0 以外の別のワード線に接続されているメモリセルを、目標レベルの第2の集合を用いてプログラムする。

#### 【0072】

例えば図 8 を見ると、第1の平面またはグループに、ビット線 B1e0 ~ B1e2127 に接続されている NAND ストリング上のメモリセルを含み、第2の平面またはグループに、ビット線 B1e2128 ~ B1e4255 に接続されている NAND ストリング上のメモリセルを含むことが可能である。別の実施形態では、第1の平面またはグループに、ビット線 B1o0 ~ B1o2127 に接続されている NAND ストリング上のメモリセルを含み、第2の平面またはグループに、ビット線 B1o2128 ~ B1o4255 に接続されている NAND ストリング上のメモリセルを含むことが可能である。別の代替例で

10

20

30

40

50

は、第1の平面またはグループに、ビット線 $0 \sim (1/2(x) - 1)$ に接続されているNANDストリング上のメモリセルが含まれ、第2の平面またはグループに、ビット線 $1/2(x) \sim (x - 1)$ に接続されているNANDストリング上のメモリセルを含むことが可能であるが、ここで、 $x$ はユーザデータ用のビット線の総数である。別の代替例では、第1の平面またはグループに、奇数線に接続されているNANDストリング上のメモリセルが含まれ、第2の平面またはグループに、偶数ビット線に接続されているNANDストリング上のメモリセルを含むことが可能である。他のグループ分けを用いてもよく、3つ以上のグループを用いることが可能である。

#### 【0073】

ステップ750で、WL0（または別のワード線）に接続されているメモリセルのすべてまたは部分集合が、読み出し比較値の集合（たとえば、Vra、Vrb、Vrc）を用いて読み出される。ステップ752で、WL0以外のワード線に接続されているメモリセルのすべてまたは部分集合が、ステップ750で用いられたと同じ読み出し比較値の集合を用いて読み出される。ここで、ステップ742と750の間に矢印を破線として、ステップ750が、ステップ740や742とは異なった時点でおよび／またはステップ740や742とは関連しない仕方で実行され得ることを示している。

10

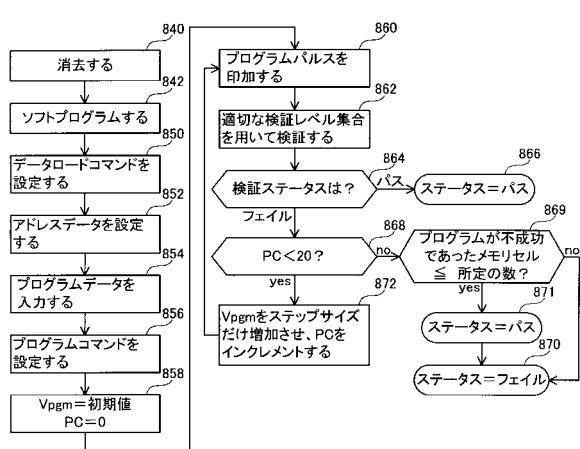

#### 【0074】

図16に、プログラミング動作の1つの実施形態を説明するフローチャートを示す。図16のプロセスは、ワード線に接続されているメモリセルを総シーケンスプログラミング法を用いてプログラムするために用いることが可能である。時点が異なればプログラムするページも異なる実施形態では、図16のプロセスは、特定のワード線もしくは特定のメモリセルの集合の1ページまたは1パスをプログラムするために用いることが可能である。プログラミングプロセスでは、複数のページや、複数のワード線に接続されているメモリセルがプログラミングされることがあるため、プログラミングプロセスで、図16のプログラミング動作が複数回実行され得ることもある。

20

#### 【0075】

ステップ840で、プログラムするメモリセルを消去する。ステップ840で、これらプログラムするメモリセルより多くのメモリセルが（たとえば、ブロック単位や他の単位で）消去されることがある。ステップ842で、ソフトプログラミングを実行して、これら消去されたメモリセルの消去閾値電圧の分布の幅を狭める。一部のメモリセルは、この消去プロセスの結果、必要以上に深く消去された状態にある。ソフトプログラミングでは、小さいプログラミングパルスを印加して、この消去されたメモリセルの消去閾値電圧を消去検証レベルに近づけることが可能である。図16のステップ850で、「データをコードする」コマンドが、コントローラ518によって発行されて、コマンド回路514に入力され、これで、データをデータ入／出力バッファ512に入力することが可能となる。この入力データは、コマンドと認識されて、コマンド回路514に入力されたコマンドラッチ信号（図示せず）を介して状態マシン516によってラッチされる。ステップ852で、ページアドレスを指定するアドレスデータが、コントローラすなわちホストから行コントローラすなわちデコーダ506に入力される。この入力データは、ページアドレスと認識されて、コマンド回路514に入力されたアドレスラッチ信号に影響されて、状態マシン516を介してラッチされる。ステップ854で、アドレス指定されたページに対するプログラムデータページが、プログラミング目的でデータ入／出力バッファ512に入力される。たとえば、1つの実施形態では、582バイトのデータを入力することが可能である。このデータは、選択されたビット線に対して適切なレジスタにラッチされる。このデータが、検証動作目的で用いられるように選択されたビット線に対する第2のレジスタにもラッチされる実施形態もある。ステップ856で、「プログラム」コマンドが、コントローラ518によって発行されて、データ入／出力バッファ512に入力される。このコマンドは、コマンド回路514に入力されたコマンドラッチ信号を介して状態マシン516によってラッチされる。

30

#### 【0076】

40

50

「プログラム」コマンドがトリガーとなって、ステップ 854 でラッチされたデータが、適切なワード線に印加された段付きパルスを用いて状態マシン 516 によって制御されている選択されたメモリセルにプログラムされる。ステップ 858 で、選択されたワード線に印加されるプログラミング電圧パルス V<sub>pgm</sub> が、開始規模（たとえば 12V まで、または他の適切なレベル）に初期化され、状態マシン 516 によって維持されているプログラムカウンタ PC が 0 に初期化される。ステップ 860 で、最初の V<sub>pgm</sub> パルスが選択されたワード線に印加される。特定のデータラッチに論理「0」が記憶されており、対応するメモリセルをプログラムすべきであることを示していれば、対応するビット線を接地する。逆に、特定のデータラッチに論理「1」が記憶されており、対応するメモリセルはその現在のデータ状態に留まるべきであることを示していれば、対応するビット線を V<sub>DD</sub> に接続して、プログラミングを抑止する。図 4 と 5 に示すように、選択されていないワード線は V<sub>pass</sub> を受け、ドレイン選択信号は V<sub>sqd</sub> に設定され、ソース選択信号は 0V に設定される。ソース線は 0 ボルトまたはほぼ 0 ボルトに設定される。

#### 【0077】

ステップ 862 で、選択されたメモリセルの状態が、図 11、13、14、15 を参照して上述したように、適切な目標レベル集合を用いて検証される。選択されたセルの閾値電圧が適切な目標レベルに到達したことが検出されたら、対応するデータラッチに記憶されているデータが論理「1」に変更される。この閾値電圧が適切な目標レベルに到達していないことが検出されたら、対応するデータラッチに記憶されているデータは変更されない。このようにして、対応するデータラッチに論理「1」が記憶されているビット線はプログラムする必要はない。データラッチがすべて論理「1」を記憶していれば、状態マシンは、選択されたセルがすべてプログラムされたことを知る。ステップ 864 で、データラッチのすべてが論理「1」を記憶しているかどうかチェックされる。そうであれば、プログラミングプロセスは成功裏に完了するが、これは、選択されたメモリセルがすべてその目標状態にプログラムされて、その状態に到達したことが検証されたからである。ステップ 866 で、「バス」状態が報告される。ここで、一部の実施形態では、ステップ 864 で、少なくとも所定の数のデータラッチが論理「1」を記憶しているかどうかチェックされる。この所定の数は、データラッチの総数未満であってもよい。これによって、すべてのメモリセルがその適切な検証レベルに到達する以前に停止することを可能としている。成功裏にプログラムされなかったメモリセルは、読み出しプロセス中に誤り訂正法を用いて訂正することが可能である。

#### 【0078】

ステップ 864 で、データラッチのすべてが論理「1」を記憶しているわけではないと判定されると、プログラミングプロセスは継続される。ステップ 868 で、プログラムカウンタ PC がプログラム制限値に達したかどうかチェックされる。プログラム制限値の一例として 20 という値があるが、しかしながら、様々な実施形態で他の値を用いてもよい。プログラムカウンタ PC が 20 以上であれば、成功裏にプログラムされなかったメモリセルの数が所定の数以下であるかどうかステップ 869 で判定する。プログラムが不成功であったメモリセルの数がこの所定の数以下であれば、プログラミングプロセスは、バスした旨のフラグが設定され、ステップ 871 でバス状態が報告される。多くの場合、成功裏にプログラムされなかったメモリセルは、読み出しプロセス中に誤り訂正法を用いて訂正することが可能である。しかしながら、プログラムが不成功であったメモリセルの数が所定の数より大きいときは、プログラミングプロセスは、フェイルした旨のフラグが設定され、ステップ 870 でフェイル状態が報告される。プログラムカウンタ PC が 20 未満であれば、ステップ 872 で、V<sub>pgm</sub> レベルがステップサイズ（たとえば 0.2 ~ 0.4 ボルトのステップサイズ）だけ増加され、プログラムカウンタ PC がインクリメントされる。ステップ 872 の後で、プロセスはステップ 860 にループバックして、次の V<sub>pgm</sub> パルスを印加する。

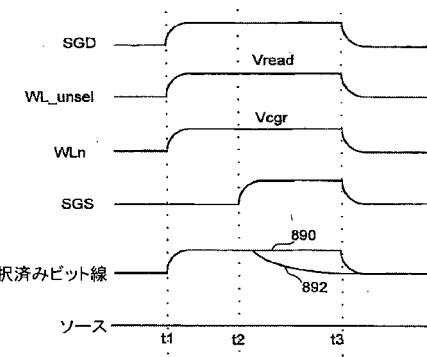

#### 【0079】

図 17 は、読み出し動作または検証動作を一回繰り返す間ににおけるさまざまな信号の動

10

20

30

40

50

作を示すタイミング図である。たとえば、メモリセルがバイナリメモリセルの場合、図17のプロセスは、読み出しプロセスまたは検証プロセスの間におのののメモリセルに対して並列に実行される。メモリセルが4つの状態（たとえばE、A、B、C）のマルチステートメモリセルの場合、図17のプロセスが読み出しプロセスまたは検証プロセスの間に各々のメモリセルに対して並列に3回実行される。例えば、4つの状態を持つメモリセルからデータを読み出すとき、読み出しプロセスは、 $V_{cgr} = V_{ra}$ で一回、 $V_{cgr} = V_{rb}$ で一回、 $V_{cgr} = V_{rc}$ または他の読み出し値の集合で一回実行してもよい。4つの状態を持つメモリセルに対してデータを検証するとき、読み出しプロセスは、 $V_{cgr} = V_{va2}$ で一回、 $V_{cgr} = V_{vb2}$ で一回、 $V_{cgr} = V_{vc2}$ または他の検証レベル集合で一回実行してもよい。

10

#### 【0080】

一般的に、読み出し動作と検証動作中は、選択されたワード線はある電圧に接続されるが、そのレベルは読み出し動作と検証動作それぞれに対して指定され、これによって、関連のメモリセルの閾値電圧がこのようなレベルに達したかどうか判定するようとする。このワード線電圧を印加した後、このメモリセルの導電電流を測定して、ワード線に印加された電圧に応答してメモリセルがオンしたかどうか判定する。導電電流の測定値がある値より大きい場合、メモリセルはオンしてワード線に印加された電圧はメモリセルの閾値電圧より高いと推測される。導電電流の測定値がそのある値より大きくなかった場合、メモリセルはオンせず、ワード線に印加された電圧はメモリセルの閾値電圧より高くなないと推測される。

20

#### 【0081】

読み出し動作または検証動作中に、あるメモリセルの導電電流を測定する多くの方法が存在する。一例では、あるメモリセルの導電電流を、それが、センスアンプ内の専用キャパシタを放電する速度で測定する。1つの実施形態では、全ビット線プログラミング方式を用いているメモリアレイでは、あるメモリセルの導電電流を、それが、センスアンプ内の専用キャパシタを放電する速度で測定することが可能である。別の例では、選択されたメモリセルの導電電流によって、このメモリセルを含んでいるNANDストリングがビット線を放電させる（又は放電させない）。ビット線上の電荷をある時間期間後に測定して、放電したかどうか判定する。1つの実施形態では、奇数／偶数プログラミング方式を用いているメモリアレイでは、あるメモリセルの導電電流を、ビット線が放電したかどうかを判定することによって測定することが可能である。

30

#### 【0082】

図17に、信号SGD、WL\_unsel、WL\_n、SGS、選択済みビット線およびVss（約0ボルト）から始まるソースを示す。SGDは、ドレイン選択ゲートのゲートに接続されているドレイン選択線上的信号を表す。SGSは、ソース選択ゲートのゲートに接続されているソース選択線上的信号を表す。WL\_nは、読み出し／検証目的で選択されたワード線である。WL\_unselは、選択されなかったワード線を表す。選択済みビット線は、読み出し／検証目的で選択されたビット線である。ソースは、メモリセルに対するソース線である。

40

#### 【0083】

図17に、あるメモリセルの導電電流を、ビット線が適切に放電したかどうかを判定することによって測定するシステムの動作を説明する。図10に示す時点t1で、SGDをVdd（たとえば約3.5ボルト）又は、一般的には3~5V範囲の別の電圧にまで上げ、選択されなかったワード線（WL\_unsel）をVread（たとえば約5.5ボルト）まで上げ、選択されたワード線WL\_nをVcgrまで上げ、選択されたビット線である選択済みビット線を約0.7ボルトまで予備充電する。電圧Vreadはバス電圧として動作するが、これは、この電圧によって、選択されなかったメモリセルがオンして、バスゲートとして動作するからである。時点t2で、SGSをVddまで上げて、ソース選択ゲートをオンさせる。これによって、ビット線上の電荷を減少させる経路が発生する。読み出し目的で選択されたメモリセルの閾値電圧がVcgrより大きければ、信号線89

50

0で示すように、選択されたメモリセルはオンせず（または少なくとも十分にはオンせず）、ビット線は放電しない（または少なくとも十分には放電しない）。読み出し目的で選択されたメモリセル中の閾値電圧が $V_{cgr}$ 未満であれば、曲線892で示すように、読み出し目的で選択されたメモリセルはオンし（導通し）、ビット線電圧は減少する。時点 $t_2$ より後であって時点 $t_3$ より前のある時点（特定の実施形態で決まるような時点）で、適切なセンスアンプによって、ビット線電圧が十分な量だけ減少したかどうか判定する。時点 $t_3$ で、図示する信号が $V_{ss}$ （または待機用もしくは回復用の別の値）まで下げる。ここで、これら信号のうちのあるもののタイミングが変更可能な実施形態も存在する。

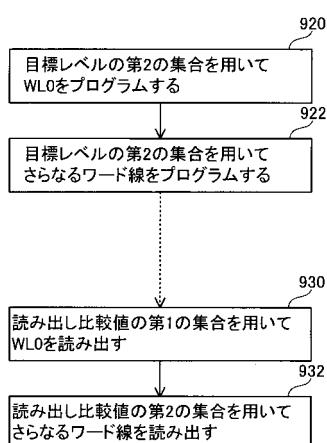

#### 【0084】

検証用の目標レベルを変更することによってプログラム外乱の影響を軽減するのではなく（またはこうすることに加えて）、読み出しプロセス中で特定のワード線（または他の記憶素子グループ）に対して互いに異なった読み出し比較値を用いることが可能である。たとえば、図18に、1つ以上の特定のワード線に対して互いに異なった読み出し比較値を用いる不揮発性記憶動作プロセスの1つの実施形態を説明する。ステップ920で、 $WL_0$ に接続されているメモリセルは、上記の目標レベルの第2の集合を用いてプログラムされる。ステップ922で、追加のワード線に接続されているメモリセルは、上記の目標レベルの第2の集合を用いてプログラムされる。ステップ930で、 $WL_0$ に接続されているメモリセルは、読み出し比較値の第1の集合を用いて読み出される。すなわち、読み出し比較値の第2の集合は、適切なワード線を介して適切な制御ゲートに印加される。ステップ932で、追加のワード線に接続されているメモリセルは、読み出し比較値の第2の集合を用いて読み出される。ここで、ステップ922と930の間にある矢印を破線として、ステップ930が、ステップ922や920とは異なった時点でおよび／またはステップ922や920とは関連しない仕方で実行され得ることを示している。

#### 【0085】

別の実施形態では、ステップ920と930を複数のワード線（例えば、以下に説明するように、 $WL_0$ 、 $WL_1$ 、 $WL_0 \sim 2$ または、 $WL_0$ を含まないがエッジのところにある集合を含む他の集合）に適用することが可能である。すなわち、2つの集合のワード線がありえる。ワード線の第1の集合は読み出し比較値の第1の集合を用いて読み出され、ワード線の第2の集合は読み出し比較値の第2の集合を用いて読み出される。

#### 【0086】

図19に、図9に示す分布に類似した閾値電圧分布の例示の集合を示す。図19は、各々の状態に対して2つの読み出し比較値を示している。読み出し比較値 $V_{ra1}$ と $V_{ra2}$ は、状態Aと関連している。読み出し比較値 $V_{rb1}$ と $V_{rb2}$ は、状態Bと関連している。読み出し比較値 $V_{rc1}$ と $V_{rc2}$ は、状態Cと関連している。1つの実施形態では、読み出し比較値の第1の集合には、 $V_{ra1}$ 、 $V_{rb1}$ 、 $V_{rc1}$ が含まれ、読み出し比較値の第2の集合には、 $V_{ra2}$ 、 $V_{rb2}$ 、 $V_{rc2}$ が含まれる。さらに、 $V_{ra1} > V_{ra2}$ 、 $V_{rb1} > V_{rb2}$ 、 $V_{rc1} > V_{rc2}$ である。したがって、ステップ930を実行するとき、図17のプロセスは、 $V_{cgr} = V_{ra1}$ で $WL_0$ に対して1回、 $V_{cgr} = V_{rb1}$ で $WL_0$ に対して1回、 $V_{cgr} = V_{rc1}$ で $WL_0$ に対して1回実行される。ステップ932を実行するとき、図17のプロセスは、 $V_{cgr} = V_{ra2}$ で対象となるワード線のおおのに対して1回、 $V_{cgr} = V_{rb2}$ で対象となるワード線の各々に対して1回実行される。読み出し比較値の第1の集合に、 $V_{ra1}$ 、 $V_{rb1}$ 、 $V_{rc1}$ が含まれたり、または、読み出し比較値の第1の集合に、 $V_{ra1}$ 、 $V_{rb2}$ 、 $V_{rc2}$ が含まれたりする実施形態もある。これ以外の順列も実施可能である。

#### 【0087】

ステップ930のもう1つの実施形態では、読み出し比較値の第1の集合を用いてワード線 $WL_0$ に接続されているメモリセルの第1の部分集合を読み出し、読み出し比較値の第3の集合を用いてワード線 $WL_0$ に接続されているメモリセルの第2の部分集合を読み

10

20

30

40

50

出す。この 2 つの部分集合は、上記したように互いに異なった平面やグループにあるメモリセルであったりする。1 つの実施形態では、この 2 つの部分集合は互いに分離している、たとえば、奇数ビット線と偶数ビット線に分かれている、すなわち、第 1 の平面またはグループに、ビット線  $0 \sim (1 / 2(x) - 1)$  に接続されている N A N D ストリング上のメモリセルが含まれ、第 2 の平面またはグループに、ビット線  $1 / 2(x) \sim (x - 1)$  に接続されている N A N D ストリング上のメモリセルが含まれるが、ここで、 $x$  はユーザデータ用のビット線の総数である。別のグループ分けも用いることが可能である。ここで、読み出し比較値の第 3 の集合は、読み出し比較値の第 2 の集合とは（部分的または完全に）異なっている。

#### 【 0 0 8 8 】

10

ステップ 930 の別の実施形態では、読み出し比較値の第 1 の集合を用いてワード線 W L 0 に接続されているメモリセルに記憶されている第 1 のデータページに対するデータを読み出し、読み出し比較値の第 3 の集合を用いてワード線 W L 0 に接続されているメモリセルに記憶されている第 2 のデータページに対するデータを読み出す。読み出し比較値の第 3 の集合は、読み出し比較値の第 2 の集合とは（部分的または完全に）異なっている。

#### 【 0 0 8 9 】

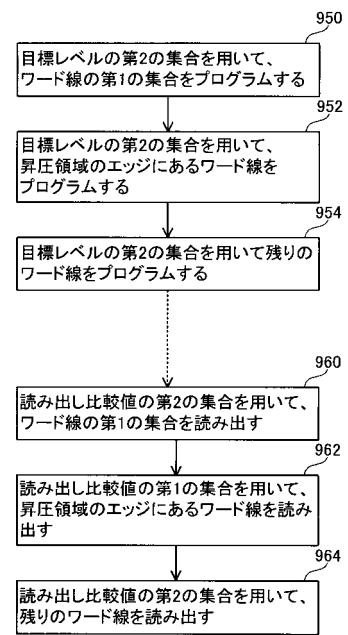

図 20 に、特定のワード線に対して互いに異なる読み出し比較値を用いる不揮発性記憶動作プロセスの別の実施形態を説明する。ステップ 950 で、ワード線の第 1 の集合に接続されているメモリセルが、上記の目標レベルの第 2 の集合を用いてプログラムされる。ステップ 952 で、昇圧領域のエッジのところにあるワード線に接続されているメモリセルが、上記した目標レベルの第 2 の集合を用いてプログラムされる。ステップ 954 で、これ以外のワード線に接続されているメモリセルが、上記した目標レベルの第 2 の集合を用いてプログラムされる。ここで、昇圧領域のエッジのところにあるワード線は、ワード線の第 1 の集合やこれ以外のワード線の一部ではない。

20

#### 【 0 0 9 0 】

図 20 のステップ 950、952、954においては、プログラミング動作によって、0 ボルト信号（または他の適切な信号）があるワード線または選択線に印加されて対応するトランジスタがオフされ、これで、昇圧領域を生成する。一例では、0 ボルトがソース選択線 S G S に印加され、これで、ソース選択ゲートがオフして、ソース線からチャネルを遮断し、N A N D ストリングが昇圧しやすくなる。一部の実施形態では、N A N D ストリングに接続されているワード線に 0 ボルト信号（または他の適切な信号）を印加して、このワード線に接続されているメモリセルを遮断して、このワード線のところで昇圧領域が終了するまたはこれから始まるようにすることが可能である。これは、複数の昇圧領域を生成するためにも利用することが可能である。

30

#### 【 0 0 9 1 】

ステップ 960 で、ワード線の第 1 の集合に接続されているメモリセルが、上記した読み出し比較値の第 2 の集合を用いて読み出される。ステップ 962 で、昇圧領域のエッジのところにあるワード線に接続されているメモリセルが、上記した読み出し比較値の第 1 の集合を用いて読み出される。ステップ 964 で、これ以外のワード線に接続されているメモリセルが、上記した読み出し比較値の第 2 の集合を用いて読み出される。ここで、ステップ 954 と 960 の間にある矢印を破線として、ステップ 960 が、ステップ 954 とは異なった時点でおよび／またはステップ 964 とは関連しない方法で実行されることを示している。

40

#### 【 0 0 9 2 】

ステップ 962 の一部の実施形態では、昇圧領域のエッジのところにあるワード線と接続しているデータページが異なれば、これを読み出す読み出し比較値の集合も異なった集合を用いることが可能である。昇圧領域のエッジのところにあるワード線と接続しているメモリセルの平面やグループを読み出すのに、互いに異なった読み出し比較値の集合を用いることが可能である。これら代替例の双方において、これら様々な読み出し比較値の集合もまた、読み出し比較値の第 2 の集合とは（部分的または完全に）異なっている。

50

## 【0093】

上記の説明は特定のワード線に対するプログラム外乱の影響を軽減することに主点を置いたものであるが、本発明は、他のなんらかの理由によってV<sub>t</sub>分布が拡大してしまうワード線による影響を軽減するためにも利用することが可能である。一部のワード線上でV<sub>t</sub>分布が拡大してしまう現象が発生するこれ以外の理由の1つとして、例えば、メモリセルの高速プログラミング動作が1つの又は限られた数のワード線に集中することによるいわゆる過剰プログラミングが挙げられる。過剰プログラミングはまた、図12に示すものと類似のV<sub>t</sub>分布をもたらす。このようなワード線に対して互いに異なった検証目標レベルまたは読み出し比較値を印加することによって、V<sub>t</sub>分布の拡大がこれらのワード線に及ぼす影響をも軽減することが可能である。

10

## 【0094】

本発明に関する前述の詳細な説明は、例証と説明のために提示されたものである。本発明を開示する形態そのもので尽きるとかこれに限るとかを意図するものではない。上記の教示に照らし合わせて、多くの修正例や変更例が可能である。説明した実施形態は、本発明とその実際の応用例の原理が最もよく説明され、これによって、他の当業者が、想定される特定の用途に適しているさまざまな実施形態で、また、様々な修正をもって、本発明を利用することが可能となるように選ばれたものである。本発明の範囲は添付請求の範囲によって定義されることを意図するものである。

## 【図面の簡単な説明】

## 【0095】

20

【図1】NANDストリングの上面図である。

【図2】NANDストリングの等価回路図である。

【図3】3つのNANDストリングを示す略図である。

【図4】NANDストリングがプログラミングされているところを示す図である。

【図5】自己昇圧方法を用いて、NANDストリングが抑止されているところを示す図である。

【図6】NANDストリングの一部分を示す図である。

【図7】メモリシステムの一例のブロック図である。

【図8】メモリアレイの編成の一例を示す図である。

【図9】閾値電圧分布の集合を示す図である。

30

【図10A】閾値電圧分布を示す図である。

【図10B】閾値電圧分布を示す図である。

【図10C】閾値電圧分布を示す図である。

【図11】不揮発性メモリをプログラミングして読み出すプロセスの1つの実施形態を説明するフローチャートである。

【図12A】閾値電圧分布を示す図である。

【図12B】閾値電圧分布を示す図である。

【図13】不揮発性メモリをプログラミングして読み出すプロセスの1つの実施形態を説明するフローチャートである。

【図14】不揮発性メモリをプログラミングして読み出すプロセスの1つの実施形態を説明するフローチャートである。

40

【図15】不揮発性メモリをプログラミングして読み出すプロセスの1つの実施形態を説明するフローチャートである。

【図16】プログラミング動作の1つの実施形態を説明するフローチャートである。

【図17】読み出し動作の1つの実施形態を説明する信号図である。

【図18】不揮発性メモリをプログラミングして読み出すプロセスの1つの実施形態を説明するフローチャートである。

【図19】閾値電圧分布の集合を示す図である。

【図20】不揮発性メモリをプログラミングして読み出すプロセスの1つの実施形態を説明するフローチャートである。

50

【図1】

Fig. 1

【図2】

Fig. 2

【図3】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10C】

【図11】

【図10A】

【図10B】

【図12A】

【図13】

【図12B】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(31)優先権主張番号 11/413,671

(32)優先日 平成18年4月28日(2006.4.28)

(33)優先権主張国 米国(US)

(56)参考文献 国際公開第2005 / 101424 (WO , A1 )

特開2004 - 326866 (JP , A)

国際公開第2004 / 079747 (WO , A1 )

特表2002 - 523895 (JP , A)

特開2002 - 358792 (JP , A)

特開2005 - 327409 (JP , A)

特開平10 - 011984 (JP , A)

特表2007 - 533055 (JP , A)

(58)調査した分野(Int.Cl. , DB名)

G11C 16/02

G11C 16/04