【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第2区分

【発行日】平成18年12月7日(2006.12.7)

【公開番号】特開2001-281628(P2001-281628A)

【公開日】平成13年10月10日(2001.10.10)

【出願番号】特願2000-98110(P2000-98110)

【国際特許分類】

|               |               |                  |

|---------------|---------------|------------------|

| <b>G 02 F</b> | <b>1/133</b>  | <b>(2006.01)</b> |

| <b>G 09 F</b> | <b>9/30</b>   | <b>(2006.01)</b> |

| <b>G 09 G</b> | <b>3/20</b>   | <b>(2006.01)</b> |

| <b>G 09 G</b> | <b>3/36</b>   | <b>(2006.01)</b> |

| <b>G 02 F</b> | <b>1/1368</b> | <b>(2006.01)</b> |

【F I】

|               |               |                |

|---------------|---------------|----------------|

| <b>G 02 F</b> | <b>1/133</b>  | <b>5 5 0</b>   |

| <b>G 09 F</b> | <b>9/30</b>   | <b>3 3 8</b>   |

| <b>G 09 G</b> | <b>3/20</b>   | <b>6 2 4 B</b> |

| <b>G 09 G</b> | <b>3/20</b>   | <b>6 4 1 G</b> |

| <b>G 09 G</b> | <b>3/20</b>   | <b>6 8 0 S</b> |

| <b>G 09 G</b> | <b>3/20</b>   | <b>6 8 0 T</b> |

| <b>G 09 G</b> | <b>3/36</b>   |                |

| <b>G 02 F</b> | <b>1/1368</b> |                |

【手続補正書】

【提出日】平成18年10月23日(2006.10.23)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】請求項6

【補正方法】変更

【補正の内容】

【請求項6】 前記複数の垂直走査線に対応してそれぞれ配置される、複数の副垂直走査線、複数の第1の基準電位配線、および複数の第2の基準電位配線をさらに備え、

各前記副画素は、

前記複数の垂直走査線のうちの対応する1本の電位に応じて、前記複数の水平走査線のうちの1本と第1の内部ノードとを接続する第1のスイッチ素子と、

前記第1の内部ノードの電位レベルを保持するための制御用容量素子と、

前記第1の内部ノードの電位レベルに応じて、前記第1の基準電位配線および第2の基準電位配線のうちのいずれか一方を第2の内部ノードと接続する接続切換回路と、

前記複数の副垂直走査線のうちの対応する1本の電位に応じて、前記第2の内部ノードと前記画素電極とを接続する第2のスイッチ素子とをさらに有する、請求項1記載の液晶表示装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】請求項7

【補正方法】変更

【補正の内容】

【請求項7】 前記接続切換回路は、

前記第1の基準電位配線と前記第2の内部ノードとの間に電気的に結合され、前記第1の内部ノードと接続されるゲート電極を有する第1導電型の薄膜トランジスタと、

前記第2の基準電位配線と前記第2の内部ノードとの間に電気的に結合され、前記第1

の内部ノードと接続されるゲート電極を有する第2導電型の薄膜トランジスタとを有する、請求項6記載の液晶表示装置。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0004

【補正方法】変更

【補正の内容】

【0004】

画素1005は液晶表示部1002において行列状に配置されている。液晶表示装置500は、さらに、各画素行ごとに配置される垂直走査線1010および共通配線1012と、各画素列ごとに配置される水平走査線1011とを備える。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0026

【補正方法】変更

【補正の内容】

【0026】

請求項7記載の液晶表示装置は、請求項6記載の液晶表示装置であって、接続切換回路は、第1の基準電位配線と第2の内部ノードとの間に電気的に結合され、第1の内部ノードと接続されるゲート電極を有する第1導電型の薄膜トランジスタと、第2の基準電位配線と第2の内部ノードとの間に電気的に結合され、第1の内部ノードと接続されるゲート電極を有する第2導電型の薄膜トランジスタとを有する。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0062

【補正方法】変更

【補正の内容】

【0062】

$$V \times (C + 4C) = 0 \times C + V \times 4C \quad \dots (2)$$

(2)式より、 $V = 4/5 \cdot V$ が得られる。これにより、副画素SPX1の画素電極の電位レベルは0から $4/5 \cdot V$ に変化し、副画素SPX2の画素電極の電位レベルはVから $4/5 \cdot V$ に変化する。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0075

【補正方法】変更

【補正の内容】

【0075】

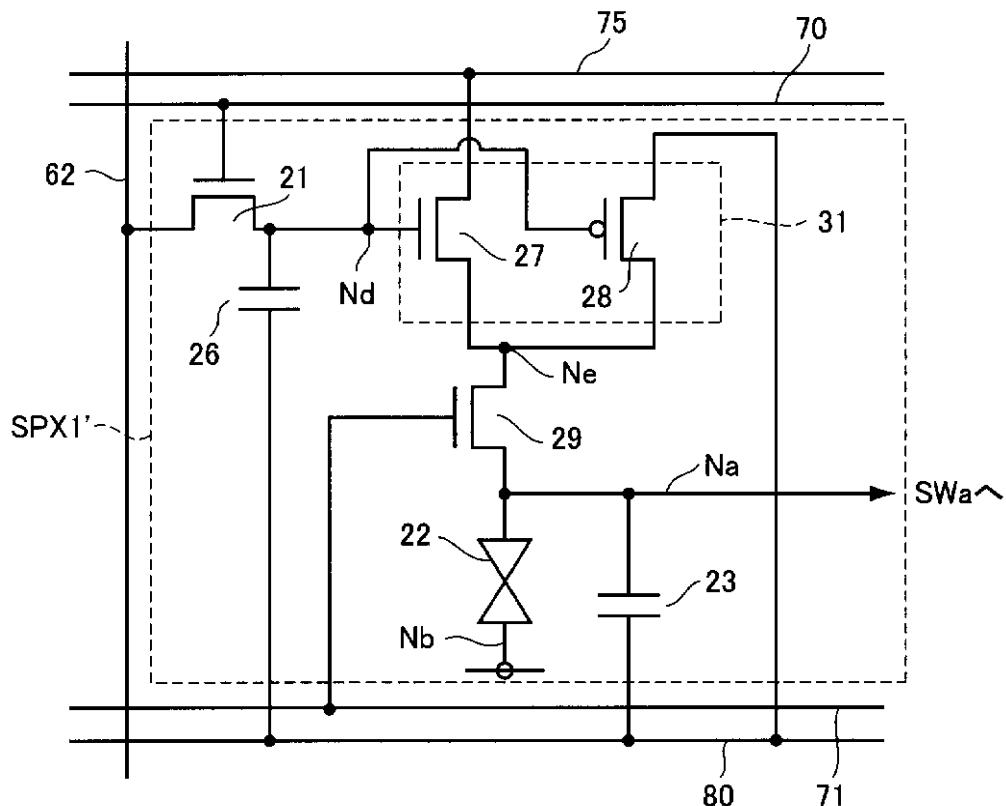

図5は、実施の形態2に従う副画素の構成を説明する回路図である。

図5を参照して、実施の形態2に従う副画素SPX1は、実施の形態1に従う副画素SPX1の構成と比較して、制御用容量素子26と、TFT素子27および28で構成される接続切換回路31と、スイッチ素子として用いられるTFT素子29とをさらに含む点で異なる。

【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0078

【補正方法】変更

【補正の内容】

【0078】

TFT素子27および28は、内部ノードNdの電位レベルに応じて、相補的にオン/

オフするので、接続切換回路 3\_1 は、内部ノード N\_d の電位レベルに応じて、画素信号線 7\_5 および共通配線 8\_0 のうちのいずれか一方を内部ノード N\_e と接続する。

## 【手続補正8】

【補正対象書類名】図面

### 【補正対象項目名】図 5

### 【補正方法】変更

## 【補正の内容】

【 図 5 】