#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization

International Bureau

#

(43) International Publication Date 3 February 2005 (03.02.2005)

**PCT**

# (10) International Publication Number WO 2005/010994 A1

(51) International Patent Classification<sup>7</sup>: H01L 29/423, 21/336

(21) International Application Number:

PCT/US2003/040320

(22) International Filing Date:

15 December 2003 (15.12.2003)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

10/607,769

27 June 2003 (27.06.2003) US

- (71) Applicant: INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, CA 95052 (US).

- (72) Inventors: HARELAND, Scott; 378 Sioux Lookout, Lino Lakes, MN 55014 (US). CHAU, Robert; 8875 SW 171st Avenue, Beaverton, OR 97007 (US). DOYLE,

Brian; 11156 NW Montreux Lane, Portland, OR 97229 (US). RIOS, Rafael; 3688 NW Bronson Crest Loop, Portland, OR 97229 (US). LINTON, Jr., Tom; 1347 Poe Lane, San Jose, CA 95130 (US). DATTA, Suman; 3028 NW Chapin Drive, Portland, OR 97229 (US).

- (74) Agents: MALLIE, Michael, J. et al.; Blakely, Sokoloff, Taylor & Zafman, 7th floor, 12400 Wilshire Boulevard, Los Angeles, CA 90025 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (BW, GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW),

[Continued on next page]

(54) Title: NONPLANAR SEMICONDUCTOR DEVICE WITH PARTIALLY OR FULLY WRAPPED AROUND GATE ELECTRODE AND METHODS OF FABRICATION

(57) Abstract: A nonplanar semiconductor device and its method of fabrication is described. The nonplanar semiconductor device includes a semiconductor body having a top surface opposite a bottom surface formed above an insulating substrate wherein the semiconductor body has a pair laterally opposite sidewalls. A gate dielectric is formed on the top surface of the semiconductor body on the laterally opposite sidewalls of the semiconductor body and on at least a portion of the bottom surface of semiconductor body. A gate electrode is formed on the gate dielectric, on the top surface of the semiconductor body and adjacent to the gate dielectric on the laterally opposite sidewalls of semiconductor body and beneath the gate dielectric on the bottom surface of the semiconductor body. A pair source/drain regions are formed in the semiconductor body on opposite sides of the gate electrode.

## WO 2005/010994 A1

Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

#### **Published:**

with international search report

# NONPLANAR SEMICONDUCTOR DEVICE WITH PARTIALLY OR FULLY WRAPPED AROUND GATE ELECTRODE AND METHODS OF FABRICATION

5

#### BACKGROUND OF THE INVENTION

#### 1. FIELD OF THE INVENTION

10

[0001] The present invention relates to the field of semiconductor integrated circuit manufacturing, and more particularly to a nonplanar fully depleted substrate transistor having a partially or fully wrapped around gate electrode and their methods of fabrication.

15

20

25

30

#### 2. DISCUSSION OF RELATED ART

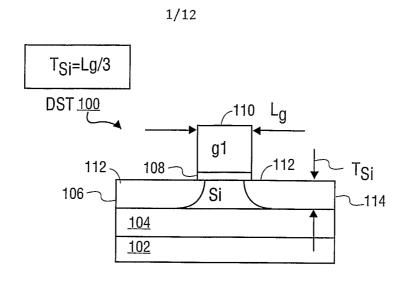

[0002] In order to increase device performance, silicon on insulator (SOI) transistors have been proposed for the fabrication of modern integrated circuits. Figure 1 illustrates a standard fully depleted silicon on insulator (SOI) transistor 100. SOI transistor 100 includes a single crystalline silicon substrate 102 having an insulating layer 104, such as a buried oxide formed thereon. A single crystalline silicon body 106 is formed on the insulating layer 104. A gate dielectric layer 108 is formed on the single crystalline silicon body 106 and a gate electrode 110 formed on the gate dielectric 108. Source 112 and drain 114 regions are formed in the silicon body 106 along laterally opposite sides of gate electrode 110. [0003] Fully depleted SOI have been proposed as a transistor structure to take advantage of ideal sub-threshold gradients for optimized on current/off current ratios. In order to achieve ideal subthreshold gradients with transistor 100, the thickness of the silicon body 106 must be about 1/3 the size of the gate length

(Lg) of the transistor or Tsi = Lg/3. However, as gate lengths scale especially as they approach 30nm, the need for ever decreasing silicon film thickness (Tsi) makes this approach increasingly impractical. At 30 nanometer gate length, the thickness required of the silicon body is thought to need to be less than 10 nanometers, and around 6 nanometer for a 20 nanometer gate length. The fabrication of thin silicon films with thicknesses of less than 10 nanometers, is considered to be extremely difficult. On one hand, obtaining wafer uniformity on the order of one nanometer is a difficult challenge. On the other hand, to be able to contact these thin films to form raised source/drain regions to decrease junction resistance, becomes almost impossible since the thin silicon layer in the source/drain regions becomes consumed during the gate etch and various cleans following the gate etch and spacer etch leaving insufficient silicon 106 for silicon to grow on.

5

10

15

20

25

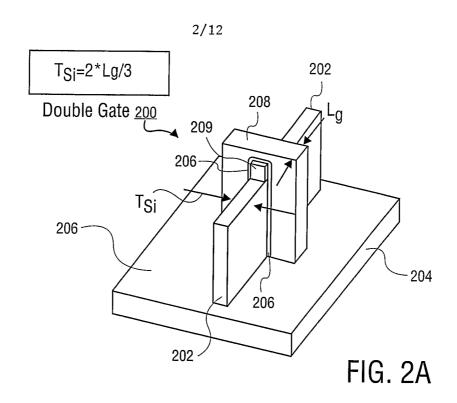

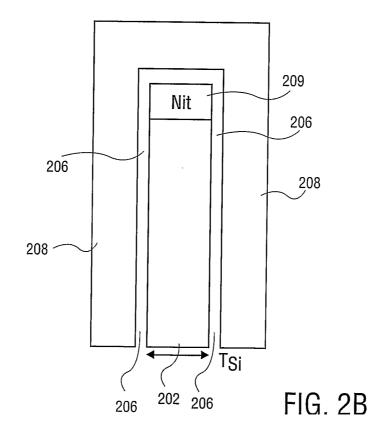

[0004] A double gate (DG) device, such as shown in Figures 2A and 2B, have been proposed to alleviate the silicon thickness issue. The double gate (DG) device 200 includes a silicon body 202 formed on an insulating substrate 204. A gate dielectric 206 is formed on two sides of the silicon body 202 and a gate electrode 208 is formed adjacent to the gate dielectric 206 formed on the two sides of the silicon body 202. A sufficiently thick insulating layer 209, such as silicon nitride, electrically isolates the gate electrode 208 from the top of silicon body 202.

[0005] Double gate (DG) device 200 essentially has two gates, one on either side of the channel of the device. Because the double gate device 200 has a gate on each side of the channel, thickness (Tsi) of the silicon body can be double that of a single gate device and still obtain a fully depleted transistor operation. That is, with a double gate device 200 a fully depleted transistor can be formed where Tsi = (2xLg)/3. The most manufacturable form of the double gate (DG) device 200, however, requires that the body 202 patterning be done with photolithography that

is 0.7 x smaller than that used to pattern the gate length (Lg) of the device. In order to obtain high density integrated circuits, it is generally desirable to have the most aggressive lithography occur with respect to the gate length (Lg) of the gate electrode 208. Although, double gate structures double the thickness of the silicon film (since there now is a gate on either side of the channel) these structures, however, are hideously difficult to fabricate. For example, silicon body 202 requires a silicon body etch which can produce a silicon body 202 with an aspect ratio (height to width) of about 5:1.

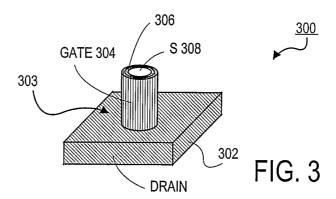

[0006] Figure 3 illustrates a pillar of MOSFET 300. The pillar of MOSFET 300 includes a drain region 302 formed in a semiconductor substrate. A circular silicon pillar 303 is formed on the semiconductor substrate. A gate dielectric layer 306 and a gate electrode 304 are formed around the circular pillar. A source region 308 is formed on the top of the silicon pillar. Current flows between the source and drain regions in a direction perpendicular to the substrate. A problem with the pillar MOSFET 300 is that is formed with elaborate and unconventional processing techniques. Another problem with the pillar MOSFET is that the source and drain regions are processed separately resulting in different electrical properties for the regions.

### 20 BRIEF DESCRIPTION OF THE DRAWINGS

5

[0007] Figure 1 is an illustration of a cross-sectional view of a depleted substrate transistor.

25 [0008] Figures 2A and Figure 2B illustrate a double gate depleted substrate transistor.

[0009] Figure 3 is an illustration of a pillar MOSFET.

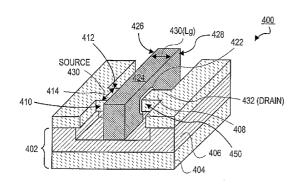

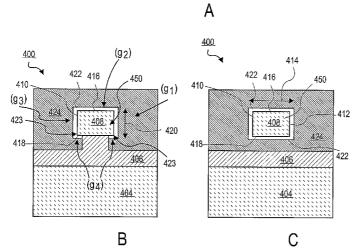

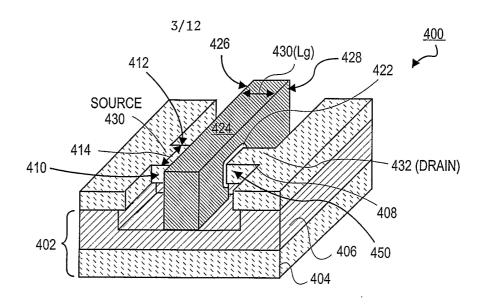

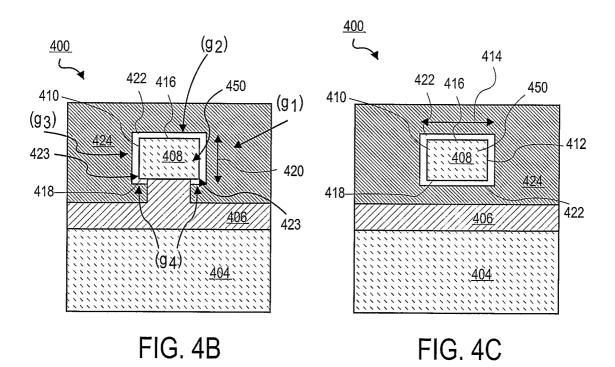

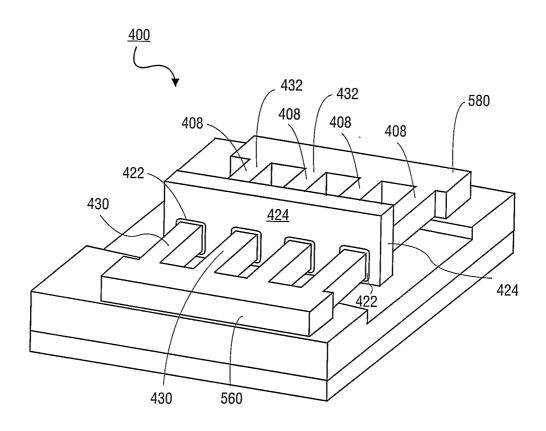

[0010] Figures 4A-4C illustrate a nonplanar transistor having a fully wrapped around or an almost wrapped around gate electrode.

- 5 [0011] Figure 5 is an illustration of a nonplanar transistor having multiple semiconductor bodies with a fully wrapped around or partially wrapped around gate electrode.

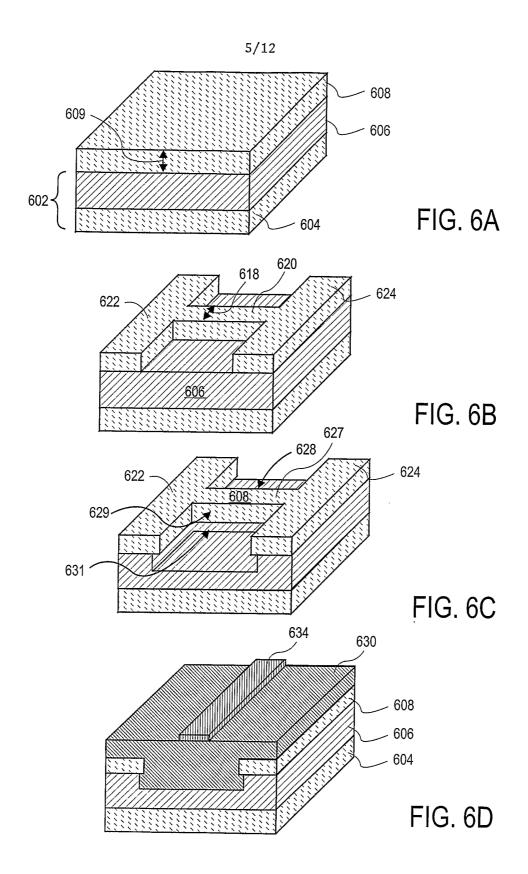

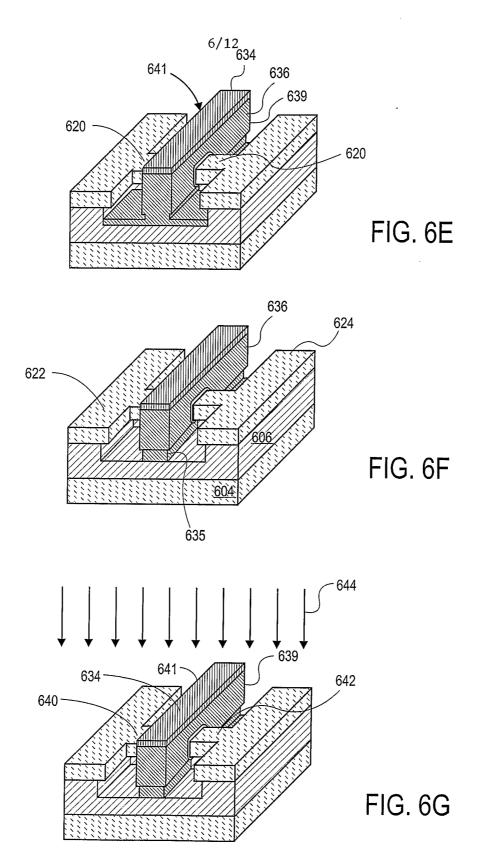

- [0012] Figures 6A-6G illustrate a method of fabricating a nonplanar transistor with

a fully wrapped around or almost wrapped around gate electrode utilizing a subtractive fabrication process.

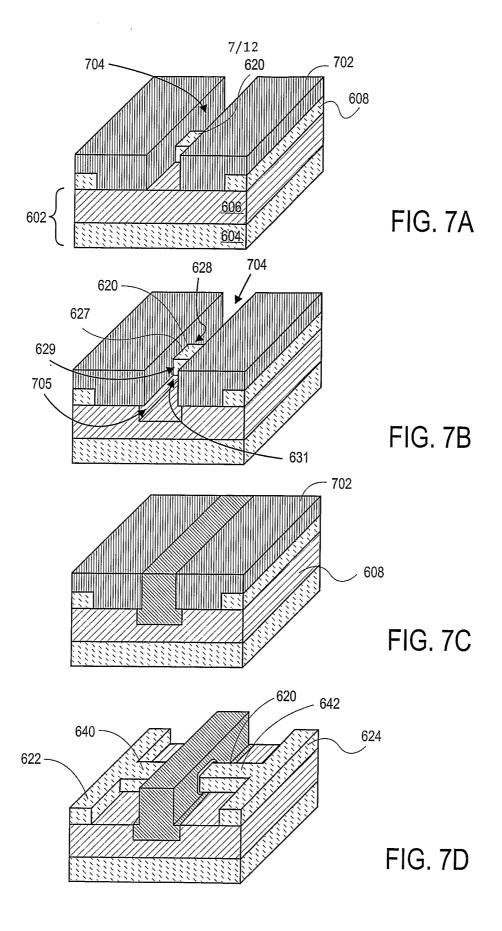

- [0013] Figures 7A-7D illustrate a method of forming a nonplanar transistor with a fully wrapped around gate electrode or an almost wrapped around gate electrode

utilizing a replacement gate fabrication process.

- [0014] Figures 8A-8G illustrate a method of forming a nonplanar transistor with a fully wrapped around gate electrode or an almost wrapped around gate electrode utilizing a replacement gate fabrication process.

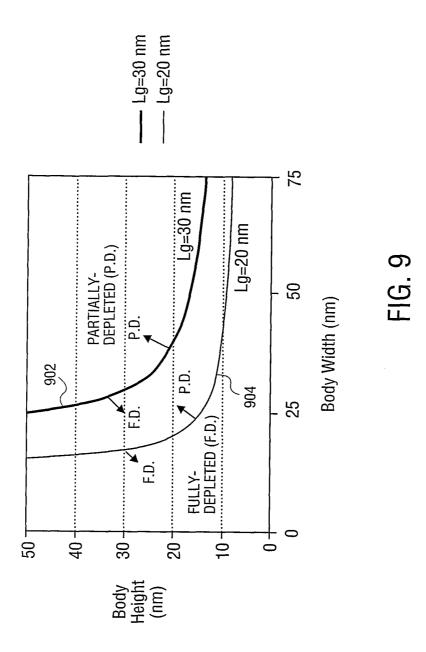

- [0015] Figure 9 is a plot which illustrates body heights and body widths which can be used to obtain partially depleted and fully depleted nonplanar transistors having gate lengths (Lg) of 30 nanometers and 30 nanometers.

# DETAILED DESCRIPTION OF THE PRESENT INVENTION

25

[0016] The present invention is a novel nonplanar device structure which has a gate electrode which is fully wrapped around the channel region or gate electrode which is almost entirely wrapped around the channel region and their methods of

fabrication. In following description numerous specific details are set forth in order to provide a thorough understanding of the present invention. In other instances, well known semiconductor processes and manufacturing techniques have not been described in particular detail in order to not unnecessarily obscure the present invention.

5

10

15

20

25

[0017] The present invention is a novel nonplanar transistor structure. In an embodiment of the present invention, the nonplanar transistor has a gate electrode which is fully wrapped around the channel region. In another embodiment of the present invention, the nonplanar transistor has a gate electrode which is partially or almost entirely wrapped around the channel region of the transistor. The advantage of a transistor having a gate electrode which is fully wrapped around the channel region or almost all around the channel region is that it is easier to deplete the channel region of the device and thereby relax the thickness (Tsi) and width (Wsi) dimensional constraints of the semiconductor body. Additionally, by completely or partially surrounding the channel of the device, the drive current of the device is enhanced by providing two additional corners in the device which increases carrier density.

[0018] Figure 4A is an overhead view of a nonplanar transistor 400 which has either a fully wrapped around gate electrode or a partially wrapped around gate electrode in accordance with embodiments of the present invention. Figure 4B is a cross-sectional view of Figure 4A taken through the gate electrode when the gate electrode is partially wrapped around the channel region of the device. Figure 4C is a cross-sectional view of Figure 4A taken through the gate electrode when the gate electrode is fully wrapped around the channel region of the device.

The nonplanar device structure is ideal for use in a fully depleted substrate transistor application. The nonplanar device structure includes a thin semiconductor body 408 formed on an insulating substrate 402. A gate dielectric 422 is formed on the top surface, sidewalls and on at least a portion of the bottom

5

10

15

20

25

surface of the semiconductor body. A gate electrode 424 is formed on the gate dielectric 422 on the top surface of the semiconductor body, is formed adjacent to the gate dielectric formed on the sidewalls of the semiconductor body and is formed beneath the gate dielectric formed on the bottom surface of the semiconductor body. Source and drain regions are formed in the semiconductor body 408 on opposite sides of the gate electrode 424. Because the gate electrode and gate dielectric surround the channel region of the semiconductor body 408 on three sides and on at least a portion of a fourth side, the semiconductor body can be easily fully depleted when the transistor is turned "ON" thereby enabling the formation of a fully depleted transistor with gate lengths less than 30 nanometers without requiring the use of ultrathin semiconductor bodies or requiring photolithographic patterning of the semiconductor bodies to dimensions less than the gate length (Lg) of the device. That is, the structure of the nonplanar transistor of the present invention enables a fully depleted transistor to be fabricated where the thickness of the semiconductor body and the width of the semiconductor body are equal to the gate length of the device. Because the novel nonplanar transistor of the present invention can be operated in a fully depleted manner, the device is characterized by ideal (i.e., very sharp) subthreshold slope (ideally 60 mV /decade at 25°C) and a reduced drain induced barrier (DIBL) short channel effect of less than 100 mV/V and ideally about 60 mV/V which results in lower leakage current when the device is turned "OFF" resulting in lower power consumption.

[0019] Examples of a nonplanar transistor 400 in accordance with embodiments of present invention are illustrated in Figure 4A-4C. Nonplanar transitor 400 is formed on an insulating substrate 402. In an embodiment of the present invention, insulating substrate 402 includes a lower monocrystalline silicon substrate 404 upon which is formed in insulating layer 406, such as a silicon dioxide film. Nonplanar transistor 400, however, can be formed on any well-

known insulating substrate such as substrates formed from silicon dioxide, nitrides, oxides, and sapphires.

[0020] Nonplanar transistor 400 includes a semiconductor body 408.

5

10

15

Semiconductor body 408 provides the source region 430, drain region 432 and channel region 450 of the device. Semiconductor body 408 can be formed of any well-known semiconductor material, such as but not limited to silicon (Si), germanium (Ge), silicon germanium (Si<sub>x</sub>Ge<sub>v</sub>), gallium arsenide (GaAs). InSb. GaP, GaSb and carbon nanotubes. Semiconductor body 408 can be formed of any well-known material which can be reversibly altered from an insulating state to a conductive state by applying external electrical controls. Semiconductor body 408 is ideally a single crystalline film when the best electrical performance of transistor 400, is desired. For example, semiconductor body 408 is a single crystalline film when transistor 400 is used in high performance applications, such as in a high density circuit, such as a microprocessor. Semiconductor body 408, however, can be a polycrystalline film when transistor 400 is used in applications requiring less stringent performance, such as in liquid crystal displays. Insulator 406 insulates semiconductor body 408 from monocrystalline silicon substrate 402. In an embodiment of the present invention, semiconductor body 408 is formed from a single crystalline silicon film.

[0021] Semiconductor body 408 has a pair of laterally opposite sidewalls 410 and 412 separated by a distance which defines a semiconductor body width (Wsi) 414. Additionally, semiconductor body 408 has a top surface 416 opposite a bottom surface 418 formed on substrate 402. The distance between the top surface 416 and the bottom surface 418 defines a body height (Tsi) 420. In an embodiment of the present invention the body height 420 is substantially equal to the body width (Wsi) 414. In an embodiment of the present invention, the body 408 has a width 414 and height (Tsi) 420 less than 30 nanometers and ideally less than 20

nanometers. In an embodiment of the present invention, the body height 420 is between ½ the body width 414 to 2 times the body width 414.

5

10

15

20

25

[0022] Nonplanar device 400 has a gate dielectric layer 422. Gate dielectric layer 422 is formed on and around three sides of the channel region 350 of semiconductor body 408 as well as on or subadjacent to at least a portion of the bottom surface 418 of the channel region 450 semiconductor body 408 as shown in Figures 4A-4C. In the partially overlap embodiment of the present invention, as shown in Figure 4B, the gate dielectric layer 422 is formed on or adjacent to sidewall 412, on top surface 416, on or adjacent to sidewall 410 and is formed on a portion of the bottom surface 418 of semiconductor body 418 which extends from sidewall 412 towards the center of the bottom surface and covers a second portion which extends from sidewall 410 towards the center portion of the bottom surface 418. In the almost wrapped around embodiment shown in Figure 4B, the gate dielectric layer 422 covers at least the lower corners 423 of the semiconductor body 408 and in another embodiment extends about 1/3 the width of semiconductor body 408 on each side. In the fully wrapped around embodiment shown in Figure 4C, the gate dielectric layer 422 is formed on or adjacent to sidewall 412, on the top surface 416, on or adjacent to sidewall 410, and on the entire bottom surface 418 of the channel region of semiconductor body 408. Gate dielectric layer 422 can be any well-known gate dielectric layer. In an embodiment of the present invention, the gate dielectric layer is a silicon dioxide  $(SiO_2)$ , silicon oxynitride  $(SiO_xN_y)$  or a silicon nitride  $(Si_3N_4)$  dielectric layer. In an embodiment of the present invention, the gate dielectric layer 422 is a silicon oxynitride film formed to a thickness of between 5-20Å. In an embodiment of the present invention, gate dielectric layer 422 is a high K gate dielectric layer, such as a metal oxide dielectric, such as but not limited to tantalum pentaoxide (Ta<sub>2</sub>O<sub>5</sub>), titantium oxide (TiO2), hafnium oxide (HfO2), HfSiOxNy, zirconium oxide (ZrO2) and

lanthanum oxide (LaO<sub>2</sub>). Gate dielectric layer 422 can be other types of high K dielectric, such as but not limited to PZT.

5

10

15

20

25

[0023] Nonplanar device 400 has a gate electrode 424. Gate electrode 424 is formed on and around gate dielectric layer 422 as shown in Figures 4A-4C. In the partially overlapped embodiment of the present invention shown in Figure 4B, the gate electrode 424 is formed on or adjacent the gate dielectric 424 formed on sidewall 412 of the channel region 450 of semiconductor body 408, is formed on gate dielectric layer 422 formed on the top surface 416 of the channel region of semiconductor body 408, is formed on or adjacent to gate dielectric laver 422 formed on sidewall 410 of the channel region of semiconductor body 408, and is formed beneath or directly subadjacent to gate dielectric layer 422 formed beneath bottom surface 418 of the channel region of semiconductor body 408. In an embodiment of the almost all around gate electrode transistor of the present invention, the gate electrode 424 extends beneath bottom surface 418 approximately 1/3 the width of semiconductor body 408 on each side of the channel region 450 of the semiconductor body. The goal is to have the gate electrode wrap around the corners 423 of the device enough to provide good corner control. In the almost all around embodiment the remaining portion of the bottom surface is formed on buried insulating layer 406. In the fully wrapped around embodiment shown in Figure 4C, gate electrode 424 is formed on or adjacent to gate dielectric layer 422 formed on sidewall 412 of the channel region of semiconductor body 408, is formed on gate dielectric layer 422 formed on the top surface 416 of the channel region of semiconductor body 408, is formed adjacent to or on the gate dielectric layer 422 formed on sidewall 410 of the channel region of semiconductor body 408, and is formed beneath or directly subadjacent to the gate dielectric layer 422 formed on the channel region of semiconductor body 408. Gate electrode 424 has a pair of laterally opposite sidewalls 426 and 428 separated by a distance which defines the gate length (Lg)

430 of transistor 400. In an embodiment of the present invention the laterally opposite sidewalls 426 and 428 of the gate electrode 424 run in a direction perpendicular to the laterally opposite sidewalls 410 and 412 of semiconductor body 408.

[0024] Gate electrode 424 can be formed of any suitable gate electrode material. In an embodiment of the present invention to gate electrode 424 comprises of polycrystalline silicon doped to a concentration density between 1x10<sup>19</sup> atoms/cm³ – 1x10<sup>21</sup> atoms/cm³. In an embodiment of the present invention the gate electrode can be a metal gate electrode, such as but not limited to, tungsten,

tantalum, titanium, and their nitrides. In an embodiment of the present invention the gate electrode is formed from a material having a work function compatible with the channel material (e.g., 4.0-5.2 eV for Si). It is to be appreciated, the gate electrode 424 need not necessarily be a single material and can be a composite stack of thin films, such as but not limited to a polycrystalline silicon/metal

electrode or a metal/polycrystalline silicon electrode.

[0025] Nonplanar transistor 400 has a source region 430 and a drain region 432. Source region 430 and drain region 432 are formed in semiconductor body 408 on opposite sides of gate electrode 424 as shown in Figure 4A. The source region 430 and the drain region 432 are formed of the same conductivity type such as N-type or P-type conductivity. In an embodiment of the present invention source region 430 and drain region 432 have a doping concentration of between 1x10<sup>19</sup> and 1x10<sup>21</sup> atoms/cm<sup>3</sup>. Source region 430 and drain region 432 can be formed of uniform concentration or can include subregions of different concentrations or doping profiles such as tip regions (e.g., source/drain extensions). In an embodiment of the present invention when transistor 400 is a symmetrical transistor, source region 430 and drain region 432 have the same doping concentration and profile. In an embodiment of the present invention when nonplanar transistor 400 is formed as an asymmetric transistor, the doping

20

25

concentration and profile of the source region 430 and the drain region 432 may vary in order to obtain a particular electrical characteristic. The source and drain regions may also include epitaxial silicon regrowth and/or silicides for improved device performance.

5

10

15

20

25

[0026] The portion of semiconductor body 408 located between source region 430 and drain region 432, defines the channel region 450 of transistor 400. The channel region 450 can also be defined as the area of the semiconductor body 408 surrounded by the gate electrode 424. At times however, the source/drain region may extend slightly beneath the gate electrode through, for example, diffusion to define a channel region slightly smaller than the gate electrode length (Lg). In an embodiment of the present invention channel region 450 is intrinsic or undoped monocrystalline silicon. In an embodiment of the present invention, channel region 450 is doped monocrystalline silicon. When channel region 450 is doped it is typically doped to a conductivity level of between 1x10<sup>16</sup> to 1x10<sup>19</sup> atoms/cm<sup>3</sup>. In an embodiment of the present invention, when the channel region is doped it is typically doped to the opposite conductivity type of the source region 430 and the drain region 432. For example, when the source and drain regions are N-type conductivity the channel region 450 would be doped to p type conductivity. Similarly, when the source and drain regions are P type conductivity the channel region would be N-type conductivity. In this manner a nonplanar transistor 400 can be formed into either a NMOS transistor or a PMOS transistor respectively. Channel region 450 can be uniformly doped or can be doped nonuniformly or with differing concentrations to provide particular electrical and performance characteristics. For example, channel regions 450 can include wellknown "halo" regions, if desired. When the transistor is turned "ON" current flows between the source region 430 and the drain region through the gated channel region 450 in a direction parallel to the plane of substrate 402.

5

10

15

20

25

[0027] By providing a gate dielectric and a gate electrode which surrounds the semiconductor body on all sides, the nonplanar transistor can be characterized as having four channels and four gates, one gate (g1) and channel which extends between the source and drain regions on side 412 of semiconductor body 408, a second gate (g2) and channel which extends between the source and drain regions on the top surface 416 of semiconductor body 408, a third gate (g3) and channel which extends between the source and drain regions on the sidewall 310 of semiconductor body 408 and a fourth channel and gate (g4) between the source and drain regions on the bottom surface 418 of semiconductor body 408. The gate "width" (Gw) of transistor 400 is the sum of the widths of the four gates. That is, the gate width of transistor 400 is equal to the height 420 of silicon body 408 at sidewall 410, plus the width of silicon body of 308 at the top surface 416, plus the height 420 of silicon body 408 at sidewall 412 plus the amount of the bottom surface of semiconductor body 408 above gate electrode 424. Larger "width" transistors can be obtained by using multiple devices coupled together (e.g., multiple silicon bodies 408 surrounded by a single gate electrode 424). [0028] As stated above the gate "width" of transistor 400 is equal to the sum of the four gate widths created from semiconductor body 408 of transistor 400. In order to fabricate the transistors with larger gate widths, transistor 400 can include an additional or multiple semiconductor bodies or fingers 408 as shown in Figure 5. Each semiconductor body 408 has a gate dielectric layer 422 formed on its top surface and sidewalls and bottom surface or a portion of the bottom surface as shown in Figure 5. Gate electrode 424 is formed on and adjacent to each gate dielectric 422 on each of the semiconductor bodies 408. Each semiconductor body 408 also includes a source region 430 and a drain region 432 formed in the semiconductor body 408 on opposite sides of gate electrode 424 as shown in Figure 5. In an embodiment of the present invention each semiconductor body 408 is formed with the same width and height (thickness) as the other

5

10

15

20

25

semiconductor bodies 408. In an embodiment of the present invention each source regions 430 and drain regions 432 of the semiconductor bodies 408 are electrically coupled together by source landing pad 560 and a drain landing pad 580 as shown in Figure 5. Alternatively, the source regions 430 and drain regions 432 can be coupled together by higher levels of metalization (e.g., metal 1, metal 2, metal 3...) used to electrically interconnect various transistors 400 together into functional circuits. The gate width of transistor 400 as shown in Figure 5 is equal to the sum of the gate width created by each of the semiconductor bodies 408. In this way, a tri-gate transistor 400 can be formed with any gate width desired. [0029] Because the channel region 450 is surrounded on all sides by gate electrode 424 and gate dielectric 422, transistor 400 can be operated in a fully depleted manner wherein when transistor 400 is turned "ON" the channel region 450 fully depletes thereby providing the advantageous electrical characteristics and performance of a fully depleted transistor. That is, when transistor 400 is turned "ON" a depletion region is formed in channel region 450 along with an inversion layer at the surfaces of region 450 (i.e., an inversion layer is formed on the side surfaces 410 and 412 and on top surface 416 and on bottom surface 418 of the semiconductor body). The inversion layer has the same conductivity type as the source and drain regions and forms a conductive channel between the source and drain regions to allow current to flow therebetween. The depletion region depletes free carriers from beneath the inversion layers. The entire channel region 450 except for the inversion layer is depleted of carriers, thus the transistor can be said to be a "fully depleted" transistor. Fully depleted transistors have improved electrical performance characteristics over non-fully depleted or partially depleted transistors. For example, operating transistor 400 in a fully depleted manner, gives transistor 400 an ideal or very steep subthreshold slope. The nonplanar transistor can be fabricated with very steep sub-threshold slope of less than 80 mV/decade, and ideally about 60 mV/decade even when fabricated

with semiconductor body thicknesses of less than 30 nm. Additionally, operating transistor 400 in the fully depleted manner, transistor 400 has an improved drain induced barrier (DIBL) lowering effect which provides for better "OFF" state leakage which results in lower leakage and thereby lower power consumption. In an embodiment of the present invention the tri-gate transistor 400 has a DIBL effect of less than 100mV/V and ideally less than 40 mV/V.

5

10

15

[0030] Figure 9 is an illustration of two plots 902 and 904 which set forth the body height and body width which will produce either fully depleted (F.D) or partially depleted (P.D) nonplanar transistors having gate length (Lg) of 30 nm (902) and 20 nm (904) respectively. In an embodiment of the present invention, the body height, body width and gate length are chosen to have dimensions in which a fully depleted transistor will be formed. In other embodiments, the nonplanar transistor has a body height, body width and gate length such that a partially depleted transistor is formed.

nonplanar transistor because the inversion layers of the channel region 450 are formed in both the horizontal and vertical directions in semiconductor body 408. The semiconductor device of the present invention can also be considered a nonplanar device because the electric field from the gate electrode 424 is applied from both horizontal (g2 and g4) and vertical sides (g1 and g3).

[0032] A method of fabricating a nonplanar transistor with a partially or fully wrapped around gate electrode in accordance with embodiments of the present invention is illustrated in Figures 6A-6G. The method of Figures 6A-6G can be referred to as a subtractive fabrication process. The fabrication of a nonplanar transistor begins with an insulating substrate 602. A silicon or semiconductor film 608 is formed on insulating substrate 602 as shown in Figure 6A. In an embodiment of the present invention, insulating substrate 602 includes a lower monocrystalline silicon substrate 604 and a top insulating layer 606, such as a

[0031] The nonplanar transistor of the present invention can be said to be a

silicon dioxide film or silicon nitride film. Insulating layer 606 isolates semiconductor film 608 from substrate 604, and in embodiment is formed to a thickness between 200-2000Å. Insulating layer 606 is sometimes referred to as a "buried oxide" layer. When a silicon or semiconductor film 608 is formed on an insulating substrate 602, a silicon or semiconductor on insulating (SOI) substrate is created.

5

10

15

20

25

[0033] Although semiconductor film 608 is ideally a silicon film, in other embodiments it can be other types of semiconductor films, such as but not limited to germanium (Ge), a silicon germanium alloy (Si<sub>x</sub>Ge<sub>y</sub>), gallium arsenide (GaAs), InSb, GaP, GaSb, as well as carbon nanotubes. In an embodiment of the present invention, semiconductor film 608 is an intrinsic (i.e., undoped) silicon film. In other embodiments, semiconductor film 608 is doped to a p type or n type conductivity with a concentration level between 1x10<sup>16</sup>-1x10<sup>19</sup> atoms/cm<sup>3</sup>. Semiconductor film 608 can be insitu doped (i.e., doped while it is deposited) or doped after it is formed on substrate 602 by for example ion-implantation. Doping after formation enables both PMOS and NMOS nonplanar devices to be fabricated easily on the same insulating substrate. The doping level of the semiconductor body at this point determines the doping level of the channel region of the device.

[0034] Semiconductor film 608 is formed to a thickness which is approximately equal to the height desired for the subsequently formed semiconductor body or bodies of the fabricated nonplanar transistor. In an embodiment of the present invention, semiconductor film 608 has a thickness or height 609 of less than 30 nanometers and ideally less than 20 nanometers. In an embodiment of the present invention, semiconductor film 608 is formed to the thickness approximately equal to the gate "length" desired of the fabricated nonplanar transistor. In an embodiment of the present invention, semiconductor film 608 is formed thicker than desired gate length of the device. In an embodiment of the

present invention, semiconductor film 680 is formed to a thickness which will enable the fabricated nonplanar transistor to be operated in a fully depleted manner for its designed gate length (Lg).

5

10

15

20

25

[0035] Semiconductor film 608 can be formed on insulating substrate 602 in any well-known method. In one method of forming a silicon on insulator substrate, known as the SIMOX technique, oxygen atoms are implanted at a high dose into a single crystalline silicon substrate and then anneal to form the buried oxide 606 within the substrate. The portion of the single crystalline silicon substrate above the buried oxide becomes the silicon film 608. Another technique currently used to form SOI substrates is an epitaxial silicon film transfer technique which is generally referred to as bonded SOI. In this technique a first silicon wafer has a thin oxide grown on its surface that will later serve as the buried oxide 606 in the SOI structure. Next, a high dose hydrogen implant is made into the first silicon wafer to form a high stress region below the silicon surface of the first wafer. This first wafer is then flipped over and bonded to the surface of a second silicon wafer. The first wafer is then cleaved along the high stress plain created by the hydrogen implant. This results in a SOI structure with a thin silicon layer on top, the buried oxide underneath all on top of the single crystalline silicon substrate. Well-known smoothing techniques, such as HCl smoothing or chemical mechanical polishing (CMP) can be used to smooth the top surface of semiconductor film 608 to its desired thickness.

[0036] At this time, if desired, isolation regions (not shown) can be formed into SOI semiconductor film 608 in order to isolate the various transistors to be formed therein from one another. Isolation regions can be formed by etching away portions of the substrate film 608 surrounding a nonplanar transistor, by for example well-known photolithographic and etching techniques, and then back filling the etched regions with an insulating film, such as SiO<sub>2</sub>.

[0037] Next, standard photolithography and etching techniques are used to define a semiconductor body or fin 620 in the semiconductor film 608 for the tri-gate transister as shown in Figure 6B. In an embodiment of the present invention, the fin or body 620 is patterned to have a width 618 which is equal to or greater than the width desired of the gate length (Lg) of the fabricated transistor. In this way, the most stringent photolithography constraints used to fabricate the transistor are associated with the gate electrode patterning and not the semiconductor body or fin definition. In an embodiment of the present invention, the semiconductor body or fins will have a width 618 less than or equal to 30 nanometers and ideally less than or equal to 20 nanometers. In an embodiment of the present invention, the semiconductor bodies or fins have a width 618 approximately equal to the silicon body height 609. In an embodiment of the present invention, the fins or bodies 620 have a width 618 which is between ½ the semiconductor body height 609 and two times the semiconductor body height 609.

5

10

15

20

25

[0038] Additionally, the photolithography and etching step can be used to form multiple semiconductor bodies or fins, for a single transistor as shown in Figure 5. In this way, transistors with different gate widths (Gw) can be fabricated across a wafer. The photolithography and etching step can also be used to form source landing pads 622 and drain landing pads 624 from the semiconductor film in order to provide contact areas for the transistor. Additionally, the landing pads can be used to connect together the various source regions and to connect together the various drain regions when multiple semiconductor bodies are used in the nonplanar transistor.

[0039] The semicoductor film 608 can be patterned into fins and landing pads by well known photolithography and etching techniques which generally include the formation of a photoresist mask by masking, exposing, and developing a blanket deposited photoresist film, and then etching semiconductor film in alignment with the photoresist mask to form one or more silicon bodies or fins 620 and source

5

10

15

20

25

and drain landing pads 622 and 624 respectively. Semiconductor film 608 is etched until the underlying buried insulating layer 606 is exposed. Well-known semiconductor etching techniques, such as anisotropic plasma etching or reactive ion etching can be used to etch semiconductor film 608 in alignment with the photoresist mask. After semiconductor film 608 is etched to form a semiconductor body or fin 620 (and source/drain landing pads 622 and 624, if desired) the photoresist mask is removed by well-known techniques, such as by chemical stripping and O<sub>2</sub> ashing, to produce the substrate shown in Figure 6B. [0040] Next, as shown in Figure 6C, a portion of the buried oxide layer 606 formed beneath semiconductor body 620 is removed. A short isotropic oxide etch can be performed to "undercut" the semiconductor body 620 and remove a portion or all of the buried oxide layer 606 beneath the semiconductor body 620. In the fabrication of an almost wrapped around gate electrode, the insulation etch (undercut etch) removes only a portion of the insulating film beneath the semiconductor body 620. In an embodiment of the present invention, the etch removes approximate 1/3 of the body width of the insulating film 606 from beneath each side of the semiconductor body 620. When forming a transistor with a fully wrapped around gate electrode, the entire portion of the buried insulating layer 606 is removed from beneath the semiconductor body 620. In such a case, the semiconductor body 620 can be supported by source and drain landing pads 622 and 624 formed on the remaining portions of the buried insulating layer. Any well known isotropic oxide etch may be utilized which is selective to the semiconductor material (i.e., an etch which can preferentially etch the insulating film 606 without significantly etching the semiconductor film 608). An etch with a selectivity of at least 10:1 is desired. When the semiconductor film 608 is silicon and the insulating film 606 is silicon oxide, a buffered oxide etch (BOE) comprising hydrogen fluoride (HF) can be utilized.

5

10

15

20

25

[0041] Next, a gate dielectric layer 626 is formed on and around each semiconductor body 620. That is, a gate dielectric layer 626 is formed on the top surface 627 of semiconductor body 620 as well as on the laterally opposite sidewalls 628 and 629 of each of the semiconductor bodies 620. When forming a partially wrapped around gate electrode, the gate dielectric 626 layer is formed on the exposed portion 631 of the underside of the semiconductor body 620. When forming a completely wrapped around gate electrode, the gate dielectric layer is formed on the entire bottom surface of the exposed semiconductor body. The gate dielectric can be a deposited dielectric or a grown dielectric. The gate dielectric layer 626 should be formed by a conformal process which enables the formation of the dielectric 626 on the underside of the semiconductor body 620. In an embodiment of the present invention, the gate dielectric layer 626 is a silicon dioxide dielectric film grown with a dry/wet oxidation process. In an embodiment of the present invention, the silicon oxide film is grown to a thickness of between 5-15Å. In an embodiment of the present invention, the gate dielectric film 626 is a deposited dielectric, such as but not limited to a high dielectric constant film, such as metal oxide dielectric, such as tantalum pentaoxide (Ta<sub>2</sub>O<sub>5</sub>), titantium oxide (TiO<sub>2</sub>), hafnium oxide (HfO<sub>2</sub>), HfSiO<sub>x</sub>N<sub>v</sub>, zirconium oxide (ZrO<sub>2</sub>) and lanthanum oxide (LaO<sub>2</sub>) or other high-K dielectrics, such as PZT and BST formed by chemical vapor deposition (CVD) or atomic layer deposition (ALD). [0042] Next, as also shown in Figure 6D, a gate electrode material 630 is blanket deposited over the substrate. The gate electrode 630 is formed on the gate dielectric layer 626 formed on the top surface 627 of semiconductor body 620 and is formed on or adjacent to the gate dielectric 626 formed on or adjacent to the sidewalls 628 and 629 of the semiconductor body 620 and is formed beneath or subadjacent to the gate dielectric on the bottom of body 620. The gate electrode material 630 is formed by a conformal process, such as CVD or ALD, in order to ensure that gate electrode material can fill beneath the undercut portion of the

semiconductor body so that the gate electrode can partially or fully wrap around the semiconductor body 608. The gate electrode material 630 can be deposited to a thickness between 200-3000Å. In an embodiment the gate electrode material is deposited to a thickness or height sufficient to form a gate electrode with a height of at least three times the height 609 of semiconductor bodies 620. In embodiment of the present invention, the gate electrode material comprises polycrystalline silicon. In another embodiment of the present invention, the gate electrode material comprises a polycrystalline silicon germanium alloy. In yet other embodiment of the present invention, the gate electrode material can comprise a metal film, such as tungsten, tantalum, and their nitrides. [0043] Next, as shown in Figure 6D, a hard mask material is deposited and defined into a patterned hard mask 632 which defines the location where the gate electrode is to be formed. The hard mask material can be formed of any material which will not be substantially etched while subsequently etching the gate electrode material into a gate electrode. In an embodiment of the present invention, the hard mask material is silicon nitride formed to a thickness between 20-100 nanometers. The hard mask material can be formed into a patterned hard mask 634 using standard photolithography and etching techniques. The patterned hard mask 634 is formed to a width which is desired for the electrode gate length of the device.

5

10

15

20

25

[0044] Next the gate electrode material is etched in alignment with the hard mask 634 to form a gate electrode 636. In an embodiment of the present invention, the gate electrode is first anisotropically etched in alignment with the hard mask to form a pair of laterally opposite sidewall 639 and 641 as shown in Figure 6E. In an embodiment of the present invention, the anisotropic etch is continued until just about all of the unmasked gate electrode material 630 is removed and just before the buried insulating layer 606 is exposed. In an alternative embodiment of the present invention, the anisotropic etch is continued until all of the unmasked gate

electrode material is removed and the buried insulating layer 606 exposed. In an embodiment of the present invention, the anisotropic etch is performed with an appropriate etch which forms a passivating polymer film on the sidewall 639 and 641 of the gate electrode to help insure that vertical sidewalls in alignment with the hard mask 634 are formed. Any suitable anisotropic etch technique and etchant which can anisotropically etch the gate electrode material without substantially etching the hard mask and semiconductor film 608 can be used. When the semiconductor film and gate electrode are formed from the same material, such as silicon, a hard mask such as silicon nitride can be used to pattern the semiconductor film into bodies and the hard mask left on during the gate patterning etch to protect the semiconductor body or bodies from etching during the gate etch. The distance between the laterally opposite sidewalls 639 and 641 defines the gate length (Lg) of the device. When the hard mask material is silicon nitride, and the gate electrode material is silicon or polysilicon, the gate electrode can be anisotropically etched and a passivating polymer film formed by a plasma etch utilizing a HBr/Cl<sub>2</sub>/O<sub>2</sub> chemistry.

5

10

15

20

25

[0045] Next, as shown in Figure 6F, after the anisotropic etch, the etch is switched to an isotropic etch. The isotropic etch removes the gate electrode material from regions underneath the semiconductor body where the gate electrode is not to be formed. It is important to remove the undesired portions of the gate electrode material from under the semiconductor body 620 so that "stringers" are not left which can short the source and drain regions to the gate electrode. The isotropic etch which is utilized to remove the "stringers" can be performed after the anisotropic etch completely etches down to the underlying insulating layer or can be done after the anisotropic etch almost reaches the underlying insulating layer. A polymer sidewall passivation on the gate electrodes protects the gate electrode from laterally etching during the isotropic etch step. Some lateral undercutting 635 of the gate electrode 634 may result near the bottom of the gate electrode but

the passivated top portion of the gate electrode should maintain its original profile. The degree of undercutting can be controlled by modifying the amount of insulating layer undercutting and the depth of the recess into the insulating layer. The gate electrode 634 is etched until the gate electrode is completely isolated from the semiconductor film 608 used to form the body 620 and source and drain region landing pads. In an embodiment of the present invention, the isotropic etch is conducted utilizing a hot phosphoric acid wet etch. In an embodiment of the present invention, the photolithography process used to define the hard mask and therefore the gate electrode 636 utilizes a minimum or smallest dimension lithography process used to fabricate the nonplanar transistor. (That is, in an embodiment of the present invention the gate length (Lg) of the gate electrode 636 has a minimum feature dimension of the transistor defined by photolithography). In an embodiment of the present invention, the gate length is less than or equal to 30 nanometers and ideally less than or equal to 20 nanometers.

[0046] Next, source 640 and drain 642 regions for the transistor are formed in semiconductor body 620 on opposite sides of gate electrode 630 as shown in Figure 6G. Source and drain regions 640 and 642, respectively, can be formed by placing dopants 644 into semiconductor bodies 620 on both sides 639, 641 of gate electrode 630 in order to form regions 640 and 642 as shown in Figure 6G. If source and drain landing pads 622 and 624 are utilized, they are also doped at this time. For a PMOS tri-gate transistor, the semiconductor fin or body 620 on opposite sides of the gate electrode are doped to a p type conductivity and to a concentration between 1x10<sup>20</sup>-1x10<sup>21</sup> atoms/cm<sup>3</sup> to form the source and drain regions. For a NMOS tri-gate transistor, the semiconductor fin or body 620 on opposite sides of the gate electrode is doped with n type conductivity ions to a concentration between 1x10<sup>20</sup>-1x10<sup>21</sup> atoms/cm<sup>3</sup> to form source and drain regions. In an embodiment of the present invention, the body is doped by ion-implantation.

In an embodiment of the present invention, the ion-implantation occurs in a vertical direction (i.e., a direction perpendicular to substrate 600) as shown in Figure 6G. When gate electrode 630 is a polysilicon gate electrode, it can be doped during the ion-implantation process by first removing hard mask 634. A polysilicon gate electrode 630 will act as a mask to prevent the ion-implantation step from doping the channel region(s) 648 of the nonplanar transistor. The channel region 648 is the portion of the semiconductor body 620 located beneath or surrounded by the gate electrode 636. If gate electrode 636 is a metal electrode, the dielectric hard mask 634 can be used to block the doping during the ion-implantation process. In other embodiments, other methods, such as solid source diffusion, may be used to dope the semiconductor body to form source and drain extensions. At this point, fabrication of a nonplanar transitor with a partially or fully wrapped around gate electrode is complete.

5

10

15

20

25

[0047] In embodiments of the present invention, "halo" regions can be formed in silicon body prior to the formation of a source/drain regions or source/drain extension regions. Halo regions are doped regions formed in the channel region 648 of the device and are of the same conductivity but of a slightly higher concentration than the doping of the channel region of the device. Halo regions can be formed by ion-implantating dopants beneath the gate electrode by utilizing large angled ion-implantation techniques.

[0048] Additionally, if desired, the substrate shown in Figure 6G can be further processed to form additional well known features, such as heavily doped source/drain contact regions, deposited silicon on the source and drain regions as well as the gate electrode, and the formation of silicide on the source/drain contact regions as well as on the gate electrode.

[0049] Figures 7A-7D illustrate a replacement gate method for forming a nonplanar transistor with an almost wrapper around or fully wrapped around gate electrode. The replacement gate technique is ideal for use when a metal gate

5

10

15

20

25

electrode is desired. The replacement gate method begins with the same substrate and processing as shown in Figure 6A and 6B of the subtractive method described above. After patterning of the semiconductor film into a semiconductor body or fin 620 and the formation of source and drain landing pads, a dielectric film 702 is blanket deposited over the semiconductor body and landing pads and over exposed portions of the buried insulating layer 608. The insulating layer is formed to a thickness desired for the gate height. The insulating layer 702 can be any suitable insulating layer, such as silicon nitride or silicon dioxide. The dielectric film 702 is formed of a material which can be selectively etched with respect to the semiconductor film 608. Additionally, the dielectric film ideally can be selectively etched with respect to the underlying buried insulating layer 606. When the buried insulating layer is silicon dioxide and the semiconductor layer 608 is silicon, the insulating layer 702 can be silicon nitride. The blanket deposited insulating film 702 is then patterned with well known photolithography and etching techniques to form an opening or trench 704 in the dielectric film 702 which defines a location where the gate electrode is to be formed. The patterned insulating film 702 forms a definition mask for the formation of the gate electrode by a damascene patterning approach. The dielectric film 702 is etched with any suitable etchant which can anisotropically etch the dielectric film 702 without etching semiconductor body 620. The insulating layer 702 is etched until the underlying buried insulating layer 606 is exposed as well as the portion of the semiconductor body which is to provide the channel region of the device as shown in Figure 7A. The opening 704 is formed with a width 706 desired of the gate length (Lg) of the nonplanar transistor.

[0050] Next, the buried insulating layer 606 is etched away from underneath the semiconductor body 620 to form an opening 705 which undercut the active channel region of the semiconductor body 620 as shown in Figure 7B. When forming a nonplanar transistor with an almost wrapped around gate electrode, the

insulating layer undercut etch removes a portion of the insulating layer from underneath each side of the semiconductor body. In an embodiment of the present invention, the undercut etch undercuts the semiconductor body by an amount which enables the subsequently formed gate electrode to wrap around at least the lower corners of the semiconductor body 620 and thereby control the current flow in the corners. In an embodiment of the present invention, when forming a nonplanar transistor with an almost wrapped around gate electrode, the undercut etch removes approximately 1/3 of the insulating layer beneath each side 628 and 629 of the semiconductor body 620. When forming a nonplanar device with a fully wrapped around gate electrode, the buried insulating layer undercut etch is continued until the entire insulating layer beneath the exposed portion (i.e., channel region) of the semiconductor body 620 is completely removed. Any well known isotropic etch which can etch the buried insulating layer without significantly etching the semiconductor body may be used. When the buried insulating layer is silicon oxide and the semiconductor body is silicon, a wet etch comprising buffered HF may be utilized to form undercut opening 705. Additionally, as shown in Figure 7B, the undercut etch will slightly undercut the patterned insulating layer 704 resulting in a slightly larger opening 705 and then trench 704.

5

10

15

20

25

[0051] Next, a gate dielectric layer 624 is formed on and around the exposed portion (i.e., channel region) of semiconductor body 620 as described above. That is, the gate dielectric layer is formed on the top surface of semiconductor body 620, is formed on the sidewalls 628 and 629of semiconductor body 620 and is formed beneath or subadjacent to the exposed portions of the underside 631 of the semiconductor body. In the case of a fully wrapped around gate electrode, the gate dielectric layer 624 is formed on the entire underside 631 of the channel region or the semiconductor body. As described above, the gate dielectric layer may be any suitable material and should be formed with a conformal deposition

process, such as atomic layer deposition (ALD) or chemical vapor deposition (CVD) to insure sufficient formation of a gate dielectric layer on the underside 631 of semiconductor body 620.

5

10

15

20

25

[0052] Next, a gate electrode material is blanket deposited over the substrate including on top of dielectric layer 702 and on top of and around the gate dielectric formed on and around semiconductor body 608 and onto insulating layer 608. The gate electrode material is deposited to a thickness sufficient to completely fill openings 705 and 706. The gate electrode material can be any suitable material used to form a gate electrode such as described above. In an embodiment of the present invention, the gate electrode material is a metal film, such as but not limited to tungsten (W), titanium nitride (TiN) and cobalt silicide (CoSi<sub>2</sub>). The gate electrode material should be formed by a deposition technique, such as chemical vapor deposition (CVD) or atomic layer deposition (ALD) so that a conformal film is formed so that the entire trench opening 706 is filled as well as the undercut regions 705 beneath the semiconductor body 620 and the dielectric mask 702. [0053] Next, a planarization technique is utilized to remove excess gate material from the top of dielectric layer 702 so that a planarized top surface may be formed as shown in Figure 7C. Any well known and suitable planarization techniques, such as chemical mechanical polishing or plasma etch back may be utilized to remove the excess gate material from the top of the dielectric film 702. [0054] Next, as shown in Figure 7D, the dielectric film 702 is removed. At this time, source and drain regions may be formed by doping portions of the semiconductor body 620 as described above. This completes the fabrication of a nonplanar device having a partially or fully wrapped around gate electrode utilizing a replacement gate process. If desired, well known additional features, such as sidewall spacers, heavily source/drain contact regions, and silicide may be added at this time.

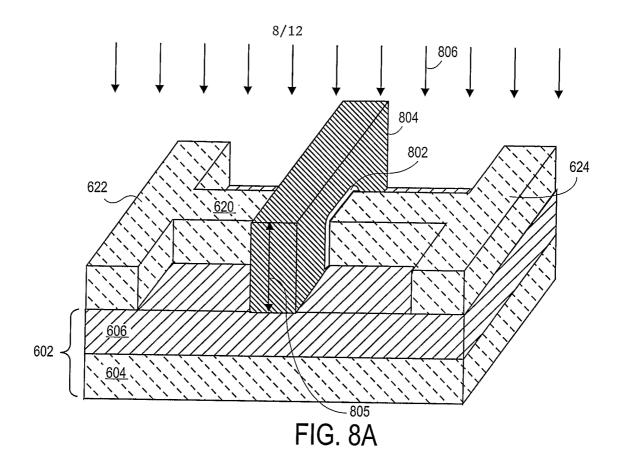

[0055] Figure 8A-8G describe a method of forming a nonplanar device having a wrap around or fully wrapped around gate electrode whereby a replacement gate process is used after the formation of additional features, such as tip regions, spacer, additional semiconductors for ray source/drain regions and silicide on the source/drain regions.

5

10

15

20

25

[0056] The process begins with the same substrate and processing as shown in Figure 6A and 6B. After the patterning of the semiconductor film 608 to form semiconductor body 620 or bodies 620 and source/drain landing pads 622 and 624, sacrificial gate oxide layer 802 and a sacrificial gate electrode 804 are formed over the top surface and sidewalls of the silicon body 620 as shown in Figure 8A. In order to form the sacrificial gate dielectric and electrode, first a sacrificial gate dielectric layer material is blanket deposited over the substrate including the exposed surfaces of insulating layer 606, the top surfaces and sidewalls of semiconductor body 620 and semiconductor landing pads 622 and 624. Next, a sacrificial gate electrode material is blanket deposited over a substrate gate dielectric layer. The sacrificial gate electrode material is deposited to a thickness desired for the height 805 of the subsequently formed gate electrode for the nonplanar device. The sacrificial gate electrode material and the sacrificial gate dielectric material are then patterned by well known techniques, such as with photolithography and etching, to form the sacrificial gate electrode 804 and sacrificial gate dielectric 802 as shown in Figure 8A. The sacrificial gate electrode and the sacrificial gate dielectric are patterned into the same shape and at the same location where the subsequently formed gate electrode and gate dielectric are to be formed. In an embodiment of the present invention, the sacrificial gate electrode material is formed from a material, such as silicon nitride or polysilicon.

[0057] Next, if desired, tip or source/drain extensions can be formed by doping the semiconductor body 620 on opposite sides of the sacrificial gate electrode 804

with impurities of the same conductivity type to be used to form a source/drain regions. The tip regions can be formed by any well known technique, such as by ion implantation, which implants dopants 806 into the semiconductor body 620 as shown in Figure 8A. The sacrificial gate 804 prevents the channel region of the semiconductor body 620 from being doped during the tip formation step. In an embodiment of the present invention, tip regions having a doping concentration between  $1 \times 10^{19} - 1 \times 10^{21}$  atoms/cm<sup>3</sup> are formed.

5

10

15

20

25

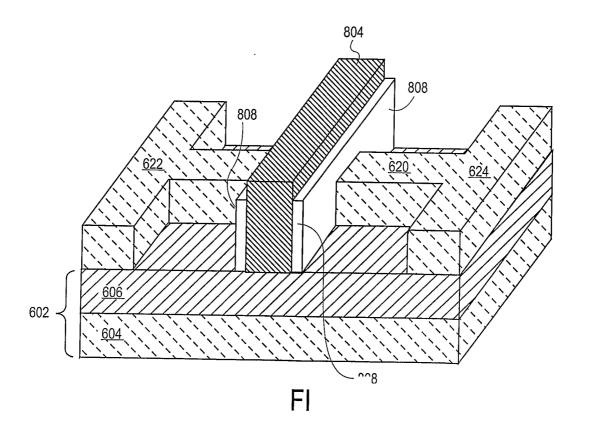

[0058] Next, if desired, dielectric sidewall spacers 808 can be formed along opposite sidewalls of the sacrificial gate electrode 804 as shown in Figure 8B.

Sidewall spacers can be formed by any well known technique, such as by blanket depositing a conformal sidewall spacer dielectric over the substrate including the top surface and sidewalls of the sacrificial gate electrode 804 as well as over the top surface and sidewalls of a semiconductor body 620 and landing pads 622 and 624 as well as onto the exposed surface of insulating substrate 602. The dielectric spacer material is deposited to a thickness which is approximately equal to the width desired for the spacers 808. In an embodiment of the present invention, the dielectric spacer material is deposited to a thickness between 20-100 nanometers. The spacer material can be silicon nitride, silicon oxide, silicon oxynitride or a combination thereof. The dielectric spacer material is then anisotropically etched back to remove the dielectric spacer material from all horizontal surfaces (e.g., top surface of the sacrificial gate electrode 804 and the top surface of semiconductor body 620 and insulating layer 606) while leaving spacer material on vertical surfaces (e.g., the sidewalls of sacrificial gate electrode 804) to form sidewall spacers 808 as shown in Figure 8B. By making the height 805 of a sacrificial gate electrode 804 sufficiently taller (e.g., 3X) than the thickness or height of the semiconductor body 620, an "over etch" of the

anisotropic etch back can be used to remove the spacer material from the

sidewalls of the semiconductor body 620 and landing pads 622 and 622 while

leaving sufficient spacer material to provide spacers 808 on the sidewalls of the sacrificial gate electrode 804.

5

10

15

20

25

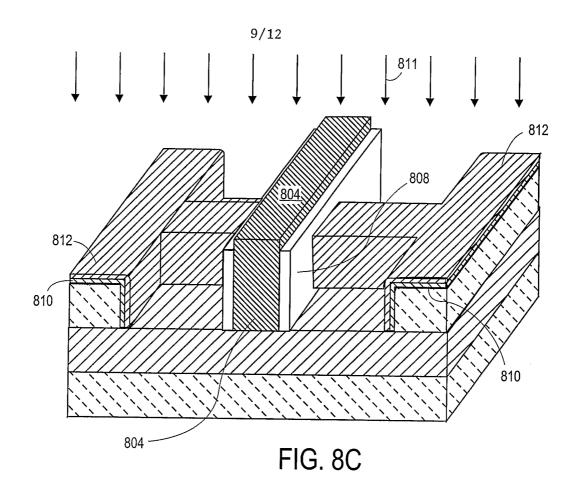

[0059] Next, as shown in Figure 8C, additional silicon 810 and/or silicide 812 can be formed onto the exposed top surface and sidewalls of the semiconductor body 620 and landing pads 622 and 624. Additional silicon can be formed on the exposed surface of the semiconductor body 620 by utilizing a selective deposition process. A selective silicon deposition process deposits silicon, such as epitaxial silicon, onto silicon containing regions, such as semiconductor body 620 and landing pads 622 and 624 and does not deposit silicon on non-silicon containing areas, such as sacrificial gate electrode 804, dielectric spacers 808 and insulating layer 606. Any well known selective deposition process maybe used to provide the additional epitaxial silicon. In an embodiment of the present invention, between 50-500Å of additional epitaxial silicon is selectively deposited onto semiconductor body 620 and landing pads 622 and 624 to form raised source/drain regions,

[0060] Next, if desired, heavy source/drain regions maybe formed in the semiconductor body (and additional silicon, if used) on opposites of the gate electrode as well as into the landing pads 622 and 624. Sidewall spacers 808 prevent the underlying previously formed tip regions and the semiconductor body 620 from being doped by the heavy source/drain implant 810. Additionally, as before, the sacrificial gate electrode 804 masks the channel region from being doped during the heavy source/drain formation step.

[0061] Additionally, if desired, silicide 812, such as but not limited to cobalt silicide, nickel siliide, and titanium silicide may be formed onto the exposed surfaces of the semiconductor body or onto the additionally added silicon film as shown in Figure 8C. Silicide can be formed onto the top surface and side surfaces of the exposed semiconductor body or additional silicon by utilizing a self-aligned or "salicide" process. In a self-aligned or "salicide" process, a refractory metal film, such as

but not limited to titanium, nickel and cobalt can be blanket deposited over the substrate including the silicon regions and dielectric regions. The substrate is then annealed to a temperature sufficient to cause the blanket deposited metal layer to react with the silicon containing regions to form a silicide. Regions, such as sidewalls spacers 808, as well as insulating layer 606 will not react with the metal and the metal will remain unreacted metal in these areas. Next, a selective wet etch can be used to remove the unreacted metal while leaving the metal silicide 812. In this way, silicide can be selectively formed only onto the silicon or semiconductor regions of a substrate as shown in Figure 8C.

5

10

15

20

25

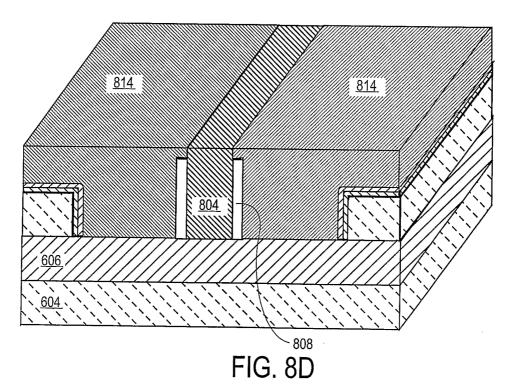

[0062] Next, as shown in Figure 8D, a dielectric layer 814 is blanket deposited over the substrate. The dielectric layer is formed to a thickness sufficient to completely cover the substrate including sacrificial gate electrode 804. The dielectric layer 814 is formed of a material which can be selectively etched with respect to the sacrificial gate material as well as semiconductor body 620. That is, the dielectric material is formed of a material whereby the sacrificial gate electrode 804 can be removed without significantly etching away the dielectric layer 814. After blanket depositing the dielectric, the dielectric layer is planarized, such as chemical mechanical planarization until the top surface of the dielectric film is planar with the sacrificial gate electrode and the top surface of the sacrificial gate electrode exposed as shown in Figure 8D.

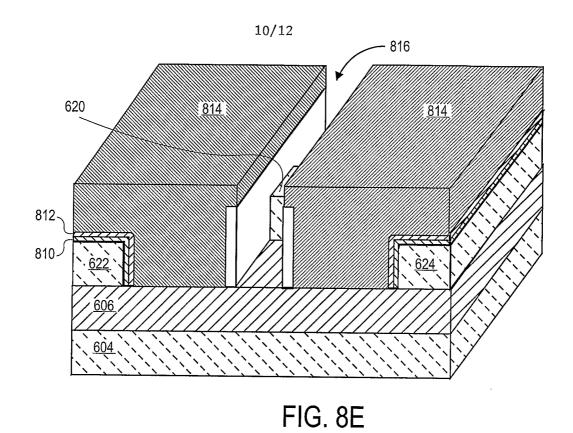

[0063] Next, as shown in Figure 8E, the sacrificial gate 804 and gate dielectric 802 are etched out to form an opening 816 where the gate electrode is to be formed. Removing the sacrificial gate 808 and the sacrificial gate dielectric layer 802 exposes the channel region of the semiconductor body 620 of the nonplanar device as shown in Figure 8E. Removal of the sacrificial gate electrode forms an opening 816 where the gate electrode is to be formed.

[0064] Next, as shown in Figure 8F, the substrate is exposed to a undercut etch to form undercut opening 818 as described above. The undercut etch removes a

portion of the insulating layer 606 from beneath the channel region of semiconductor body 620 as shown in Figure 8F. The undercut etch can be used completely remove the insulating layer 606 from beneath the channel of semiconductor body 620 to expose the entire underside of the channel region of semiconductor body 620 in order to form a fully wrapped around gate electrode. Alternatively, the undercut etch may remove only a portion of the insulating layer 606 from beneath each side of the channel region of semiconductor body 620 so that a partially wrapped around gate electrode can be fabricated as described above.

5

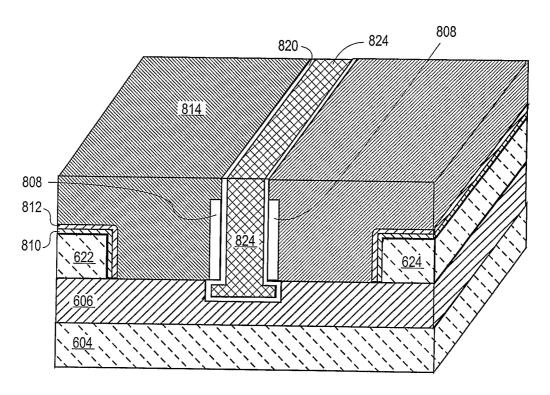

10 [0065] Next, as gate dielectric 820 and a gate electrode 824 are formed in openings 816 and 818 as shown in Figure 8G. First, a gate dielectric film 820 is blanket deposited over the substrate. The gate dielectric material covers the top surface and sidewalls of the channel region of the semiconductor body 620 as well as the exposed lower surfaces of the semiconductor body 620 as described 15 above. The gate dielectric material is formed by a conformal process, such as CVD or ALD, in order to ensure the formation of the gate dielectric material on the exposed underside of the channel region of the semiconductor body 620. Next, a gate electrode material is blanket deposited over the gate dielectric. The gate electrode material may be any well known gate electrode material, such as described above. The gate electrode material and gate dielectric are then 20 chemically mechanically planarized until the top surface of the dielectric layer 814 is revealed as shown in Figure 8G. Once the gate electrode material and the gate dielectric material are polished back or removed from the top dielectric material 814, a gate electrode 824 and gate dielectric layer 820 have been formed. The 25 gate dielectric and gate electrode either partially or fully wraps around the channel region of the semiconductor body 620 as described above. Dielectric layer 814 can left on the nonplanar device as shown in Figure 8G and become part of the "back end" or interlayer dielectric (ILD) and metalization system used to

electrically couple various nonplanar devices together into functional circuits. Alternatively, dielectric layer 814 can be removed at this time and replaced by another type of interlayer dielectric for the "back end". This completes this method of forming a nonplanar device having a fully wrapped around or partially wrapped around gate electrode.

[0066] Thus, nonplanar transistors with partially or fully wrapped around gate electrodes and their methods of fabrication have been described.

10

5

#### IN THE CLAIMS

We claim:

10

15

20

25

5 1. A nonplanar semiconductor device comprising:

a semiconductor body having a top surface opposite a bottom surface formed above an insulating substrate, wherein said semiconductor body has a pair of laterally opposite sidewalls;

a gate dielectric formed on said top surface of said semiconductor body, on said bottom surface of said semiconductor body, and on said laterally opposite sidewalls of said semiconductor body;

a gate electrode formed on said gate dielectric, on said top surface of said semiconductor body and adjacent to said gate dielectric on said laterally opposite sidewalls of said semiconductor body and beneath said gate dielectric on said bottom surface of said semiconductor body; and

a pair of source/drain regions formed in said semiconductor body on opposite sides of said gate electrode.

- 2. The semiconductor device of claim 1 wherein said semiconductor body is a single crystalline silicon film.

- 3. The semiconductor device of claim 1 wherein said semiconductor body is selected from the group consisting of germanium, silicon germanium, gallium arsenide, InSb, GaP, GaSb and carbon nanotubes.

4. The semiconductor device of claim 1 wherein said gate electrode comprises a material selected from the group consisting of polycrystalline silicon, tungsten, tantalum, titanium, and metal nitrides.

5. The semiconductor device of claim 1 wherein said insulating substrate comprises an oxide film formed on a monocrystalline silicon substrate.

- 5 6. The semiconductor device of claim 1 wherein said semiconductor device further includes at least one additional semiconductor body having a top surface and a bottom surface, and a pair of laterally opposite sidewalls wherein a gate dielectric layer is formed said top surface, said bottom surface and said sidewalls of said at least one other semiconductor body, and wherein said gate electrode is formed on said gate dielectric on said top surface of said at least one other semiconductor body, and adjacent to said gate dielectric on said laterally opposite sidewalls of said at least one other semiconductor body, and beneath the gate dielectric on said bottom surface of said at least one other semiconductor body.

- 15 7. A nonplanar semiconductor device comprising:

20

25

a semiconductor body having a top surface opposite a bottom surface having a portion formed on an insulating substrate, said semiconductor body having laterally opposite sidewalls formed above said insulating substrate;

a gate dielectric formed on said top surface of said semiconductor body, on said laterally opposite sidewalls of said semiconductor body, and on portion of the bottom surface of said semiconductor body not on said insulating substrate;

a gate electrode formed on said gate dielectric on said top surface of said semiconductor body and adjacent to said gate dielectric on said laterally opposite sidewalls of said semiconductor body, and beneath said gate dielectric on said bottom surface of said semiconductor body; and

a pair of source/drain regions formed in said silicon body on opposite sides of said gate electrode.

8. The semiconductor device of claim 7 wherein said semiconductor body is a single crystalline silicon film.

- 9. The semiconductor device of claim 7 wherein said semiconductor body is

5 selected from the group consisting of germanium, silicon germanium, gallium arsenide, InSb, GaP, GaSb and carbon nanotubes.

- 10. The semiconductor device of claim 7 wherein said gate electrode comprises a material selected from the group consisting of polycrystalline silicon, tungsten, tantalum, titanium and metal nitrides.

- 11. The semiconductor device of claim 7 wherein said insulating substrate comprises an oxide film formed on a monocrystalline silicon substrate.

10

- 15 12. The semiconductor device of claim 1 wherein said semiconductor device further includes at least one additional semiconductor body having a top surface and a bottom surface, and a pair of laterally opposite sidewalls wherein a gate dielectric layer is formed said top surface, said bottom surface and said sidewalls of said at least one other semiconductor body, and wherein said gate electrode is formed on said gate dielectric on said top surface of said at least one other semiconductor body, and adjacent to said gate dielectric on said laterally opposite sidewalls of said at least one other semiconductor body, and beneath the gate dielectric on said bottom surface of said at least one other semiconductor body.

- 25 13. A method of forming a nonplanar semiconductor device comprising: forming a semiconductor body having a top surface opposite a bottom surface and a pair of laterally opposite sidewalls above an insulating substrate;

forming a gate dielectric on said top surface of said semiconductor body, on said laterally opposite sidewalls of said semiconductor body, and on at least a portion of said bottom surface of said semiconductor body;

forming a gate electrode on said gate dielectric on said top surface of said semiconductor body and adjacent to said gate dielectric on said laterally opposite sidewalls of said semiconductor body and subadjacent to said gate dielectric formed on at least a portion of said bottom surface of said semiconductor body; and

forming a pair of source/drain regions in said semiconductor body on opposite sides of said gate electrode.

14. The method for forming said semiconductor device of claim 13 wherein said gate dielectric and gate electrode are formed beneath the entire channel region of said semiconductor body.

15

5

15. The method of claim 13 wherein a portion of the bottom surface of said semiconductor body is formed on said insulating substrate wherein said portion on said insulating substrate is located beneath said gate electrode above said top surface of said semiconductor body.

20

- 16. The method of claim 13 wherein said semiconductor body is a single crystalline silicon film.

- 17. The method of claim 13 wherein said semiconductor body is selected from

25 the group consisting of germanium, silicon germanium, gallium arsenide, InSb,

GaP, GaSb and carbon nanotubes.

18. The method of claim 13 wherein said gate electrode comprises a material selected from the group consisting of polycrystalline silicon, tungsten, tantalum, titanium and metal nitrides.

- 5 19. The method of claim 13 wherein said insulating substrate comprises an oxide film formed on a monocrystalline silicon substrate.

- 20. The method of claim 13 further including forming at least one additional semiconductor body having a top surface and a bottom surface, and a pair of laterally opposite sidewalls and forming a gate dielectric layer over said top surface, said bottom surface and said sidewalls of said at least one other semiconductor body, and wherein said gate electrode is formed on said gate dielectric on said top surface of said at least one other semiconductor body, and adjacent to said gate dielectric on said laterally opposite sidewalls of said at least one other semiconductor body, and beneath the gate dielectric on said bottom surface of said at least one other semiconductor body.

- 21. A method of forming a nonplanar transistor comprising:

10

15

20

25

forming a semiconductor body having a pair of laterally opposite sidewalls and a top surface and a bottom surface on an insulating substrate;

removing a portion of said insulating substrate from beneath said semiconductor body to undercut said semiconductor body and expose a portion of said bottom surface of said semiconductor body;

forming a gate dielectric on said top surface of said semiconductor body, on said sidewalls of said semiconductor body, and on said exposed bottom portion of said semiconductor body;

depositing a gate material over and around said semiconductor body and beneath said exposed portion of said semiconductor body;

etching gate electrode material into a gate electrode utilizing a first anisotropic etch followed by a isotropic etch to form a gate electrode which is formed over the gate dielectric layer on the top surface of said semiconductor body and is formed adjacent the gate dielectric formed on the sidewalls of said semiconductor body and is formed beneath said gate dielectric formed on said exposed portions of said bottom surface of said semiconductor body; and

placing dopants into said semiconductor body on opposite sides of said gate electrode to form a pair of source/drain regions.

- 10 22. The method of claim 21 wherein said semiconductor body is formed from single crystalline silicon.

- 23. The method of claim 22 wherein said insulating substrate comprises a lower monocrystalline silicon substrate and a top silicon oxide,

15

20

5

24. A method of forming a nonplanar transistor comprising:

forming a semiconductor body having a top surface and a bottom surface and a pair of laterally opposite sidewalls on an insulating substrate:

forming a dielectric film over and around said semiconductor body, wherein said dielectric film has an opening which exposes the channel region of said semiconductor body;