(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-21436

(P2009-21436A)

(43) 公開日 平成21年1月29日(2009.1.29)

| (51) Int.Cl.          | F 1        | テーマコード (参考) |

|-----------------------|------------|-------------|

| HO1L 49/00 (2006.01)  | HO1L 49/00 | Z 5FO38     |

| HO1L 45/00 (2006.01)  | HO1L 45/00 | C 5FO83     |

| HO1L 27/10 (2006.01)  | HO1L 27/10 | 451         |

| HO1L 21/822 (2006.01) | HO1L 27/04 | M           |

| HO1L 27/04 (2006.01)  |            |             |

審査請求 未請求 請求項の数 17 O L (全 26 頁)

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2007-183478 (P2007-183478) | (71) 出願人 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号     |

| (22) 出願日  | 平成19年7月12日 (2007.7.12)       | (74) 代理人 | 110000350<br>ポレール特許業務法人                         |

|           |                              | (72) 発明者 | 笛子 佳孝<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

|           |                              | (72) 発明者 | 寺尾 元康<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

|           |                              | (72) 発明者 | 高浦 則克<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所中央研究所内 |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】3個以上の電極間の接続を切り替えができる簡単な構造の、小面積、不揮発、高機能のデバイスを提供する。

【解決手段】少なくとも1つの電極が、固体電解質膜2の中を移動し易い銅、銀などを含む3つ以上の電極を有し、その電極は固体電解質膜を介して対向し、電圧を印加することにより電極間に導電バスが生成または消滅されてスイッチオン／スイッチオフ動作をさせる。さらに、2電極間に生成された導電バスは、別の第3の電極に電圧を印加することで、導電バスで繋がれた2電極間に電圧を印加することなく消滅させることができた。

【選択図】図2

図 2

**【特許請求の範囲】****【請求項 1】**

半導体基板上に設けられ第1の金属を含む第1の電極と、

前記第1の電極と対向して設けられ、前記第1の金属と異なる第2の金属を含む少なくとも2つの第2の電極と、

前記第1の電極と前記少なくとも2つの第2の電極との間に介在する固体電解質膜とを有し、

前記第1の金属が、電圧印加によりイオン化し、前記固体電解質膜中を移動し前記移動経路に沿って堆積することで、前記固体電解質膜中に低抵抗な導電パスを生成する金属であることを特徴とする半導体装置。

10

**【請求項 2】**

前記第1の電極と前記固体電解質膜との間にそれぞれと接して設けられ第3の金属を高濃度に含む固体電解質膜を有し、

前記第3の金属が、電圧印加によりイオン化し、前記固体電解質膜中を移動することで、前記固体電解質膜中に低抵抗な導電パスを生成する金属であることを特徴とする請求項1に記載の半導体装置。

**【請求項 3】**

前記低抵抗な導電パスは、前記第1の金属を含んでなる金属フィラメントからなることを特徴とする請求項1に記載の半導体装置。

**【請求項 4】**

前記導電パスが、前記第1および第2の電極間に電圧を印加することなく持続的に保持される不揮発性を有することを特徴とする請求項3に記載の半導体装置。

20

**【請求項 5】**

前記第1の金属が、銅であることを特徴とする請求項1に記載の半導体装置。

**【請求項 6】**

前記第1の金属が、銀であることを特徴とする請求項1に記載の半導体装置。

**【請求項 7】**

前記第1の金属と前記第3の金属が、銅または銀であることを特徴とする請求項2に記載の半導体装置。

30

**【請求項 8】**

前記第1の金属がタンクステンまたはタンタルであり、前記第3の金属が銅または銀であることを特徴とする請求項2に記載の半導体装置。

**【請求項 9】**

前記第1の電極下部の少なくとも一部が、前記固体電解質膜と接していることを特徴とする請求項1に記載の半導体装置。

**【請求項 10】**

前記半導体基板上に平面的に設けられた前記第1の電極および前記少なくとも2つの第2の電極のそれぞれが、前記半導体基板の主面を基準に同じ標高で前記固体電解質膜と接していることを特徴とする請求項1に記載の半導体装置。

40

**【請求項 11】**

前記第1の電極および前記第2の電極の少なくともいずれか一つの電極が、前記半導体基板上に設けられた絶縁膜への埋め込み配線またはプラグで形成されていることを特徴とする請求項1に記載の半導体装置。

**【請求項 12】**

前記第1の電極および前記第2の電極の少なくともいずれか一つの電極が、前記電極と接して設けられた絶縁膜との界面に、前記第1および第2の電極に含まれる金属の前記絶縁膜への拡散を抑制するバリアメタルを含むことを特徴とする請求項1に記載の半導体装置。

**【請求項 13】**

前記バリアメタルが、Ti、TiN、Ta、あるいはTaNであることを特徴とする請求項12に

50

記載の半導体装置。

**【請求項 1 4】**

前記第1の電極および前記第2の電極のそれぞれの側壁の少なくとも一部が、固体電解質膜に接していることを特徴とする請求項1に記載の半導体装置。

**【請求項 1 5】**

半導体基板上に設けられた少なくとも3つの電極を有し、

前記少なくとも3つの電極のいずれか2つの第1および第2の電極間に印加される電圧により、前記第1および第2の電極間に形成された導電バスを、前記第1および第2の電極とは異なる第3の電極と前記第1または第2の電極との間に電圧を印加することで、前記第1および第2の電極間に電圧を印加することなく、前記第3の電極と前記第1または第2の電極との間に形成された前記導電バスとは別の導電バスに切り替えることを特徴とする半導体装置。10

**【請求項 1 6】**

請求項15に記載の半導体装置を具備してなる複数のセルで構成されたアレイを有し、

前記セルの各々は、電極間に導電バスを生成する時に陽電圧が印加される陽極電極と、負電圧が印加される陰極電極とを備え、

前記セルの一つが有する陰極電極の一つと、前記セルの一つとは別のセルが有する陽極電極の一つとが金属配線で電気的に接続されていることを特徴とする半導体装置。20

**【請求項 1 7】**

前記セルの一つが有する陰極電極の一つと、前記セルの一つが有する陽極電極の一つとの間に電圧印加して導電バスを形成することにより、前記セルの一つが有する陽極電極と、前記別のセルが有する陽極電極とを電気的に接続し、20

該電圧印加を別の複数のセルに適用することにより、前記アレイ内の複数のセルが所望の経路で電気的に接続されることを特徴とする請求項16に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、半導体装置に関し、特に電気的切り替えが可能な不揮発性ロジックデバイスの高集積化、高性能化を実現する技術、その応用である人間に近い記憶および論理判断能力を持つ半導体装置に関する。30

**【背景技術】**

**【0 0 0 2】**

従来のCMOSで構成されたロジックデバイスは、面積が大きいこと、電源OFF時にリセットされてしまうこと、という欠点があった。これに対して、非特許文献1ではロジックデバイスの1例であるクロスバスイッチで、構成要素であるSRAMとパストランジスタのうち面積が大きく揮発性のSRAM部分を、小面積かつ不揮発の固体電解質ナノスイッチで置換することで問題を解決することを提案されている。

**【0 0 0 3】**

また、ロジックデバイスの進んだ応用先として、人工知能を実現する試みであるニューラルネットワーク(非特許文献2、3)がある。人の脳には、経験を元に迅速に判断したり必要な事項だけを記憶したりできるといった現在最先端のコンピュータでも実現できていない優れた機能がある。こうした機能を実現しようとする従来技術がニューラルネットワークだが、これまでの試みでは期待されたような成果は得られていない。40

**【0 0 0 4】**

**【非特許文献1】**「インターナショナル ソリッドーステート サーキット コンフェラنس (International Solid-State Circuits Conference)」、2004、p.15-19

**【非特許文献2】**甘利俊一、外山敬介編 「脳科学大事典」、朝倉書店 (2000)

**【非特許文献3】**Jeff Hawkins and Sandra Blakeslee、 “On intelligence”、 Times Books (2004)

**【非特許文献4】**<http://www.taiiku.tsukuba.ac.jp/coe/symposium2.html>

【非特許文献 5】<http://www.sat.t.u-tokyo.ac.jp/~kohno/lecturenotes.html>

【非特許文献 6】是角圭祐、森江隆、野村修、中野鉄平、真継優和、岩田穆「AD融合／混載アーキテクチャによる顔・物体認識のための画像フィルタリングプロセッサ」、電子情報通信学会 集積回路研究会、ICD2005-58、(2005)、p.19-24

【発明の開示】

【発明が解決しようとする課題】

【0005】

セル間の配線接続の強度を変化させることで学習、記憶させるのがニューラルネットワークである。ハードウェア的観点から従来のニューラルネットワークは、セル同士を複雑に配線で接続する必要があったため、高機能の実現に必須の大規模化が実現できなかった。

10

【0006】

本発明の目的は、3個以上の電極間の接続を切り替えができる簡単な構造のデバイスを提供し、大規模なロジックを小面積で実現することにある。

【0007】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

20

本発明の半導体装置は、電圧印加により固体電解質膜中に金属フィラメントでできた導電バスの生成／消滅により、固体電解質膜を介して対向する電極間をスイッチングさせる。また、本発明の半導体装置は、固体電解質膜を介して対向する電極は、従来の半導体装置のように2つでは無く、3つ以上あり、なおかつそのうちの少なくとも3つは同じくらいの距離を隔てて対向している。更に固体電解質膜を介して対向している電極のうち1つ以上が銅、銀などの固体電解質膜中を移動しやすい原子を含むか、または固体電解質膜の一部に銅、銀などの固体電解質膜中を移動しやすい原子を高濃度で含むものである。

【0009】

また、本発明の半導体装置は、スイッチング動作させる際に対応する電極間に電圧を印加する。すなわち銅、銀などの固体電解質膜中を移動しやすい原子を含む電極、または銅、銀などの固体電解質膜中を移動しやすい原子を含む固体電解質膜の部分に近接している電極を陽極になるようにすることで、固体電解質膜中にこれら金属でできたフィラメントが生成され電子の導電バスとなり、スイッチオン状態とできる。また逆の極性の電圧を印加することでスイッチオフ動作させる。本発明の半導体装置は、従来の固体電解質膜を用いたこれら2端子間の電圧印加によるスイッチング動作に加え、2端子間に生成された導電バスを第3の電極に電位を印加するだけで消滅させるという新しい動作をさせるものである。

30

【発明の効果】

【0010】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

40

従来、複雑な構造であったロジックデバイスを固体電解質を用いた単純な構造のデバイスで作成することで、デバイスの小面積化による製造コストの低減が可能となる。また、簡単な構造ゆえ大規模化が可能であり、瞬時の認識、判断など人間の脳の優れた機能を実現することができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返し

50

の説明は省略する。

< 実施例 1 >

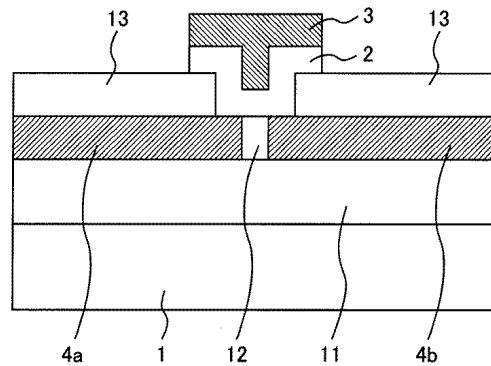

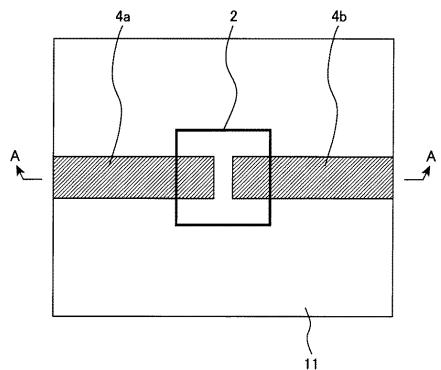

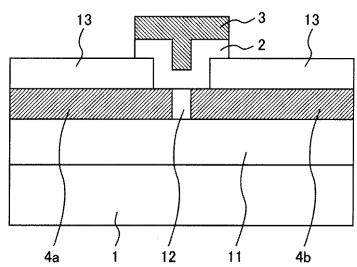

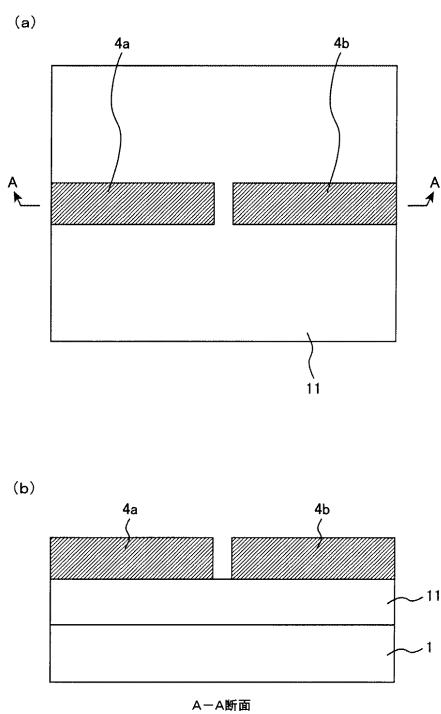

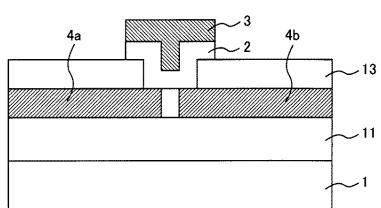

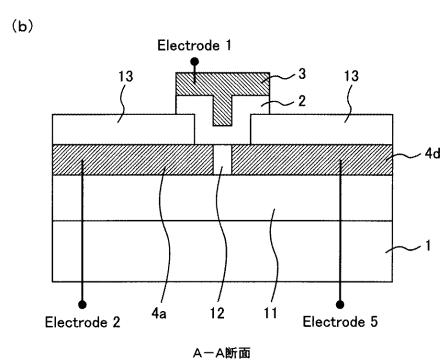

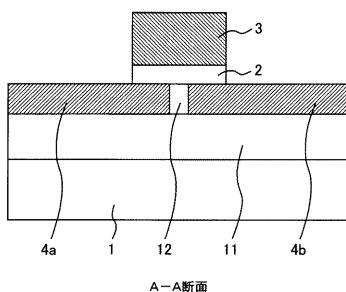

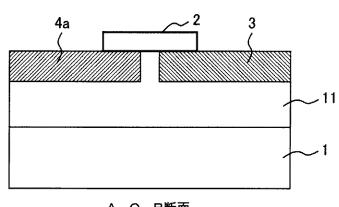

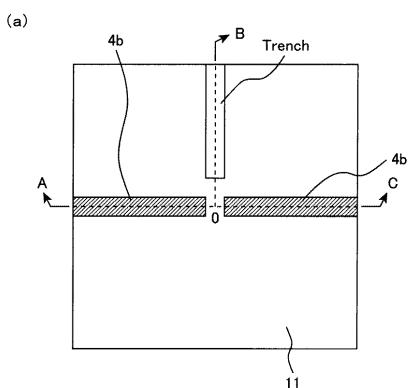

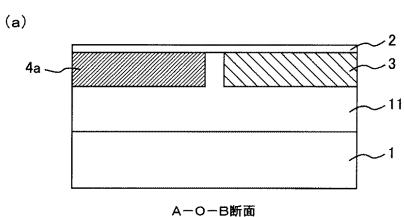

図 1 は、本発明の実施例 1 である半導体装置の一例を示した一部平面であり、図 2 は図 1 におけるA - A線断面図である。なお、図 1 の平面図において、図面を見やすくするために一部の部材は省略している。

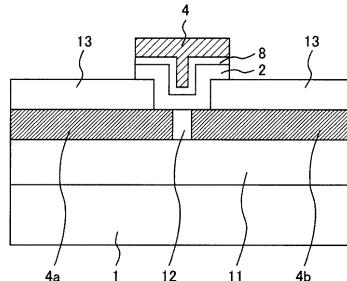

本実施例の半導体装置は、電気抵抗の高い固体電解質膜材料中で銅などの金属イオンが微細な導電パスを形成することでスイッチオン状態、形成された導電パスが消滅することでスイッチオフ状態となる現象を用いたスイッチデバイスである。前記の導電パスの生成 / 消滅は、電極間に印加された電圧により固体電解質材料中を銅 (Cu) などの金属イオンが移動する事で起こる。この半導体装置は、絶縁膜 11 上に形成されたタンゲステンで形成された電極 4a、4b とその間を絶縁する絶縁膜 12、絶縁膜 12 と電極 4a、4b の上に形成された固体電解質膜 2 とその上部に形成された Cu 電極 3、そして銅電極 3 が極狭い領域で固体電解質膜 2 を介して電極 4a、4b と接近するように設けられた絶縁膜 13 を有する。

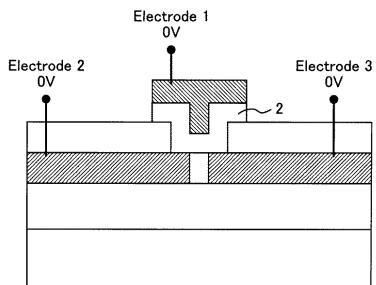

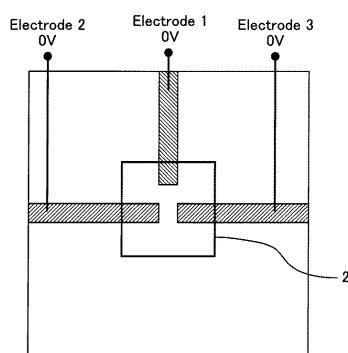

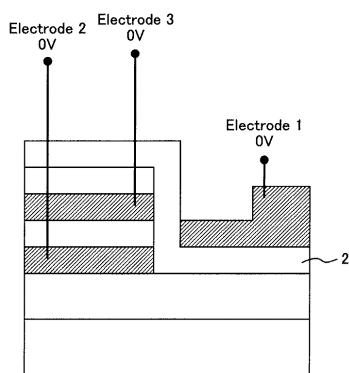

【 0 0 1 2 】

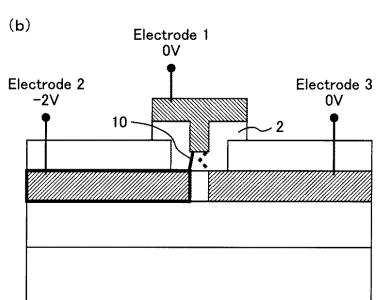

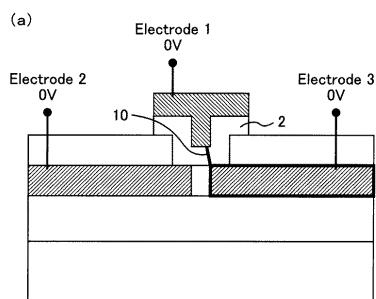

本実施例の半導体装置の動作を説明するために、図 3 のように 3 つの電極を Electrode 1、2、3 と定義する。図 3 は、3 つの電極が全て 0V で、固体電解質膜 2 の中には金属 (Cu) でできた導電パスが生成されていない状態である。

【 0 0 1 3 】

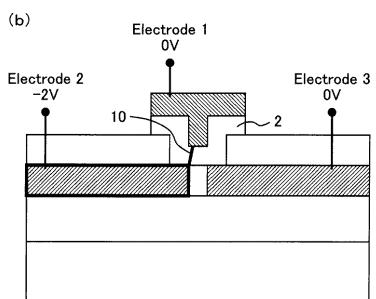

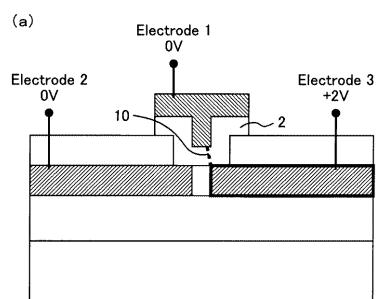

図 3 の状態から電極間に導電パスを生成するためには、例えば図 4 (a) のように Electrode 1、2 には 0V、Electrode 3 には -2V 程度の電位を印加し、Electrode 1 と Electrode 3 の間に電位差が生じさせる。Electrode 1 (Cu 電極 3) に含まれる Cu 原子の一部は、固体電解質 2 との境界で Cu+ にイオン化し固体電解質中に生じた電界により Electrode 3 の方向に移動する。この反応が進むと、Cu 原子は固体電解質中でフィラメントを形成する。Electrode 1 と 3 の間が Cu のフィラメントで繋がると、このフィラメントが電子の導電パス 10 となり、Electrode 1 と 3 の間の電流が飛躍的に増大する。これがスイッチオン動作である。生成された導電パス 10 は、Electrode 3 の電位を 0V にしても存在し続ける不揮発性のものである。同様に図 3 の状態から図 4 (b) のように Electrode 2 に -2V 程度の電位を印加すると導電パス 10 が Electrode 1 と 2 の間に形成されスイッチオン状態となる。

【 0 0 1 4 】

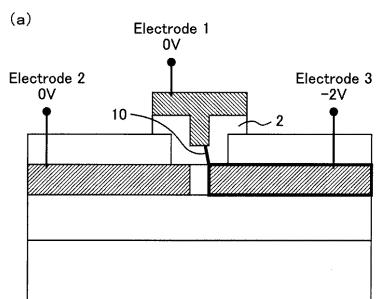

逆に図 4 (a) で生成されている導電パス 10 を切断するためには、Electrode 1、2 に 0V、Electrode 3 に +2V を印加する。フィラメントを形成している Cu 原子はイオン化 (Cu+) して電界により固体電解質 2 中を Electrode 1 の方向に移動する。Electrode 1 の表面に到達すると Cu+ から Cu に戻り電極の一部を形成する。この反応が進むと、フィラメントを形成していた Cu 原子が減少し、やがてフィラメントは消滅もしくは切断される。電子電流の導電パスが無くなるため、Electrode 1 と 3 の間の電流は激減する。これがスイッチオフ動作である。導電パスが切断されたスイッチオフ状態は Electrode 3 の電圧を 0V にしても維持される。同様に図 4 (b) の状態から図 5 (b) のように Electrode 2 に +2V 程度の電位を印加すると Electrode 1 と 2 の間に形成された導電パス 10 が切断され、スイッチオフ状態となる。

【 0 0 1 5 】

実施例 1 の半導体装置で、Electrode 1 - Electrode 2 間、Electrode 1 - Electrode 3 間、Electrode 2 - Electrode 3 間距離を同じ程度、たとえば数 10nm 程度にすると、図 4、5 のような 2 電極間だけのスイッチオン / スイッチオフ動作に加え、電極間の干渉現象を利用した動作が可能となる。

【 0 0 1 6 】

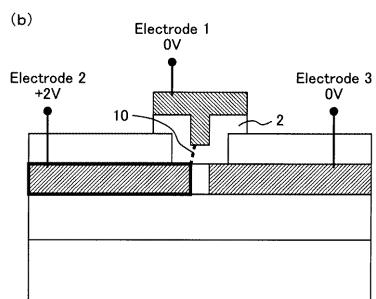

実施例 1 の半導体装置を図 4 (a) の方法で図 6 (a) の状態、すなわち Electrode 1 - Electrode 3 間がオン状態で Electrode 1 - Electrode 2 間がオフ状態にする。この状態で、Electrode 1、3 に 0V、Electrode 2 に -2V の電位を印加する。すると、図 4 (b) の動作

10

20

30

40

50

と同様に、Electrode 1 からイオン化した銅 (Cu+) がElectrode 2 の方へ固体電解質膜 2 中を移動し Cu フィラメントを形成する。Electrode1 - Electrode2 間が Cu フィラメントで繋がると導電パス 10 が形成され、Electrode1 - Electrode2 間がスイッチオン状態となる。これと同時に、図 6 (a) でフィラメントを形成していた Cu 原子は、Electrode 2 に印加された - 2 V の影響でイオン化され Electrode 2 の方向へ固体電解質膜 2 中を移動する。反応が進むとフィラメントを形成していた Cu 原子が減少しやがて切断される。つまり Electrode 1 - Electrode 3 間はスイッチオフ状態となる。結果として、図 6 (b) の動作では、Electrode 1 - Electrode 3 間に電位差を与えることなく Electrode 1 - Electrode 3 間から Electrode 1 - Electrode 2 間に導電パス 10 を切り替えるという従来の半導体装置には無い新しい動作が実現されている。

10

#### 【0017】

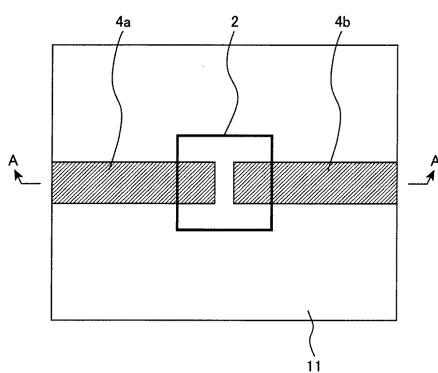

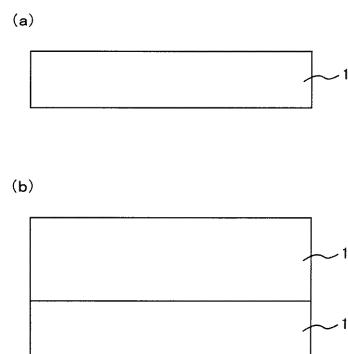

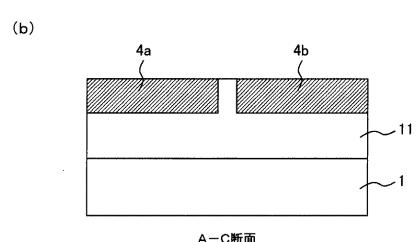

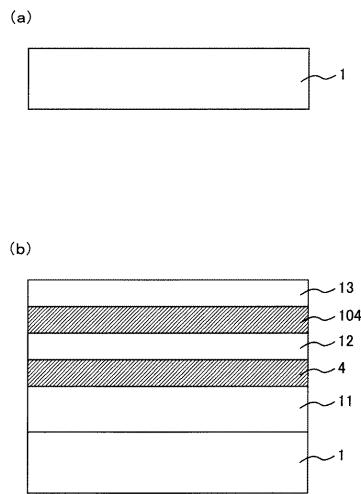

図 7 ~ 図 10 は、実施例 1 の半導体装置の製造方法の 1 例を示した断面図および平面図である。

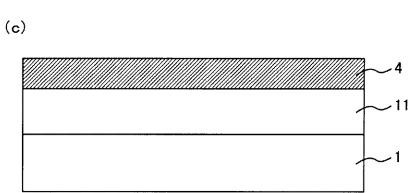

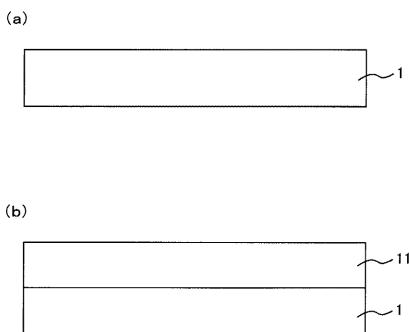

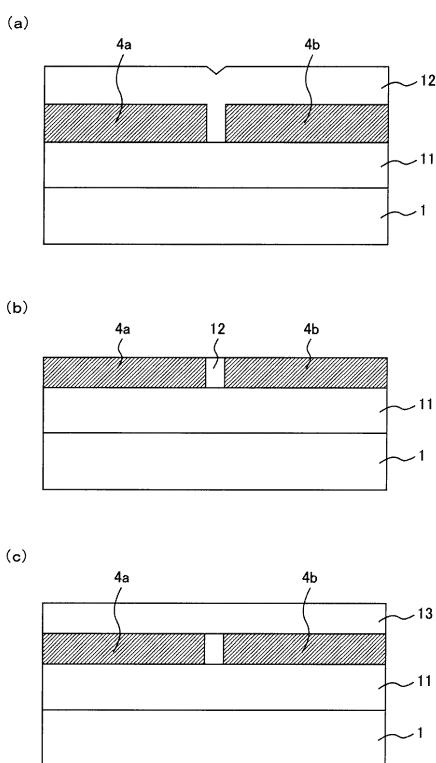

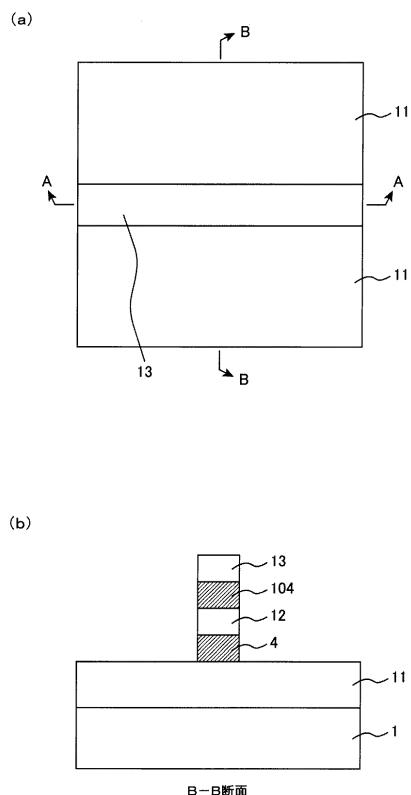

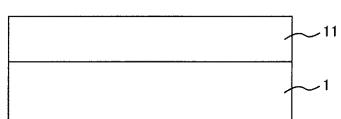

まず、半導体基板 1 を用意する (図 7 (a))。続いて絶縁膜 11 を例えば Chemical Vapor Deposition (CVD) 法を用いて 200 nm 程度堆積する (図 7 (b))。続いて、例えばタンゲステン膜 4 を CVD 法を用いて 100 nm 程度堆積する (図 7 (c))。次にリソグラフィとドライエッチング技術により、タンゲステン膜 4 を、4a と 4b にパターニングする。パターニング形状の平面図が図 8 (a)、図 8 (a) の A - A 線断面図が図 8 (b) である。

20

次に、シリコン酸化膜 12 を CVD 法で堆積する (図 9 (a))。このとき、図 8 (a) と (b) でパターニングしたタンゲステン 4 のスペースがシリコン酸化膜 12 で完全に埋まるようにする。

#### 【0018】

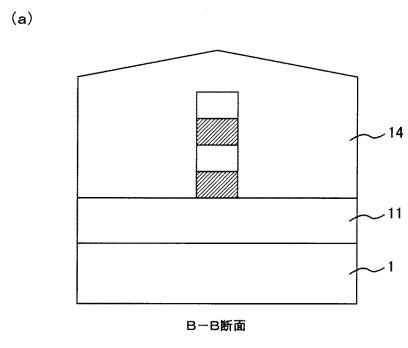

次に、化学的機械研磨 (CMP) 法を用いてシリコン酸化膜 12 の一部を除去し、タンゲステン 4a、4b の上表面を露出させる (図 9 (b))。次にシリコン酸化膜 13 を 100 nm 程度堆積する (図 9 (c))。

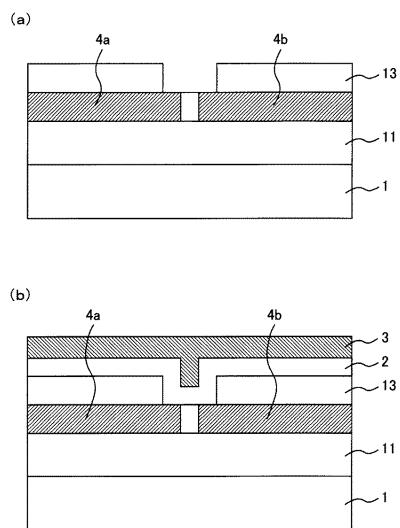

次にリソグラフィとドライエッチング技術により、シリコン酸化膜 13 をパターニングしスペースを形成する。このとき、タンゲステン 4a、4b の上表面の一部が露出するようとする (図 10 (a))。

30

#### 【0019】

次に、固体電解質膜 2 と Cu 膜 3 をスパッタ法または、CVD 法で堆積する (図 10 (b))。固体電解質膜 2 としては、たとえば CuS<sub>2</sub>、CuTaO、CuTaSなどを用いることができる。

次にリソグラフィとドライエッチング技術により、Cu 電極膜 3 と固体電解質膜 2 をパターニングする (図 10 (c))。

#### 【0020】

その後、図には示していないが、層間絶縁膜を形成した後、Cu 電極 3、タンゲステン電極 4a、4b に至るコンタクト孔および、半導体基板 1 上に形成した集積回路のコンタクト孔、を形成し、続いて金属膜を堆積してこれをパターニングして配線とし、半導体装置を完成した。

40

#### 【0021】

本実施の半導体装置は、単純な構造ゆえ小面積でありなおかつ不揮発のスイッチである。従来の CMOS を用いた大面積かつ揮発性のスイッチと比較して、製造コスト、機能の両面で上回ることができた。

#### < 実施例 2 >

実施例 1 では、固体電解質膜を 1 層で形成し電極の 1 つ (電極 3) を拡散しやすい元素 Cu で形成していたが、固体電解質膜を 2 層で形成し一方を拡散しやすい元素を高濃度で含むようにし、なおかつ純粋な Cu 電極を用いないこともできる。

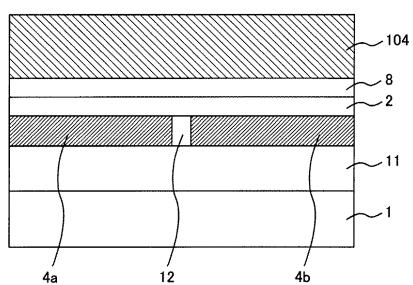

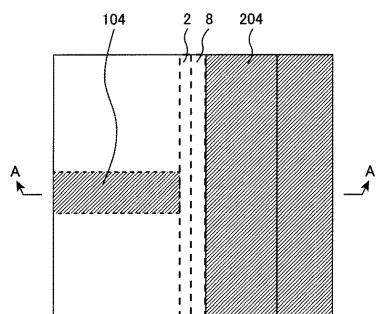

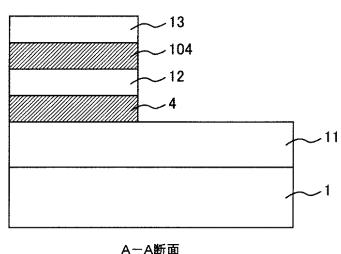

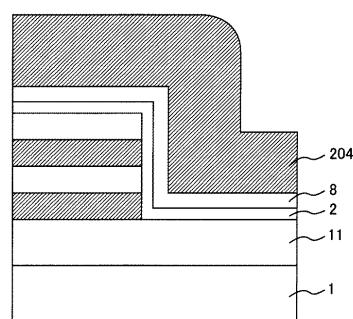

図 11 は、本発明の実施例 2 である半導体集積回路装置の一例を示した図 1 の A - A 線断面図である。

50

## 【0022】

実施例1と同様に電極に電圧印加することで、Cuを高濃度に含む固体電解質膜8から供給されるCuで固体電解質膜2にCuフィラメントを形成させること、固体電解質膜2に生成されたCuフィラメントのCuを固体電解質膜8に戻すことでCuフィラメントを消滅させることができる。固体電解質膜8はCu原子を多く含み低抵抗なので、ほとんど電極の一部と考えられる。固体電解質膜2中にCuフィラメントを生成／消滅させることでスイッチオン／スイッチオフ動作を実現できる。図4から図6と同様の電圧印加により、実施例1の半導体装置と同じ動作を実現できる。

## 【0023】

固体電解質膜2、固体電解質膜8の組合せとしては、例えば、固体電解質膜2／固体電解質膜8 = CuTaO / CuTaS、CuTaO / CuS、WO<sub>3</sub> / CuTaS、WO<sub>3</sub> / CuS、Ta<sub>2</sub>O<sub>5</sub> / CuTaS、Ta<sub>2</sub>O<sub>5</sub> / CuSなど、また銅の代わりに銀(Ag)を固体電解質膜中の導電パスとなるフィラメント形成用金属原子としてTa<sub>2</sub>O<sub>5</sub> / Ag<sub>2</sub>Sなどが可能である。

10

## 【0024】

本実施例2の半導体装置は、図7～図10に示した実施例1の半導体装置の製造方法の1例で、固体電解質膜2を固体電解質膜2と固体電解質膜8の積層に、Cu膜3をタンゲステン膜4に変更することで製造可能である。

20

本実施の半導体装置は、単純な構造ゆえ小面積でありなおかつ不揮発のスイッチである。従来のCMOSを用いた大面積かつ揮発性のスイッチと比較して、製造コスト、機能の両面で上回ることができた。

## &lt;実施例3&gt;

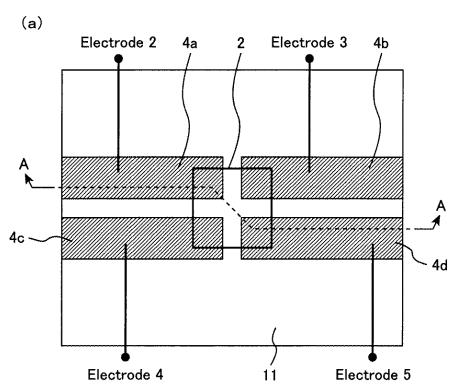

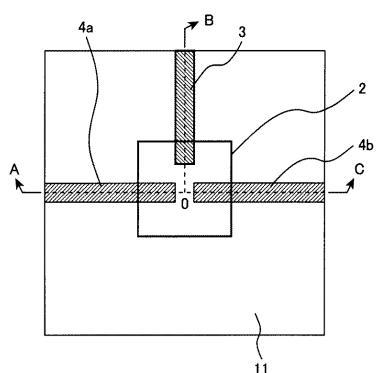

実施例1、2では、3電極を有する半導体装置の例であったが、電極の数を更に増やすこともできる。図12(a)は本発明の実施例3である半導体集積回路装置の一例を示した一部平面図、図12(b)は図12(a)のA-A線断面図である。

## 【0025】

実施例1と同様に、導電パスが固体電解質膜2に生成されていない状態、すなわち全電極間がスイッチオフの状態で、例えばElectrode2に-2V程度の電圧を印加しElectrode1、3、4、5を0Vにすると、Electrode1とElectrode2の間に導電パスが生成されスイッチオン状態となる。生成された導電パスはElectrode2に+2V、Electrode1、3、4、5を0Vにすると切断、あるいは消滅できスイッチオフ状態とすることができる。また、Electrode1とElectrode2の間に導電パスが生成されていて他には導電パスが形成されていない状態で、例えばElectrode3に-2Vを印加しElectrode1、2、4、5を0Vにすると、Electrode3に印加された-2Vによる電界でElectrode1とElectrode2の間に生成されていた導電パスが消滅し代わりにElectrode1とElectrode3の間に導電パスが生成される。結果的に、Electrode1-Electrode2間に電位差を与えることなくElectrode1-Electrode2間からElectrode1-Electrode3間に導電パスを切り替えるという動作が実現される。このような導電パスの切り替え動作は、Electrode1-Electrode2、Electrode1-Electrode3、Electrode1-Electrode4、Electrode1-Electrode5の全ての電極間で相互に行なうことができる。

30

実施例1、2では電極の数は3つ、本実施例3では電極の数は5つだが更に電極数を増やすことももちろん可能である。

40

## 【0026】

また、実施例2と同様に固体電解質膜2とCu電極の組合せの代わりに、固体電解質膜2、固体電解質膜8、タンゲステン電極4の組合せを用いることも可能である。固体電解質膜2、固体電解質膜8の組合せについても実施例2と同様のものが可能である。

本実施の半導体装置は、単純な構造ゆえ小面積でありなおかつ不揮発のスイッチである。従来のCMOSを用いた大面積かつ揮発性のスイッチと比較して、製造コスト、機能の両面で上回ることができた。

## &lt;実施例4&gt;

50

実施例1、2、3では、絶縁膜13のスペースを利用して、極狭い範囲だけで固体電解質膜を介して電極間が近接するようにしたが、上側の電極と固体電解質膜の微細加工技術を用いることもできる。

#### 【0027】

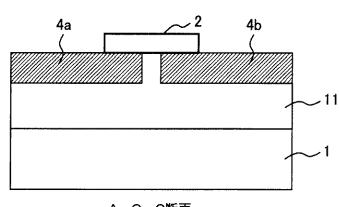

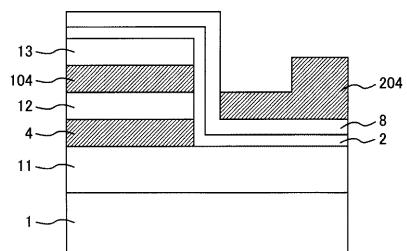

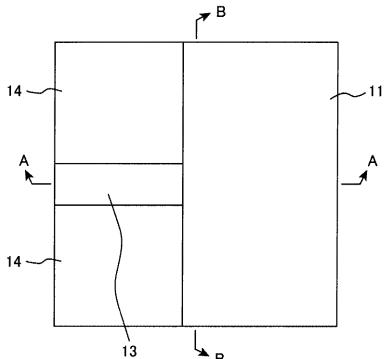

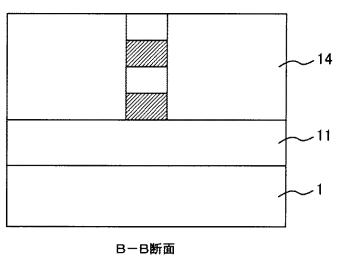

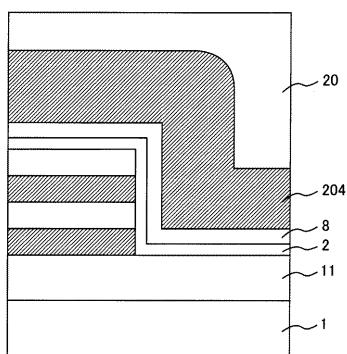

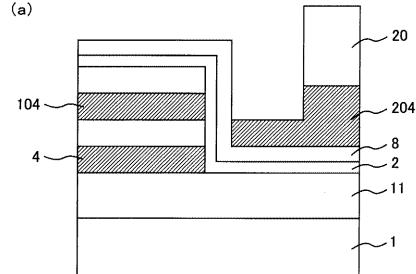

図13は、本発明の実施例4である半導体装置の一例を示した一部平面であり、図14は図13におけるA-A線断面図である。なお、図13の平面図において、図面を見やすくするために一部の部材は省略している。

本実施例4の半導体装置は、実施例2と同様に、固体電解質膜2、8の下側にタンゲステン電極が2個（電極4aと4b）、上側に電極が1個（電極104）を有する。動作原理は実施例2と同じであり、また動作電圧も同様である。

10

#### 【0028】

本実施例4の半導体装置の製造方法は、以下の通りである。実施例1の図9(a)の後、固体電解質膜2、固体電解質膜2よりもCuを高濃度で含み低効率の固体電解質膜8、タンゲステン膜104を堆積する（図15）。その後、リソグラフィとドライエッティング技術を用いて、タンゲステン膜104、固体電解質膜8、固体電解質膜2を順にパターニングする。

#### 【0029】

その後、図には示していないが、層間絶縁膜を形成した後、タンゲステン電極4a、4b、104に至るコンタクト孔および、半導体基板1上に形成した集積回路のコンタクト孔、を形成し、続いて金属膜を堆積してこれをパターニングして配線とし、半導体装置を完成した。

20

#### 【0030】

本実施の半導体装置は、単純な構造ゆえ小面積でありなおかつ不揮発のスイッチである。従来のCMOSを用いた大面積かつ揮発性のスイッチと比較して、製造コスト、機能の両面で上回ることができた。

20

#### <実施例5>

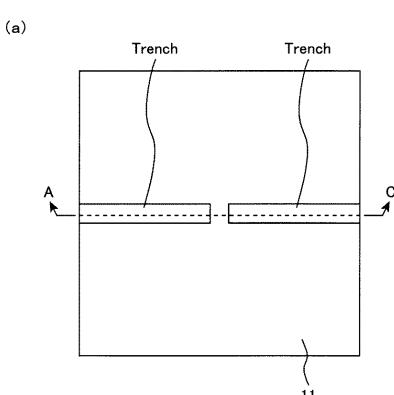

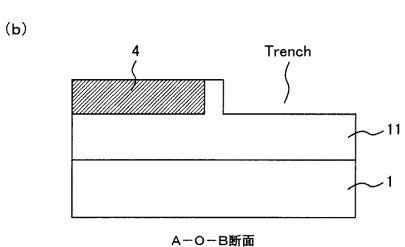

図16は、本発明の実施例5である半導体装置の一例を示した一部平面であり、図17(a)と(b)はそれぞれ図16におけるA-O-C線断面図、A-O-B線断面図である。なお、図16の平面図において、図面を見やすくするために一部の部材は省略している。本実施例の半導体装置は、実施例1、2、3と同様に電気抵抗の高い固体電解質膜中でCuなどの金属イオンが微細な導電バスを生成することでスイッチオン状態、形成された導電バスを消滅させることでスイッチオフ状態となる現象を用いたスイッチデバイスである。前記の導電バスの生成／消滅は、電極間に印加する電圧により固体電解質膜中をCuなどの金属イオンが移動する事で生じさせる。

30

#### 【0031】

本実施例5の半導体装置は、絶縁膜11と、絶縁膜11に形成された溝内に埋め込まれたタンゲステン電極4a、4bと、同じく絶縁膜11に形成された溝内に埋め込まれたCu電極3と、前記電極4a、4b、3が近接している部分を覆う固体電解質膜2を有する。

30

#### 【0032】

図18のように3つの電極をElectrode1、2、3と定義する。図18は、3つの電極が全て0Vで、固体電解質膜2の中には金属(Cu)でできた導電バスが形成されていない状態である。

40

本実施例の半導体装置は、Electrode1、2、3に実施例1で説明した図4、図5、図6と同様の電圧を印加することにより、固体電解質膜2中の導電バスの生成／消滅によるスイッチオン／スイッチオフ動作が可能である。実施例1と同様に、スイッチオン状態、スイッチオフ状態共に不揮発であり電極への電圧印加を止めても維持される。

#### 【0033】

図19～図24は、実施例5の半導体装置の製造方法の1例を示した断面図および平面図である。

50

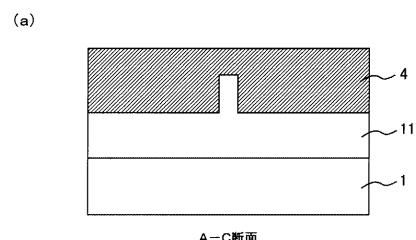

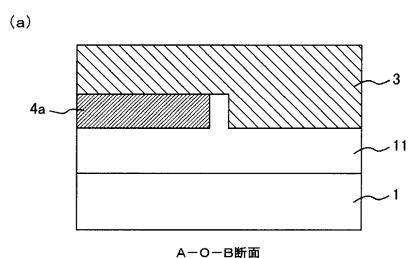

まず、半導体基板1を用意する(図19(a))。続いて絶縁膜11を例えればCVD法を用いて200nm程度堆積する(図19(b))。続いて、リソグラフィとドライエッチング技術により、絶縁膜11中に100nm程度の深さの溝(Trench)を2つ形成する。これらの溝は後の工程で、電極4a、4bが形成されるスペースである。この状態での平面図が図20(a)、図20(a)のA-A線断面図が図20(b)である。

#### 【0034】

次に例えばタンゲステン膜4を溝が完全に埋まるように堆積する(図21(a))。このときバリアメタルを溝表面に堆積しておくと、タンゲステン原子が不必要に絶縁膜11中に拡散するのを防ぐことができる。バリアメタルにはたとえばTi、TiNの積層膜を用いることができる。

10

#### 【0035】

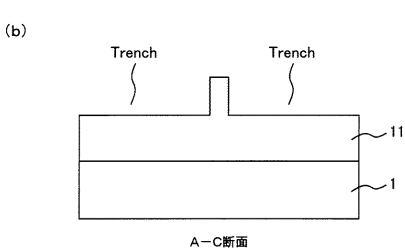

次に、CMP法を用いてタンゲステン膜4の一部を除去し、シリコン酸化膜11の上表面を露出させる(図21(b))。シリコン酸化膜11の上表面を露出させることで、図20(a)と(b)で形成した2つの溝に埋め込まれたタンゲステン4a、4bは残るが、4aと4bは互いにシリコン酸化膜11で分離される。

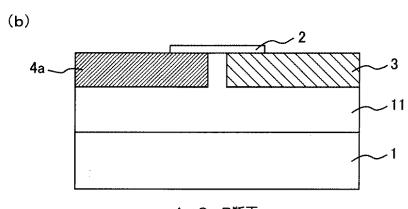

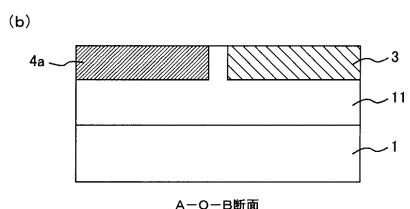

次に、リソグラフィとドライエッチング技術により、絶縁膜11中に100nm程度の深さの溝(Trench)を1つ形成する。この溝は後の工程で、Cu電極3が形成されるスペースである。この状態での平面図が図22(a)、図22(a)のA-O-B線断面図が図22(b)である。次に例えば銅膜3を溝が完全に埋まるように堆積する(図23(a))。このときバリアメタルを溝表面に堆積しておくと、Cu原子が不必要に絶縁膜11中に拡散するのを防ぐことができる。バリアメタルにはたとえばTa、TaNの積層膜を用いることができる。

20

#### 【0036】

次に、CMP法を用いてCu膜3の一部を除去し、シリコン酸化膜11の上表面とタンゲステン電極4a、4bの上表面を露出させる(図23(b))。シリコン酸化膜11の上表面とタンゲステン電極4a、4bの上表面を露出させることで、タンゲステン電極4a、4b、Cu電極3は互いにシリコン酸化膜11で分離される。

#### 【0037】

次に、固体電解質膜2をスパッタ法または、CVD法で堆積する(図24(a))。次にリソグラフィとドライエッチング技術により、固体電解質膜2をパターニングする(図24(b))。

30

その後、図には示していないが、層間絶縁膜を形成した後、タンゲステン電極4a、4bとCu電極3に至るコンタクト孔および、半導体基板1上に形成した集積回路のコンタクト孔、を形成し、続いて金属膜を堆積してこれをパターニングして配線とし、半導体装置を完成了。

#### 【0038】

本実施の半導体装置は、単純な構造ゆえ小面積でありなおかつ不揮発のスイッチである。従来のCMOSを用いた大面積かつ揮発性のスイッチと比較して、製造コスト、機能の両面で上回ることができた。

40

#### <実施例6>

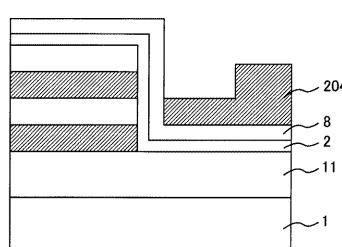

図25は、本発明の実施例6である半導体装置の一例を示した一部平面であり、図26は図25におけるA-A線断面図である。なお、図25の平面図において、図面を見やすくするために一部の部材は省略している。

#### 【0039】

本実施例の半導体装置は、実施例1～5と同様に電気抵抗の高い固体電解質膜材料中でCuなどの金属イオンが微細な導電バスを生成することでスイッチオン状態、生成された導電バスが消滅することでスイッチオフ状態となる現象を用いたスイッチデバイスである。前記の導電バスの生成/消滅は、電極間に印加した電圧で固体電解質材料中をCuなどの金属イオンが移動する事で生じさせる。

#### 【0040】

50

このスイッチデバイスは、絶縁膜11と、絶縁膜11上に積層されたタングステン電極4、絶縁膜12、タングステン電極104、絶縁膜13、固体電解質膜2と固体電解質膜2よりもCuを高濃度に含み低抵抗率の固体電解質膜8、そして前記2つのタングステン電極とは固体電解質膜2、8を介して対抗した1つのタングステン電極204を有する。図27のように3つの電極をElectrode1、2、3と定義する。図27は、3つの電極が全て0Vで、固体電解質膜2の中には金属(銅)でできた導電バスが生成されていない状態である。

#### 【0041】

本実施例の半導体装置は、Electrode1、2、3に対して、実施例2で説明したのと同様の電圧印加を行うことで、固体電解質膜2中の導電バスの生成／消滅によるスイッチオン／スイッチオフ動作が可能である。実施例2と同様に、スイッチオン状態、スイッチオフ状態共に不揮発であり電極への電圧印加を止めても維持される。

10

#### 【0042】

図28～図35は、本実施例6の半導体装置の製造方法の1例を示した断面図および平面図である。

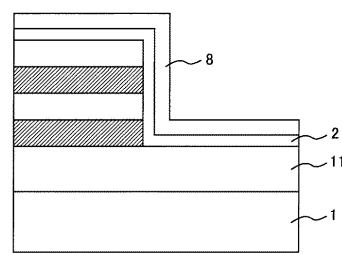

まず、半導体基板1を用意する(図28(a))。続いて絶縁膜11を200nm程度、タングステン電極4、絶縁膜12、タングステン膜104、絶縁膜13を例えばCVD法を用いて100nm程度ずつ堆積する(図28(b))。続いて、リソグラフィとドライエッティング技術により、絶縁膜13、タングステン膜104、絶縁膜12、タングステン膜4をストライプ状にパターニングする。この状態での平面図が図29(a)、図29(a)のB-B線断面図が図29(b)である。

20

#### 【0043】

次に絶縁膜14を前記ストライプ状にパターニングされた絶縁膜13、タングステン膜104、絶縁膜12、タングステン膜4が完全に埋まるように堆積する(図30(a))。次に、CMP法を用いて絶縁膜14の一部を除去し、絶縁膜13の上表面を露出させる(図30(b))。

30

#### 【0044】

次に、リソグラフィとドライエッティング技術により、前記ストライプ形状の積層膜をパターニングする。この段階での平面図が図31、図31のA-A線断面が図32(a)、B-B線断面が図32(b)である。

次に、固体電解質膜2、固体電解質膜2よりも銅を高濃度に含み低効率の固体電解質膜8をスパッタ法または、CVD法で堆積する(図33(a))。このとき固体電解質膜2と固体電解質膜8の積層膜の厚さがタングステン膜4の厚さと等しくなるようにするといい。

30

次に、タングステン膜204を例えばスパッタ法で堆積する(図33(b))。次に、レジスト20を塗布する(図34(a))。

#### 【0045】

次に、エッチバックによりレジスト20の一部を除去しタングステン膜204の表面を露出させる(図34(b))。次にタングステン膜204だけを選択的にエッティングし固体電解質膜8に接している部分の標高がタングステン膜104の下表面とほぼ等しくなるようにする(図35(a))。レジストを除去すると図35(b)となる。

40

#### 【0046】

その後、図には示していないが、層間絶縁膜を形成した後、3つのタングステン電極4、104、204に至るコンタクト孔および、半導体基板1上に形成した集積回路のコンタクト孔、を形成し、続いて金属膜を堆積してこれをパターニングして配線とし、半導体装置を完成した。

#### 【0047】

本実施の半導体装置は、単純な構造ゆえ小面積でありなおかつ不揮発のスイッチである。従来のCMOSを用いた大面積かつ揮発性のスイッチと比較して、製造コスト、機能の両面で上回ることができた。

50

## &lt; 実施例 7 &gt;

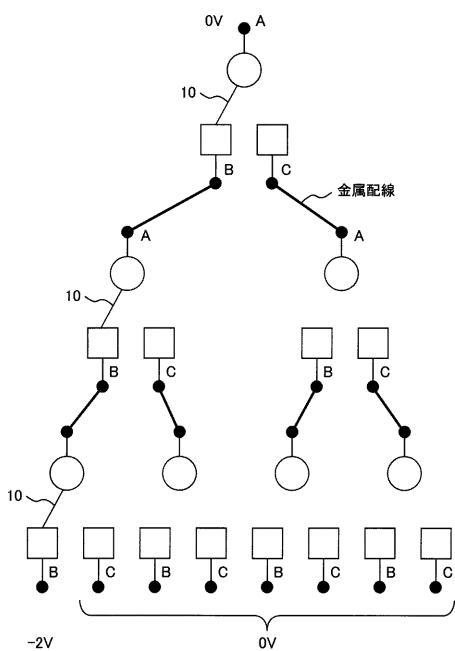

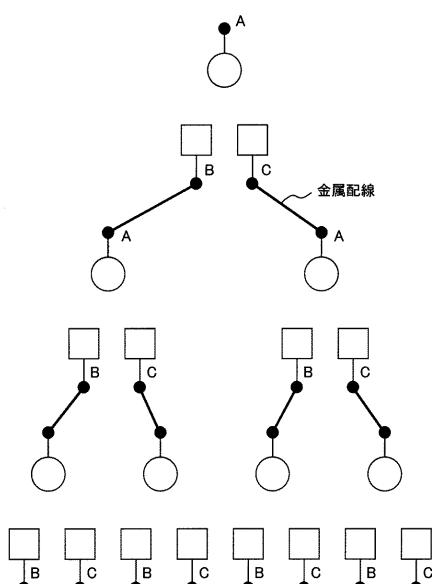

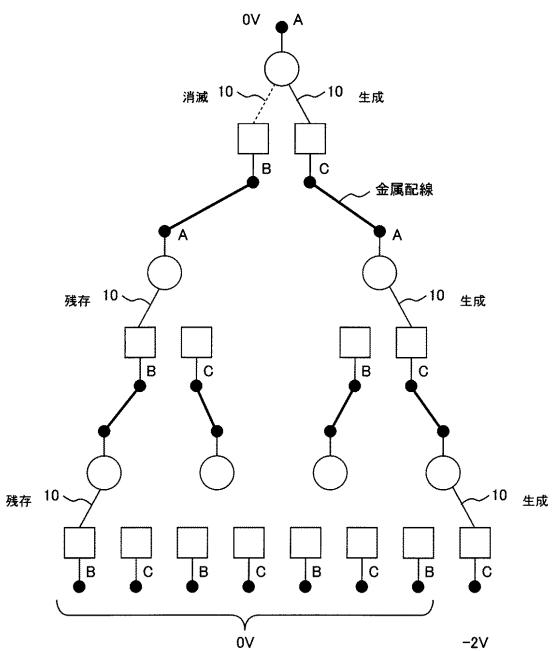

実施例 1 から 6 のような半導体装置は、記号的には図 3 6 ( a ) のように書ける。導電バス生成時（スイッチオン動作時）の陽極を 、陰極を で表している。図 3 6 ( b ) は電極 A - C 間のスイッチオン動作、図 3 6 ( c ) は、電極 A - C 間の導電バスを電極 A - B 間に切替える動作を表している。この半導体装置を複数個使用して、図 3 7 のように半導体装置の導電バス生成時の陽極と他の半導体装置の導電バス生成時の陰極を金属配線で接続しアレイを構成することができる。

## 【 0 0 4 8 】

図 3 8 のように、半導体装置の 1 つの電極に例えば - 2V を印加すると、導電バスが複数の半導体装置内で形成され長距離の導電バスが同時生成できる。また、図 3 8 で導電バスが生成された状態で、図 3 9 のように別の電極に例えば - 2V を印加すると、新しく導電バスが生成されるのと同時に、導電バスが消滅する箇所ができ長距離の導電バス全体の切り替えができる。

本実施例の半導体装置は、多段のロジックのスイッチ切り替えを瞬時に行なうのに適した半導体装置であった。

## &lt; 実施例 8 &gt;

固体電解質膜中を Cu 、 Ag などの金属が移動し、これら Cu や Ag のフィラメントを生成 / 消滅させることによるスイッチング現象は、大脳新皮質で見られる神経細胞どうしのシナプス結合の生成 / 消滅に類似している。シナプス結合は、神経細胞の興奮状態（電位パルス発振状態）を接続先の神経細胞に伝えるが、興奮状態の伝達に使用される頻度に応じて接続が強化されたり弱まったりする。この接続の強度の変化が、学習に対応していると考えられる。実施例 1 から 6 のようなスイッチングデバイスを相互に接続して神経細胞どうしのシナプス結合を模倣することが可能である。

## 【 0 0 4 9 】

神経細胞は複数（数千～数万）のシナプスが 1 つの神経細胞に接続されているという意味で多入力である。また興奮状態を他の神経細胞に伝える軸索は 1 つの神経細胞あたり 1 本だけ存在するが、途中で多数の分岐をし、分岐先の先端で他の神経細胞にシナプス接続している意味で多出力である。

## 【 0 0 5 0 】

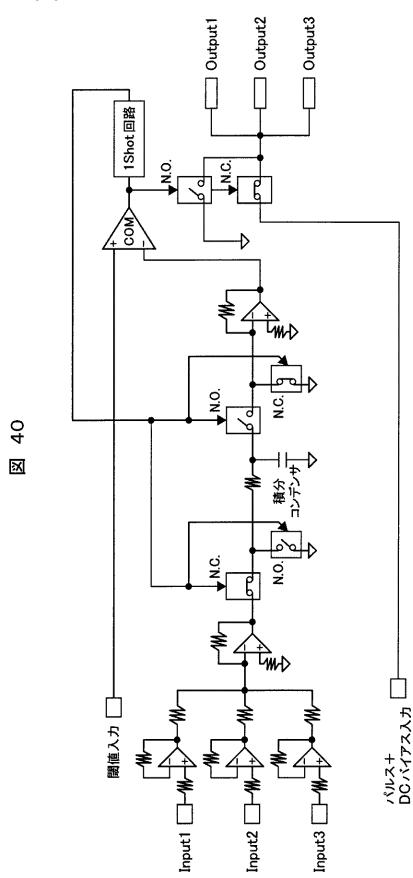

パルス電圧の多入力と多出力を模倣するための回路は、例えば図 4 0 のように組むことができる。図 4 0 は神経細胞 1 つに対応していて、入力 1 、 2 、 3 には他の神経細胞を模倣した回路からのパルス電圧が入力される。

## 【 0 0 5 1 】

このセル回路（神経細胞対応回路）は、複数の入力を積分するブロック（積分コンデンサーの付近）、神経細胞の種類や機能などに対応する閾値を外部から与えることができるコンパレータ回路ブロック（「閾値入力」が入っている付近）、パルス発生器からのパルス波形と、領域の神経細胞の興奮度を外部から上げ下げする広い意味の神経伝達物質の実効的総量に対応する DC バイアスとの和を入力する回路ブロック（「神経伝達物質対応入力」が入っている付近）、入力の積分値を出力パルス列の持続時間に変換する回路ブロック（コンパレータ回路ブロックからの出力信号により、図の中央部でスイッチを制御している付近）、 1 shot 回路で、パルス列終了後の休み時間を決める回路、およびイオンスイッチに接続する分岐出力ブロック（Output1～3）より構成される。 1 shot 中にコンデンサーが充電され、 1 shot が終わると複数のスイッチが同期して切り替わるので、入力の積分値により電圧レベルがコンパレータレベルを瞬時に越え、積分コンデンサーが並列抵抗で放電されることにより、コンデンサーの蓄電量に対応する時間後にコンパレータレベルを下回るまで、出力側に接続されるイオンスイッチに安定なイオン導電バスを形成するのに十分なパルスが出力される。

## 【 0 0 5 2 】

各 Input 、 Output にオペアンプが 1 つずつ入れてあるが、これらはインピーダンスをマッチングさせるためのもので、それ以外の回路であらかじめ考慮しておけば必

10

20

30

40

50

要ない。入力、出力側のオペアンプを除去して考えると、出力の分岐のいくつかが既にイオンスイッチによって他の神経細胞回路に接続されている場合、接続先の神経細胞回路の入力側は高い電圧レベルにホールドされているので、そちらに電流が流れることがなく、未接続の神経細胞に向かって電流が流れてイオン接続が形成される。セル回路間の接続を、異なる処理ではできるだけ共用しないようにする点が、従来のニューラルネットワークと異なる。

#### 【0053】

このように早い者勝ちで確率的に形成されるシナップス接続であるが、有効なものは生き残り、意味のないものは徐々に切れることによって最適化が行われる。実際の神経細胞ネットワークでは、有効なものは上位階層に信号が伝わって良いものと判断されると、報酬としてそのネットワーク領域の神経伝達物質の実効的総量を増加させ、またその領域の血流量を増加させ、活性化するフィードバック機構が存在するので、シナップス接続も強化される。このフィードバック入力による活性化の役割を、上記の神経伝達物質対応回路ブロックが果たす。この役割は従来のニューラルネットワークの教師信号の役割と似ているが、正否を判定して個別のセル回路の入力に与えるのではなく、領域を活性化している点が異なる。

10

#### 【0054】

神経伝達物質対応回路ブロックに上位階層から与える報酬は、予め決められた範囲のセル回路群に与えればよく、活性化すべき実際のネットワークの範囲と多少ズレっていても、当該ネットワークの領域内のセル回路間には相互の出力伝達もあるので、正しい範囲が活性化すると考えられる。この回路ブロックへの入力波形は、電圧が上下に交互に繰り返す、近傍のセル回路用に統一されたクロックで生成されたパルス電圧と、報酬に対応するDCバイアス電圧からなる。実際の神経細胞では個々のセル回路が発火（興奮）するとパルスを出すが、電気回路では位相差によりうなりを生じて強い雑音を発生したり不安定になったりするおそれがあるのでこのようにした。

20

#### 【0055】

最初のイオン接続形成時は、DCバイアス電圧はほとんど0であるため、シナップス対応部分にイオン導電パスを形成しようとするプラス電圧とマイナス電圧が交互に作用するが、電極の形状および材質の非対称から、プラス電圧の時にはインパクトイオン化でキャリアが増倍されることによる電流が相対的に多く流れ、それをきっかけに弱いながらも、イオン導電パスが形成され、保持される。好ましい論理処理ができるネットワークができたらには報酬DCバイアス電圧が加わることにより、イオン導電パスが強化される。シナップス接続の強化に対応する。DCバイアス電圧は、既に存在するイオン接続を強化するが、新たに生成することはない程度の値とする。

30

#### 【0056】

一方、コンパレータ回路ブロックは、コンパレータレベルの上がり下がりによって、複数の入力の1つで興奮状態になり出力を出すか、複数で興奮状態になり出力を出すか、すなわち、デジタル論理回路のORやANDに近い処理をすることもできる。出力を出さないセル回路が存在することは、セル回路のネットワークで処理される情報の過度の錯綜による混乱を防ぐために重要である。

40

図の回路では実際の神経細胞より1桁以上早い動作が可能であることを確認した。この実験では神経伝達物質対応のDCバイアス電圧としてはマイナスの電圧を印加した。

#### 【0057】

この回路の出力波形は、神経細胞のバースト（例えば、非特許文献5参照）と呼ばれる一定時間パルス列を出す興奮状態に対応している。コンパレータ入力は一定でも良いが、繰り返し矩形波を入力してもよい。実際の神経細胞の出力波形は正方向に大きく、負方向に小さい、というよう正負非対称であるが、試作回路の出力波形は基本的に神経伝達物質対応ブロックに入れるパルス波形に依存するため、神経細胞が興奮時に発するパルス電圧波形に合わせることが可能である。例えばバースト出力だけを出すような神経細胞を模擬する場合、多少出力信号は変化するがInputからの入力以外の2つの入力信号は1

50

本化してもよい。

#### 【0058】

入力パルスのタイミング差を重視する従来のセル回路 S T D P (シナプス タイミングディレイ パルス回路) の例が(例えは、非特許文献 4 あるいは非特許文献 6 を参照]に述べられている。本報告の場合、バーストを構成する個々のパルスは、所定の範囲、例えは大脳新皮質の微細柱状構造であるコラムに相当する領域のセル回路には同じパルス発振回路からパルスが与えられるのでほとんど同期する。しかし、バーストの始まりと終わりはセル回路毎に異なる。従って、バーストの位相の同期が意味を持つことにより、前頭前野の神経細胞への複数入力の位相同期による総合判断なども模擬することができると考えられる。

10

#### 【0059】

次にシナプス対応部分との接続について述べる。

固体電解質中の金属イオンの電界移動のパターンには、少なくとも 2 つのパターンがある。

1つは固体電解質中で金属のプラスイオンが動きやすい、すなわちモビリティーが高い場合である。この場合、金属イオン濃度が高い導電パスが最初は形成されず、対電極、すなわち陰極に金属イオンが大量に堆積すると、そのピークが陽極まで達し、導電パスとなる。もう 1 つは金属のプラスイオンが動きにくい場合である。

#### 【0060】

この場合、金属イオンは膜のうち相対的に隙間の多い場所に押し込まれ、フィラメント状の導電パスを形成する。後者が、シナプス接続の模擬には適していると考えられる。イオンスイッチアレーでは、対電極を 2 つ持ち、相互に電界がオーバーラップしているので、1 つの対電極への接続、続いてもう 1 つの対電極への接続時に横電界による元の接続の切断、という動作ができる。これら対電極には、別々のセル回路の出力が接続されている。対電極に対向するベース電極が、次の層のセル回路の入力に接続されている。

20

#### 【0061】

一般的には、対電極をベース電極の斜め上方の多角形の頂点に相当する位置に多数配置し、任意の 1 つまたは複数の電極とイオン導電パスで接続し、さらには切り替えが可能であると考えられる。

#### 【0062】

本発明のセル回路は、下記の理由でイオンスイッチを動作させるのに適していると考えられる。

30

1. 電圧が正負方向に振れるバースト状のパルス列を発生するので、固体電解質中のイオンを動かして導電パスを形成しやすい。

2. 導電パスができるか切れるかは神経伝達物質対応入力の D C バイアスによって決めることが可能。

3. 入力側のオペアンプを省略すれば、注目しているセル回路と、その先の既に積分コンデンサーに電荷が蓄積されているセル回路の入力電極との間には電位差が生じないので、自動的に未使用のセル回路へのイオン接続が形成される。

#### 【0063】

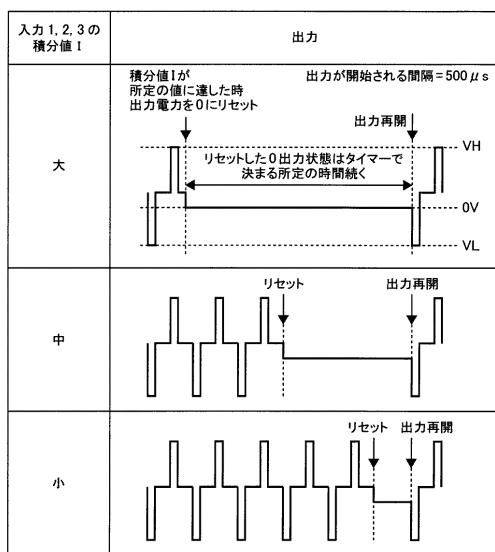

一定時間における入力パルスの積分値に応じて、回路の出力波形と固体電解質スイッチング素子への印加電圧が図 4 1 のように決める。

40

この出力パルスが同様に組まれた次の回路の入力となる。複数の回路を互いに接続させた回路を動作させると、各回路の固体電解質スイッチング素子の抵抗を変化させることができる。抵抗の変化は、固体電解質膜中に形成される金属フィラメントの太さに依存する。この抵抗の変化を学習とみなすことができる。

このような回路どうしの接続を大規模化することで、人の大脳新皮質のもつ優れた機能を半導体で実現できる可能性がある。

#### 【産業上の利用可能性】

#### 【0064】

50

本発明の半導体装置は、ロジックデバイスのスイッチ部分全般に用いて好適のものである。また、将来的には、脳機能を実現する半導体装置に用いて好適のものである。

【図面の簡単な説明】

【0065】

【図1】本発明の実施例1と実施例2である半導体装置の一例を示した一部平面図である。

【図2】本発明の実施例1である半導体装置の一例を示した一部断面図(図1のA-A線断面)である。

【図3】本発明の実施例1である半導体装置のスイッチオフ状態を示した一部断面図(図1のA-A線断面)である。

【図4】(a)と(b)は、本発明の実施例1である半導体装置のスイッチオン動作を示した一部断面図(図1のA-A線断面)である。

【図5】(a)と(b)は、本発明の実施例1である半導体装置のスイッチオフ動作を示した一部断面図(図1のA-A線断面)である。

【図6】(a)は、本発明の実施例1である半導体装置でElectrode1-Electrode3間がオン、Electrode1-Electrode2間がオフの状態を示した一部断面図(図1のA-A線断面)であり、(b)は、本発明の実施例1である半導体装置の接続切り替え動作を示した一部断面図(図1のA-A線断面)である。

【図7】(a)～(c)は、実施例1の半導体装置の製造方法の一例を示した断面図である。

【図8】(a)は、実施例1の半導体装置の製造方法の一例を示した平面図であり、(b)は、実施例1の半導体装置の製造方法の一例を示した断面図である。

【図9】(a)～(c)は、実施例1の半導体装置の製造方法の一例を示した断面図である。

【図10】(a)～(c)は、実施例1の半導体装置の製造方法の一例を示した断面図である。

【図11】本発明の実施例2である半導体装置の一例を示した一部断面図(図1のA-A線断面)である。

【図12】(a)は、本発明の実施例3である半導体装置の一例を示した一部平面図であり、(b)は、図12(a)のA-A線断面図である。

【図13】本発明の実施例4である半導体装置の一例を示した一部平面図である。

【図14】本発明の実施例4である半導体装置の一例を示した一部断面図である。図13におけるA-A線断面図である。

【図15】実施例4の半導体装置の製造方法の一例を示した一部断面図である。

【図16】本発明の実施例5である半導体装置の一例を示した一部平面図である。

【図17】(a)は、本発明の実施例5である半導体装置の一例を示した一部断面図(図16のA-O-C線断面)であり、(b)は、本発明の実施例5である半導体装置の一例を示した一部断面図(図16のA-O-B線断面)である。

【図18】本発明の実施例5である半導体装置のスイッチオフ状態を示した一部平面図である。

【図19】(a)と(b)は、実施例5の半導体装置の製造方法の一例を示した一部断面図である。

【図20】(a)は、実施例5の半導体装置の製造方法の一例を示した平面図であり、(b)は、実施例5の半導体装置の製造方法の一例を示した一部断面図である。図20(a)のA-C線断面図である。

【図21】(a)と(b)は、実施例5の半導体装置の製造方法の一例を示した一部断面図である。

【図22】(a)は、実施例5の半導体装置の製造方法の一例を示した平面図であり、(b)は、実施例5の半導体装置の製造方法の一例を示した一部断面図である。図22(a)のA-O-B線断面図である。

10

20

30

40

50

【図23】(a)と(b)は、実施例5の半導体装置の製造方法の一例を示した一部断面図である。

【図24】(a)と(b)は、実施例5の半導体装置の製造方法の一例を示した一部断面図である。

【図25】本発明の実施例6である半導体装置の一例を示した一部平面図である。

【図26】本発明の実施例6である半導体装置の一例を示した一部断面図である。図25におけるA-A線断面図である。

【図27】本発明の実施例6である半導体装置のスイッチオフ状態を示した一部平面図である。

【図28】(a)と(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。

【図29】(a)は、実施例6の半導体装置の製造方法の一例を示した平面図であり、(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。図29(a)におけるB-B線断面図である。

【図30】(a)と(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。

【図31】実施例6の半導体装置の製造方法の一例を示した一部平面図である。

【図32】(a)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。図31のA-A線断面図であり、(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。図31のB-B線断面図である。

【図33】(a)と(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。

【図34】(a)と(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。

【図35】(a)と(b)は、実施例6の半導体装置の製造方法の一例を示した一部断面図である。

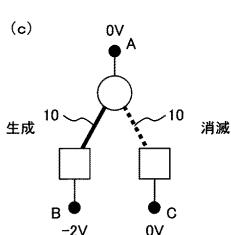

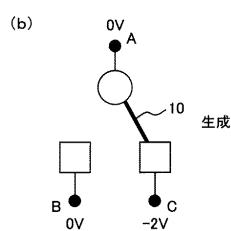

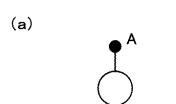

【図36】(a)は、実施例7の半導体装置のアレイを構成する半導体装置を記号化して表したものの一例であり、(b)は、実施例7の半導体装置のアレイを構成する半導体装置の電極A-電極C間のスイッチオン動作を表したものであり、(c)は、実施例7の半導体装置のアレイを構成する半導体装置の電極A-電極C間の導電パスを電極A-電極B間に切替える動作を表したものである。

【図37】実施例7の半導体装置のアレイ構成の一例である。

【図38】実施例7の半導体装置の導電パス切り替え動作の一例である。

【図39】実施例7の半導体装置の導電パス切り替え動作の一例である。

【図40】神経細胞を模倣したC E L L回路図である。

【図41】図40の回路の入出力関係を示した図である。

#### 【符号の説明】

#### 【0066】

1...半導体基板(シリコン基板)、

2...固体電解質膜、

3...銅、銀などの拡散しやすい原子を含む電極、

4、4a、4b、4c、4d、104、204...タンゲステン、白金などの不活性金属材料で形成された電極、

8...銅、銀などの拡散しやすい原子を固体電解質膜2よりも高濃度に含み低抵抗率の固体電解質膜、

10...金属でできた導電パス、

11、12、13、14...絶縁膜、

20...レジスト、

T r e n c h...溝、

E l e c t r o d e 1...電極、

10

20

30

40

50

Electrode 2 ... 電極、

Electrode 3 ... 電極、

Electrode 4 ... 電極、

Electrode 5 ... 電極。

【図1】

図1

【図3】

図3

【図2】

図2

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

(c)

【図 1 2】

図 12

A-A断面

【図 1 3】

図 13

【図 1 4】

図 14

A-A断面

【図 1 5】

図 15

【図 1 6】

図 16

【図 1 7】

図 17

(a)

A-O-C断面

(b)

A-O-B断面

【図 18】

図 18

【図 19】

図 19

【図 21】

図 21

【図 20】

図 20

【図 22】

図 22

【図23】

図23

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

図27

【図 28】

図 28

【図 29】

図 29

【図 30】

図 30

【図 31】

図 31

(b)

B-B断面

【図32】

図32

(a)

A-A断面

(b)

B-B断面

【図33】

図33

(a)

A-A断面

(b)

A-A断面

【図34】

図34

(a)

(b)

【図35】

図35

(a)

(b)

【図 3 6】

図 36

【図 3 8】

図 38

【図 3 7】

図 37

【図 3 9】

図 39

【図 40】

図 40

【図 41】

図 41

---

フロントページの続き

(72)発明者 藤崎 芳久

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

(72)発明者 児玉 征之

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

(72)発明者 荒澤 伸幸

東京都国分寺市東恋ヶ窪一丁目 280 番地 株式会社日立製作所中央研究所内

F ターム(参考) 5F038 CD16 DF01 DF05 DF17 EZ15 EZ20

5F083 FZ10 GA09 JA37 JA39 JA40 PR40