(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5658128号

(P5658128)

(45) 発行日 平成27年1月21日(2015.1.21)

(24) 登録日 平成26年12月5日(2014.12.5)

(51) Int.Cl.

F 1

G06F 12/16 (2006.01)

G06F 12/16 320G

G06F 11/10 (2006.01)

G06F 11/10 330K

G06F 12/16 320H

請求項の数 19 (全 20 頁)

(21) 出願番号 特願2011-256126 (P2011-256126)

(22) 出願日 平成23年11月24日 (2011.11.24)

(65) 公開番号 特開2012-118979 (P2012-118979A)

(43) 公開日 平成24年6月21日 (2012.6.21)

審査請求日 平成26年5月28日 (2014.5.28)

(31) 優先権主張番号 12/960004

(32) 優先日 平成22年12月3日 (2010.12.3)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 NANDフラッシュ・メモリにおける確率論的多層エラー訂正のためのシステム、方法、およびコンピュータ・プログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリからデータを検索するためのシステムであって、

メモリと通信するデコーダであって、

前記メモリにおけるページ上に記憶されたコードワードを受信することであって、前記コードワードが、データおよび前記データに応じて発生された第1の層のチェック・シンボルを含む、前記受信することと、

前記コードワードが、前記第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することと、

前記判定に応じて、

第2の層のチェック・シンボルを受信することであって、前記第2の層のチェック・シンボルが、前記データに応じて、更に前記コードワードを含む前記ページよりも前に書き込まれた前記メモリにおける他のページの内容に応じて発生される、前記受信することと、

前記第2の層のチェック・シンボルに応じて前記コードワードを訂正することと、

前記訂正したコードワードを出力することと

を含む方法を実行するための前記デコーダ

を備えている、前記システム。

## 【請求項 2】

前記コードワードを訂正することが更に統計的エラー・モデルに応じて行われる、請求

10

20

項 1 に記載のシステム。

【請求項 3】

前記統計的エラー・モデルが前記判定に応じて変更される、請求項 2 に記載のシステム。

。

【請求項 4】

前記コードワードを訂正することが更に各セルごとの集合エラー重みベクトルに応じて行われ、前記ベクトルが、前記セルについてのビット・ライン・ディスター・バンス・エラー重みベクトル、前記セルについての浮動ゲート結合エラー重みベクトル、および前記セルについての多数のページ・プログラムから導出されたエラー重みベクトルの少なくとも 1 つから計算される、請求項 1 に記載のシステム。

10

【請求項 5】

前記セルについて前記エラー重みベクトルを計算することが更に、前記セルの指定された近隣領域内のセルの内容に応じて行われる、請求項 4 に記載のシステム。

【請求項 6】

前記統計的エラー・モデルが、前記コードワードおよび前記第 2 の層のチェック・シンボルを用いて前記コードワードを訂正するためにメッセージ伝達アルゴリズムによって用いられる、請求項 2 に記載のシステム。

【請求項 7】

前記メモリがマルチ・レベル・セル (MLC) NAND フラッシュ・メモリであり、前記コードワードの前記訂正が更に、2 次元データ・パターンに対応したエラー重みを含むルックアップ・テーブル・セットに応じて行われる、請求項 1 に記載のシステム。

20

【請求項 8】

前記方法が、

前記コードワードが、前記第 1 の層のチェック・シンボルを用いて訂正することができないエラーを含まないと判定し、これに応じて、前記コードワードおよび前記第 1 の層のチェック・シンボルに応じて前記コードワードを訂正すること

を更に含む、請求項 1 に記載のシステム。

【請求項 9】

前記第 2 の層のチェック・シンボルの少なくとも 1 つのサブセットが第 2 のメモリに記憶されている、請求項 1 に記載のシステム。

30

【請求項 10】

メモリからデータを検索するための、コンピュータにより実施される方法であって、コンピュータが、

前記メモリにおけるページ上に記憶されたコードワードを受信するステップであって、前記コードワードが、データおよび前記データに応じて発生された第 1 の層のチェック・シンボルを含む、前記受信するステップと、

前記コードワードが、前記第 1 の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定するステップと、

前記判定に応じて、

第 2 の層のチェック・シンボルを受信するステップであって、前記第 2 の層のチェック・シンボルが、前記データに応じて、更に前記コードワードを含む前記ページよりも前に書き込まれた前記メモリにおける他のページの内容に応じて発生される、当該受信するステップと、

40

前記第 2 の層のチェック・シンボルに応じて前記コードワードを訂正するステップと、

前記訂正したコードワードを出力するステップと

を実行することを含む、前記方法。

【請求項 11】

前記メモリがマルチ・レベル・セル (MLC) NAND フラッシュ・メモリであり、前記コードワードの前記訂正が更に、2 次元データ・パターンに対応したエラー重みを含む

50

ルックアップ・テーブル・セットに応じて行われる、請求項 10 に記載の方法。

【請求項 12】

前記コンピュータが、

前記コードワードが前記第 1 の層のチェック・シンボルを用いて訂正することができないエラーを含まないと判定し、これに応じて、前記コードワードおよび前記第 1 の層のチェック・シンボルに応じて前記コードワードを訂正するステップを実行することをさらに含む、請求項 10 に記載の方法。

【請求項 13】

メモリからデータを検索するためのコンピュータ・プログラムであって、コンピュータに、請求項 10 ~ 12 のいずれか一項に記載の方法の各ステップを実行させる前記コンピュータ・プログラム。

10

【請求項 14】

システムであって、

メモリおよびエラー訂正キャッシュと通信するエンコーダであって、

データおよび前記メモリにおけるページの書き込みアドレスを受信することであって、前記メモリが前記ページおよび以前に書き込んだページを含む、当該受信することと、データに応じて第 1 の層のチェック・シンボルを発生することと、

前記データおよび前記以前に書き込んだページの少なくとも 1 つの内容に応じて第 2 の層のチェック・シンボルを発生することと、

前記第 1 の層のチェック・シンボルおよび前記データをコードワードとして前記ページに記憶することと、

20

前記データおよび前記第 2 の層のチェック・シンボルを前記エラー訂正キャッシュに記憶することと

を含む方法を実行するための前記エンコーダを備えている、前記システム。

【請求項 15】

前記メモリおよび前記エラー訂正キャッシュと通信するデコーダであって、

前記コードワードおよび前記第 2 の層のチェック・シンボルを受信することと、

前記コードワードが、前記第 1 の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することと、

前記第 2 の層のチェック・シンボルに応じて前記コードワードを訂正することと

30

を含む方法を実行するための前記デコーダを更に備えている、請求項 14 に記載のシステム。

【請求項 16】

前記第 2 の層のチェック・シンボルを発生させることが更に低密度パリティ・チェック (L D P C) ・コードに応じて行われる、請求項 14 に記載のシステム。

【請求項 17】

前記第 2 の層のチェック・シンボルを発生させることが、プログラム可能な数の以前に書き込んだページの内容に応じて行われる、請求項 14 に記載のシステム。

【請求項 18】

前記メモリが N A N D フラッシュ・メモリであり、前記第 2 の層のチェック・シンボルを発生させることが、現在書き込んでいるページと同じブロック内のプログラム可能な数の以前に書き込んだページに応じて行われ、これらの以前に書き込んだページからのデータが前記エラー訂正キャッシュに記憶されている、請求項 14 に記載のシステム。

40

【請求項 19】

以前に書き込んだページの使用数が、メモリ・ブロックをプログラムした回数、前記メモリ・ブロックのシンボル・エラー・レート、および前記メモリの統計的エラー・モデルの少なくとも 1 つに応じて変更される、請求項 14 に記載のシステム。

【発明の詳細な説明】

【技術分野】

【0001】

50

本発明は、一般にコンピュータ・メモリに関し、更に具体的には N A N D ( not-and ) フラッシュ・メモリにおける確率論的多層エラー訂正に関する。

【背景技術】

【0002】

P C M ( phasechange memory : 相変化メモリ ) およびフラッシュ・メモリは、耐久性が限られた ( 「寿命が限られた」とも言う ) 不揮発性メモリの一例である。かかるメモリは、多数の書き込みサイクル ( P C M ではリセット・サイクル、フラッシュ・メモリではプログラム / 消去サイクル ) を経た後にメモリ・セルが摩耗して信頼性高く情報を記憶することができなくなるという意味で、耐久性が限られている。

【発明の概要】

10

【発明が解決しようとする課題】

【0003】

N A N D フラッシュ・メモリは、消費者向けおよび企業向けの双方の用途で不揮発性記憶媒体としてますます用いられるようになっている。最新の N A N D フラッシュ・メモリ・デバイスの 1 つの特徴は、強いデータ依存性およびデバイス依存性のエラー・モードを示すと共に、多くの場合セル間依存性を示すことである。周囲のセルのプログラミングおよび電荷レベルが、隣接セルで生じるエラー状況に対して直接的な影響を及ぼす場合がある。

【0004】

20

また、 N A N D メモリでは、プログラミング段階の間に保持エラーのために引き起こされるランダム・エラーが生じやすい場合がある。典型的なエラー作用には、背景パターン依存 ( B P D : background pattern dependency ) エラー、ビット・ライン・ディスタンス ( B L D : bit-line disturbance ) ・エラー、ページおよびプログラム・ディスタンス ( P G M : page and program disturbance ) ・エラー、および浮動ゲート結合 ( F G C : floating gate coupling ) エラーが含まれる。これらのタイプのエラー作用は、場合によっては、メモリ使用に制約を課すことによって軽減することができる。例えば、 1 メモリ・ブロックのみを順次書き込み可能と規定することによって、これらのエラーのいくつかを排除または軽減することができる。しかしながら、かかる制約は、書き込み待ち時間の延長、摩耗の増大、および書き込み増幅等の望ましくない副作用をもたらす場合がある。更に、異なるプログラム・レベルでは同一でないエラー遷移確率を有することがある。

30

【課題を解決するための手段】

【0005】

一実施形態は、メモリからデータを検索するためのシステムである。このシステムは、メモリと通信するデコーダを含む。デコーダは、メモリにおけるページ上に記憶されたコードワードを受信することを含む方法を実行するためのものであり、コードワードは、データおよびこのデータに応じて発生された第 1 の層のチェック・シンボルを含む。この方法は更に、コードワードが第 1 の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて第 2 の層のチェック・シンボルを受信する。第 2 の層のチェック・シンボルは、データの受信に応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第 2 の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

40

【0006】

別の実施形態は、メモリからデータを検索するための、コンピュータにより実施される方法である。この方法は、メモリにおけるページ上に記憶されたコードワードを受信することを含み、コードワードは、データおよびこのデータに応じて発生された第 1 の層のチェック・シンボルを含む。この方法は更に、コードワードが第 1 の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、これに応じて第 2 の層のチェック・シンボルを受信する。第 2 の層のチェック・シンボルは、データに応

50

じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生させる。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

#### 【0007】

別の実施形態は、メモリからデータを検索するためのコンピュータ・プログラムである。タンジブルな記憶媒体がこのコンピュータ・プログラムを含み、この記憶媒体は処理回路によって読み取り可能であり、方法を実行するために処理回路によって実行される命令を記憶する。この方法は、メモリにおけるページ上に記憶されたコードワードを受信することを含み、コードワードは、データおよびこのデータに応じて発生された第1の層のチェック・シンボルを含む。この方法は更に、コードワードが第1の層のチェック・シンボルを用いて訂正することができないエラーを含むと判定することを含み、この判定に応じて第2の層のチェック・シンボルを受信する。第2の層のチェック・シンボルは、データに応じて、更にコードワードを含むページよりも前に書き込まれたメモリにおける他のページの内容に応じて発生される。第2の層のチェック・シンボルに応じてコードワードを訂正する。訂正したコードワードを出力する。

10

#### 【0008】

更に別の実施形態は、メモリおよびエラー訂正キャッシュと通信するエンコーダを含むシステムである。エンコーダは、データおよびメモリにおけるページの書き込みアドレスを受信することを含む方法を実行するためのものである。メモリは、そのページおよび以前に書き込んだページを含む。データに応じて第1の層のチェック・シンボルを発生し、データおよび以前に書き込んだページの少なくとも1つの内容に応じて第2の層のチェック・シンボルを発生する。第1の層のチェック・シンボルおよびデータをコードワードとしてページに記憶する。データおよび第2の層のチェック・シンボルをエラー訂正キャッシュに記憶する。

20

#### 【0009】

本実施形態の技法によって、更に別の特徴および利点が実現される。本明細書において他の実施形態および態様が記載され、これらは特許請求する本発明の一部と見なされる。本発明をその利点および特徴と共により良く理解するために、以下の記載および図面を参照する。

#### 【0010】

30

本明細書の末尾における特許請求の範囲において、本発明と考えられる主題について特に指摘し明確に特許請求する。本発明の前述およびその他の特徴および利点は、添付図面と関連付けた以下の詳細な説明から明らかとなろう。

#### 【図面の簡単な説明】

#### 【0011】

【図1】一実施形態に従った、メモリにおいてデータを記憶し検索するためのシステムのブロック図を示す。

【図2】一実施形態に従った、メモリにおいてデータを記憶し検索するためのシステムのブロック図を示す。

【図3】一実施形態によって実施可能であるNANDフラッシュ・メモリのブロック図を示す。

40

【図4】一実施形態に従った、NANDフラッシュ・メモリおよび第2の層の符号化モジュールのブロック図を示す。

【図5】一実施形態に従った、第2の層のエラー訂正コード訂正計算機構を示す。

【図6】一実施形態に従った、NANDフラッシュ・メモリおよび第2の層の復号モジュールのブロック図を示す。

【図7】一実施形態に従った、マルチ・レベル・セル(MLC)NANDフラッシュ・セルに4レベルの情報を記憶するために用いる閾値電圧を示す。

【図8】一実施形態に従った、MLC NANDフラッシュの2次元(2D)データ・パターンに対応した重みを含むルックアップ・テーブルを示す。

50

【図9】一実施形態に従った、第2の層のエラー訂正を用いた訂正エラーのためのプロセス・フローを示す。

【発明を実施するための形態】

【0012】

一実施形態は、例えば時間履歴、周囲のビット・パターン、およびかかる周囲のビット・パターンと背景パターン依存(BPD)エラー、ビット・ライン・ディスター・バンス(BLD)・エラー、ページおよびプログラム・ディスター・バンス(PGM)・エラー、浮動ゲート結合(FGC)エラーとの間の関係に基づいて、異なるメモリ・セルについて異なるエラー重みを計算するエラー訂正技法を用いることにより、NANDフラッシュ・メモリの信頼性を向上させることを対象とする。

10

【0013】

一実施形態が含む多層エラー訂正システムにおいては、後の層の復号プロセスは、所与のセルに記憶されたデータに対してメモリ・セル近隣領域の時間履歴および二次元(2D)データ/ビット・パターンが及ぼす影響についての統計的知識を利用する。従って、読み取りレベルおよび近隣ビット・パターンに基づいて、異なるメモリ・セル位置に異なるエラー重みを割り当てる。これらのエラー重みに取り入れられた概念とは、セル位置では多かれ少なかれ誘発エラーが生じる可能性があるというものであり、多かれ少なかれ、プログラムされた値および近隣セル位置に記憶された値に基づいて、ある一定のタイプの誘発エラーが生じる可能性があるというものである(この場合エラーのタイプはエラー発生前後のセルの値によって規定される)。

20

【0014】

本明細書に記載する実施形態は、これまでの解決策よりも優れたいいくつかの利点を提供する。第1に、実施形態は、一般的なエラー訂正コードを用いるのではなく特定のエラーの作用をモデル化し、これによって実施形態は信頼性を高める。第2に、実施形態はデバイス回路を変更する必要がないので、いかなるNANDフラッシュ・デバイスであっても実際に容易に用いることができる。更に、実施形態は、回路レベルの改良のみによって可能であるよりもいっそう信頼性を高めるために、回路レベルの改良と組み合わせて用いることができる。更に、時間履歴を用いてエラー重みを更新することによって、本明細書に記載する実施形態は特定のNANDデバイスの特徴に適合する。更に、実施形態は、従来のエラー・コードと共に用いて、従来のコードに障害が発生した場合にのみ呼び出すようにすることができる。これによって、読み取り待ち時間を過度に延長させずに実施形態を使用可能であることを保証する。

30

【0015】

一実施形態では2層エラー訂正コード(ECC)を用いる。一実施形態において、第1の層のECCは、代数ECCを含むアルゴリズムを用いて発生させ、そのパリティ・ビット/シンボルはフラッシュ・メモリのページ・スペア・エリアに記憶されている。第2の層のECCを発生させ、そのパリティ・ビット/シンボルは部分的にフラッシュ・メモリのページ・スペア・エリアに記憶され、部分的に別の不揮発性メモリ領域(例えばフラッシュ・メモリ、ハード・ディスク)等の二次メモリ構造に記憶されている。一実施形態では、第2の層のECCパリティ・シンボルを計算するために、前の数ページにおいてプログラムされアクセスのためにキャッシュされたデータを用いる第2の層のECCエンコーダと共に、ログベース・ファイル構造のフラッシュ・メモリ・デバイスを用いる。

40

【0016】

本明細書において用いる場合、「ビット」という言葉は、従来0および1のセットからの2文字の値を取る二進数のことである。本明細書において用いる場合、「シンボル」という言葉は、ビットよりも大きい数の値を取ることができるものを指す。すなわち、可能性としては3つ以上の有限の文字の値を取るもののことである。このため、1つのシンボルは、文字(0、1、2、3)から可能な4つの値を取り得る。

【0017】

一実施形態においては、復号の際、フラッシュ・メモリから読み取ったデータを最初に

50

待ち時間の短い従来の第1の層のECCデコーダに入力する。第1の層のECCデコーダによってこのデータを訂正可能である場合は、訂正済みのデータを出力する。第1の層のECCデコーダによってこのデータを訂正することができない場合、これを第2の層のECCモジュールに入力し、第2の層のECCモジュールが2Dブロック・ビット・パターンを読み取ってこれを用いていっそう洗練されたエラー訂正分析を実行する。一実施形態では、これは、各セル位置がエラーを有する可能性がどの程度であるか、およびそのセル位置について各エラー・タイプの可能性がどの程度であるかに基づいて、様々なセル位置についてエラー重みベクトルを計算することを伴う。エラー重み値という言葉は、エラーを含まない、所与のタイプのエラーの可能性を示す従来の確率値を示す。重みまたは条件確率値は、重みまたは確率モデルに従って割り当てられ、これはエラー訂正モジュールが検出したエラーに基づいて更新される。

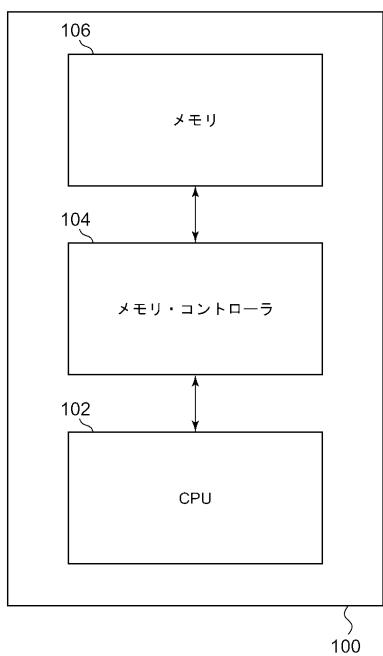

## 【0018】

図1は、一実施形態に従った、メモリにおいてデータを記憶および検索するためのシステムのブロック図を示す。図1に示したシステム100は、コンピュータ・プロセッサ102と、メモリ・セルを有するメモリ106と、メモリ106に記憶するデータをコンピュータ・プロセッサ102から受信するためのメモリ・コントローラ104と、を含む。一実施形態では、メモリ・セルはページ内に配列され、ページはブロック内に配列されている。このため、1ブロックは複数のページを含み、各ページは複数のメモリ・セルを含む。

## 【0019】

一実施形態において、メモリ・コントローラ104は、コンピュータ・プロセッサ102と通信可能に結合され、コンピュータ・プロセッサ102から書き込み要求を受信する。書き込み要求は、メモリ106に書き込まれるデータと、データを書き込むメモリ106内の位置を識別するための論理アドレスと、を含む。メモリ・コントローラ104は、メモリ106内の物理アドレスにデータを記憶する。一実施形態では、メモリ・コントローラ104は、データを記憶または検索する場合、論理アドレスをメモリ106内の物理アドレスにマッピングする。メモリ106内のデータが修正されるたびに、所与の論理アドレスに対する物理アドレスを変更することができる。

## 【0020】

システム100は、本明細書に記載する処理を実行するために利用可能なコンフィギュレーションの一例である。システム100は、単一のメモリ106、メモリ・コントローラ104、およびコンピュータ・プロセッサ102によって図示しているが、他の実施形態は、2つ以上のメモリ106、メモリ・コントローラ104、またはコンピュータ・プロセッサ102を有する他のシステムにおいても動作することは理解されよう。一実施形態では、メモリ106、メモリ・コントローラ104、およびコンピュータ・プロセッサ102は、同一のコンピュータ内に位置しない。例えば、メモリ106およびメモリ・コントローラ104は1つの物理位置（例えばメモリ・モジュール上）に位置することができ、コンピュータ・プロセッサ102は別の物理位置に位置する（例えばコンピュータ・プロセッサ102はネットワークを介してメモリ・コントローラ104にアクセスする）。更に、本明細書に記載した処理の部分は、1つ以上のメモリ106、メモリ・コントローラ104、およびコンピュータ・プロセッサ102にまたがる場合がある。

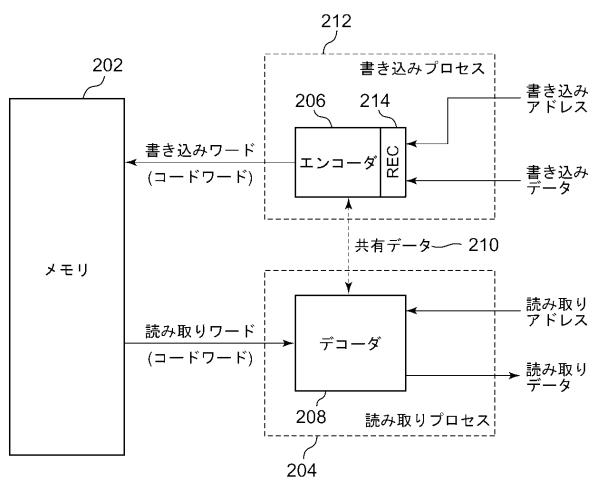

## 【0021】

図2は、一実施形態に従った、メモリにおいてデータを記憶し検索するためのシステムのブロック図を示す。図2に示すシステムは、メモリ・セルのブロック（各ブロックは複数のページから成る）を有するメモリ202（メモリ106等）と、書き込みデータを受信し、メモリ・セルに記憶するためのECC書き込みワードを発生するためのエンコーダ206と、メモリから読み取りワードを受信し読み取りデータを発生するためのデコーダ208と、エンコーダ206およびデコーダ208の双方によって用いるための記憶データの特徴を記憶する共有データ210と、を含む。一実施形態では、エンコーダ206および共有データ210は書き込みプロセス212によって用いられ、デコーダ208およ

10

20

30

40

50

び共有データ210は読み取りプロセス204によって用いられる。

【0022】

一実施形態において、エンコーダ206、デコーダ208、および共有データ210は、メモリ・コントローラ（メモリ・コントローラ104等）またはメモリ・モジュール上に位置している。代替的な実施形態では、エンコーダ206、デコーダ208、および共有データ210は、メモリ・デバイス上に位置している。共有データ210は、レジスタまたは、エンコーダ206およびデコーダ208の双方によってアクセス可能である他のいずれかの記憶位置に記憶することができる。

【0023】

一実施形態において、メモリ202は、NANDフラッシュ・メモリ・デバイスまたは、限定ではないがPCMデバイス等の他の不揮発性メモリ・デバイスによって実施される。一実施形態では、メモリ202は、シングル・レベル・セルNANDフラッシュ・メモリ・デバイスによって実施される。別の実施形態では、メモリ202は、マルチ・レベル・セルNANDフラッシュ・メモリ・デバイスによって実施される。

10

【0024】

図2に示したエンコーダ206に対する入力は、書き込まれるページのアドレス（本明細書では「書き込みアドレス」とも称する）と、ページに書き込まれるデータ（本明細書では「書き込みデータ」とも称する）と、を含む。図2に示すように、入力は、エンコーダ206上に位置する受信器204を介して受信される。一実施形態では、入力は、受信器（例えばメモリ・デバイス、メモリ・モジュール、メモリ・コントローラ、または他の位置に位置する）を介して受信される。受信器は、入力を受信するためのハードウェア、または入力が位置する記憶位置（例えばレジスタ）、あるいはその両方を含む様々な方法で実施することができる。

20

【0025】

図2に示すデコーダ208に対する入力は、読み取られるメモリ位置（例えばページ）のアドレスを含む。一実施形態では、入力は、受信器214（例えばメモリ・デバイス、メモリ・モジュール、メモリ・コントローラ、または他の位置に位置する）を介して受信される。受信器は、入力を受信するためのハードウェア、または入力が位置する記憶位置（例えばレジスタ）、あるいはその両方を含む様々な方法で実施することができる。

30

【0026】

図2に示したデコーダ208からの出力は読み取りデータを含む。一実施形態では、出力は、送信器（例えばメモリ・デバイス、メモリ・モジュール、メモリ・コントローラ、または他の位置に位置する）によって行われる。送信器（図示せず）は、出力を送信するためのハードウェア、および出力が記憶されている記憶位置またはレジスタを含む様々な方法で実施することができる。エンコーダ206およびデコーダ208は、本明細書に記載した処理を実行するために利用可能なコンピュータの一例である。

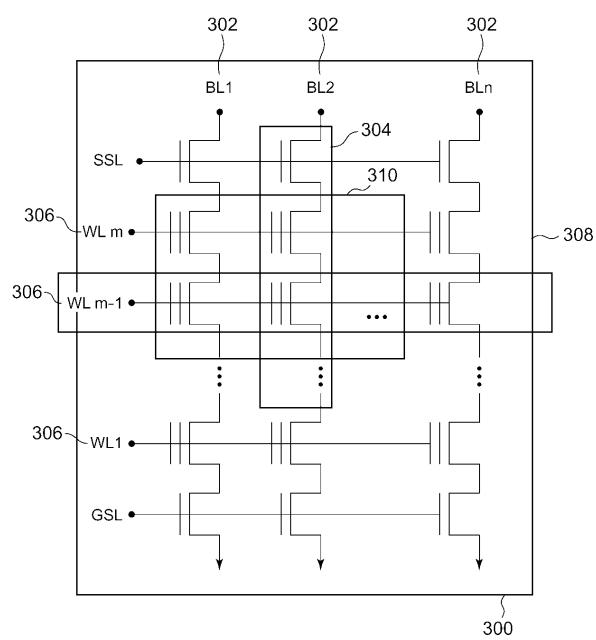

【0027】

図3は、一実施形態に従った、図1のメモリ106または図2のメモリ202等のNANDフラッシュ・メモリのブロック図を示す。図3に示すNANDフラッシュ・メモリ300は、ワード・ライン306およびビット・ライン302に配列された複数のメモリ・セルを含む。一実施形態では、1ページは、1ワード・ライン306におけるメモリ・セル内の複数のビットから成る。マルチ・レベル・セル（MLC）・デバイスを含む実施形態では、各ページは1行分のセルからの所与のビットプレーンから成る。例えば、あるページは1行分のセルの最下位ビットを含むことができ、別のページは1行分のセルの最上位ビットを含むことができる。

40

【0028】

一実施形態において、物理ブロック・アドレスと論理ブロック・アドレスとの間のマッピングは、メモリ・コントローラ104等のコントローラに維持されている。書き込み用の論理アドレスおよびデータが与えられると、コントローラは、データを書き込むための消去済み物理ページを選択し、論理・物理マッピングを記録する。一実施形態では、ログ

50

ベースのファイル・システムを用いる。この場合、物理ページは、最後の論理ページが書き込まれたブロック内の次の消去済みページであり、ページは、例えばG S L (global select line: グローバル選択ライン)に対する近接に基づいて順序付けされる。

#### 【0029】

NANDフラッシュ・メモリは、多数のファクターに基づいてデータ依存性およびデバイス依存性のエラーを示す。これらのエラーには、例えば、BPDエラー、BLD、FGCエラー、PGMエラー、ならびに他の非均一エラーおよびエラー遷移が含まれる。エラーは、NANDフラッシュに記憶されたデータおよびメモリ・セル相互の位置に基づいて発生する。一実施形態では、例えば図3のセル・ブロック310等の他の近隣セルをプログラムした場合、図3のターゲットのメモリ・ページ308はFGCによって影響を受ける場合がある。同様に、例えば304のセルのようなビット・ライン302の1つに沿ったセルに書き込んだ場合、ターゲットのメモリ・ページ308はBLD/BPDによって影響を受ける可能性がある。更に、ページを再プログラムした場合または隣接メモリ・ページに書き込んだ場合、ターゲットのメモリ・ページはPGMエラーによって影響を受ける可能性がある。更に、NANDフラッシュ・メモリ300の劣化によるシンボルのランダム・スイッチング等のエラーが更に別のエラーを引き起こす場合があり、それらのタイプは非均一である傾向がある（すなわち、デバイスに応じて、あるタイプのエラーが他のタイプのエラーよりも発生の可能性が高いことがある）。これらのタイプのエラーは全て統計的にモデル化して、予測エラー検出および訂正を行うことができる。例えば、MLC

NANDブロックにおいて非均一エラーが引き起こす「01」から「10」への誤ったビット遷移は、「10」から「01」よりも可能性がはるかに高いという知識を用いて、メモリ300のターゲット・ページにおけるエラーからいっそう正確に復旧することができる。

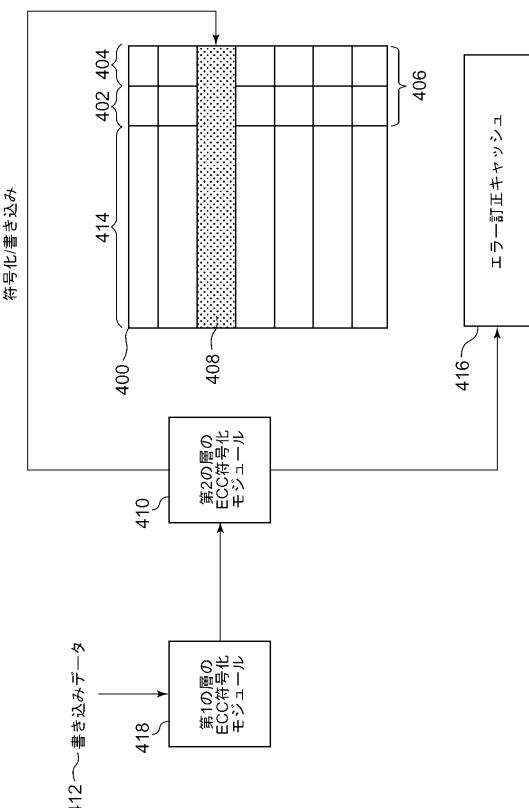

#### 【0030】

図4は、一実施形態に従った、2層ECCプロセスを用いてデータを記憶するためのフラッシュ・メモリ400を図示する。一実施形態では、フラッシュ・メモリ400はNANDフラッシュ・メモリであり、第1の層のECC符号化モジュール418および第2の層のECC符号化モジュール410は、図2に示したような書き込みプロセス212の間にエンコーダ206によって実施される。

#### 【0031】

図4に示したフラッシュ・メモリ400は、ターゲット・ページ408に記憶されたワード等の、データおよびECCチェック・ビット/チェック・シンボルを含む複数の書き込みワード（本明細書においてコードワードとも称する）を記憶している。図4に示すように、各ワードは、データ・バイト（すなわち書き込みデータ）を記憶するためのデータ・セグメント414と、データ・セグメント414内のデータに関連付けられたチェック・ビット/チェック・シンボルを記憶するための2つ以上のエラー訂正セグメント406と、を含む。一実施形態では、エラー訂正セグメント406は、第1の層のチェック・ビット/シンボルを記憶するための第1の層のエラー訂正セグメント402と、第2の層のチェック・ビット/シンボルを記憶するための第2の層のエラー訂正セグメント404と、を含む。フラッシュ・メモリ400に記憶される予定の書き込みデータ412は、第1の層のECC符号化モジュール418における処理のために（例えば第1の層のチェック・シンボルを発生させるために）受信され、次いで処理のために（例えば第2の層のチェック・シンボルを発生させるために）第2の層のECC符号化モジュール410に渡される。一実施形態では、書き込みデータ412は、図1のコンピュータ・プロセッサ102等のコンピュータ・プロセッサから、またはエンコーダ206における別の符号化モジュールから受信される。他の実施形態では、書き込みデータ412は、第1の層のECC符号化モジュール418および第2の層のECC符号化モジュール410の双方によって受信され、これらが、時間的に重複することはあるが別個に処理を行い、データ・セグメント414に記憶される書き込みデータ412に関連付けられたチェック・シンボルを発生させる。

10

20

30

40

50

## 【0032】

一実施形態において、第1の層のECC符号化モジュール418が書き込みデータ412からECCチェック・シンボルを発生させる際には、リード・ソロモン符号または、限定ではないが、繰り返しコード、パリティ・シンボル、チェック・サム、および暗号ハッシュ等の技法を用いる他のECCコードを用いる。

## 【0033】

一実施形態では、第2の層のECC符号化モジュール410は、低密度パリティ・チェック(LDPC)コードを用いて、書き込みデータ412および以前に書き込んだデータ・ページ(例えば書き込みワードまたはコードワードを含む)から、ECCチェック・シンボルを発生させる。一実施形態では、LDPCコードはフラッシュ・エラー・モードの統計的モデルに基づいたものであり、以前に書き込んでエラー訂正キャッシュ416にキャッシュされているデータを用いて第2の層のECCチェック・シンボルを発生させる。これについては以下で更に詳細に説明する。

10

## 【0034】

いったん第1の層のECC符号化モジュール418および第2の層のECC符号化モジュール410が処理を完了して、ECCチェック・シンボルを発生させると、書き込みデータならびに第1および第2の層のECCチェック・シンボルをターゲット・ページ408に記憶する。書き込みデータ412(本明細書では「データ」とも称する)をフラッシュ・メモリ400のデータ・セグメント414に記憶し、第1の層のECCチェック・シンボルを第1の層のエラー訂正セグメント402に記憶し、第2の層のECCチェック・シンボルを第2の層のエラー訂正セグメント404に記憶する。代替的な実施形態では、第2の層のECCチェック・シンボルを別個のフラッシュ・メモリに記憶する。他の実施形態では、第2の層のECCチェック・シンボルを、第2の層のエラー訂正セグメント404および別個のフラッシュ・メモリ間で分割する。また、書き込みデータ412および第2の層のECCエラー訂正シンボル404のコピーをエラー訂正キャッシュ416に記憶する。別の実施形態では、エラー訂正キャッシュは更に、第1の層のエラー訂正セグメント402のチェック・シンボルも記憶する。一実施形態において、エラー訂正キャッシュ416は、DRAM(dynamic random access memory)またはeDRAM(embedded DRAM)またはSRAM(static random access memory)または他の比較的短い読み取り待ち時間を有する揮発性メモリ等の揮発性メモリに書き込まれる。別の実施形態では、エラー訂正キャッシュ416はPCM等の不揮発性メモリに書き込まれる。

20

## 【0035】

一実施形態において、エラー訂正キャッシュ416は、「C」ページの履歴データを記憶するように構成されている。ここで、Cは、データ412について第2の層のECCコードを計算するために用いられる履歴データの以前に書き込んだページ数である。一実施形態では、これらのページは、現在のページと同じブロック内にプログラムしたこれまでのCページである。Cはプログラムすることができ、いかなるサイズとすることも可能であるが、Cが増大するにつれて、第2の層のECCコードの有効性およびエラー訂正キャッシュ416に対する記憶装置容量の要求の双方が増大する。一実施形態では、Cは、メモリ・ブロックをプログラムした回数、メモリ・ブロックのシンボル・エラー・レート、またはメモリの統計的エラー・モデルに基づいてプログラムすることができる。更に別の実施形態では、エラー訂正キャッシュ416は、当技術分野において既知であるような、迅速なデータの記憶および検索が可能ないずれかの記憶デバイスである。

30

## 【0036】

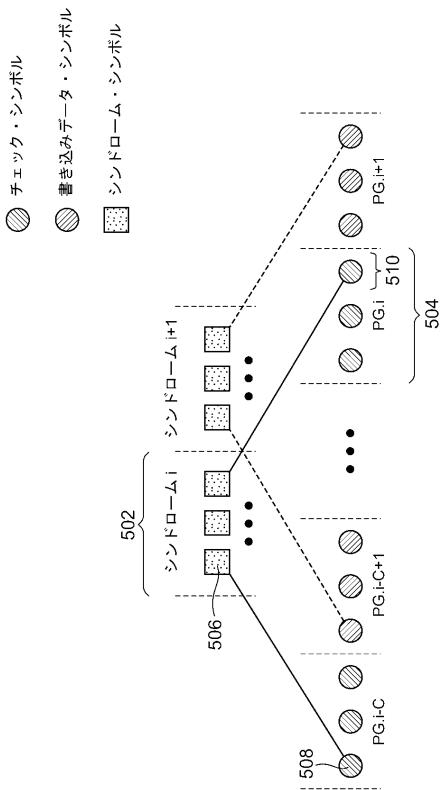

図5は、一実施形態に従った、第2の層のECCチェック・シンボルを発生させるためのブロック図を示す。一実施形態において、第2の層のECC発生は、図4の第2の層のECC符号化モジュール410において実行される。第2の層のECCにおけるチェック・シンボルの数(またはECCの「レート」)は、上述した様々なタイプのエラー(例えばBPD、BLD、FGC、PGM、非均一エラー・タイプ等)の統計的モデルに基づいて発生させる。一実施形態では、第2の層のECC符号化モジュール410は、チェック

40

50

・シンボル  $i_{510}$  等のチェックを発生させる。一実施形態では、図 1 のメモリ  $106$  等のメモリに記憶するために、時刻「 $i$ 」で書き込みデータを受信する。この書き込みデータと、現在書き込んでいるページと同じブロック内に書き込まれた最後の C ページの第 2 の層の ECC チェック・シンボル・コンポーネントと、を用いることによって、チェック・シンボル  $i_{510}$  (すなわちメモリに記憶するための書き込みデータのため) を時刻  $i$  において計算する。このコンポーネントは、現在のページについて受信した書き込みデータと同様に、図 4 のエラー訂正キャッシュ  $416$  に記憶されている。一実施形態では、C は、エラー訂正キャッシュ  $416$  をシンボル単位のページ・サイズで除算したシンボル単位のサイズとして計算される。一実施形態では、チェック・シンボル  $i_{510}$  は、アプリオリに選択した低密度パリティ・チェック (L D P C) ・マトリクスを用いて計算される。

10 パリティ・チェック・マトリクスにより、書き込みデータ・シンボルおよび第 2 の層の ECC チェック・シンボルの線形結合としてシンドローム・シンボル  $502$  を計算することができる。更に、パリティ・チェック・マトリクスでは、書き込みデータ・ページ・シンボルと、現在のページおよびエラー訂正キャッシュ  $416$  に記憶された同一ブロックに属する以前の C ページにのみ属するチェック・シンボルとの線形結合として、シンドローム・シンボル  $i_{502}$  を計算するようになっている。現在のページについてのチェック・シンボル  $i_{510}$  は、シンドローム・シンボル  $502$  が全てゼロであることを保証するよう計算される。書き込みデータおよび第 2 の層の ECC チェック・シンボルはメモリに記憶される。L D P C マトリクスは当業者に既知の技法を用いて生成される。

## 【0037】

20

第 2 の層のフラッシュ認識 ECC 発生について、図 4 の第 2 の層の ECC 符号化モジュール  $410$  で実行されるものとして説明しているが、第 2 の層のフラッシュ認識 ECC 発生は、コンピュータ・プロセッサ  $102$  上のソフトウェアとして、またはメモリ  $106$ 、メモリ・コントローラ  $104$ 、エンコーダ  $206$ 、またはスタンダロン・モジュールのいずれかのハードウェアまたはソフトウェア・モジュールとして実行可能であることは理解されよう。

## 【0038】

30

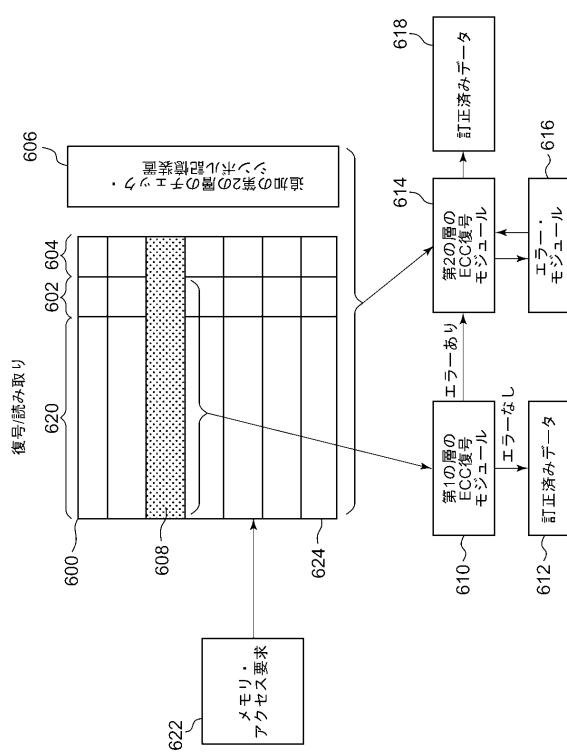

図 6 は、図 1 のメモリ  $106$  等のメモリ  $600$  からデータを検索する実施形態を示す。要求側からメモリ・アクセス要求  $622$  を受信する。一実施形態では、メモリ・アクセス要求  $622$  (これはメモリ  $600$  内のデータ・ページ  $608$  に対応するメモリ・アドレスを含む) は、図 2 のデコーダ  $208$  等のデコーダにおいて受信される。メモリ  $600$  からデータ・ページ  $608$  (本明細書では「コードワード」とも称する) を検索する。図 6 に示すように、データ・ページ  $608$  は、データ・セグメント  $620$ 、第 1 の層の ECC チェック・シンボル  $602$ 、および第 2 の層の ECC チェック・シンボル  $604$  を含む。第 1 の層の ECC モジュール  $610$  はデータ・ページ  $608$  をチェックして、データがエラーを有するか否か、および、かかるエラーが第 1 の層の ECC デコーダによって訂正可能であるか否かを判定する。データ・ページがエラーを有しない場合、またはエラーが第 1 の層の ECC チェック・シンボルによって訂正可能である場合、これは要求側に戻される。一実施形態においては、読み取りデータとして要求側に戻す前に、訂正済みデータ  $612$  に対して更に復号を実行する (例えばシンボル拡張、伸張等)。

40

## 【0039】

40

第 1 の層の ECC 復号モジュール  $610$  は、データ・ページ  $608$  が第 1 の層の ECC 復号モジュール  $610$  によって訂正可能でないエラーを含むと判定すると、ページ  $608$  を含むブロック  $624$  からのデータを、他のチェック・シンボル記憶装置  $606$  に記憶されたいずれかの追加の第 2 の層のチェック・シンボルと共に、更に処理するために第 2 の層の ECC 復号モジュール  $614$  に渡す。第 2 の層の ECC 復号モジュール  $614$  は、第 2 の層のエラー・チェック・シンボル  $604$  および記憶装置  $606$  に記憶された第 2 の層の ECC チェック・シンボルならびにエラー確率モデル  $616$  を用いて、データを訂正する。これについては以下で更に詳細に説明する。エラー確率モデルはメタデータであり、揮発性 DRAM または不揮発性メモリまたはそれらの組み合わせに記憶されている。いつ

50

たんデータが訂正されると、エラー確率モデル 616 は、訂正されたエラーに基づいて更新される。第 2 の層のエラー訂正が必要となるたびに、更新されたエラー確率モデル 616 が用いられて同様に更新される。いったんデータが訂正されたら、訂正済みデータ 618 は要求側に戻される。

【0040】

一実施形態において、第 1 の層の ECC チェック・シンボル 602 および第 2 の層の ECC チェック・シンボル 604 が異なる位置に記憶されている場合は、メモリ・アクセス要求 622 に応答してデータ・セグメント 620 および第 1 の層の ECC チェック・シンボル 602 のみが検索される。この実施形態では、第 2 の層の ECC チェック・シンボル 604 および記憶装置 606 が検索されるのは、第 2 の層の ECC 復号モジュール 641 10 を用いてページを復号する場合だけである。

【0041】

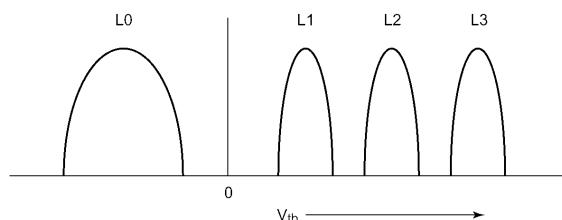

図 7 は、一実施形態における 4 マルチ・レベル・セル (4MLC) NAND フラッシュ・セルに 4 レベルの情報を記憶するために用いる閾値電圧を示す。4MLC は、フラッシュ・メモリの 1 メモリ・セルにおいて 4 つの離散データ・シンボルを含む。図 7 は 4MLC 電圧閾値を示すが、他の実施形態では MLC の他の電圧閾値および他のビット・レベルを使用可能であることは理解されよう。閾値電圧の低い方から順に、4 つのレベルを L0、L1、L2、および L3 と記す。

【0042】

図 8 は、ルックアップ・テーブル・セットの形態で要約されたエラー確率モデル 616 の一実施形態を示す。統計的エラー確率モデル 616 は、セル上に記憶された特定のプログラムされたレベルがエラーによって別の特定レベルに変化する可能性がどの程度であるかに関する情報を含む。かかるエラー・イベントの可能性は一般に、セルの近隣領域の 2 次元 (2D) データ・パターン (これは FGC タイプのエラーに影響を及ぼす)、同一ページおよび他のページ上の他のセルのプログラミング履歴 (これは BPD、BLD、および PGM タイプのエラーに影響を及ぼす)、ならびにデバイス依存性のレベル遷移挙動等のファクターに依存する。一実施形態では、統計的エラー確率モデル 616 は条件確率値 (「エラー重み」とも記す) の集合を含み、それらの各々は、上述のファクターの 1 つ以上を条件としてある記憶値が別の値に変化する可能性を要約する。別の実施形態では、統計的エラー・モデルは 1 つ以上のアポステリオリ条件確率を含み、それらの各々は、セルから値が読み取られて上述のファクターの 1 つ以上が与えられた場合に、セルに記憶された元の値が読み取ったレベルとは異なる所与のレベルであった可能性を要約する。 20 30

【0043】

図 8 の実施形態では、各ルックアップ・テーブルはアポステリオリのエラー重み (すなわち条件確率) を記憶しており、これは、所与のセルから読み取った値  $v_1$  がエラーの際に真の記憶値  $v_2$  から生じたものである可能性を、 $v_1$ 、 $v_2$ 、および上述したファクターの 1 つの関数として要約する。エラー重みベクトル  $w$ 、 $x$ 、および  $y$  の各々は 16 の成分を有し、ここで成分

【数 1】

$$v_2 * 4 + v_1 \quad 40$$

は、読み取り値が  $v_1$  であることを条件として、更に各テーブルがファクターの値に基づくことを条件として、真の記憶値が  $v_2$  であった確率を表す。一実施形態では、重みテーブル 1 802 における第 1 のエラー重みベクトルを割り当てるには、MLC レベル L3 にある各ページ位置の 8 近隣 (neighbor) 数をカウントし、ページ位置におけるデータ値を計算に入れる。このため、例えば、 $w_{00}$  は 16 成分ベクトルであり、成分

【数 2】

$$w_{00}(v_2 * 4 + v_1) \quad 50$$

は、読み取り値が  $v_1$  であることを条件とし、更に 8 近隣値のどれも L3 でなかったとい

う事実を条件として、真の記憶値が  $v_2$  であった確率を表す。一実施形態では、重みテーブル 2 804 に示したような第 2 のエラー重みベクトルは、現在のセルと同じビット・ライン上のプログラムしたセル値の分布に基づいて、更に現在のデータ値に基づいて計算される。重みテーブル 3 806 における第 3 のエラー・ベクトルは、ページ・プログラム数および現在のデータ値に基づいて計算される。これらのテーブルは、第 2 の層の ECC 復号モジュール 614 による各復号の後に更新され、これによって重みモデルに時間履歴を組み込む。これによって、重みモデルは、他のデバイスとは著しく異なることがある。使用中の特定の NAND フラッシュ・デバイスに適合することができる。一実施形態では、各第 2 の層の ECC 復号において観察されるエラー頻度をモデルのエラー重みと線形結合して、新しいモデル・エラー重みを形成する。当技術分野において周知の他の技法を用いて、第 2 の層の ECC デコーダの各使用時に観察される経験的な頻度を組み込むことによって、モデルを更新することができる。別の実施形態では、第 1 の層の ECC デコーダの各使用時に観察されるエラーを用いてモデルを更新する。

【 0 0 4 4 】

代替的な実施形態では、図 8 に示した重みテーブルのサブセットを組み合わせ、もっと高い次元の重みモデルを用いて、これらの条件の連結作用をモデル化する。別の実施形態では、ページに対するプログラム / 消去サイクル数の作用、ページ上で以前に認められたエラーの数、近隣ページ上で認められたエラーの数およびタイプ、ならびにページがプログラムされた順序が、重みテーブルに更に組み込まれる。更に別の実施形態では、セルごとでなくベクトルごとに重みを計算する。更に別の実施形態では、記憶されたメタデータは、ブロック・ページがプログラムされた順序を含み、この順序に基づいて重みの計算を行う。このため、例えば、重みテーブル 1 8 0 2 におけるエラー重みベクトルは、所与のセル位置の近隣領域においてこの所与のセル位置の後にプログラムされたセル位置の数に依存する。代替的な実施形態では、多数のページに対して同時に復号を実行する。一実施形態では、図 6 の第 2 の層の E C C 復号モジュール 6 1 4 は動的プログラミングを用いる。このため、例えばビタビ・アルゴリズムを用いて多数のページを同時に復号することができます。

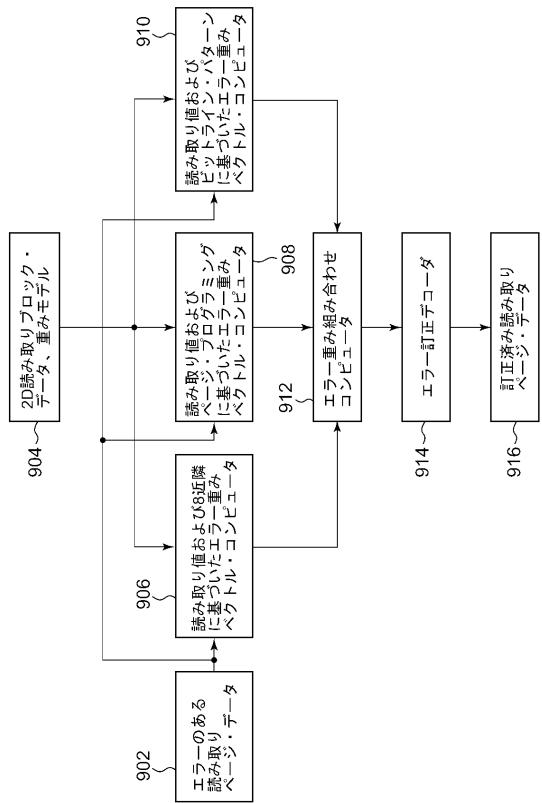

【 0 0 4 5 】

る確率モデルを用いて、各セルごとにかかる確率ベクトルを計算する。この確率ベクトルをエラー重みベクトルとも呼ぶ。

#### 【0046】

ブロック912において、ブロック906、908、および910で計算したエラー重みベクトルを組み合わせて、各セルごとに1つのエラー重みベクトルを形成する。このベクトルの $i$ 番目の成分は、ブロック内のそのセルおよび他のセルから読み取った値を条件として、セルの真の記憶値がレベル $i$ である確率である。一実施形態では、条件付き独立性の仮定 (conditional independence assumption) を用いて、各セルごとに集合エラー重みベクトル (すなわち、所与のセルについての真の値が、個々のエラー重みベクトルによって与えられる、所与のセルについての真の値が $i$ である確率を適切に正規化した積である確率) を生成する。ブロック914において、ソフト・エラー訂正デコーダは、ブロック912で計算した集合重み付け訂正ベクトルを、エラーのあるデータに対して用いる。一実施形態において、デコーダはLDPCデコーダであり、和積または最大積等の当技術分野において周知のアルゴリズムにより、メッセージ伝達アルゴリズムを用いてデータを復号する。ブロック916において、訂正済み読み取りページ・データが生成され、要求側に戻される。

#### 【0047】

技術的な作用および利点には、エラー訂正を計算する場合にフレッシュ・メモリ・エラー・モードの統計的モデルを考慮することによるエラー訂正の信頼性向上が含まれる。別の利点は、いっそう多くのエラーを正確に訂正することでフレッシュ・メモリの信頼性を高めることによってデバイスの寿命を改善することである。更に別の利点は、本発明を実施するためにハードウェア・デバイスの変更が必要ないことである。また別の利点は、BPD、BLD、FGC、PGM等に基づいたエラーの統計的モデルに基づいて訂正を行うことができる機能によって、書き込みの制約 (例えば非順次プログラミング、部分的なページ・プログラミングの禁止) を軽減可能であることである。

#### 【0048】

本明細書において用いた用語は、特定の実施形態を記載する目的のためだけのものであり、本開示を限定することは意図していない。本明細書において用いたように、単数形「1つの」は、文脈によって明らかに他の場合が示されない限り、複数形を含むことが意図されている。また、「含む」または「含んでいる」という言葉あるいはその両方は、本明細書において用いられた場合、述べた特徴、整数、ステップ、動作、要素、または構成要素あるいはそれら全ての存在を規定するが、1つ以上の他の特徴、整数、ステップ、動作、要素、構成要素、またはそれらのグループあるいはそれら全ての存在または追加を除外するものではないことは、理解されよう。

#### 【0049】

以下の特許請求の範囲における全てのミーンズまたはステップ・プラス・ファンクション要素の対応する構造、材料、行為、および均等物は、具体的に特許請求したような他の特許請求した要素と組み合わせて機能を実行するためのいずれかの構造、材料、または行為を含むことが意図されている。本開示の記載は、例示および記述の目的のために提示したが、網羅的であることや、開示した形態に本発明を限定することは、意図していない。本発明の範囲および思想から逸脱することなく、当業者には多くの変更および変形が明らかであろう。実施形態は、本開示の原理および実際的な用途を最良に説明するため、更に、想定される特定の用途に適した様々な変更と共に様々な実施形態に関して当業者が本発明を理解することを可能とするために、選択し記載したものである。

#### 【0050】

当業者には認められるであろうが、本発明の態様は、システム、方法、またはコンピュータ・プログラムとして具現化することができる。従って、本発明の態様は、全体的にハードウェアの実施形態、全体的にソフトウェアの実施形態 (ファームウェア、常駐ソフトウェア、マイクロコード等を含む)、または、ソフトウェアおよびハードウェアの態様を組み合わせた実施形態という形態を取ることができ、それらは全て本明細書において、「

10

20

30

40

50

回路」、「モジュール」、または「システム」と一般的に称することができる。更に、本発明の態様は、具現化されたコンピュータ読み取り可能プログラム・コードを有する1つ以上のコンピュータ読み取り可能媒体において具現化されるコンピュータ・プログラムの形態を取ることも可能である。

#### 【0051】

1つ以上のコンピュータ読み取り可能媒体のあらゆる組み合わせを利用することができる。コンピュータ読み取り可能媒体は、コンピュータ読み取り可能信号媒体またはコンピュータ読み取り可能記憶媒体とすることができます。コンピュータ読み取り可能記憶媒体は例えば、限定ではないが、電子、磁気、光、電磁、赤外線、または半導体のシステム、装置、デバイス、または前述のもののいずれかの適切な組み合わせとすることができます。コンピュータ読み取り可能記憶媒体の更に具体的な例（非網羅的な列挙）は、以下を含む。すなわち、1本以上のワイヤを含む電気的接続、携帯型コンピュータ・ディスクケット、ハード・ディスク、ランダム・アクセス・メモリ（RAM）、読み取り専用メモリ（ROM）、消去可能プログラマブル読み取り専用メモリ（EPROMまたはフラッシュ・メモリ）、光ファイバ、携帯型コンパクト・ディスク読み取り専用メモリ（CD-ROM）、光記憶デバイス、磁気記憶デバイス、または前述のもののいずれかの適切な組み合わせである。この文書の文脈において、コンピュータ読み取り可能記憶媒体は、命令実行システム、装置、またはデバイスによってまたはそれと接続して用いるためにプログラムを含有または記憶することが可能ないずれかのタンジブルな媒体とすることができます。

#### 【0052】

コンピュータ読み取り可能信号媒体は、例えばベースバンドにおいてまたは搬送波の一部として、具現化されたコンピュータ読み取り可能プログラム・コードを有する伝播データ信号を含むことができる。かかる伝播信号は様々な形態のいずれかを取ることができ、それらは限定ではないが、電磁、光、またはそれらのいずれかの適切な組み合わせを含む。コンピュータ読み取り可能信号媒体は、コンピュータ読み取り可能記憶媒体でないが、命令実行システム、装置、またはデバイスによってまたはそれと接続して用いるためにプログラムを伝達、伝播、または転送することが可能ないずれかのコンピュータ読み取り可能媒体とすることができます。

#### 【0053】

コンピュータ読み取り可能媒体上で具現化されるプログラム・コードは、限定ではないが、無線、有線、光ファイバ・ケーブル、RF等、または前述のもののいずれかの適切な組み合わせを含むいずれかの適切な媒体を用いて伝送することができる。

#### 【0054】

本発明の態様の動作を実行するためのコンピュータ・プログラム・コードは、Java（R）、Smalltalk（R）、C++等のオブジェクト指向プログラミング言語、および、「C」プログラミング言語または同様のプログラミング言語等の従来の手順プログラミング言語を含む1つ以上のプログラミング言語のいずれかの組み合わせにおいて記述することができる。プログラム・コードは、全体的にユーザのコンピュータ上で、部分的にユーザのコンピュータ上で、スタンドアロンのソフトウェア・パッケージとして、部分的にユーザのコンピュータ上でおよび部分的に遠隔コンピュータ上で、または全体的に遠隔コンピュータもしくはサーバ上で、実行することができる。後者の場合、遠隔コンピュータは、ローカル・エリア・ネットワーク（LAN）またはワイド・エリア・ネットワーク（WAN）を含むいずれかのタイプのネットワークを介してユーザのコンピュータに接続することができ、または、接続は、（例えばインターネット・サービス・プロバイダを用いてインターネットを介して）外部コンピュータに対して行うことができる。

#### 【0055】

本発明の実施形態に従った方法、装置（システム）、およびコンピュータ・プログラムのフローチャート図またはブロック図あるいはその両方を参照して、本発明の態様について以下に記載する。フローチャート図またはブロック図あるいはその両方の各ブロックならびにフローチャート図またはブロック図あるいはその両方におけるブロックの組み合わ

10

20

30

40

50

せは、コンピュータ・プログラム命令によって実施可能であることは理解されよう。これらのコンピュータ・プログラム命令は、汎用コンピュータ、特殊目的コンピュータ、または他のプログラマブル・データ処理装置のプロセッサに提供されて機械を生成することができ、これによって、コンピュータまたは他のプログラマブル・データ処理装置のプロセッサによって実行される命令が、フローチャートまたはブロック図あるいはその両方のブロックまたは複数のブロックに規定された機能／行為を実施するための手段を生成するようになっている。

【0056】

また、これらのコンピュータ・プログラム命令はコンピュータ読み取り可能媒体に記憶することができ、これによって、コンピュータ、他のプログラマブル・データ処理装置、または他のデバイスに特定の方法で機能するように指示することができ、これにより、コンピュータ読み取り可能媒体に記憶された命令が、フローチャートまたはブロック図あるいはその両方のブロックまたは複数のブロックに規定された機能／行為を実施する命令を含む製造品を生成するようになっている。

10

【0057】

また、コンピュータ・プログラム命令を、コンピュータ、他のプログラマブル・データ処理装置、または他のデバイスにロードして、そのコンピュータ、他のプログラマブル装置、または他のデバイス上で一連の動作ステップを実行させてコンピュータ実施プロセスを生成することができ、これによって、コンピュータまたは他のプログラマブル装置上で実行する命令が、フローチャートまたはブロック図あるいはその両方のブロックまたは複数のブロックに規定された機能／行為を実施するためのプロセスを提供するようになっている。

20

【0058】

本明細書に示したフロー図は一例に過ぎない。本発明の思想から逸脱することなく記載した図またはステップ（または動作）に対する多くの変形が可能である。例えば、ステップは異なる順序で実行することができ、またはステップを追加、削除、もしくは変更することも可能である。これらの全ての変形は、特許請求する本発明の一部と見なされる。

【0059】

本発明の好適な実施形態について記載したが、当業者は、現在および今後の双方で、以下の特許請求の範囲内に該当する様々な改良および向上を実施可能であることは理解されよう。これらの特許請求の範囲は、最初に記載した本発明についての適正な保護を維持するように解釈されるものである。

30

【符号の説明】

【0060】

100 システム

102 C P U

104 メモリ・コントローラ

106、202 メモリ

206 エンコーダ

208 デコーダ

214 受信器

412 第2のE C C符号化モジュール

416 エラー訂正キャッシュ

418 第1のE C C符号化モジュール

610 第1の層のE C C復号モジュール

614 第2の層のE C C復号モジュール

616 エラー・モジュール

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

| ビット・<br>ライングラム<br>の分布                                                |                                                                      | ページ・<br>フレーム<br>の数                                                   | 16成分エラー重み<br>ベクトル(読み取り値<br>V <sub>1</sub> および<br>V <sub>2</sub> の閾数) |

|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| 16成分エラー重み<br>ベクトル(読み取り値<br>V <sub>1</sub> および<br>V <sub>2</sub> の閾数) |

| 0                                                                    | W <sub>00</sub>                                                      | t <sub>0</sub>                                                       | X <sub>00</sub>                                                      |

| 1                                                                    | W <sub>01</sub>                                                      | t <sub>1</sub>                                                       | X <sub>01</sub>                                                      |

| ...                                                                  |                                                                      | ...                                                                  | ...                                                                  |

| 7                                                                    | W <sub>07</sub>                                                      | t <sub>7</sub>                                                       | X <sub>07</sub>                                                      |

【図9】

---

フロントページの続き

(72)発明者 アシシュ・ジャグモハン

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ キチャワン・ロード1101

インターナショナル・ビジネス・マシーンズ ティージェイ・ワトソン・リサーチ・センター内

(72)発明者 ミケーレ・マルティノ・フランセスキーニ

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ キチャワン・ロード1101

インターナショナル・ビジネス・マシーンズ ティージェイ・ワトソン・リサーチ・センター内

(72)発明者 ルイス・エー・ラストラス モンタノ

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ ピー・オー・ボックス218

ルート134 キチャワン・ロード1101 インターナショナル・ビジネス・マシーンズ テ

ィージェイ・ワトソン・リサーチ・センター内

(72)発明者 マヤンク・シャルマ

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ ピー・オー・ボックス218

ルート134 キチャワン・ロード1101 インターナショナル・ビジネス・マシーンズ テ

ィージェイ・ワトソン・リサーチ・センター内

審査官 松永 稔

(56)参考文献 特開2010-238363(JP, A)

特開2008-108356(JP, A)

国際公開第2010/011692(WO, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 16

G 06 F 11 / 10