(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년11월11일

(11) 등록번호 10-0926094

(24) 등록일자 2009년11월03일

(51) Int. Cl.

H01L 33/00 (2006.01)

(21) 출원번호 10-2007-7023098

(22) 출원일자 2006년02월15일

심사청구일자 2007년10월09일

(85) 번역문제출일자 2007년10월09일

(65) 공개번호 10-2007-0116086

(43) 공개일자 2007년12월06일

(86) 국제출원번호 PCT/JP2006/303088

(87) 국제공개번호 WO 2006/095566

국제공개일자 2006년09월14일

(30) 우선권주장

JP-P-2005-00065074 2005년03월09일 일본(JP)

(56) 선행기술조사문현

JP2004087930 A

US20026433367 A1

JP2003243302 A

전체 청구항 수 : 총 23 항

심사관 : 이용배

(54) 질화물 반도체 발광 소자 및 그 제조 방법

### (57) 요 약

질화물 반도체 발광 소자는 기판; 제 1 도전형 반도체층, 발광층, 및 제 2 도전형 반도체층을 포함하는 질화물 반도체층; 상기 제 2 도전형 반도체층의 제 1 표면의 적어도 일부에 접하는 투광성 전극; 및 상기 제 1 도전형 반도체층에 접하는 제 2 전극을 포함하고: 상기 기판은 상기 소자의 주변부에서 상기 질화물 반도체층의 제 1 부분의 제거에 의해 노출된 제 1 영역이 형성된 제 1 면, 및 상기 소자의 주변부 이외에 있어서 상기 투광성 전극에 접하고 있는 상기 질화물 반도체층의 적어도 제 2 부분의 제거에 의해 노출된 제 2 영역을 구비하고 있다. 상기 소자의 제조 방법은 제 1 노출 영역을 형성하기 위해 상기 기판이 노출될 때까지 상기 소자의 주변부에서 상기 질화물 반도체층의 제 1 부분을 제거하는 공정, 및 제 2 노출 영역을 형성하기 위해 상기 기판에 도달할 때까지 상기 소자의 주변부 이외에서 상기 투광성 전극에 접하는 상기 질화물 반도체층의 적어도 제 2 부분을 제거하는 공정을 포함하고; 상기 공정들은 레이저에 의한 제거와 습식 에칭에 의한 제거의 조합에 의해 이루어진다.

대 표 도 - 도2

## 특허청구의 범위

### 청구항 1

기판;

제 1 도전형 반도체층, 발광층, 및 제 2 도전형 반도체층을 포함하는 질화물 반도체층;

상기 제 2 도전형 반도체층의 제 1 면의 적어도 일부에 접하는 투광성 전극; 및

상기 제 1 도전형 반도체층에 접하는 제 2 전극을 포함하고:

상기 기판은 소자의 주변부에서 상기 질화물 반도체층의 제 1 부분이 제거되어 노출된 제 1 영역, 및 상기 소자의 주변부 이외에 있어서 상기 투광성 전극에 접하고 있는 상기 질화물 반도체층의 적어도 제 2 부분이 기판에 도달할 때까지 제거되어 노출된 제 2 영역을 구비하고 있고,

상기 소자의 주변부에서 제거된 상기 질화물 반도체층의 상기 제 1 부분은 상기 기판의 방향으로 증가되어 있고, 상기 제거후의 상기 기판에 접하는 상기 질화물 반도체층의 적어도 일부에는 상기 기판을 향하여 기울어진 측면이 형성될 수 있으며,

상기 기판의 상기 제 2 영역을 형성하는 상기 질화물 반도체층의 하나의 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\theta_1$ )는  $90^\circ$  보다 크고  $180^\circ$  보다 작은 것을 특징으로 하는 질화물 반도체 발광 소자.

### 청구항 2

삭제

### 청구항 3

제 1 항에 있어서,

상기 기판의 상기 제 2 영역은 상기 투광성 전극 바로 아래에 배치된 부분을 구비하고 있는 것을 특징으로 하는 질화물 반도체 발광 소자.

### 청구항 4

삭제

### 청구항 5

제 1 항에 있어서,

상기 기판의 상기 제 2 영역을 형성하는 상기 질화물 반도체층의 하나의 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\theta_1$ )는  $95^\circ$  이상  $170^\circ$  이하인 것을 특징으로 하는 질화물 반도체 발광 소자.

### 청구항 6

제 1 항에 있어서,

상기 기판의 상기 제 2 영역을 형성하는 상기 질화물 반도체층의 하나의 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\theta_1$ )는  $100^\circ$  이상  $160^\circ$  이하인 것을 특징으로 하는 질화물 반도체 발광 소자.

### 청구항 7

제 1 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분은 상기 질화물 반도체층의 상기 제 1 부분의 둘레 길이의 1%~1000%의 범위의 길이를 갖는 둘레를 갖는 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 8**

제 1 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분은 상기 질화물 반도체층의 상기 제 1 부분의 둘레 길이의 5%~500%의 범위의 길이를 갖는 둘레를 갖는 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 9**

제 1 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분은 상기 질화물 반도체층의 상기 제 1 부분의 둘레 길이의 10%~200%의 범위의 길이를 갖는 둘레를 갖는 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 10**

제 1 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분은 원형의 개구부인 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 11**

제 1 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분은 직선으로 둘러싸인 형상인 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 12**

제 1 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분은 상기 투광성 전극에 접하는 상기 질화물 반도체층내에 적어도 하나가 형성되어 있는 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 13**

제 1 항에 있어서,

상기 기판의 상기 제 2 영역의 내부에는 상기 질화물 반도체층의 상기 제 2 부분에 대응하는 형상의 가공 마크가 형성되어 있는 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 14**

제 1 항에 있어서,

상기 제 1 부분을 형성하는 상기 질화물 반도체층의 하나의 기울어진 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\theta_2$ )는  $90^\circ$  보다 크고  $180^\circ$  보다 작은 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 15**

제 1 항에 있어서,

상기 제 1 부분을 형성하는 상기 질화물 반도체층의 하나의 기울어진 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\theta_2$ )는  $95^\circ$  이상  $170^\circ$  이하인 것을 특징으로 하는 질화물 반도체 발광 소자.

**청구항 16**

제 1 항에 있어서,

상기 제 1 부분을 형성하는 상기 질화물 반도체층의 하나의 기울어진 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\theta_2$ )는  $100^\circ$  이상  $160^\circ$  이하인 것을 특징으로 하는 질화물 반도체 발광

소자.

### 청구항 17

제 1 항에 있어서,

상기 기판의 상기 제 1 및 제 2 영역과 상기 질화물 반도체층의 측면에는 각각 반사막이 형성되어 있는 것을 특징으로 하는 질화물 반도체 발광 소자.

### 청구항 18

제 1 항에 있어서,

상기 기판은 사파이어로 형성되는 것을 특징으로 하는 질화물 반도체 발광 소자.

### 청구항 19

기판; 제 1 도전형 반도체층, 발광층, 및 제 2 도전형 반도체층을 포함하는 질화물 반도체층; 상기 제 2 도전형 반도체층의 제 1 면의 적어도 일부에 접하는 투광성 전극; 및 상기 제 1 도전형 반도체층에 접하는 제 2 전극을 포함하는 질화물 반도체 발광 소자의 제조 방법으로서:

제 1 노출 영역을 형성하기 위해 상기 기판이 노출될 때까지 상기 소자의 주변부에서 상기 질화물 반도체층의 제 1 부분을 제거하는 공정, 및

제 2 노출 영역을 형성하기 위해 상기 기판에 도달할 때까지 상기 소자의 주변부 이외에서 상기 투광성 전극에 접하는 상기 질화물 반도체층의 적어도 제 2 부분을 제거하는 공정을 포함하고;

상기 공정들은 레이저에 의한 제거와 습식 에칭에 의한 제거의 조합에 의해 이루어지는 것을 특징으로 하는 질화물 반도체 발광 소자의 제조 방법.

### 청구항 20

제 19 항에 있어서,

상기 질화물 반도체층의 적어도 상기 제 2 부분의 제거는 습식 에칭의 조건을 제어함으로써 상기 기판의 방향으로 증가되어 상기 제거 후 남은 상기 반도체층에 상기 기판을 향하여 기울어진 측면을 형성하는 것을 특징으로 하는 질화물 반도체 발광 소자의 제조 방법.

### 청구항 21

제 19 항 또는 제 20 항에 있어서,

상기 질화물 반도체층의 상기 적어도 제 2 부분을 기판에 도달할 때까지 제거하는 공정은, 200~300°C의 온도에서 습식에칭함으로써, 상기 기판의 상기 제 2 노출영역의 일부가 상기 투광성 전극 바로 아래에 오도록 하는 것을 특징으로 하는 질화물 반도체 발광 소자의 제조 방법.

### 청구항 22

제 19 항 또는 제 20 항에 있어서,

상기 질화물 반도체층의 상기 제 2 부분에 대응하는 형상의 가공 마크가 레이저를 사용한 가공에 의해 상기 기판의 상기 제 2 노출 영역의 중앙부에 형성되는 것을 특징으로 하는 질화물 반도체 발광 소자의 제조 방법.

### 청구항 23

제 19 항 또는 제 20 항에 있어서,

상기 제 1 부분이 제거된 상기 질화물 반도체층은 상기 질화물 반도체층의 상기 제 1 부분의 제거 중에 상기 습식 에칭의 조건을 제어함으로써 외측으로 기울어진 측면을 갖는 것을 특징으로 하는 질화물 반도체 발광 소자의 제조 방법.

### 청구항 24

제 1 항에 기재된 질화물 반도체 발광 소자와 형광 물질이 조합된 것을 특징으로 하는 광원.

### 청구항 25

제 24 항에 기재된 광원이 형성된 것을 특징으로 하는 조명 기구.

## 명세서

### 기술 분야

- <1> 본 출원은 2005년 3월 17일에 출원된 미국 출원 60/662,369와 35 U.S.C. § 111(b)에 따라 2005년 3월 9일에 출원된 일본 특허출원 제2005-065074호의 출원일의 35 U.S.C. § 119(e)(1)에 따른 이익을 주장하는 35 U.S.C. § 111(a)하에 출원된 출원이다.

- <2> 본 발명은 질화물 반도체 발광 소자 특히, 광 방출 효율이 향상된 질화물 반도체 발광 다이오드와 그 제조 방법에 관한 것이다.

### 배경 기술

- <3> III족 질화물 반도체(본 발명에서는 생략하여 "질화물 반도체"라 함)는 가시광으로부터 자외광 영역에 대응하는 에너지의 직접 변이형의 밴드갭(bandgap)을 포함하고, 고효율의 발광이 가능하여 결과적으로 발광 다이오드(LED) 또는 레이저 다이오드(LD) 등의 상업적 제품화가 이루어져 있다. 특히, 형광 물질과의 조합에 의한 백색 발광 다이오드의 실현은 발광 다이오드의 응용을 위한 새로운 분야로 기대되고 있다.

- <4> 발광 다이오드의 출력은 관련 소자로부터 외부로의 광 방출 효율에 의해 크게 영향을 받는다. 광 방출의 효율에 있어서 소자의 표면상의 전반사가 큰 영향을 주는 요인으로서 작용한다. 잘 알려져 있는 바와 같이, 굴절률이 큰 반도체층으로부터 굴절률이 작은 외부로 광이 진행할 때 임계각( $\Theta_c$ )을 초과하는 부분의 광은 소자의 계면상에서 전반사를 일으켜서 광이 굴절률이 작은 외부로 방출되지 않는다.

- <5> 계면에서의 전반사에 의한 광 방출의 제한을 회피하기 위해 계면을 거칠게하는 방법(예컨대, 일본 특허 제 2836687호)과 소자의 형상을 가공하여 다른 면의 이스케이프 콘(Escape Cone)을 이용하는 방법이 알려져 있다(예컨대, 일본 특허 제2784537호)

- <6> 일반적인 발광 다이오드는 소자의 제조상의 용이함을 위해 대부분 직사각 육면체의 형상으로 이루어진다. 이 경우 이스케이프 콘을 형성할 수 있는 계면의 수는 6으로 한정된다.

- <7> 이스케이프 콘의 상세한 입체각의 크기는 각 계면의 특성에 따라 결정된다. 물론, 각 입체각의 전체 크기가 계면의 수에 비례하여 증가한다.

- <8> 따라서, 발광 다이오드 소자의 형상을 일반적인 직사각 육면체로부터 면의 수를 증가시키도록 함으로써 발광 다이오드 소자의 출력이 증가한다. 면수의 증가에 의한 출력 향상의 극한은 소자를 반구 돔 형상으로 가공하는 방법이다. 이 극한의 방법으로 수많은 종래 기술이 이미 소개되었다(예컨대, 일본 특허 공개 소61-222285호 공보).

- <9> 그러나, 소자의 면수를 증가시키는 방법은 소자의 가공이 용이하지 않기 때문에 제품의 수율을 현저히 저하시키는 문제를 수반한다. 따라서, 에칭 가공에 의해 소자 표면에 미세한 홈 가공을 행하여 실질적인 면수를 증가시키는 방법도 제안되어 있다(예컨대, 일본 특허 공개 2002-164574호 공보 및 일본 특허 공개 2004-87930호 공보 참조). 일본 특허 공개 2004-87930호 공보는 전극 바로 아래에 전류가 집중되는 것을 방지하도록 가공된 전류 저지 홈의 역할을 개시한다.

- <10> 광 방출 효율의 향상을 위해 면의 수가 실질적으로 증가하면 결과적으로 추가된 면의 면적이 증가되어 효과가 단조롭게 증가한다. 소자의 표면에 홈 가공이 이루어지면 형성된 홈이 깊을수록 광 방출 효율이 상승한다.

- <11> 그러나, 질화물 반도체는 반응성이 부족하고, 가공이 용이하지 않다. 일반적으로는 염소계의 가스를 이용하고, 에칭 가스가 플라즈마로 여기된 반응종에 의해 에칭을 행하는 드라이 에칭이 주류이다. 드라이 에칭의 사용에도 불구하고 가공 속도는 현저하게 감소되어 수  $\mu\text{m}/\text{h}$ 밖에 되지 않는다.

- <12> 또한, 고에너지의 플라즈마에 의한 가공이기 때문에 하전 입자(charged particle)에 의한 대전 파괴, 자외선에 의해 열화를 수반하는 것으로 알려져 있다. 가공량을 증대시키기 위해 장시간의 에칭을 행하면 그 영향도 무시

할 수 없고, 발광 다이오드의 특성이 향상되지 않는 문제가 있었다.

- <13> 본 발명은 질화물 반도체 발광 소자의 광 방출 효율을 향상시키는 것을 목적으로 한다. 따라서, 소자 형상의 가공을 용이하게 하고, 수율의 향상을 목적으로 한다.

- <14> 본 발명은 상기 목적을 달성하기 위해 이루어진 것이고, 이하의 본 발명의 실시형태를 채택한다.

### 발명의 상세한 설명

- <15> 본 발명은 기판; 제 1 도전형 반도체층, 발광층, 및 제 2 도전형 반도체층을 포함하는 질화물 반도체층; 상기 제 2 도전형 반도체층의 제 1 면의 적어도 일부에 접하는 투광성 전극; 및 상기 제 1 도전형 반도체층에 접하는 제 2 전극을 포함하고: 상기 기판은 상기 소자의 주변부에서 상기 질화물 반도체층의 제 1 부분이 제거되어 노출된 제 1 영역이 형성된 제 1 면, 및 상기 소자의 주변부 이외에 있어서 상기 투광성 전극에 접하고 있는 상기 질화물 반도체층의 적어도 제 2 부분이 기판에 도달할 때까지 제거되어 노출된 제 2 영역을 구비하고 있는 질화물 반도체 발광 소자를 제 1 실시형태로서 제공한다.

- <16> 상기 제 1 실시형태를 포함하는 본 발명의 제 2 실시형태에 있어서, 상기 소자의 주변부에서 제거된 상기 질화물 반도체층의 상기 제 1 부분은 상기 기판의 방향으로 증가되어 있고, 상기 제거후의 상기 기판에 접하는 상기 질화물 반도체층의 적어도 일부에는 상기 기판을 향하여 기울어진 측면이 형성될 수 있다.

- <17> 상기 제 1 또는 상기 제 2 실시형태를 포함하는 본 발명의 제 3 실시형태에 있어서, 상기 기판의 상기 제 2 영역은 상기 투광성 전극 바로 아래에 배치된 부분을 구비하고 있다.

- <18> 상기 제 2 실시형태를 포함하는 본 발명의 제 4 실시형태에 있어서, 상기 기판의 상기 제 2 영역을 결정하는 상기 질화물 반도체층의 하나의 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\Theta_1$ )는  $90^\circ$  보다 크고  $180^\circ$  보다 작다.

- <19> 상기 제 2 실시형태를 포함하는 본 발명의 제 5 실시형태에 있어서, 상기 기판의 상기 제 2 영역을 결정하는 상기 질화물 반도체층의 하나의 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\Theta_1$ )는  $95^\circ$  이상  $170^\circ$  이하이다.

- <20> 상기 제 2 실시형태를 포함하는 본 발명의 제 6 실시형태에 있어서, 상기 기판의 상기 제 영역을 결정하는 상기 질화물 반도체층의 하나의 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\Theta_1$ )는  $100^\circ$  이상  $160^\circ$  이하이다.

- <21> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 7 실시형태에 있어서, 상기 질화물 반도체층의 상기 제 2 부분은 상기 질화물 반도체층의 상기 제 1 부분의 둘레 길이의 1%~1000%의 범위의 길이를 갖는 둘레를 구비하고 있다.

- <22> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 8 실시형태에 있어서, 상기 질화물 반도체층의 상기 제 2 부분은 상기 질화물 반도체층의 상기 제 1 부분의 둘레 길이의 5%~500%의 범위의 길이를 갖는 둘레를 구비하고 있다.

- <23> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 9 실시형태에 있어서, 상기 질화물 반도체층의 상기 제 2 부분은 상기 질화물 반도체층의 상기 제 1 부분의 둘레 길이의 10%~200%의 범위의 길이를 갖는 둘레를 구비하고 있다.

- <24> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 10 실시형태에 있어서, 상기 질화물 반도체층의 상기 제 2 부분은 거의 원형의 개구부이다.

- <25> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 11 실시형태에 있어서, 상기 질화물 반도체층의 상기 제 2 부분은 거의 직선으로 둘러싸인 형상이다.

- <26> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 12 실시형태에 있어서, 상기 질화물 반도체층의 상기 제 2 부분은 상기 투광성 전극에 접하는 상기 질화물 반도체층내에 적어도 하나씩 형성되어 있다.

- <27> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 13 실시형태에 있어서, 상기 기판의 상기 제 2 영역의 내부에는 상기 질화물 반도체층의 상기 제 2 부분에 거의 대응하는 형상의 가공 마크가 형성되어 있다.

- <28> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 14 실시형태에 있어서, 상기 제 1 부분을 결정하는 상기 질화물 반도체층의 하나의 기울어진 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\Theta_2$ )는  $90^\circ$  보다 크고  $180^\circ$  보다 작다.

- <29> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 15 실시형태에 있어서, 상기 제 1 부분을 결정하는 상기 질화물 반도체층의 하나의 기울어진 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\Theta_2$ )는  $95^\circ$  이상  $170^\circ$  이하이다.

- <30> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 16 실시형태에 있어서, 상기 제 1 부분을 결정하는 상기 질화물 반도체층의 하나의 기울어진 측면에 대한 법선과 상기 기판의 상기 제 1 면에 대한 법선이 형성하는 각도( $\Theta_2$ )는  $100^\circ$  이상  $160^\circ$  이하이다.

- <31> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 17 실시형태에 있어서, 상기 기판의 상기 제 1 및 제 2 영역과 상기 질화물 반도체층의 측면에는 각각 반사막이 형성되어 있다.

- <32> 상기 제 1 또는 제 2 실시형태를 포함하는 본 발명의 제 18 실시형태에 있어서, 상기 기판은 사파이어로 형성된다.

- <33> 본 발명은 기판; 제 1 도전형 반도체층, 발광층, 및 제 2 도전형 반도체층을 포함하는 질화물 반도체층; 상기 제 2 도전형 반도체층의 제 1 면의 적어도 일부에 접하는 투광성 전극; 및 상기 제 1 도전형 반도체층에 접하는 제 2 전극을 포함하는 질화물 반도체 발광 소자의 제조 방법으로서: 제 1 노출 영역을 형성하기 위해 상기 기판이 노출될 때까지 상기 소자의 주변부에서 상기 질화물 반도체층의 제 1 부분을 제거하는 공정, 및 제 2 노출 영역을 형성하기 위해 상기 기판에 도달할 때까지 상기 소자의 주변부 이외에서 상기 투광성 전극에 접하는 상기 질화물 반도체층의 적어도 제 2 부분을 제거하는 공정을 포함하고; 상기 공정들은 레이저에 의한 제거와 습식 에칭에 의한 제거의 조합에 의해 이루어지는 질화물 반도체 발광 소자의 제조 방법을 제 19 실시형태로서 더 제공한다.

- <34> 상기 제 19 실시형태를 포함하는 본 발명의 제 20 실시형태에 있어서, 상기 질화물 반도체층의 적어도 상기 제 2 부분의 제거는 습식 에칭의 조건을 제어함으로써 상기 기판의 방향으로 증가되어 상기 제거 후 남은 상기 반도체층에 상기 기판을 향하여 기울어진 측면을 형성한다.

- <35> 상기 제 19 또는 상기 제 20 실시형태를 포함하는 본 발명의 제 21 실시형태에 있어서, 상기 질화물 반도체층의 상기 적어도 상기 제 2 부분을 기판에 도달할 때까지 제거하는 공정은,  $200\sim300^\circ\text{C}$ 의 온도에서 습식에칭함으로써, 상기 기판의 상기 제 2 노출 영역의 일부가 상기 투광성 전극 바로 아래에 오도록 한다.

- <36> 상기 제 19 또는 상기 제 20 실시형태를 포함하는 본 발명의 제 22 실시형태에 있어서, 레이저를 사용한 가공에 의해 상기 질화물 반도체층의 상기 제 2 부분에 거의 대응하는 형상 마크가 상기 기판의 상기 제 2 노출 영역의 거의 중앙부에 형성된다.

- <37> 상기 제 19 또는 상기 제 20 실시형태를 포함하는 본 발명의 제 23 실시형태에 있어서, 상기 제 1 부분이 제거된 상기 질화물 반도체층은 상기 질화물 반도체층의 상기 제 1 부분의 제거 중에 상기 습식 에칭의 조건을 제어함으로써 외측으로 기울어진 측면을 구비하고 있다.

- <38> 본 발명은 상기 제 1 또는 제 2 실시형태의 질화물 반도체 발광 소자와 형광 물질이 조합된 광원을 제 24 실시 형태로서 더 제공한다.

- <39> 본 발명은 상기 제 24 실시형태의 광원이 형성된 조명 기구를 제 25 실시형태로서 더 제공한다.

- <40> 본 발명에 의하면, 광 방출 효율이 향상되고, 관련 소자의 형상 가공을 불량이 야기되지 않는 가공법으로 행할 수 있어 수율의 향상을 도모할 수 있다. 본 발명은 전류가 전하의 바로 아래에 집중되는 것을 방지하여 질화물 반도체층 내의 넓은 범위에 광이 방출될 수 있는 효과도 있다.

- <41> 본 발명의 목적, 특징, 및 장점은 첨부 도면을 참조한 다음의 설명으로부터 당업자에게 자명하게 될 것이다.

### 실 시 예

- <54> 본 발명의 질화물 반도체 발광 소자는, 상기 제 1 실시형태에 기재한 바와 같이, 소자의 주변부에서 기판의 제 1 면이 질화물 반도체층의 제 1 부분이 제거되어 노출된 제 1 영역을 구비하고, 소자의 주변부(반도체층의 제 1

면) 이외의 투광성 전극에 접하고 있는 질화물 반도체층의 적어도 제 2 부분이 기판에 도달할 때까지 제거되어 기판의 제 1 면의 제 2 영역이 노출된 제 2 부분이 형성된다. 본 발명의 제 2 실시형태에서는 기판을 향하여 질화물 반도체층의 제거를 증가시켜, 기판에 접하는 제거후에 남겨진 질화물 반도체층의 측면의 적어도 일부가 기판을 향하여 기울어진다. 이 기울어짐은 소자 주변부의 내부와 외부 중 어느 한쪽 또는 모두에 형성될 수 있고, 양쪽 모두에 형성되는 것이 바람직하다.

<55> 이하, 첨부 도면을 참조하여 본 발명을 상세히 설명한다.

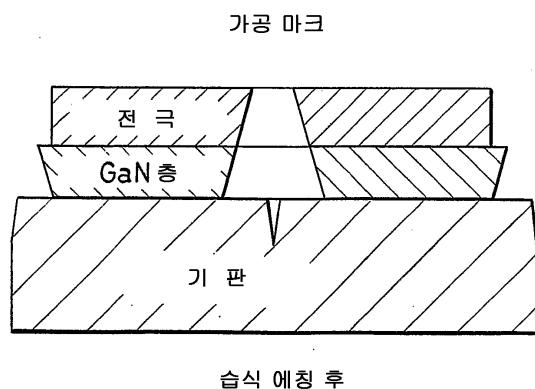

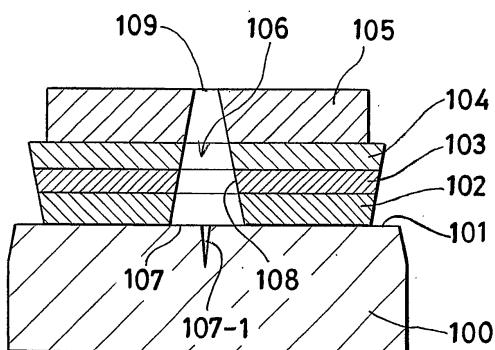

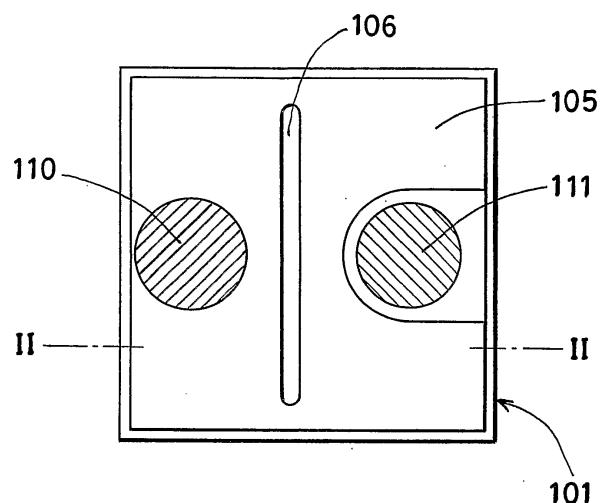

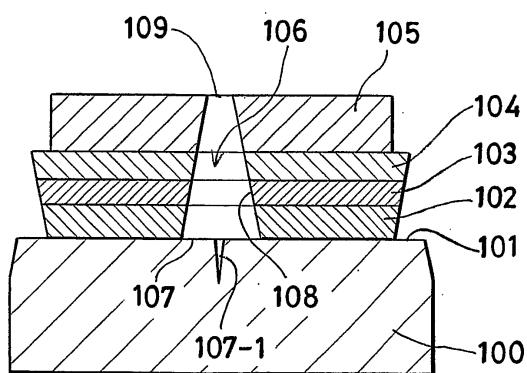

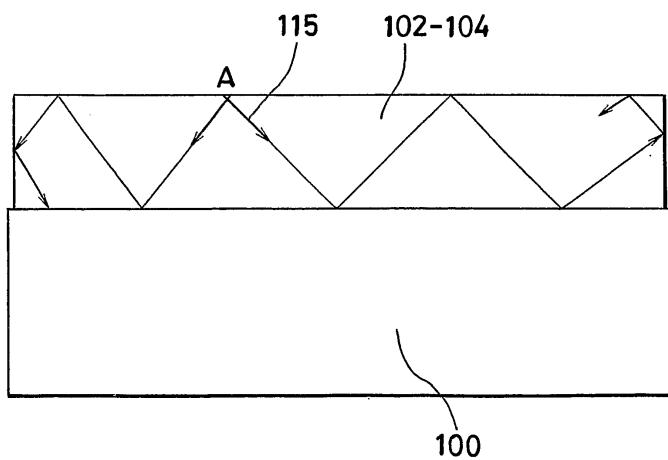

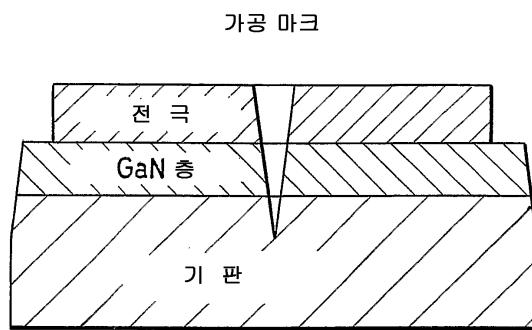

<56> 도 1은 본 발명에 의한 질화물 반도체 발광 소자의 일례를 나타낸 평면도이고, 도 2는 도 1에 있어서의 II-II 선단면도이다. 도면에 있어서, 참조 번호 100은 기판, 101은 기판 주변부의 노출면, 102는 제 1 도전형 반도체층 103은 발광층, 104는 제 2 도전형 반도체층, 105는 p형 전극이다. 도시된 반도체층은 기본 구성을 나타낸다. 예컨대, 버퍼층(buffer layer), 클래드층(clad layer), 및 접촉층을 더 포함할 수 있다.

<57> 본 발명의 질화물 반도체 발광 소자는 소자의 주변부에서 질화물 반도체층의 적어도 제 1 부분의 제거에 의한 기판의 노출면(101)을 구비한다. 각 소자는 반도체 웨이퍼에 전극 등이 형성된 후 반도체 웨이퍼를 분리함으로써 얻어진다. 이 분리의 코스 중에서 각 소자의 경계면에는 기판의 내부에 도달할 때까지 레이저 가공에 의해 홈이 형성된다.

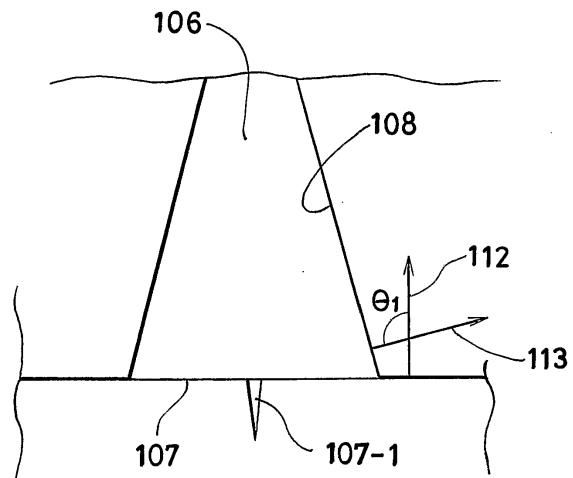

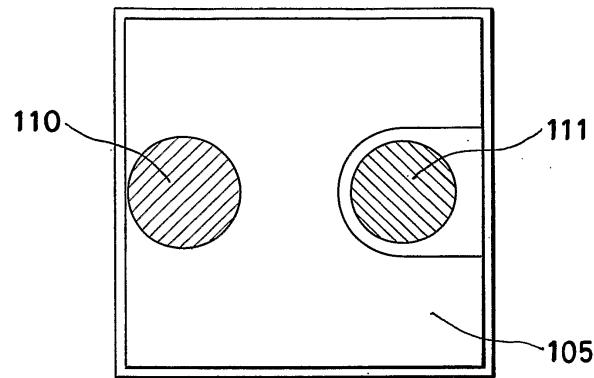

<58> 또한, 주변부 이외의 질화물 반도체층의 일부가 기판에 도달할 때까지 제거되어 이 제거 부분에서 기판이 노출된다. 이 제거에 의해 반도체층의 제 1 면에 개구부(109)를 포함하는 오목홈(106)이 형성된다. 이 오목홈의 선단은 기판의 제 1 면에 도달하거나 기판 내부에 남겨질 수 있다. 도 3은 이 오목홈부의 확대 단면도이다. 도 3에 있어서, 107은 오목홈의 저부에 있어서의 기판 표면이고, 108은 오목홈의 경사면이고, 109는 오목홈의 개구이고, 112는 기판의 주면에 대한 법선이고, 113은 경사면(108)에 대한 법선이고,  $\theta_1$ 은 법선(112, 113)에 의해 형성된 각도이다.

<59> 반도체층내에 오목홈을 형성함으로써 반도체층의 면수가 증가하고, 상기한 바와 같은 이유로 광 방출 효율이 향상된다. 오목홈은 하측(기판의 방향으로)을 향하여 확대된 형상, 즉 기판을 향하여 기울어진 오목홈의 측면을 구비한 형상인 것이 바람직하다. 또한, 오목홈의 저면의 일부는 투광성 전극 바로 아래에 놓이는 것이 바람직하다.

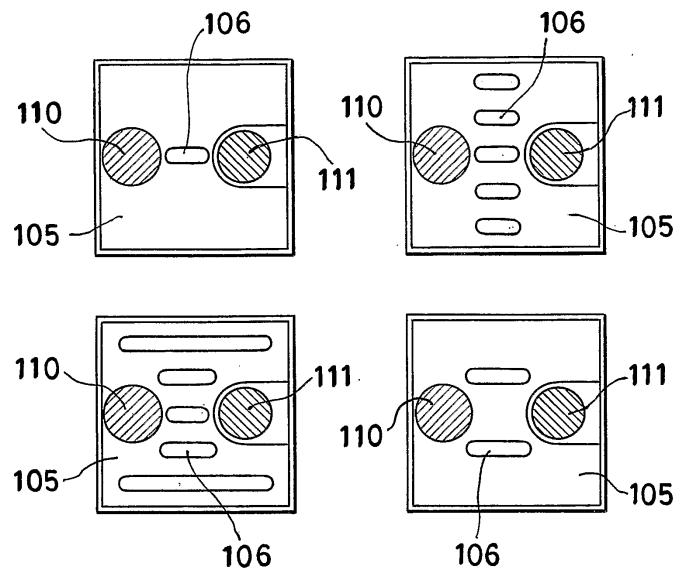

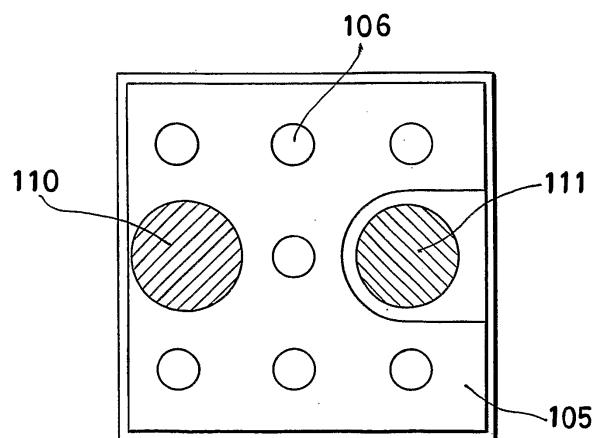

<60> 오목홈의 기울어진 정도를 나타내는 각도( $\theta_1$ )는 가능하면  $90^\circ$  보다 크고  $180^\circ$  보다 작은 넓은 범위에서 선택될 수 있고,  $95^\circ$  이상  $170^\circ$  이하의 범위가 바람직하고,  $100^\circ$  이상  $160^\circ$  이하의 범위가 더욱 바람직하다.

<61> 소자의 주변부 이외의 질화물 반도체층을 제거하는 부분[개구(109)]은 적어도 하나씩 형성되고, 그 둘레 길이는 넓은 범위로 선택할 수 있다. 소자의 주변부에 있어서 제거하는 둘레 길이에 대한 비로 표현되는 이 길이는 예컨대, 1%~1000%의 범위, 바람직하게는 5%~500%의 범위, 더욱 바람직하게는 10%~200%의 범위에서 자유롭게 선택된다.

<62> 개구의 형상은 특별한 제한 없이 선택될 수 있다. 직사각 형상, 정사각형 등의 직선 등으로 둘러싸인 형상, 또는 원형 등의 곡선 등으로 둘러싸인 형상이 될 수 있다. 특히, 원형은 가공에 사용될 레이저빔의 직경에 근접한 직경을 갖는 것이 바람직하다. 이 경우 제거 부분은 고정 제거 면적에 대하여 더 큰 둘레 길이를 가질 수 있다. 개구는 하측을 향하여 확대된 직경 또는 측면을 갖는 것이 바람직하다. 개구의 수와 형상은 도 1, 도 5, 및 도 6에 도시되어 있다.

<63> 소자의 주변부 내외에 있어서의 반도체층의 제거에 의해 노출된 기판면과 반도체층의 측면에는 전반사에 의한 광의 방출을 보강하기 위한 반사막(도시되지 않음)이 형성될 수 있다. 이 반사막은 금속으로 이루어진 반사막, 유전체 다층막을 사용하는 반사막 등의 공지의 반사막이 될 수 있다. 유전체 다층막에 의한 방법에서는  $\text{SiO}_2/\text{TiO}_2$ , 및  $\text{SiO}_2/\text{ZrO}_2$  등의 산화물의 조합이 공지 기술에 속한다. 금속의 고반사막으로서 예컨대, Ag, Pt, Rh, 및 Al 등이 공지 기술에 속한다.

<64> 개구 형성 후 노출된 기판 표면의 중앙부에는 거의 개구의 형상에 따른 가공 마크(107-1)가 형성되는 것이 바람직하다. 이것에 의해서도 광 방출 효율이 향상될 수 있다. 레이저에 의한 가공 중에 기판내에 홈과 같은 단면을 가진 형상으로 가공 마크가 형성된다.

<65> 가공 마크의 존재는 기판 내부의 전반사에 의해 진행하는 광에 대해서도 개구를 기판에 형성하는 동작과 동가이다. 이 가공 마크에 의해 광은 질화물 반도체층의 제거 부분을 통해 방출된다.

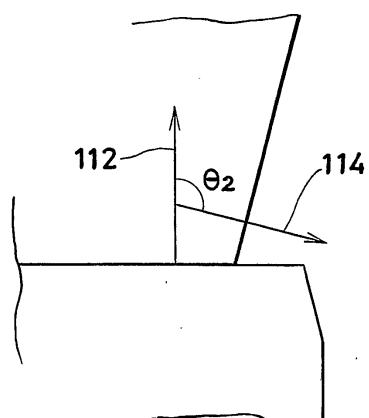

- <66> 본 발명의 질화물 반도체 발광 소자는 그 질화물 반도체층의 측면이 외측을 향하여 기울어져 있는 것이 바람직하다. 이 기울어진 상태가 도 2에 도시되어 있고, 경사부가 도 4에 확대 도시되어 있다. 도 4에 있어서, 112는 기판 표면에 대한 법선을 나타내고, 114는 경사면에 대한 법선을 나타낸다. 이 두 법선에 의해 형성된 각도를  $\Theta_2$ 로 표시한다. 이 각도( $\Theta_2$ )는 상기 각도( $\Theta_1$ )와 마찬가지로  $90^\circ$  보다 크고  $180^\circ$  보다 작은 범위에서 선택될 수도 있다.  $95^\circ$  이상  $170^\circ$  이하의 범위가 바람직하고,  $100^\circ$  이상  $160^\circ$  이하의 범위가 더욱 바람직하다.

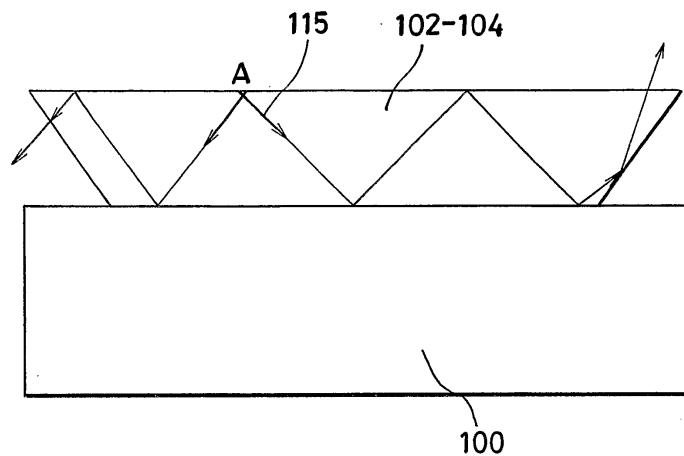

- <67> 반도체층의 측면을 상기한 바와 같이 기울임으로써 광 방출 효율을 향상시킬 수 있다. 이 향상을 위한 이유는 확실하지 않지만 이하의 추측에 의해 설명될 수 있다. 이 추측은 이하에 도 7 및 도 8을 참조하여 설명될 것이다.

- <68> 도 8은 종래 질화물 반도체를 나타낸다. 광이 A점에서 발광하여 화살선과 같이 진행하는 경우 예컨대, 이 광이 임계각보다 큰 각으로 반도체의 측면에 입사하면 광은 입사점에서 반사되고, 반도체층과 기판 사이의 계면상에서도 반사된다. 따라서, 광 방출 효율이 저하된다.

- <69> 이에 대하여, 도 7의 경우에 있어서의 광은 반도체층의 측면상에서 반사되지만 반도체층과 기판 사이의 계면을 통하여 결국 입사각이 임계각 내이기 때문에 소자로부터 방출된다.

- <70> 일반적으로 질화물 반도체는 이종 기판(heterogeneous substrate)상에서 성장시키지만 질화물 반도체와 이종 기판은 굴절률이 상이하다. 층상(層狀)의 물체내에 광이 전파될 때 수직 단면에서는 단면에서의 반사에 의해 광이 물체내로 리턴된다. 본 발명의 경우와 마찬가지로 단면이 경사면이면 경사면은 광의 진행 방향을 변경시키고, 다른 면을 통한 광의 방출에 기여한다.

- <71> 본 발명에서는 동일 방향으로 놓여진 질화물 반도체층과 기판의 측면은 연속면을 형성하지 않는 것이 바람직하다. 본 발명에서는 광이 질화물 반도체층 내에 집중되지만 연속면의 형성이 바람직하지 않은 것은 질화물 반도체층과 기판의 접합면의 외측부에 있어서 도 7과 같이 공간이 생기면 그 개소에서의 굴절률의 변화가 커지고 광이 발광면측으로 복귀되기 쉬워지기 때문이다.

- <72> 본 발명의 III족 질화물 반도체 적층물의 기판을 위해 사파이어 단결정( $\text{Al}_2\text{O}_3$ ; A면, C면, M면, 및 R면), 스페넬 단결정( $\text{MgAl}_2\text{O}_4$ )으로 대표되는 산화물 단결정, 및  $\text{SiC}$  단결정 등의 모든 공자의 기판 재료가 특별한 제한 없이 사용될 수 있다. 상기 열거된 기판 재료 중에서 사파이어 단결정이 특히 유리하다. 사파이어는 질화물 반도체의 굴절률 보다 작은 1.7의 굴절률을 갖는다. 따라서, 광 방출 효율의 향상을 위해 질화물 반도체층 내에 형성된 가공의 효과가 최대로 발휘된다. 또한, 기판의 면 방향은 특별히 한정되지 않는다. 기판은 저스트 기판(just substrate) 또는 오프각(off angle)을 부여한 기판이 될 수 있다. 사파이어 기판의 표면은 미러면(mirror surface) 또는 요철면이 될 수 있다. 요철면의 형성은 에칭 및 레이저 애블레이션(laser ablation) 등의 수단으로 달성될 수 있다.

- <73> 상기 기판상에 제 1 도전형층, 발광층, 및 제 2 도전형층을 포함하는 질화물 반도체층을 구성층에 대하여 최적의 조건하에 적층한다. 본 발명의 질화물 반도체는 일반식  $\text{Al}_x\text{Ga}_{1-x-y}\text{In}_y\text{N}$ ( $0 \leq x, y \leq 1, 0 \leq x+y \leq 1$ )으로 표현된다.

- <74> 질화물 반도체층이 기판상에 적층된 후 음전극을 형성하기 위한 영역과 구성 소자를 분리하기 위한 영역이 공자의 포토리소그래피법에 의해 패터닝된다. 음 전극의 형성을 위한 영역의 배치에 있어서 음 전극의 형성을 위한 영역은 양 전극의 형성을 위한 영역에 대하여 대각의 위치에 있는 것이 바람직하지만 다른 위치가 될 수도 있다. 패터닝은 양 전극의 형성 후에 수행될 수 있다.

- <75> 구성 소자의 분리를 위한 영역은 음 전극과 양 전극을 포함하는 영역을 일반적으로 직사각형으로 범위를 정하는 실시형태로 음 전극 형성용 영역과 동시에 형성된다. 본 발명에 있어서, 질화물 반도체층의 제거는 레이저에 의한 제거와 습식 에칭에 의한 제거의 조합에 의해 이루어지기 때문에 구성 소자의 분리를 위한 영역의 형성은 생략될 수 있다.

- <76> 포토리소그래피법에 의해 패터닝된 기판상의 질화물 반도체층은 건식 에칭에 의해 에칭된다. 이 경우, 에칭에 사용되는 가스의 종류는 일반적으로 염소계 가스가 사용된다. 공자의 염소계 가스는  $\text{Cl}_2$ ,  $\text{SiCl}_4$ , 및  $\text{BCl}_3$ , 그리고  $\text{H}_2$ 와  $\text{Ar}$  등의 가스를 침가하여 혼합한 것을 포함한다. 이것들의 조합을 적절히 선택하여 사용할 수 있다.

- <77> 여기서 논의하는 공정은 플라즈마를 수반하는 공정이다. 따라서, 이 공정은 습식 처리에 앞서 수행되는 것이 바람직하다. 기판에 도달할 때까지 계속되는 레이저에 의한 질화물 반도체층의 제거 공정 전후에 수행될 수도 있

다.

- <78> 음 전극은 다양한 조성 및 구조가 널리 알려져 있다. 모든 공지의 음 전극이 특별한 제한 없이 사용될 수 있다. n 콘택트층에 접하는 음전극용 콘택트 재료로서는 Al, Ti, Ni, 및 Au뿐만 아니라 Cr, W, 및 V가 사용될 수 있다. 음 전극 전체를 다층 구조로 형성하여 본딩 특성을 얻을 수 있다. 특히, 최표면(outermost surface)의 Au 코팅이 본딩 가공을 용이하게 하는데 유리하다.

- <79> 양 전극은 다양한 조성 및 구조가 널리 알려져 있다. 이러한 공지의 양 전극은 특별한 제한 없이 사용될 수 있다.

- <80> 투광성 양 전극 재료는 Pt, Pd, Au, Cr, Ni, Cu, 및 Co 등의 원소를 포함할 수 있다. 일부가 산화된 구조의 재료를 형성함으로써 재료의 투광성의 향상이 가능하다는 것이 알려져 있다.

- <81> 투광성 양 전극 재료는 상기 금속 외에 도전성 산화물이 될 수 있다.  $In_2O_3$ , ITO, ZnO, 및  $SnO_2$  등의 공지의 도전성 산화물이 사용될 수 있다. 상기 금속과 상기 산화물의 조합에 의한 투광성 전극이 될 수 있다.

- <82> 이어서, 레이저 가공 및 습식 에칭에 의한 반도체층의 제거를 설명한다.

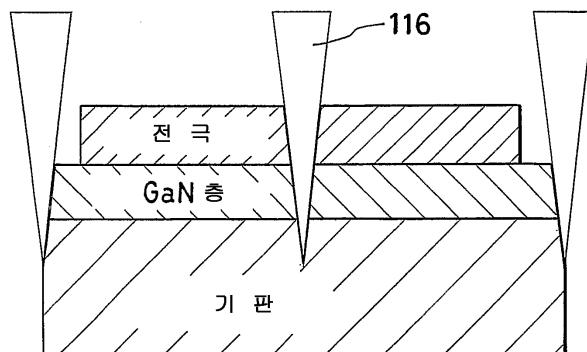

- <83> 도 10은 레이저에 의한 반도체층의 조사를 나타낸 개략 단면도이고, 도 11은 조사에 의해 반도체층이 제거된 소자의 상태를 나타낸 개략 단면도이고, 도 12는 습식 에칭에 의해 반도체층이 제거된 소자의 상태를 나타낸 개략 단면도이다. 도 10에 있어서 116은 레이저 빔을 나타낸다.

- <84> 각 소자가 분할되면 각 소자의 주변부에서 기판이 노출될 필요가 있다. 이를 위해 소자내의 반도체층을 기판에 도달할 때까지 제거한다. 이어서, 주변부 이외의 반도체층에 오목홈을 형성하기 위해 반도체층을 기판에 도달할 때까지 제거한다. 이 제거는 처음에 레이저(도 10 및 도 11)에 의해 수행한다. 이 경우, 레이저는 질화물 반도체의 흡수단(absorption terminal) 보다 짧은 파장을 갖는 것이 바람직하다. 질화물 반도체의 높은 흡수 계수 때문에 가공 위치가 레이저에 의해 조사되는 위치로 한정된다. 레이저용 광학계를 적절히 선택함으로써  $10\mu m$ 보다 좁은 폭으로 가공이 가능하여 소자의 수율이 향상된다.

- <85> 소자의 주변부에서의 질화물 반도체층의 제거 공정에서 기판의 레이저 가공 깊이는  $1\mu m$  이상의 범위에서 임의로 선택될 수 있다. 가공 깊이가 지나치게 작으면 후속 분할 처리에 의해 얻어질 개별 소자의 형상 불량이 발생할 수 있다. 가공 깊이가  $10\mu m$  이상이면 이 불량의 발생이 억제될 수 있다.  $20\mu m$  이상의 가공 깊이가 더욱 유리하다.

- <86> 주변부 이외의 투광성 전극에 접한 질화물 반도체의 일부를 레이저로 제거하는 공정은 주변부의 제거 공정과 동일한 조건, 또는 상이한 조건하에서 수행될 수 있다. 큰 가공 깊이는 후속 분할 처리에서 얻어질 소자 형상의 불량을 야기할 수 있기 때문에 제거 가공량은 주변부에서의 제거 가공량보다 적은 것이 바람직하다. 가공 깊이를 바람직하게는  $10\mu m$  이하로, 더욱 바람직하게는  $5\mu m$  정도로 유지함으로써 분할된 소자 형상에 불량이 발생하는 것을 억제할 수 있다.

- <87> 기판에 도달할 때까지 레이저에 의해 질화물 반도체의 적어도 일부를 제거하는 공정 전에 투광성 전극 또는 질화물 반도체층의 일부를 제거하는 공정이 추가될 수 있다. 이를 위해, 질화물 반도체는 레이저로 제거될 부분을 제외하고 마스킹(masking)되어 제거 영역 이외의 부분이 보호된다. 이 경우, 마스킹되지 않은 영역이 레이저로 제거될 부분보다 커도 문제가 발생하지 않는다. 이 공정은 전극의 형성 전에 개별 소자를 분리하는 공정과 동시에 수행될 수 있다.

- <88> 마스킹을 위해  $SiO_2$  및 레지스트가 사용될 수 있다. 다른 가능한 마스킹 재료로서는 투광성 전극과 질화물 반도체층의 제거 중에 마스크로서 수정되지 않은 형태로 사용될 수 있기 때문에 상기 공정에서 마스킹 동작의 코스에 있어서의 패터닝 동작 중에 사용되는 레지스트가 특히 유리하다. 패터닝을 위해 사용되는 대신에 레이저에 의한 제거 후의 습식 에칭 동작 중에 마스크로서 사용될 수 있다.

- <89> 레이저로 반도체층을 제거한 후 반도체층을 더욱 제거하기 위해 습식 에칭 동작을 수행한다(도 12). 이 습식 에칭은 인산, 황산, KOH 등으로 수행된다. 소정의 가열 장치에 미리 넣어진 비커에 에칭제를 첨가하고  $100^\circ C \sim 400^\circ C$  범위의 온도로 가열한다. 가열 온도가 지나치게 낮으면 에칭 속도가 저하된다. 지나치게 높으면 파 Ying 가열로 인해 에칭면이 거칠게 된다. 바람직하게는  $150^\circ C \sim 300^\circ C$  범위의 온도에서 충분한 에칭 속도와 양호한 에칭면이 얻어진다.

- <90> 에칭된 측면은 에칭 조건에 의해 변화된다. 에칭 온도가 지나치게 낮으면 수직의 에칭된 면이 발달된다. 에칭

온도가 지나치게 높으면 기판을 향한 경사면이 발달된다. 중간 온도 범위에서는 이 두가지 상황이 혼합된 경우가 발생하기 쉽다. 이 경우에 실제로 발생하는 것은 고온에서 발달된 경사면과 수직면 사이의 각도의 경우가 있거나, 측면의 일부에 경사면이 발달하고 나머지 측면에서 수직면일 수 있다. 대부분의 경우에 경사면은 (1-101)의 패시트면(facet plane)으로 나타나지만 그 이외의 경우도 발생할 수 있다. 경사면을 얻기 위한 바람직한 온도 범위는 200°C ~ 300°C이다.

- <91> 오목홈 측면상의 경사면은 전반사에 의한 광의 방출을 유효하게 수행하도록 하는데 유리하다. 전체 측면상에 형성된 경사면이 특히 유리하다. 고온에서의 에칭이 제조된 소자의 특성에 주는 영향이 문제가 될 경우에는 전체 측면상에 경사면이 형성될 필요는 없다.

- <92> 질화물 반도체는 전위를 비롯하여 각종의 결함을 많이 포함하고 있는 것으로 알려져 있다. 습식 에칭 동작의 코스 중에 이러한 결함은 이 에칭에 의해 형성된 면에 오목 결함 또는 볼록 결함을 발생시킬 수 있지만 이러한 상황은 지장은 없다.

- <93> 오목홈과 경사 측면의 저면에서의 전반사에 의해 광의 방출을 보강하기 위해 이 면에 반사막을 형성하는 것이 바람직하다. 이 막을 형성하는 방법으로서 마그네트론 스퍼터(magnetron sputter)에 의한 방법이 특히 유리하다. 다른 수단이 대신 사용될 수 있다. 또한, 반사막으로서 형성된 금속막을 보조 전극으로서 사용할 수 있다.

- <94> 레이저에 의한 제거와 습식 에칭에 의한 제거를 조합시켜서 질화물 반도체층을 기판에 도달할 때까지 제거한 후 시료를 제 2 면으로부터 브레이킹 장치(breaking device)를 사용하여 분리하고, 소자 특성을 평가한다. 다이아몬드에 의한 스크라이빙(scribing) 동작과 브레이킹의 코스 중에 수행되는 다이싱 동작이 조합되어 소자의 주변부에서 기판에 도달할 때까지 가공한 선과 브레이킹의 선이 일치되면 분리 공정시에 소자 형상의 수율 향상에 있어서 유리하다.

- <95> 본 발명의 실시예를 이하에 설명한다.

- <96> <실시예 1>

- <97> 사파이어( $Al_2O_3$ ) C면의 기판 상에 일본 특허 공개 2003-243302호 공보에 개시된 방법에 따라  $AlN$  베퍼를 통해 두께  $6\mu m$ 의 도핑되지 않은  $GaN$ 층,  $Ge$ 를 주기적으로 도핑하여 평균 캐리어 농도가  $1 \times 10^{19} cm^{-3}$ 로 조정된 두께  $4\mu m$ 의 n형 콘택트층,  $In_{0.1}Ga_{0.9}N$ 으로 이루어진 두께  $12.5\mu m$ 의 n형 클래드층,  $GaN$ 으로 이루어진 두께  $16nm$ 의 배리어 층, 및  $In_{0.2}Ga_{0.8}N$ 으로 이루어진 두께  $2.5nm$ 의 웰층(well layer)을 교대로 5회 적층시킨 후 배리어층이 형성된 다중 양자 웰 구조의 발광층 및  $Mg$ 로 도핑되고(농도 :  $8 \times 10^{19} / cm^3$ )  $Al_{0.03}Ga_{0.97}N$ 으로 이루어진 두께  $0.15\mu m$ 의 p 콘택트층을 순차적으로 적층하여 질화물 반도체층을 제조한다.

- <98> 공지의 리소그래피법과 RIE를 사용함으로써 질화물 반도체층의 표면을 통해 각 소자의 경계 부분 및 n형 콘택트 층의 일부를 노출시킨다.

- <99> 화합물 반도체 적층층의 p 콘택트층상의 소정 위치에 공지의 리소그래피법과 리프트-오프법을 사용함으로써 p 콘택트층으로부터 Pt와 Au의 투광성 양 전극이 형성된다. 이어서, 공지의 리소그래피법과 리프트-오프법을 사용함으로써 반도체층으로부터 본딩 패드가 형성된다.

- <100> 각 소자상에 전극을 형성하는 공정이 완료된 후 리소그래피법에 사용된 포토레지스트로 웨이퍼를 코팅한다. 도 1에 도시된 바와 같이, 리소그래피법을 다시 사용하여 소자의 경계 부분과 오목홈 형성 부분을 거의 선형으로 노출시킨다.

- <101> 소자의 경계 부분에서 질화물 반도체층을 기판에 도달할 때까지 제거하기 위한 레이저 가공을 파장  $266nm$ , 주파수  $50kHz$ , 출력  $1.6W$ , 가공 속도  $70mm/\text{초}$ 의 조건하에서 수행한다. 이 조건하에서의 가공에 의해 질화물층이 제거되고 사파이어 기판에  $20\mu m$ 의 깊이에 이르기까지 가공 마크가 형성된다. 스테이지를  $90^\circ$ 의 각도로 회전시킨 후 소자의 경계 부분을 동일 조건하에서 Y축 방향으로 가공한다.

- <102> 투광성 전극부를 펄스 발진(pulse oscillation)에 의해 버스트 모드(burst mode)에서 가공한다. 시료 스테이지를 출력  $1.6W$ , 속도  $30mm/\text{초}$ 의 조건하에서 스캐닝하고, 가공 위치에 일치된 시점으로 레이저를 발진시킨다. 조사부에서는 레이저 빔의 형상으로 투광성 전극과 질화물층을 제거한다. 동일 조건하에서 기판에  $5\mu m$  두께의 가공 마크가 남겨진다.

<103> 질화물 반도체층의 부분적 제거 공정이 종료된 후의 시료를 가열 장치에 의해 180°C로 가열된 오르토 인산 용액 (aqueous orthophosphoric acid solution)이 들어있는 석형 비커에 20분간 담궈서 습식 에칭을 행한다. 이 에칭에 의한 질화물 반도체층의 총 제거량은 5.2 $\mu\text{m}$ 이다. 습식 에칭이 종료된 기판 및 질화물 반도체층을 초음파증에서 물로 세정하고 레지스트로 이루어진 에칭 마스크가 제거될 때까지 유기 세정을 더욱 행한다.

<104> 에칭 처리후의 기판 및 질화물 반도체층을 80 $\mu\text{m}$ 의 두께까지 기판측상에서 연마한다. 그 후, 브레이킹 장치에 의해 각 소자를 분리한다.

<105> 분리된 소자의 출력을 적분구(integrating sphere)로 평가한 경우 이 출력은 7.1mW로 확인되었다. 질화물 반도체층의 소자 표면의 개구부는 100 $\mu\text{m}$ 의 길이와 10 $\mu\text{m}$ 의 폭을 갖는 것에 대해 소자 내부의 기판에 접하는 부분에서 길이가 118 $\mu\text{m}$ 이고 폭이 28 $\mu\text{m}$ 였다.

#### <실시예 2>

<107> 이하, 변경된 조건하에서 얻어진 본 발명의 실시예를 설명한다.

<108> 기판상의 질화물 반도체층의 성장과 전극은 형성을 실시예 1과 마찬가지 방식으로 수행하였다. 전극 형성후의 마스크로서 실시예 1에 비해 에칭 내성을 증가시키기 위해 SiO<sub>2</sub> 마스크를 1000Å 스퍼터에 의해 웨이퍼의 전면에 퇴적한다. 레이저 가공을 실시예 1과 동일 조건하에서 실시하지만 SiO<sub>2</sub> 마스크의 패터닝을 생략하고 레이저에 의한 질화물 반도체층의 제거 공정과 동시에 도 6의 패턴으로 실시한다. 구멍 형성후의 기판을 실시예 1과 동일한 장치내에 180°C에서 20분간 담궈서 습식 에칭을 행한다.

<109> 습식 에칭후의 웨이퍼 표면을 다시 코팅한다. 도 6의 패턴으로 소자 표면에 형성된 구멍의 위치에서 리소그래피 법에 의해 레지스트를 제거한다. 1000Å까지 스퍼터링에 의해 Pt를 퇴적시킴으로써 반사막을 형성하고, 리프트-오프법에 의해 불필요한 부분의 Pt를 제거하여 구멍의 측면에 반사막을 형성한다. 기판 처리와 평가를 실시예 1과 동일 방식으로 실시한다.

<110> 분리된 소자의 출력을 평가한 경우 이 출력은 8.0mW로 확인되었다. 개구부는 직경이 10 $\mu\text{m}$ 이지만 소자 내부의 기판에 접하는 부분에서의 직경은 28 $\mu\text{m}$ 이다.

#### <비교예>

<112> 이하, 비교를 위해 습식 에칭을 생략한 실시예를 설명한다.

<113> 질화물 반도체층의 성장과 제거를 실시예 1 및 실시예 2와 동일 조건하에서 실시한다.

<114> 흠 형성 후, 습식 에칭을 실시하지 않고 각 소자를 분리한다.

<115> 분리된 소자의 출력을 평가한 경우 이 출력은 5.1mW로 확인되었다.

### 산업상 이용 가능성

<116> 본 발명의 질화물 반도체 발광 소자는 발광 다이오드의 고출력화를 위한 형상 가공을 심각한 불량을 발생시키지 않는 습식 에칭에 의해 실시하여 수율 저하를 억제하는 것이 가능하게 한다. 이 발광 다이오드와 형광체를 조합시킴으로써 백색광의 광원을 얻을 수 있고 조명 기구용으로 사용할 수 있다.

### 도면의 간단한 설명

<42> 도 1은 실시예 1에서 제작된 질화물 반도체 발광 다이오드의 평면도이다.

<43> 도 2는 도 1의 II-II 단면도이다.

<44> 도 3은 도 1에 도시된 오목홀의 확대 도면이다.

<45> 도 4는 도 1의 측면에 있어서 기판의 노출면의 확대 도면이다.

<46> 도 5는 다양한 형태의 오목홀을 나타낸 질화물 반도체 발광 다이오드의 평면도이다.

<47> 도 6은 실시예 2에서 형성된 질화물 반도체 발광 다이오드의 평면도이다.

<48> 도 7은 본 발명의 발광 소자에 있어서 광의 진행을 나타낸 설명도이다.

<49> 도 8은 종래 발광 소자에 있어서 광의 진행을 나타낸 설명도이다.

<50> 도 9는 종래 질화물 반도체 발광 다이오드의 평면도이다.

<51> 도 10은 소자를 레이저 가공한 상태를 나타낸 개략 단면도이다.

<52> 도 11은 소자를 레이저 가공한 후의 상태를 나타낸 개략 단면도이다.

<53> 도 12는 소자를 습식 에칭에 의해 가공한 후의 상태를 나타낸 개략 단면도이다.

## 도면

### 도면1

### 도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

레이저 가공

도면11

가공 후

도면12