공개특허 10-2025-0093510

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)(11) 공개번호 10-2025-0093510

(43) 공개일자 2025년06월24일

- (51) 국제특허분류(Int. Cl.)

*H10D 30/67* (2025.01) *H01L 21/02* (2006.01)

*H10D 30/01* (2025.01) *H10D 62/80* (2025.01)

- (52) CPC특허분류

*H10D 30/6755* (2025.01)

*H01L 21/02565* (2013.01)

- (21) 출원번호 10-2025-7015123

- (22) 출원일자(국제) 2023년10월16일

심사청구일자 없음

- (85) 번역문제출일자 2025년05월08일

- (86) 국제출원번호 PCT/IB2023/060395

- (87) 국제공개번호 WO 2024/084366

국제공개일자 2024년04월25일

- (30) 우선권주장

JP-P-2022-168999 2022년10월21일 일본(JP)

JP-P-2022-173106 2022년10월28일 일본(JP)

- (71) 출원인

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

- (72) 발명자

이사카 후미토

일본 243-0036 가나가와Ken 아쓰기시 하세 398 가

부시키가이샤 한도오따이 에네루기 켄큐쇼 내

에기 유지

일본 243-0036 가나가와Ken 아쓰기시 하세 398 가

부시키가이샤 한도오따이 에네루기 켄큐쇼 내

(뒷면에 계속)

- (74) 대리인

장훈

전체 청구항 수 : 총 19 항

(54) 발명의 명칭 반도체 장치 및 기억 장치

### (57) 요약

미세화 또는 고집적화가 가능한 반도체 장치를 제공한다. 상기 반도체 장치에 적합한 산화물 반도체를 제공한다. 제 1 면을 따라 제공된 부분과, 제 1 면에 대하여 경사진 제 2 면을 따라 제공된 부분의 두께의 차이가 작은 산화물 반도체를 형성한다. 알루미늄 함유량이 0.01ppm 이상 500ppm 이하인 전구체를 사용하여 ALD법에 의하여 알루미늄 농도가 0.01 atomic% 이상 10atomic% 이하인 산화물 반도체를 성막한다. 또한 마이크로파 처리 등의 불순물 제거 처리를 수행함으로써 산화물 반도체의 결정성을 높인다.

### 대 표 도

(52) CPC특허분류

*H10D 30/031* (2025.01)

*H10D 30/6757* (2025.01)

*H10D 62/875* (2025.01)

(72) 발명자

**오우노 토시카즈**

일본 243-0036 가나가와켄 아쓰기시 하세 398 가부

시키가이사 한도오따이 에네루기 켄큐쇼 내

**오쿠노 나오카**

일본 243-0036 가나가와켄 아쓰기시 하세 398 가부

시키가이사 한도오따이 에네루기 켄큐쇼 내

**타카하시 히로노부**

일본 243-0036 가나가와켄 아쓰기시 하세 398 가부

시키가이사 한도오따이 에네루기 켄큐쇼 내

---

**쿠니타케 히토시**

일본 194-0032 토쿄토 마치다시 흄마치다 3599-60

**카케하타 테츠야**

일본 243-0036 가나가와켄 아쓰기시 하세 398 가부

시키가이사 한도오따이 에네루기 켄큐쇼 내

## 명세서

### 청구범위

#### 청구항 1

반도체 장치로서,

산화물 반도체, 제 1 도전체, 제 2 도전체, 제 3 도전체, 및 제 1 절연체를 가지고,

상기 제 1 도전체 및 상기 제 2 도전체는 각각 상기 산화물 반도체와 접하는 부분을 가지고,

상기 제 3 도전체는 상기 제 1 절연체를 개재(介在)하여 상기 산화물 반도체와 중첩되고,

상기 산화물 반도체는 제 1 면을 따라 제공된 제 1 부분과, 상기 제 1 면에 대하여 경사진 제 2 면을 따라 제공된 제 2 부분을 가지고,

상기 제 1 부분의 두께에 대한 상기 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고,

상기 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고,

상기 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인, 반도체 장치.

#### 청구항 2

반도체 장치로서,

산화물 반도체, 제 1 도전체, 제 2 도전체, 제 3 도전체, 제 1 절연체, 및 제 2 절연체를 가지고,

상기 제 1 절연체는 상기 제 1 도전체의 상면과 접하고,

상기 제 2 도전체는 상기 제 1 절연체 위에 위치하고,

상기 산화물 반도체는 상기 제 1 도전체의 상면과 접하는 제 1 부분, 상기 제 1 절연체의 측면과 접하는 제 2 부분, 및 상기 제 2 도전체와 접하는 제 3 부분을 가지고,

상기 제 2 절연체는 상기 산화물 반도체 위에 위치하고,

상기 제 3 도전체는 상기 제 2 절연체 위에 위치하고, 상기 제 2 절연체를 개재하여 상기 산화물 반도체와 중첩되고,

상기 제 1 부분의 두께에 대한 상기 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고,

상기 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고,

상기 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인, 반도체 장치.

#### 청구항 3

반도체 장치로서,

산화물 반도체, 제 1 도전체, 제 2 도전체, 제 3 도전체, 제 1 절연체, 및 제 2 절연체를 가지고,

상기 제 1 절연체는 상기 제 1 도전체의 상면과 접하고,

상기 제 2 도전체는 상기 제 1 절연체 위에 위치하고,

상기 제 1 절연체 및 상기 제 2 도전체는 상기 제 1 도전체에 도달하는 제 1 개구부를 가지고,

상기 산화물 반도체는 상기 제 1 개구부의 내측에 상기 제 1 도전체의 상면과 접하는 제 1 부분 및 상기 제 1 절연체의 측면과 접하는 제 2 부분을 가지며, 상기 제 2 도전체와 접하는 제 3 부분을 가지고,

상기 제 2 절연체는 상기 산화물 반도체 위에 위치하고,

상기 제 3 도전체는 상기 제 2 절연체 위에 위치하고, 상기 제 1 개구부와 중첩되는 위치에서 상기 제 2 절연체

를 개재하여 상기 산화물 반도체와 중첩되고,

상기 제 1 부분의 두께에 대한 상기 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고,

상기 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고,

상기 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인, 반도체 장치.

#### 청구항 4

반도체 장치로서,

제 1 절연체와,

상기 제 1 절연체를 덮는 산화물 반도체와,

상기 산화물 반도체 위의 제 1 도전체 및 제 2 도전체와,

상기 제 1 도전체 및 상기 제 2 도전체 위에 배치되고, 상기 제 1 도전체와 상기 제 2 도전체 사이의 영역과 중첩되는 개구를 가지는 제 2 절연체와,

상기 개구 내에 배치되고 상기 산화물 반도체 위에 배치되는 제 3 절연체와,

상기 개구 내에 배치되고 상기 제 3 절연체 위에 배치되는 제 3 도전체를 가지고,

채널 폭 방향의 단면에서 보았을 때 상기 제 1 절연체의 높이는 상기 제 1 절연체의 폭보다 길고,

상기 산화물 반도체는 제 1 면을 따라 제공된 제 1 부분과, 상기 제 1 면에 대하여 경사진 제 2 면을 따라 제공된 제 2 부분을 가지고,

상기 제 1 부분의 두께에 대한 상기 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고,

상기 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고,

상기 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인, 반도체 장치.

#### 청구항 5

제 4 항에 있어서,

평면에서 보았을 때 상기 제 2 절연체의 개구의 측면은 상기 제 1 도전체의 측면 및 상기 제 2 도전체의 측면과 일치 또는 실질적으로 일치하는, 반도체 장치.

#### 청구항 6

제 4 항에 있어서,

상기 제 1 도전체는 트랜지스터의 소스 전극 및 드레인 전극 중 한쪽으로서 기능하고,

상기 제 2 도전체는 상기 트랜지스터의 소스 전극 및 드레인 전극 중 다른 쪽으로서 기능하고,

상기 제 3 도전체는 상기 트랜지스터의 게이트 전극으로서 기능하는, 반도체 장치.

#### 청구항 7

제 6 항에 있어서,

상기 트랜지스터의 채널 폭 방향의 단면에서 보았을 때,

상기 제 1 절연체의 한쪽 측면에서 상기 산화물 반도체와 상기 제 3 도전체가 상기 제 3 절연체를 사이에 두고 마주 보고,

상기 제 1 절연체의 다른 쪽 측면에서 상기 산화물 반도체와 상기 제 3 도전체가 상기 제 3 절연체를 사이에 두고 마주 보는, 반도체 장치.

#### 청구항 8

제 6 항에 있어서,

상기 트랜지스터의 채널 폭 방향의 단면에서 보았을 때,

상기 제 1 도전체는 상기 제 1 절연체의 한쪽 측면 측 및 다른 쪽 측면 측에서 상기 산화물 반도체와 접하고,

상기 제 2 도전체는 상기 제 1 절연체의 한쪽 측면 측 및 다른 쪽 측면 측에서 상기 산화물 반도체와 접하는, 반도체 장치.

### 청구항 9

제 6 항에 있어서,

상기 트랜지스터의 채널 폭 방향의 단면에서 보았을 때 상기 제 1 절연체의 높이는 상기 제 1 절연체의 폭의 2 배 이상 20배 이하인, 반도체 장치.

### 청구항 10

제 1 항 내지 제 9 항 중 어느 한 항에 있어서,

상기 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 5atomic% 이하인, 반도체 장치.

### 청구항 11

제 1 항 내지 제 9 항 중 어느 한 항에 있어서,

상기 산화물 반도체의 탄소 농도는  $1 \times 10^{17}$  atoms/cm<sup>3</sup> 이상  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 이하인, 반도체 장치.

### 청구항 12

기억 장치로서,

제 3 항에 기재된 반도체 장치와, 제 4 도전체와, 제 3 절연체와, 용량 소자를 가지고,

상기 용량 소자는 제 5 도전체와, 상기 제 5 도전체 위의 제 4 절연체와, 상기 제 4 절연체 위의 상기 제 1 도전체를 가지고,

상기 제 3 절연체에는 상기 제 4 도전체에 도달하는 제 2 개구부가 제공되고,

상기 제 5 도전체의 적어도 일부, 상기 제 4 절연체의 적어도 일부, 및 상기 제 1 도전체의 적어도 일부는 상기 제 2 개구부에 배치되는, 기억 장치.

### 청구항 13

기억 장치로서,

제 4 항 내지 제 9 항 중 어느 한 항에 기재된 반도체 장치와, 용량 소자를 가지고,

상기 용량 소자의 한쪽 전극이 상기 반도체 장치의 상기 제 1 도전체와 전기적으로 접속되는, 기억 장치.

### 청구항 14

제 13 항에 있어서,

상기 용량 소자는 상기 제 3 도전체 위에 배치되고,

상기 용량 소자의 적어도 일부는 상기 산화물 반도체 및 상기 제 3 도전체와 중첩되는, 기억 장치.

### 청구항 15

금속 산화물의 성막 방법으로서,

인듐을 포함한 제 1 화합물을 체임버 내에 공급하고 그 후에 산화제를 상기 체임버 내에 공급하는 제 1 공정과,

제 2 화합물을 상기 체임버 내에 공급하고 그 후에 상기 산화제를 상기 체임버 내에 공급하는 제 2 공정을 가지

고,

상기 제 1 화합물의 알루미늄 함유량은 0.01ppm 이상 500ppm 이하이고,

상기 제 2 화합물의 알루미늄 함유량은 상기 제 1 화합물의 알루미늄 함유량보다 적고,

상기 제 2 화합물은 갈륨, 주석, 또는 아연을 포함하는, 금속 산화물의 성막 방법.

### 청구항 16

금속 산화물의 성막 방법으로서,

인듐을 포함한 제 1 화합물을 체임버 내에 공급하고 그 후에 산화제를 상기 체임버 내에 공급하는 제 1 공정과, 제 2 화합물을 상기 체임버 내에 공급하고 그 후에 상기 산화제를 상기 체임버 내에 공급하는 제 2 공정을 가지고,

상기 제 1 화합물의 알루미늄 함유량은 0.01ppm 이상 500ppm 이하이고,

상기 제 2 화합물의 알루미늄 함유량은 상기 제 1 화합물의 알루미늄 함유량보다 적고,

상기 제 1 공정에서의 상기 산화제를 공급하는 시간과 상기 제 2 공정에서의 상기 산화제를 공급하는 시간의 합은 90초 이상인, 금속 산화물의 성막 방법.

### 청구항 17

제 16 항에 있어서,

상기 제 2 화합물은 갈륨 또는 아연을 포함하는, 금속 산화물의 성막 방법.

### 청구항 18

제 15 항 또는 제 16 항에 있어서,

상기 제 1 공정 및 상기 제 2 공정을 각각 한 번 이상 수행하고 그 후에 산소를 포함하는 분위기하에서 마이크로파 처리를 수행하는, 금속 산화물의 성막 방법.

### 청구항 19

제 15 항 또는 제 16 항에 있어서,

상기 제 1 공정 및 상기 제 2 공정을 각각 한 번 이상 수행하고 그 후에 산소를 포함하는 분위기하에서 마이크로파 처리를 수행하는 것을 제 1 사이클로 하여,

상기 제 1 사이클을 여러 번 반복하는, 금속 산화물의 성막 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명의 일 형태는 금속 산화물의 성막 방법에 관한 것이다. 또한 본 발명의 일 형태는 상기 금속 산화물을 가지는 트랜지스터 및 트랜지스터의 제작 방법에 관한 것이다. 또한 본 발명의 일 형태는 상기 금속 산화물을 사용한 반도체 장치 및 반도체 장치의 제작 방법에 관한 것이다. 또한 본 발명의 일 형태는 상기 금속 산화물을 사용한 기억 장치 및 기억 장치의 제작 방법에 관한 것이다.

[0002] 또한 본 발명의 일 형태는 상기 기술분야에 한정되지 않는다. 본 발명의 일 형태의 기술분야의 일례로서는 반도체 장치, 표시 장치, 발광 장치, 축전 장치, 기억 장치, 전자 기기, 조명 장치, 입력 장치(예를 들어 터치 센서), 출력 장치(예를 들어 터치 패널), 이들의 구동 방법, 또는 이들의 제조 방법을 들 수 있다.

[0003] 또한 본 명세서 등에서 반도체 장치란, 반도체 특성을 이용한 장치이고, 반도체 소자(트랜지스터, 다이오드, 포토다이오드 등)를 포함한 회로, 이 회로를 가지는 장치 등을 말한다. 또한 반도체 특성을 이용함으로써 기능할 수 있는 장치 전반을 말한다. 예를 들어 집적 회로, 집적 회로를 가지는 칩, 패키지에 칩을 수납한 전자 부품은 반도체 장치의 일례이다. 또한 기억 장치, 표시 장치, 발광 장치, 조명 장치, 및 전자 기기는 이들 자체가

반도체 장치이며, 각각이 반도체 장치를 가지는 경우가 있다.

## 배경기술

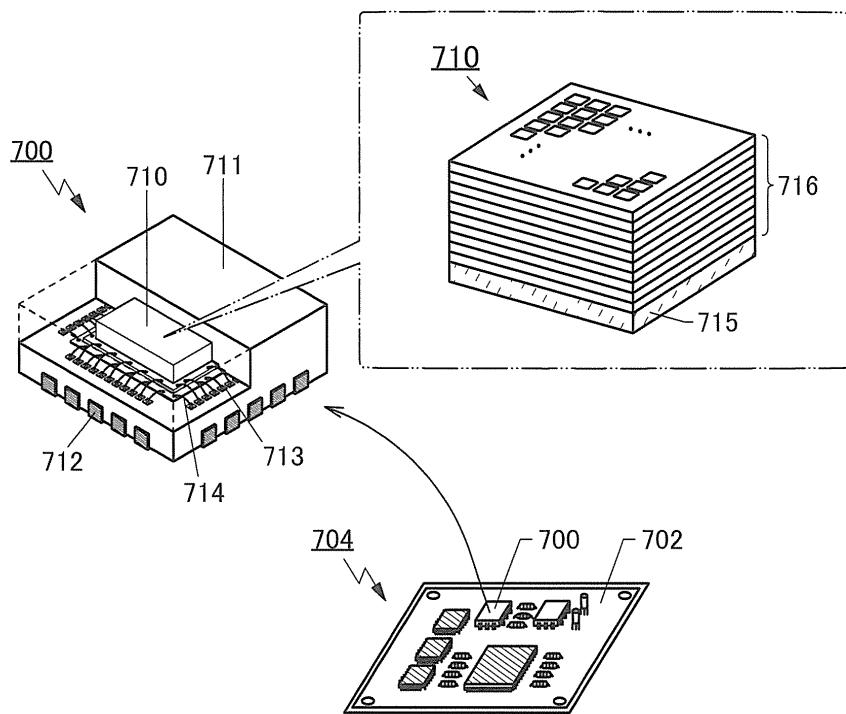

- [0004] 근년, 반도체 장치의 개발이 진행되고 있고, LSI, CPU, 메모리 등이 주로 반도체 장치에 사용되고 있다. CPU는 반도체 웨이퍼를 가공하여 칩으로 형성한 반도체 집적 회로(적어도 트랜지스터 및 메모리)를 가지고, 접속 단자인 전극이 형성된 반도체 소자의 집합체이다.

- [0005] LSI, CPU, 메모리 등의 반도체 회로(IC칩)는 회로 기판, 예를 들어 인쇄 배선 기판에 실장되고, 다양한 전자 기기의 부품 중 하나로서 사용된다.

- [0006] 또한 절연 표면을 가지는 기판 위에 형성된 반도체 박막을 사용하여 트랜지스터를 구성하는 기술이 주목받고 있다. 상기 트랜지스터는 집적 회로(IC)나 표시 장치와 같은 전자 디바이스에 널리 응용되고 있다. 트랜지스터에 적용할 수 있는 반도체 재료로서 실리콘계 반도체 재료가 널리 알려져 있지만, 그 외의 재료로서 산화물 반도체가 주목을 받고 있다.

- [0007] 또한 산화물 반도체를 사용한 트랜지스터는 비도통 상태에서 누설 전류가 매우 낮은 것이 알려져 있다. 예를 들어 특허문헌 1에는 산화물 반도체를 사용한 트랜지스터의 누설 전류가 낮다는 특성을 응용한 소비 전력이 낮은 CPU 등이 개시(開示)되어 있다. 또한 예를 들어 특허문헌 2에는 산화물 반도체를 사용한 트랜지스터의 누설 전류가 낮다는 특성을 응용하여, 장기간에 걸쳐 기억 내용을 유지할 수 있는 기억 장치 등이 개시되어 있다.

- [0008] 또한 근년에는 전자 기기가 소형화, 경량화되면서, 밀도가 더 높아진 집적 회로에 대한 요구가 높아지고 있다. 또한 집적 회로를 포함하는 반도체 장치의 생산성 향상이 요구되고 있다. 예를 들어 특허문헌 3 및 비특허문헌 1에서는 산화물 반도체막을 사용한 제 1 트랜지스터와 산화물 반도체막을 사용한 제 2 트랜지스터를 적층시켜 메모리 셀을 복수로 중첩시켜 제공함으로써 집적 회로의 밀도를 높이는 기술이 개시되어 있다.

- [0009] 또한 트랜지스터를 수직형으로 할 수 있으면, 집적 회로의 밀도를 높일 수 있다. 예를 들어 특허문헌 4에는 산화물 반도체의 측면이 게이트 절연체를 개재(介在)하여 게이트 전극으로 덮인 수직형 트랜지스터가 개시되어 있다.

- [0010] 또한 산화물 반도체에서 단결정도 비정질도 아닌 CAAC(c-axis aligned crystalline) 구조 및 nc(nanocrystalline) 구조가 발견되었다(비특허문헌 2 및 비특허문헌 3 참조).

- [0011] 비특허문헌 2 및 비특허문헌 3에는 CAAC 구조를 가지는 산화물 반도체를 사용하여 트랜지스터를 제작하는 기술이 개시되어 있다.

## 선행기술문헌

### 특허문헌

- [0012] (특허문헌 0001) 일본 공개특허공보 특개2012-257187호

(특허문헌 0002) 일본 공개특허공보 특개2011-151383호

(특허문헌 0003) 국제공개공보 WO2021/053473호

(특허문헌 0004) 일본 공개특허공보 특개2013-211537호

### 비특허문헌

- [0013] (비특허문헌 0001) M. Oota et al., "3D-Stacked CAAC-In-Ga-Zn Oxide FETs with Gate Length of 72nm", IEDM Tech. Dig., 2019, pp.50-53

(비특허문헌 0002) S. Yamazaki et al., "SID Symposium Digest of Technical Papers", 2012, volume 43, issue 1, pp.183-186

(비특허문헌 0003) S. Yamazaki et al., "Japanese Journal of Applied Physics", 2014, volume 53, Number 4S, pp.04ED18-1-04ED18-10

## 발명의 내용

### 해결하려는 과제

[0014]

본 발명의 일 형태는 신규 금속 산화물 및 그 성막 방법을 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 미세화 또는 고집적화가 가능한 트랜지스터, 반도체 장치, 또는 기억 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 신뢰성이 높은 트랜지스터, 반도체 장치, 또는 기억 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 온 전류가 큰 트랜지스터를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 전기 특성이 양호한 트랜지스터를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 소비 전력이 낮은 반도체 장치 또는 기억 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 동작 속도가 빠른 기억 장치를 제공하는 것을 과제 중 하나로 한다. 또는 본 발명의 일 형태는 상기 트랜지스터, 반도체 장치, 또는 기억 장치의 제작 방법을 제공하는 것을 과제 중 하나로 한다.

[0015]

또한 이들 과제의 기재는 다른 과제의 존재를 방해하는 것이 아니다. 본 발명의 일 형태는 이들 과제 모두를 반드시 해결할 필요는 없는 것으로 한다. 명세서, 도면, 청구항의 기재에서 이들 이외의 과제를 추출할 수 있다.

### 과제의 해결 수단

[0016]

본 발명의 일 형태는 산화물 반도체, 제 1 도전체, 제 2 도전체, 제 3 도전체, 및 제 1 절연체를 가지고, 제 1 도전체 및 제 2 도전체는 각각 산화물 반도체와 접하는 부분을 가지고, 제 3 도전체는 제 1 절연체를 개재하여 산화물 반도체와 중첩되고, 산화물 반도체는 제 1 면을 따라 제공된 제 1 부분과, 제 1 면에 대하여 경사진 제 2 면을 따라 제공된 제 2 부분을 가지고, 제 1 부분의 두께에 대한 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고, 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고, 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인 반도체 장치이다.

[0017]

또한 본 발명의 일 형태는 산화물 반도체, 제 1 도전체, 제 2 도전체, 제 3 도전체, 제 1 절연체, 및 제 2 절연체를 가지고, 제 1 절연체는 제 1 도전체의 상면과 접하고, 제 2 도전체는 제 1 절연체 위에 위치하고, 산화물 반도체는 제 1 도전체의 상면과 접하는 제 1 부분, 제 1 절연체의 측면과 접하는 제 2 부분, 및 제 2 도전체와 접하는 제 3 부분을 가지고, 제 2 절연체는 산화물 반도체 위에 위치하고, 제 3 도전체는 제 2 절연체 위에 위치하고, 제 2 절연체를 개재하여 산화물 반도체와 중첩되고, 제 1 부분의 두께에 대한 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고, 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고, 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인 반도체 장치이다.

[0018]

또한 본 발명의 일 형태는 산화물 반도체, 제 1 도전체, 제 2 도전체, 제 3 도전체, 제 1 절연체, 및 제 2 절연체를 가지고, 제 1 절연체는 제 1 도전체의 상면과 접하고, 제 2 도전체는 제 1 절연체 위에 위치하고, 제 1 절연체 및 제 2 도전체는 제 1 도전체에 도달하는 제 1 개구부를 가지고, 산화물 반도체는 제 1 개구부의 내측에 제 1 도전체의 상면과 접하는 제 1 부분 및 제 1 절연체의 측면과 접하는 제 2 부분을 가지며, 제 2 도전체와 접하는 제 3 부분을 가지고, 제 2 절연체는 산화물 반도체 위에 위치하고, 제 3 도전체는 제 2 절연체 위에 위치하고, 제 1 개구부와 중첩되는 위치에서 제 2 절연체를 개재하여 산화물 반도체와 중첩되고, 제 1 부분의 두께에 대한 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고, 산화물 반도체는, 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고, 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인 반도체 장치이다.

[0019]

산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 5atomic% 이하인 것이 바람직하다.

[0020]

산화물 반도체의 탄소 농도는  $1 \times 10^{17} \text{ atoms/cm}^3$  이상  $5 \times 10^{19} \text{ atoms/cm}^3$  이하인 것이 바람직하다.

[0021]

또한 본 발명의 일 형태는 상기 반도체 장치와, 제 4 도전체와, 제 3 절연체와, 용량 소자를 가지고, 용량 소자는 제 5 도전체와, 제 5 도전체 위의 제 4 절연체와, 제 4 절연체 위의 제 1 도전체를 가지고, 제 3 절연체에는 제 4 도전체에 도달하는 제 2 개구부가 제공되고, 제 5 도전체의 적어도 일부, 제 4 절연체의 적어도 일부, 및 제 1 도전체의 적어도 일부는 제 2 개구부에 배치되는 기억 장치이다.

- [0022] 또한 본 발명의 일 형태는 인듐을 포함한 제 1 화합물을 체임버 내에 공급하고 그 후에 산화제를 체임버 내에 공급하는 제 1 공정과, 제 2 화합물을 체임버 내에 공급하고 그 후에 산화제를 체임버 내에 공급하는 제 2 공정을 가지고, 제 1 화합물의 알루미늄 함유량은 0.01ppm 이상 500ppm 이하이고, 제 2 화합물의 알루미늄 함유량은 제 1 화합물의 알루미늄 함유량보다 적고, 제 2 화합물은 갈륨, 주석, 또는 아연을 포함하는 금속 산화물의 성막 방법이다.

- [0023] 또한 본 발명의 일 형태는 인듐을 포함한 제 1 화합물을 체임버 내에 공급하고 그 후에 산화제를 체임버 내에 공급하는 제 1 공정과, 제 2 화합물을 체임버 내에 공급하고 그 후에 산화제를 체임버 내에 공급하는 제 2 공정을 가지고, 제 1 화합물의 알루미늄 함유량은 0.01ppm 이상 500ppm 이하이고, 제 2 화합물의 알루미늄 함유량은 제 1 화합물의 알루미늄 함유량보다 적고, 제 1 공정에서의 산화제를 공급하는 시간과 제 2 공정에서의 산화제를 공급하는 시간의 합은 90초 이상인 금속 산화물의 성막 방법이다.

- [0024] 제 2 화합물은 갈륨 또는 아연을 포함하는 것이 바람직하다.

- [0025] 제 1 공정 및 제 2 공정을 각각 한 번 이상 수행하고 그 후에 산소를 포함하는 분위기하에서 마이크로파 처리를 수행하는 것이 바람직하다.

- [0026] 제 1 공정 및 제 2 공정을 각각 한 번 이상 수행하고 그 후에 산소를 포함하는 분위기하에서 마이크로파 처리를 수행하는 것을 제 1 사이클로 하여, 제 1 사이클을 여러 번 반복하는 것이 바람직하다.

- [0027] 또한 본 발명의 일 형태는 제 1 절연체와, 제 1 절연체를 덮는 산화물 반도체와, 산화물 반도체 위의 제 1 도전체 및 제 2 도전체와, 제 1 도전체 및 제 2 도전체 위에 배치되고, 제 1 도전체와 제 2 도전체 사이의 영역과 중첩되는 개구를 가지는 제 2 절연체와, 개구 내에 배치되고 산화물 반도체 위에 배치되는 제 3 절연체와, 개구 내에 배치되고 제 3 절연체 위에 배치되는 제 3 도전체를 가지고, 채널 폭 방향의 단면에서 보았을 때 제 1 절연체의 높이는 제 1 절연체의 폭보다 길고, 산화물 반도체는 제 1 면을 따라 제공된 제 1 부분과, 제 1 면에 대하여 경사진 제 2 면을 따라 제공된 제 2 부분을 가지고, 제 1 부분의 두께에 대한 제 2 부분의 두께의 비는 0.8 이상 1.2 이하이고, 산화물 반도체는 인듐과, 갈륨, 주석, 및 아연 중에서 선택되는 어느 하나 또는 복수를 포함하고, 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 10atomic% 이하인 반도체 장치이다. 산화물 반도체의 알루미늄 농도는 0.01atomic% 이상 5atomic% 이하인 것이 더 바람직하다. 또한 산화물 반도체의 탄소 농도는  $1 \times 10^{17}$  atoms/cm<sup>3</sup> 이상  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 이하인 것이 바람직하다.

- [0028] 평면에서 보았을 때 제 2 절연체의 개구의 측면은 제 1 도전체의 측면 및 제 2 도전체의 측면과 일치 또는 실질적으로 일치하는 것이 바람직하다.

- [0029] 제 1 도전체는 트랜지스터의 소스 전극 및 드레인 전극 중 한쪽으로서 기능하는 것이 바람직하다. 제 2 도전체는 트랜지스터의 소스 전극 및 드레인 전극 중 다른 쪽으로서 기능하는 것이 바람직하다. 제 3 도전체는 트랜지스터의 게이트 전극으로서 기능하는 것이 바람직하다.

- [0030] 트랜지스터의 채널 폭 방향의 단면에서 보았을 때, 제 1 절연체의 한쪽 측면에서 산화물 반도체와 제 3 도전체가 제 3 절연체를 사이에 두고 마주 보고, 제 1 절연체의 다른 쪽 측면에서 산화물 반도체와 제 3 도전체가 제 3 절연체를 사이에 두고 마주 보는 것이 바람직하다.

- [0031] 트랜지스터의 채널 폭 방향의 단면에서 보았을 때, 제 1 도전체는 제 1 절연체의 한쪽 측면 측 및 다른 쪽 측면 측에서 산화물 반도체와 접하고, 제 2 도전체는 제 1 절연체의 한쪽 측면 측 및 다른 쪽 측면 측에서 산화물 반도체와 접하는 것이 바람직하다.

- [0032] 트랜지스터의 채널 폭 방향의 단면에서 보았을 때 제 1 절연체의 높이는 제 1 절연체의 폭의 2배 이상 20배 이하인 것이 바람직하다.

- [0033] 또한 본 발명의 일 형태는 상기 반도체 장치와 용량 소자를 가지고, 용량 소자의 한쪽 전극이 반도체 장치의 제 1 도전체와 전기적으로 접속되는 기억 장치이다. 용량 소자는 제 3 도전체 위에 배치되는 것이 바람직하다. 용량 소자의 적어도 일부는 산화물 반도체 및 제 3 도전체와 중첩되는 것이 바람직하다.

### 발명의 효과

- [0034] 본 발명의 일 형태에 의하여 신규 금속 산화물 및 그 성막 방법을 제공할 수 있다. 본 발명의 일 형태에 의하여 미세화 또는 고집적화가 가능한 트랜지스터, 반도체 장치, 또는 기억 장치를 제공할 수 있다. 본 발명의 일

형태에 의하여 신뢰성이 높은 트랜지스터, 반도체 장치, 또는 기억 장치를 제공할 수 있다. 본 발명의 일 형태에 의하여 온 전류가 큰 트랜지스터를 제공할 수 있다. 본 발명의 일 형태에 의하여 전기 특성이 양호한 트랜지스터를 제공할 수 있다. 본 발명의 일 형태에 의하여 소비 전력이 낮은 반도체 장치 또는 기억 장치를 제공할 수 있다. 본 발명의 일 형태에 의하여 동작 속도가 빠른 기억 장치를 제공할 수 있다. 본 발명의 일 형태에 의하여 상기 트랜지스터, 반도체 장치, 또는 기억 장치의 제작 방법을 제공할 수 있다.

[0035] 또한 이들 효과의 기재는 다른 효과의 존재를 방해하는 것은 아니다. 본 발명의 일 형태는 반드시 이들 효과 모두를 가질 필요는 없다. 명세서, 도면, 청구항의 기재에서 이들 외의 효과를 추출할 수 있다.

### 도면의 간단한 설명

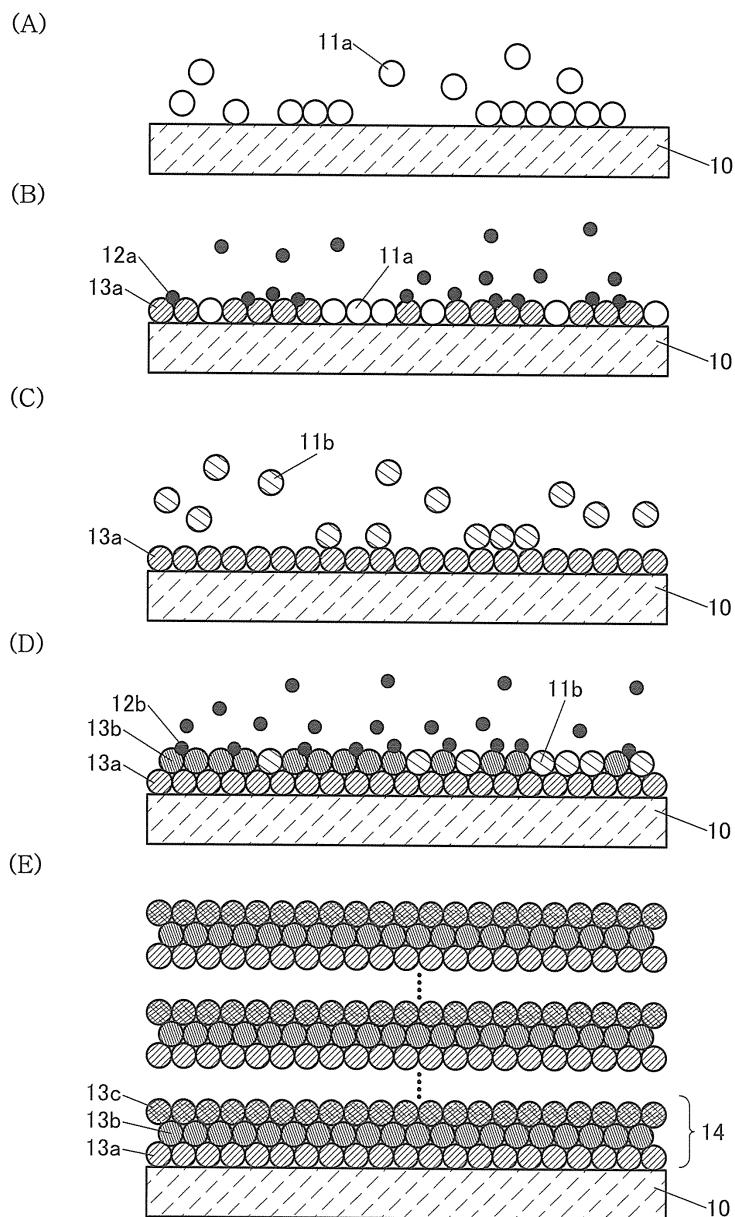

[0036] 도 1의 (A) 내지 (E)는 금속 산화물의 성막 방법의 일례를 나타낸 단면도이다.

도 2의 (A) 내지 (D)는 금속 산화물의 일례를 나타낸 단면도이다.

도 3의 (A) 내지 (D)는 금속 산화물의 일례를 나타낸 단면도이다.

도 4의 (A) 내지 (C)는 금속 산화물의 원자수비의 범위의 일례를 나타낸 도면이다.

도 5의 (A) 내지 (D)는 금속 산화물의 성막 방법의 일례를 나타낸 단면도이다.

도 6의 (A) 내지 (C)는 금속 산화물의 성막 방법의 일례를 나타낸 단면도이다.

도 7은 성막 장치의 일례를 나타낸 평면도 및 단면도이다.

도 8의 (A) 및 (B)는 성막 장치의 일례를 나타낸 단면도이다.

도 9의 (A) 내지 (C)는 성막 장치의 일례를 나타낸 단면도이다.

도 10의 (A) 및 (B)는 성막 장치의 일례를 나타낸 단면도이다.

도 11의 (A) 및 (B)는 금속 산화물의 성막 방법의 일례를 나타낸 도면이다.

도 12의 (A) 및 (B)는 금속 산화물의 성막 방법의 일례를 나타낸 도면이다.

도 13은 금속 산화물의 성막 방법의 일례를 나타낸 도면이다.

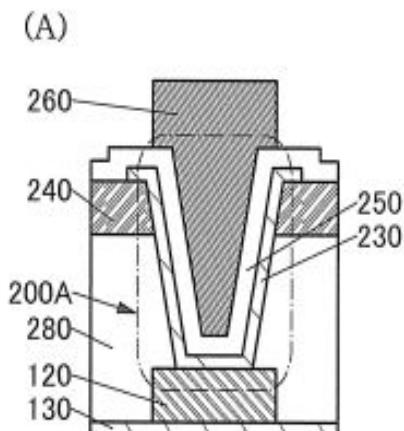

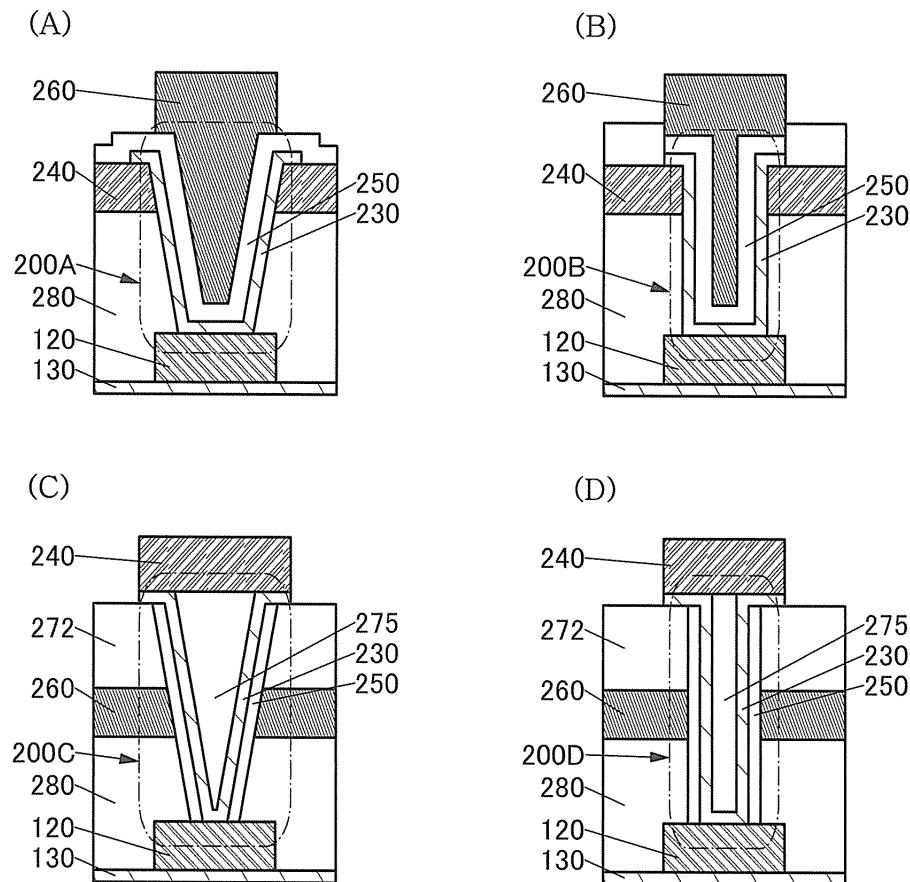

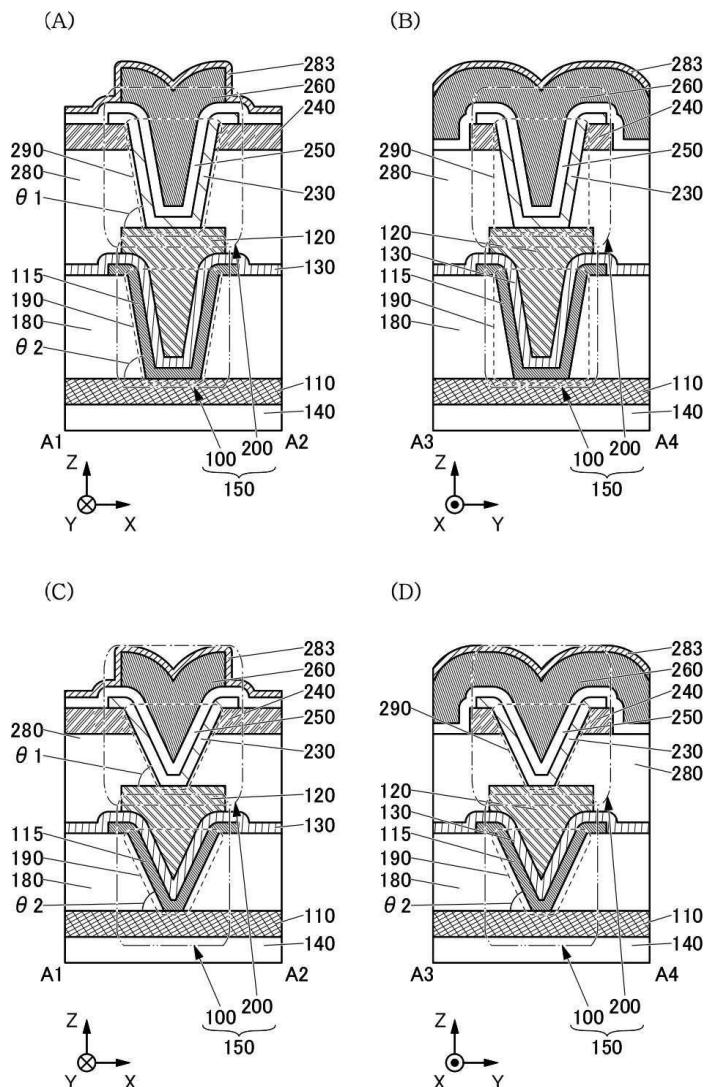

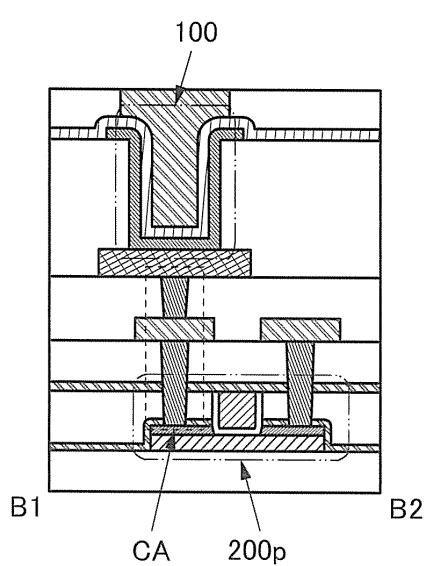

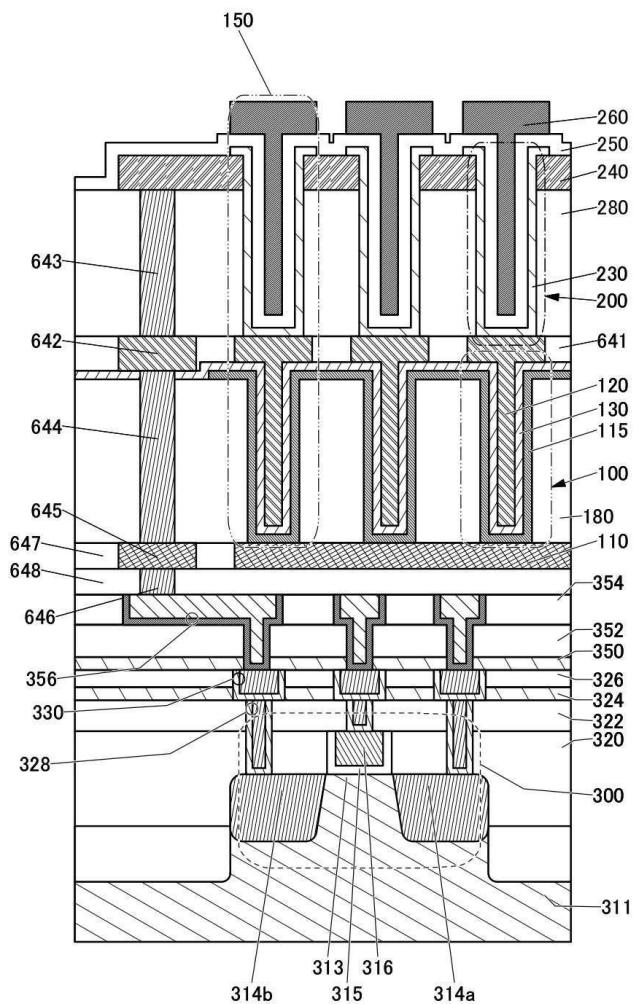

도 14의 (A) 내지 (D)는 기억 장치의 일례를 나타낸 단면도이다.

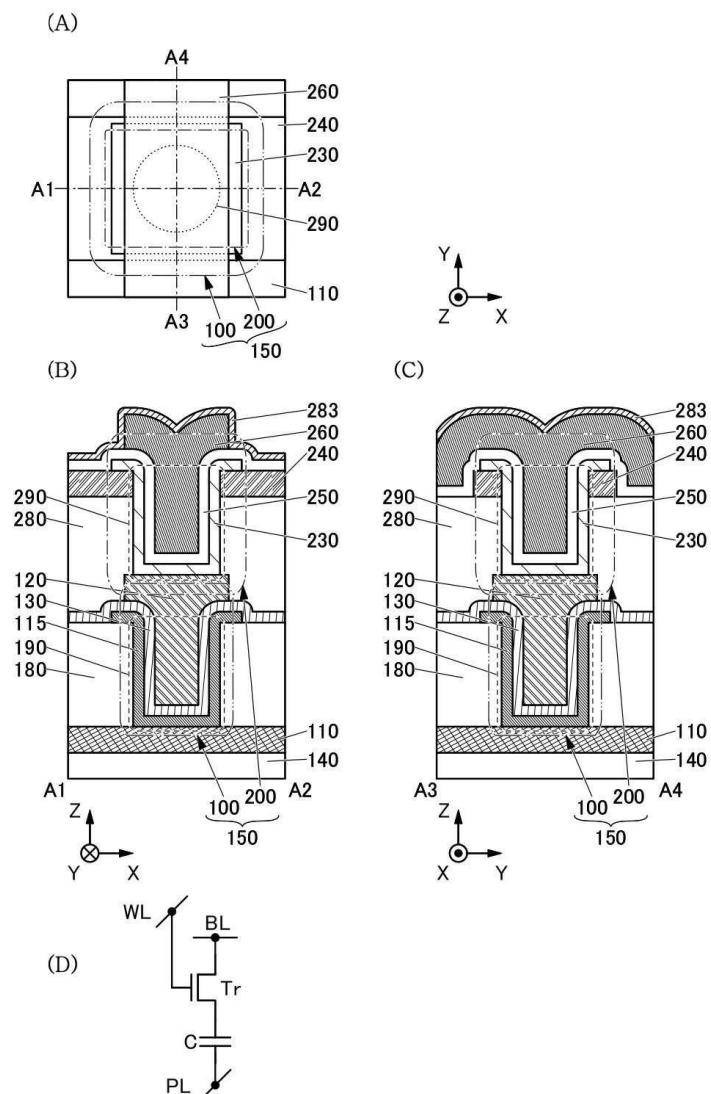

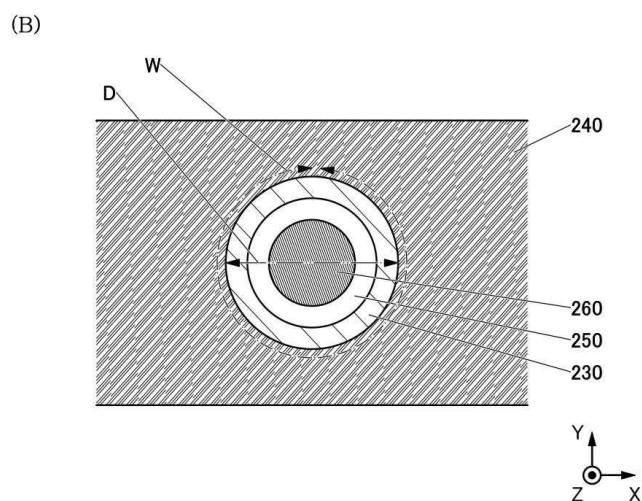

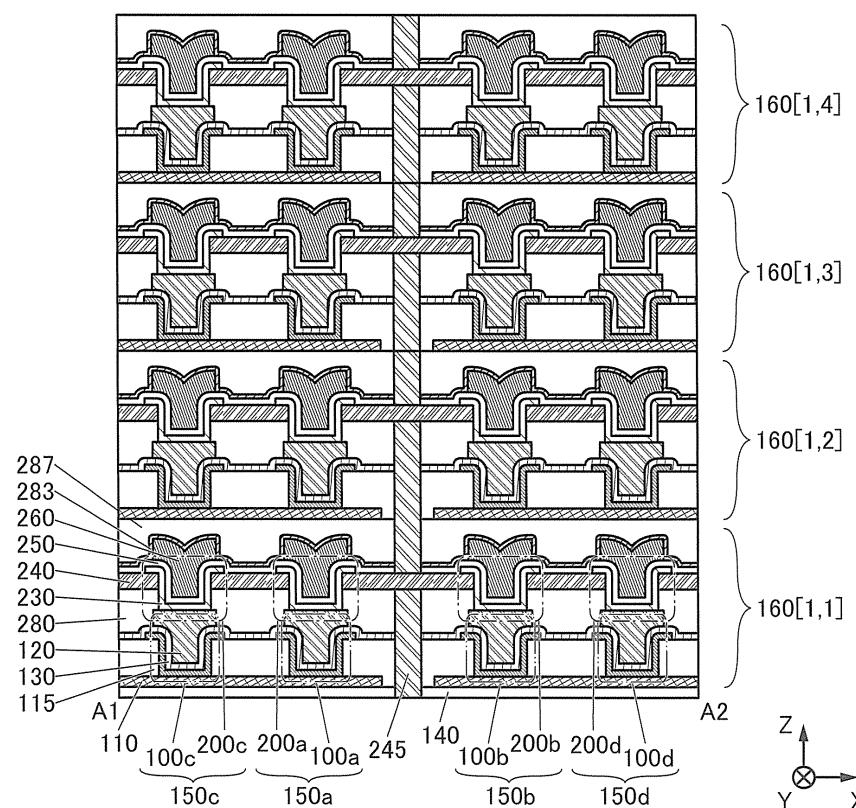

도 15의 (A)는 기억 장치의 일례를 나타낸 평면도이다. 도 15의 (B) 및 (C)는 기억 장치의 일례를 나타낸 단면도이다. 도 15의 (D)는 기억 장치의 일례를 나타낸 회로도이다.

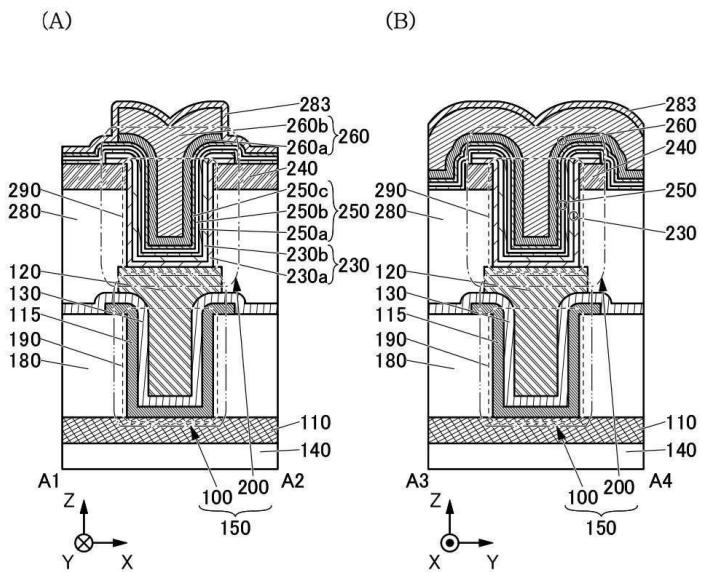

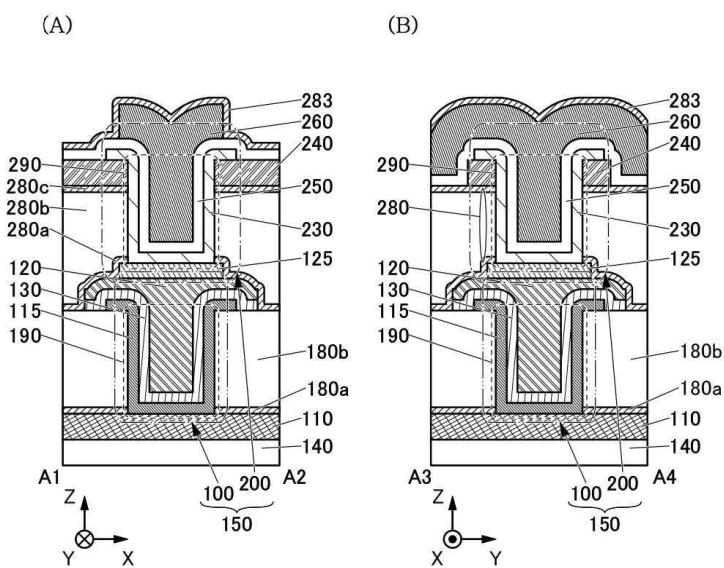

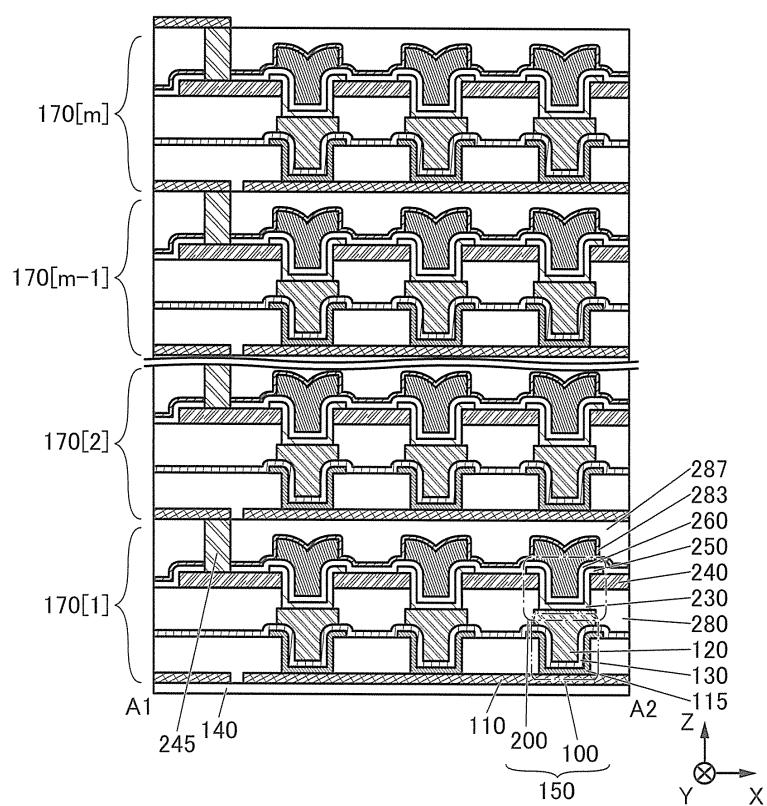

도 16의 (A) 및 (B)는 기억 장치의 일례를 나타낸 단면도이다.

도 17의 (A) 내지 (D)는 기억 장치의 일례를 나타낸 단면도이다.

도 18의 (A) 및 (B)는 기억 장치의 일례를 나타낸 단면도이다.

도 19의 (A) 내지 (D)는 기억 장치의 일례를 나타낸 단면도이다.

도 20의 (A) 및 (B)는 기억 장치의 일례를 나타낸 단면도이다.

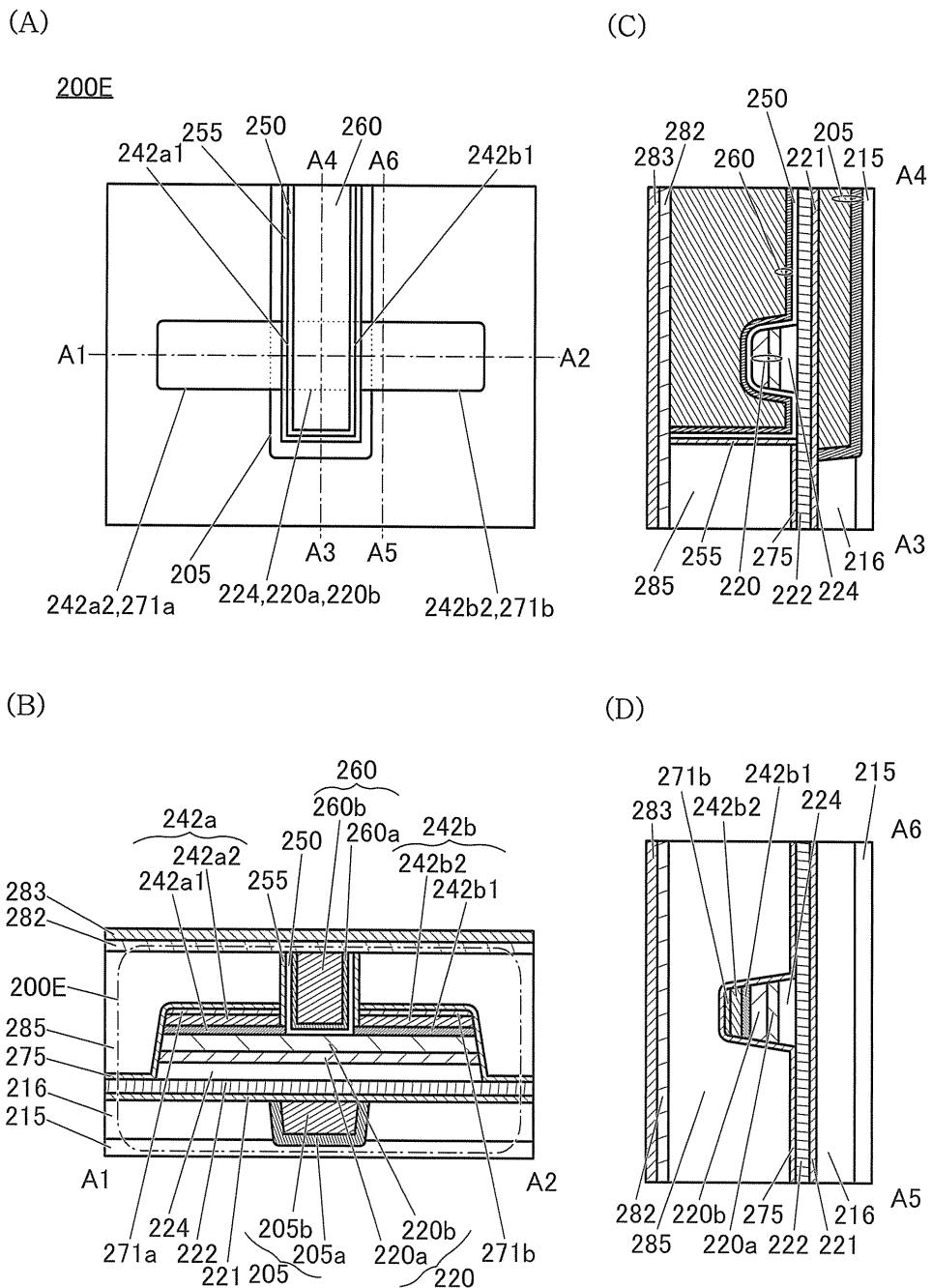

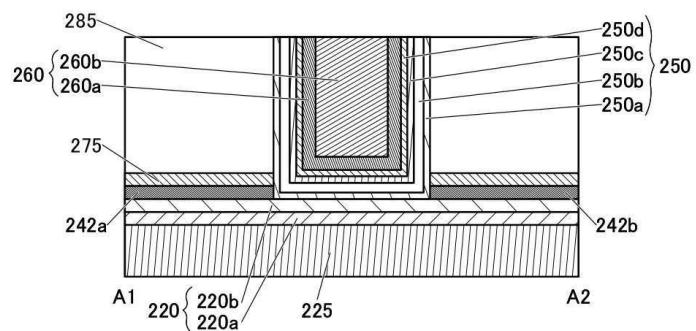

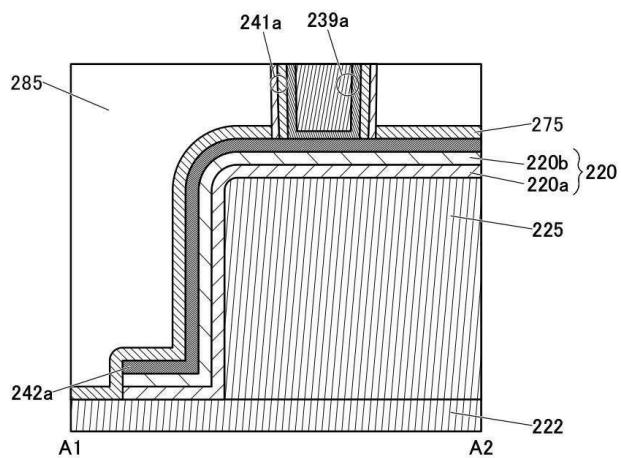

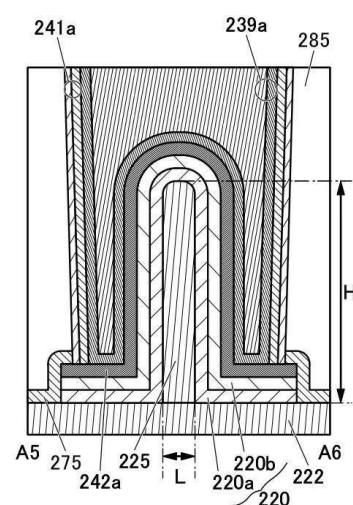

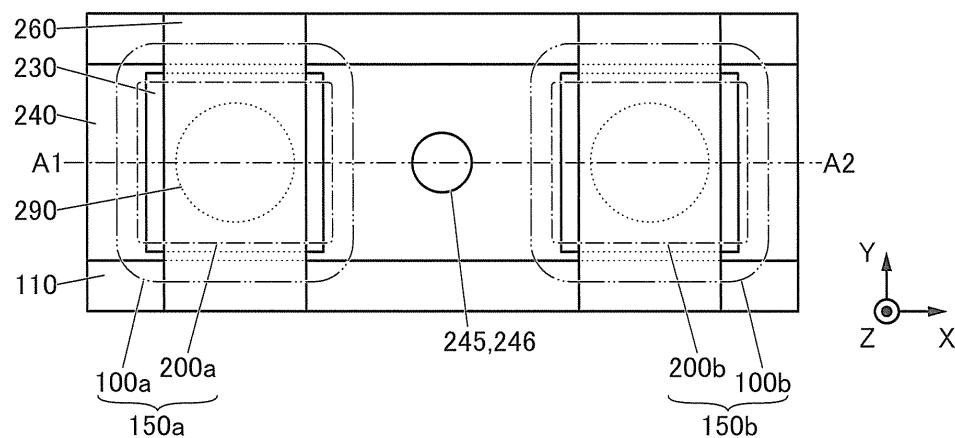

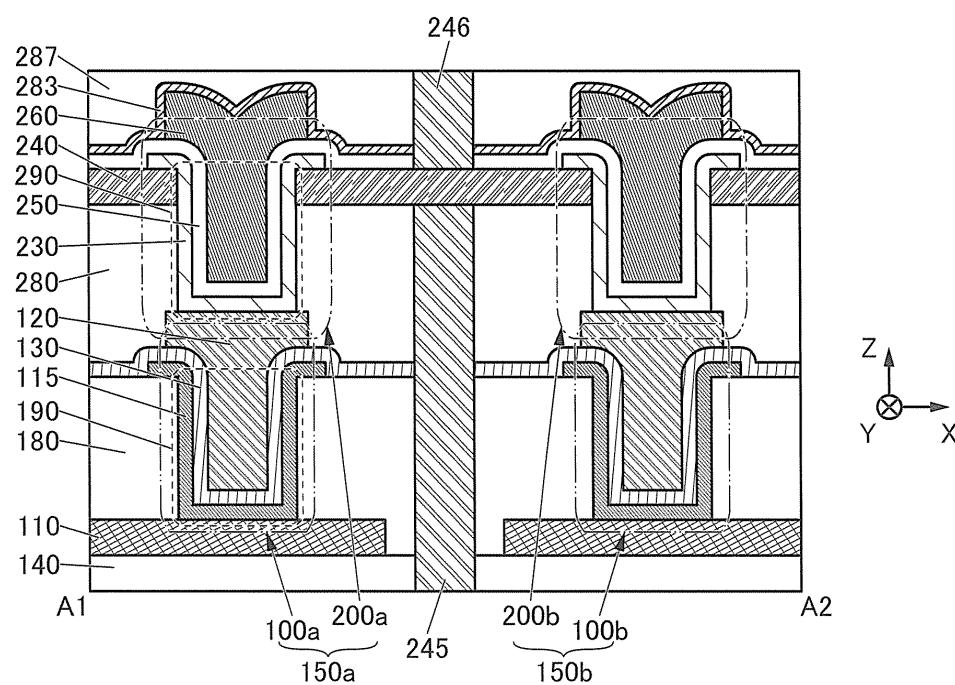

도 21의 (A)는 반도체 장치의 일례를 나타낸 평면도이다. 도 21의 (B) 내지 (D)는 반도체 장치의 일례를 나타낸 단면도이다.

도 22의 (A) 및 (B)는 반도체 장치의 일례를 나타낸 단면도이다.

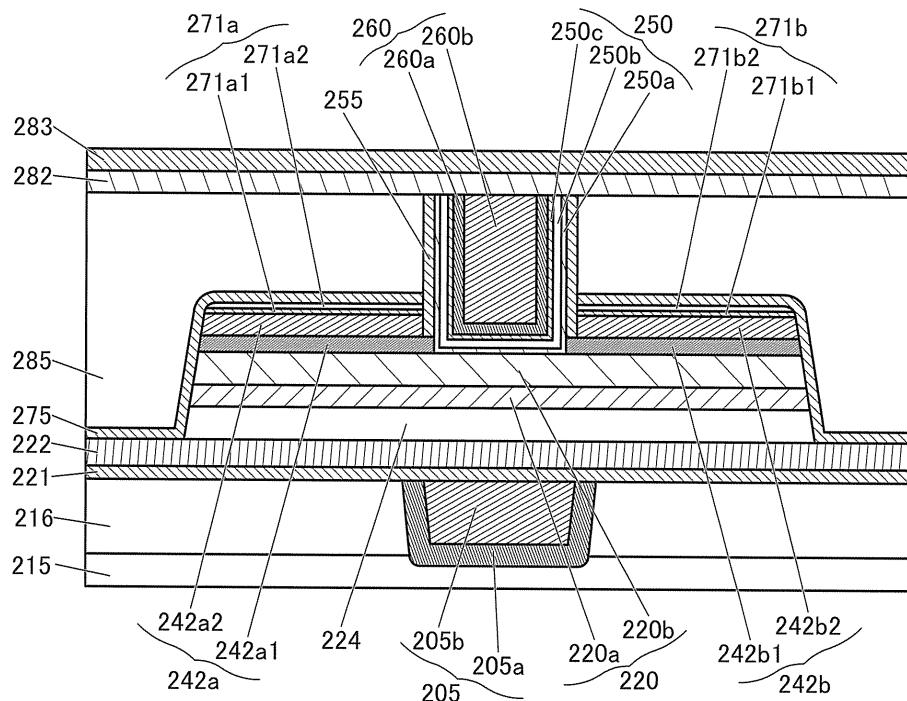

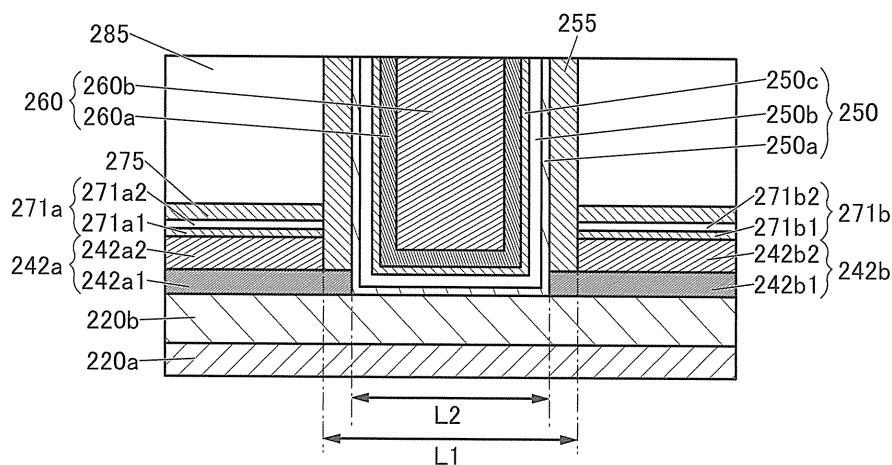

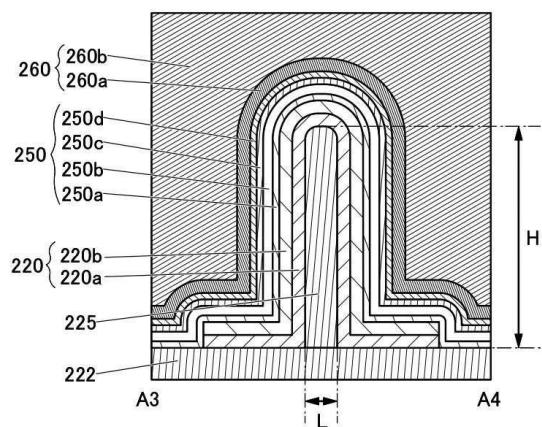

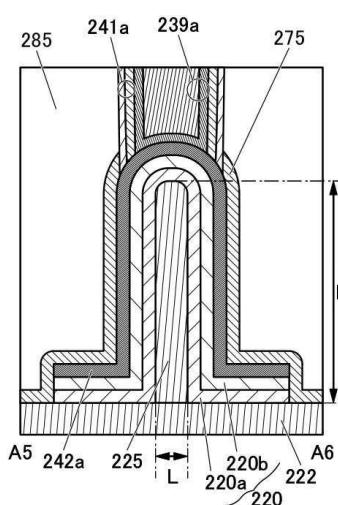

도 23의 (A)는 반도체 장치의 일례를 나타낸 평면도이다. 도 23의 (B) 내지 (D)는 반도체 장치의 일례를 나타낸 단면도이다.

도 24의 (A) 및 (B)는 반도체 장치의 일례를 나타낸 단면도이다.

도 25의 (A) 내지 (C)는 반도체 장치의 일례를 나타낸 단면도이다.

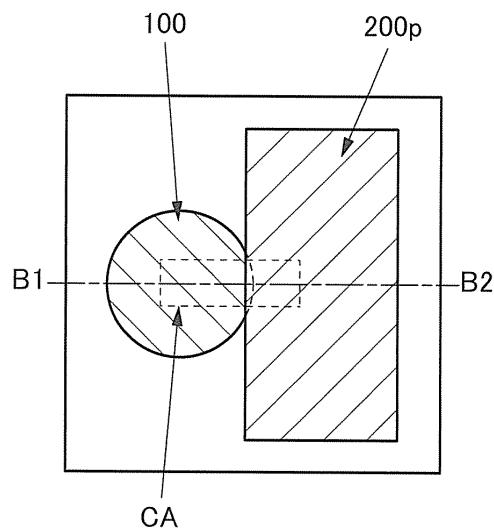

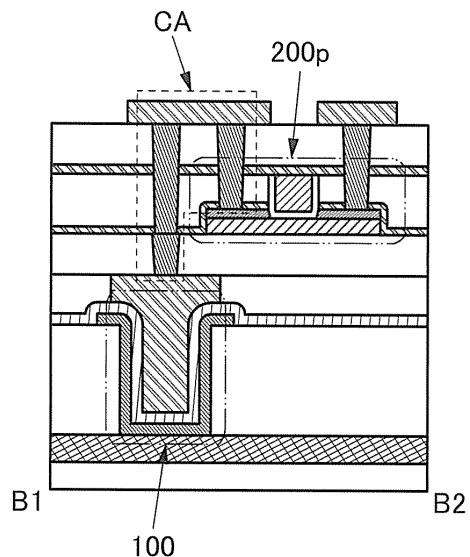

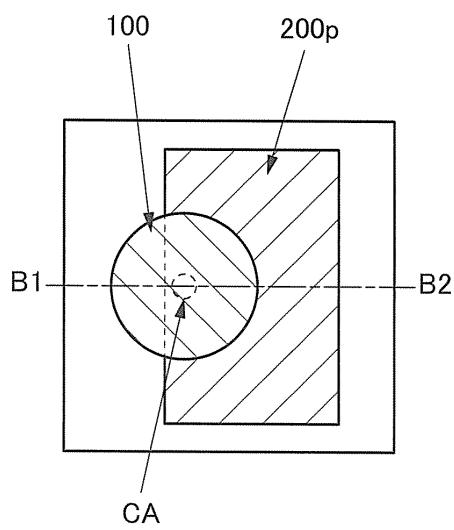

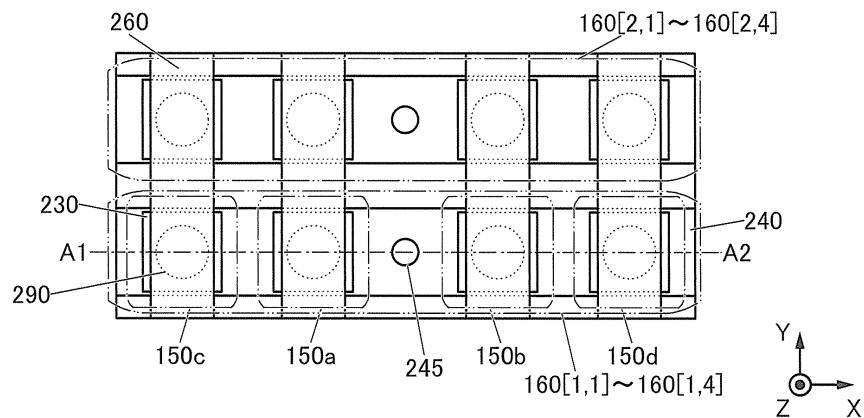

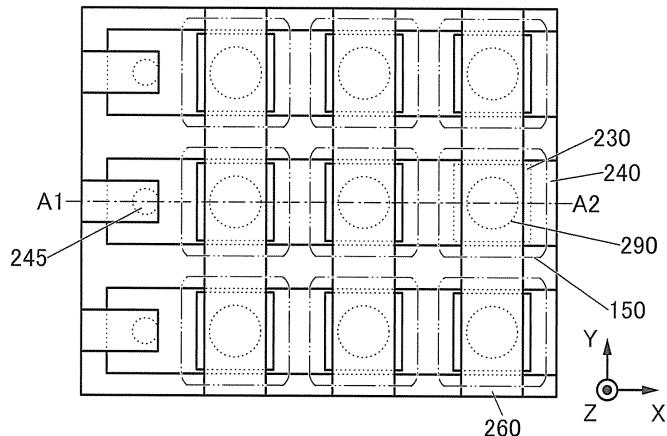

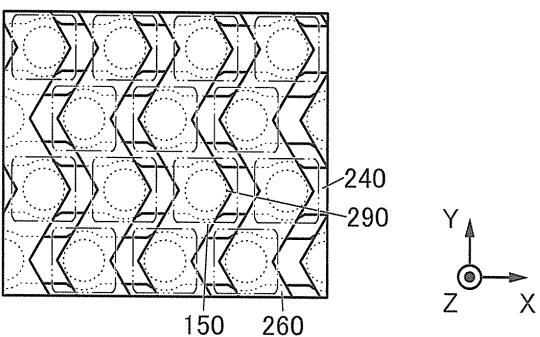

도 26의 (A) 및 (C)는 기억 장치의 일례를 나타낸 평면도이다. 도 26의 (B) 및 (D)는 기억 장치의 일례를 나타낸 단면도이다.

도 27의 (A)는 기억 장치의 일례를 나타낸 평면도이다. 도 27의 (B)는 기억 장치의 일례를 나타낸 단면도이다.

도 28의 (A)는 기억 장치의 일례를 나타낸 평면도이다. 도 28의 (B)는 기억 장치의 일례를 나타낸 단면도이다.

도 29의 (A)는 기억 장치의 일례를 나타낸 평면도이다. 도 29의 (B)는 기억 장치의 일례를 나타낸 단면도이다.

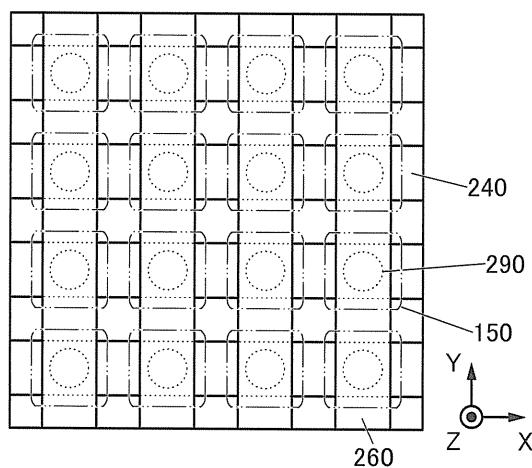

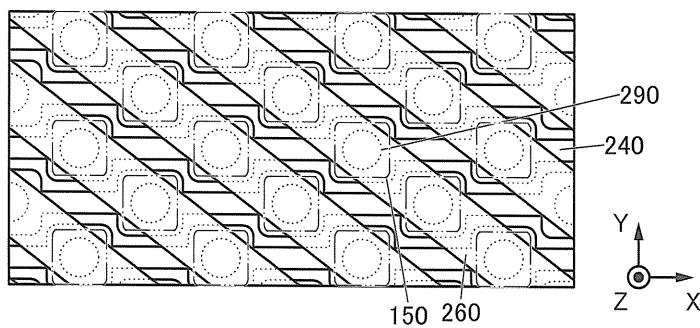

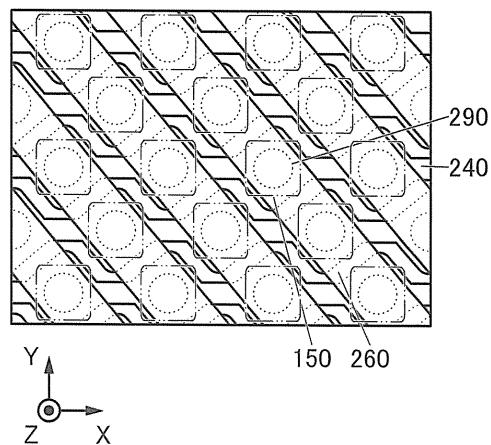

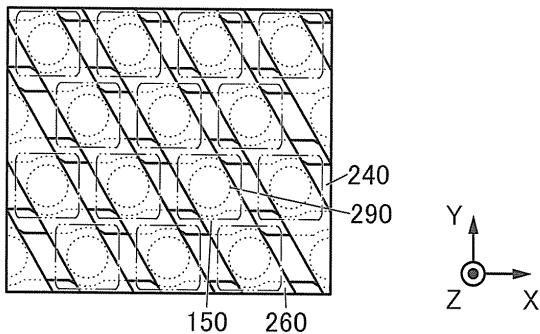

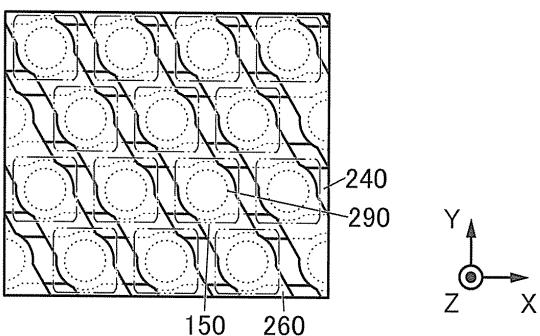

도 30의 (A) 내지 (C)는 기억 장치의 일례를 나타낸 평면 레이아웃을 나타낸 것이다.

도 31의 (A) 내지 (C)는 기억 장치의 일례를 나타낸 평면 레이아웃을 나타낸 것이다.

도 32는 기억 장치의 일례를 나타낸 단면도이다.

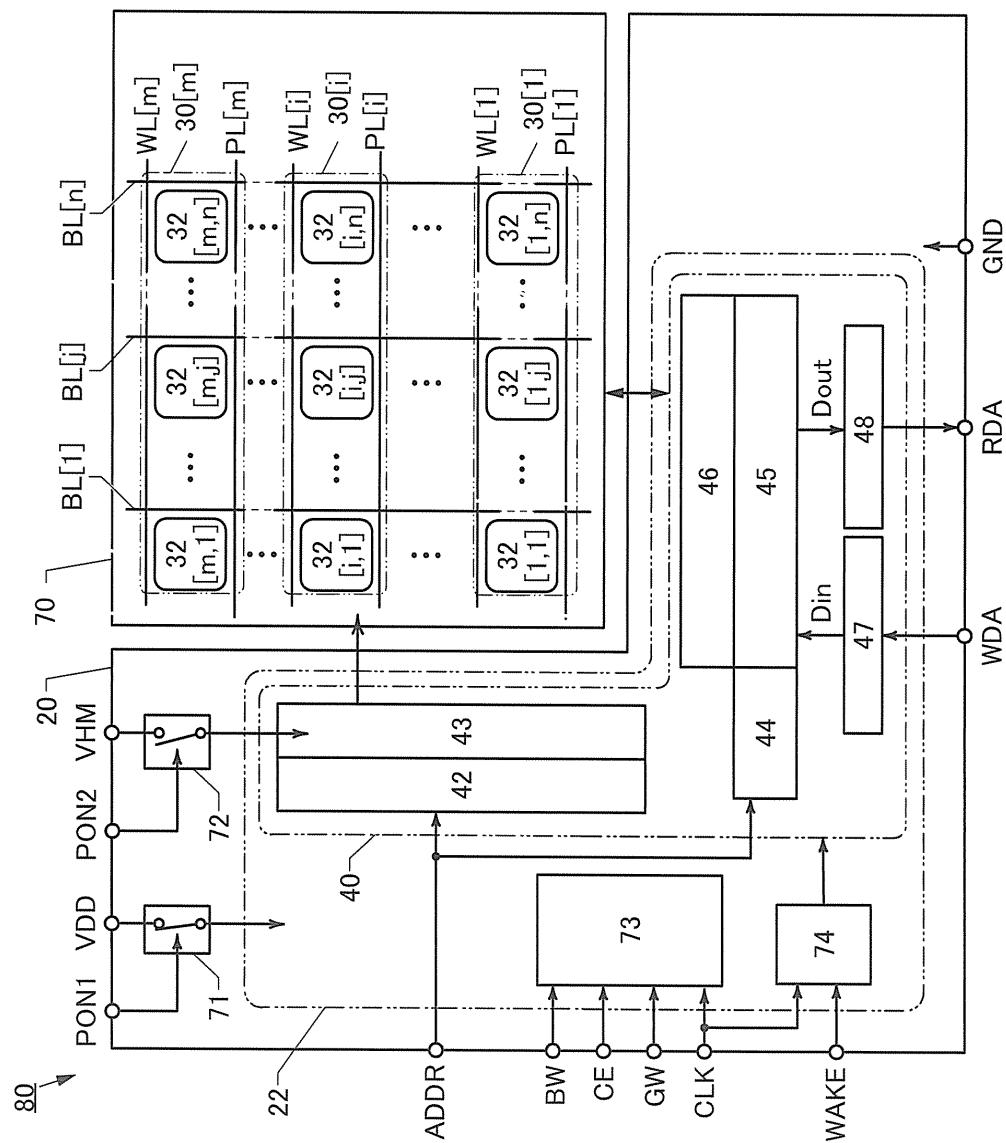

도 33은 기억 장치의 일례를 나타낸 블록도이다.

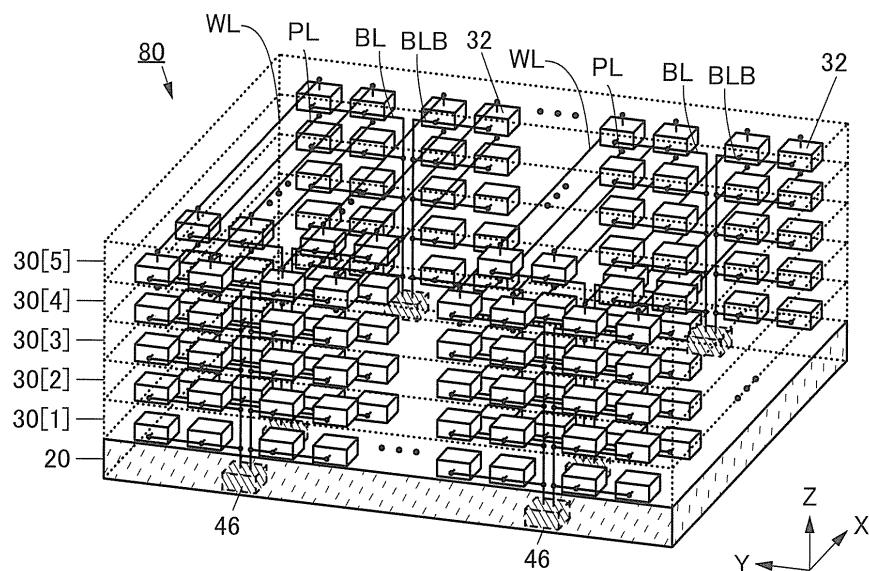

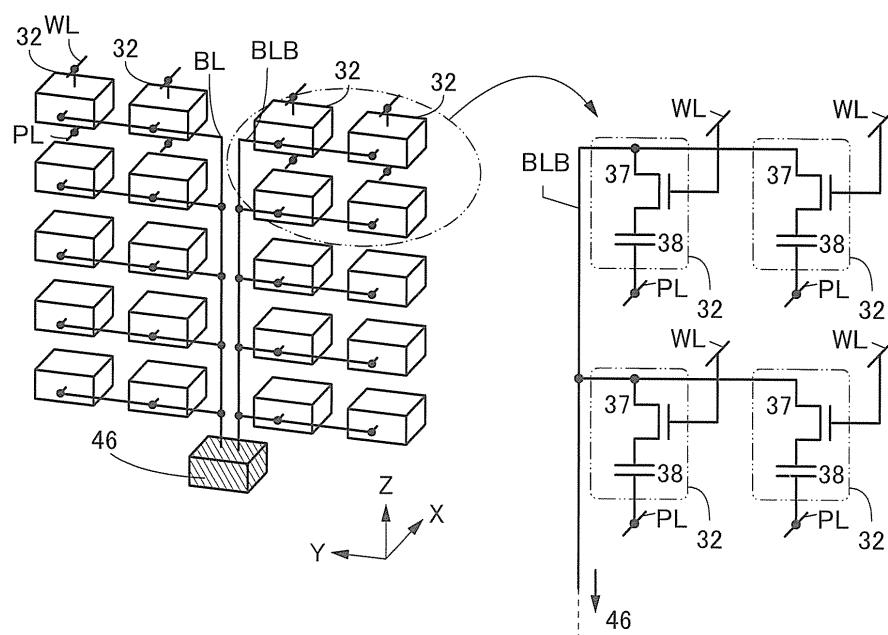

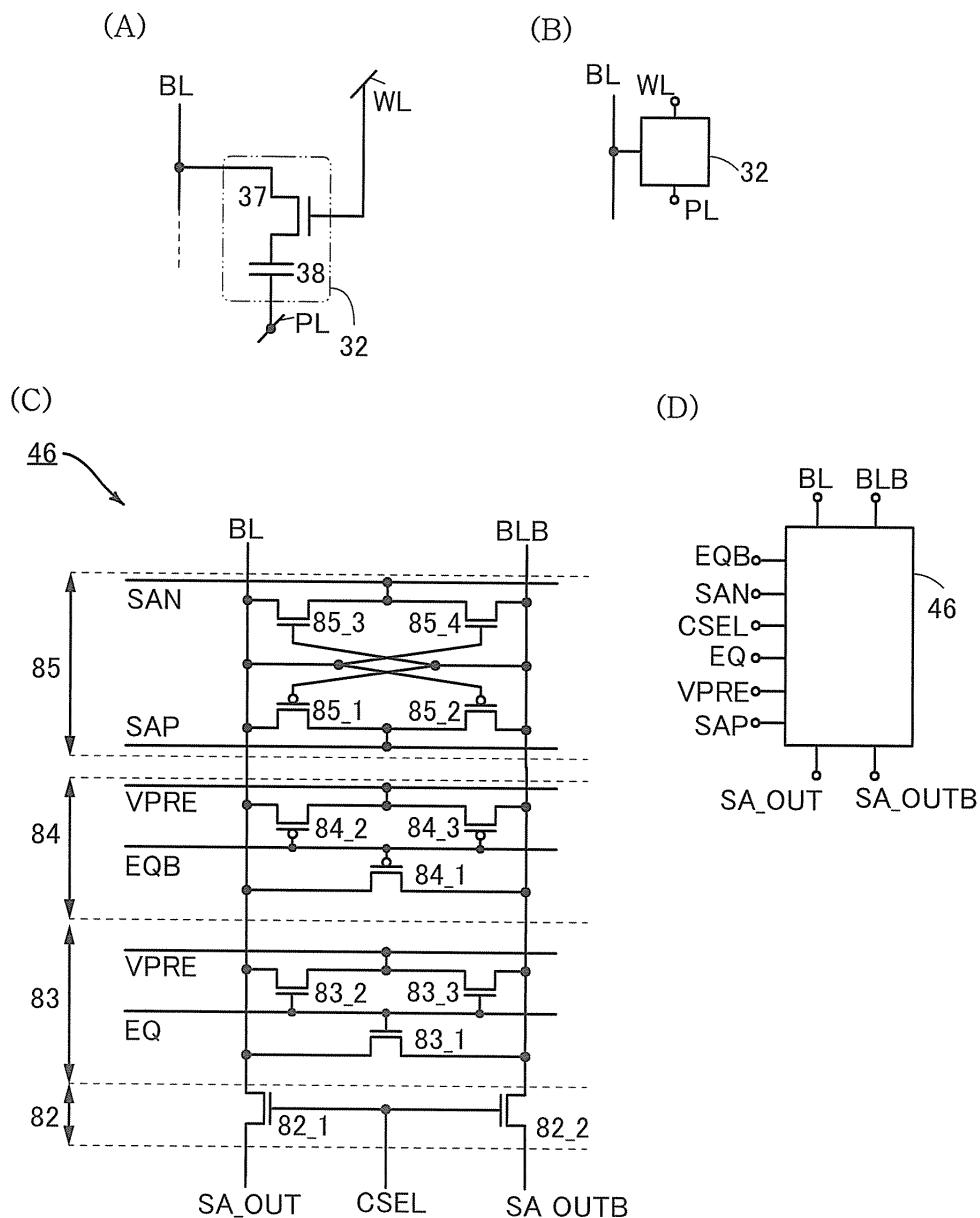

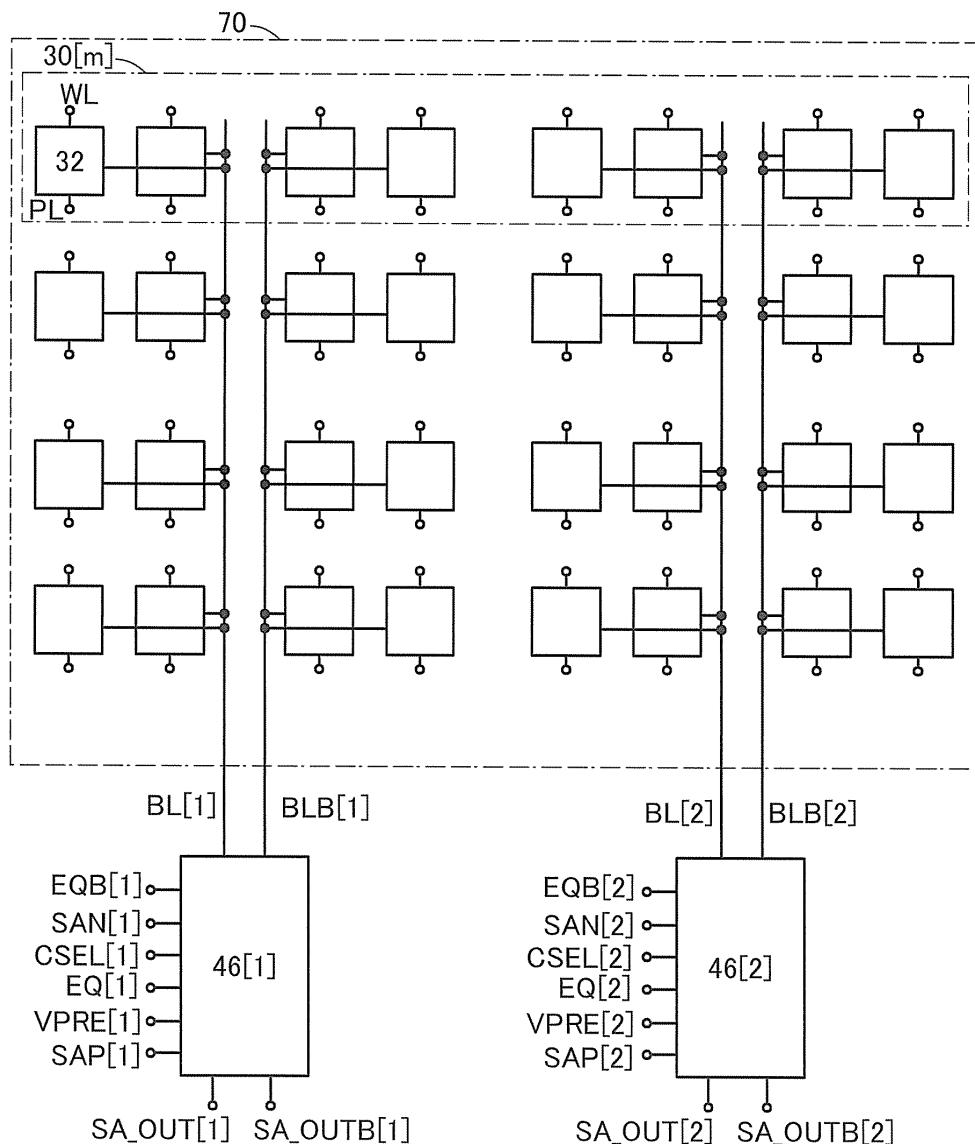

도 34의 (A) 및 (B)는 기억 장치의 일례를 나타낸 모식도이다.

도 35의 (A) 내지 (D)는 기억 장치의 일례를 나타낸 회로도이다.

도 36은 기억 장치의 일례를 나타낸 회로도이다.

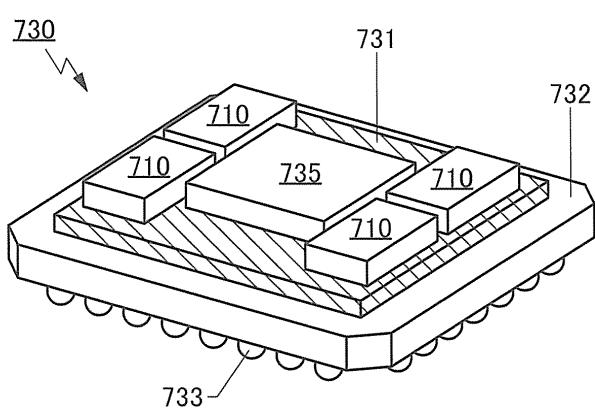

도 37의 (A) 및 (B)는 전자 부품의 일례를 나타낸 도면이다.

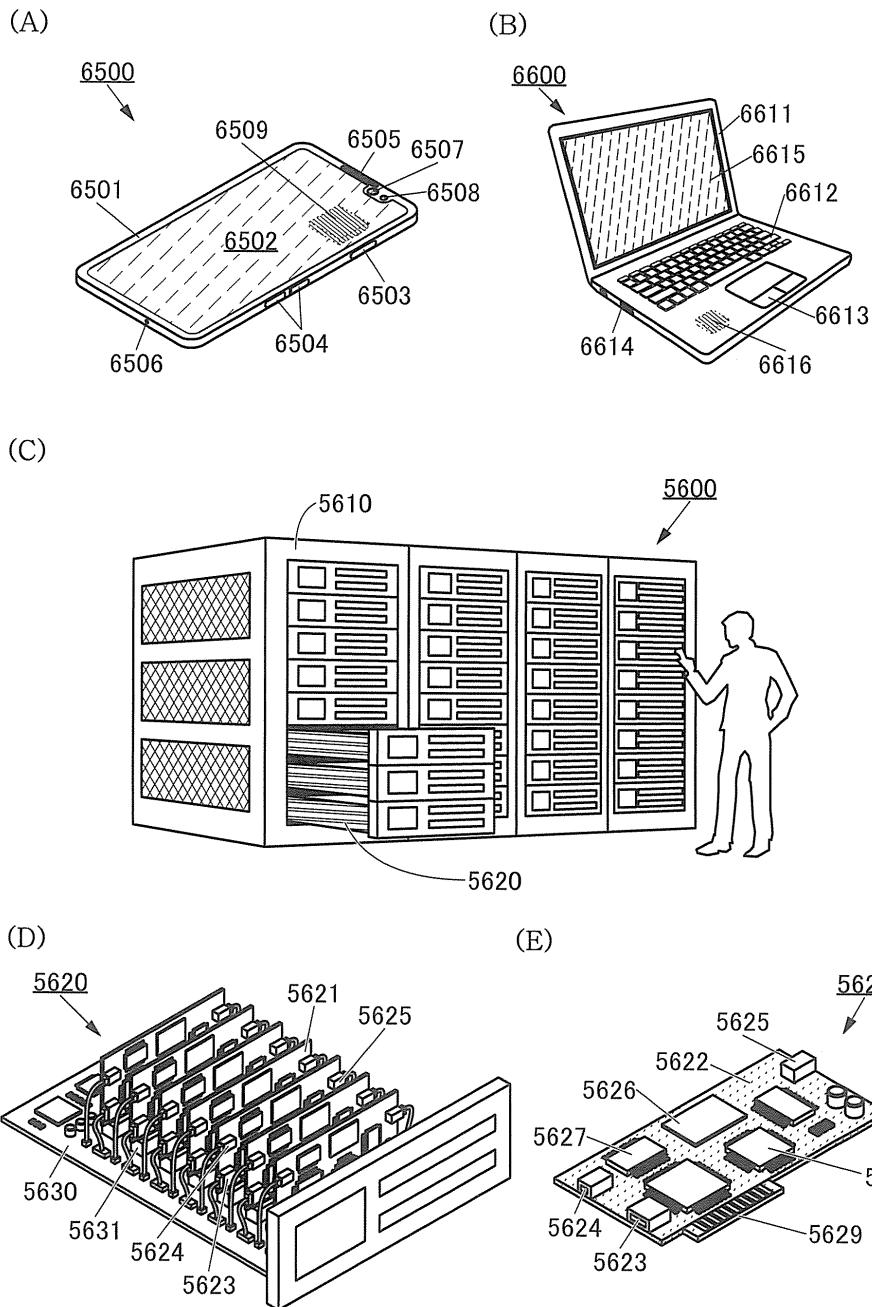

도 38의 (A) 및 (B)는 전자 기기의 일례를 나타낸 도면이다. 도 38의 (C) 내지 (E)는 대형 컴퓨터의 일례를 나타낸 도면이다.

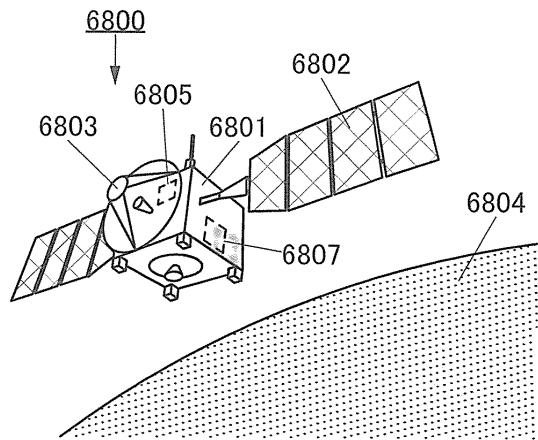

도 39는 우주용 기기의 일례를 나타낸 도면이다.

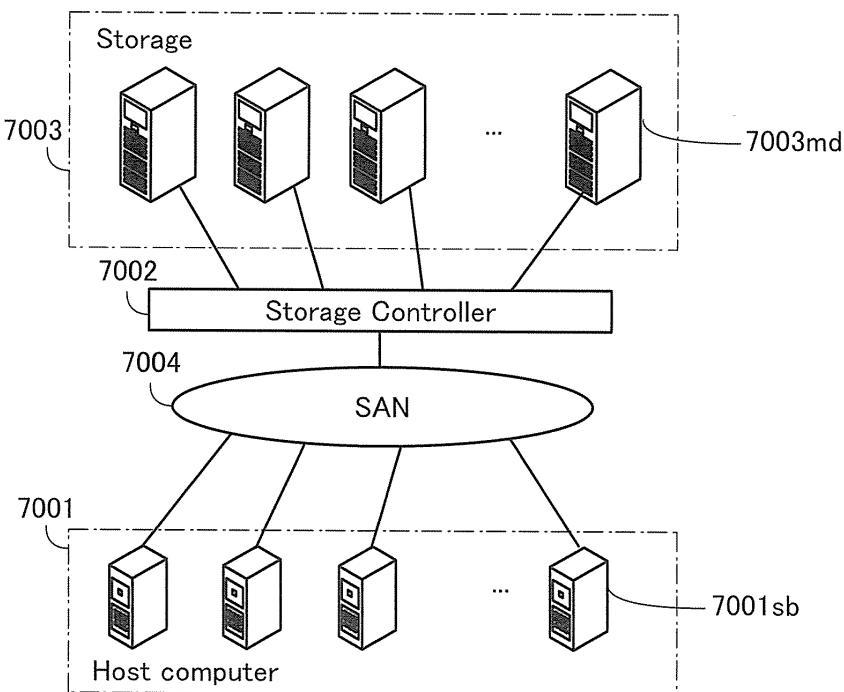

도 40은 데이터 센터에 적용할 수 있는 스토리지 시스템의 일례를 나타낸 도면이다.

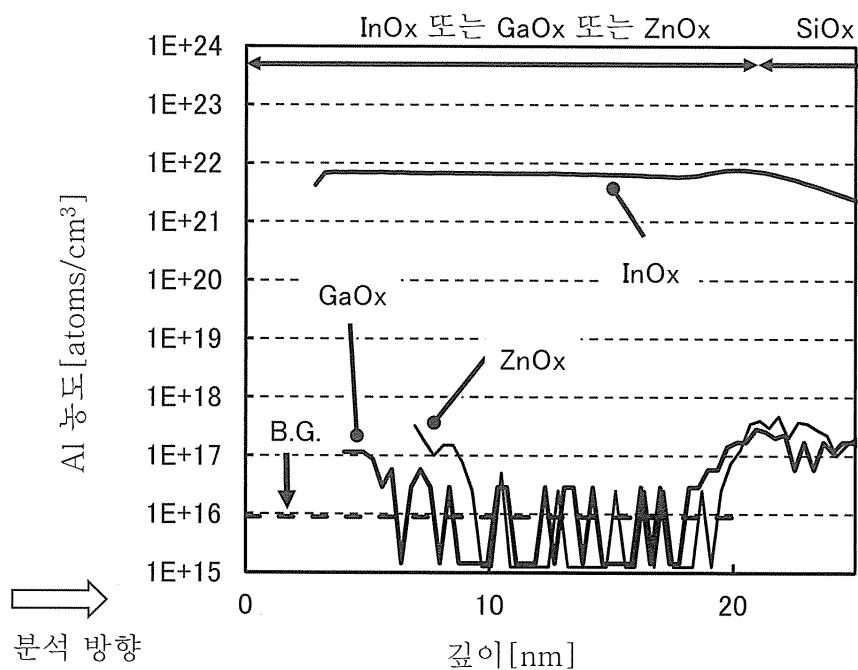

도 41은 실시예 1의 XPS 분석의 결과를 나타낸 도면이다.

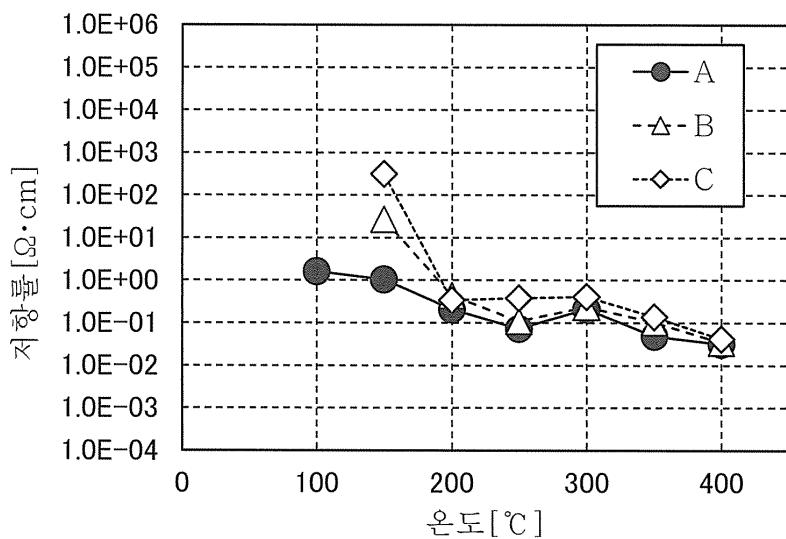

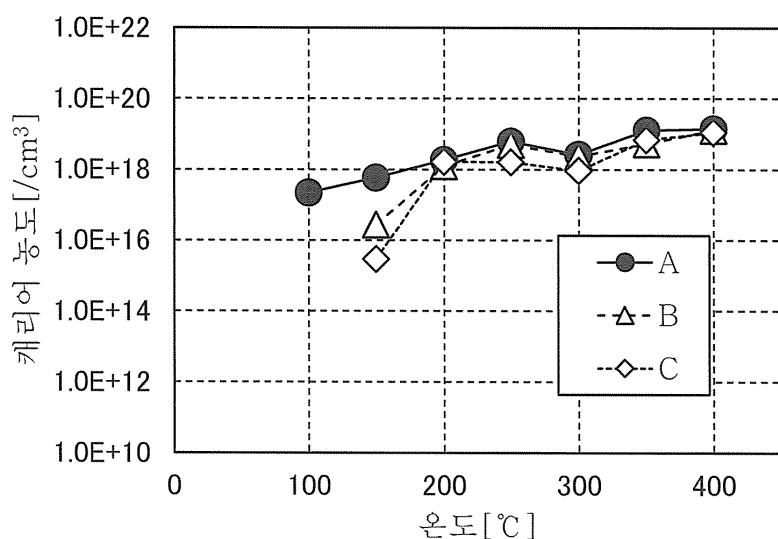

도 42의 (A) 및 (B)는 실시예 1의 홀(Hall) 효과 측정의 결과를 나타낸 도면이다.

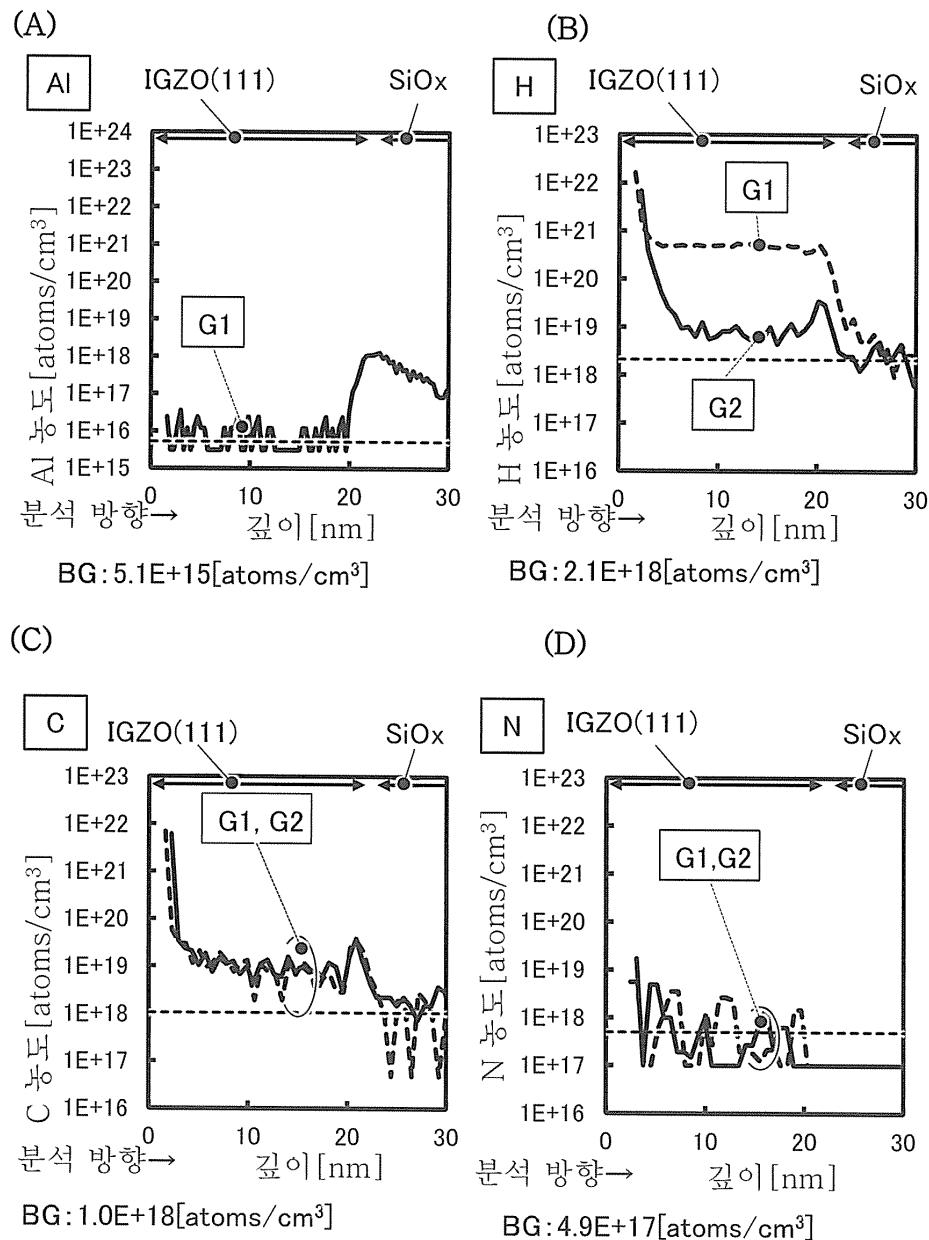

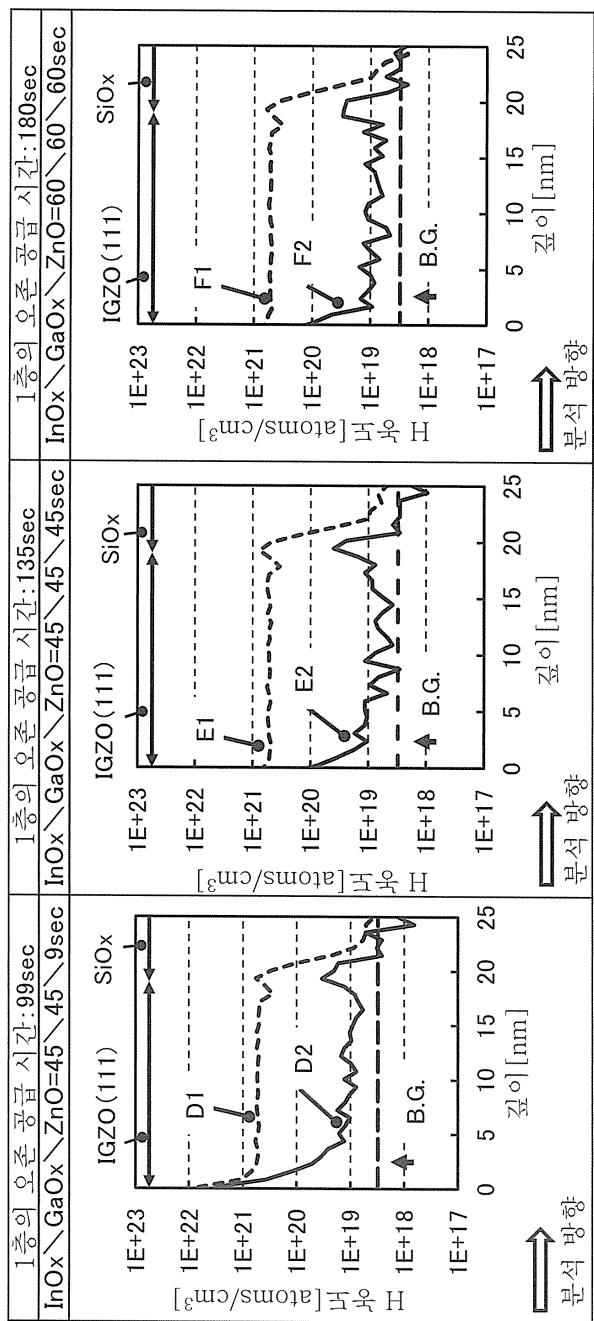

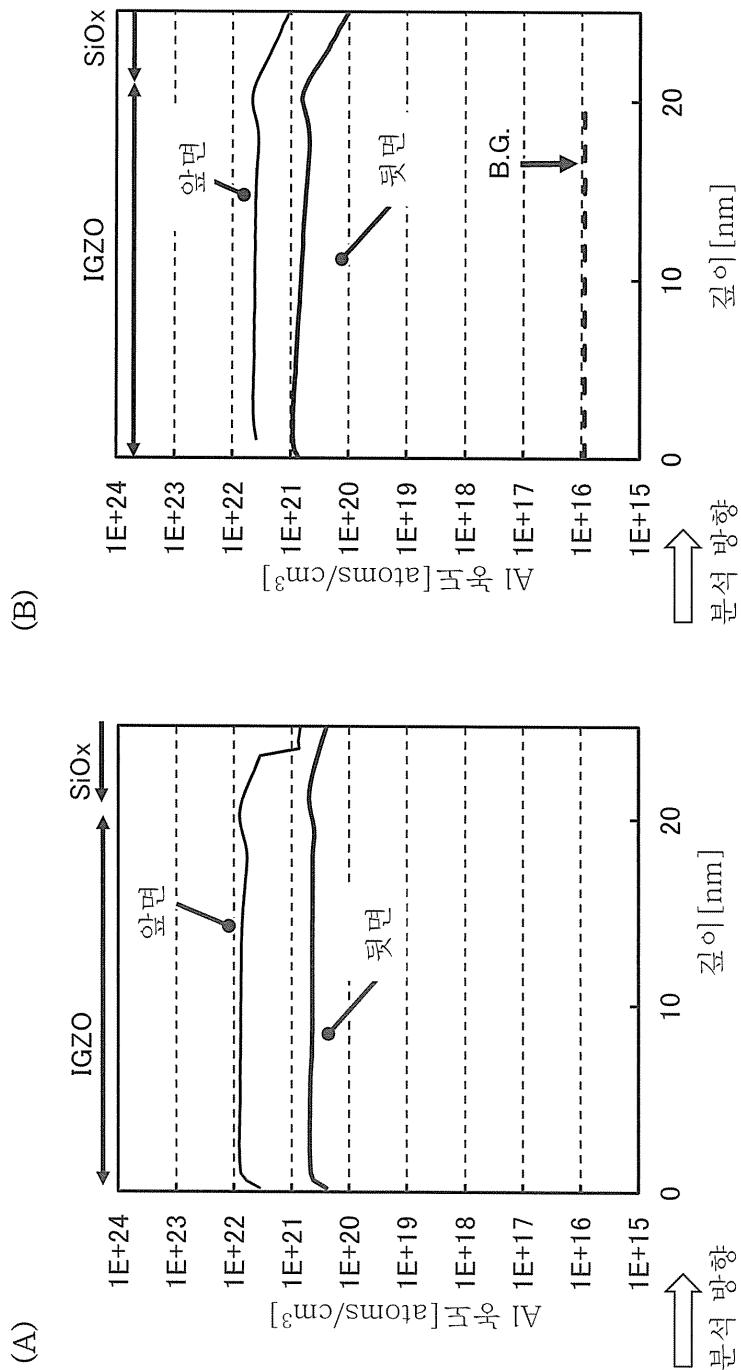

도 43은 실시예 1의 SIMS 분석의 결과를 나타낸 도면이다.

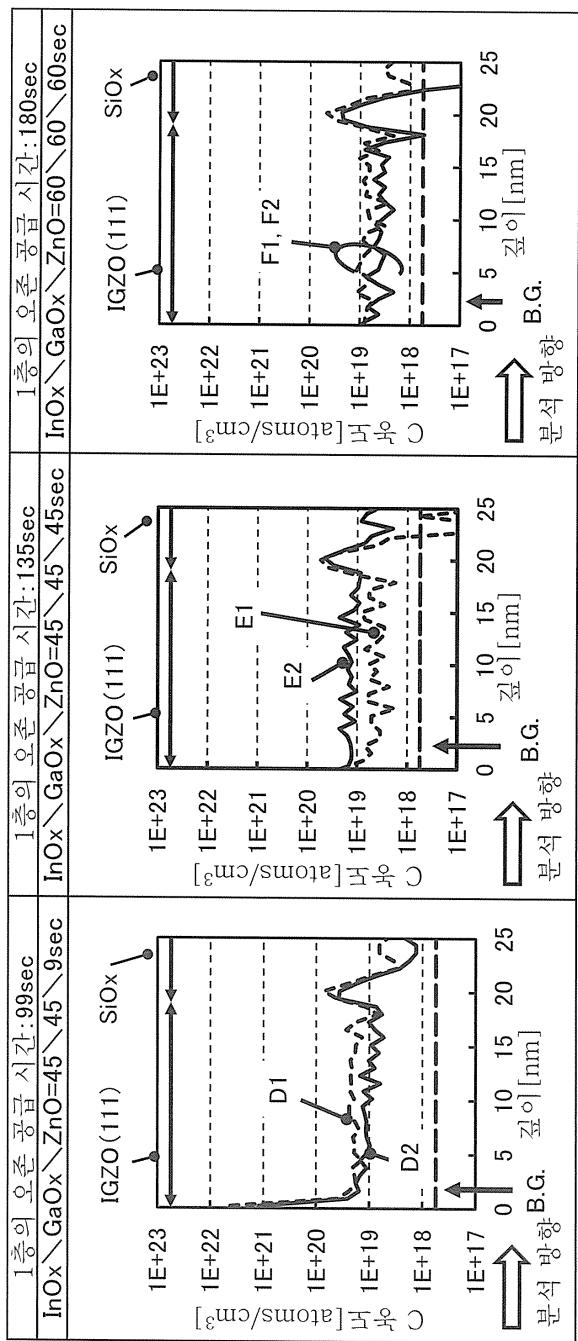

도 44는 실시예 1의 SIMS 분석의 결과를 나타낸 도면이다.

도 45는 실시예 1의 SIMS 분석의 결과를 나타낸 도면이다.

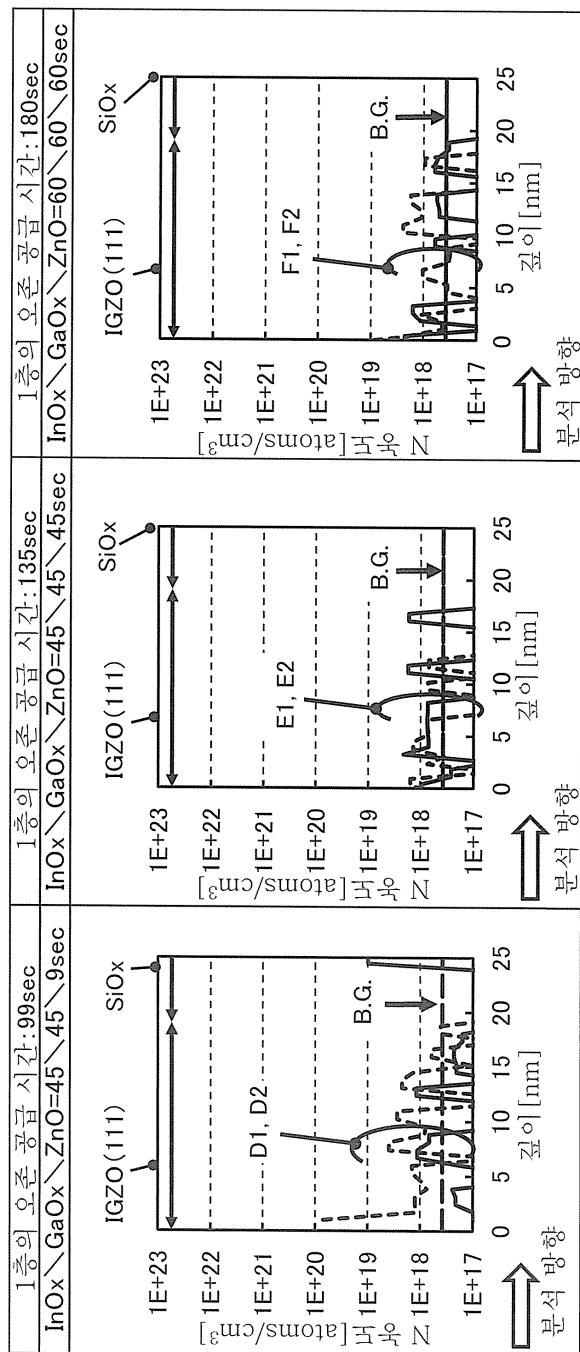

도 46의 (A) 및 (B)는 실시예 1의 SIMS 분석의 결과를 나타낸 도면이다.

도 47은 실시예 1의 SIMS 분석의 결과를 나타낸 도면이다.

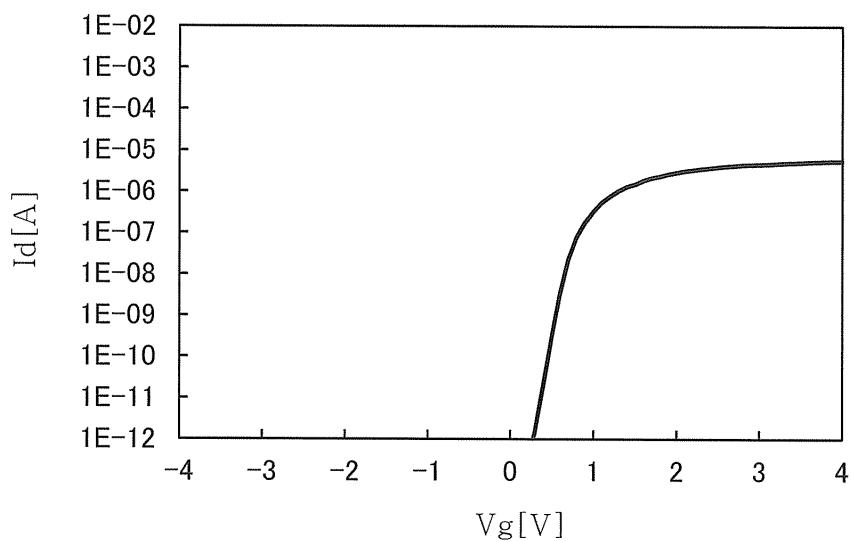

도 48은 실시예 1의 트랜지스터의 Id-Vg 특성을 나타낸 도면이다.

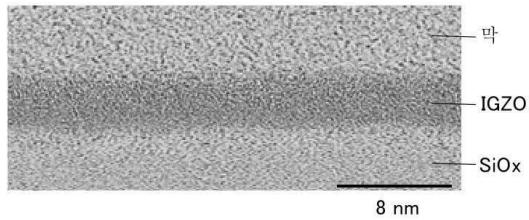

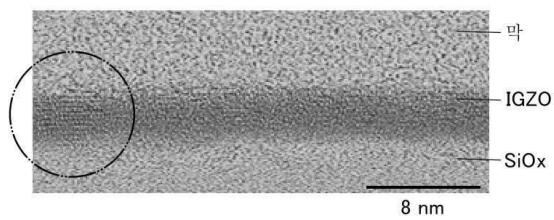

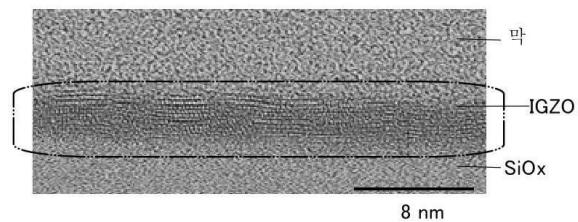

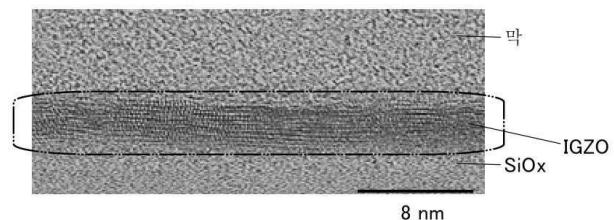

도 49의 (A) 내지 (D)는 실시예 1의 IGZO막의 단면 관찰 이미지이다.

도 50의 (A) 내지 (D)는 실시예 2의 SIMS 분석의 결과를 나타낸 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0037]

실시형태에 대하여 도면을 사용하여 자세히 설명한다. 다만 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 벗어남이 없이 그 형태 및 자세한 사항을 다양하게 변경할 수 있다는 것은 통상의 기술자라면 쉽게 이해할 수 있다. 따라서 본 발명은 이하에 나타내는 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다.

[0038]

또한 이하에서 설명하는 발명의 구성에서 동일한 부분 또는 같은 기능을 가지는 부분에는 동일한 부호를 다른 도면 간에서 공통적으로 사용하고, 그 반복적인 설명은 생략한다. 또한 같은 기능을 가지는 부분을 가리키는 경우에는 해치 패턴을 동일하게 하고, 특별히 부호를 붙이지 않는 경우가 있다.

[0039]

또한 도면에 나타낸 각 구성의 위치, 크기, 및 범위 등을 이해를 쉽게 하기 위하여 실제의 위치, 크기, 및 범위 등을 나타내지 않는 경우가 있다. 그러므로 개시된 발명은 반드시 도면에 개시된 위치, 크기, 및 범위 등에 한정되지 않는다.

[0040]

또한 본 명세서 등에서 "제 1", "제 2"라는 서수사는 편의상 사용하는 것이며, 구성 요소의 개수 또는 구성 요소의 순서(예를 들어 공정 순서 또는 적층 순서)를 한정하는 것이 아니다. 또한 본 명세서의 어떤 부분에 있어

서 구성 요소에 붙이는 서수사와 본 명세서의 다른 부분 또는 청구범위에 있어서 상기 구성 요소에 붙이는 서수사가 일치하지 않는 경우가 있다.

[0041] 또한 트랜지스터는 반도체 소자의 일종이며, 전류 또는 전압을 증폭하는 기능 및 도통 또는 비도통을 제어하는 스위칭 동작 등을 실현할 수 있다. 본 명세서에서 트랜지스터는 IGFET(Insulated Gate Field Effect Transistor) 및 박막 트랜지스터(TFT: Thin Film Transistor)를 포함한다.

[0042] 또한 본 명세서 등에서 트랜지스터란 게이트와, 드레인과, 소스를 포함한 적어도 3개의 단자를 가지는 소자이다. 그리고 드레인(드레인 단자, 드레인 영역, 또는 드레인 전극)과 소스(소스 단자, 소스 영역, 또는 소스 전극) 사이에 채널이 형성되는 영역(채널 형성 영역이라고도 함)을 가지고, 채널 형성 영역을 통하여 소스와 드레인 사이에 전류를 흘릴 수 있다. 또한 본 명세서 등에서 채널 형성 영역이란 전류가 주로 흐르는 영역을 말한다.

[0043] 또한 "소스" 및 "드레인"의 기능은 상이한 극성의 트랜지스터를 채용하는 경우 또는 회로 동작에서 전류의 방향이 변화되는 경우 등에는 서로 바꿔는 경우가 있다. 그러므로 본 명세서에서는 "소스" 및 "드레인"이라는 용어는 서로 바꿔 사용할 수 있는 것으로 한다.

[0044] 또한 반도체의 불순물이란, 예를 들어 반도체를 구성하는 주성분 외의 것을 말한다. 예를 들어 농도가 0.1atomic% 미만인 원소는 불순물이라고 할 수 있다. 불순물이 포함됨으로써, 예를 들어 반도체의 결함 준위 밀도가 높아지거나, 결정성의 저하 등이 일어나는 경우가 있다. 반도체가 산화물 반도체인 경우, 반도체의 특성을 변화시키는 불순물로서는 예를 들어 1족 원소, 2족 원소, 13족 원소, 14족 원소, 15족 원소, 산화물 반도체의 주성분 이외의 전이 금속 등이 있다. 구체적으로는 예를 들어 수소, 리튬, 소듐, 실리콘, 붕소, 인, 탄소, 또는 질소 등이 있다. 또한 물도 불순물로서 기능하는 경우가 있다. 또한 예를 들어 불순물의 혼입으로 인하여 산화물 반도체에 산소 결손( $V_0$ 라고도 함)이 형성되는 경우가 있다.

[0045] 또한 본 명세서 등에서 산화질화물이란, 그 조성으로서 질소보다 산소의 함유량이 많은 재료를 가리킨다. 질화산화물이란, 그 조성으로서 산소보다 질소의 함유량이 많은 재료를 가리킨다.

[0046] 막에 포함되는 수소, 산소, 탄소, 질소 등의 원소의 함유량의 분석에는 예를 들어 이차 이온 질량 분석법(SIMS: Secondary Ion Mass Spectrometry) 또는 X선 광전자 분광법(XPS: X-ray Photoelectron Spectroscopy)을 사용할 수 있다. 목적 원소의 함유율이 높은(예를 들어 0.5atomic% 이상 또는 1atomic% 이상) 경우에는 XPS가 적합하다. 한편, 목적 원소의 함유율이 낮은(예를 들어 0.5atomic% 이하 또는 1atomic% 이하) 경우에는 SIMS가 적합하다. 원소의 함유량을 비교할 때, SIMS와 XPS의 양쪽의 분석 방법을 사용한 복합 해석을 수행하는 것이 더 바람직하다.

[0047] 또한 본 명세서 등에서 "절연체"라는 용어를 절연막 또는 절연층이라고 바꿔 말할 수 있다. 또한 "도전체"라는 용어를 도전막 또는 도전층이라고 바꿔 말할 수 있다. 또한 "반도체"라는 용어를 반도체막 또는 반도체층이라고 바꿔 말할 수 있다.

[0048] 또한 본 명세서 등에서 "평행"이란, 2개의 직선이  $-10^\circ$  이상  $10^\circ$  이하의 각도로 배치되어 있는 상태를 말한다. 따라서  $-5^\circ$  이상  $5^\circ$  이하의 경우도 포함된다. 또한 "실질적으로 평행"이란, 2개의 직선이  $-30^\circ$  이상  $30^\circ$  이하의 각도로 배치되어 있는 상태를 말한다. 또한 "수직"이란, 2개의 직선이  $80^\circ$  이상  $100^\circ$  이하의 각도로 배치되어 있는 상태를 말한다. 따라서  $85^\circ$  이상  $95^\circ$  이하의 경우도 포함된다. 또한 "실질적으로 수직"이란, 2개의 직선이  $60^\circ$  이상  $120^\circ$  이하의 각도로 배치되어 있는 상태를 말한다.

[0049] 본 명세서 등에서 "전기적으로 접속"에는 "어떠한 전기적 작용을 가지는 것"을 통하여 접속되는 경우가 포함된다. 여기서 "어떠한 전기적 작용을 가지는 것"은 접속 대상 사이에서의 전기 신호의 주고받음을 가능하게 하는 것이면 특별히 제한을 받지 않는다. 예를 들어 "어떠한 전기적 작용을 가지는 것"에는 전극 또는 배선을 비롯하여 트랜지스터 등의 스위칭 소자, 저항 소자, 코일, 용량 소자, 이를 이외의 각종 기능을 가지는 소자 등이 포함된다.

[0050] 본 명세서 등에서 특별히 언급이 없는 경우, 오프 전류란, 트랜지스터가 오프 상태(비도통 상태, 차단 상태라고도 함)일 때의 소스와 드레인 사이의 누설 전류를 말한다. 특별히 언급이 없는 경우, 오프 상태란, n채널형 트랜지스터에서는 게이트와 소스 사이의 전압( $V_{gs}$ )이 문턱 전압( $V_{th}$ )보다 낮은(p채널형 트랜지스터에서는  $V_{th}$ 보다 높은) 상태를 말한다.

[0051] 본 명세서 등에서 어떤 구성 요소의 상면 형상이란 평면에서 보았을 때 상기 구성 요소의 윤곽 형상을

가리킨다. 또한 평면에서 본다란, 상기 구성 요소의 피형성면 또는 상기 구성 요소가 형성되는 지지체(예를 들어 기판)의 표면의 법선 방향에서 보는 것을 말한다.

[0052] 또한 본 명세서 등에서 테이퍼 형상이란, 구조의 측면의 적어도 일부가 기판면 또는 피형성면에 대하여 경사져 제공된 형상을 가리킨다. 예를 들어 경사진 측면과 기판면 또는 피형성면이 이루는 각(테이퍼 각이라고도 함)이  $90^\circ$  미만인 영역을 가지는 것이 바람직하다. 또한 구조의 측면, 기판면, 및 피형성면은 반드시 완전히 평탄할 필요는 없고, 미소한 곡률을 가지는 대략 평면 형상 또는 미세한 요철을 가지는 대략 평면 형상을 가져도 좋다.

[0053] 본 명세서 등에서 A는 B와 접한다고 기재되는 경우, A의 적어도 일부가 B와 접한다. 그러므로 예를 들어 A는 B와 접하는 영역을 가진다고 바꿔 말할 수 있다.

[0054] 본 명세서 등에서 A는 B 위에 위치한다고 기재되는 경우, A의 적어도 일부가 B 위에 위치한다. 그러므로 예를 들어 A는 B 위에 위치하는 영역을 가진다고 바꿔 말할 수 있다.

[0055] 본 명세서 등에서 A는 B를 덮는다고 기재되는 경우, A의 적어도 일부가 B를 덮는다. 그러므로 예를 들어 A는 B를 덮는 영역을 가진다고 바꿔 말할 수 있다.

[0056] 본 명세서 등에서 A는 B와 중첩된다고 기재되는 경우, A의 적어도 일부가 B와 중첩된다. 그러므로 예를 들어 A는 B와 중첩되는 영역을 가진다고 바꿔 말할 수 있다.

[0057] (실시형태 1)

[0058] 본 실시형태에서는 본 발명의 일 형태의 금속 산화물을 및 그 성막 방법에 대하여 도 1 내지 도 13을 사용하여 설명한다.

[0059] 본 발명의 일 형태의 금속 산화물은 금속 산화물을 구성하는 원소의 종류, 조합, 조성 등에 따라, 반도체 재료, 절연성 재료, 및 도전성 재료 중 어느 것으로서 사용할 수 있다. 본 발명의 일 형태의 금속 산화물은 예를 들어 트랜지스터의 반도체층에 사용할 수 있다. 상기 금속 산화물을 산화물 반도체 또는 산화물이라고 부르는 경우도 있다.

[0060] 본 발명의 일 형태의 금속 산화물의 성막 방법에서는 ALD(Atomic Layer Deposition)법을 사용하기 때문에 두께가 매우 얇은 막을 균일하게 형성할 수 있다. 그러므로 미세한 트랜지스터를 구성하는 금속 산화물의 성막에 적합하다.

[0061] 본 발명의 일 형태의 금속 산화물의 성막 방법에서는 무기 전구체 및 유기 전구체 중 한쪽 또는 양쪽을 사용할 수 있다. 여기서 유기 전구체란, 구성 원소에 탄소를 포함한 전구체이고, 무기 전구체란, 구성 원소에 탄소를 포함하지 않는 전구체이다.

[0062] 무기 전구체를 사용하여 성막된 금속 산화물은 유기 전구체를 사용하여 성막된 금속 산화물에 비하여 막 내의 불순물 농도(예를 들어 수소 농도, 탄소 농도, 및 질소 농도 중 적어도 하나)를 낮게 할 수 있다.

[0063] 또한 유기 전구체를 사용함으로써, 무기 전구체를 사용하는 경우에 비하여 금속 산화물의 성막 온도를 낮출 수 있다.

[0064] 여기서, 불순물을 포함한 전구체를 사용하여 금속 산화물을 성막하면, 금속 산화물 내에 상기 불순물이 들어가 금속 산화물의 물성, 나아가서는 상기 금속 산화물을 사용한 반도체 장치의 특성에 악영향을 미칠 우려가 있다.

[0065] 예를 들어, 알루미늄을 주성분으로서 포함하지 않은 금속 산화물에 불순물인 알루미늄이 많이 포함되면 상기 금속 산화물의 물성에 영향을 미치는 경우가 있다. 여기서 알루미늄을 주성분으로서 포함하지 않은 금속 산화물로서는 인듐 아연 산화물(In-Zn 산화물), 인듐 갈륨 아연 산화물(In-Ga-Zn 산화물, IGZO라고도 기재함) 등을 들 수 있다.

[0066] 예를 들어, IGZO막 내에 알루미늄이 산화 상태( $\text{Al}_2\text{O}_3$  등)로 존재하면 IGZO막이 고저항화된다. 그리고 고저항화된 IGZO막을 반도체층에 사용하면 트랜지스터의 온 전류가 낮게 된다.

[0067] 한편, 알루미늄은 산소와의 결합 해리 에너지가 높아 캐리어 억제 원소로서 기능한다. 구체적으로는 알루미늄과 산소의 결합 해리 에너지는 Ga와 산소의 결합 해리 에너지보다 높다. 따라서 IGZO막 내에 알루미늄이 존재함으로써, 산소 결손(Vo)이 생성되기 어렵게 할 수 있다. Vo가 생성되기 어려운 IGZO막을 반도체층에 사용하면, 트랜지스터의 광 네거티브 바이어스 열화를 억제할 수 있다. 그러므로, 금속 산화물 내의 알루미늄

은 완전히 제거하지 않아도 되고, 악영향을 미치지 않을 정도로 금속 산화물 내에 포함되어도 좋은 경우가 있다.

[0068] 그래서 본 발명의 일 형태의 금속 산화물의 성막 방법에서는, 알루미늄 함유량이 적은 전구체를 사용하여 알루미늄을 주성분으로서 포함하지 않는 금속 산화물을 제작한다. 이에 의하여 성막한 금속 산화물 내의 알루미늄 농도가 높아지는 것을 억제할 수 있다.

[0069] 또한 ALD법을 사용하여 형성된 금속 산화물에서는 성막 후에 금속 산화물에 대하여 가열 처리를 수행하여도 막 내의 불순물을 충분히 제거하는 것은 어려운 경우가 있다. 한편, 불순물의 함유량이 적은 금속 산화물을 성막하기 위하여 트랜지스터 또는 반도체 장치의 제작 공정에서의 최고 온도를 높일 정도의 고온 처리(예를 들어 700°C를 넘는 처리)를 수행하면 생산성이 저하된다.

[0070] 그래서 본 발명의 일 형태의 금속 산화물의 성막 방법에서는, 산화제를 충분히 공급함으로써 막 내의 탄소 농도를 저감한다. 예를 들어 금속 산화물의 성막 공정 전체에서의 산화제를 공급하는 공정의 합계 시간을 충분히 길게 한다. 또는 산화제에 포함되는 오존( $O_3$ )의 비율을 크게 한다.

[0071] 또한 불순물 제거 처리로서, 성막 후에 산소를 포함하는 분위기하에서 마이크로파 처리를 수행하는 것이 바람직하다. 산소를 포함하는 분위기하에서 마이크로파 처리를 수행함으로써 막 내의 불순물을 제거할 수 있다. 이로써 전구체 등의 원료에 포함되는 불순물이 금속 산화물을 내에 잔존하는 것을 억제할 수 있다. 따라서 금속 산화물 내의 불순물 농도를 저감할 수 있다. 또한 금속 산화물의 결정성을 높일 수 있다.

[0072] 성막 중에 산소를 포함하는 분위기하에서 불순물 제거 처리를 간헐적으로 수행하는 것이 바람직하다. 성막 중에 불순물 제거 처리를 수행함으로써, 성막 후에 수행하는 경우에 비하여 막 내의 불순물을 더 확실하게 제거할 수 있다. 또한 불순물 제거 처리는 성막 중 및 성막 후의 양쪽에서 수행하여도 좋다.

[0073] 이상으로부터, 본 발명의 일 형태의 금속 산화물의 성막 방법을 사용하여, 미세한 트랜지스터의 반도체층에 사용하는, 불순물의 함유량이 적은 금속 산화물을 형성할 수 있다. 또한 본 발명의 일 형태의 금속 산화물의 성막 방법을 사용하여, 미세한 트랜지스터의 반도체층에 사용하는, 결정성이 높은 금속 산화물을 형성할 수 있다. 이에 의하여, 미세하며 전기 특성이 양호한 트랜지스터를 실현할 수 있다. 또한 미세하며 신뢰성이 양호한 트랜지스터를 실현할 수 있다. 특히 CAAC 구조의 금속 산화물을 형성하는 것이 바람직하다.

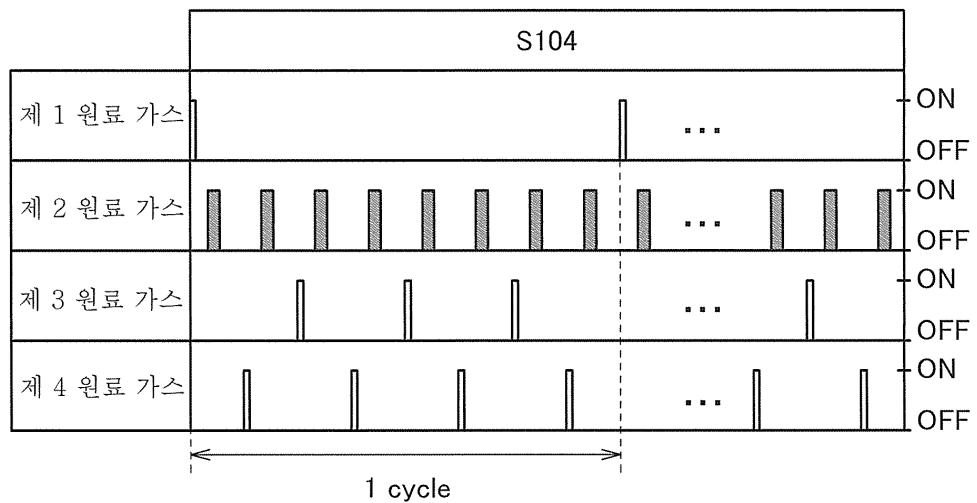

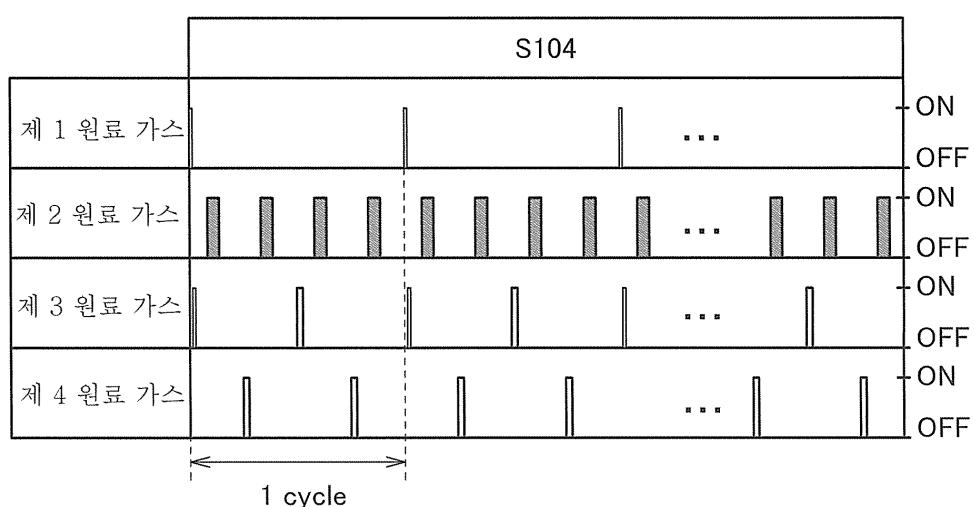

[0074] 구체적으로는 본 발명의 일 형태는 인듐을 포함한 제 1 화합물을 체임버 내에 공급하고 그 후 산화제를 체임버 내에 공급하는 제 1 공정과, 제 2 화합물을 체임버 내에 공급하고 그 후 산화제를 체임버 내에 공급하는 제 2 공정을 가지는 금속 산화물의 성막 방법이다. 또한 제 3 화합물을 체임버 내에 공급하고 그 후 산화제를 체임버 내에 공급하는 제 3 공정을 가져도 좋다.

[0075] 제 1 화합물의 알루미늄 함유량은 0.001ppm 이상, 0.01ppm 이상, 또는 0.1ppm 이상인 것이 바람직하고, 또한 1000ppm 이하인 것이 바람직하고, 500ppm 이하인 것이 더 바람직하고, 100ppm 이하인 것이 더 바람직하고, 50ppm 이하인 것이 더 바람직하고, 10ppm 이하인 것이 바람직하고, 1ppm 이하인 것이 더 바람직하다.

[0076] 제 2 화합물 및 제 3 화합물은 각각 갈륨, 주석, 및 아연 중 적어도 하나를 포함하는 것이 바람직하다. 제 2 화합물의 알루미늄 함유량 및 제 3 화합물의 알루미늄 함유량의 바람직한 범위는 제 1 화합물의 알루미늄 함유량의 바람직한 범위와 마찬가지이다. 특히, 제 2 화합물 및 제 3 화합물은 각각 제 1 화합물보다 알루미늄 함유량이 적은 것이 바람직하다.

[0077] 금속 산화물의 성막 공정에서, 1사이클에서의 산화제를 공급하는 시간의 합계는 10초 이상이 바람직하고, 30초 이상이 더 바람직하고, 60초 이상이 더 바람직하고, 90초 이상이 더 바람직하고, 120초 이상이 더 바람직하고, 또한 150초 이하, 200초 이하, 250초 이하, 또는 300초 이하가 바람직하다. 제 1 화합물과 제 2 화합물의 2개를 사용하여 금속 산화물을 성막하는 경우에는, 상술한 제 1 공정과 제 2 공정을 한 번씩 수행하는 것을 1사이클로 한다. 1사이클에서의 산화제를 공급하는 시간의 합계는 제 1 공정에서의 산화제를 공급하는 시간과 제 2 공정에서의 산화제를 공급하는 시간의 합에 상당한다. 제 3 화합물을 추가한 3개의 화합물을 사용하여 금속 산화물을 성막하는 경우에는, 상술한 제 1 공정, 제 2 공정, 및 제 3 공정을 한 번씩 수행하는 것을 1사이클로 한다. 1사이클에서의 산화제를 공급하는 시간의 합계는 제 1 공정 내지 제 3 공정에서의 산화제를 공급하는 시간의 합에 상당한다.

[0078] 산화제를 공급하는 시간이 길수록 금속 산화물 내의 탄소 농도를 저감할 수 있어 바람직하다. 한편, 산화제를 공급하는 시간이 짧을수록, 금속 산화물을 성막하기 위하여 필요한 시간이 짧게 되어 바람직하다.

- [0079] 산화제를 공급할 때, 가스 내의 오존의 비율을 10% 이상으로 하는 것이 바람직하고, 20% 이상이 더 바람직하고, 30% 이상이 더 바람직하고, 40% 이상이 더 바람직하고, 50% 이상이 더 바람직하고, 60% 이상이 더 바람직하고, 70% 이상이 더 바람직하고, 80% 이상이 더 바람직하고, 90% 이상이 더 바람직하고, 100%가 특히 바람직하다. 오존의 비율이 클수록, 금속의 산화를 촉진하고 금속 산화물 내의 탄소 농도를 저감할 수 있어 바람직하다.

- [0080] 산화제를 공급할 때, 기관 온도를 150°C 이상, 200°C 이상, 또는 250°C 이상으로 하는 것이 바람직하다. 기관 온도의 상한으로서는, 제 1 화합물 등의 전구체의 분해 온도 및 오존의 분해 온도(예를 들어 300°C) 중 보다 낮은 것을 사용할 수 있다. 기관 온도를 높게 함으로써 금속 산화물 내의 불순물 농도를 저감할 수 있어 바람직하다.

- [0081] 본 발명의 일 형태의 금속 산화물의 성막 방법에 있어서, 제 1 공정 및 제 2 공정을 각각 한 번 이상 수행한 후 산소를 포함하는 분위기하에서 불순물 제거 처리를 수행하는 것이 바람직하다. 불순물 제거 처리는 금속 산화물 내에 포함된 불순물을 막 중에서 이탈시키는 처리이다. 불순물 제거 처리에서는 금속 산화물 내에 포함된 수소, 탄소, 및 질소 등을 막 중에서 이탈시키는 것이 바람직하다. 또한 불순물 제거 처리에서는 금속 산화물 내에 산소를 공급하는 것이 바람직하다. 이에 의하여 금속 산화물 내의 산소 결손( $V_0$ ) 및 불순물을 저감할 수 있다. 산소 결손( $V_0$ ) 및 불순물이 저감된 금속 산화물을 사용함으로써 트랜지스터의 전기 특성 및 신뢰성을 높일 수 있다.

- [0082] 불순물 제거 처리로서는 예를 들어 플라스마 처리, 마이크로파 처리, 및 가열 처리가 있다.

- [0083] 플라스마 처리 또는 마이크로파 처리를 수행할 때는 각각 기관의 온도를 실온(예를 들어 25°C) 이상, 100°C 이상, 200°C 이상, 300°C 이상, 또는 400°C 이상으로 하고, 또한 500°C 이하 또는 450°C 이하로 하는 것이 바람직하다. 또한 가열 처리의 온도는 100°C 이상, 200°C 이상, 300°C 이상, 또는 400°C 이상으로 하고, 또한 500°C 이하 또는 450°C 이하로 하는 것이 바람직하다.

- [0084] 불순물 제거 처리를 수행할 때의 온도는 특히 트랜지스터 또는 반도체 장치의 제작 공정에서의 최고 온도 이하의 온도로 함으로써, 생산성을 저하시키지 않고 금속 산화물 내의 불순물의 함유량을 저감할 수 있기 때문에 바람직하다. 예를 들어 본 발명의 일 형태의 금속 산화물이 사용되는 트랜지스터 또는 반도체 장치의 제작에서의 최고 온도를 500°C 이하, 바람직하게는 450°C 이하로 함으로써 트랜지스터 또는 반도체 장치의 생산성을 높일 수 있다.

- [0085] 또한 불순물 제거 처리는 제 1 화합물 및 제 2 화합물 중 어느 분해 온도보다 낮은 온도에서 수행하는 것이 바람직하다. 또한 제 3 화합물을 사용하는 경우에는 제 3 화합물의 분해 온도보다 낮은 온도에서 수행하는 것이 바람직하다. 또한 불순물 제거 처리는 500°C보다 높은 온도(예를 들어 500°C보다 높고 700°C 이하)에서 수행하여도 좋다.

- [0086] 불순물 제거 처리는 광(예를 들어 자외광)을 조사하면서 수행하여도 좋다. 이에 의하여 불순물의 이탈의 촉진을 도모할 수 있다. 광원으로서는 레이저, 수은등 등을 들 수 있다. 예를 들어 광 여기에 의하여 산소 라디칼을 발생시켜 수소, 탄소, 또는 질소 등과 반응시킴으로써, 막 내의 불순물의 저감 및 결정화의 촉진을 도모할 수 있다. 광 조사를 수행함으로써 광 조사를 수행하지 않는 경우에 비하여 가열 온도를 낮게 하여도 불순물의 제거가 용이해질 경우가 있다.

- [0087] 또한 성막 중에 광을 조사하여도 좋다. 예를 들어 제 1 공정에서, 제 1 화합물을 체임버 내에 공급할 때 및 산화제를 체임버 내에 공급할 때 중 한쪽 또는 양쪽에 있어서 금속 산화물의 피형성면에 광을 조사하여도 좋다. 제 2 공정 및 제 3 공정에 대해서도 마찬가지이다.

- [0088] 제 1 공정 및 제 2 공정을 각각 한 번 이상 수행한 후 산소를 포함하는 분위기하에서 불순물 제거 처리를 수행하는 것을 제 1 사이클로 하여, 상기 제 1 사이클을 여러 번 반복하는 것이 바람직하다.

- [0089] 또는 제 1 공정 및 제 2 공정을 각각 한 번 이상 수행한 후 산소를 포함하는 분위기하에서 불순물 제거 처리를 수행하는 것을 제 1 사이클로 하고, 제 1 사이클과는 다른 순서로 제 1 공정 및 제 2 공정을 각각 한 번 이상 수행한 후 산소를 포함하는 분위기하에서 불순물 제거 처리를 수행하는 것을 제 2 사이클로 하여, 제 1 사이클과 제 2 사이클을 번갈아 여러 번 반복하는 것이 바람직하다.

- [0090] 제 1 사이클 및 제 2 사이클에서는 각각 예를 들어 제 1 공정 및 제 2 공정 중 횟수가 적은 쪽 또는 양쪽을 5회 이상 10회 이하의 범위로 수행할 때마다 불순물 제거 처리를 수행하는 것이 바람직하다.

- [0091] 금속 산화물을 성막한 후에 불순물 제거 처리를 수행하는 것만으로는 불순물을 충분히 제거할 수 없는 경우가 있다. 성막 중에 불순물 제거 처리를 간헐적으로(간격을 두고) 도입함으로써, 금속 산화물 내의 불순물을 충분히 제거할 수 있다.

- [0092] 또한 본 발명의 일 형태는 인듐을 포함한 전구체(예를 들어 트라이에틸인듐 전구체)를 체임버 내에 공급하고, 그 후에 산화제를 체임버 내에 공급하는, ALD법을 사용한 인듐 화합물의 성막 방법이다. 상기 전구체의 알루미늄 함유량은 0.001ppm 이상, 0.01ppm 이상, 또는 0.1ppm 이상인 것이 바람직하고, 또한 1000ppm 이하인 것이 바람직하고, 500ppm 이하인 것이 더 바람직하고, 100ppm 이하인 것이 더 바람직하고, 50ppm 이하인 것이 더 바람직하고, 10ppm 이하인 것이 바람직하고, 1ppm 이하인 것이 더 바람직하다.

- [0093] <금속 산화물>

- [0094] 금속 산화물은 격자 결함을 가지는 경우가 있다. 격자 결함으로서는 원자 공공, 이종 원자 등의 점결함, 전위(轉位) 등의 선결함, 결정계 등이 면결함, 공극 등의 체적 결함이 있다. 또한 격자 결함이 생성되는 요인으로서는 구성 원소의 원자수의 비율의 차이(구성 원자의 과부족) 및 불순물 등이 있다.

- [0095] 금속 산화물을 트랜지스터의 반도체층에 사용하는 경우, 금속 산화물 내의 격자 결함은 캐리어가 생성되거나 포획되는 요인이 될 수 있다. 따라서 격자 결함이 많은 금속 산화물을 트랜지스터의 반도체층에 사용하면, 상기 트랜지스터의 전기 특성이 불안정해질 우려가 있다. 따라서 트랜지스터의 반도체층에 사용하는 금속 산화물은 격자 결함이 적은 것이 바람직하다.

- [0096] 금속 산화물을 사용한 트랜지스터는 특히 금속 산화물 내의 채널 형성 영역에 산소 결손( $V_0$ ) 및 불순물이 존재하면, 전기 특성이 변동되기 쉬우므로 신뢰성이 저하되는 경우가 있다. 또한 산소 결손 근방의 수소가, 산소 결손에 수소가 들어간 결함(이하,  $V_0H$ 라고 하는 경우가 있음)을 형성하여, 캐리어가 되는 전자를 생성하는 경우가 있다. 이로써 금속 산화물 내의 채널 형성 영역에 산소 결손이 포함되면, 트랜지스터는 노멀리 온 특성(게이트 전극에 전압을 인가하지 않아도 채널이 존재하고 트랜지스터에 전류가 흐르는 특성)을 가지기 쉽다. 따라서 금속 산화물 내의 채널 형성 영역에서는 산소 결손 및 불순물은 가능한 한 저감되어 있는 것이 바람직하다. 바꿔 말하면, 금속 산화물 내의 채널 형성 영역은 캐리어 농도가 저감되고 i형화(진성화) 또는 실질적으로 i형화되어 있는 것이 바람직하다.

- [0097] 금속 산화물 내에 존재하기 쉬운 격자 결함의 종류 및 격자 결함의 존재량은 금속 산화물의 구조 또는 성막 방법 등에 따라 다르다.

- [0098] 금속 산화물의 구조는 단결정 구조와, 그 외의 구조(비단결정 구조)로 나누어진다. 비단결정 구조로서는 예를 들어 CAAC 구조, 다결정(polygonal crystalline) 구조, nc 구조, a-like(amorphous-like) 구조, 및 비정질 구조 등이 있다. a-like 구조는 nc 구조와 비정질 구조의 중간의 구조를 가진다.

- [0099] 또한 본 발명의 일 형태의 금속 산화물의 결정성은 특별히 묻지 않는다.

- [0100] 또한 a-like 구조를 가지는 금속 산화물 및 비정질 구조를 가지는 금속 산화물은 공동 또는 저밀도 영역을 가진다. 즉 a-like 구조를 가지는 금속 산화물 및 비정질 구조를 가지는 금속 산화물은 nc 구조를 가지는 금속 산화물 및 CAAC 구조를 가지는 금속 산화물보다 결정성이 낮다. 또한 a-like 구조를 가지는 금속 산화물은 nc 구조를 가지는 금속 산화물 및 CAAC 구조를 가지는 금속 산화물보다 금속 산화물 내의 수소 농도가 높다. 따라서 a-like 구조를 가지는 금속 산화물 및 비정질 구조를 가지는 금속 산화물에서는 격자 결함이 생성되기 쉽다.

- [0101] 따라서 트랜지스터의 반도체층에는 결정부를 가지는 금속 산화물을 사용하는 것이 바람직하고, 결정성이 높은 금속 산화물을 사용하는 것이 더 바람직하다. 예를 들어 CAAC 구조를 가지는 금속 산화물 또는 단결정 구조의 금속 산화물을 사용하는 것이 바람직하다. 상기 금속 산화물을 트랜지스터에 사용함으로써, 전기 특성이 양호한 트랜지스터를 실현할 수 있다. 또한 신뢰성이 높은 트랜지스터를 실현할 수 있다.

- [0102] 또한 트랜지스터의 채널 형성 영역에는, 상기 트랜지스터의 온 전류가 커지는 금속 산화물을 사용하는 것이 바람직하다. 상기 트랜지스터의 온 전류를 크게 하기 위해서는, 상기 트랜지스터에 사용하는 금속 산화물의 이동도를 높이는 것이 좋다. 금속 산화물의 이동도를 높이기 위해서는 캐리어(n채널형 트랜지스터의 경우에는 전자)의 전송(傳送)을 향상시키거나, 캐리어의 전송에 기여하는 산란 인자를 저감시킬 필요가 있다. 또한 캐리어는 채널 형성 영역을 통하여 소스로부터 드레인으로 흐른다. 따라서 캐리어가 채널 길이 방향으로 흐르기 쉬운 채널 형성 영역을 제공함으로써 트랜지스터의 온 전류를 크게 할 수 있다.

- [0103] 여기서 채널 형성 영역을 포함하는 금속 산화물에 결정성이 높은 금속 산화물을 사용하는 것이 바람직하다. 또한 상기 결정은 복수의 층(예를 들어 제 1 층과, 제 2 층과, 제 3 층)이 적층된 결정 구조를 가지는 것이 바람직하다. 즉 상기 결정은 층상 결정 구조(층상 결정, 층상 구조라고도 함)를 가진다. 이때 상기 결정의 c축의 방향은 복수의 층이 적층되는 방향이 된다. 상기 결정을 가지는 금속 산화물에는 예를 들어 단결정 산화물 반도체, CAAC-OS(c-axis aligned crystalline oxide semiconductor) 등이 포함된다.

- [0104] 또한 상기 결정의 c축을 금속 산화물의 피형성면 또는 막 표면에 대한 법선 방향으로 배향하는 것이 바람직하다. 이에 의하여, 복수의 층은 금속 산화물의 피형성면 또는 막 표면에 평행 또는 실질적으로 평행하게 배치된다. 즉 복수의 층은 채널 길이 방향으로 전개된다.

- [0105] 예를 들어 상기와 같은 3층의 층상 결정 구조는 이하와 같은 구조가 된다. 제 1 층은 상기 제 1 층에 포함되는 금속이 중심에 존재하는 산소의 팔면체형의 원자 배위 구조를 가진다. 또한 제 2 층은 상기 제 2 층에 포함되는 금속이 중심에 존재하는 산소의 삼각 쌍뿔형 또는 사면체형의 원자 배위 구조를 가진다. 또한 제 3 층은 상기 제 3 층에 포함되는 금속이 중심에 존재하는 산소의 삼각 쌍뿔형 또는 사면체형의 원자 배위 구조를 가진다.

- [0106] 상기 결정의 결정 구조로서 예를 들어  $\text{YbFe}_2\text{O}_4$ 형 구조,  $\text{Yb}_2\text{Fe}_3\text{O}_7$ 형 구조, 이들의 변형 구조 등이 있다.

- [0107] 또한 제 1 층 내지 제 3 층은 각각 하나의 금속 원소 또는 가수가 같은 복수의 금속 원소와, 산소로 구성되는 것이 바람직하다. 또한 제 1 층을 구성하는 하나 또는 복수의 금속 원소의 가수와, 제 2 층을 구성하는 하나 또는 복수의 금속 원소의 가수는 같은 것이 바람직하다. 또한 제 1 층과 제 2 층은 같은 금속 원소를 포함하여도 좋다. 또한 제 1 층을 구성하는 하나 또는 복수의 금속 원소의 가수와, 제 3 층을 구성하는 하나 또는 복수의 금속 원소의 가수는 상이한 것이 바람직하다.

- [0108] 상기 구성으로 함으로써, 금속 산화물의 결정성이 향상되고, 상기 금속 산화물의 이동도를 높일 수 있다. 따라서 상기 금속 산화물을 트랜지스터의 채널 형성 영역에 사용함으로써, 트랜지스터의 온 전류가 커져 상기 트랜지스터의 전기 특성을 향상시킬 수 있다.

- [0109] 본 발명의 일 형태의 금속 산화물은 적어도 인듐 또는 아연을 포함하는 것이 바람직하다. 특히 인듐 및 아연을 포함하는 것이 바람직하다. 또한 이들에 더하여 인듐 또는 아연과 가수가 같은 금속 원소를 적어도 하나 포함하는 것이 바람직하다. 상기 금속 원소로서 예를 들어 갈륨, 주석이 있다. 또한 이트륨, 붕소, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데넘, 란타넘, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텉스텐, 마그네슘, 칼슘, 코발트, 및 알루미늄 등에서 선택된 1종류 또는 복수 종류가 포함되어도 좋다.

- [0110] 여기서는 금속 산화물이 인듐(In), 원소 M, 및 아연(Zn)을 포함하는 In-M-Zn 산화물인 경우에 대하여 생각한다. 또한 원소 M은 갈륨 또는 주석으로 한다. 이 외에 원소 M에 적용할 수 있는 원소로서는 이트륨, 붕소, 타이타늄, 철, 니켈, 저마늄, 지르코늄, 몰리브데넘, 란타넘, 세륨, 네오디뮴, 하프늄, 탄탈럼, 텉스텐, 마그네슘, 칼슘, 코발트, 알루미늄 등이 있다. 다만 원소 M으로서, 상술한 원소를 복수 조합하여도 되는 경우가 있다.

- [0111] 본 발명의 일 형태의 금속 산화물로서는 예를 들어 인듐 아연 산화물(In-Zn 산화물), 인듐 주석 산화물(In-Sn 산화물), 인듐 타이타늄 산화물(In-Ti 산화물), 인듐 갈륨 산화물(In-Ga 산화물), 인듐 갈륨 주석 산화물(In-Ga-Sn 산화물), 갈륨 아연 산화물(Ga-Zn 산화물, GZO라고도 기재함), 인듐 주석 아연 산화물(In-Sn-Zn 산화물, ITZO(등록 상표)라고도 기재함), 인듐 타이타늄 아연 산화물(In-Ti-Zn 산화물), 인듐 갈륨 아연 산화물(In-Ga-Zn 산화물, IGZO라고도 기재함), 인듐 갈륨 주석 아연 산화물(In-Ga-Sn-Zn 산화물, IGZTO라고도 기재함) 등이 있다.

- [0112] 금속 산화물에 포함된 모든 금속 원소의 원자수의 합에 대한 인듐의 원자수의 비율을 높게 함으로써 트랜지스터의 전계 효과 이동도를 높일 수 있다.

- [0113] 또한 금속 산화물은 인듐 대신에, 원소 주기율표에서의 주기 번호가 큰 금속 원소 중 1종류 또는 복수 종류를 포함하여도 좋다. 또는 금속 산화물은 인듐 대신에, 주기 번호가 큰 금속 원소 중 1종류 또는 복수 종류를 포함하여도 좋다. 금속 원소의 궤도의 중첩이 클수록 금속 산화물에서의 캐리어 전도는 크게 될 경향이 있다. 따라서 주기 번호가 큰 금속 원소를 포함함으로써 트랜지스터의 전계 효과 이동도를 높일 수 있는 경우가 있다. 주기 번호가 큰 금속 원소로서는 5주기에 속하는 금속 원소 및 6주기에 속하는 금속 원소 등을 들 수 있다. 상기 금속 원소로서 구체적으로는 이트륨, 지르코늄, 은, 카드뮴, 주석, 안티모니, 바륨, 납, 비스무트, 란타넘, 세륨, 프라세오디뮴, 네오디뮴, 프로메튬, 사마륨, 및 유로퓸 등을 들 수 있다. 또한 란타넘, 세륨, 프라세오디뮴, 네오디뮴, 프로메튬, 사마륨, 및 유로퓸은 경희토류 원소라고도 불린다.

- [0114] 또한 금속 산화물은 비금속 원소의 1종류 또는 복수 종류를 포함하여도 좋다. 금속 산화물이 비금속 원소를 포함함으로써 트랜지스터의 전계 효과 이동도를 높일 수 있는 경우가 있다. 비금속 원소로서 예를 들어 탄소, 질소, 인, 헝, 셀레늄, 플루오린, 염소, 브로민, 및 수소 등이 있다.

- [0115] 또한 금속 산화물에 포함된 모든 금속 원소의 원자수의 합에 대한 아연의 원자수의 비율을 높게 함으로써 결정성이 높은 금속 산화물이 되어 금속 산화물 내의 불순물의 확산을 억제할 수 있다. 따라서 트랜지스터의 전기 특성의 변동이 억제되어 신뢰성을 높일 수 있다.

- [0116] 또한 금속 산화물에 포함된 모든 금속 원소의 원자수의 합에 대한 원소 M의 원자수의 비율을 높게 함으로써 금속 산화물에 산소 결손이 형성되는 것을 억제할 수 있다. 따라서 산소 결손에 기인한 캐리어 생성이 억제되어 오프 전류가 작은 트랜지스터로 할 수 있다. 또한 트랜지스터의 전기 특성의 변동이 억제되어 신뢰성을 높일 수 있다.

- [0117] 또한 금속 산화물에 포함되는 모든 금속 원소의 원자수의 합에 대한 In의 원자수의 비율을 높임으로써, 트랜지스터는 큰 온 전류 및 높은 주파수 특성을 얻을 수 있다.

- [0118] 본 실시형태에서는 금속 산화물로서 In-Ga-Zn 산화물을 예로 들어 설명하는 경우가 있다.

- [0119] 상기 층상 결정 구조를 가지는 금속 산화물을 형성하기 위해서는 한 층씩 원자를 퇴적하는 것이 바람직하다. 본 발명의 일 형태의 금속 산화물의 성막 방법에서는 ALD법을 사용하기 때문에, 상기 층상 결정 구조를 가지는 금속 산화물을 형성하는 것이 용이하다.

- [0120] ALD법으로서는 전구체와 반응제의 반응을 열 에너지만으로 수행하는 열 ALD(Thermal ALD)법 및 플라스마 여기된 반응제를 사용하는 플라스마 ALD(PEALD: Plasma Enhanced ALD)법 등을 들 수 있다.

- [0121] ALD법에서는 한 층씩 원자를 퇴적할 수 있기 때문에, 매우 얇게 성막이 가능하고, 종횡비가 높은 구조에 대한 성막이 가능하고, 펀홀 등의 결함이 적은 성막이 가능하고, 피복성이 우수한 성막이 가능하고, 저온에서의 성막이 가능하다는 등의 효과가 있다. 또한 PEALD법에서는 플라스마를 이용함으로써 더 낮은 온도에서 성막을 수행할 수 있기 때문에 바람직한 경우가 있다. 또한 ALD법에서 사용하는 전구체에는 탄소 또는 염소 등의 원소가 포함되는 것이 있다. 그러므로 ALD법에 의하여 제공된 막은, 다른 성막법에 의하여 제공된 막에 비하여 탄소 또는 염소 등의 원소를 많이 포함하는 경우가 있다. 또한 이들 원소의 정량은 XPS 또는 SIMS를 사용하여 수행할 수 있다. 또한 본 발명의 일 형태의 금속 산화물의 성막 방법에서는 ALD법을 사용하는데, 성막 시의 기관온도가 높은 조건의 채용 및 불순물 제거 처리의 실시 중 한쪽 또는 양쪽을 적용하기 때문에, 이들을 적용하지 않고 ALD법을 사용하는 경우에 비하여 막 내에 포함되는 탄소 및 염소의 양이 적은 경우가 있다.

- [0122] ALD법은 타깃 등으로부터 방출되는 입자가 퇴적되는 성막 방법과는 달리, 피처리물의 표면에서의 반응에 의하여 막이 형성되는 성막 방법이다. 따라서 피처리물의 형상의 영향을 받기 어렵고 단차 피복성이 양호한 성막 방법이다. 특히 ALD법은 우수한 단차 피복성과 우수한 두께 균일성을 가지기 때문에, 종횡비가 높은 개구부의 표면을 피복하는 경우 등에 적합하다. 다만 ALD법은 성막 속도가 비교적 느리기 때문에, 성막 속도가 빠른 스퍼터링법 또는 CVD법 등 다른 성막 방법과 조합하여 사용되는 것이 바람직한 경우도 있다. 예를 들어 스퍼터링법을 사용하여 제 1 금속 산화물을 성막하고, 상기 제 1 금속 산화물 위에 ALD법을 사용하여 제 2 금속 산화물을 성막하는 방법 등이 있다. 예를 들어 상기 제 1 금속 산화물이 결정부를 가지는 경우, 상기 제 2 금속 산화물이 상기 결정부를 핵으로 하여 결정 성장하는 경우가 있다.

- [0123] ALD법은 원료 가스의 도입량을 변화시킴으로써, 얻어지는 막의 조성을 제어할 수 있다. 예를 들어 ALD법은 원료 가스의 도입량, 도입 횟수(펄스 횟수라고도 함) 1 펄스에 필요한 시간(펄스 시간이라고도 함) 등을 조절함으로써, 임의의 조성의 막을 성막할 수 있다. 또한 예를 들어 ALD법은 성막하면서 원료 가스를 변화시킴으로써, 조성이 연속적으로 변화된 막을 성막할 수 있다. 원료 가스를 변화시키면서 성막하는 경우에는, 복수의 성막실을 사용하여 성막하는 경우에 비하여, 반송 및 압력 조정에 걸리는 시간이 불필요하기 때문에 성막에 걸리는 시간을 단축할 수 있다. 따라서 반도체 장치의 생산성을 높일 수 있는 경우가 있다.

- [0124] <금속 산화물을 포함한 트랜지스터>

- [0125] 다음으로, 금속 산화물(산화물 반도체)을 트랜지스터에 사용하는 경우에 대하여 설명한다. 이하에서는 반도체 층에 산화물 반도체를 사용한 트랜지스터를 OS 트랜지스터라고 기재하고, 반도체층에 실리콘을 사용한 트랜지스터를 Si 트랜지스터라고 기재하는 경우가 있다.

- [0126] 본 발명의 일 형태의 금속 산화물(산화물 반도체)을 트랜지스터에 사용함으로써 전계 효과 이동도가 높은 트랜

지스터를 실현할 수 있다. 또한 신뢰성이 높은 트랜지스터를 실현할 수 있다. 또한 미세화 또는 고집적화된 트랜지스터를 실현할 수 있다. 예를 들어 채널 길이가 2nm 이상 30nm 이하인 트랜지스터를 제작할 수 있다.

[0127] 트랜지스터의 채널 형성 영역에는 캐리어 농도가 낮은 산화물 반도체를 사용하는 것이 바람직하다. 예를 들어 산화물 반도체의 채널 형성 영역의 캐리어 농도는  $1 \times 10^{18} \text{ cm}^{-3}$  이하,  $1 \times 10^{17} \text{ cm}^{-3}$  이하,  $1 \times 10^{16} \text{ cm}^{-3}$  이하,  $1 \times 10^{15} \text{ cm}^{-3}$  이하,  $1 \times 10^{14} \text{ cm}^{-3}$  이하,  $1 \times 10^{13} \text{ cm}^{-3}$  이하,  $1 \times 10^{12} \text{ cm}^{-3}$  이하,  $1 \times 10^{11} \text{ cm}^{-3}$  이하, 또는  $1 \times 10^{10} \text{ cm}^{-3}$  이하인 것이 바람직하다. 또한 채널 형성 영역의 캐리어 농도의 하한값에 대해서는 특별히 한정되지 않지만, 예를 들어  $1 \times 10^{-9} \text{ cm}^{-3}$  으로 할 수 있다.

[0128] 또한 산화물 반도체막의 캐리어 농도를 낮추는 경우에는, 산화물 반도체막 내의 불순물 농도를 낮추고 결함 준위 밀도를 낮춘다. 본 명세서 등에서 불순물 농도가 낮고 결함 준위 밀도가 낮은 것을 고순도 진성 또는 실질적으로 고순도 진성이라고 한다. 또한 캐리어 농도가 낮은 산화물 반도체를 고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체라고 부르는 경우가 있다.

[0129] 또한 고순도 진성 또는 실질적으로 고순도 진성인 산화물 반도체막은 결함 준위 밀도가 낮기 때문에 트랩 준위 밀도도 낮아지는 경우가 있다.

[0130] 또한 산화물 반도체의 트랩 준위에 포획된 전하는 소실되는 데 걸리는 시간이 길고, 마치 고정 전하처럼 작용하는 경우가 있다. 그러므로 트랩 준위 밀도가 높은 산화물 반도체에 채널 형성 영역이 형성되는 트랜지스터는 전기 특성이 불안정해지는 경우가 있다.

[0131] 따라서 트랜지스터의 전기 특성을 안정적으로 하기 위해서는, 산화물 반도체 내의 불순물 농도를 저감하는 것이 유효하다. 또한 산화물 반도체 내의 불순물 농도를 저감하기 위해서는, 균접한 막 내의 불순물 농도도 저감하는 것이 바람직하다. 불순물로서는 수소, 탄소, 질소 등이 있다. 또한 산화물 반도체 내의 불순물이란, 예를 들어 산화물 반도체를 구성하는 주성분 이외를 말한다. 예를 들어 농도가 0.1atomic% 미만인 원소는 불순물이라고 할 수 있다.

[0132] 또한 산화물 반도체의 밴드 갭은 실리콘의 밴드 갭(대표적으로는 1.1eV)보다 큰 것이 바람직하고, 바람직하게는 2eV 이상, 더 바람직하게는 2.5eV 이상, 더 바람직하게는 3.0eV 이상이다. 실리콘보다 밴드 갭이 큰 산화물 반도체를 사용함으로써 트랜지스터의 오프 전류(Ioff라고도 부름)를 저감할 수 있다.

[0133] 또한 Si 트랜지스터에서는 트랜지스터의 미세화가 진행됨에 따라 단채널 효과(ショート チャネル エフェクト: Short Channel Effect: SCE라고도 함)가 발현한다. 그러므로 Si 트랜지스터는 미세화가 어렵다. 단채널 효과가 발현하는 요인의 하나로서 실리콘의 밴드 갭이 작은 것을 들 수 있다. 한편, OS 트랜지스터는 밴드 갭이 큰 반도체 재료인 산화물 반도체를 사용하기 때문에 단채널 효과를 억제할 수 있다. 바꿔 말하면, OS 트랜지스터는 단채널 효과가 없거나 단채널 효과가 매우 적은 트랜지스터이다.

[0134] 또한 단채널 효과란 트랜지스터의 미세화(채널 길이의 축소)에 따라 현재화되는 전기 특성의 열화이다. 단채널 효과의 구체적인 예로서는 문턱 전압의 저하, 서브스레숄드 스윙값(S값이라고 표기하는 경우가 있음)의 증대, 누설 전류의 증대 등이 있다. 여기서 S값이란, 드레인 전압을 일정하게 하여 드레인 전류를 한 자릿수 변화시키는 서브스레숄드 영역에서의 게이트 전압의 변화량을 말한다.

[0135] 또한 단채널 효과에 대한 내성의 지표로서 특성 길이(Characteristic Length)가 널리 사용되고 있다. 특성 길이란, 채널 형성 영역의 페텐셜의 굴곡성의 지표이다. 특성 길이가 짧을수록 페텐셜이 가파르게 상승되기 때문에 단채널 효과에 강하다고 할 수 있다.

[0136] OS 트랜지스터는 축적형 트랜지스터이고, Si 트랜지스터는 반전형 트랜지스터이다. 따라서 Si 트랜지스터에 비하여 OS 트랜지스터는 소스 영역-채널 형성 영역 사이의 특성 길이 및 드레인 영역-채널 형성 영역 사이의 특성 길이가 짧다. 따라서 OS 트랜지스터는 Si 트랜지스터보다 단채널 효과에 강하다. 즉 채널 길이가 짧은 트랜지스터를 제작하고자 하는 경우에는, OS 트랜지스터가 Si 트랜지스터보다 적합하다.

[0137] 채널 형성 영역이 i형 또는 실질적으로 i형이 될 때까지 산화물 반도체의 캐리어 농도를 낮춘 경우에도, 단채널 트랜지스터에서는 Conduction-Band-Lowering(CBL) 효과에 의하여 채널 형성 영역의 전도대 하단이 낮아지기 때문에, 소스 영역 또는 드레인 영역과 채널 형성 영역 사이의 전도대 하단의 에너지 차이는 0.1eV 이상 0.2eV 이하까지 작아질 가능성이 있다. 이에 의하여, OS 트랜지스터는 채널 형성 영역이 n형 영역이 되고, 소스 영역

및 드레인 영역이  $n^+$ 형 영역이 되는  $n^+/n^-/n^+$ 의 축적형 junction-less 트랜지스터 구조 또는  $n^+/n^-/n^+$ 의 축적형 non-junction 트랜지스터 구조를 가지는 것으로 간주할 수도 있다.

[0138] OS 트랜지스터를 상기 구조로 함으로써, 반도체 장치를 미세화 또는 고집적화하여도 양호한 전기 특성을 가질 수 있다. 예를 들어 OS 트랜지스터의 채널 길이 또는 게이트 길이가 20nm 이하, 15nm 이하, 10nm 이하, 7nm 이하, 또는 6nm 이하이며, 1nm 이상, 3nm 이상, 또는 5nm 이상인 경우에도 양호한 전기 특성을 얻을 수 있다. 한편, Si 트랜지스터에서는 단채널 효과가 발현하기 때문에, 20nm 이하 또는 15nm 이하의 게이트 길이로 하기 어려운 경우가 있다. 따라서 OS 트랜지스터는 Si 트랜지스터에 비하여 채널 길이가 짧은 트랜지스터에 적합하게 사용할 수 있다. 또한 게이트 길이란, 트랜지스터 동작 시에 캐리어가 채널 형성 영역 내부를 이동하는 방향에서의 게이트 전극의 길이이다.

[0139] 또한 OS 트랜지스터를 미세화함으로써 트랜지스터의 고주파 특성을 향상시킬 수 있다. 구체적으로는 트랜지스터의 차단 주파수를 향상시킬 수 있다. OS 트랜지스터의 게이트 길이가 상기 범위 내에 있는 경우, 예를 들어 실온 환경하에서 트랜지스터의 차단 주파수를 50GHz 이상, 바람직하게는 100GHz 이상, 더 바람직하게는 150GHz 이상으로 할 수 있다.

[0140] <금속 산화물 내의 불순물>

[0141] 여기서 금속 산화물(산화물 반도체) 내에서의 각 불순물의 영향에 대하여 설명한다.

[0142] 상술한 바와 같이, 산화물 반도체에서 의도치 않게 알루미늄이 많이 포함되면, 상기 산화물 반도체의 물성에 영향을 미치는 경우가 있다. 예를 들어 알루미늄이 산화 상태( $Al_2O_3$  등)로 존재하면 산화물 반도체가 고저항화된다. 그리고 고저항화된 산화물 반도체를 트랜지스터의 채널 형성 영역에 사용하면 트랜지스터의 온 전류가 낮게 된다.

[0143] 한편, 알루미늄은 산소와의 결합 해리 에너지가 높아 캐리어 억제 원소로서 기능한다. 산화물 반도체 내에 알루미늄이 존재함으로써, 산소 결손(Vo)이 생성되기 어렵게 할 수 있다. Vo가 생성되기 어려운 산화물 반도체를 트랜지스터의 채널 형성 영역에 사용하면, 트랜지스터의 광 네거티브 바이어스 열화를 억제할 수 있다.

[0144] 그러므로, 트랜지스터의 신뢰성과 전기 특성의 양쪽이 양호하게 되도록 산화물 반도체 내의 알루미늄 농도를 낮게 하는 것이 바람직하다. 또는 트랜지스터의 온 전류가 충분히 높게 되도록 알루미늄 농도를 매우 낮게 하는 것이 바람직하다.

[0145] 예를 들어 STEM-EDX에 의하여 얻어지는 산화물 반도체의 채널 형성 영역에서의 알루미늄 농도는 0.01atomic% 이상인 것이 바람직하고, 또한 10atomic% 이하인 것이 바람직하고, 5atomic% 이하인 것이 더 바람직하고, 3atomic% 이하인 것이 더 바람직하고, 1atomic% 이하인 것이 더 바람직하고, 0.1atomic% 이하인 것이 더 바람직하다. 또는 0.01atomic% 이하이어도 좋다.

[0146] 또한 SIMS에 의하여 얻어지는 산화물 반도체의 채널 형성 영역에서의 알루미늄 농도는  $1 \times 10^{22} \text{ atoms/cm}^3$  이하가 바람직하고,  $1 \times 10^{21} \text{ atoms/cm}^3$  이하가 더 바람직하고,  $1 \times 10^{20} \text{ atoms/cm}^3$  이하가 더 바람직하고,  $5 \times 10^{19} \text{ atoms/cm}^3$  이하가 더 바람직하고,  $1 \times 10^{19} \text{ atoms/cm}^3$  이하가 더 바람직하고,  $5 \times 10^{18} \text{ atoms/cm}^3$  이하가 더 바람직하고,  $1 \times 10^{18} \text{ atoms/cm}^3$  이하가 더 바람직하다.

[0147] SIMS 분석은 그 원리상, 시료 표면 근방 및 재질이 상이한 막들의 계면 근방의 데이터를 정확히 얻기 어려운 것이 알려져 있다. 그래서, 막 내에서의 어느 원소의 농도를 SIMS로 분석하는 경우, 값에 극단적인 변동이 없고 거의 일정한 값이 얻어지는 영역에서의 평균값을 상기 원소의 농도로서 채용한다. 또한 측정 대상이 되는 막의 두께가 작은 경우, 인접한 막 내의 원소의 영향을 받아, 거의 일정한 값이 얻어지는 영역을 찾을 수 없을 경우가 있다. 이 경우, 상기 원소의 농도의 최댓값 또는 최솟값을 상기 막 내의 원소의 농도로서 채용할 수 있다. 또한 최댓값을 의미하는 피크, 최솟값을 의미하는 골짜기가 존재하지 않는 경우에는 변곡점의 값을 상기 원소의 농도로서 채용할 수 있다.

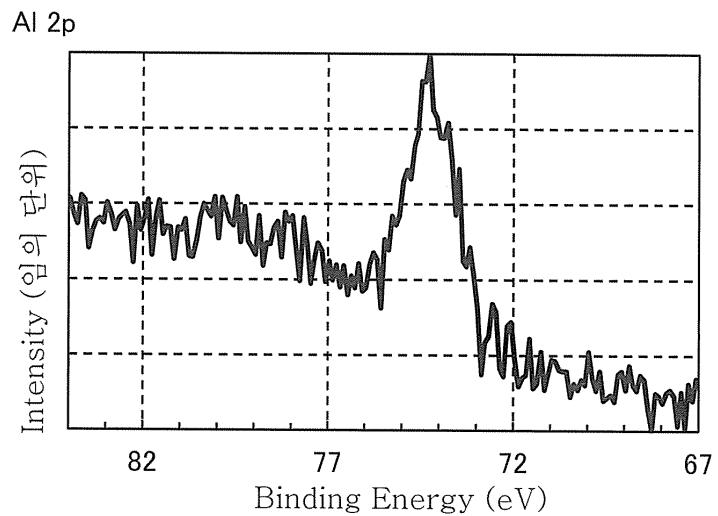

[0148] 또한 산화물 반도체를 XPS 분석함으로써 얻어지는 Al2p의 스펙트럼에 의하여 알루미늄의 존재, 나아가서는 존재하는 알루미늄의 상태를 확인할 수 있다. 예를 들어 74.2eV 이상 74.8eV 이하의 범위에 피크 위치를 가지는 경우에는, 알루미늄이 산화 상태로 존재한다고 할 수 있다.

[0149] 산화물 반도체에 14족 원소의 하나인 실리콘 또는 탄소가 포함되면 산화물 반도체에서 결함 준위가 형성된다.

그러므로 SIMS에 의하여 얻어지는 산화물 반도체의 채널 형성 영역에서의 탄소 농도는  $1 \times 10^{20} \text{ atoms/cm}^3$  이하, 바람직하게는  $5 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $3 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $3 \times 10^{18} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{18} \text{ atoms/cm}^3$  이하로 한다. 또한 SIMS에 의하여 얻어지는 산화물 반도체의 채널 형성 영역에서의 실리콘 농도는  $1 \times 10^{20} \text{ atoms/cm}^3$  이하, 바람직하게는  $5 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $3 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $3 \times 10^{18} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{18} \text{ atoms/cm}^3$  이하로 한다.

[0150] 또한 산화물 반도체에 질소가 포함되면, 캐리어인 전자가 발생하고 캐리어 농도가 증가되어 n형화되기 쉽다. 그러므로 질소가 포함되는 산화물 반도체를 반도체로서 사용한 트랜지스터는 노멀리 온 특성을 가지기 쉽다. 또는 산화물 반도체에 질소가 포함되면 트랩 준위가 형성되는 경우가 있다. 이 결과, 트랜지스터의 전기 특성이 불안정해지는 경우가 있다. 그러므로 SIMS에 의하여 얻어지는 산화물 반도체의 채널 형성 영역에서의 질소 농도는  $1 \times 10^{20} \text{ atoms/cm}^3$  이하, 바람직하게는  $5 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $5 \times 10^{18} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{18} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $5 \times 10^{17} \text{ atoms/cm}^3$  이하로 한다.

[0151] 또한 산화물 반도체에 포함되는 수소는 금속 원자와 결합하는 산소와 반응하여 물이 되기 때문에 산소 결손을 형성하는 경우가 있다. 상기 산소 결손에 수소가 들어감으로써, 캐리어인 전자가 생성되는 경우가 있다. 또한 수소의 일부가 금속 원자와 결합하는 산소와 결합하여, 캐리어인 전자를 생성하는 경우가 있다. 따라서 수소가 포함되는 산화물 반도체를 사용한 트랜지스터는 노멀리 온 특성을 가지기 쉽다. 그러므로 산화물 반도체의 채널 형성 영역에서의 수소는 가능한 한 저감되어 있는 것이 바람직하다. 구체적으로는 SIMS에 의하여 얻어지는 산화물 반도체의 채널 형성 영역에서의 수소 농도는  $1 \times 10^{20} \text{ atoms/cm}^3$  이하, 바람직하게는  $5 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{19} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $5 \times 10^{18} \text{ atoms/cm}^3$  이하, 더 바람직하게는  $1 \times 10^{18} \text{ atoms/cm}^3$  이하로 한다.

[0152] 또한 산화물 반도체에 알칼리 금속 또는 알칼리 토금속이 포함되면, 결함 준위를 형성하고 캐리어를 생성하는 경우가 있다. 따라서 알칼리 금속 또는 알칼리 토금속이 포함되는 산화물 반도체를 사용한 트랜지스터는 노멀리 온 특성을 가지기 쉽다. 그러므로 SIMS에 의하여 얻어지는 산화물 반도체의 채널 형성 영역 내의 알칼리 금속 또는 알칼리 토금속의 농도를  $1 \times 10^{18} \text{ atoms/cm}^3$  이하로, 바람직하게는  $2 \times 10^{16} \text{ atoms/cm}^3$  이하로 한다.

[0153] 불순물이 충분히 저감된 산화물 반도체를 트랜지스터의 채널 형성 영역에 사용함으로써, 안정된 전기 특성을 부여할 수 있다.

[0154] <성막 방법 1>

[0155] 다음으로 본 발명의 일 형태의 금속 산화물의 성막 방법에 대하여 설명한다. 이하에서는 ALD법을 이용한 성막 장치(이하 ALD 장치라고도 함)를 사용하여 금속 산화물을 성막하는 방법에 대하여 설명한다.

[0156] ALD법을 이용한 성막 장치에서는, 반응을 위한 제 1 원료 가스(전구체, 금속 전구체라고 부르는 경우도 있음)와 제 2 원료 가스(반응제, 산화제, 비금속 전구체라고 부르는 경우도 있음)를 번갈아 체임버에 도입하고, 이들 원료 가스의 도입을 반복함으로써 성막을 수행한다. 또한 원료 가스의 도입의 전환은, 예를 들어 각각의 스위칭 밸브(고속 밸브라고 부르는 경우도 있음)를 전환하여 수행할 수 있다. 또한 원료 가스를 도입할 때, 질소( $N_2$ ), 아르곤(Ar), 또는 헬륨(He) 등의 불활성 가스를 캐리어 가스로서 원료 가스와 함께 체임버에 도입하여도 좋다. 캐리어 가스를 사용함으로써, 원료 가스의 휘발성이 낮거나 증기압이 낮은 경우에도, 원료 가스가 배관 내부 및 밸브 내부에 흡착되는 것을 억제하고, 원료 가스를 체임버에 도입할 수 있다. 또한 형성되는 막의 균일성도 향상되어 바람직하다.

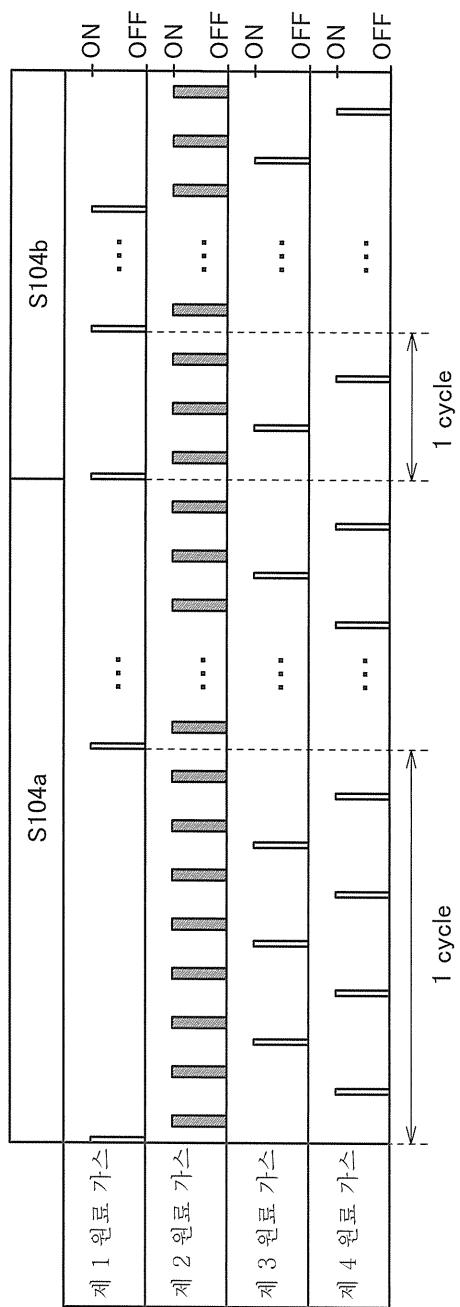

[0157] 본 발명의 일 형태인 3층의 층상 결정 구조를 가지는 금속 산화물을 ALD법을 사용하여 성막하는 방법의 일례에 대하여 도 1의 (A) 내지 (E)를 사용하여 설명한다.

[0158] 우선 제 1 단계로서, 도 1의 (A)에 나타낸 바와 같이, 전구체(11a)를 체임버에 도입하여 기판(10)의 표면에 전구체(11a)를 흡착시킨다.

- [0159] 여기서 도 1의 (A)에 나타낸 바와 같이, 전구체(11a)가 기판(10)의 표면에 흡착됨으로써, 표면 화학 반응의 자기 정지 기구가 작용하므로, 기판(10) 위의 전구체(11a)의 층 위에 전구체(11a)가 더 흡착되지는 않는다. 또한 표면 화학 반응의 자기 정지 기구가 작용하는 기판 온도의 적정 범위를 ALD Window라고도 한다. ALD Window는 전구체의 온도 특성, 증기압, 분해 온도 등으로 결정된다.

- [0160] 다음으로 제 2 단계로서, 불활성 가스(예를 들어 아르곤, 헬륨, 또는 질소)를 체임버에 도입하여 과잉한 전구체(11a) 및 반응 생성물 등을 체임버로부터 배출한다. 제 2 단계는 퍼지(purge)라고도 불린다.

- [0161] 제 2 단계에서는 불활성 가스를 체임버에 도입하는 대신에, 진공 배기를 수행하여 과잉한 전구체 및 반응 생성물 등을 체임버로부터 배출하여도 좋다. 또한 본 명세서 등에서 진공 배기란, 적어도 대기압보다 낮은 압력(감압 상태)으로 배기하는 것을 가리킨다.

- [0162] 다음으로 제 3 단계로서, 도 1의 (B)에 나타낸 바와 같이, 반응제(12a)(예를 들어 산화제)를 체임버에 도입하여 기판(10)의 표면에 흡착된 전구체(11a)와 반응시켜, 전구체(11a)를 구성하는 금속 원소를 기판(10)에 흡착시킨 채로 전구체(11a)에 포함되는 성분의 일부를 이탈시킨다. 이에 의하여, 전구체(11a)의 일부가 산화되어 형성된 산화물(13a)의 층이 기판(10)의 표면에 형성된다.

- [0163] 산화제로서는 오존( $O_3$ ), 산소( $O_2$ ), 물( $H_2O$ ), 이산화 질소( $N_2O$ ), 과산화 수소( $H_2O_2$ ), 및 이들의 플라스마, 라디칼, 이온 등을 들 수 있다.

- [0164] 또한 플라스마 ALD법을 수행하는 경우에는, 산화제로서 산소를 상시 계속 공급하고, 제 3 단계에서 플라스마를 발생시켜도 좋다. 이에 의하여, 제 3 단계에서 산소 플라스마가 형성되어 반응제(12a)로서 기능한다. 이 경우, 제 3 단계 이외에서 상기 온도로 가열된 산소와 반응하지 않는 전구체(11a)를 사용하면 좋다.

- [0165] 다음으로 제 4 단계로서, 불활성 가스의 도입 또는 진공 배기에 의하여 과잉한 반응제(12a) 및 반응 생성물 등을 체임버로부터 배출한다.

- [0166] 다음으로 도 1의 (C)에 나타낸 바와 같이, 전구체(11a)와 다른 금속 원소를 포함한 전구체(11b)를 도입하고 제 1 단계와 같은 공정을 수행하여 산화물(13a)의 층의 표면에 전구체(11b)를 흡착시킨다.

- [0167] 여기서 도 1의 (C)에 나타낸 바와 같이, 전구체(11b)가 산화물(13a)의 층에 흡착됨으로써, 표면 화학 반응의 자기 정지 기구가 작용하므로, 기판(10) 위의 전구체(11b)의 층 위에 전구체(11b)가 더 흡착되지는 않는다.

- [0168] 다음으로 제 2 단계와 마찬가지로, 불활성 가스의 도입 또는 진공 배기에 의하여 과잉한 전구체(11b) 및 반응 생성물 등을 체임버로부터 배출한다.

- [0169] 다음으로 도 1의 (D)에 나타낸 바와 같이, 반응제(12b)를 체임버에 도입하여 제 3 단계와 같은 공정을 수행한다. 이에 의하여, 전구체(11b)의 일부가 산화되어 형성된 산화물(13b)의 층이 산화물(13a)의 층 위에 형성된다.

- [0170] 반응제(12b)는 반응제(12a)와 같은 재료이어도 좋고, 다른 재료이어도 좋다.

- [0171] 다음으로 제 4 단계와 마찬가지로, 불활성 가스의 도입 또는 진공 배기에 의하여 과잉한 반응제(12b) 및 반응 생성물 등을 체임버로부터 배출한다.

- [0172] 또한 마찬가지로 제 1 단계 내지 제 4 단계를 수행하여 산화물(13c)의 층을 산화물(13b)의 층 위에 형성한다. 산화물(13c)의 층을 형성할 때에는 전구체(11a) 및 전구체(11b)와는 다른 금속 원소를 포함한 화합물을 전구체로서 사용한다. 반응제는 반응제(12a, 12b) 중 한쪽 또는 양쪽과 같은 재료이어도 좋고, 어느 쪽과도 다른 재료이어도 좋다.

- [0173] 이와 같이, 산화물(13a) 내지 산화물(13c)을 형성하는 공정을 반복적으로 수행함으로써, 산화물(13a) 내지 산화물(13c)의 적층 구조(14)가 반복되는 층상 결정 구조의 금속 산화물을 형성할 수 있다(도 1의 (E)). 즉 제 1 단계 내지 제 4 단계를 한 세트(1사이클이라고도 함)로 하여 산화물의 층을 형성할 수 있고, 상기 세트를 반복함으로써 복수의 산화물의 층이 적층된 층상 결정 구조를 형성할 수 있다.

- [0174] 또한 층상 결정 구조의 금속 산화물의 두께는 1nm 이상 100nm 미만이 바람직하고, 3nm 이상 20nm 미만이 더 바람직하다.

- [0175] 층상 결정 구조의 금속 산화물, 특히 CAAC 구조의 금속 산화물을 형성하는 데에 있어서, 도 1에 나타낸 공정은 기판을 가열하면서 수행하는 것이 바람직하다. 기판 온도를 200°C 이상 600°C 이하로 하는 것이 바람직하고,

300°C 이상 450°C 이하로 하는 것이 더 바람직하다. 또한 기판 온도는 사용하는 전구체의 어느 분해 온도보다 낮은 온도로 하는 것이 바람직하다. 이에 의하여, ALD법에 의한 성막 중에 사용되는 복수 종류의 전구체가 각각 분해되지 않고 대상물(예를 들어 기판)에 흡착될 수 있다.

[0176] 이러한 온도 범위에서 기판을 가열하면서 상기 성막을 수행함으로써, 제 1 단계 내지 제 4 단계의 각 과정에서, 전구체 또는 반응체 등에 포함되는 수소 또는 탄소 등의 불순물을 금속 산화물 내에서 제거할 수 있다. 예를 들어 금속 산화물 내의 탄소를 CO<sub>2</sub>, CO로서 방출시킬 수 있다. 또한 예를 들어 금속 산화물 내의 수소를 H<sub>2</sub>O로서 방출시킬 수 있다. 또한 상기 불순물의 제거와 동시에 금속 원자 및 산소 원자가 재배열되어, 각 산화물의 층을 높은 질서성으로 배열시킬 수 있다. 따라서 결정성이 높은 층상 결정 구조의 금속 산화물, 특히 CAAC 구조의 금속 산화물을 형성할 수 있다.

[0177] 또한 도 1의 (A)에서는 기판(10) 위에 전구체(11a)를 흡착시키는 구성을 예시하였지만, 이에 한정되지 않는다. 예를 들어 기판(10) 위에 절연막(산소, 질소, 실리콘, 알루미늄, 하프늄 등의 하나 또는 복수를 포함한 절연막) 또는 도전막(텅스텐, 탄탈럼, 몰리브데늄, 지르코늄, 알루미늄, 타이타늄 등의 하나 또는 복수를 포함한 도전막) 등을 제공하고, 그 위에 전구체(11a)를 흡착시켜도 좋다. 또는 기판(10) 위에 있는 절연막 및 도전막 등으로 형성된 구조물 위에 전구체(11a)를 흡착시켜도 좋다.

[0178] 상기 온도 범위에서 기판을 가열하면서 성막을 수행하기 때문에, 상기 성막에 사용하는 전구체는 분해 온도가 지나치게 낮지 않은 것이 바람직하다. 한편, 분해 온도가 지나치게 높으면, 취급이 어렵고 성막 시의 기판 온도를 매우 높게 할 필요가 있어 바람직하지 않다. 예를 들어 전구체의 분해 온도가 200°C 이상 700°C 이하인 것이 바람직하고, 300°C 이상 650°C 이하인 것이 더 바람직하고, 400°C 이상 600°C 이하인 것이 더 바람직하다.

[0179] 무기 전구체는 수소 및 탄소 등의 불순물이 적어, 성막되는 금속 산화물 내의 불순물 농도가 증가되는 것을 억제할 수 있다. 한편 무기 전구체는 유기 전구체에 비하여 분해 온도가 높은 경향이 있다.

[0180] 그래서 본 발명의 일 형태의 금속 산화물의 성막 방법에서는 유기 전구체를 사용하고, 기판을 가열하면서 성막하거나 불순물 제거 처리를 수행하는 것 등에 의하여, 성막되는 금속 산화물 내의 불순물 농도의 증가를 억제하는 것을 도모한다.

[0181] 불순물 제거 처리를 수행하는 빈도는 특별히 한정되지 않는다. 빈도가 높을수록 불순물의 제거가 용이해져 바람직하지만, 생산성이 낮아질 우려가 있다. 빈도가 낮을수록 금속 산화물의 성막 공정 시간을 단축할 수 있어 바람직하지만, 불순물을 충분히 제거할 수 없을 우려가 있다. 예를 들어 산화물(13a) 내지 산화물(13c)을 형성하는 공정을 반복적으로 수행하고, 산화물의 층을 복수 형성할 때마다 불순물 제거 처리를 수행하는 것이 바람직하다. 예를 들어 산화물(13a) 내지 산화물(13c) 중 어느 한 층을 형성할 때마다 불순물 제거 처리를 수행할 수도 있지만, 산화물의 층을 복수 형성할 때마다 또는 적층 구조(14)를 복수 형성할 때마다 불순물 제거 처리를 수행하면 공정이 간략화될 수 있어 더 바람직하다. 또는 금속 산화물의 성막이 끝난 후에, 불순물 제거 처리를 한 번 수행하여도 좋다.

[0182] 예를 들어 산화물의 층을 n층(n은 1 이상 100 이하의 정수, 바람직하게는 2 이상 50 이하의 정수, 더 바람직하게는 5 이상 30층 이하의 정수) 형성할 때마다 불순물 제거 처리를 수행하여도 좋다. 예를 들어 산화물(13a, 13b, 13c, 13a, 13b)을 이 순서대로 형성하고 불순물 제거 처리를 수행하고, 산화물(13c, 13a, 13b, 13c, 13a)을 이 순서대로 형성하고 불순물 제거 처리를 수행하고, 산화물(13b, 13c, 13a, 13b, 13c)을 이 순서대로 형성하고 불순물 제거 처리를 수행하는 것을 반복함으로써, 금속 산화물을 형성할 수 있다.

[0183] 또한 예를 들어 적층 구조(14)를 m층(m은 1 이상 50 이하의 정수, 바람직하게는 2 이상 30 이하의 정수, 더 바람직하게는 5 이상 10 이하의 정수) 형성할 때마다 불순물 제거 처리를 수행하여도 좋다.

[0184] 상술한 바와 같이 불순물 제거 처리로서는 예를 들어 플라스마 처리, 마이크로파 처리, 및 가열 처리가 있다. 또한 불순물 제거 처리는 광을 조사하면서 수행하여도 좋다.

[0185] 불순물 제거 처리를 수행하는 체임버는 제 1 단계 내지 제 4 단계를 수행하는 체임버와 같은 체임버이어도 좋고, 다른 체임버이어도 좋다. 즉 성막용 체임버와 불순물 제거 처리용 체임버가 같아도 좋고, 달라도 좋다.

[0186] 플라스마 처리 또는 마이크로파 처리를 수행할 때는 각각 기판의 온도를 실온(예를 들어 25°C) 이상, 100°C 이상, 200°C 이상, 300°C 이상, 또는 400°C 이상으로 하고, 또한 500°C 이하 또는 450°C 이하로 하는 것이 바람직하다. 또한 가열 처리의 온도는 100°C 이상, 200°C 이상, 300°C 이상, 또는 400°C 이상으로 하고, 또한 500°C 이하 또는 450°C 이하로 하는 것이 바람직하다. 불순물 제거 처리를 수행할 때의 온도는 특히 트랜지스터 또는

반도체 장치의 제작 공정에서의 최고 온도 이하의 온도로 함으로써, 생산성을 저하시키지 않고 금속 산화물 내의 불순물의 함유량을 저감할 수 있기 때문에 바람직하다.

[0187] 또한 상술한 제 3 단계에서 산소 플라스마를 사용하는 경우, 제 3 단계의 처리 시간을 길게 함으로써 불순물 제거 처리로서의 플라스마 처리를 겸할 수 있다. 예를 들어 제 3 단계의 처리 시간을 여러 번에 한 번, 다른 번 보다 길게 함으로써 불순물 제거 처리를 겸하는 공정으로 하여도 좋다.

[0188] 여기서 마이크로파 처리란, 예를 들어 마이크로파를 사용하여 고밀도 플라스마를 발생시키는 전원을 가진 장치를 사용한 처리를 말한다. 또한 본 명세서 등에서 마이크로파란, 300MHz 이상 300GHz 이하의 주파수를 가지는 전자기파를 가리키는 것으로 한다. 마이크로파 처리는 마이크로파 여기 고밀도 플라스마 처리라고도 할 수 있다.

[0189] 마이크로파 처리에서는, 예를 들어 마이크로파를 사용하여 고밀도 플라스마를 발생시키는 전원을 가지는 마이크로파 처리 장치를 사용하는 것이 바람직하다. 여기서 마이크로파 처리 장치의 주파수는 300MHz 이상 300GHz 이하가 바람직하고, 2.4GHz 이상 2.5GHz 이하가 더 바람직하고, 예를 들어 2.45GHz로 할 수 있다. 고밀도 플라스마를 사용함으로써 밀도가 높은 산소 라디칼을 생성할 수 있다. 또한 마이크로파 처리 장치의 마이크로파를 인가하는 전원의 전력은 1000W 이상 10000W 이하가 바람직하고, 2000W 이상 5000W 이하가 더 바람직하다. 또한 마이크로파 처리 장치는 기판 측에 RF를 인가하는 전원을 가져도 좋다. 또한 기판 측에 RF를 인가함으로써, 고밀도 플라스마에 의하여 생성된 산소 이온을 막 내에 효율적으로 도입할 수 있다.

[0190] 마이크로파 처리는 감압하에서 수행하는 것이 바람직하고, 압력은 10Pa 이상 1000Pa 이하가 바람직하고, 300Pa 이상 700Pa 이하가 더 바람직하다. 또한 처리 온도는 실온(25°C) 이상 750°C 이하가 바람직하고, 300°C 이상 500°C 이하가 더 바람직하고, 400°C 이상 450°C 이하로 할 수 있다.

[0191] 또한 마이크로파 처리 또는 플라스마 처리를 수행한 후에, 외기에 노출시키지 않고 연속하여 가열 처리를 수행하여도 좋다. 가열 처리의 온도는 예를 들어 100°C 이상 750°C 이하인 것이 바람직하고, 300°C 이상 500°C 이하인 것이 더 바람직하고, 400°C 이상 450°C 이하인 것이 더 바람직하다.

[0192] 마이크로파 처리는 예를 들어 산소 가스와 아르곤 가스를 사용하여 수행할 수 있다. 여기서 산소 유량비( $O_2/(O_2+Ar)$ )는 0%보다 크고 100% 이하로 한다. 바람직하게는 산소 유량비( $O_2/(O_2+Ar)$ )를 0%보다 크고 50% 이하로 한다. 더 바람직하게는 산소 유량비( $O_2/(O_2+Ar)$ )를 10% 이상 40% 이하로 한다. 더 바람직하게는 산소 유량비( $O_2/(O_2+Ar)$ )를 10% 이상 30% 이하로 한다.

[0193] 또한 가열 처리는 질소 가스 분위기 또는 불활성 가스 분위기, 혹은 산화성 가스를 10ppm 이상, 1% 이상, 또는 10% 이상 포함하는 분위기에서 수행한다. 예를 들어 질소 가스와 산소 가스의 혼합 분위기에서 가열 처리를 수행하는 경우, 산소 가스를 20% 정도로 하는 것이 바람직하다. 또한 가열 처리는 감압 상태에서 수행하여도 좋다. 또는 질소 가스 분위기 또는 불활성 가스 분위기에서 가열 처리를 수행한 후에, 이탈된 산소를 보충하기 위하여 산화성 가스를 10ppm 이상, 1% 이상, 또는 10% 이상 포함하는 분위기에서 가열 처리를 수행하여도 좋다. 또한 가열 처리는 초건조 공기(물의 함유량이 20ppm 이하, 바람직하게는 1ppm 이하, 바람직하게는 10ppb 이하의 공기)의 분위기하에서 수행하여도 좋다.

[0194] 가열 처리에서 사용하는 가스는 고순도화되어 있는 것이 바람직하다. 예를 들어 가열 처리에서 사용하는 가스에 포함되는 수분량은 1ppb 이하가 바람직하고, 0.1ppb 이하가 더 바람직하고, 0.05ppb 이하가 더 바람직하다. 고순도화된 가스를 사용하여 가열 처리를 수행함으로써, 금속 산화물 내에 수분 등이 들어가는 것을 가능한 한 방지할 수 있다.

[0195] 이와 같이 가열 처리를 수행함으로써, 금속 산화물에 포함되는 수소 또는 탄소 등의 불순물을 제거할 수 있다. 예를 들어 금속 산화물 내의 탄소를  $CO_2$  및  $CO$ 로서 방출시키고, 금속 산화물 내의 수소를  $H_2O$ 로서 방출시킬 수 있다.

[0196] 또한 금속 산화물의 성막 후(소정의 총수의 적층 구조(14)를 모두 형성한 후, 다른 재료 또는 다른 조성의 막을 형성하기 전)에 가열 처리를 수행하는 것이 바람직하다. 특히 상기 ALD법에 의한 성막 후에 외기에 노출시키지 않고 연속하여 가열 처리를 수행하는 것이 바람직하다. 이로써 금속 산화물의 성막 후에, 막 내의 수소 또는 탄소 등의 불순물을 증가시키지 않고 가열 처리를 수행할 수 있다. 상기 가열 처리는 100°C 이상 500°C 이하에서 수행하는 것이 바람직하고, 200°C 이상 500°C 이하가 더 바람직하고, 250°C 이상 500°C 이하가 더 바람직하고, 300°C 이상 500°C 이하가 더 바람직하고, 350°C 이상 450°C 이하가 더 바람직하고, 400°C 이상 450°C 이하

가 더 바람직하다. 또한 가열 처리는 질소 가스 분위기 또는 불활성 가스 분위기, 혹은 산화성 가스를 10ppm 이상, 1% 이상, 또는 10% 이상 포함하는 분위기에서 수행한다. 또한 가열 처리는 감압 상태에서 수행하여도 좋다. 또는 질소 가스 분위기 또는 불활성 가스 분위기에서 가열 처리를 수행한 후에, 이탈된 산소를 보충하기 위하여 산화성 가스를 10ppm 이상, 1% 이상, 또는 10% 이상 포함하는 분위기에서 가열 처리를 수행하여도 좋다.

[0197] 이와 같이 가열 처리를 수행함으로써, 금속 산화물에 포함되는 수소 또는 탄소 등의 불순물을 제거할 수 있다. 예를 들어 금속 산화물 내의 탄소를 CO<sub>2</sub> 및 CO로서 방출시키고, 금속 산화물 내의 수소를 H<sub>2</sub>O로서 방출시킬 수 있다. 또한 상기 불순물의 제거와 동시에 금속 원자 및 산소 원자가 재배열되어 결정성을 향상시킬 수 있다. 따라서 결정성이 높은 층상 결정 구조의 금속 산화물, 특히 상기 CAAC 구조의 금속 산화물을 형성할 수 있다.

[0198] 또한 금속 산화물의 성막 후에 플라스마 처리 또는 마이크로파 처리를 수행하여도 좋다.

[0199] 또한 도 1에서는 산화물(13a) 내지 산화물(13c)의 적층 구조(14)가 반복되는 구조에 대하여 설명하였지만, 본 발명은 이에 한정되는 것이 아니다. 예를 들어 단층, 2층, 또는 4층 이상의 산화물의 층이 반복적으로 형성되는 금속 산화물로 하여도 좋다. 또한 도 1에서는 산화물(13a), 산화물(13b), 산화물(13c)의 순서를 바꾸지 않고 반복적으로 적층이 수행되었지만, 이에 한정되는 것이 아니다. 예를 들어 적층할 때마다 산화물(13a), 산화물(13b), 산화물(13c)의 순서를 바꿔도 좋다. 또한 막의 도중에서 산화물(13a), 산화물(13b), 산화물(13c)의 조성을 변경하여도 좋다. 또한 도 1에서는 산화물(13a), 산화물(13b), 산화물(13c)과 같이 상이한 산화물의 층이 인접되도록 제공되어 있지만, 이에 한정되는 것이 아니다. 예를 들어 산화물(13a), 산화물(13a), 산화물(13b), 산화물(13b), 산화물(13c)과 같이, 같은 산화물의 층을 연속적으로 제공하는 구성으로 하여도 좋다.

[0200] 또한 본 명세서에서 이하에 특별히 기재되어 있지 않으면, 반응제 또는 산화제로서 오존, 산소, 물을 사용하는 경우, 이들은 가스 상태 및 분자 상태에 한정되지 않고, 플라스마 상태, 라디칼 상태, 및 이온 상태의 것도 포함하는 것으로 한다. 플라스마 상태, 라디칼 상태, 또는 이온 상태의 산화제를 사용하여 성막하는 경우, 후술하는 라디칼 ALD 장치 또는 플라스마 ALD 장치를 사용하면 좋다.

[0201] 전구체에 포함되는 탄소 또는 수소 등의 불순물을 제거하기 위해서는, 상기 전구체에 산화제를 충분히 반응시키는 것이 바람직하다. 예를 들어 산화제를 도입하는 펄스 시간을 길게 하면 좋다. 금속 산화물의 성막 공정에서, 1사이클에서의 산화제를 공급하는 시간의 바람직한 예는 상술한 바와 같다. 또는 산화제를 여러 번 도입하여도 좋다. 산화제를 여러 번 도입하는 경우, 같은 종류의 산화제를 도입하여도 좋고, 상이한 종류의 산화제를 도입하여도 좋다. 예를 들어 물을 제 1 산화제로서 체임버에 도입한 후에 진공 배기를 수행하고, 수소를 포함하지 않는 오존 또는 산소를 제 2 산화제로서 체임버에 도입한 후에 진공 배기를 수행하여도 좋다.

[0202] 또한 앞의 설명에서는, 제 1 원료 가스를 체임버에 도입한 후에 제 2 원료 가스를 체임버에 도입하는 예를 설명하였지만, 본 발명은 이에 한정되지 않는다. 제 2 원료 가스를 체임버에 도입한 후에 제 1 원료 가스를 체임버에 도입하여도 좋다. 즉 먼저 제 3 단계 및 제 4 단계를 수행하고, 이어서 제 1 단계, 제 2 단계, 제 3 단계, 및 제 4 단계를 수행하고, 이후 제 1 단계 내지 제 4 단계를 반복 수행함으로써 성막을 수행하여도 좋다. 또한 제 3 단계 및 제 4 단계를 여러 번 반복한 후에 제 1 단계 내지 제 4 단계를 반복적으로 수행함으로써 성막을 하여도 좋다.

[0203] 이러한 식으로, 제 1 단계 전에 제 3 단계 및 제 4 단계를 한 번씩 또는 여러 번 수행하면 체임버 내의 성막 분위기를 제어할 수 있기 때문에 바람직하다. 예를 들어 제 3 단계에서 산화제로서 O<sub>3</sub> 및 O<sub>2</sub>를 도입함으로써 체임버 내를 산소 분위기로 할 수 있다. 체임버 내를 산소 분위기로 하여 성막을 하면, 형성되는 막 내의 산소 농도를 높일 수 있어 바람직하다. 또한 상기 막의 하지가 되는 절연체 및 산화물에도 산소를 공급할 수 있다. 이와 같은 방법을 사용하여 형성된 반도체 장치는 양호한 특성을 가지고 높은 신뢰성을 얻을 수 있다. 또한 예를 들어 제 3 단계에서 산화제로서 물을 도입함으로써 피형성면에 친수기를 형성할 수 있다. 이에 의하여 전구체의 흡착성을 더 향상시킬 수 있다.

[0204] 또한 제 1 단계 및 제 2 단계 후에, 제 3 단계에서의 제 2 원료 가스의 도입과 제 4 단계에서의 진공 배기 또는 불활성 가스의 도입을 여러 번 반복하여 수행하여도 좋다. 즉 제 1 단계, 제 2 단계, 제 3 단계, 제 4 단계, 제 3 단계, 제 4 단계와 같이, 제 3 단계와 제 4 단계를 반복하여 수행한 후에 제 1 단계 및 제 2 단계를 수행하여도 좋다.

[0205] 예를 들어 제 3 단계에서 산화제로서 O<sub>3</sub> 및 O<sub>2</sub>를 도입하고, 제 4 단계에서 불활성 가스의 도입을 수행하고, 이

공정을 여러 번 반복하여도 좋다. 또한 제 3 단계와 제 4 단계를 반복하는 경우, 반드시 같은 종류의 원료 가스의 도입을 반복할 필요는 없다. 예를 들어 첫 번째의 제 3 단계에서 산화제로서  $H_2O$ 를 사용하고, 두 번째 이후의 제 3 단계에서 산화제로서  $O_2$ 를 사용하여도 좋다.

[0206] 이러한 식으로, 체임버 내에서 산화제의 도입과 불활성 가스의 도입(또는 진공 배기)을 단시간에 여러 번 반복함으로써, 기판 표면에 흡착된 전구체로부터 불필요한 수소 원자, 탄소 원자 등을 더 확실하게 제거하고, 체임버 외에 배제할 수 있다. 또한 산화제의 종류를 2종류로 늘림으로써, 기판 표면에 흡착된 전구체로부터 불필요한 수소 원자 등을 더 많이 제거할 수 있다. 이와 같이, 성막 중에 수소 원자가 막 내로 들어가지 않도록 함으로써, 형성된 막에 포함되는 물, 수소 등을 저감할 수 있다.

[0207] 이와 같은 방법을 사용함으로써, TDS 분석에서  $100^{\circ}C$  이상  $700^{\circ}C$  이하 또는  $100^{\circ}C$  이상  $500^{\circ}C$  이하의 표면 온도의 범위에서, 물 분자의 이탈량이  $1.0 \times 10^{13}$  molecule/cm<sup>2</sup> 이상  $1.0 \times 10^{16}$  molecule/cm<sup>2</sup> 이하, 더 바람직하게는  $1.0 \times 10^{13}$  molecule/cm<sup>2</sup> 이상  $3.0 \times 10^{15}$  molecule/cm<sup>2</sup> 이하인 막을 형성할 수 있다.

[0208] ALD법은 열 에너지를 사용하여 전구체와 반응제를 반응시켜 수행하는 성막 방법이다. 전구체 및 반응제의 반응에 필요한 온도는 이들의 온도 특성, 증기압, 분해 온도 등에 따라 결정되지만,  $100^{\circ}C$  이상  $600^{\circ}C$  이하, 바람직하게는  $200^{\circ}C$  이상  $600^{\circ}C$  이하, 더 바람직하게는  $300^{\circ}C$  이상  $600^{\circ}C$  이하이다.

[0209] 또한 상기 전구체 및 반응제의 반응에 더하여, 제 3 원료 가스로서 플라스마 여기된 반응제도 체임버에 도입함으로써 처리를 수행하는 ALD법을 플라스마 ALD법이라고 부르는 경우가 있다. 이 경우, 제 3 원료 가스의 도입부에는 플라스마 생성 장치가 제공된다. 플라스마의 생성에는 유도 결합 플라스마(Inductively Coupled Plasma: ICP)를 사용할 수 있다. 또한 이에 대하여 전구체 및 반응제의 반응을 열 에너지로 수행하는 ALD법을 열 ALD법이라고 부르는 경우가 있다.

[0210] 플라스마 ALD법에서는, 제 3 단계에서 플라스마 여기된 반응제를 도입함으로써 성막을 수행한다. 또는 제 1 단계 내지 제 4 단계를 반복하여 수행하는 것과 동시에, 플라스마 여기된 반응제(제 2 반응제)를 도입함으로써 성막을 수행한다. 이 경우, 제 3 단계에서 도입되는 반응제를 제 1 반응제라고 부른다. 플라스마 ALD법에서 제 3 원료 가스로서 사용하는 제 2 반응제에는 상기 산화제와 같은 재료를 사용할 수 있다. 즉 제 2 반응제로서, 플라스마 여기된 오존, 산소, 및 물을 사용할 수 있다. 또한 제 2 반응제로서는 산화제 외에 질화제를 사용하여도 좋다. 질화제로서는 질소( $N_2$ ) 또는 암모니아( $NH_3$ )를 사용할 수 있다. 또한 질소( $N_2$ )와 수소( $H_2$ )의 혼합ガ스를 질화제로서 사용할 수 있다. 예를 들어 질소( $N_2$ ) 5%, 수소( $H_2$ ) 95%의 혼합 가스를 질화제로서 사용할 수 있다. 플라스마 여기된 질소 또는 암모니아를 도입하면서 성막을 수행함으로써 금속 질화막 등의 질화막을 형성할 수 있다.

[0211] 또한 제 2 반응제의 캐리어 가스로서 아르곤(Ar), 헬륨(He), 또는 질소( $N_2$ )를 사용하여도 좋다. 아르곤, 헬륨, 또는 질소 등의 캐리어 가스를 사용함으로써, 플라스마의 방전이 용이해지고, 플라스마 여기된 제 2 반응제가 용이하게 생성되기 때문에 바람직하다. 또한 플라스마 ALD법을 사용하여 금속 산화막 등의 산화막을 형성하는 경우, 캐리어 가스로서 질소를 사용하면 막 내에 질소가 혼입되어 원하는 막질을 얻을 수 없는 경우가 있다. 이 경우, 캐리어 가스로서 아르곤 또는 헬륨을 사용하는 것이 바람직하다.

[0212] ALD법은 매우 얇은 막을 균일한 막 두께로 성막할 수 있다. 또한 요철을 가지는 면에 대해서도 표면 피복률이 높다.

[0213] 또한 플라스마 ALD법에 의하여 성막함으로써, 열 ALD법에 비하여 더 낮은 온도에서의 성막이 가능하다. 플라스마 ALD법은 예를 들어  $100^{\circ}C$  이하에서도 성막 속도를 저하시키지 않고 성막을 수행할 수 있는 경우가 있다.

[0214] 또한 플라스마 ALD법을 수행하는 경우에는, 유도 결합형 플라스마(ICP) 또는 전자 사이클로트론 공명 플라스마(ECR) 등의 플라스마원과 기판의 사이를 띄우고 플라스마를 발생시킴으로써 플라스마 대미지를 억제할 수 있다.

[0215] <금속 산화물의 결정 내의 원자 배열>

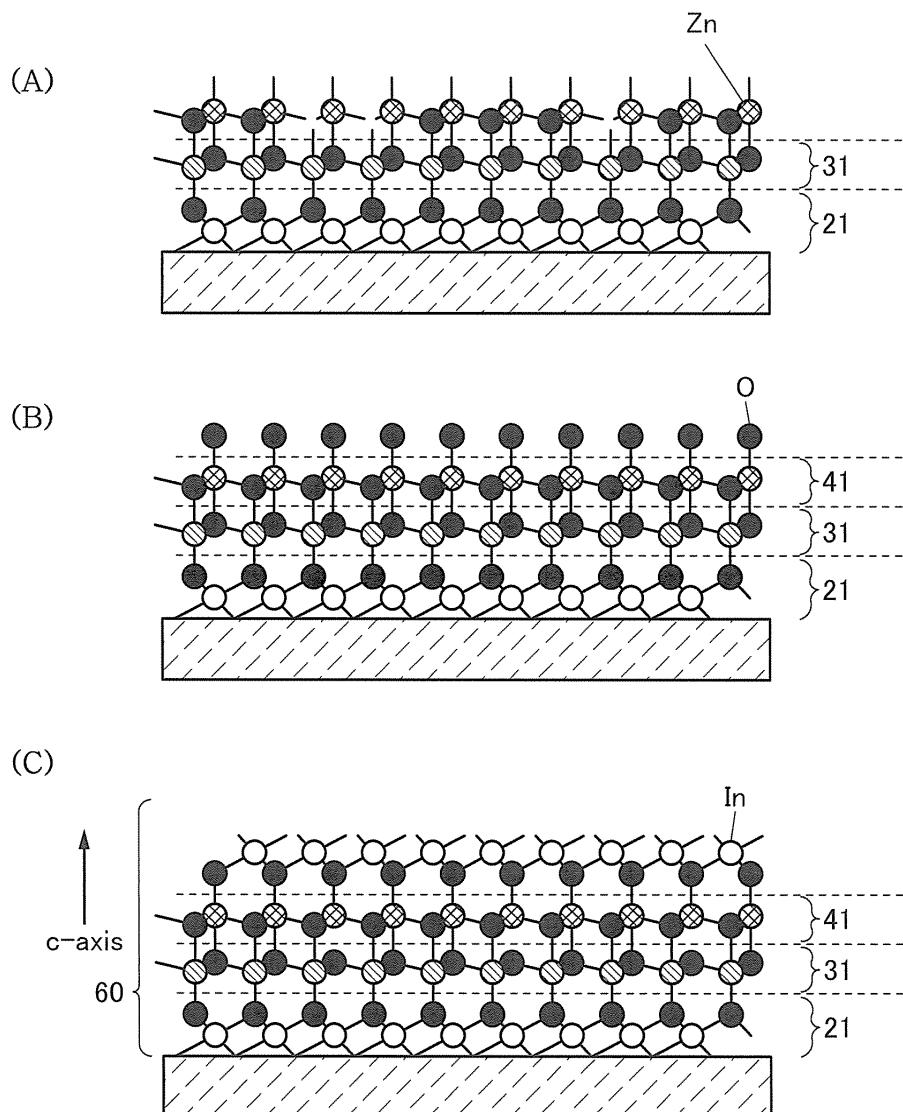

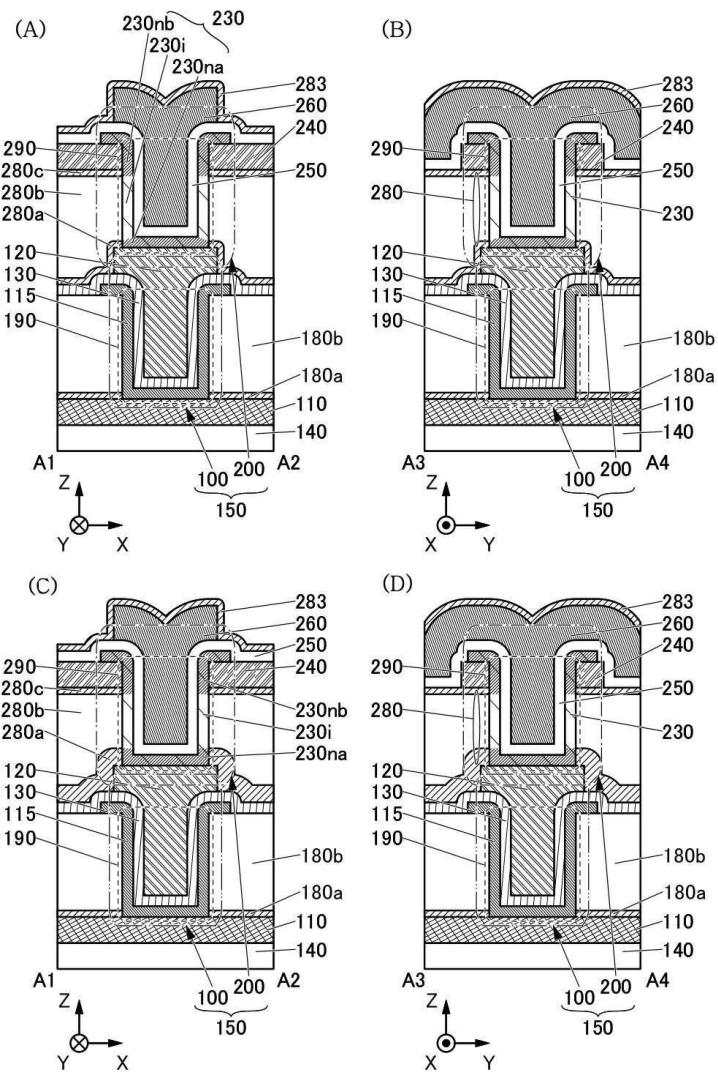

[0216] 여기서 층상 결정 구조의 금속 산화물이 In-M-Zn 산화물인 경우의 결정 내의 원자 배열에 대하여 도 2의 (A) 내지 (D) 및 도 3의 (A) 내지 (D)를 사용하여 설명한다. 또한 도 2의 (B), (D), 도 3의 (B), (D)에서는 원자를 공(원형)으로 나타내고, 금속 원자와 산소 원자의 결합을 선으로 나타내었다. 도 2의 (B), (D), 도 3의 (B), (D)에서 In-M-Zn 산화물의 결정 구조에서의 c축 방향은 도면 중의 화살표로 나타내었다(c-axis). 또한 In-M-Zn

산화물의 결정 구조에서의 a-b면 방향은 도 2의 (B), (D), 도 3의 (B), (D) 중의 화살표로 나타낸 c축 방향에 수직인 방향이다.

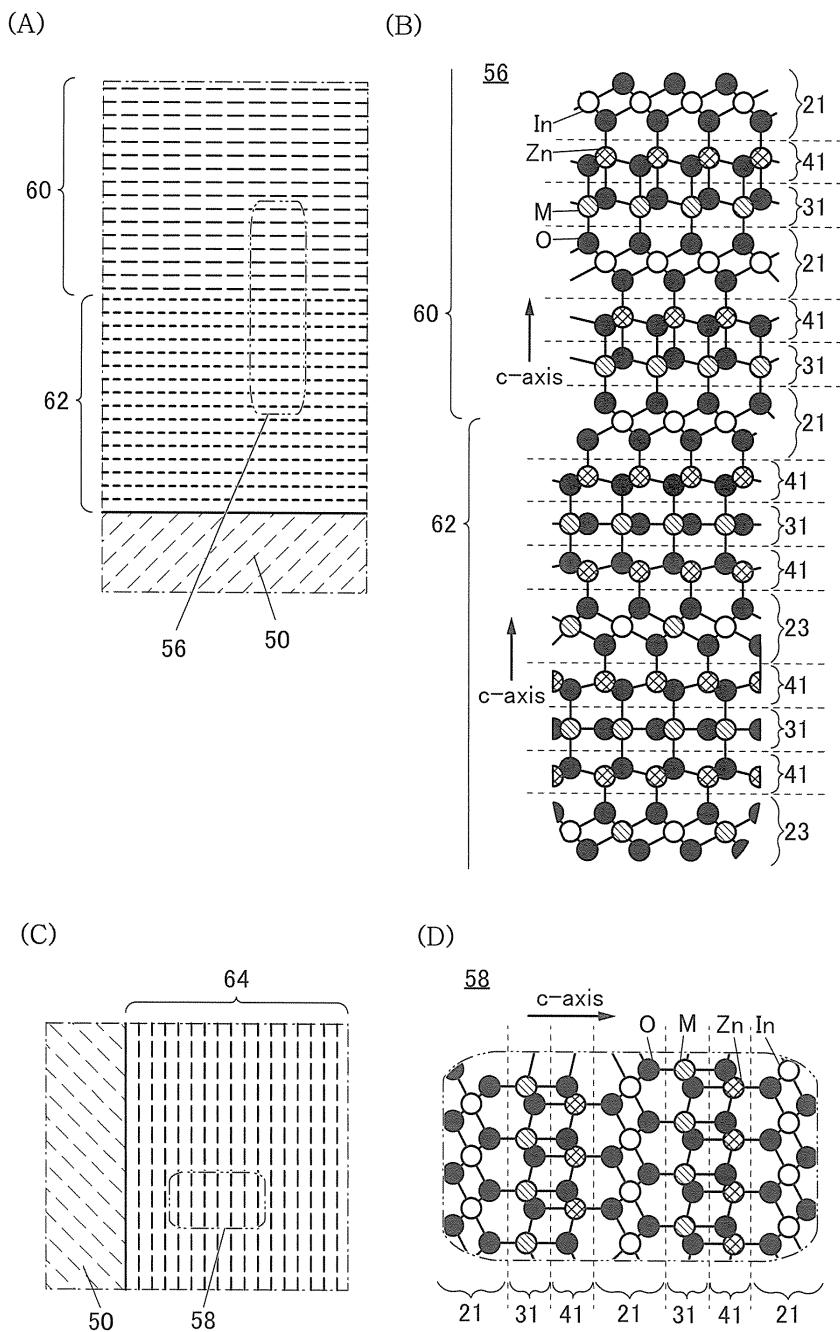

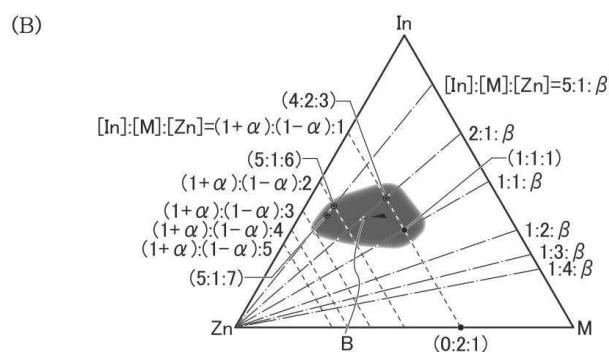

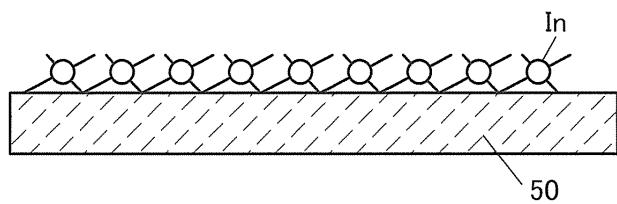

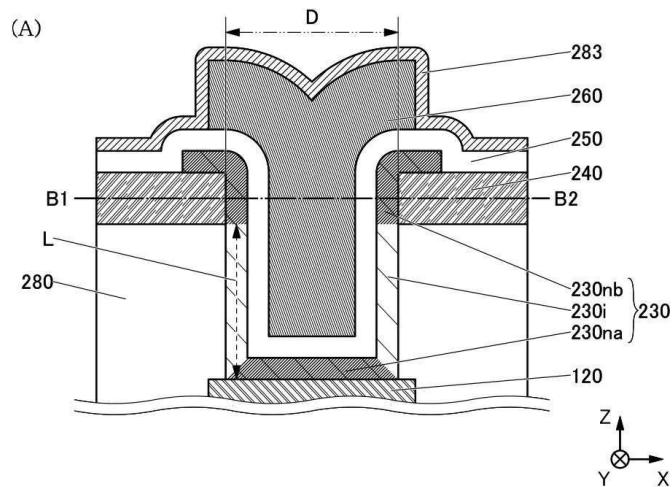

[0217] 도 2의 (A)는 구조체(50)에 형성된 In-M-Zn 산화물을 포함한 산화물(60)을 나타낸 도면이다. 여기서 구조체란, 트랜지스터 등의 반도체 장치를 구성하는 요소를 가리킨다. 구조체(50)에는 기판, 게이트 전극, 소스 전극, 및 드레인 전극 등의 도전체, 게이트 절연막, 충간 절연막, 하지 절연막 등의 절연체, 금속 산화물 또는 실리콘 등의 반도체 등이 포함된다. 도 2의 (A)에서는 구조체(50)의 피성막면이 기판(도시하지 않았음)에 평행하게 배치되는 경우를 나타내었다.

[0218] 도 2의 (B)는 도 2의 (A)에서의 산화물(60)의 일부인 영역(53)에서의 결정 내의 원자 배열을 나타낸 확대도이다. 여기서 도 2의 (A) 및 (B)에 나타낸 산화물(60)의 조성은  $In:M:Zn=1:1:1$ [원자수비]이고, 결정 구조는  $YbFe_2O_4$ 형 구조로 한다. 또한 원소 M은 +3가의 금속 원소로 한다.

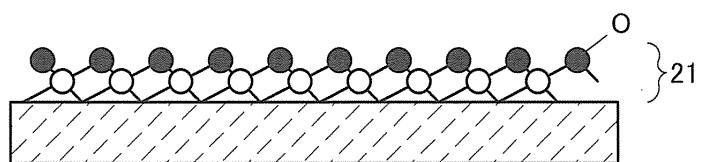

[0219] 도 2의 (B)에 나타낸 바와 같이, 산화물(60)이 가지는 결정은 인듐(In)과 산소를 포함한 층(21), 원소 M과 산소를 포함한 층(31), 아연(Zn)과 산소를 포함한 층(41)이 순차적으로 반복하여 적층되어 있다. 층(21), 층(31), 및 층(41)은 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하게 배치되어 있다. 즉 산화물(60)의 a-b면은 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하고, 산화물(60)의 c축은 구조체(50)의 피성막면의 법선 방향에 평행 또는 실질적으로 평행하다.

[0220] 도 2의 (B)에 나타낸 바와 같이, 상기 결정이 가지는 층(21), 층(31), 층(41)의 각각이 하나의 금속 원소와 산소로 구성됨으로써 결정성 좋게 배열되고, 상기 금속 산화물의 이동도를 높일 수 있다.

[0221] 또한  $In:M:Zn=1:1:1$ [원자수비]의 In-M-Zn 산화물은 도 2의 (B)에 나타낸 구조에 한정되는 것이 아니다. 층(21), 층(31), 층(41)의 적층 순서가 변경되어도 좋다. 예를 들어 층(21), 층(41), 층(31)의 순서로 반복적으로 적층되어도 좋다. 또는 층(21), 층(31), 층(41), 층(21), 층(41), 층(31)의 순서로 반복적으로 적층되어도 좋다. 또한 층(31)의 원소 M의 일부가 아연으로 치환되고, 층(41)의 아연의 일부가 원소 M으로 치환되어도 좋다.

[0222] 상기에서는 조성이  $In:M:Zn=1:1:1$ [원자수비]인 In-M-Zn 산화물을 형성하는 예를 나타내었지만, 조성식이  $In_{(1-\alpha)}M_{(1-\alpha)}O_3(ZnO)_m$ ( $\alpha$ 는 0보다 크고 1보다 작은 실수,  $m$ 은 양의 수)으로 나타내어지는 결정성 In-M-Zn 산화물은 마찬가지로 층상 결정 구조를 가질 수 있다. 이 예로서, 도 2의 (C) 및 (D)를 사용하여 조성이  $In:M:Zn=1:3:4$ [원자수비]인 In-M-Zn 산화물에 대하여 설명한다.

[0223] 도 2의 (C)는 구조체(50)에 형성된 In-M-Zn 산화물을 포함한 산화물(62)을 나타낸 도면이다. 도 2의 (D)는 도 2의 (C)에서의 산화물(62)의 일부인 영역(54)에서의 결정 내의 원자 배열을 나타낸 확대도이다.

[0224] 도 2의 (D)에 나타낸 바와 같이, 산화물(62)이 가지는 결정은 인듐(In)과 원소 M과 산소를 포함한 층(23), 아연(Zn)과 산소를 포함한 층(41), 및 원소 M과 산소를 포함한 층(31)을 가진다. 산화물(62)에서 복수의 층은 층(23), 층(41), 층(31), 층(41)의 순서로 반복적으로 적층되어 있다. 층(23), 층(31), 및 층(41)은 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하게 배치되어 있다. 즉 산화물(62)의 a-b면은 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하고, 산화물(62)의 c축은 구조체(50)의 피성막면의 법선 방향에 평행 또는 실질적으로 평행하다.

[0225] 또한  $In:M:Zn=1:3:4$ [원자수비]의 In-M-Zn 산화물은 도 2의 (D)에 나타낸 구조에 한정되는 것이 아니고,  $In:M:Zn=1:3:4$ [원자수비]의 범위 내에서 구조가 변화되어도 좋다. 예를 들어 층(23), 층(31), 층(41)의 적층 순서가 변경되어도 좋다. 또한 층(31)의 원소 M의 일부가 아연으로 치환되고, 층(41)의 아연의 일부가 원소 M으로 치환되어도 좋다. 또한 층(23) 대신에 층(21) 또는 층(31)이 형성되어도 좋다.

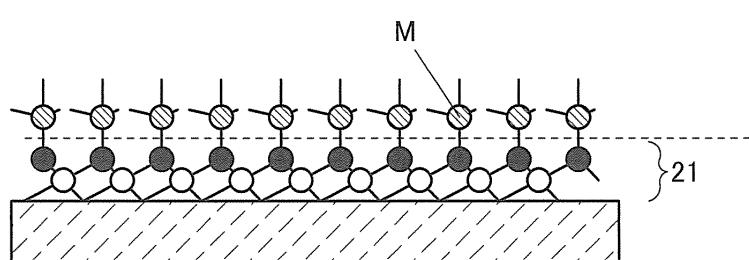

[0226] 또한 도 3의 (A)에 나타낸 바와 같이, 구조체(50) 위에 산화물(62)을 형성하고 그 위에 산화물(60)을 형성하는 적층 구조로 하여도 좋다. 여기서 도 3의 (B)는 도 3의 (A)에서의 산화물(62) 및 산화물(60)의 일부인 영역(56)에서의 결정 내의 원자 배열을 나타낸 확대도이다.

[0227] 상술한 바와 같이, 산화물(62)은  $In:M:Zn=1:3:4$ [원자수비]의 In-M-Zn 산화물이고, 산화물(60)은  $In:M:Zn=1:1:1$ [원자수비]의 In-M-Zn 산화물이다. 즉 도 3의 (A)에 나타낸 산화물은 막의 도중에서 원자수비가 변화된 산화막이다. 또한 도 3의 (B)에 나타낸 바와 같이, 산화물(62)을 층상 결정 구조로 함으로써, 산화물(62) 위의 산화물(60)의 결정성을 양호하게 할 수 있다.

- [0228] 또한 산화물(62) 및 산화물(60)은 도 3의 (B)에 나타낸 구조에 한정되는 것이 아니고, 상술한 바와 같이 산화물(62) 및 산화물(60)의 구조를 변화시켜도 좋다. 또한 도 3의 (B)에서 산화물(62)과 산화물(60)의 경계에 층(21)을 배치하였지만, 이에 한정되는 것이 아니다. 예를 들어 산화물(62)과 산화물(60)의 경계에 층(23)이 형성되어 있어도 좋다.

- [0229] 상술한 바와 같이, ALD법에서는 종횡비가 높은 구조에 대한 성막이 가능하고, 구조체의 측면에 대해서도 피복성 좋게 성막할 수 있다. ALD법을 사용함으로써, 피성막면의 방향에 상관없이 CAAC 구조 등의 결정성 금속 산화물을 용이하게 형성할 수 있다. 예를 들어 구조체가 볼록 형상 또는 오목 형상을 가지는 경우에도, 구조체의 상면, 밑면, 측면, 및 경사진 면에 대하여 피복성 좋게 금속 산화물을 형성할 수 있다. 즉 각 피성막면에서 법선 방향으로 실질적으로 일정한 막 두께를 가지는 금속 산화물을 형성할 수 있다. 구조체의 상면, 밑면, 측면, 및 경사진 면 각각에 형성된 금속 산화물에서, 최대 막 두께에 대한 최소 막 두께의 비를 0.5 이상 1 이하, 바람직 하게는 0.7 이상 1 이하, 더 바람직하게는 0.9 이상 1 이하로 할 수 있다. 이때 금속 산화물이 결정 구조를 가지는 경우, 그 c축은 각 피성막면의 법선 방향에 실질적으로 평행한 방향으로 배향된다. 즉 c축은 각 피성막면에 수직으로 배향된다.

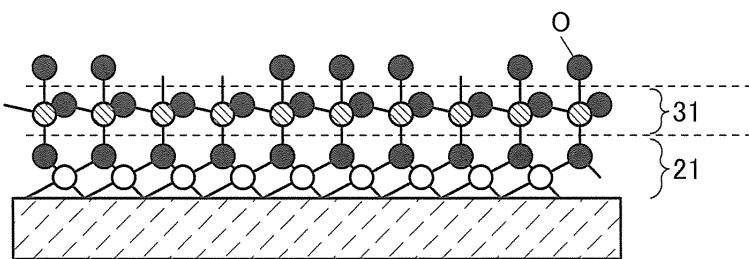

- [0230] 여기서 도 3의 (C)에서는 구조체(50)의 피성막면이 기판(도시하지 않았음)에 수직으로 배치되고, 구조체(50)의 표면에 산화물(64)이 형성되는 경우를 나타내었다. 도 3의 (D)는 도 3의 (C)에서의 산화물(64)의 일부인 영역(58)의 확대도이다. 도 3의 (D)에서는 구조체(50)의 측면에 인듐(In)을 포함한 층(21)과, 원소 M을 포함한 층(31)과, 아연(Zn)을 포함한 층(41)이 피성막면에 대하여 적층되어 있는 모습을 나타내었다. 인듐을 포함한 층(21)은 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하게 배치되고, 그 위에 원소 M을 포함한 층(31)이 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하게 배치되고, 또한 그 위에 아연을 포함한 층(41)이 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하게 배치되어 있다. 즉 산화물(60)의 a-b면은 구조체(50)의 피성막면에 평행 또는 실질적으로 평행하고, 산화물(60)의 c축은 구조체(50)의 피성막면의 법선 방향에 평행 또는 실질적으로 평행하다. 또한 도 3의 (C) 및 (D)에서는 In:M:Zn=1:1:1[원자수비]의 In-M-Zn 산화물의 예를 나타내었지만, 다른 원자수비의 산화물도 마찬가지로, 피성막면이 기판에 수직으로 배치된 구조체(50)의 표면에 형성될 수 있다.

- [0231] 또한 상기에서 In:M:Zn=1:1:1[원자수비] 및 In:M:Zn=1:3:4[원자수비]의 금속 산화물의 예를 나타내었지만, 본 발명은 이에 한정되는 것이 아니다.

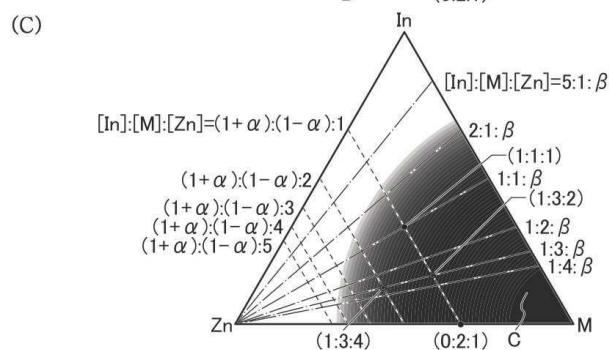

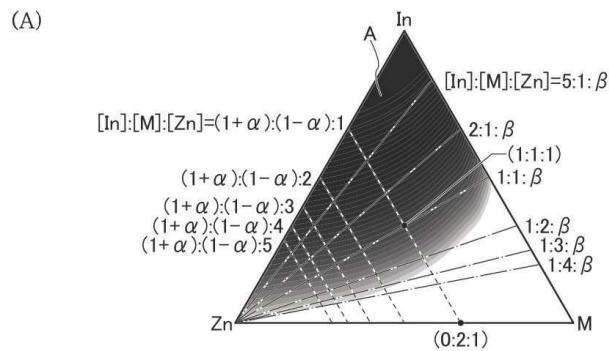

- [0232] 이하에서 도 4의 (A), (B), 및 (C)를 사용하여, 본 발명의 일 형태에서 설명하는 산화물에 사용할 수 있는 금속 산화물에 포함되는 인듐, 원소 M, 및 아연의 원자수비의 바람직한 범위에 대하여 설명한다. 또한 도 4의 (A), (B), 및 (C)에는 산소의 원자수비를 기재하지 않았다. 또한 금속 산화물에 포함되는 인듐, 원소 M, 및 아연의 원자수비 각각의 항을 [In], [M], 및 [Zn]으로 한다.

- [0233] 도 4의 (A), (B), 및 (C)에서 파선은 원자수비가  $[In]:[M]:[Zn]=(1+\alpha):(1-\alpha):1 (-1\leq\alpha\leq 1)$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=(1+\alpha):(1-\alpha):2$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=(1+\alpha):(1-\alpha):3$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=(1+\alpha):(1-\alpha):4$ 인 라인, 및 원자수비가  $[In]:[M]:[Zn]=(1+\alpha):(1-\alpha):5$ 인 라인을 나타낸다.

- [0234] 또한 일점쇄선은 원자수비가  $[In]:[M]:[Zn]=5:1:\beta (\beta \geq 0)$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=2:1:\beta$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=1:1:\beta$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=1:2:\beta$ 인 라인, 원자수비가  $[In]:[M]:[Zn]=1:3:\beta$ 인 라인, 및 원자수비가  $[In]:[M]:[Zn]=1:4:\beta$ 인 라인을 나타낸다.

- [0235] 또한 도 4의 (A), (B), 및 (C)에 나타낸, 원자수비가  $[In]:[M]:[Zn]=0:2:1$  및 그 균방값인 금속 산화물은 스피넬형 결정 구조를 가지기 쉽다.

- [0236] 또한 금속 산화물 내에서 복수의 상이 공존하는 경우가 있다(2상 공존, 3상 공존 등). 예를 들어 원자수비가  $[In]:[M]:[Zn]=0:2:1$ 의 균방값인 경우, 스피넬형 결정 구조와 충상 결정 구조의 2상이 공존하기 쉽다. 또한 원자수비가  $[In]:[M]:[Zn]=1:0:0$ 의 균방값인 경우, 빅스비아이트(bixbyite)형 결정 구조와 충상 결정 구조의 2상이 공존하기 쉽다. 금속 산화물 내에서 복수의 상이 공존하는 경우, 상이한 결정 구조들 사이에서 결정립계가 형성되는 경우가 있다.

- [0237] 도 4의 (A)에 나타낸 영역 A는 금속 산화물에 포함되는 인듐, 원소 M, 및 아연의 원자수비의 바람직한 범위의 일례에 대하여 나타낸 것이다.

- [0238] 금속 산화물은 인듐의 함유율을 높임으로써 캐리어 이동도(전자 이동도)를 높일 수 있다. 따라서 인듐의 함유

율이 높은 금속 산화물은 인듐의 함유율이 낮은 금속 산화물에 비하여 캐리어 이동도가 높다.

[0239] 한편, 금속 산화물 내의 인듐 및 아연의 함유율이 낮아지면 캐리어 이동도는 낮아진다. 따라서 원자수비가  $[In]:[M]:[Zn]=0:1:0$  및 그 근방값인 경우(예를 들어 도 4의 (C)에 나타낸 영역 C)에는 절연성이 높아진다. 또한 영역 C는 상술한 스피넬형 결정 구조를 가지기 쉬운 영역을 포함하기 때문에, 스피넬형 결정 구조를 가지기 쉬운 영역을 피하는 조성으로 하는 것이 바람직하다.

[0240] 예를 들어 채널 형성 영역 및 저저항 영역에 사용되는 금속 산화물은 캐리어 이동도가 높은, 도 4의 (A)의 영역 A로 나타내어지는 원자수비를 가지는 것이 바람직하다. 채널 형성 영역 및 저저항 영역에 사용되는 금속 산화물은, 예를 들어  $In:Ga:Zn=4:2:3$  내지 4.1 및 그 근방값 정도가 되도록 하면 좋다. 또한 예를 들어  $In:Ga:Zn=1:1:1$  및 그 근방값 정도가 되도록 하면 좋다. 한편, 채널 형성 영역 및 저저항 영역을 둘러싸도록 금속 산화물을 제공하는 경우에는 절연성이 비교적 높은, 도 4의 (C)의 영역 C로 나타내어지는 원자수비를 가지는 것이 바람직하다. 채널 형성 영역 및 저저항 영역을 둘러싸도록 제공되는 금속 산화물은, 예를 들어  $In:Ga:Zn=1:3:4$  및 그 근방값 정도, 또는  $In:Ga:Zn=1:3:2$  및 그 근방값 정도가 되도록 하면 좋다. 또는 채널 형성 영역 및 저저항 영역을 둘러싸도록 제공되는 금속 산화물로서는, 채널 형성 영역 및 저저항 영역에 사용되는 금속 산화물과 같은 금속 산화물을 사용하여도 좋다.

[0241] 특히 도 4의 (B)에 나타낸 영역 B에서는, 영역 A 중에서도 캐리어 이동도가 높고 신뢰성이 높으며 우수한 금속 산화물이 얻어진다.

[0242] 또한 영역 B는  $[In]:[M]:[Zn]=4:2:3$  내지 4.1 및 그 근방값을 포함한다. 근방값에는 예를 들어  $[In]:[M]:[Zn]=5:3:4$ 가 포함된다. 또한 영역 B는  $[In]:[M]:[Zn]=5:1:6$  및 그 근방값, 그리고  $[In]:[M]:[Zn]=5:1:7$  및 그 근방값을 포함한다. 또한 영역 B는  $[In]:[M]:[Zn]=1:1:1$  및 그 근방값을 포함한다.

[0243] 이상과 같이, 상기 금속 산화물의 전기 전도 특성은 원자수비에 따라 크게 다르다. 상술한 바와 같이 ALD법을 사용하여 금속 산화물을 성막함으로써, 각 원자수비에 따른 충상 결정 구조를 가지는 금속 산화물을 성막할 수 있다. 따라서 ALD법을 사용함으로써 요구되는 특성에 맞추어 금속 산화물을 성막할 수 있다.

#### <성막 방법 2>

[0245] 다음으로 도 2의 (A) 및 (B)에 나타낸 In-M-Zn 산화물을 포함한 산화물(60)의 자세한 형성 방법에 대하여 도 5의 (A) 내지 (D) 및 도 6의 (A) 내지 (C)를 사용하여 설명한다.

[0246] 먼저 도 5의 (A)에 나타낸 바와 같이, 인듐을 포함한 전구체를 포함하는 원료 가스를 체임버에 도입하여 구조체 (50)의 표면에 상기 전구체를 흡착시킨다.

[0247] 인듐을 포함한 전구체의 알루미늄 함유량은 0.001ppm 이상, 0.01ppm 이상, 또는 0.1ppm 이상인 것이 바람직하고, 1000ppm 이하인 것이 바람직하고, 500ppm 이하인 것이 더 바람직하고, 100ppm 이하인 것이 더 바람직하고, 50ppm 이하인 것이 더 바람직하고, 10ppm 이하인 것이 더 바람직하고, 1ppm 이하인 것이 더 바람직하다. 또한 인듐을 포함한 전구체의 알루미늄 함유량은 0.001ppm 이하이어도 좋다.

[0248] 또한 본 실시형태에서 사용하는 전구체로서는 두 번 이상의 증류(정류(精留)라고도 함)를 수행하여 정제된 전구체를 사용하는 것이 바람직하다. 이러한 전구체를 사용함으로써, 불순물이 적은 금속 산화물을 성막하는 것이 용이해지므로 바람직하다. 증류를 여러 번 수행함으로써, 전구체 제조에 사용하는 출발 재료에 기인한 불순물이 전구체에 잔존하는 것을 더 억제할 수 있어 바람직하다. 또한 본 발명은 상기에 한정되지 않고, 증류를 한번 수행함으로써, 즉 단증류를 수행함으로써 정제된 전구체를 사용하여도 좋다. 단증류로 함으로써 제조 비용을 절감할 수 있어 바람직하다.

[0249] 여기서 전구체를 포함하는 원료 가스에는 전구체 외에, 아르곤, 헬륨, 또는 질소 등의 캐리어 가스가 포함된다.

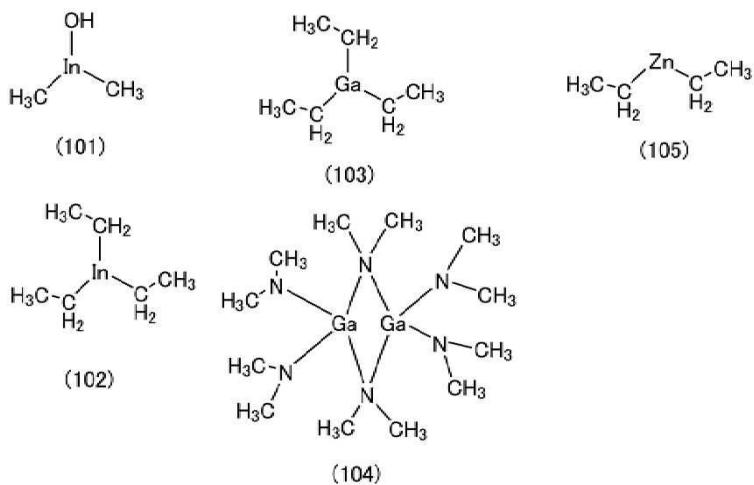

[0250] 인듐을 포함한 전구체로서는 예를 들어 트라이메틸인듐(하기 구조식(101)), 트라이에틸인듐(하기 구조식(102)), 에틸다이메틸인듐, 트리스(1-메틸에틸)인듐, 트리스(2,2,6,6-테트라메틸-3,5-헵테이디아이온산)인듐, 사이클로펜타다이에닐인듐, 인듐(III)아세틸아세토네이트, (다이에틸포스피노)다이메틸인듐, 클로로다이메틸인듐, 브로모다이메틸인듐, 다이메틸(2-프로파노레이트)인듐, 트라이플루오로인듐(플루오린화 인듐(III)), 염화 인듐(III), 브로민화 인듐(III), 및 아이오딘화 인듐(III)이 있다.

[0251] 다음으로 상기 원료 가스의 도입을 멈추고 체임버 내를 퍼지하여 과잉한 전구체 및 반응 생성물 등을 체임버로

부터 배출한다.

[0252] 그리고 도 5의 (B)에 나타낸 바와 같이, 산소를 포함한 산화제를 반응제로서 체임버에 도입하여, 흡착된 전구체와 반응시켜, 인듐을 기판에 흡착시킨 채로 인듐 이외의 성분을 이탈시킴으로써, 인듐과 산소가 결합된 층(21)을 형성한다.

[0253] 산화제로서 오존( $O_3$ ), 산소( $O_2$ ), 물( $H_2O$ ), 이산화 질소( $N_2O$ ), 과산화 수소( $H_2O_2$ ), 및 이들의 플라스마, 라디칼, 이온을 사용할 수 있다.

[0254] 산화제를 공급할 때, 가스 내의 오존의 비율을 10% 이상으로 하는 것이 바람직하고, 20% 이상이 더 바람직하고, 30% 이상이 더 바람직하고, 40% 이상이 더 바람직하고, 50% 이상이 더 바람직하고, 60% 이상이 더 바람직하고, 70% 이상이 더 바람직하고, 80% 이상이 더 바람직하고, 90% 이상이 더 바람직하고, 100%가 특히 바람직하다. 오존의 비율이 클수록, 금속의 산화가 촉진되고 금속 산화물 내의 탄소 농도를 저감할 수 있어 바람직하다.

[0255] 다음으로 상기 산화제의 도입을 멈추고 체임버 내를 퍼지하여 과잉한 반응제 및 반응 생성물 등을 체임버로부터 배출한다.

[0256] 다음으로 도 5의 (C)에 나타낸 바와 같이, 원소 M을 포함한 전구체를 포함하는 원료 가스를 체임버에 도입하여 층(21) 위에 상기 전구체를 흡착시킨다. 여기서 원소 M으로서는 갈륨 또는 주석을 사용하는 것이 바람직하다.

[0257] 원소 M을 포함한 전구체의 알루미늄 함유량은 0.001ppm 이상, 0.01ppm 이상, 또는 0.1ppm 이상인 것이 바람직하고, 1000ppm 이하인 것이 바람직하고, 500ppm 이하인 것이 더 바람직하고, 100ppm 이하인 것이 더 바람직하고, 50ppm 이하인 것이 더 바람직하고, 10ppm 이하인 것이 더 바람직하고, 1ppm 이하인 것이 더 바람직하다. 또한 원소 M을 포함한 전구체의 알루미늄 함유량은 0.001ppm 이하이어도 좋다.

[0258] 갈륨을 포함한 전구체로서는 예를 들어 트라이메틸갈륨, 트라이에틸갈륨(하기 구조식(103)), 트리스(다이메틸아마이드)갈륨(하기 구조식(104)), 트라이페닐갈륨, 다이에틸(3-메틸-2,4-사이클로프로페인다이엔-1-일)갈륨, [4-(1,1-다이메틸)페닐]다이메틸갈륨, 다이메틸(4-메틸페닐)갈륨, 다이메틸페닐갈륨, 베틸다이페닐갈륨, 에틸다이메틸갈륨, 다이메틸메틸렌갈륨, 갈륨(III)아세틸아세토네이트, 트리스(2,2,6,6-테트라메틸-3,5-헵테인다이온산)갈륨, 다이메틸(2-메틸-2-프로파노레이토)갈륨, 메톡시다이메틸갈륨, 하이드록시다이메틸갈륨, (메탄싸이올레이토)다이메틸갈륨, 클로로다이메틸갈륨, 클로로다이에틸갈륨, 클로로다이프로필갈륨, 브로모다이메틸갈륨, 브로모다이에틸갈륨, 다이메틸요오드갈륨, 클로로비스(2,2-다이메틸프로필)갈륨, 플루오린화 갈륨(III), 염화갈륨(III), 브로민화 갈륨(III), 및 아이오딘화 갈륨(III)이 있다.

[0259] 주석을 포함한 전구체로서는 예를 들어 테트라메틸주석, 테트라에틸주석, 테트라에텐일주석, 테트라알릴주석, 트라이뷰틸바이닐주석, 알릴트라이뷰틸주석, 트라이뷰틸스타닐아세틸렌, 트라이뷰틸페닐주석, 클로로트라이메틸주석, 클로로트라이에틸주석, 플루오린화 주석(IV), 염화 주석(IV), 브로민화 주석(IV), 및 아이오딘화 주석(IV)이 있다.

[0260] 다음으로 상기 원료 가스의 도입을 멈추고 체임버 내를 퍼지하여 과잉한 전구체 및 반응 생성물을 체임버로부터 배출한다.

[0261] 다음으로 도 5의 (D)에 나타낸 바와 같이, 반응제로서 산화제를 체임버에 도입하여, 흡착된 전구체와 반응시켜, 원소 M을 기판에 흡착시킨 채로 원소 M 이외의 성분을 이탈시킴으로써, 원소 M과 산소가 결합된 층(31)을 형성한다. 이때 층(31) 위에 흡착된 산소의 일부가 후술하는 층(41)을 구성하는 경우가 있다.

[0262] 다음으로 상기 산화제의 도입을 멈추고 체임버 내를 퍼지하여 과잉한 반응제 및 반응 생성물을 체임버로부터 배출한다.

[0263] 다음으로 도 6의 (A)에 나타낸 바와 같이, 아연을 포함한 전구체를 포함하는 원료 가스를 체임버에 도입하여 층(31) 위에 전구체를 흡착시킨다. 이때 아연과 산소가 결합된 층(41)의 일부가 형성되는 경우가 있다.

[0264] 아연을 포함한 전구체의 알루미늄 함유량은 0.001ppm 이상, 0.01ppm 이상, 또는 0.1ppm 이상인 것이 바람직하고, 1000ppm 이하인 것이 바람직하고, 500ppm 이하인 것이 더 바람직하고, 100ppm 이하인 것이 더 바람직하고, 50ppm 이하인 것이 더 바람직하고, 10ppm 이하인 것이 더 바람직하고, 1ppm 이하인 것이 더 바람직하다. 또한 아연을 포함한 전구체의 알루미늄 함유량은 0.001ppm 이하이어도 좋다.

[0265] 아연을 포함한 전구체로서는 예를 들어 다이메틸아연, 다이에틸아연(하기 구조식(105)), 비스(1-메틸에틸)아연, 비스(1,1-다이메틸에틸)아연, 다이뷰틸아연, 다이에텐일아연, 다이사이클로헥실아연, 비스(2,2,6,6-테트라메틸-

3,5-헵테인다이온산)아연, 플루오린화 아연, 염화 아연, 클로로메틸아연, 브로민화 아연, 브로모메틸아연, 및 아이오딘화 아연이 있다.

- [0266] 다음으로 상기 원료 가스의 도입을 멈추고 체임버 내를 퍼지하여 과잉한 전구체 및 반응 생성물 등을 체임버로부터 배출한다.

- [0267] 다음으로 도 6의 (B)에 나타낸 바와 같이, 반응체로서 산화제를 체임버에 도입하여, 흡착된 전구체와 반응시켜, 아연을 기판에 흡착시킨 채로 아연 이외의 성분을 이탈시킴으로써, 아연과 산소가 결합된 층(41)을 형성한다.

- [0268] 여기서 도 5의 (B), (D), 및 도 6의 (B)에 나타낸 3개의 공정에서의 산화제를 공급하는 시간의 합계는 10초 이상이 바람직하고, 30초 이상이 더 바람직하고, 60초 이상이 더 바람직하고, 90초 이상이 더 바람직하고, 120초 이상이 더 바람직하고, 또한 150초 이하, 200초 이하, 250초 이하, 또는 300초 이하가 바람직하다.

- [0269] 산화제를 공급하는 시간이 길수록 산화물(60) 내의 탄소 농도를 저감할 수 있어 바람직하다. 한편, 산화제를 공급하는 시간이 짧을수록, 산화물(60)을 성막하기 위하여 필요한 시간이 짧게 되어 바람직하다.

- [0270] 다음으로 상기 산화제의 도입을 멈추고 체임버 내를 퍼지하여 과잉한 반응제 및 반응 생성물 등을 체임버로부터 배출한다.

- [0271] 다음으로 층(41) 위에 상술한 방법으로 층(21)을 다시 형성한다(도 6의 (C)). 이상의 방법을 반복함으로써 기판 또는 구조체 위에 산화물(60)을 형성할 수 있다.

- [0272] 여기서, 앞에서 열거한 전구체의 일례를 이하에 나타낸다.

- [0273] [화학식 1]

- [0274]

- [0275] 또한 앞에서 열거한 전구체에는 금속 원소 외에, 탄소 및 염소 중 한쪽 또는 양쪽을 포함하는 것이 있다. 탄소를 포함한 전구체를 사용하여 형성된 막에는 탄소가 포함되는 경우가 있다. 또한 염소 등의 할로젠을 포함한 전구체를 사용하여 형성된 막에는 염소 등의 할로젠이 포함되는 경우가 있다.

- [0276] 도 5의 (A) 내지 (D) 및 도 6의 (A) 내지 (C)에 나타낸 공정은 기판을 가열하면서 수행하는 것이 바람직하다. 예를 들어 기판 온도를 150°C 이상, 200°C 이상, 또는 250°C 이상으로 하는 것이 바람직하다. 또한 600°C 이하, 500°C 이하, 450°C 이하, 400°C 이하, 또는 전구체의 분해 온도 이하로 하는 것이 바람직하다. 또한 산화제로서 오존을 사용하는 경우에는 오존의 분해 온도 이하로 하는 것이 바람직하다. 이와 같은 온도 범위에서 기판을 가열하면서 상기 성막을 수행함으로써, 도 5의 (A) 내지 도 6의 (C)의 각 과정에서, 전구체 또는 반응제 등에 포함되는 수소 또는 탄소 등의 불순물을 금속 산화물 내에서 제거할 수 있다. 예를 들어 금속 산화물 내의 탄소를 CO<sub>2</sub> 및 CO로서 방출시키고, 금속 산화물 내의 수소를 H<sub>2</sub>O로서 방출시킬 수 있다. 또한 상기 불순물의 제거와 동시에 금속 원자 및 산소 원자가 재배열되어, 각 산화물의 층을 높은 질서성으로 배열시킬 수 있다. 따라서 결정부를 가지는 금속 산화물을 형성할 수 있다. 또한 결정성이 높은 층상 결정 구조의 금속 산화물, 예를 들어 CAAC 구조의 금속 산화물을 형성할 수 있다.

- [0277] 또한 산화물(60)의 성막 중에 상술한 불순물 제거 처리를 간헐적으로 수행하는 것이 바람직하다. 예를 들어 층

(21), 층(31), 및 층(41)의 3층 구조를 n번(n은 1 이상 50 이하의 정수, 바람직하게는 2 이상 30 이하의 정수, 더 바람직하게는 5 이상 10 이하의 정수) 형성할 때마다 상술한 불순물 제거 처리를 수행하는 것이 바람직하다. 또한 산화물(60) 성막 후에도 불순물 제거 처리를 수행하는 것이 바람직하다.

[0278] 불순물 제거 처리를 수행함으로써, 금속 산화물을 포함되는 수소 또는 탄소 등의 불순물을 제거할 수 있다. 예를 들어 금속 산화물 내의 탄소를 CO<sub>2</sub> 및 CO로서 방출시키고, 금속 산화물 내의 수소를 H<sub>2</sub>O로서 방출시킬 수 있다. 또한 상기 불순물의 제거와 동시에 금속 원자 및 산소 원자가 재배열되어 결정성을 향상시킬 수 있다. 따라서 결정부를 가지는 금속 산화물을 형성할 수 있다. 또한 결정성이 높은 층상 결정 구조의 금속 산화물, 특히 상기 CAAC 구조의 금속 산화물을 형성할 수 있다.

[0279] 상술한 바와 같이 ALD법을 사용하여 산화물(60)을 형성함으로써, 페성막면의 법선 방향에 실질적으로 평행하게 c축이 배향된 CAAC 구조의 금속 산화물을 형성할 수 있다.

[0280] 또한 도 5의 (A) 내지 (D) 및 도 6의 (A) 내지 (C)에서는 인듐을 포함한 층으로서 층(21)을 형성하고, 그 위에 원소 M을 포함한 층으로서 층(31)을 형성한 후, 그 위에 아연을 포함한 층으로서 층(41)을 형성하는 예를 나타내었지만, 본 실시형태는 이에 한정되지 않는다. 층(31) 및 층(41) 중 한쪽을 형성하고, 그 위에 층(21)을 형성한 후, 그 위에 층(31) 및 층(41) 중 다른 쪽을 형성하여도 좋다. 또는 층(31) 및 층(41) 중 한쪽을 형성하고, 그 위에 층(31) 및 층(41) 중 다른 쪽을 형성한 후, 그 위에 층(21)을 형성하여도 좋다.

[0281] 또한 In:M:Zn=1:1:1[원자수비]과 다른 원자수비의 금속 산화물을 형성하는 경우에는 원자수비에 따라 상기 층(21), 상기 층(31), 상기 층(41)을 적절히 형성하면 좋다. 예를 들어 도 6의 (A)에 나타낸 층(31)의 형성 전후에 층(41)의 형성을 여러 번 반복함으로써, 2개의 층(21) 사이에 원하는 원자수, 층수, 및 두께를 가지는 층(31)과 층(41)의 적층을 형성하면 좋다.

[0282] 또한 각종 반도체 장치를 제작하는 경우, 본 발명의 일 형태의 금속 산화물과 기타 금속 산화물의 양쪽을 사용하여도 좋다. 예를 들어 본 발명의 일 형태의 금속 산화물은 인듐 및 아연 중 적어도 한쪽과 알루미늄을 포함한 금속 산화물(갈륨 및 주석 중 적어도 한쪽을 더 포함하여도 좋음)과 조합하여 사용하여도 좋다.

[0283] 인듐 및 아연 중 적어도 한쪽과 알루미늄을 포함한 금속 산화물로서는, 예를 들어 인듐 갈륨 알루미늄 산화물(In-Ga-Al 산화물), 알루미늄 아연 산화물(Al-Zn 산화물, AZO라고도 기재함), 인듐 알루미늄 아연 산화물(In-Al-Zn 산화물, IAZO라고도 기재함), 인듐 갈륨 알루미늄 아연 산화물(In-Ga-Al-Zn 산화물, IGAZO, IGZAO, 또는 IAGZO라고도 기재함)이 있다.

[0284] 알루미늄을 포함한 전구체로서는 예를 들어 트라이메틸알루미늄, 트라이에틸알루미늄, 클로로다이메틸알루미늄, 다이클로로메틸알루미늄, 브로모다이메틸알루미늄, 요오드다이메틸알루미늄, 알루미늄아세틸아세토네이트, 트리스(2,2,6,6-테트라메틸-3,5-헵테인디아이온산)알루미늄, 다이메틸클로로알루미늄, 다이에틸클로로알루미늄, 염화알루미늄(III), 브로민화 알루미늄(III), 및 아이오딘화 알루미늄(III)이 있다.

[0285] <성막 장치>

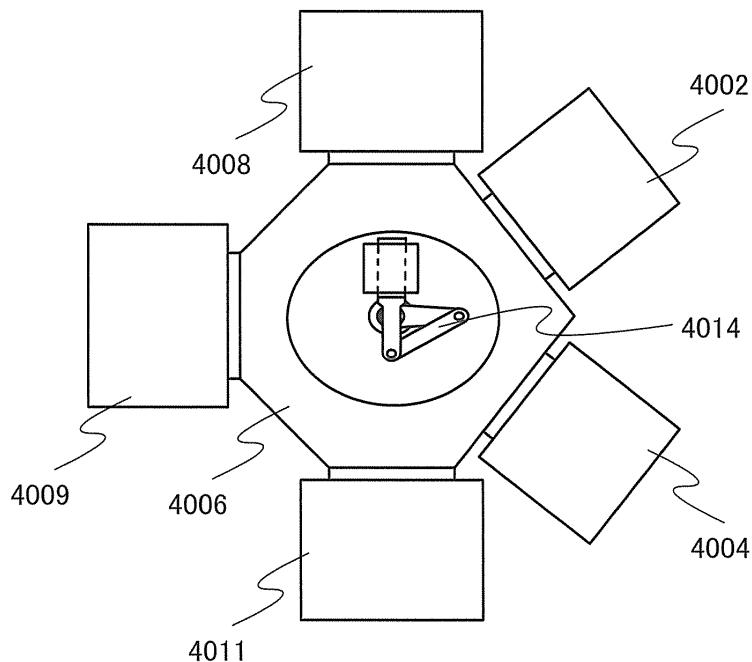

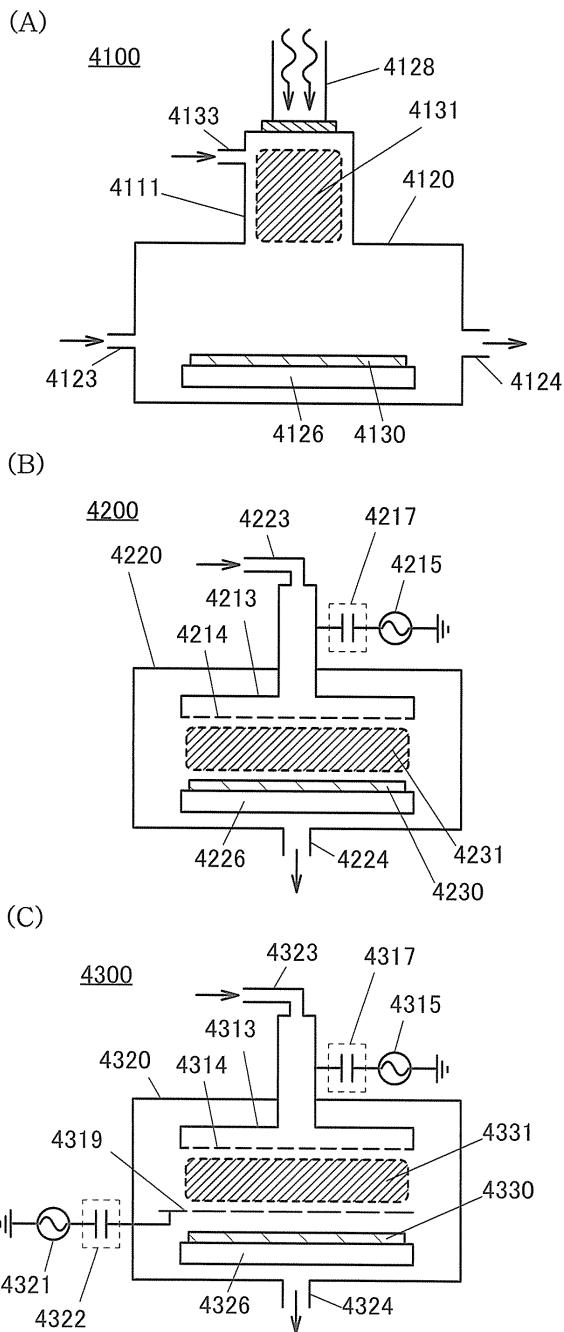

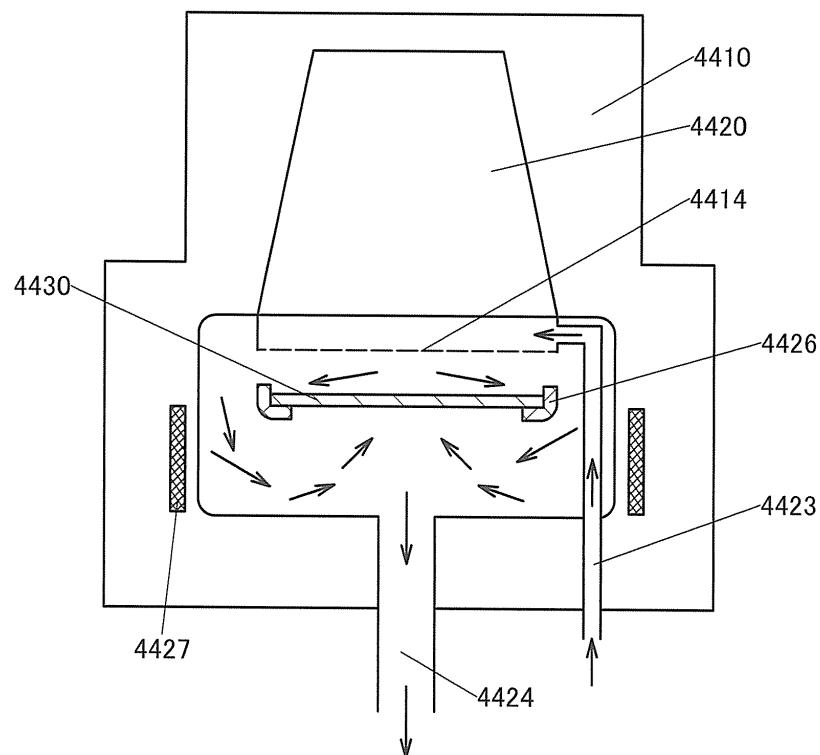

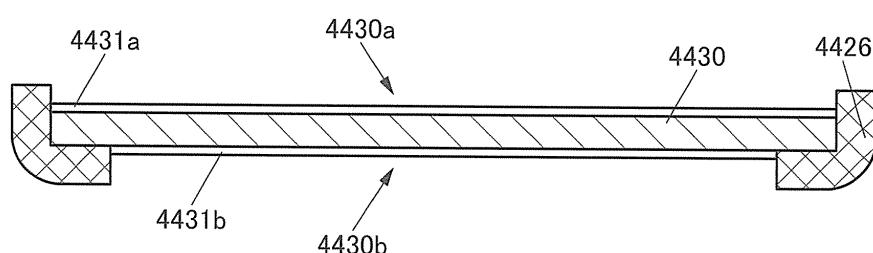

[0286] ALD법을 사용하여 성막할 수 있는 장치의 일례로서 성막 장치(4000)의 구성에 대하여 도 7 내지 도 10을 사용하여 설명한다. 도 7은 멀티 체임버형 성막 장치(4000)의 모식도이고, 도 8 내지 도 10은 성막 장치(4000)에 사용할 수 있는 ALD 장치의 단면도이다.

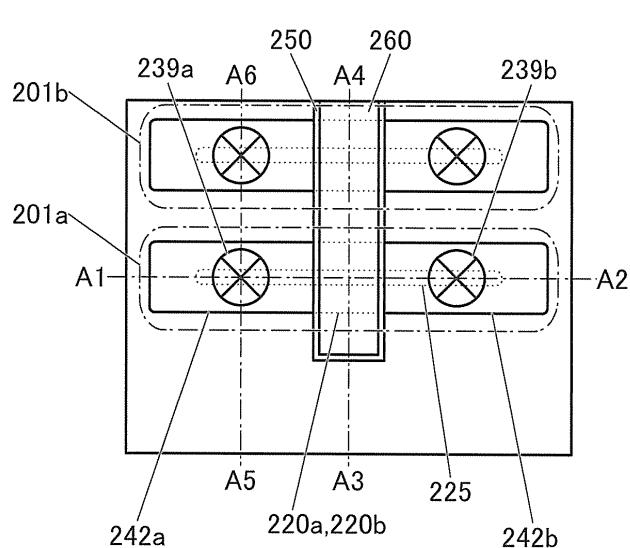

[0287] 도 7에 나타낸 성막 장치(4000)는 반입 반출실(4002)과, 반입 반출실(4004)과, 반송실(4006)과, 성막실(4008)과, 성막실(4009)과, 처리실(4011)과, 반송 암(4014)을 가진다. 여기서 반입 반출실(4002), 반입 반출실(4004), 성막실(4008), 성막실(4009), 및 처리실(4011)은 반송실(4006)에 각각 게이트 밸브를 통하여 독립적으로 접속되어 있다. 이에 의하여, 성막실(4008), 성막실(4009), 및 처리실(4011)에서 대기에 노출시키지 않고 연속하여 처리를 수행할 수 있기 때문에, 막 내에 불순물이 혼입되는 것을 방지할 수 있다. 또한 기판과 막의 계면 및 각 막의 계면의 오염이 저감되기 때문에 청정한 계면을 얻을 수 있다.

[0288] 또한 반입 반출실(4002), 반입 반출실(4004), 반송실(4006), 성막실(4008), 성막실(4009), 및 처리실(4011)은 수분의 부착 등을 방지하기 위하여, 이슬점이 관리된 불활성 가스(질소 가스 등)가 충전되는 것이 바람직하고, 감압이 유지되는 것이 바람직하다.

[0289] 성막실(4008) 및 성막실(4009)에는 ALD 장치를 사용할 수 있다. 또한 성막실(4008) 및 성막실(4009) 중 어느 것에 ALD 장치 이외의 성막 장치를 사용하는 구성으로 하여도 좋다. 성막실(4008) 및 성막실(4009)에 사용할

수 있는 성막 장치로서는 예를 들어 스퍼터링 장치, 플라스마 CVD(PECVD: Plasma Enhanced CVD) 장치, 열 CVD(TCVD: Thermal CVD) 장치, 광 CVD(Photo CVD) 장치, 금속 CVD(MCVD: Metal CVD) 장치, 유기 금속 CVD(MOCVD: Metal Organic CVD) 장치 등이 있다.

[0290] 또한 처리실(4011)에는 가열 장치(대표적으로는 진공 가열 장치), 플라스마 발생 장치(대표적으로는 마이크로파 처리 장치) 등 성막 장치 이외의 기능을 가지는 장치를 사용하는 것이 바람직하다.

[0291] 예를 들어 성막실(4008)을 ALD 장치로 하고, 성막실(4009)을 스퍼터링 장치로 하고, 처리실(4011)을 가열 장치로 한 경우, 성막실(4009)에서 하지 절연막을 성막하고, 성막실(4008)에서 활성층으로서 기능하는 산화물 반도체막을 성막하고, 처리실(4011)에서 산화물 반도체막 성막 후의 가열 처리를 수행할 수 있다. 이때 하지 절연막의 성막, 산화물 반도체막의 성막, 및 가열 처리를 대기에 노출시키지 않고 연속하여 수행할 수 있다. 따라서 금속 산화물의 성막 후에 막 내의 수소 또는 탄소 등의 불순물을 증가시키지 않고 가열 처리를 수행할 수 있다.

[0292] 또한 성막 장치(4000)는 반입 반출실(4002), 반입 반출실(4004), 성막실(4008), 성막실(4009), 및 처리실(4011)을 가지는 구성으로 하였지만, 본 발명은 이에 한정되는 것이 아니다. 성막 장치(4000)의 성막실을 하나 또는 3개 이상으로 하는 구성으로 하여도 좋다. 또한 성막 장치(4000)의 처리실을 2개 이상으로 하는 구성으로 하여도 좋다. 또한 성막 장치(4000)는 매엽식(枚葉式)으로 하여도 좋고, 복수의 기판을 일괄적으로 성막하는 배치식으로 하여도 좋다.

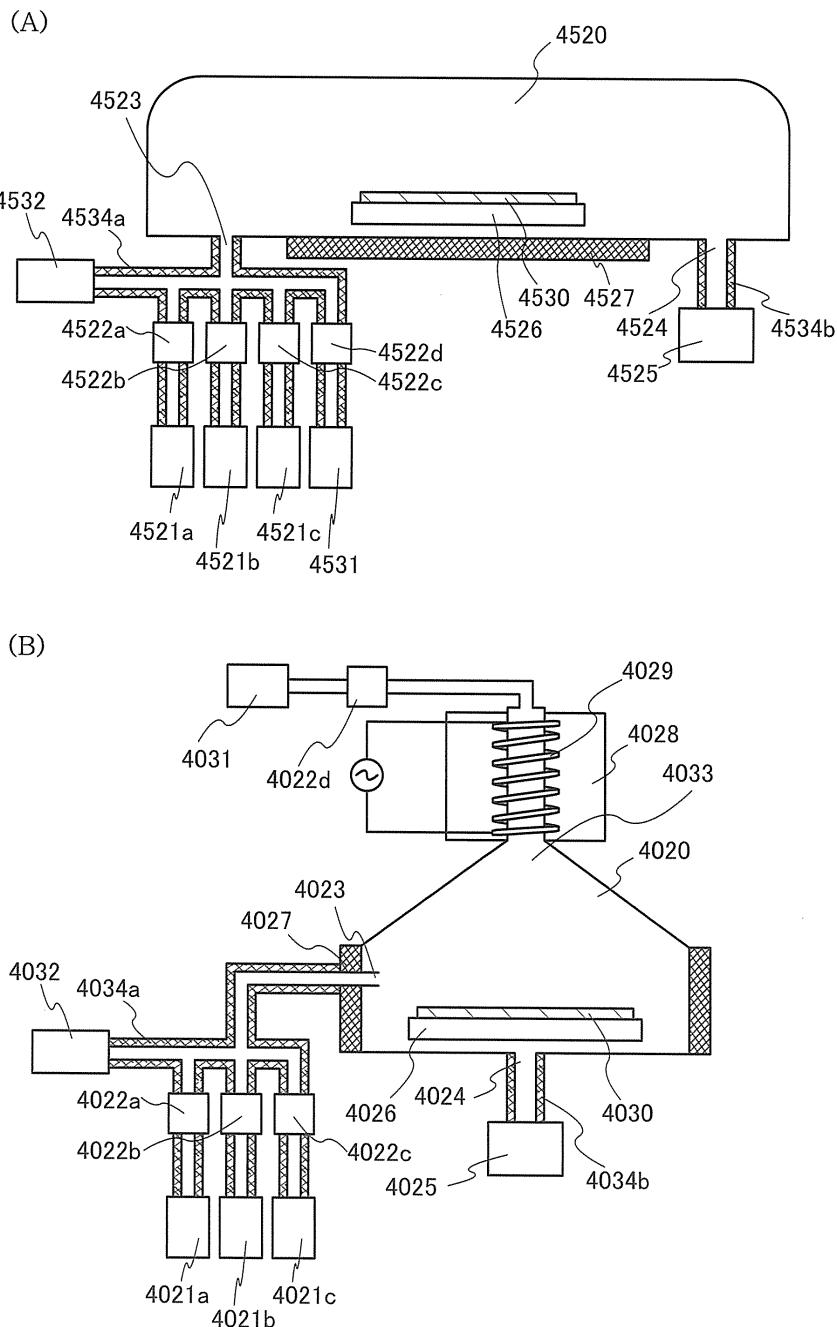

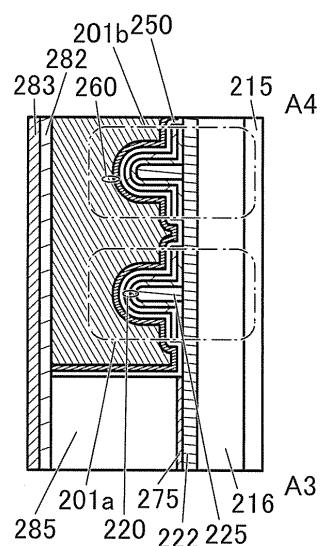

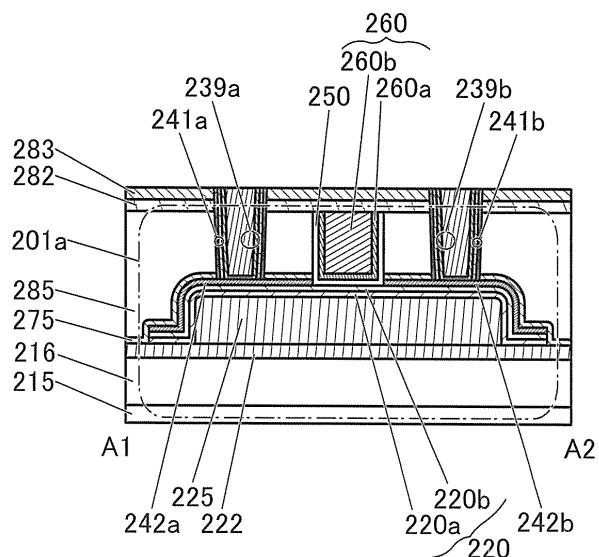

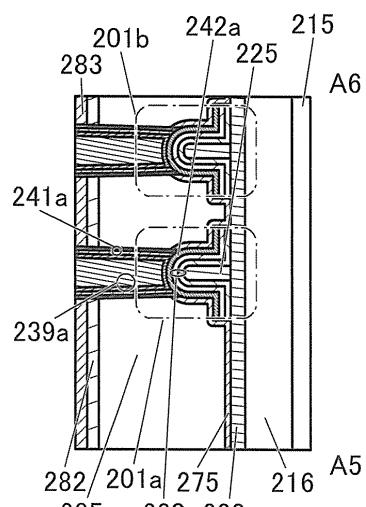

[0293] <ALD 장치>

[0294] 다음으로 성막 장치(4000)에 사용할 수 있는 열 ALD 장치의 구성에 대하여 도 8의 (A)를 사용하여 설명한다. 열 ALD 장치는 성막실(체임버(4520))과, 원료 공급부(4521)(원료 공급부(4521a) 내지 원료 공급부(4521c))와, 원료 공급부(4531)와, 도입량 제어기인 고속 벨브(4522a) 내지 고속 벨브(4522d)와, 가스 공급부(4532)와, 원료 도입구(4523)와, 원료 배출구(4524)와, 배기 장치(4525)를 가진다. 체임버(4520) 내에 설치되는 원료 도입구(4523)는 공급관 및 벨브를 통하여 원료 공급부(4521a), 원료 공급부(4521b), 원료 공급부(4521c), 원료 공급부(4531), 및 가스 공급부(4532)와 각각 접속되어 있고, 원료 배출구(4524)는 예를 들어 배출관, 벨브, 및 압력 조정기를 통하여 배기 장치(4525)와 접속되어 있다.

[0295] 체임버(4520) 내부에는 기판 홀더(4526)가 있고, 그 기판 홀더(4526) 위에 기판(4530)을 배치한다. 기판 홀더(4526)는 회전 기구를 가져도 좋다. 또한 체임버(4520) 외벽에는 히터(4527)가 제공되어 있고, 체임버(4520) 내부, 기판 홀더(4526), 및 기판(4530)의 표면 등의 온도를 제어할 수 있다. 히터(4527)는 기판(4530)의 표면의 온도를 100°C 이상 600°C 이하, 바람직하게는 300°C 이상 500°C 이하, 더 바람직하게는 400°C 이상 450°C 이하로 제어할 수 있는 것이 바람직하다. 예를 들어 히터(4527) 자체의 온도는 100°C 이상 600°C 이하로 설정할 수 있는 것이 바람직하다. 이와 같은 온도 범위에서 기판을 가열하면서 성막을 수행함으로써, 전구체 또는 반응제 등에 포함되는 수소 또는 탄소 등의 불순물이 금속 산화물 내에 잔존하는 것을 억제할 수 있다. 또한 이들 불순물의 제거와 동시에 금속 원자 및 산소 원자가 재배열되어, 각 산화물의 층을 높은 질서성으로 배열시킬 수 있다. 따라서 결정성이 높은 층상 결정 구조의 금속 산화물을 형성할 수 있다. 또한 히터(4527)를 사용하여 금속 산화물 성막 후의 열처리를 수행하여도 좋다.

[0296] 원료 공급부(4521a), 원료 공급부(4521b), 원료 공급부(4521c), 및 원료 공급부(4531)에서는 기화기 또는 가열 수단 등에 의하여 고체 원료 또는 액체 원료로부터 원료 가스를 형성한다. 또는 원료 공급부(4521a), 원료 공급부(4521b), 원료 공급부(4521c), 및 원료 공급부(4531)는 기체 원료 가스를 공급하는 구성으로 하여도 좋다.

[0297] 도 8의 (A)에 나타낸 성막 장치에서는 원료 공급부(4521) 및 원료 공급부(4531)에서 사용하는 원료(휘발성 유기 금속 화합물 등)를 적절히 선택하여 체임버(4520)에 도입함으로써 금속 산화물을 형성할 수 있다. 상술한 바와 같이 금속 산화물로서 인듐, 갈륨, 아연을 포함한 In-Ga-Zn 산화물을 형성하는 경우, 도 8의 (A)에 나타낸 바와 같이 적어도 3개의 원료 공급부(4521a) 내지 원료 공급부(4521c)와 적어도 하나의 원료 공급부(4531)가 제공된 성막 장치를 사용하는 것이 바람직하다.

[0298] 예를 들어 원료 공급부(4521a)로부터 인듐을 포함한 전구체가 공급되고, 원료 공급부(4521b)로부터 갈륨을 포함한 전구체가 공급되고, 원료 공급부(4521c)로부터 아연을 포함한 전구체가 공급된다. 인듐을 포함한 전구체, 갈륨을 포함한 전구체, 및 아연을 포함한 전구체로서 각각 상술한 전구체를 사용할 수 있다.

[0299] 또한 원료 공급부(4531)로부터는 반응제가 공급된다. 반응제로서는 오존, 산소, 물 중 적어도 하나를 포함한

산화제를 사용할 수 있다.

[0300] 또한 가스 공급부(4532)로부터는 캐리어 가스가 공급된다. 캐리어 가스로서 아르곤(Ar), 헬륨(He), 또는 질소(N<sub>2</sub>) 등의 불활성 가스를 사용할 수 있다. 원료 공급부(4521)의 전구체 및 원료 공급부(4531)의 반응제는 상기 캐리어 가스와 혼합되어 체임버(4520)에 도입된다.

[0301] 또한 원료 공급부(4521a), 원료 공급부(4521b), 원료 공급부(4521c), 원료 공급부(4531), 및 가스 공급부(4532)와 체임버(4520) 사이의 배관 또는 밸브 등을 덮어 배관 히터(4534a)가 제공된다. 또한 배기 장치(4525)와 체임버(4520) 사이의 배관 또는 밸브 등을 덮어 배관 히터(4534b)가 제공된다. 배관 히터(4534a) 및 배관 히터(4534b)의 온도는 예를 들어 실온 이상 300°C 이하의 범위에서 적절히 설정하면 좋다. 이와 같은 배관 히터를 제공함으로써, 원료 공급부(4521)로부터 공급된 전구체 등이 가스 도입계 및 가스 배기계의 배관 등의 내벽에 응고되는 것을 방지할 수 있다. 또한 배관 히터(4534a), 배관 히터(4534b), 및 히터(4527)의 온도는 각각 독립적으로 제어할 수 있는 것이 바람직하다. 또는 배관 히터(4534a), 배관 히터(4534b), 및 히터(4527)의 온도 제어가 일괄적으로 조정될 수 있어도 좋다.

[0302] 고속 밸브(4522a) 내지 고속 밸브(4522d)는 시간에 따라 정밀하게 제어할 수 있다. 이에 의하여, 원료 공급부(4521a), 원료 공급부(4521b), 원료 공급부(4521c), 및 원료 공급부(4531)로부터 공급되는 원료 가스를 제어하여 체임버(4520)에 도입할 수 있다.

[0303] 예를 들어 원료 공급부(4521a), 원료 공급부(4521b), 및 원료 공급부(4521c)에 포함되는 전구체를 공급하는 경우에는 고속 밸브(4522a) 내지 고속 밸브(4522c) 중 대응하는 고속 밸브를 연다. 또한 원료 공급부(4531)에 포함되는 반응제를 공급하는 경우에는 고속 밸브(4522d)를 연다. 또한 체임버(4520)를 페지하는 경우에는 고속 밸브(4522a) 내지 고속 밸브(4522d)를 닫고 가스 공급부(4532)에 포함되는 캐리어 가스만을 체임버(4520)에 도입한다.

[0304] 또한 도 8의 (A)에서는 원료 공급부(4521)를 3개, 원료 공급부(4531)를 하나 제공하는 예를 나타내었지만, 본 실시형태는 이에 한정되지 않는다. 원료 공급부(4521)를 하나, 2개, 또는 4개 이상 제공하여도 좋다. 또한 원료 공급부(4531)를 2개 이상 제공하여도 좋다.