(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-526220

(P2016-526220A)

(43) 公表日 平成28年9月1日(2016.9.1)

|                              |             |             |

|------------------------------|-------------|-------------|

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

| <b>G06F 9/30</b> (2006.01)   | G06F 9/30   | 350F 5B033  |

| <b>G06F 15/173</b> (2006.01) | G06F 15/173 | 683C 5B045  |

審査請求 未請求 予備審査請求 未請求 (全 85 頁)

|               |                              |          |                                                                                                                         |

|---------------|------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2016-515113 (P2016-515113) | (71) 出願人 | 505000815<br>コーヒーレント・ロジックス・インコーポレーテッド<br>アメリカ合衆国・78746・テキサス州<br>・オースティン・サウス キャピタル オブ テキサス ハイウェイ・1120・ビルディング 3, スイート 310 |

| (86) (22) 出願日 | 平成26年5月23日 (2014.5.23)       | (74) 代理人 | 100064621<br>弁理士 山川 政樹                                                                                                  |

| (85) 翻訳文提出日   | 平成28年1月14日 (2016.1.14)       | (74) 代理人 | 100098394<br>弁理士 山川 茂樹                                                                                                  |

| (86) 國際出願番号   | PCT/US2014/039345            | (72) 発明者 | ドーア,マイケル・ビー<br>アメリカ合衆国・78620・テキサス州<br>・ドリッピング スプリングス・オーク<br>メドウ ドライブ・1210                                               |

| (87) 國際公開番号   | W02014/190263                |          |                                                                                                                         |

| (87) 國際公開日    | 平成26年11月27日 (2014.11.27)     |          |                                                                                                                         |

| (31) 優先権主張番号  | 61/827,117                   |          |                                                                                                                         |

| (32) 優先日      | 平成25年5月24日 (2013.5.24)       |          |                                                                                                                         |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                         |

最終頁に続く

(54) 【発明の名称】プログラム可能な最適化を有するメモリネットワークプロセッサ

## (57) 【要約】

高パフォーマンス及び低電力散逸のために最適化された処理要素を有するマルチプロセッサシステムと、関連する上記処理要素をプログラミングする方法との、様々な実施形態が開示される。各処理要素は、フェッチユニットと、複数のアドレス生成器ユニットと、複数のパイプライン化されたデータ経路とを備えてよい。フェッチユニットは、マルチパート命令を受信するよう構成されてよく、このマルチパート命令は複数のフィールドを含む。第1のアドレス生成器ユニットは、複数のフィールドのうちの第1のフィールドに応じた算術演算を実施するよう構成されてよい。第2のアドレス生成器ユニットは、複数のアドレスのうちの少なくとも1つのアドレスを生成するよう構成されてよく、各アドレスは、複数のフィールドそれぞれに依存する。並列アセンブリ言語を用いて、複数のアドレス生成器ユニット及び複数のパイプライン化されたデータ経路を制御してよい。

【選択図】図20

FIG. 20

**【特許請求の範囲】****【請求項 1】**

マルチパート命令を受信するよう構成されたフェッチユニットであって、前記マルチパート命令は複数のフィールドを含む、フェッチユニット；及び

複数のアドレス生成器ユニット

を備える、装置であって、

前記複数のアドレス生成器ユニットのうちの第1のアドレス生成器ユニットは、前記複数のフィールドのうちの第1のフィールドに応じた算術演算を実施するよう構成され、

第2のアドレス生成器ユニットは、複数のアドレスのうちの少なくとも1つのアドレスを生成するよう構成され、

前記複数のアドレスはそれぞれ、前記複数のフィールドそれぞれに依存する、装置。

**【請求項 2】**

前記複数のアドレスのうちの第1のアドレスに応じた第1のデータを保存するよう構成された、保存ユニットを更に備える、請求項1に記載の装置。

**【請求項 3】**

前記フェッチユニットは更に、前記複数のアドレスのうちの第2のアドレスに応じた第2のデータをフェッチするよう構成される、請求項2に記載の装置。

**【請求項 4】**

第3のアドレス生成器ユニットは、前記複数のアドレスのうちの少なくとも1つの別のアドレスを生成するよう構成される、請求項1に記載の装置。

**【請求項 5】**

前記複数のフィールドのサブセットの各フィールドは、前記複数のアドレス生成器ユニットそれぞれが実施する演算を符号化する、請求項1に記載の装置。

**【請求項 6】**

プロセッサを動作させるための方法であって、前記方法は：

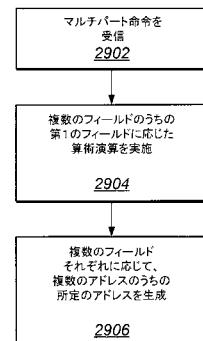

マルチパート命令を受信するステップであって、前記マルチパート命令は複数のフィールドを含む、ステップ；

前記複数のフィールドのうちの第1のフィールドに応じた算術演算を実施するステップ；及び

前記複数のフィールドそれぞれに応じた、複数のアドレスのうちの所定のアドレスを生成するステップ

を含む、方法。

**【請求項 7】**

前記複数のアドレスのうちの第1のアドレスに応じた第1のデータを保存するステップを更に含む、請求項6に記載の方法。

**【請求項 8】**

前記複数のアドレスのうちの第2のアドレスに応じた第2のデータをフェッチするステップを更に含む、請求項7に記載の方法。

**【請求項 9】**

前記プロセッサは複数のアドレス生成器ユニットを含み、

前記算術演算を実施するステップは、前記複数のアドレス生成器ユニットのうちの少なくとも1つのアドレス生成器ユニットを用いて前記算術演算を実施するステップを含む、請求項6に記載の方法。

**【請求項 10】**

前記複数のフィールドのサブセットの各フィールドは、前記複数のアドレス生成器ユニットそれぞれが実施する演算を符号化する、請求項9に記載の方法。

**【請求項 11】**

複数のプロセッサ；及び

複数の動的に構成可能な通信要素

を備える、システムであって、

10

20

30

40

50

前記複数のプロセッサ及び前記複数の動的に構成可能な通信要素は、散在型の配置において連結され、

前記複数のプロセッサのうちの所定のプロセッサは：

マルチパート命令を受信し、ここで前記マルチパート命令は複数のフィールドを含み；

前記複数のフィールドのうちの所定のフィールドに応じた算術演算を実施し；

前記複数のフィールドのサブセットに応じた複数のアドレスを生成する

よう構成される、システム。

【請求項 1 2】

前記複数のプロセッサはそれぞれ、前記複数のアドレスのうちの第1のアドレスに応じた第1のデータを保存するよう、更に構成される、請求項1 1に記載のシステム。 10

【請求項 1 3】

前記複数のプロセッサのうちの前記所定のプロセッサは、前記複数のアドレスのうちの第2のアドレスに応じた第2のデータをフェッチするよう、更に構成される、請求項1 2に記載のシステム。

【請求項 1 4】

前記複数のプロセッサのうちの前記所定のプロセッサは、複数のアドレス生成器ユニットを含む、請求項1 1に記載のシステム。

【請求項 1 5】

前記複数のフィールドのサブセットの各フィールドは、前記複数のアドレス生成器ユニットそれぞれが実施する演算を符号化する、請求項1 4に記載のシステム。 20

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明はマルチプロセッサシステムに関し、より詳細には、プロセッサ動作及び実行の改善、並びにこのようなシステムを標的にしたソフトウェアの開発に関する。

【背景技術】

【0 0 0 2】

一般的なハードウェアシステムの主たる目的は、完全なプログラム可能性を保持したまま、特定用途向け（非プログラマブル）ハードウェアパフォーマンスを達成することである。従来、これら2つの概念は対極にある。特定用途向けハードウェアは、可能な限り最も効率のよい方法で特定の機能を実施する、固定型ハードウェアソリューションである。これは通常、機能あたりのエネルギー又は1つ若しくは複数の演算あたりのエネルギーに関して、及び製品の部分コストに関連し得る（回路）面積あたりの機能に関して、測定される。コスト及び市場ダイナミクスにより、この目的を満たそうという試みのための革新が推進されてきた。チップ製品のコストは、ダイ面積及び最終パッケージを含む多くの因子で構成される。コストはまた、製品を開発するための全体的なエコシステムも考慮しなければならない。このエコシステムのコストは、特定の用途を特定のハードウェアソリューションに還元するための時間、システム全体を構成するために必要な特定のハードウェアソリューションの個数、並びにカスタマイズされた通信及びメモリ構造によって全ての特定のハードウェアソリューションを集積するためにかかる時間で構成される。従って、多数の特定ハードウェアソリューションの全てをそのカスタム相互接続によってサポートするために、完全に集積されたソリューションが必要となり、これにより単一チップダイに関して極めて大きな面積が必要となる。従来このプロセスは、面積、エネルギー及び市場に出るまでの時間に関して効率的でないソリューションの原因となっていた。 40

【0 0 0 3】

プログラム可能性の世界及び標的のハードウェアの概念を考慮すると、ハードウェアアーキテクチャ及びソフトウェア開発スタイルの視点からの市場又は展望は：Intel、AMD（Intel又はArm命令セットベース）、ARM等の企業が提供する汎用プロセッサ（GPP）；NVIDIA及びAMD（以前はATIであり、2006年にAMDにより買収）等からのグラフィカルプロセッシングユニット（GPU）；TI及びAna

log Devices からのデジタル信号プロセッサ (D S P) ; X i l i n x 、 A l t e r a 等からのフィールドプログラマブルゲートアレイ (F P G A) ; C a v i u m 及び T i l e r a からのマルチコア / メニーコアプロセッサ ; 特定用途向け集積回路 (A S I C S) 又はシステムオンチップ (S o C) によって提示される。

#### 【0004】

##### 汎用プロセッサ (G P P)

G P P は、40年以上に亘って考えられてきた、極めて古いものの検証はされているハードウェアアーキテクチャに基づく、汎用処理のためのものであり、即ち「何でも屋 (a j a c k o f a l l t r a d e s)」になろうとしている。G P P の主要な目的は、ユーザインターフェース (U I) と、M S W o r d 、E x c e l 、e メール等の、高度にインタラクティブな U I 集約型アプリケーションとを、これらをサポートするオペレーティングシステム (例えば W i n d o w s (登録商標) 、L i n u x (登録商標) ) によって駆動することである。電力散逸に大きな影響を及ぼすハードウェア特性は、マルチレベルキャッシュ、複雑なハードウェアメモリ管理ユニット、大型のバス、大型のクロック生成構造である。要するにこれらは、そのタスクを実施するために多くの電力を散逸する。ソフトウェア開発の視点から、これは、標的とするのが最も簡単なソフトウェアプログラミングモデルであると考えられる。これは、ユーザが、連続して又は順次実行される単一のスレッドを開発しているという視点からのものである。並列処理又は複数ハードウェアスレッド (約 4 スレッド超) を導入する場合、これらを効率的にプログラムする能力は大幅に困難となる。これは、このアーキテクチャが根本的に並列スレッド演算をサポートするように開発されておらず、従ってハードウェアアーキテクチャは途方も無い量のオーバヘッド及び複雑さを管理する必要があるという事実による。ソフトウェアプログラミングモデルは、複数ソフトウェアスレッドの定義をサポートするために A P I 又は言語拡張の導入を必要とする。これは必ずしも複雑でないものの、残念ながら現行の G P P ハードウェアアーキテクチャはこのような複雑さを必要とする。

#### 【0005】

高次において、世界中の全てのスーパコンピュータで C 、 C + + 、 F o r t r a n 等を用いて長年に亘って広く使用してきた A P I は、 M P I (メッセージ受け渡しインターフェース) A P I であり、これは 1990 年代初頭から業界標準である。これは極めて単純な、よく理解されている、ハードウェア実装経路を制限しない A P I である。 M P I A P I は、ハードウェア非依存性様式での、ソフトウェアスレッド及び通信の定義を可能とする。これは O p e n M P 、 C o a r r a y F o r t r a n 、 O p e n C L 等、及び仮定された下層のハードウェアモデルを本的に記述する他の言語 / A P I とは異なっており、従って解釈の柔軟性を制限し、前方互換性の問題を引き起こす。換言すると、これらの言語 / A P I を用いる場合、プログラマは、標的とする全ての新規のハードウェアプラットフォームのためにプログラムを書き直す必要がある。

#### 【0006】

##### グラフィカルプロセッシングユニット (G P U)

G P U は従来、データを処理して表示することを標的として開発してきた。これらは、そのコア外 (外部) メモリモデル要件及び内部コアメモリモデル要件により、ハードウェアアーキテクチャ的に制約されている。コア外メモリは、G P P に、データを G P U メモリ空間に配置するよう要求する。続いて G P U はそのデータを引き込み、そのデータに對してパイプライン様式で動作して、上記データを外部メモリ空間に戻す。ここからデータをディスプレイに送信でき、又は G P P は、汎用処理下での動作において更に使用 / 記憶するために、データを G P U メモリ空間外に移動させる必要がある。ハードウェアの非効率性は、(1) コア外ハードウェア制約をサポートするためにデータを移動させるために必要なサポート、及び(2) 深いパイプライン構造の S I M D 機械と同様の、能率化されたパイプラインにおいて処理されるよう、データが制約を受ける、内部コアメモリ構造によるものである。その結果、データを処理するためのハードウェアの非効率性により、電力が高くなる。使用されるソフトウェアプログラミングモデルは、極めてハードウェア

10

20

30

40

50

中心的なものであり、OpenCL、CUDA等であり、従って、効率性を達成するには複雑であり、移植可能性があまり高くなく、新規のハードウェア標的プラットフォームに移動させようとする際には、コードを書き直して再構成しなければならない。

#### 【0007】

##### デジタル信号プロセッサ (DSP)

DSPは、一般的な信号処理のために削減及び標的化された命令セットを有するGPPとして考えることができる。これらは、その兄弟 / 姉妹GPPと同一のキャッシュ、MMU及びバスからの悪影響を受ける。Vitterbi / Turbo復号化又は動作推定等の、いずれの実際に高スループットの処理機能は、通常は市場における特定の規格の限定的なセットをサポートするだけの、限定された能力を有するASIC加速器へと削減されている。プログラミングモデルは、単一のハードウェアスレッドを標的とする場合のGPPと同様であるが、実行ユニットハードウェアにおける信号処理命令アプローチにより、いずれの高効率を達成するには、複数の機能のハンドアセンブリ、又はDSP製造企業のライブラリの使用を必要とする。上述の並列GPPと同様に、多数の並列DSPアーキテクチャを生成する際、問題は更に悪化する。

10

#### 【0008】

##### フィールドプログラマブルゲートアレイ (FPGA)

FPGAは完全に異なるハードウェアアプローチであり、この場合機能性の定義はビットレベルで実施でき、論理機能間の通信はプログラム可能な配線構造を通して実施される。このハードウェアアプローチは、途方も無い量のオーバヘッド及び複雑さを導入する。これにより、効率的なプログラミングが、Verilog又はVHDL等のハードウェアプログラミング言語で実施される。コンパイルプロセスは、ASIC / SOCにおいて必要とされるものと同様であるものの、構造化された配線ファブリックを有する、プログラム可能な配線及びプログラム可能な論理導入タイミング収束障害により、遙かに複雑となる。FPGAはそのFPGAがプログラムされた目的の機能そのもののみを実施し、それ以外を一切実施しないため、1度に1つの機能のみを比較する場合、特定の機能に関する電力散逸及びパフォーマンススループットは、GPP又はGPUより明らかに良好である。しかしながら、GPPの能力の全てをFPGAに実装しようとした場合、GPPよりも明らかに悪くなる。ハードウェアレベルにおけるプログラミングの困難さは明らかである（例えばタイミング収束）。FPGAのプログラミングは実際には「プログラミング」ではなく、論理 / ハードウェア設計であり、またVHDL / Verilogはプログラミング言語ではなく、論理 / ハードウェア設計言語である。

20

30

40

#### 【0009】

##### マルチコア / メニーコア

殆ど全てのマルチコア / メニーコアアーキテクチャは、ハードウェアの視点から、コアプロセッサ、キャッシュ、MMU、バス、全ての関連する論理を採用し、これらを、その周囲の通信バス / ファブリックによってダイ上で複製している。マルチコアアーキテクチャの例はIBMのCell、Intel及びAMDのクアッドコア及びNマルチコア、Cavium及びTileraの製品、多数のカスタムSOC等である。更に、マルチコアアーキテクチャにおいて達成される電力の低減は主に取るに足らないものである。この明らかな結果は、マルチコアアプローチがGPUアプローチを単に複製するという事実に由来する。マルチコアアーキテクチャにおける唯一の実際の電力節約は、以前は別個のダイ上にあったコアが追加の通信バスに接続されることにより、もはや不要となったI/Oドライバの削減である。従って、マルチコアアプローチは電力のいずれの低下につながらない。第2に、ソフトウェアプログラミングモデルは上述のGPPから改善されない。

#### 【0010】

##### 特定用途向け集積回路 (ASIC) 又はシステムオンチップ (SOC)

他のアプローチに関して識別される事項のリストは、特定の市場に関して、パフォーマンス効率及びコスト目標を達成するための唯一の方法が、特定のGPP、DSP及びASIC加速器を有するカスタムチップを開発してSOCを形成することであると考えられる

50

ことが多い理由である。S o Cは、必要な場合はプログラム可能性と、電力散逸とコストとの間のバランスを取るための特定の機能に関するA S I C性能とを提供する。しかしながら現在、ソフトウェアプログラミングモデルは、上述のプログラム可能なハードウェアソリューションのもとで議論されたものよりも更に複雑である。更にS o Cは、完全にプログラム可能なソリューションと関連する柔軟性の損失につながり得る。

#### 【0011】

これらのプログラム可能なハードウェアソリューション全てに共通なのは、現在市場において提示されているソフトウェアプログラミングモデルが、その標準化をより効率的にサポートするために、実行モデル及び下層のハードウェアアーキテクチャを外挿することに焦点を合わせている点である。実行モデルの特徴をソフトウェアプログラミングモデルに外挿することは、より一般的な並列プログラミング言語のうちのいくつかの重要な特徴を見ると観察できる。現在使用されているアプローチを示すいくつかの例は、O p e n M P、O p e n C L、M P Iである。

10

#### 【0012】

##### O p e n M P

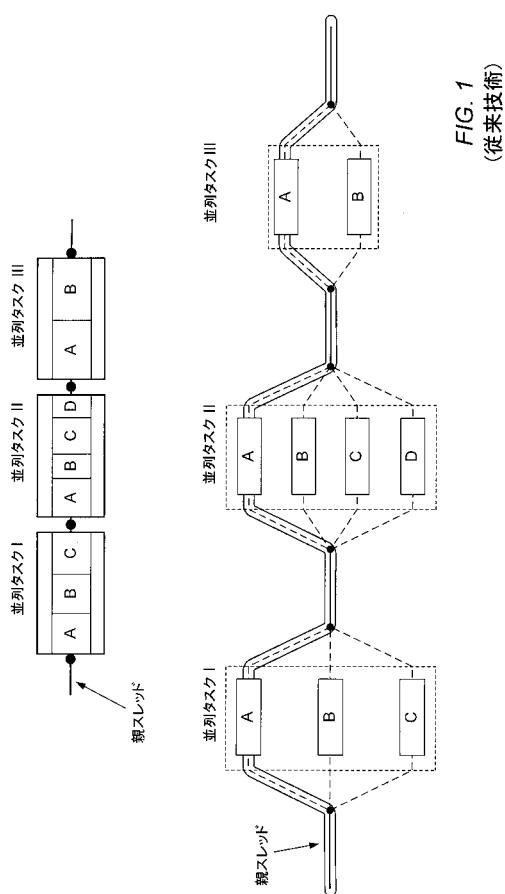

O p e n M P（オープンマルチプロセッシング）は、共有メモリマルチプロセッシングプログラミングをサポートする業界標準のA P Iである。O p e n M Pは、コンパイラ指示文、ライブラリルーチン、及びランタイム挙動に影響を与える環境変数のセットを含む。これは、並列化方法によるマルチスレッディングをサポートし、これによって親スレッド（連続して実行される一連の命令）は特定の数のスレーブスレッドに分岐し、タスクがこれらの間で分割される。そしてこれらのスレッドは同時に実行され、ランタイム環境はスレッドを、利用法、機械負荷及び他の因子に応じて異なるリソース又はプロセッサに割り当てる。スレッドの数は、ランタイム環境によって、環境変数に基づいて、又は関数を使用するコード内に割り当てることができる。従って、並列に実行されることが意図されたコードのセクションは、このセクションの実行前にスレッドを形成させるプリプロセッサ指示文によってマークされる。C / C + +では、これは# p r o g r a m sの使用による。デフォルトでは、各スレッドはコードの並列化されたセクションを独立して実行する。タスクの並列処理及びデータの並列処理の両方を達成できる。並列化されたコードの実行後、複数のスレッドは親スレッドへ連結され、これはプログラムの最後まで進み続ける。図1は、O p e n M Pを利用したマルチスレッディングを示しており、ここで親スレッドは、コードの複数のブロックを並列に実行する多数のスレッドに分岐する。スレッド間通信をサポートするために、O p e n M Pの拡張、又は別の異なる業界標準A P I（例えばM P I（メッセージ受け渡しインターフェース））を使用してよい。

20

#### 【0013】

##### O p e n C L

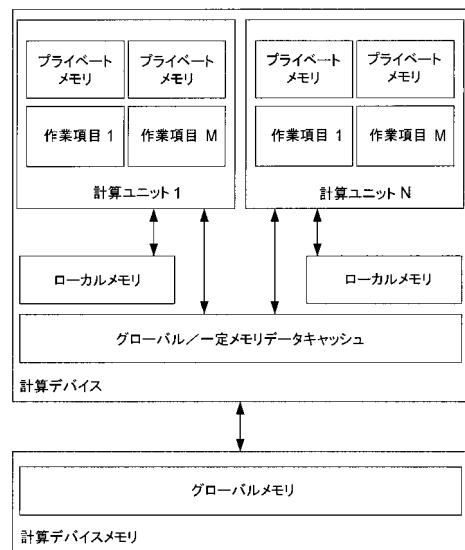

オープン計算言語（O p e n C L）は、中央演算処理装置（C P U）グラフィカルプロセッシングユニット（G P U）、デジタル信号プロセッサ（D S P）、フィールドプログラマブルゲートアレイ（F P G A）及び他のプロセッサを備える異質な複数のプラットフォームに亘る実行を可能とすることを目的として、プログラムを記述するためのフレームワークである。これは抽象化が限定されたクロース・トゥ・ハードウェアインターフェースをサポートするよう設計されている。このため、O p e n C Lベースのプログラムは一般に、満足できるパフォーマンスを達成するために、下層のハードウェアに関する高度な知識を必要とする。O p e n C Lプログラムはまた、異なるハードウェアアーキテクチャを再標的化する際にリファクタリングを必要とする。図2に示すように、O p e n C Lは、厳密な処理モデル、制御モデル、メモリモデル、通信モデル階層をサポートする。

30

#### 【0014】

O p e n C Lは、何らかの制限及び追加を伴って、A N S I Cプログラミング言語を用いてカーネルを記述することをサポートする。これは、関数へのポインタ、再帰、ビットフィールド、可変長配列、標準ヘッダファイルの使用を可能としない。複数のベクタタイプ及び演算を伴う並列処理、同期化、並びに複数のワークアイテム／グループを伴う作

40

50

業を行うための関数をサポートするよう、上記言語を拡張する。アプリケーションプログラミングインターフェース（A P I）を用いて、プラットフォームを定義して制御する。OpenCLは、コースレベルにおいて、タスクベース及びデータベースの並列処理を用いた並列計算をサポートする。

【0015】

M P I

メッセージ受け渡しインターフェース（M P I）は、標準化された、言語非依存の、スケーラブルな、移植可能な、メッセージ受け渡し通信プロトコルA P Iである。M P I A P Iは、言語特異性構文を用いて、言語非依存性の方法で、（ノード／サーバ／コンピュータインスタンスに対してマッピングされた）プロセスのセット間の、必須の仮想トポロジ、同期化、及び通信機能を提供する（バインディング）。M P I A P I規格は、様々な挙動を定義できるポイントツーポイント及び集合／同報通信送受信動作並びにプロセスの同期のためのサポートを含む、ライブラリルーチンのコアの構文及び意味規則を定義する。M P Iは今日のハイパフォーマンス計算において使用される主要なモデルであり続けている。

10

【0016】

M P I A P Iは、最もハードウェア非依存性のアプローチであり、従って提示された例の基礎として使用される。

【0017】

マルチプロセッサシステム上での並列実行のためのソフトウェアアプリケーションの開発の、従来技術によるアプローチは、一般に、開発の容易さと並列実行の効率性との間のトレードオフを必要とする。換言すると、一般に、プログラマにとって開発プロセスが容易であればあるほど、結果として得られる実行可能なプログラムをハードウェア上で同時に実行する効率が低くなり、また反対に、より効率的な並列実行は一般に、プログラマによる相当に多大な努力を必要とし、即ち非効率的な処理を回避するために、及び標的ハードウェアの、効率増進性特徴を使用するために、プログラムを更に詳細に設計する必要がある。

20

【発明の概要】

【発明が解決しようとする課題】

【0018】

従って、ソフトウェアプログラミングモデルを駆動するためのアプリケーションのソフトウェア記述又はシステムレベルビューと、実行モデル及び下層ハードウェアアーキテクチャを標的化するためのこれらの後の使用とを促進するための、改善されたシステム及び方法が望まれている。また、このプロセスを通してアプリケーションの効率的かつプログラム可能な実装を可能とする機構を提供する改善も望まれている。

30

【課題を解決するための手段】

【0019】

高パフォーマンス及び低電力散逸のために最適化された処理要素を有するマルチプロセッサシステムと、関連する上記処理要素をプログラミングする方法との、様々な実施形態が開示される。

40

【0020】

第1の実施形態は、フェッチユニット及び複数のアドレス生成器ユニットを備えるプロセッサ装置に関する。フェッチユニットはマルチパート命令を受信するよう構成され、マルチパート命令は複数のフィールドを含む。第1のアドレス生成器ユニットは、複数のフィールドのうちの第1のフィールドに応じた算術演算を実施するよう構成される。第2のアドレス生成器ユニットは、複数のアドレスのうち少なくとも1つのアドレスを生成するよう構成され、各アドレスは、複数のフィールドそれぞれに依存する。

【0021】

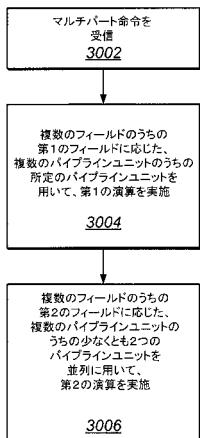

多数のデータ経路を制御することに関する第2の実施形態は、フェッチユニット及び実行ユニットを備えるプロセッサ装置を伴う。フェッチユニットはマルチパート命令を受信

50

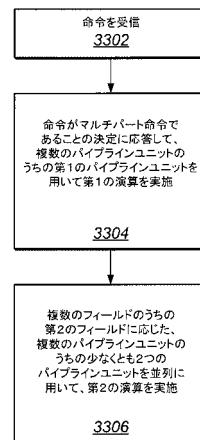

するよう構成され、マルチパート命令は複数のフィールドを含む。実行ユニットは複数のパイプラインユニットを含み、実行ユニットは：1) 複数のフィールドのうちの第1のフィールドに応じて、複数のパイプラインユニットのうちの所定のパイプラインユニットを用いて第1の演算を実施するよう；及び2) 複数のフィールドのうちの第2のフィールドに応じて、複数のパイプラインユニットのうちの少なくとも2つのパイプラインユニットを並列に用いて第2の演算を実施するよう、構成される。

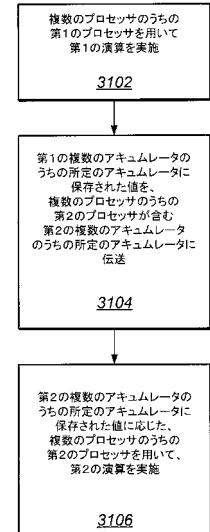

【0022】

累算の転送に関する第3の実施形態は、フェッチユニット及び実行ユニットを備えるプロセッサ装置を伴う。フェッチユニットは命令を受信するよう構成される。実行ユニットは複数のパイプラインユニットを含み、上記複数のパイプラインユニットの各パイプラインユニットはアキュムレータユニットを含み、実行ユニットは：1) 受信した命令に応じて、複数のパイプラインユニットのうちの第1のパイプラインユニットを用いて第1の演算を実施して、ある結果を生成するよう；2) 複数のパイプラインユニットのうちの第1のパイプラインユニットのアキュムレータユニットに上記結果を保存するよう；及び3) 複数のパイプラインユニットのうちの第1のパイプラインユニットのアキュムレータユニットに保存された結果を、プロセッサのアキュムレータユニットに転送するよう、構成される。

10

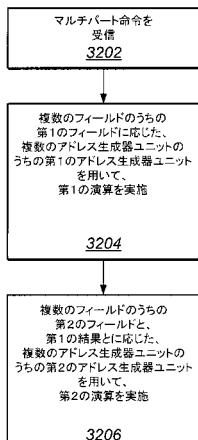

【0023】

アドレス生成器ユニットの連結に関する第4の実施形態は、フェッチユニット及び複数のアドレス生成器ユニットを備えるプロセッサ装置を伴う。フェッチユニットはマルチパート命令を受信するよう構成され、マルチパート命令は複数のフィールドを含む。第1のアドレス生成器ユニットは、複数のフィールドのうちの第1のフィールドに応じて第1の演算を実施して、第1の結果を生成するよう構成される。第2のアドレス生成器ユニットは、複数のフィールドのうちの第2のフィールド及び上記第1の結果に応じて第2の演算を実施するよう構成される。

20

【0024】

第5の実施形態は、單一パート／マルチパート決定を伴う命令を受信できるプロセッサ装置に関する。プロセッサ装置は、命令を受信するよう構成されたフェッチユニットと、実行ユニットとを備えてよい。実行ユニットは、複数のパイプラインユニットを備えてよい。実行ユニットは：1) 命令がマルチパート命令であることの決定に応答して、複数のパイプラインユニットのうちの第1のパイプラインユニットを用いて第1の演算を実施するよう（ここでマルチパート命令は複数のフィールドを含み、第1の演算は複数のフィールドのうちの第1のフィールドに依存する）；及び2) 複数のフィールドのうちの第2のフィールドに応じて、複数のパイプラインユニットのうちの少なくとも2つのパイプラインユニットを並列に用いて第2の演算を実施するよう、構成してよい。

30

【0025】

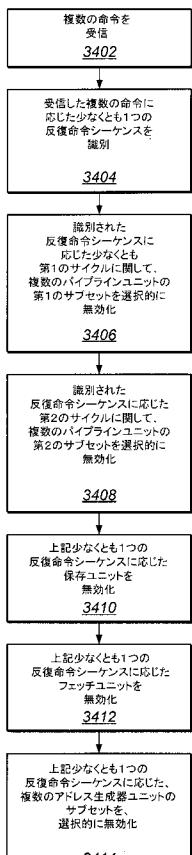

第6の実施形態は、反復ループ中にプロセッサの未使用部分をパワーダウンさせることができる、プロセッサ装置に関する。このプロセッサ装置は、フェッチユニット及び実行ユニットを備えてよい。フェッチユニットは、複数の命令を受信して、受信した複数の命令に基づいて少なくとも1つの反復命令シーケンスを識別するよう構成される。上記少なくとも1つの反復命令シーケンスは、複数の命令のうちの少なくとも1つを含む。実行ユニットは複数のパイプラインユニットを含み、実行ユニットは：1) 識別された反復命令シーケンスに基づく少なくとも第1のサイクルに関する、複数のパイプラインユニットの第1のサブセットを選択的に無効化するよう；及び2) 識別された反復命令シーケンスに応じた第2のサイクルに関する、複数のパイプラインユニットの第2のサブセットを選択的に無効化するよう、構成される。

40

【0026】

マルチプロセッサシステム上の並列実行のために標的化されたソフトウェアを開発するための方法の実施形態を提示する。

【0027】

50

例えばマルチプロセッサシステム上での展開及び実行のために標的化されたアプリケーションの、所望のシステムの複数のビューを指定する入力を受信してよい。各ビューは、システムの各態様を提示又は指定してよく、またこれらビューは総体として、効率的な並列実行のためにマルチプロセッサシステムが展開できる実行可能なプログラムを生成するためにコンパイラ（又は他のソフトウェアツール）が使用できる情報を提供してよい。

#### 【0028】

この入力は、様々な形態のいずれで、また様々なツールのいずれを介して受信されてよい。例えばいくつかの実施形態では、入力はユーザによって提供されてよく、即ちユーザ入力であってよい。他の実施形態では、入力は所望に応じて別のシステム又はプロセス、ストレージ媒体等から受信されてよい。更に入力はローカルに提供されてよく、又はローカルエリアネットワーク（LAN）若しくはインターネット等の広域ネットワーク（WAN）を介して受信されてよい。例示的な一実施形態では、ユーザはスプレッドシート中でビューを指定してよい。別の例示的実施形態では、ユーザはウィザード、即ちグラフィカルユーザインタフェース（GUI）への入力を行ってよく、これは指定プロセスを通して、例えばプロンプト、有用な提案等によってユーザをリードする。更なる実施形態では、ユーザは入力／指定プロセスを管理するためにチェックリストを使用してよく、指定される各アイテム、例えばビュー、サブビュー等がチェックリストに挙げられており、チェックリストは各チェックリストアイテムが指定されているか（されていないか）を示す。別の例示的実施形態では、1つ又は複数のテンプレート又はフォームを提供してよく、ユーザはビューを指定する情報で上記テンプレート又はフォームを埋めてよい。

10

20

30

40

#### 【0029】

各ビューは、アプリケーションの動作又は実行の各態様を含むか又はその表現となってよい。多数のビューはメモリビュー、通信ビュー、制御ビュー、処理ビューを含んでよい。他のビューも所望に応じて定義又は指定してよい。一実施形態では、各ビューは、ビューの更に詳細な属性を指定する複数のサブビュー（又は「ファセット（facet）」）を含むか又は指定してよい。例えば各ビューは、サイズ、拳動及びアクセシビリティサブビュー（又はファセット）を含んでよく、各サブビューは、各サブビューがその一部となっているビューに関連する特定の意味を有してよい。

#### 【0030】

従って例えば、メモリビューは：アプリケーションによる使用に必要な又は利用可能なメモリのサイズ（又は量）、即ちデータを処理するためにアプリケーションが使用するメモリ構造サイズ；メモリの拳動、即ちメモリ構造が所定のタイミングで拳動する様式；並びにメモリのアクセシビリティ、即ち例えばアプリケーション及び／又はシステムによるメモリ構造のアクセシビリティを指定してよい。

30

#### 【0031】

同様に、入力は：通信ビュー（通信ビューの各サブビュー、例えば通信サイズ、拳動、アクセシビリティを定義することを含む）；制御ビュー（制御サイズ、拳動、アクセシビリティを含む）；並びに処理ビュー（処理サイズ、拳動、アクセシビリティを含む）を定義又は指定してよい。

40

#### 【0032】

いくつかの実施形態では、ビュー又はサブビューのうちのいくつかは、他のサブビュー又はビューの指定によって、例えば同一の又は異なるビューのサブビューによって、自動的に定義又は指定され得ることに留意されたい。従って例えば、メモリサイズ、拳動及びアクセシビリティが指定されると、通信拳動が自動的に指定され得る。別の様式で考えると、いくつかの実施形態では、ビューは、方程式の数が変数の数を超える線形方程式の優決定系と同様に、「過剰に指定される」か又は「過剰に決定される」場合がある。

50

#### 【0033】

本出願で使用される特定の用語又は標識は単なる例示であること、並びに所望に応じて本出願で開示される新規の構成要素、情報及びプロセスに対していずれの名称を使用してよいことに留意されたい。例えば所望に応じて、ビュー又は態様はモデル等と呼ばれる場

合もあり、本出願で開示されるサブビューはサブモデル、ファセット、プロパティ等と呼ばれる場合もある。

【0034】

システムのビューが指定又は定義されると、これらのビューを表す情報は、アプリケーションのソースコード内に含まれ得る。この包含は、広範な方法のうちのいずれにおいて実施され得る。例えはいくつかの実施形態では、情報はアプリケーションの1つ又は複数のヘッダファイルに含まれ得る。他の実施形態では、情報は、アプリケーションプログラム要素又は構成要素の中でとりわけ、1つ又は複数の動的リンクライブラリ(DLL)又はマクロ定義に含まれ得る。より一般には、ビューを表す情報は、所望に応じていずれの様式及びいずれの形態でアプリケーションソースコードに組み込まれてよい。

10

【0035】

ソースコードは例えは、コンパイラ又は他のツールによって処理でき、これはシステムに関して指定又は定義された複数のビューを表す情報を分析することを含む。例えは一実施形態では、コンパイラは、アプリケーションソースコード内の複数のビューを表す情報を認識するよう構成してよく、またこの情報を抽出及び分析してよい。他の実施形態では、コンパイラは情報を原位置で分析してよい。

【0036】

実行可能なプログラムは上記処理に基づいて生成してよく、ここで上記実行可能なプログラムは、効率的な並列実行のためにマルチプロセッサシステムに展開可能である。換言すると、コンパイラは、指定されたビューの分析を含む上記処理に基づいて、実行可能なプログラムを生成してよい。

20

【0037】

従って、本技術の実施形態は、上述のようなソフトウェア開発への従来技術のアプローチの様々な欠点に対処でき、これによってユーザは、システムの動作、例えはマルチプロセッサシステム上でのアプリケーションの動作に関する様々な要件又は制約を指定でき、これら指定された要件又は制約をコンパイラ(又は他のツール)が使用して、システム上で効率的に実行できる実行可能なコードを生成してよい。

【図面の簡単な説明】

【0038】

【図1】図1は、OpenMPを利用したマルチスレッディングを示し、親スレッドはコードのブロックを並列に実行する多数のスレッドに分岐する。

30

【図2】図2は、OpenCLの厳密処理モデル、制御モデル、メモリモデル、通信モデル階層を示す。

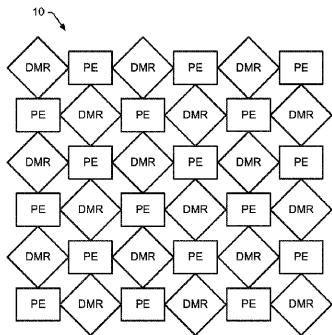

【図3】図3は、マルチプロセッサシステム(MPS)の一実施形態を示すブロック図である。

【図4】図4は、MPS接続スキームの一実施形態を示すブロック図である。

【図5】図5は、MPSファブリックの一実施形態を示す更に詳細な図である。

【図6】図6は、図5のアーキテクチャ例に従ってDMR(円)と共に均一に分散させたPE(正方形)からなる、例示的なMPSを示す。

【図7】図7は、動的に構成可能なプロセッサ(PE)の一実施形態を示すブロック図である。

40

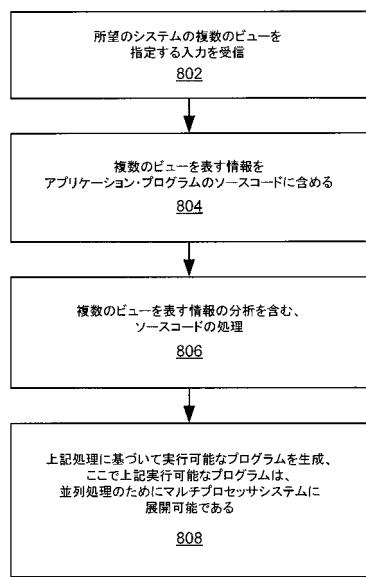

【図8】図8は、一実施形態による、マルチプロセッサシステム上での並列実行のために標的化されたアプリケーションソフトウェアを開発するための方法のフローチャートである。

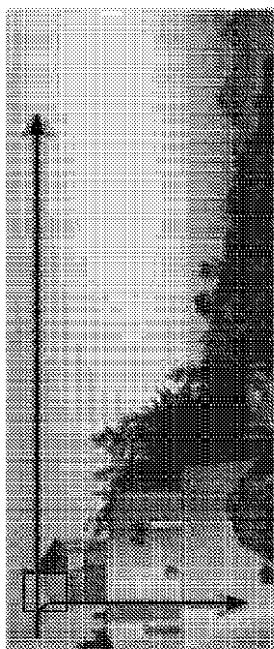

【図9A】図9Aは、一般的な2Dフィルタリング組織スキームを示す。

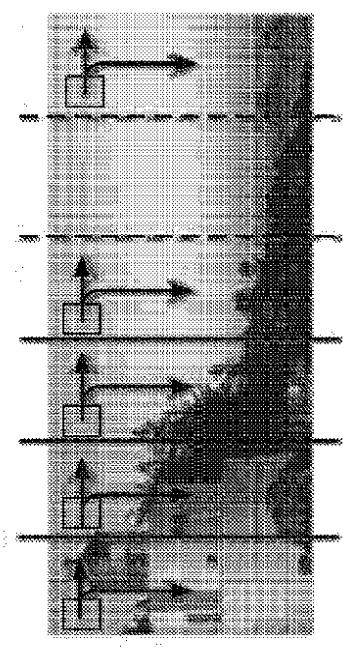

【図9B】図9Bは、別の一般的な2Dフィルタリング組織スキームを示す。

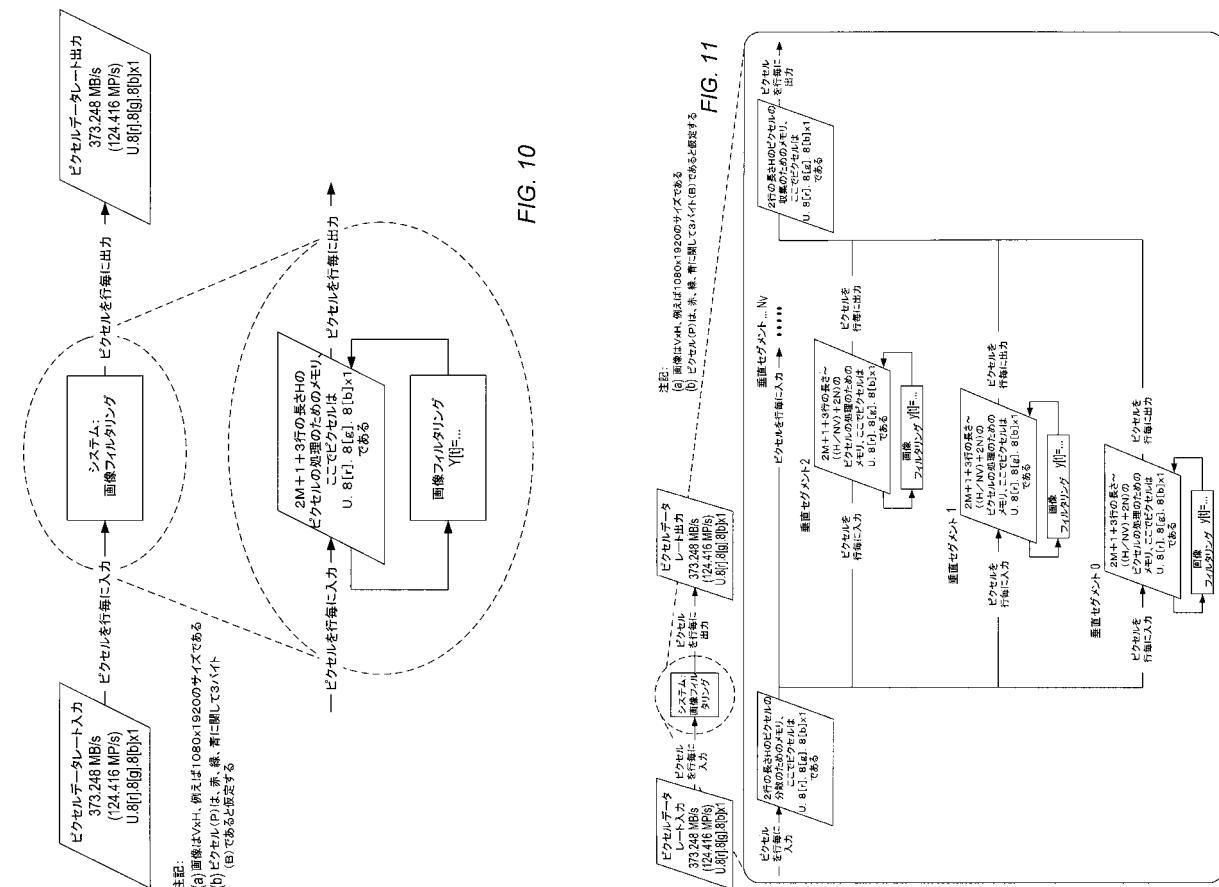

【図10】図10は、単一のプロセッサによる画像フィルタリングのブロック図を示す。

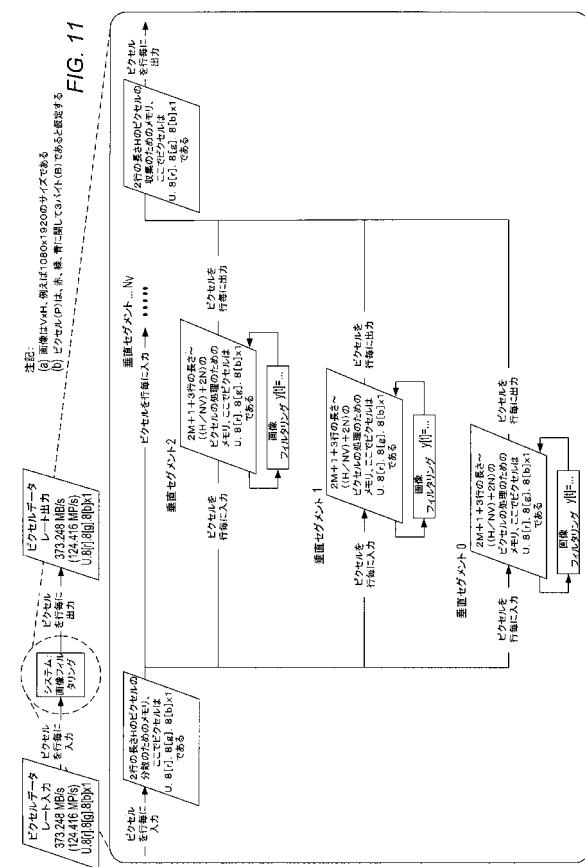

【図11】図11は、多数のプロセッサによる画像フィルタリングのブロック図を示す。

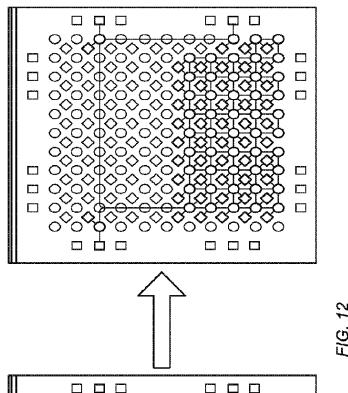

【図12】図12は、例示的なビデオ2Dフィルタシステムのための、MPS上での2つの異なるリソースレイアウトを示す。

50

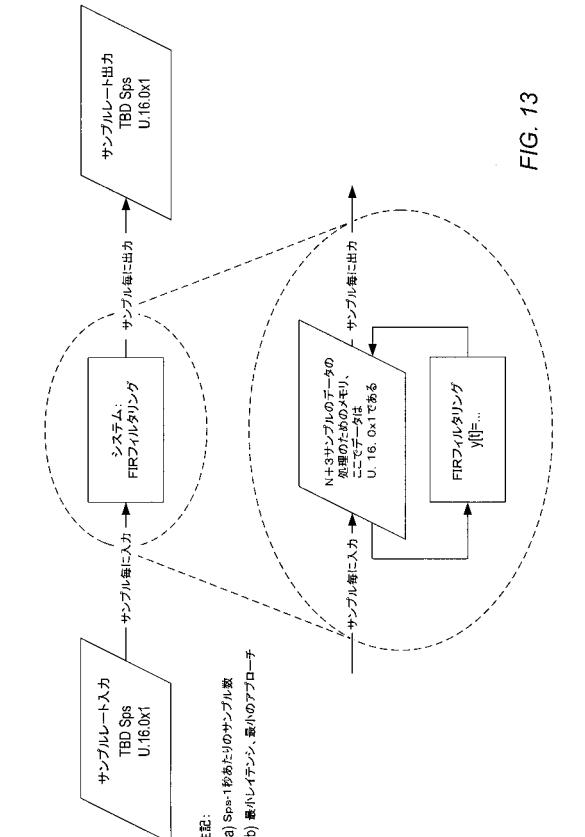

【図 1 3】図 1 3 は、単一のプロセッサを用いた F I R フィルタを示すブロック図である。

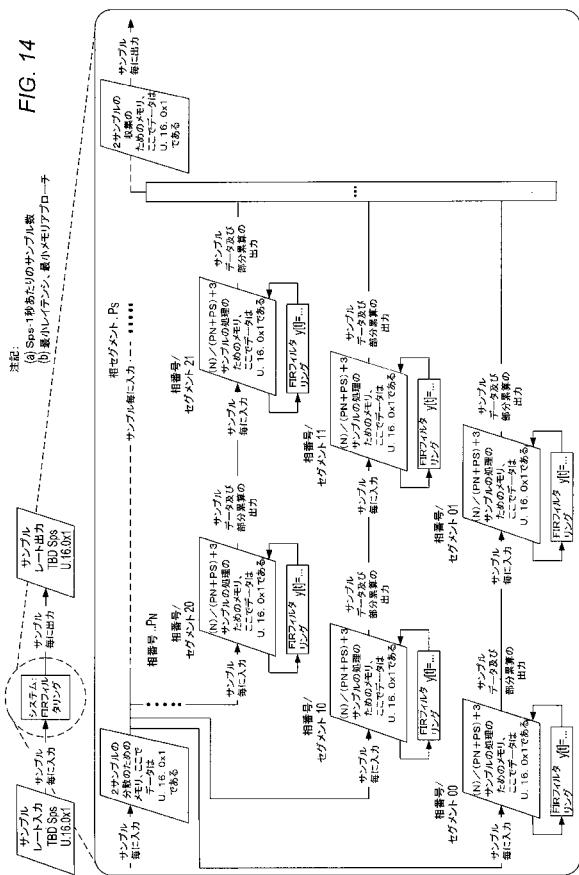

【図 1 4】図 1 4 は、多数のプロセッサを用いた F I R フィルタを示すブロック図である。

【図 1 5】図 1 5 は、サンプルバッファに関するメモリ構造を示す。

【図 1 6】図 1 6 は、メモリ通信挙動に関する経時的構造を示す。

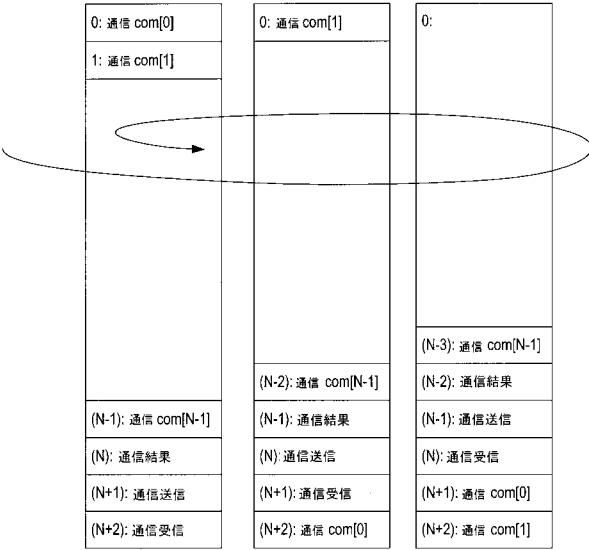

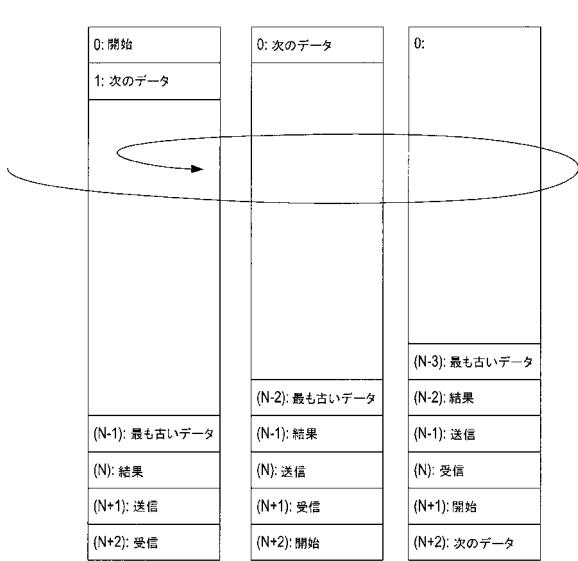

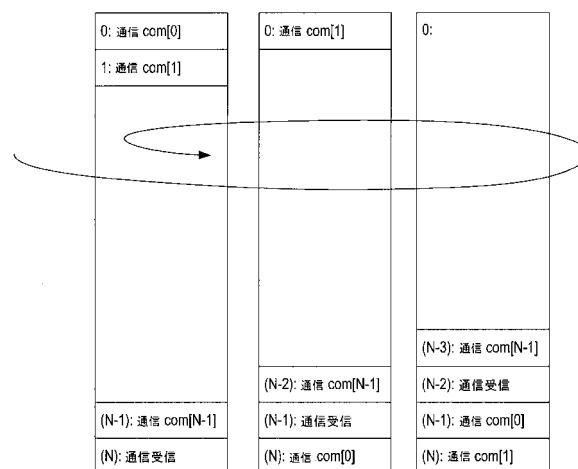

【図 1 7】図 1 7 は、F I R フィルタの一部に関する、メモリ通信挙動に関する経時的構造を示す。

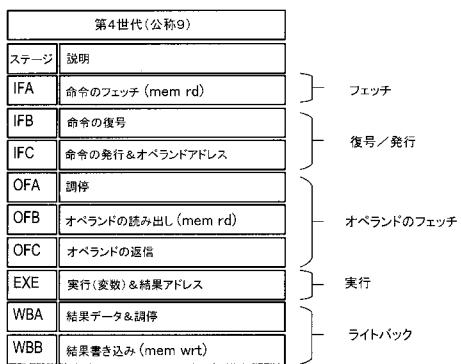

【図 1 8】図 1 8 は、9 ステージ P E パイプラインの一実施形態のパイプラインステージを示す。

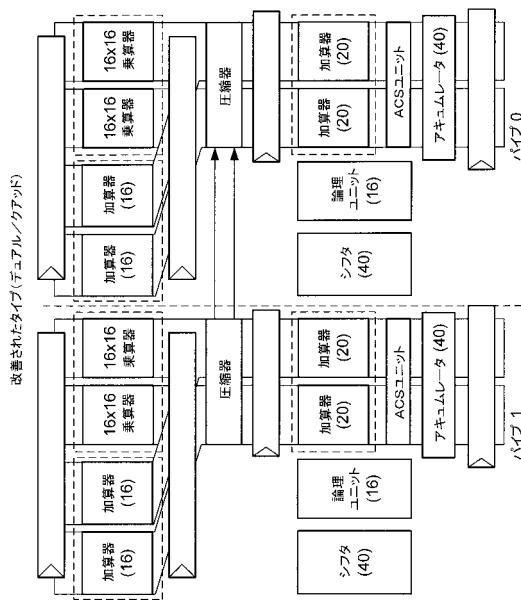

【図 1 9】図 1 9 は、単一 P E データ経路アーキテクチャ及び改善された P E データ経路アーキテクチャの実施形態のブロック図を示す。

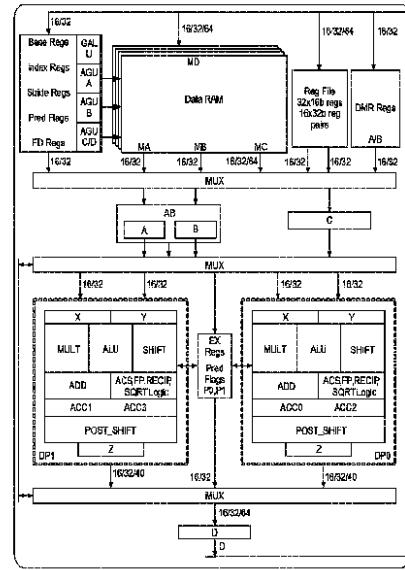

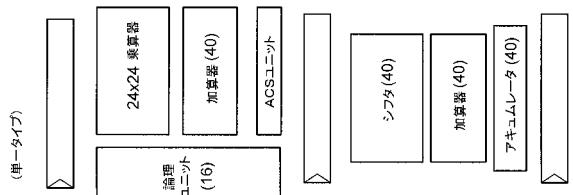

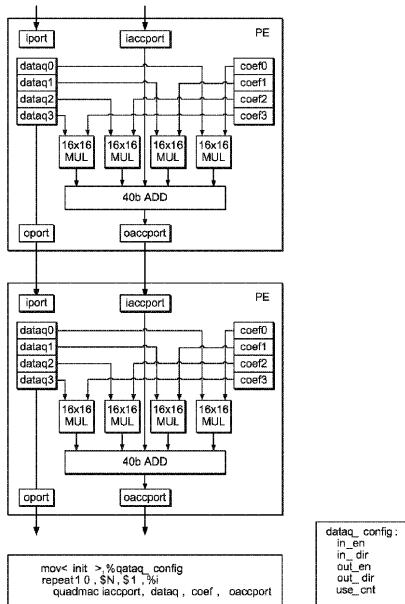

【図 2 0】図 2 0 は、データ経路の一実施形態を示すブロック図である。

【図 2 1】図 2 1 は、アキュムレータ転送を実施する 2 つの P E の一実施形態を示すブロック図である。

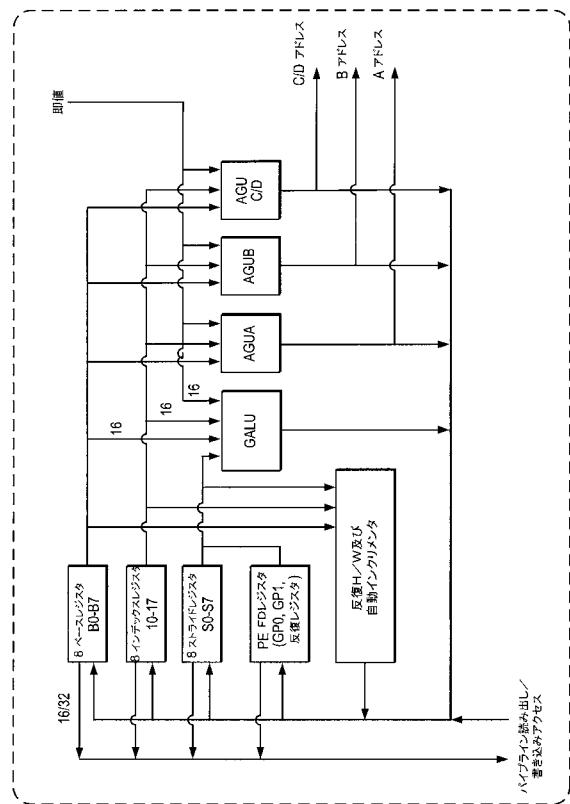

【図 2 2】図 2 2 は、P E のアドレス生成論理の一実施形態を示すブロック図である。

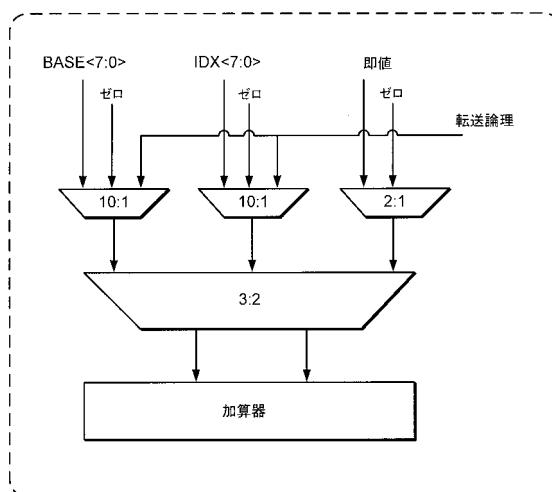

【図 2 3】図 2 3 は、アドレス生成ユニット ( A G U ) の一実施形態を示すブロック図である。

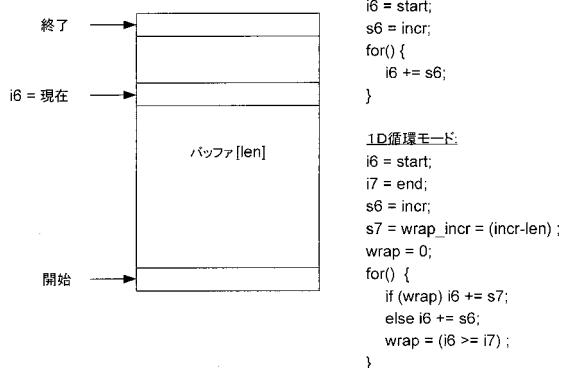

【図 2 4】図 2 4 は、循環バッファの一実施形態の概念図である。

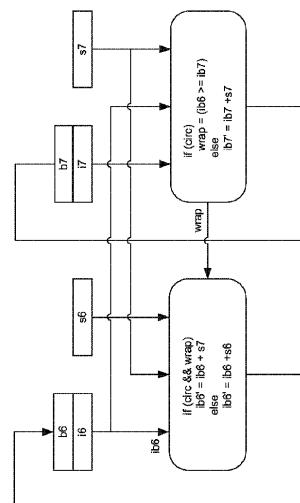

【図 2 5】図 2 5 は、図 2 4 の循環バッファの制御の一実施形態を示すブロック図である。

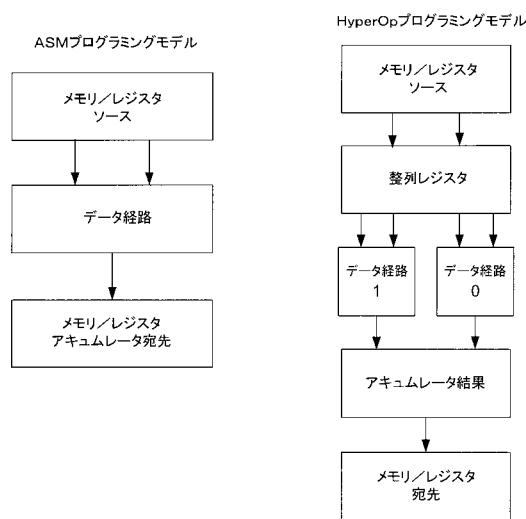

【図 2 6】図 2 6 は、従来のプログラミングモデル及び H y p e r O p プログラミングモデルを示す 2 つのブロック図を示す。

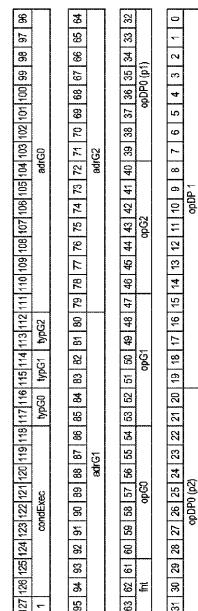

【図 2 7】図 2 7 は、H y p e r O p 命令の一実施形態を示す。

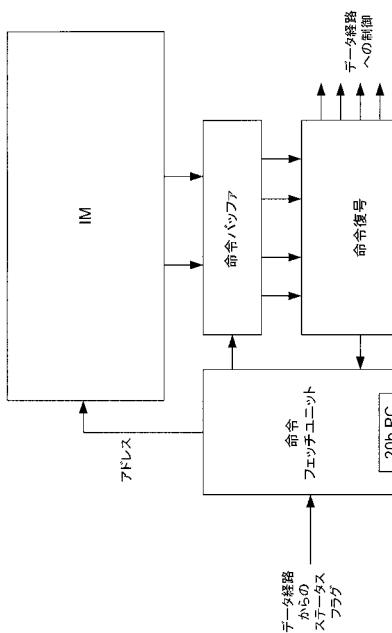

【図 2 8】図 2 8 は、命令フェッチ及び復号化ユニットの一実施形態を示すブロック図である。

【図 2 9】図 2 9 は、マルチパート命令を受信及び実行する第 1 の実施形態を示すフローチャートである。

【図 3 0】図 3 0 は、マルチパート命令を受信及び実行する第 1 の実施形態を示すフローチャートである。

【図 3 1】図 3 1 は、プロセッサによる演算の実施の一実施形態を示すフローチャートである。

【図 3 2】図 3 2 は、プロセッサによる演算の実施の一実施形態を示すフローチャートである。

【図 3 3】図 3 3 は、プロセッサを動作させる一実施形態を示すフローチャートである。

【図 3 4】図 3 4 は、複数のパイプラインユニットを有するプロセッサを動作させる第 1 の実施形態を示すフローチャートである。

【発明を実施するための形態】

【0 0 3 9】

本開示は様々な修正及び代替形態を許容するものであるが、その具体的な実施形態を例として図面に示し、また本明細書で詳細に説明する。しかしながら、上記具体的実施形態の図及び詳細な説明は、図示されている特定の形態に開示を限定することを意図したものではなく、反対に、添付の請求項によって定義されるような本開示の精神及び範囲内にある全ての修正例、均等物及び代替例を包含することを意図したものであることを理解されたい。本明細書において使用されている見出しあは、単に組織化を目的としたものであり、これらの使用は本説明の範囲の限定を意味しない。本出願全体を通して使用される単語「してよい / し得る / できる ( m a y ) 」は、許容の意味で（即ち「可能性がある」ことを意味して）使用されており、強制の意味で（即ち「しなければならない」ことを意味して）使用されるものではない。同様に、単語「含む ( i n c l u d e / i n c l u d i n g / i n c l u d e s ) 」は、ある対象を含むもののそれに限定されないことを意味する。

10

20

30

40

50

## 【0040】

様々なユニット、回路又はその他の構成部品は、1つ又は複数のタスクを実施する「よう構成される（configured to）」として記載され得る。このような文脈において「よう構成される」は、動作中に上記1つ又は複数のタスクを実施する「回路構成を有する」ことを一般に意味する、構造の広範な説明である。従ってユニット／回路／構成部品は、ユニット／回路／構成部品が現在オンでなくても上記タスクを実施するよう構成できる。一般に「よう構成される」に対応する構造を形成する回路構成は、ハードウェア回路を含んでよい。同様に、記載を簡略化するために、様々なユニット／回路／構成部品は、1つ又は複数のタスクを実施するとして記載され得る。このような記載は「よう構成される」という語句を含むものとして解釈されるものとする。1つ又は複数のタスクを実施するよう構成されるユニット／回路／構成部品の例挙は、これらユニット／回路／構成部品に関して米国特許法第112条第6段落の解釈を援用しないことを明示的に意図したものである。より一般には、いずれの要素の例挙は、「…のための手段（means for）」又は「…のためのステップ（step for）」という語句が具体的に使用されていない限り、上記要素に関して米国特許法第112条第6段落の解釈を援用しないことを明示的に意図したものである。

10

## 【0041】

## 参照による援用

Michael B. Doerr、William H. Halliday、David A. Gibson、Craig M. Chaseを発明者とする、発明の名称「Processing System With Interspersed Stall Propagating Processors And Communication Elements」の米国特許第7415594号は、その全体を参照することにより、本明細書においてその全体が完全に論述されているかのように、本明細書に援用されるものとする。

20

## 【0042】

## 用語

コンピュータシステム 用語「コンピュータシステム」は、パーソナルコンピュータシステム（PC）、メインフレームコンピュータシステム、ワークステーション、ネットワーク家電、インターネット家電、パーソナルデジタルアシスタント（PDA）、テレビジョンシステム、グリッドコンピュティングシステム若しくはその他のデバイス又はデバイスの組み合わせを含む、様々なタイプの計算又は処理システムのいずれかを指す。一般に、用語「コンピュータシステム」は、メモリ媒体からの命令を実行する少なくとも1つのプロセッサを有するいずれのデバイス（又は複数のデバイスの組み合わせ）を包含するものとして広く定義できる。

30

## 【0043】

ソフトウェアアプリケーション 用語「ソフトウェアアプリケーション」（本出願では単に「アプリケーション」とも呼ぶ）は、その一般的な意味の全範囲を有することを意図したものであり、1つ又は複数のメモリに記憶でき、かつ1つ又は複数のプロセッサが実行できる、あらゆるタイプのプログラム命令、コード、スクリプト及び／又はデータ又はこれらの組み合わせを含む。例示的なソフトウェアアプリケーションは、C、C++、FORTRAN、Java（登録商標）、アセンブリ言語等のテキストベースプログラム言語で書かれたプログラム；グラフィックプログラム（グラフィックプログラム言語で書かれたプログラム）；アセンブリ言語プログラム；機械言語にコンパイルされたプログラム；スクリプト；並びに他のタイプの実行可能なソフトウェアを含む。一般にプログラムは、1つ又は複数のデータ構造を指定し、またこれらの構造内のデータに対して取るべき手順のステップを指定して1つ又は複数の機能を実施する、命令のセットである。プログラムは、特定の機械アーキテクチャに関して標準化される場合が多い。更に抽象的には、プログラムの手順のステップは、上記プログラムのアルゴリズムと呼ばれる場合がある。

40

## 【0044】

50

アプリケーションは、マルチプロセッサシステム（MPS）の1つ又は複数のプロセッサ上で実行でき、MPSのローカルメモリのうちの1つ若しくは複数からデータを読み出すことができ、及び／又はMPSのローカルメモリのうちの1つ若しくは複数にデータを書き込むことができる。アプリケーションは、1つ又は複数の計算タスクを含んでよく、ここで各タスクは典型的にはMPSの単一のプロセッサ上で実行され、1つ又は複数のアプリケーションからの1つ又は複数のタスクと上記プロセッサを共有してよい。アプリケーションは、特定の機能又は演算を実施してよい。アプリケーションが2つ以上のタスクを含む場合、これらタスクは互いに通信して上記機能又は演算を実施してよい。

#### 【0045】

MPSは複数のアプリケーションを同時に実行してよく、例えばこれらアプリケーションは互いに並列に実行される。アプリケーションは互いに通信してよく、これらアプリケーションが実施する各機能又は演算は、より大きい又はより高いレベルの機能又は演算を実施するために互いを利用してよい。

10

#### 【0046】

ソフトウェアプログラミングモデル ソフトウェアプログラミングモデルは、簡単に言うと、ユーザの、機械及びその動作環境のビューである。ソフトウェアプログラミングモデルは、アプリケーションを記述できる1つ又は複数の言語、並びに上記1つ又は複数の言語で直接表現できるものを超えた抽象化及びセル化された機能性を提供するライブラリを含む。ソフトウェアプログラミングはまた、それを通してアプリケーションがその外部のエンティティ（I/O、拡張メモリ等）と相互作用する、及びそれを通して上記アプリケーションに関するメタ情報（例えばパフォーマンス制約又は要件）が表現される、機構も含む。プログラミングモデルの2つの主要な部分は、並列処理がアプリケーション内でどのように表現されるか又はアプリケーションからどのように引き出されるかを示す制御モデル、及びアプリケーションの並列のエンティティがどのように情報を共有するかを示す通信モデルである。

20

#### 【0047】

ソフトウェアプログラミングモデルは、実際の制御及びデータフロー及びアプリケーションが最終的に実行された場合に発生することになる通信の、「理想化された」ビューを提示する。演算の意味規則は、下層の実装がソフトウェアプログラミングモデルにおいて記述された通りに正確に実施されているかのようになるものであり、同一の効果（答え）が得られる限り、実際に行われるステップは重要ではない。実際の実装ステップは、コードの効率及び／又はデータサイズ、速度、電力消費等の理由により異なり得る。

30

#### 【0048】

ソフトウェアプログラミングモデルの考慮すべき重要な事柄は、ツールセット（コンパイラ等）による、及びそれに続く実行モデル下でのアプリケーションの正確かつ効率的な処理をサポートするために十分な情報もキャプチャしながら、便利かつ自然でユーザにとって直感的な用語でのアプリケーションの表現をサポートする機構を、ソフトウェアプログラミングモデルがユーザに同時に提供することである。

#### 【0049】

ハードウェアプログラミング／実行モデル ハードウェアプログラミングモデル又は実行モデルは、アプリケーションがどのように実行されるかを表す。これは、アプリケーションの論理及びデータオブジェクトに対応する情報のセットがどのように表現されるか、並びにその情報が経時にどのように処理されて、アプリケーションによって指定された機能が達成されるかを定義する。システムツール（コンパイラ、並列処理抽出器、配置配線（place and route）等）の目的は、アプリケーションをそのソフトウェアプログラミングモデル表現から対応する実行モデル表現に変換することである。実行モデルは、（例えばライブラリを通して）ソフトウェアプログラミングモデルによって記述された機能性をサポートし、（例えばO/Sを通して）ハードウェアの使用を監視、調停、管理するために必要な機構を含む。

40

#### 【0050】

50

実行モデルは、ソフトウェアプログラミングモデルと極めて密接に対応してよく、又は完全に異なっていてよい。ソフトウェアプログラミングモデルの異なる複数の様態は、実行モデルへの異なる直接的対応度を有してよい。対応のレベルは、下層のハードウェアアーキテクチャが、元々の（ソフトウェア）プログラミングモデルとどの程度類似しているかに関連する。類似性が高いほど対応性が高い。

#### 【0051】

下層のハードウェアアーキテクチャ 下層のハードウェアアーキテクチャは、計算が実行される物理デバイスのアーキテクチャである。このレベルでは、全ての動作はデバイスが実行する物理的動作に直接対応する。下層のハードウェアアーキテクチャを記述できる抽象のレベルは、（設計空間開発中の評価、シミュレーション、特性決定、トレードオフ分析に有用な）高次概念アーキテクチャから、（製作されるデバイスの物理的設計の実施に有用な）低次実装アーキテクチャに変化し得る。実装レベルにおいてさえ、下層のハードウェアアーキテクチャの異なる複数の例は、能力又は性能において異なり得る。例えばある例は  $10 \times 10$  グリッドの処理ユニットを実装してよく、その一方で別の例はたった  $6 \times 6$  グリッドしか実装しなくてよい。これらはそれぞれ能力が異なるものの、下層のハードウェアアーキテクチャとの整合性を保持している。

#### 【0052】

自動的に（automatically）：その作用又は動作を直接指定又は実施するユーザ入力を必要とせずに、コンピュータシステム（例えばコンピュータシステムが実行するソフトウェア）又はデバイス（例えば回路構成、プログラム可能なハードウェア要素、ASIC等）が実施する動作又は操作について用いる。従って用語「自動的に」は、ユーザが手動で実施又は指定する操作（ここでユーザが操作を直接実施するために入力を提供する）と対照的なものである。自動処理は、ユーザが提供する入力によって開始される場合があるが、これに続く「自動的に」実施される動作は、ユーザが指定するものではなく、即ち「手動で」実施される（ユーザが各動作の実施を指定する）ものではない。例えばユーザが、各フィールドを選択し、（例えば情報をタピングすることによって、チェックボックスを選択することによって、無線選択によって等）情報を指定する入力を提供することによって、電子フォームを埋める場合、仮にコンピュータシステムがユーザの動作に応答して上記フォームを更新しなければならないとしても、これは上記フォームを手動で埋めたことになる。このようなフォームはコンピュータシステムによって自動で埋めることができ、この場合コンピュータシステム（例えばコンピュータシステム上で実行されるソフトウェア）は、フォームのフィールドを分析して、フィールドへの回答を指定するいずれのユーザ入力を必要とせずにフォームを埋める。上述のように、ユーザはフォームを自動で埋める動作を発動する場合はあるが、実際にフォームを埋める動作には関わらない（例えばユーザはフィールドへの回答を手動で指定せず、回答は自動的に完了する）。本明細書は、ユーザが行う動作に応答して自動的に実施される操作の様々な例を提供する。

#### 【0053】

##### MPSシステムの概要

マルチプロセッサシステム（MPS）及び関連する方法の様々な実施形態を説明する。マルチプロセッサシステム（MPS）は、複数の処理要素（PE）を含むシステムとして定義できる。MPSは、これらPE間に散在する複数のメモリを有してよく、あるいは单一の共有メモリを有してよい。本明細書で使用される場合、用語「処理要素（processing element）」は、プロセッサ若しくはCPU（中央演算処理装置）、マイクロプロセッサ又はプロセッサコアを指す。MPSは2つ以上のいずれの個数のPEを含んでよいが、いくつかのMPSは、典型的には汎用プロセッサ（GPP）を1つのみ、又は数個のGPPのみを含む従来のコンピュータシステムよりも有意に多い個数のPEを含んでよいことに留意されたい。例えばいくつかのMPSは、4、8、16、32又は64個のPEを含んでよい（他の例は例えば数ダース、数百個又は数千個ものPEを含む）。いくつかの実施形態では、大型MPSに好適なPEは、低電力消費を目的とした特別

10

20

30

40

50

な構成により、従来のコンピュータシステムによって使用される汎用プロセッサよりもエネルギー効率が高いものであってよい。

#### 【0054】

MPSはまた、PE及び/又はメモリを相互接続する相互接続ネットワーク(IN)も含んでよい。PE及びメモリは、円形次元(例えばループ又はリング)を含む1、2、3又は4以上の次元で相互接続してよい。より高い次元のMPSは、より低い次元のファブリケーション媒体上にマッピングできる。例えば4次元(4D)超立方体の形状を有するMPSは、シリコン集積回路(IC)チップの3Dスタック上に、又は単一の2Dチップ上に、又は計算ユニットの1Dの線上にさえ、マッピングできる。低次元のMPSをより高次元の媒体にマッピングすることもできる。例えば計算ユニットの1Dの線を、ICチップの2D平面上に曲がりくねった形状で展開でき、又はチップの3D積層体へと巻くことができる。MPSは複数のタイプの計算ユニットと、プロセッサ及びメモリが散在する構成とを含んでよい。広い意味でのMPSには、MPSの階層又は入れ子構成、特に相互接続されたICチップからなるMPSも含まれ、この場合ICチップは1つ又は複数のMPSを含み、これらMPSもまた更に深い階層構造を有してよい。

10

#### 【0055】

本出願において使用される用語MPSは、複数のプロセッサの比較的均一なセットと、いわゆる「プラットフォームIC」チップ上に集積された汎用プロセッサ及び特殊化されたプロセッサの異種集団との両方を包含する。プラットフォームICチップは数個~多数のプロセッサを含んでよく、これらは典型的には共有メモリによって相互接続され、場合によってはオンチップネットワークによって相互接続される。MPSと「プラットフォームIC」チップとの間には違いがあってもなくてもよい。しかしながら「プラットフォームIC」チップは、特定の垂直的市場における特定の技術要件に対処するために市販されているものであってよい。

20

#### 【0056】

一般に、MPSのためのメモリは階層として組織してよく、この階層は頂部に高速なメモリを有し、階層を1段ずつ下がるにつれてより低速であるがより大容量のメモリを有する。MPS中において、階層の頂部の補助メモリは、各PEの近傍に位置してよい。各補助メモリは、最適な命令又は最適なデータを保持するよう特殊化できる。特定のPEのための補助メモリは、そのPE専用のものであっても、又は他のPEと共に用であってよい。

30

#### 【0057】

メモリ階層を更に下がると、各PEに隣接する補助メモリの何倍も大きいビット容量を有する半導体同期ダイナミックランダムアクセスメモリ(SDRAM)等の、比較的大型の共有メモリが存在してよい。SDRAMは、その製作を特定化するために、PE及び補助メモリとは分離された1つ又は複数のICチップ上に位置してよい。メモリ階層を更に下がると、フラッシュメモリ、磁気ディスク及び光学ディスク等の他のタイプのメモリが存在してよい。

#### 【0058】

MPSは、特定の機能を達成できるよう、ソフトウェアプログラムを用いてプログラムされてよい。各機能は、MPS中のPEのうちの1つ又は複数によって実行されてよい。しばしば、MPS上で複数のプログラムを同時に実行してよい。プログラムは、より複雑な機能を実施するために、及び並列処理技術を採用することによってより単純な機能をより迅速に実施するために、共に実行され、互いに通信してよい。PE間のこのような協調を、本出願では連携処理と呼ぶ。

40

#### 【0059】

MPSは、関連するデータ及びコマンドのソースが入力データ及びコマンドを提供するよりも早くこれらを受信でき、無視できる程度に十分に低いレイテンシで結果を提供できるよう、十分な速さでアプリケーション又はプログラムを実行できる。このようなアプリケーションは、遅延なくリアルタイムで動作する、即ち「リアルタイムアプリケーション

50

」と呼ばれる。関連する入力データ（又はコマンド）は「リアルタイムデータ」（又は「リアルタイムコマンド」）と呼ばれる。例えばMPSは入力信号を介してリアルタイムデータを受信してよい。アプリケーション、プログラム又は機能のうちの1つ又は複数は入力信号を処理してよく、場合によっては、1つ又は複数のプログラムに基づいて修正された又は追加のリアルタイムデータを伴う出力信号を生成してよい。

#### 【0060】

##### 図3 MPS ブロック図及び概要

図3は、マルチプロセッサシステム（MPS）の一実施形態を示すブロック図である。図示されている実施形態では、MPS10は複数の処理要素（PE）及び複数のデータメモリルータ（DMR）を含み、DMRは、データ及び命令を互いに通信するよう連結された、動的に構成可能な通信器、又は動的に構成可能な通信要素と呼ぶこともできる。本出願で使用される場合、PEはPEノードとも呼ばれる場合があり、またDMRはDMRノードとも呼ばれる場合がある。

10

#### 【0061】

処理システム（MPS）10は、GPMC、DSP、FPGA又はASICが現在使用されている様々なシステム及びアプリケーションのいずれにおいて使用してよい。従って例えば、処理システム10は、様々なタイプのコンピュータシステム又は計算を必要とする他のデバイスのいずれにおいて使用してよい。1つの考えられる実施形態では、処理システム10を、デジタルルビデオディスプレイシステムの信号処理デバイスとして使用する。

20

#### 【0062】

一実施形態では、PEは、データを操作するために構成された1つ又は複数の算術論理ユニット（ALU）、ALUを制御するために構成された1つ又は複数の命令処理ユニット（IPU）、命令又はデータを保持するよう構成された1つ又は複数のメモリ、並びに様々な種類の多重化装置及び復号器を含んでよい。このような実施形態は多数のポート（「プロセッサポート」）を含んでよく、これらのうちのいくつかはDMRに接続されるよう構成されてよく、残りは他のPEに接続されるよう構成されてよい。図7はPEの一実施形態のブロック図であり、これについて以下に更に説明する。

#### 【0063】

一実施形態では、DMRは、データ及び命令を保持するよう構成された1つ又は複数のランダムアクセスメモリ（RAM）、構成可能なコントローラ、クロスバースイッチ等のネットワークスイッチ、レジスタ並びに多重化装置を含んでよい。このような実施形態は多数のポートを含んでよく、これらのうちのいくつかはPEに接続されるよう構成されてよく（本出願ではPEタイプポートと呼ばれる）、残りはDMRに接続されるよう構成されてよい（本出願ではDMRタイプポートと呼ばれる）。DMR又はPEのいずれに又はいずれから接続されるように構成されているかにかかわらず、いずれの所定のポートに関して、このような所定のポートを通して特定のクロックサイクル内に伝送可能なデータの量は、様々な実施形態において変化し得ることに留意されたい。例えば一実施形態では、所定のポートは、1クロックサイクルにつき1データ語を伝送するよう構成されてよく、その一方で別の実施形態では、所定のポートは1クロックサイクルにつき複数のデータ語を伝送するよう構成されてよい。更に別の実施形態では、所定のポートは、時分割多重化等の技術を採用して、複数のクロックサイクルに亘って1つのデータ語を伝送してよく、これによってポートを含む物理的接続の個数を削減できる。

30

#### 【0064】

MPS10の一実施形態では、各PEは、命令のために予約された小型ローカルメモリを含んでよく、ローカルデータストレージを極めて僅かしか有しなくてよい。このような実施形態では、各PEに近接するDMRは、所定のPEにオペランドを提供するよう構成されてよい。特定の実施形態では、多数のPE命令に関して、1クロックサイクル中に、所定のPEが近隣のDMRからオペランドを読み出し、ALU演算を実行し、ALU結果を所定の近隣のDMRに保存してよい。これにより、1つのPEからのALU結果を、そ

40

50

のクロックサイクル中に、実行の直後に複数の他の P E にとって利用可能とすることができます。このようにして結果を生成することにより、近隣の P E の実行を密接に連携したもの、即ち「緊密に連結されたもの」とすることができる。

#### 【 0 0 6 5 】

本出願で使用される場合、所定の D M R 又は P E の視点から、近隣の D M R 又は P E は、特定のレイテンシ範囲内で上記所定の D M R 又は P E からアクセスできる D M R 又は P E を指す。いくつかの実施形態では、近接関係の程度を定義するレイテンシは、例えばクロック速度等の因子に応じて変化し得る。更にいくつかの実施形態では、近接の複数の度合いを定義してよく、これらの度合いは、異なる複数のアクセスレイテンシに対応してよい。例えば一実施形態では、「最も近い近接」は、データが要求されたクロックサイクルと同一のクロックサイクル中にこのデータを供給できるデバイスとして定義してよく、「次に近い近接」は、データが要求された後、1クロックサイクル以内にこのデータを供給できるデバイスとして定義してよく、これ以降も同様である。他の実施形態では、近接関係を定量化するために他のメトリクスを使用してよいことも考えられる。

10

#### 【 0 0 6 6 】

所定の M P S 実施形態では、いくつかの D M R 及び P E は、他の D M R 及び P E と論理的に隣接してよい。本出願で使用される場合、「論理的に隣接する」は、あるデバイスの1つ又は複数のポートが、他のデバイスの各ポートに、介在する D M R 又は P E を通過せずに直接接続されるような、ある D M R 及び別の D M R 又はある D M R 及びある P E といった2つのデバイス間の関係を指す。更に所定の M P S の実施形態では、いくつかの D M R 及び P E は、他の D M R 及び P E と物理的に隣接してよい。本出願で使用される場合、「物理的に隣接する」は、ある D M R 及び別の D M R 又はある D M R 及びある P E といった2つのデバイス間に他のいずれの D M R 又は P E も物理的に位置していないような、これら2つのデバイス間の関係を指す。

20

#### 【 0 0 6 7 】

いくつかの M P S の実施形態では、論理的及び / 又は物理的に隣接する D M R 及び P E 等のデバイスは、近接している又は近隣のデバイスでもある。しかしながらいくつかの実施形態では、所定のデバイス間の論理的及び / 又は物理的な隣接は、これら所定のデバイス間に、近接関係又は特定の度合いの近接関係を伴わないことに留意されたい。例えば一実施形態では、ある D M R は、相当な距離だけ離れて位置する別の D M R に直接接続されてよい。このようなペアは論理的には隣接しているものの物理的には隣接していない場合があり、一方の D M R から他方の D M R への信号伝播時間は、近接のレイテンシ要件を満たすには長過ぎるものとなり得る。同様に一実施形態では、ある D M R は別の D M R と物理的には隣接しているものの直接接続されておらず、従って論理的には隣接していない場合がある。一方の D M R から他方の D M R へのアクセスは、1つ又は複数の中間ノードを横断し得、結果として発生する通過遅延は、近接のレイテンシ要件を満たすには大き過ぎるものとなり得る。

30

#### 【 0 0 6 8 】

M P S 1 0 の所定の実施形態の技術及び実装形態に応じて、 D M R の複数のポートの具体的な数及び D M R のメモリのサイズは、全体としての D M R の所望の実行速度及びサイズとバランスを取ってよい。例えばある D M R の実施形態は、4つの P E タイプポート、4つの D M R タイプポート、4 K 語のメモリを含んでよい。このような D M R の実施形態は、ダイレクトメモリアクセス ( D M A ) 機構を提供するよう構成されてよい。 D M A 機構により、 P E が結果を計算している間に、所定の D M R が、他の D M R へ若しくは他の D M R から、又は M P S 1 0 の外部の位置へ若しくは M P S 1 0 の外部の位置から、効率的にデータをコピーできるようになる。

40

#### 【 0 0 6 9 】

M P S 1 0 の一実施形態では、データ及び命令は、複数の異なる方法のうちの1つによって D M R 間で伝送されてよい。シリアルバスは M P S 1 0 内の全てのメモリに供給されてよく、このようなバスは、外部メモリから M P S 1 0 を初期化するために、又は M P S

50

データ構造の試験をサポートするために使用できる。短距離伝送に関して、所定の P E は、その近隣の D M R へ又は近隣の D M R からデータを直接移動させるようプログラムされてよい。データ又は命令を更に長距離に亘って伝送するために、D M R のネットワーク内において通信経路を動的に生成及び破壊してよい。

【 0 0 7 0 】

このような比較的長距離のデータ伝送のために、M P S 1 0 内の相互接続された D M R のネットワークは、通信経路用のスイッチドローティングファブリック ( S R F ) を構成してよい。このような実施形態では、S R F 内の通信経路を管理するために少なくとも 2 つの方法が存在し得る。第 1 の方法はグローバルプログラミングによるものであり、経路はソフトウェア制御によって（例えば人であるプログラマによって又はルーティング能力を有するコンパイラによって）選択でき、命令を D M R 構成コントローラにコードしてクロスバーを適切にプログラムできる。経路を生成するために、その経路に沿った全ての D M R を、特定のルーティング機能によって明白にプログラムしてよい。経路が頻繁に生成及び破壊される動的な環境において、多数のクロスバー構成コードが必要となり得、これらのストレージは潜在的に限定された D M R R A M リソースを消費し得る。

10

【 0 0 7 1 】

通信経路を管理するための第 2 の方法は、「ワームホールルーティング」と呼ばれる。ワームホールルーティングを実装するために、各 D M R は、ステアリング機能のセットと、メッセージと呼ばれる語のシーケンスの、S R F を通る進行を停止及び再開させる機構とを含んでよい。全ての通信経路がステアリング機能を共通して使用及び再使用してよいため、D M R R A M を占有し得る構成コードの量は、上述のグローバルプログラミング法よりも大幅に小さくなり得る。ワームホールルーティング法に関して、ここでもまたソフトウェア制御を使用して、経路が使用する特定のリンクを選択してよいが、経路生成（本出願ではセットアップとも呼ぶ）及び破壊／リンク解放（本出願ではティアダウンとも呼ぶ）のプロセスは、最小のソフトウェア介入を伴ってハードウェア内に実装できる。

20

【 0 0 7 2 】

経路上でのデータ語の潜在的な損失を防止するために、M P S 1 0 の実施形態は、経路に沿った受信器と伝送器との間のフロー制御を実装してよい。フロー制御は、対応する受信器がそれ以上データを受信できない場合に伝送器を停止させることができ、また対応する受信器がデータを受信する準備ができた状態となった場合に伝送器を再開させることができる機構を指す。経路上でのデータのフローの停止及び再開は、ワームホールルーティングにおけるメッセージの進行の停止及び再開と多くの類似点を有し、これら 2 つは統合されたスキーム内で組み合わせることができる。

30

【 0 0 7 3 】

一実施形態では、M P S 1 0 は複数の P E 及び D M R を含んでよく、これら P E は同一であってよく、これら D M R は同一であってよく、均一なアレイ内で接続されてよい。均一なアレイにおいて、P E の大半は同一であってよく、P E の大半はそれぞれ、D M R への同一数の接続を有してよい。また均一なアレイにおいて、D M R の大半は同一であってよく、D M R の大半はそれぞれ、他の D M R 及び P E への同数の接続を有してよい。M P S の一実施形態の P E 及び D M R は、実質的に均一な様式で散在していてよい。本出願で使用される場合、「実質的に均一な散在」は、D M R に対する P E の比が、アレイの複数の部分領域の大半に亘って一貫している構成を指す。

40

【 0 0 7 4 】

実質的に均一な様式で配設された均一なアレイは、予測可能な相互接続パターンを提供する、アレイ全体に亘ってソフトウェアモジュールを再使用できるようにする等、特定の有利な特徴を有し得る。一実施形態では、均一なアレイにより、少数の P E 及び D M R の例を設計及び試験できる。システムは、1 つの D M R 及び 1 つの P E を備えるユニットを作成し、このユニットを複数回反復する、即ち「タイルリングする ( t i l i n g ) 」ことによって、組み立てることができる。このようなアプローチは、共通のシステム要素の再使用により、設計及び試験コストを低下させることができる。

50

## 【0075】

また、P E 及び D M R の構成可能な性質により、物理的に均一なアレイ上で極めて広範な不均一挙動が発生するようにプログラムできるようにすることができることに留意されたい。しかしながら代替実施形態では、M P S 1 0 は不均一なD M R 及びP E ユニットで形成してもよく、これらユニットは、規則的な若しくは不規則なアレイに、又はランダムにさえ接続してよい。一実施形態では、P E 及びD M R の相互接続は、例えば集積回路(I C)、セラミック基材又はプリント回路基板(P C B)上の回路トレースとして実装してよい。しかしながら代替実施形態では、このような相互接続は、例えば電磁エネルギー(即ち電波若しくは光学エネルギー)、無線(即ち無誘導)エネルギー、粒子(電子ビーム等)、又は分子上の電位のための導波路といった様々な細密通信リンクのいずれであってよい。

10

## 【0076】

M P S 1 0 は単一の集積回路上に実装してよい。一実施形態では、複数のM P S 集積回路を組み合わせて、より大型のシステムを生成してよい。M P S 1 0 の所定の実施形態は、シリコン集積回路(S i I C)技術を用いて実装してよく、またこのような技術の固有の特徴の原因となる様々な特徴部分を採用してよい。例えばS i I Cチップ上の回路は薄い平面内に制限され得る。これに対応して、M P S 1 0 の所定の実施形態は、図3に示すようなP E 及びD M R の2次元アレイを採用してよい。しかしながら、P E 及びD M R の異なる構成を含む、M P S の代替実施形態が考えられる。

20

## 【0077】

更に、S i I Cチップ上で使用可能な配線密度は、このようなチップ間でのものより遙かに高くてよく、各チップは、オンチップ信号とオフチップ信号とをインターフェース接続するために特別な入力/出力(I/O)回路の周縁部を有してよい。これに対応して、M P S 1 0 の所定の実施形態は、チップのコアにあるP E 及びD M R の均一なアレイと、チップの周縁部に沿った修正されたP E / D M R ユニットとで構成された、若干不均一なアレイを採用してよい。しかしながら、均一なP E / D M R ユニットと修正されたP E / D M R ユニットとの異なる構成及び組み合わせを含む、M P S の代替実施形態が考えられる。

20

## 【0078】

また、S i I C回路によって実施される計算動作により熱が生成される場合があり、これはI Cパッケージングによって除去できる。I Cパッケージングの増大には追加の空間が必要となり得、I Cパッケージングを通る、及びI Cパッケージングの周囲の相互接続は、経路の長さに比例する遅延を招き得る。従って上述のように、極めて大型のM P S は、多数のチップを相互接続することによって構成してよい。このような多チップM P S 実施形態のプログラミングは、チップ間信号遅延がチップ内遅延より遙かに長いことを考慮したものであってよい。

30

## 【0079】

所定のS i I C M P S 1 0 の実施形態では、単一のチップ上に実装できるP E 及びD M R の最大数は、所定のS i I C技術によって可能な小型化、並びに各P E 及びD M R の複雑さによって決定できる。このようなM P S の実施形態では、P E 及びD M R の回路複雑性は、標的レベルの計算スループットを達成することを条件として最小化できる。このように最小化されたP E 及びD M R を、本出願では「合理化された(b e i n g s t r e a m l i n e d)」と呼ぶ場合がある。M P S 1 0 の一実施形態では、P E に関するスループットの標的レベルは、同一のS i I C技術において作製される最良のデジタル信号プロセッサ(D S P)の算術実行ユニットのスループットの標的レベルに匹敵するものであってよい。しかしながら、標的P E スループットに関する代替的な基準を使用してよい他のM P S の実施形態が考えられる。

40

## 【0080】

いくつかの実施形態では、M P S 1 0 は、D S P 及びF P G A アーキテクチャの最良の特徴を採用してよい。D S P と同様、M P S 1 0 は、多数の処理ユニット及びオンチップ

50

メモリを有するプログラム可能なチップであってよい。しかしながらDSPに対して、MPS処理ユニットは合理化されてよく、個数が多くてよく、またMPS処理ユニット間のデータ移動並びにオンチップ及びオフチップのデータ移動の帯域幅を最大化するために、新規の方法で相互接続されてよい。DSPより多くの処理ユニットを有することにより、MPS10は、単位時間あたりに更に多くの多重化を実施でき、合理化された処理ユニットはエネルギー使用を最小化できる。内部並列処理を行う多くのDSPは、バス指向性アーキテクチャであってよい。いくつかの実施形態では、MPS10はバスを含まなくてよく、SRF内に埋め込まれた、例えばDMR内で近接した共有ローカルメモリを含んでよく、これにより、バス指向性アーキテクチャより有意に高い総帯域幅を提供できる。

## 【0081】

FPGAアプローチと比べて、いくつかのMPSの実施形態はより粗粒化されていてよい。例えばMPSの一実施形態では、演算は自然語長（例えば16ビット）を有してよく、自然語長の倍数のデータを用いて実施した場合、計算はより効率的となり得る。いくつかのMPSの実施形態では、PE及びDMRは、FPGAにおいて実現される同等の構造よりも密であってよく、これにより、比較的短い平均配線長、低い配線抵抗、少ないエネルギー使用を得ることができる。FPGA実装形態とは対照的に、いくつかのMPSの実施形態では、MPS内の全てのALUはプロセッサの一部（即ちPE）であってよく、これは、オペランドのフェッチ、及びDMR内にある周囲の迅速なメモリへの結果のライトバック（write back）を促進できる。ALU、フェッチ及びライトバック動作に関するタイミング及びクロックスキューの問題は、ICチップの設計中に一度に解決でき、またFPGA実装形態において典型的であるように、新規のアプリケーションそれぞれにおいて再度解決する必要はない。

10

## 【0082】

## MPSトポロジ及び通信

図3に示すMPS10は、図示したようにPE間にDMRを散在させることによって、迅速なメモリへの十分な接続をPEに提供できる。このような構成は、分離型（即ち非散在型）構成に対して、所定のPEがDMR内のメモリにアクセスするために必要な時間を削減でき、本出願ではこれを散在型グリッド構成と呼ぶ場合がある。図3の実施形態では、PEとDMRとの比はおよそ1:1である。しかしながら、異なるPEとDMRとの比を含んでよい他のMPSの実施形態が考えられる。

20

## 【0083】

DMRとPEとの間の接続は、図3には明示されていない。というのは、異なるタイプ及び数の接続を用いる、多数の可能な接続スキームが存在し得るためである。

30

## 【0084】

## 図4 MPS接続スキーム

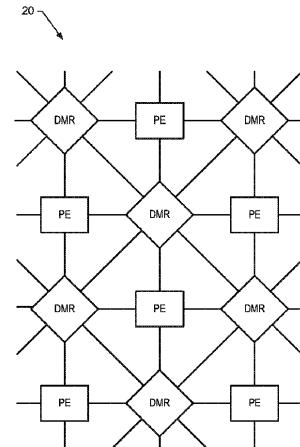

図4は、MPS接続スキームの一実施形態を示すブロック図である。MPS接続スキーム20は、複数のDMR及びPEを含み、図3のMPSの一部分を説明するものであり得る。MPS接続スキーム20では、各PEは4つの近隣のDMRに接続され、各DMRは4つの近隣のPE及び4つの近隣のDMRに接続される。従ってMPS接続スキーム20は、上述のPlanar接続スキームを説明するものであり得る。

40

## 【0085】

MPS接続スキーム20において高帯域幅ポートをサポートするために、ポート間（PE-DMR間又はDMR-DMR間）の接続は短くてよく（即ち近隣に限定されてよく）、また幅であってよい（これは、接続のデータ部分の導電体（ライン）の数が、ALUオペランド中で使用されるビット数と同一であり得ることを意味する）。PE-DMR間接続はアドレスラインを含んでよい。DMR-DMR間接続は必ずしもアドレスラインを有しなくてよいが、フロー制御用ラインを有してよい。

## 【0086】

PEノードを簡素なまま維持することによって、大型アレイ（例えばMPSの一実施形態では、16行×16列=256個のPE）を、単一のVLSI IC上に、それほど高

50

くないコストで配置できる。好適なVLSI技術は、シリコン又は他の半導体内に双極トランジスタを有する又は有しない、相補型金属酸化膜半導体(CMOS)電界効果トランジスタを含んでよいが、これに限定されない。

#### 【0087】

いくつかのMPSの実施形態では、ノード間の通信はプログラマの制御下であってよい。MPSにおいて、各PEは近隣のDMRとデータ／命令を通信してよく、また任意にこれらのDMRを通して他のDMR及びPEへと通信してよい。これは、短距離に亘る少量のデータの伝送に関して非常に効率的である。しかしながら、より大きなデータのブロック又はより長い距離に関しては、DMAエンジンを用いてデータを移動させることにより、PEを、ALU演算を実施できるよう自由にすると、より効率的である。

10

#### 【0088】

比較的長距離のブロックの移動に関して、いくつかのMPSの実施形態は、PEを関与させずにDMR間でメモリメモリ間伝送を行うための手段を提供できる。PEは、近隣のDMRのDMRタイプポートに、このようなポートと関連する特別なSMアドレスによって、間接的にアクセスできる。これにより、PEは、メッセージを送信するための新規の経路を生成して、後にこの経路をティアダウンし、あるいはメッセージを受信してよい。PEはまた、伝送されるデータのブロックを近隣のDMRのSMバッファ内に保存してよく、続いてこの近隣のDMRに、DMAの動作を、上記動作と関連する特別なSMアドレスによって開始させるよう指示してよい。これによりPEは、近隣のDMRがデータのDMA伝送を調整している間に他のタスクを進めることができるようになる。

20

#### 【0089】

MPSの様々な実施形態は、有用なアルゴリズムを実行するための有利な環境を提供できる。(例えば画像データを分析するための)関心対象となるアルゴリズムは、ALUのフロー図へと分解できる。各フロー図はMPSアレイ上にツリー、格子又は多数のフィードバック／フィードフォワード経路を含むいずれの任意のネットワークとしてマッピングできる。1つのALUの有限精度は、複数のPE及びDMRを組み合わせることによって多数の語の正確な結果を得られるように拡張されてよい。フロー図をMPSにマッピングする際、ノード間の距離に比例するPE/DMRノード間の通信遅延は上昇し得る。また、通信キューが大きい場合又は再構成が頻繁に行われる場合、マッピングは各ノードにおいてより多くのメモリを必要とし得る。これらの因子は、通信遅延、キュー及び再構成を考慮に入れることができる綿密なプログラミングによって補償できる。

30

#### 【0090】

シストリックアルゴリズムは、MPSの様々な実施形態に対して特に効率的にマッピングを行うことができるアルゴリズムのクラスを表す。シストリックアルゴリズムは、行列演算、画像処理、信号処理における幅広い応用のために開発された。シストリックアルゴリズムでは、多数のプロセッサが同期して協働し、困難な計算を実施できる。理想的なアルゴリズム実装形態では、各プロセッサは、アルゴリズムが必要とされる限り、同一の演算(又は複数の演算の短いループ)を何度も何度も実施でき、データは、データ語のバランスの取れた生成及び消費を伴って、近隣の接続によって、プロセッサのネットワークを通って流れることができる。生成される各中間結果データ語が後続の計算によって即座に消費される場合、必要なメモリの量を最小化できる。シストリックアルゴリズムの利点は、合理化されたプロセッサを使用でき、メモリ要件を最小化でき、標準的な低コストのVLSI技術を使用して高い算術演算速度を達成できる能力を含んでよい。

40

#### 【0091】

MPSのある実施形態は、1つのチップ及びMIMDアーキテクチャ全体につき多数のプロセッサを有してよく、上記MIMDアーキテクチャは、 SIMDシステム及び分散型MIMDシステムといった他のクラスのシステムの演算をエミュレートするよう構成されてよい。いくつかの実施形態では、MPSはチップの異なる領域で異なるアルゴリズムを同時に実行できる。またいくつかの実施形態では、電力を節約するために、プログラマは、少なくともいくつかのPE及びDMRへのクロックを選択的に有効化及び無効化できる

50

。従って、使用されていない P E 及び D M R を無効化できる。

#### 【0092】

##### P E / D M R ファブリック

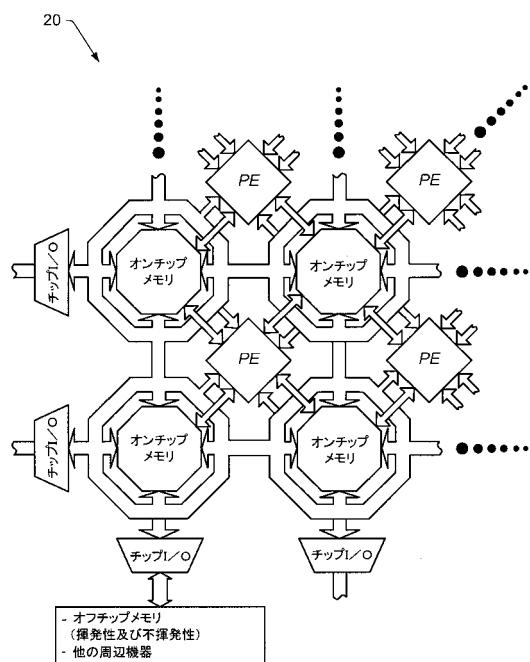

図 5 は、M P S ファブリックの一実施形態を示す更に詳細な図である。図 5 では、各 P E は 4 つの D M R に取り囲まれ、これを用いて各 P E はメモリ要求及びメッセージを通信できる。各 D M R は、ファブリックの縁部に近い場所を除いて、4 つの他の D M R に取り囲まれ、上記縁部では各 D M R はチップ I / O ポートに隣接してよい。各 D M R は近隣の D M R 又はチップ I / O ポートと通信して、通信経路をセットアップし、上記通信経路上でメッセージを送受信できる。

#### 【0093】

##### M P S の演算

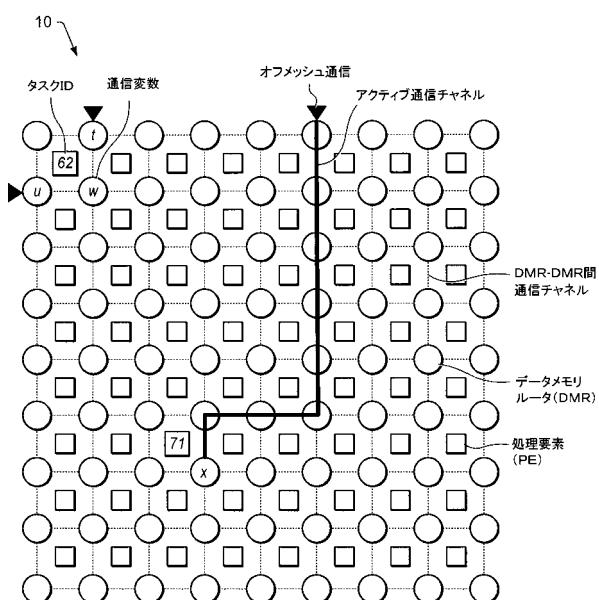

図 6 は、図 5 に示すアーキテクチャ例に従って、 $9 \times 9$  の D M R (円) のアレイと共に均一に散在する  $8 \times 8$  の P E (正方形) のアレイからなる、例示的な M P S を示す。プログラムは、P E に割り当てられるタスクへとコンパイルできる。第 1 の例示的なプログラムは、タスク I D の = 6 2 でコンパイルされており、アレイの左上隅の特定の P E に割り当てられている。変数 u、v、w は、プログラムソースコード中の宣言された通信変数であり、隣接する D M R の特定のメモリアドレスに割り当てられる。u、v は I / O ポートのためのバッファであり、w は、関連する D M R とのオンチップネットワーク通信のためのバッファである。第 2 の例示的なプログラムは、タスク I D = 7 1 でコンパイルされており、アレイの内部の特定の P E に割り当てられている。変数 x は宣言された通信変数であり、図示されている D M R に割り当てられている。変数 x に関連する通信経路は、x が割り当てられた D M R から、他の D M R を通って、最上行の I / O ポートへと続く。図示したように、これら 2 つの例示的なプログラムは互いに通信しないが、これらは、タスク 7 1 に別の通信変数を追加し、タスク 7 1 の D M R と、タスク 6 2 に隣接する D M R の変数 w との間に経路を追加することによって、容易に通信させることができる。

10

20

30

40

50

#### 【0094】

##### 動的に構成可能なプロセッサ

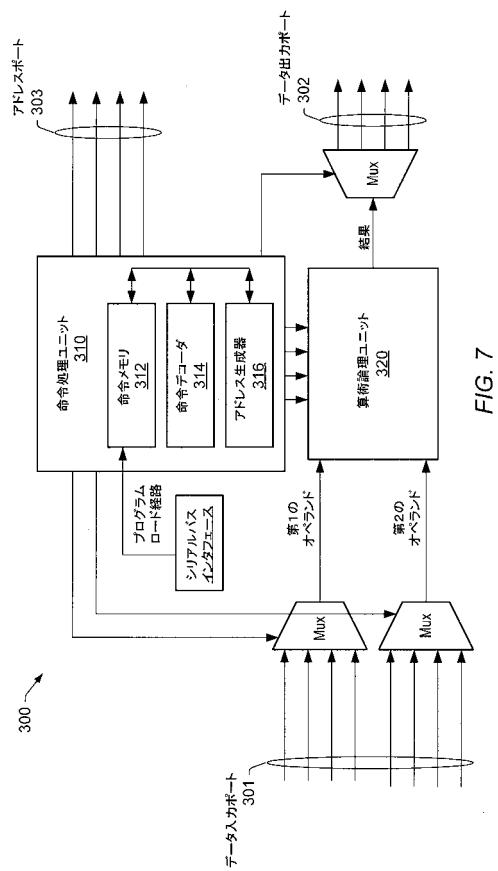

図 7 は、動的に構成できる処理要素 (P E) の例を示すブロック図である。P E 3 0 0 は、図 3 ~ 6 に示す動的に構成可能なプロセッサ (D C P) を説明するものであってよい。P E 3 0 0 は、その命令メモリを再プログラムする方法を有しているため、動的に構成可能である。図 7 ではこれは、シリアルバスインターフェースからのロード経路を通して行われる。シリアルバスは、全ての D M R 及び P E メモリをバスコントローラと接続する、2 次相互接続ネットワークであってよく、バスコントローラは 1 つ又は複数の P E によって及びチップ I / O ポートによってアクセスできる。P E を再プログラムするためには、P E を待機状態にしてよく、続いて命令メモリを新規のプログラムで上書きし、プログラムカウンタを設定し、その後 P E を待機状態から解放して上記新規のプログラムの実行を開始させてよい。P E 3 0 0 は、少なくとも 1 つの算術論理ユニット (A L U) 3 2 0 を制御するために連結された命令処理ユニット (I P U) 3 1 0 を含む。P E 3 0 0 はまた、複数の多重化装置 (本出願では m u x とも呼ばれる) に連結された複数のデータ入力ポート 3 0 1 も含み、上記多重化装置は、A L U 3 2 0 のための少なくとも第 1 及び第 2 のオペランド入力を選択するために連結される。P E 3 0 0 は更に、A L U 3 2 0 から結果データを受信するために m u x を介して連結された複数のデータ出力ポート 3 0 2 と、命令処理ユニット 3 1 0 からアドレスデータを受信するために連結された複数のアドレスポート 3 0 3 とを含む。

#### 【0095】

アドレスポート 3 0 3 は、近隣の D M R のメモリに対する読み書きを行うためにアドレスを搬送するよう構成されてよい。データ入力ポート 3 0 1 及びデータ出力ポート 3 0 2 は、近隣の D M R から及び近隣の D M R へデータを搬送するよう構成されてよい。図示されている P E 3 0 0 の実施形態では、データ入力ポート 3 0 1、データ出力ポート 3 0 2 、アドレスポート 3 0 3 はそれぞれ 4 つのポートを含み、これは図 5 の例示的なアーキテ

クチャと一致する。

【0096】

図7の例では、米国特許第7415594号に記載されているような従来技術において典型的である、単一のALU320が示されている。しかしながら、1つのPEにつき更に多くのALUが存在し、これによってPEが遙かに高い処理スループットのための潜在能力を有する、代替実施形態が考えられる。その例を本明細書中のこれ以後において示し、議論する。

【0097】

PE300は、データ語に対する算術/論理ユニット演算を実施するよう構成され、選択される演算は、IPU310が処理している現在の命令に依存する。柔軟なプログラミングをサポートするために、IPU310は、複数のアドレス指定可能な位置を含む少なくとも1つの命令メモリ312、命令復号器314、アドレス生成器316を含んでよく、これらはそれぞれ様々な相互接続機構を介して相互接続される。他の実施形態では、IPU310は2つ以上の命令メモリを含んでよいこと、又は追加の機能性を含んでよいことが考えられる。他の実施形態では更に、IPU310に示した機能性を異なるタイプの複数のユニットに分割してよいこと、又は単一の機能ユニットで実装してよいことも考えられる。

10

【0098】

IPU310は、データ入力ポート301に連結されたプログラムロード経路を介して、命令メモリ312内での保存のためにプログラムデータを受信するよう構成されてよい。命令メモリ312はまた、グローバルシリアルバス(図示せず)を介して読み書きしてよい。命令復号器314による特定の命令の復号化に応じて、IPU310は、データ入力ポート301及びデータ出力ポート302に連結された様々なmuxを制御して、近隣のDMRへ及び近隣のDMRからデータを案内するよう構成されてよい。IPU310は更に、アドレス生成器316が生成したアドレスを、アドレスポート303を介して近隣のDMRへと搬送することによって、例えばそこに位置するRAMに対して読み出し又は書き込みを行うよう構成されてよい。アドレス生成器316はまた、命令メモリ312からフェッチされ、命令復号器314によって復号化される、次の命令アドレスを生成するよう構成された、プログラムカウンタレジスタ(図示せず)も含んでよい。

20

【0099】

一実施形態では、PE300はデータレジスタファイル、データキャッシュ、又はデータオペランド若しくは結果データ用のいずれのローカルストレージを含まなくてよい。このような実施形態では、PE300は、データオペランドの読み出し及び結果データの書き込みを行うことができる迅速なストレージ媒体としてPE300が直接接続されているDMRに含まれるメモリを利用するよう構成されてよい。いくつかの実施形態では、所定のPEは異なる近隣のDMRから同時に又は異なる時点に異なるデータを得ることができる。以下に更に詳細に説明するように、いくつかの実施形態では、所定のPEは、上記所定のPEが直接接続されていないDMR内のデータの読み出し及び書き込みを、このような遠隔DMRから上記所定のPEの近隣のDMRへの経路を確立することによって行うよう構成されてもよい。

30

【0100】

PE300が実装する命令は、算術演算及び論理演算並びにメタ命令をサポートしてよい。PE命令は、2つのオペランド及び1つの結果に関するメモリをアドレス指定するために十分なビット長を有してよく、これにより1クロックサイクルでこれらの値の読み出し及び書き込みを行うことができる。

40

【0101】

他の実施形態は、追加の命令又は異なる命令のセットを実装してよいことに留意されたい。いくつかの実施形態では、1つ又は複数のデータオペランドを必要とする所定の命令の実行中、所定のPEは、近隣のDMRメモリに直接アクセスして上記必要なオペランドにアクセスするよう構成されてよい。

50

## 【0102】

P E 3 0 0 はメタ命令を実行するよう構成されてよい。本出願で使用される場合、メタ命令は、命令メモリ 3 1 2 等の P E 命令メモリに保存された命令に対する演算を実施できる命令を指す。基本的なメタ命令は、近隣の D M R の R A M から命令メモリ 3 1 2 をロードすること（即ちオーバレイをロードすること）であってよい。D M R メモリから命令メモリをロードすることにより、データと命令との間のメモリの分割をソフトウェアプログラミングによって決定できる。従ってアプリケーションのプログラマは、自身のソフトウェアを、利用可能なメモリの最良の利用に関して最適化できる。いくつかの実施形態では、P E 3 0 0 は、I P U 命令メモリを修正できる他のメタ命令を含んでよく、又は例えば試験、エラー分析及び／若しくはエラー修復のために D M R メモリに命令メモリをセーブしてよい。

10

## 【0103】

A L U 3 2 0 は、特定の P E 3 0 0 の実施形態でサポートされる命令によって定義される演算を含む、少なくとも固定小数点数系に関する演算を実施するよう構成されてよい。例えば一実施形態では、A L U 3 2 0 は固定小数点型加算、減算、乗算、積和、論理及びシフト演算を実施するよう構成されてよい。いくつかの実施形態では、A L U 3 2 0 は、拡張精度演算をサポートするために、過去の計算から得られたキャリービットを保持するよう構成されてよい。他の実施形態では、A L U 3 2 0 は、浮動小数点型演算、又は特定のアルゴリズムを実装するために選択された特定目的のための演算を実施するよう構成されてよい。

20

## 【0104】

図 8 並列実行のためのソフトウェアを開発するための方法のフローチャート

図 8 は、一実施形態による、マルチプロセッサシステム上の並列実行を標的としたソフトウェアを開発するための方法を示す。図 5 に示す方法は、とりわけここで説明するコンピュータシステム又はデバイスのいずれと併用してよい。様々な実施形態では、図示されている方法の要素のうちのいくつかは同時に、若しくは図示されているものとは異なる順序で実施されてよく、又は省略されてよい。所望に応じて追加の方法の要素を実施してもよい。図示したように、この方法は以下のように動作し得る。

30

## 【0105】

× 8 0 2 に示すように、例示的な一実施形態では、例えばマルチプロセッサシステム上の展開及び実行のために標的化されたアプリケーションの、所望のシステムの複数のビューを指定する入力を受信してよい。各ビューは、システムの各態様を提示又は指定してよく、またこれらビューは総体として、効率的な並列実行のためにマルチプロセッサシステムが展開できる実行可能なプログラムを生成するためにコンパイラ（又は他のソフトウェアツール）が使用できる情報を提供してよい。

## 【0106】

この入力は、様々な形態のいずれで、また様々なツールのいずれを介して受信されてよい。例えはいくつかの実施形態では、入力はユーザによって提供されてよく、即ちユーザ入力であってよい。他の実施形態では、入力は所望に応じて別のシステム又はプロセス、ストレージ媒体等から受信されてよい。更に入力はローカルに提供されてよく、又はローカルエリアネットワーク（L A N ）若しくはインターネット等の広域ネットワーク（W A N ）を介して受信されてよい。例示的な一実施形態では、ユーザはスプレッドシート中でビューを指定してよい。別の例示的実施形態では、ユーザはウィザード、即ちグラフィカルユーザインターフェース（G U I ）への入力をやってよく、これは指定プロセスを通して、例えばプロンプト、有用な提案等によってユーザをリードする。更なる実施形態では、ユーザは入力／指定プロセスを管理するためにチェックリストを使用してよく、指定される各アイテム、例えはビュー、サブビュー等がチェックリストに挙げられており、チェックリストは各チェックリストアイテムが指定されているか（されていないか）を示す。別の例示的実施形態では、1つ又は複数のテンプレート又はフォームを提供してよく、ユーザはビューを指定する情報で上記テンプレート又はフォームを埋めてよい。

40

50

## 【0107】

各ビューは、アプリケーションの動作又は実行の各様を含むか又はその表現となつてよい。多数のビューはメモリビュー、通信ビュー、制御ビュー、処理ビューを含んでよい。他のビューも所望に応じて定義又は指定してよい。一実施形態では、各ビューは、ビューの更に詳細な属性を指定する複数のサブビュー（又は「ファセット」）を含むか又は指定してよい。例えば各ビューは、サイズ、拳動及びアクセシビリティサブビュー（又はファセット）を含んでよく、各サブビューは、各サブビューがその一部となつてあるビューに関連する特定の意味を有してよい。

## 【0108】

従つて例えば、メモリビューは：アプリケーションによる使用に必要な又は利用可能なメモリのサイズ（又は量）、即ちデータを処理するためにアプリケーションが使用するメモリ構造サイズ；メモリの拳動、即ちメモリ構造が所定のタイミングで拳動する様式；並びにメモリのアクセシビリティ、即ち例えばアプリケーション及び／又はシステムによるメモリ構造のアクセシビリティを指定してよい。

10

## 【0109】

同様に、入力は：通信ビュー（通信ビューの各サブビュー、例えば通信サイズ、拳動、アクセシビリティを定義することを含む）；制御ビュー（制御サイズ、拳動、アクセシビリティを含む）；並びに処理ビュー（処理サイズ、拳動、アクセシビリティを含む）を定義又は指定してよい。

20

## 【0110】

いくつかの実施形態では、ビュー又はサブビューのうちのいくつかは、他のサブビュー又はビューの指定によって、例えば同一の又は異なるビューのサブビューによって、自動的に定義又は指定され得ることに留意されたい。従つて例えば、メモリサイズ、拳動及びアクセシビリティが指定されると、通信拳動が自動的に指定され得る。別の様式で考えると、いくつかの実施形態では、ビューは、方程式の数が変数の数を超える線形方程式の優決定系と同様に、「過剰に指定される」か又は「過剰に決定される」場合がある。

30

## 【0111】

本出願で使用される特定の用語又は標識は単なる例示であること、並びに所望に応じて本出願で開示される新規の構成要素、情報及びプロセスに対していずれの名称を使用してよいことに留意されたい。例えば所望に応じて、ビュー又は態様はモデル等と呼ばれる場合もあり、本出願で開示されるサブビューはサブモデル、ファセット、プロパティ等と呼ばれる場合もある。

30

## 【0112】

システムのビューが指定又は定義されると、これらのビューを表す情報は、 $\times 804$ に示すように、アプリケーションのソースコード内に含まれ得る。この包含は、広範な方法のうちのいずれにおいて実施され得る。例えばいくつかの実施形態では、情報はアプリケーションの1つ又は複数のヘッダファイルに含まれ得る。他の実施形態では、情報は、アプリケーションプログラム要素又は構成要素の中でとりわけ、1つ又は複数の動的リンクライブラリ（DLL）又はマクロ定義に含まれ得る。より一般には、ビューを表す情報は、所望に応じていずれの様式及びいずれの形態でアプリケーションソースコードに組み込まれてよい。

40

## 【0113】

$\times 806$ では、ソースコードは例えば、コンパイラ又は他のツールによって処理でき、これはシステムに関して指定又は定義された複数のビューを表す情報を分析することを含む。例えば一実施形態では、コンパイラは、アプリケーションソースコード内の複数のビューを表す情報を認識するよう構成してよく、またこの情報を抽出及び分析してよい。他の実施形態では、コンパイラは情報を原位置で分析してよい。

## 【0114】

$\times 808$ に示すように、実行可能なプログラムは上記処理に基づいて生成してよく、ここで上記実行可能なプログラムは、効率的な並列実行のためにマルチプロセッサシステム

50

に展開可能である。換言すると、コンパイラは、指定されたビューの分析を含む×806の処理に基づいて、実行可能なプログラムを生成してよい。

【0115】

従って、本技術の実施形態は、上述のようなソフトウェア開発への従来技術のアプローチの様々な欠点に対処でき、これによってユーザは、システムの動作、例えばマルチプロセッサシステム上でのアプリケーションの動作に関する様々な要件又は制約を指定でき、これら指定された要件又は制約をコンパイラ（又は他のツール）が使用して、システム上で効率的に実行できる実行可能なコードを生成してよい。

【0116】

以下に、上述の技術の様々な例示的実施形態を提示する。

10

【0117】

1. マルチプロセッサシステム内での並列実行のためのアプリケーションソフトウェアを開発するための方法であって、上記方法は、コンピュータが：第1の入力に応答して所望のシステムの複数のビューを指定するステップ（ここで上記複数のビューは：メモリビュー；通信ビュー；制御ビュー；及び処理ビューを含む）；アプリケーションプログラムのソースコードに上記複数のビューを表す情報を含めるステップ；アプリケーションプログラムのソースコードを処理するステップ（上記複数のビューを表す情報を分析するステップを含む）；並びに上記処理ステップに基づいて、実行可能なプログラムを生成するステップ（上記実行可能なプログラムは並列実行のためにマルチプロセッサシステムに展開可能である）を実施することを含む、方法。

20

【0118】

2. 複数のビューを指定する上記ステップは、各ビューに関して：サイズ；挙動；及びアクセシビリティを指定するステップを含む、実施形態1の方法。

【0119】

3. 上記入力は：ウィザード；グラフィカルユーザインターフェース；スプレッドシート；又はデータファイルのうちの少なくとも1つが受信するユーザ入力を含む、実施形態1の方法。

【0120】

4. ソースコードに上記複数のビューを表す情報を含める上記ステップは：アプリケーションプログラムの1つ若しくは複数のヘッダファイル；アプリケーションプログラムに関するマクロ定義；又は1つ若しくは複数の動的リンクライブラリ（DLL）のうちの1つ又は複数に上記情報を含めるステップを含む、実施形態1の方法。

30

【0121】

5. 上記処理ステップ及び上記生成ステップはコンパイラによって実施される、実施形態1の方法。

【0122】

6. 上記マルチプロセッサシステムはHyperXアーキテクチャを備える、実施形態1の方法。

【0123】

更なる実施形態

40

以下に、上述の技術の更なる例示的実施形態の説明を提示するが、開示される実施形態は単なる例示であり、本技術の実装をいずれの特定の形態、機能又は外観に限定することを意図したものではないことに留意されたい。特定の（非限定的な）使用のケースとして2つの例示的実施形態：撮像フィルタ及び有限インパルス応答（FIR）フィルタを提示する。

【0124】

定義されたシステムのビュー及びプロセス

あるシステムにおいてデータは、上記システムがリアルタイム型であるかそうでないかに関わらず、無線受信機、画像センサ又は他の入力収集デバイスのいずれかからの（実際の又は概念上の）ストリームとして受信されることが多い。受信されるデータは、アルゴ

50

リズム及びその代表データ構造に対して自然である方法で処理されることが望ましい。これは、処理のために、サンプル形態、ブロック形態又はハイブリッド形態のデータ構造を取り扱う能力を必要とし得る。これはまた、処理システムの通信及びメモリアーキテクチャが、様々なアルゴリズム及びデータ構造システムをサポートできるよう、リアルタイムに動的であり、かつ適合可能であることを必要とし得る。

## 【0125】

例示的な使用のケース：撮像フィルタ

一例として、等式1によって特徴付けられる例示的な撮像フィルタを考える。

## 【0126】

## 【数1】

$$y[r, c, t] = \sum_{r=-M}^{r=M} \sum_{c=-N}^{c=N} h[r, c, t] x[r, c, t]$$

等式1

## 【0127】

ここでtは時間であり、rは行インデックスであり、cは列インデックスであり、 $x[r, c, t]$ は入力ピクセルであり、 $h[r, c, t]$ はフィルタ係数であり、 $y[r, c, t]$ は出力ピクセルである。

20

## 【0128】

合計は $2M + 1$ 行及び $2N + 1$ 列に亘っており、従ってフィルタの寸法的なメモリサイズは $(2M + 1) \times (2N + 1)$ であり、最小のレイテンシが望ましい。

## 【0129】

撮像フィルタシステムを用いた、図8の方法の記述

例示的な撮像フィルタリングプロセスを、図9Aに図式的に示す。このアプローチでは、ピクセル（ピクセルデータ）のデータストリームは通常、行毎に受信される。フィルタ及び/又は境界条件のデータ要件を満たすために十分な行数のデータが受信されると、図示されているように、データを水平に横断するように2次元フィルタを走らせて、フィルタリングされた画像を生成してよい。図9Aのアプローチは図10においてブロック図の形態で表されており、この図10は、単一のプロセスを有する画像フィルタリングのブロック図を示す。

30

## 【0130】

画像データをより迅速に処理するために、一般的なスキームは、画像を垂直方向に分割するものであり、各垂直セグメントのデータは、ピクセル毎、行毎に（処理リソースに）受信されて、図9Bに示すように並列にフィルタリングが実施される。図9Bの並列アプローチは図11においてブロック図の形態で表されており、この図11は、複数のプロセスを有する画像フィルタリングのブロック図を示す。

40

## 【0131】

MPFIをサポートするANSI C言語ベースのソフトウェアプログラミングモデルにおいてスレッドを処理するための本技術の実施形態を実装する例示的なプログラム（フィルタカーネルのコード例）は、以下のように書くことができる：

```

/* filter_kernel.c

/* example hx3xxx pseudo code for 2D filter

#include <mpx.h>

#include <math.h>

#include "filter_system.h"

```

50

```

// initialize variables

int 2d_lin_buffer [(ROW+3)*COL];

// initialize 2D circular line buffer on 2d_buffer

void init_2D_circ_lin_buf ( .... )

{ .... }

// update 2D circular line address on 2d_buffer

void update_2D_circ_lin_address ( .... )

{ .... }

// 2D filter function with calculations written through

// line based pointers for efficiency. This is unnatural.

// Performs function while receiving next line of data and

// sending out previously calculated results.

void 2d_filter ( .... )

{ .... }

mpx_cell filter_kernel ( .... ) 20

{ // begin mpi_cell..

// initialize

init_2D_circ_lin_buf ( .... );

while (1)

{ // begin while

MPX_Recv( .... ); // non-blocking line receive

2d_filter( .... ); // perform filter across line of data

MPX_Send( .... ); // non-blocking line send of results

update_2D_circ_lin_address ( .... );

} // end while

} // end mpx_cell

```

コード部分 A : filter\_kernel.c フィルタカーネルのコード例

【0132】

スレッドを処理する「filter\_kernel.c」を構成するシステムは、以下のように書くことができる（フィルタシステムのコード例）：

```

/* filter_system.c

/* example hx3xxx pseudo code for 2D filter system

#include <mpx.h>

#include <math.h>

#include "filter_system.h"

```

10

30

40

50

```

mpx_cell filter_system ( . . . )

{ // begin mpx_cell..

// system defined through MPX_PARALLEL

if (MPX_RANK == MPX_PARALLEL)

{ // begin MPX_PARALLEL

distribution_and_collection: di_co_sys( . . . );

filter_thread_00: filter_kernel ( . . . );

filter_thread_01: filter_kernel ( . . . );

filter_thread_02: filter_kernel ( . . . );

. . .

} // end MPX_PARALLEL

} // end mpx_cell

```

10

コード部分 B : filter\_system.c フィルタシステムのコード例

【0133】

「void 2d\_filter( . . . )」関数は以下の例のように書くことができる :

20

```

// apply filter across line of data

for( col = begin; . . . )

{ // begin col = begin..

result [ col ] = 0;

for ( i = 0; . . . )

{ // begin i = 0..

for ( j = 0; . . . )

{ // begin j = 0..

// operations

result[ col ] += (long)( filter[ i ] [ j ] . . .

* data[ i ] [ address_line[ i ] - offset + j ] );

} // end for j = 0..

} // end for i = 0..

} // end for col = begin..

```

30

コード部分 C : M × N フィルタとして実装される 2d\_filter 関数

```

// apply Laplacian filter across line of data

```

40

```

for ( col = begin; . . . )

{ // begin for begin = 0..

// operations..

temp = in_data[ address_line[ center ] + col - Lap ] . . .

+ in_data[ address_line[ center ] + col + Lap ];

temp += (long)( in_data[ address_line[ center - Lap ] + col ] . . .

+ in_data[ address_line[ center + Lap ] + col ] );

temp -= (long)( 4 * in_data[ address_line[ center ] + col ] );

result_data[ col ] = abs(temp);

```

50

```

} // end for col = begin..

```

コード部分 D : ラプラシアンフィルタとして実装される 2 d \_ f i l t e r 関数

```

// apply Laplacian filter across line of data

```

```

address_center = address_line[ center ];

address_n_Lap = address_line[ center - Lap ];

address_p_Lap = address_line[ center + Lap ];

```

10

```

for ( col = begin; ... )

{ // begin for begin = 0..

// operations ..

temp = in_data[ address_center + col - Lap ] ...

+ in_data[ address_center + col + Lap ];

temp += (long)( in_data[ address_n_Lap + col ] ...

+ in_data[ address_p_Lap + col ] );

temp -= (long)( 4 * in_data[ address_center + col ] );

result_data[ col ] = abs(temp);

} // end for col = begin..

```

20

コード部分 E : ラプラシアンフィルタとして実装される、簡略化された v o i d 2 d \_ f i l t e r 関数

【 0 1 3 4 】

ここで提示したコード部分 / プログラムは単なる例示であり、いずれの特定のプログラム言語に実施形態を限定することを意図したものではないことに留意されたい。

【 0 1 3 5 】

論理的には、A N S I C ソフトウェアプログラミングモデルを有する M P I は、雑多なメモリ及び適合可能な通信スキームの全要件をサポートできる。実行モデルは、ソフトウェアプログラミングモデルの要件を満たす能力を提供できる。更にソフトウェアプログラミングモデルは、可変リアルタイムパフォーマンスを標的とすることができるスケーラブルなコードをサポートできる。

30

【 0 1 3 6 】

結果の例は、図 1 2 に示すような、例えば ( C o h e r e n t L o g i x , I n c o r p o r a t e d から提供される ) 例示的な  $h \times 3 \times \times \times$  プロセッサ等のメモリ ネットワークプロセッサ上で実現される。より具体的には、図 1 2 は、 $h \times 3 \times 100$  プロセッサ上で、C コードの行を変更せず、30 f p s ( 左の画像 ) 、続いて 60 f p s ( 右の画像 ) で示されている、例示的な 4 K ビデオ 2 D フィルタシステムのリソースのレイアウトを示す。ここでソフトウェアスレッドの数は増大しており、追加のハードウェアスレッドを使用してフレームレートスループットを上昇させることができる。

40

【 0 1 3 7 】

上述のように、現行のアプローチの 1 つの問題は、ソフトウェアプログラミングモデルが標的ハードウェアの特徴の外挿をサポートする場合、システムの効率的な記述ができないという点である。システムを適切に記述するためには、システムの挙動及びインタラクティブ性の全ての重要な態様を、プログラミングモデルの制御、通信、メモリ及び処理モデルそれぞれの中で何らかの方法でキャプチャしなければならない。最後の 2 つ、即ちメモリ及び処理モデルは、通常はアドレス指定されず、実行モデルから暗黙的に割り当てられると想定される。

【 0 1 3 8 】

従って、いずれのシステムを効率的に定義することは、システム全体を効率的に定義す

50

ることを必要とし得る。この例では、議論の焦点は、通信構造のプロパティ及びメモリプロパティとのインタラクティブ性からシステムを記述し、またシステム要件から処理を記述することに当たっている。図8の方法を参照して上述したように、これは、メモリ構造のプロパティ、即ち：通信をサポートするために使用される構造のサイズ；処理をサポートするために使用される構造のサイズ；処理をサポートするための構造の挙動；通信をサポートするための構造の挙動；処理をサポートするための構造のアクセシビリティ；及び通信をサポートするための構造のアクセシビリティを定義することを伴い得る。これに続いて、通信、制御及び処理プロパティを引き出すか又は明確に定義できる。

#### 【0139】

上述の撮像フィルタの例に関して、これは以下の様式で実施できる。

10

#### 【0140】

メモリ構造のサイズの定義：

図11に示すように、この撮像フィルタの例では、システムに関して最も自然なメモリ構造をサポートするために、循環ラインバッファアドレス指定スキームを生成する必要があり得る。メモリ構造は、フィルタのサイズ、即ち現在のデータのフィルタ処理に必要な行数（このケースでは $2M + 1$ ）と、処理の現在の結果をキャプチャするための更なる行と、次のデータのラインを同時に受信するための更なる行と、フィルタ処理の過去に計算された結果を送信するための更なる行とを加算した数によって定義できる。従ってこの例示的なアプリケーションに関して、メモリ構造のサイズは、積 $(2M + 4) * (2N; H / N)$ 個のピクセルとして定義又は指定できる。

20

#### 【0141】

メモリ構造の挙動の定義：

構造のサイズに加えて、所定の時点における構造の挙動を明確に定義する必要がある。この特定のケースでは、メモリの挙動は、過去に受信された処理済みのデータと、利用可能な、即ち到着済みの新規のデータとに対して定義される。具体的には、この例示的実施形態では、現在の処理のために使用されることになる、「現在のデータ」として表示できるメモリのセクションが存在し、そのサイズは「 $2M + 1$ 」行×「 $2N + 1$ 」超の列であり、また、次のデータのラインを受信するメモリのセクションが存在し、過去に計算された結果を保持するメモリのセクションが存在し、最後に、処理から現在の結果を収集するメモリのセクションが存在する。現在の処理が完了し、過去に計算された結果が送信された後、受信されたばかりの次のデータのラインが、今度は現在のデータの第1のラインとなるように、メモリの挙動を更新できる。そして現在の結果は、送信されるべき過去に計算された結果となり、現在の結果はその位置を再割り当てされる。従って、これらメモリセクションをこのように回転式で使用することにより、メモリ構造の挙動を定義でき、又は特徴付けることができる。

30

#### 【0142】

メモリ構造のアクセシビリティの定義

各メモリセクションは、定義されたアクセシビリティを有する必要がある。この特定の例示的なケースでは、現在のデータに関しては、このデータは標準的な2次元アレイの形態でアクセス可能である必要がある。上述のメモリ構造の挙動に従って、新規のデータのラインが到着して新規のデータの第1の行となり、データの最も古い又は最後の行が脱落する度に、ユーザ／プログラマの視点からのデータの自然な書き込み及びアクセスをサポートするために、物理アドレスへの2次元アクセスを更新してよい。他の3つのメモリのセクション（上述）は、データ及びフィルタリングの結果の受信並びに結果の送信をサポートする、データの1次元アレイを効果的に実装できる。

40

#### 【0143】

通信プロパティ（サイズ、挙動、アクセシビリティ）の定義

メモリ構造のサイズ、挙動、アクセシビリティが定義されると、通信間又は通信内、制御、及び処理プロパティを、そのシステム又は別のシステム内のインタラクティブ性に基づいて引き出すことができ、又は明確に定義できる。この特定のケースでは、システムの

50

入力プロパティを、メモリ構造のサイズ、挙動、アクセシビリティの定義から引き出すことができる。例えば通信無線機内のインターリーバ及び／又はデインターリーバの場合に關してといった他のシステムは、より明確な定義が必要となり得る。

【0144】

一実施形態では、次のステップは、ソフトウェアプログラミングモデル内でシステムのプロパティを効果的に表現することであってよい。これを行うには、MPI等のAPIを生成又は拡張してANSI Cをサポートすること、C++で特定のクラス構造を生成すること等を含むがこれらに限定されない、多数の方法が存在する。しかしながら、具体的な語彙的表現は重要ではない。重要なのは、プログラミングモデルがこれらの（動的な）システムの定義を認識すること、即ちツールフローがシステムの定義を解釈でき、続いてシステムを標的の実行モデル及び下層のハードウェアアーキテクチャに効果的にマッピングできることである。

10

【0145】

例示的なコードであるコード部分A、filter\_kernel.cは、制御モデル、通信モデル並びに補助メモリ構造及び処理に明らかにアプローチし、またそのように解釈される必要があり得る。これは、システムを直感的に表現でき、システムを定義でき、又は効率的にシステムを解釈できるような方法で、制御、通信及びメモリ構造の間で動的インタラクティブ性を定義できない。

20

【0146】

撮像フィルタの例を用いて続けると、filter\_kernel.cは以下のように書き換えできる：

```

/* filter_kernel.c

/* example pseudo code for 2D filter incorporating system

// property defintion

#include <mpx.h>

#include <math.h>

#include "filter_system.h"

// initialize variables

mpx_2d_lin int buffer[(ROW+3)*COL];

// 2D filter function with calculations written naturally as for (i, j)

// and performs function while receiving next line of data and

// sending previously calculated results.

void 2d_filter( .... )

{.... }

mpx_cell filter_kernel ( .... )

{ // begin mpi_cell..

while(1)

{ // begin while

MPX_Recv( .... ); // non-blocking line receive

2d_filter( .... ); //perform filter across line of data

MPX_Send( .... ); // non-blocking line send of results

} // end while

} // end mpx_cell

```

30

40

コード部分F：filter\_kernel.c 一実施形態によるシステムのプロパティの定義を組み込んだ、フィルタカーネルの更新されたコード例

50

## 【0147】

理解できるように、上記更新されたコード例であるコード部分Fにおいて、プログラム文「`mpx_2d_line int buffer[(ROW+3)*COL];`」は変数を宣言しており、具体的には、この時点ではプログラミングモデルによってサポートされている、上述のサイズ、挙動、アクセシビリティプロパティを備えるメモリ構造を宣言している。

## 【0148】

従ってここで、コード部分Aの「`void 2d_filter(...)`」関数を自然な形態で書くことができ、以下の2つの例において提示されるように、その処理において高い演算効率を達成できる：

10

```

// perform filter across line of data

for( col = begin; ... )

{ // begin col = begin..

result_data[ col ] = 0;

for ( i = 0 ; ... )

{ // begin i = 0..

for ( j = 0 ; ... )

{ // begin j = 0..

// operations

result_data[ col ] += (long)( filter[ i ][ j ]...

* in_data[ i ][ col - offset + j ] );

} // end for j = 0..

} // end for i = 0..

} // end for col = begin..

```

20

コード部分G：M×Nフィルタとして実装される`2d_filter`関数の、更新されたコード例

30

```

// apply Laplacian filter across line of data

for ( col = begin; ... )

{ // begin for begin = 0..

// operations ..

result_data[ col ] = abs ( (4 * in_data[ center ][ col ] )...

- in_data[ center ][ col - Lap ]...

- in_data[ center ][ col + Lap ]...

- in_data[ center - Lap ][ col ] ...

- in_data[ center + Lap ][ col ] );

} // end for col = begin..

```

40

コード部分H：ラプラシアンフィルタとして実装される`void 2d_filter`関数の、更新されたコード例

## 【0149】

続いて、プログラム文「`MPX_RECV(...); // non-blocking line receive`」は、挙動及びアクセシビリティのプロパティを自動的に更新する単回更新を提供できる。これは、受信されるべき次のデータのライン、処理するための現在のデータ、収集されるべき現在の結果をセットアップする。

## 【0150】

50

ツールフロー内において、コンパイラは、システムの挙動を解釈するよう、及び定義されたシステムの機能性をサポートするために、ハードウェアリソースをより効果的にマッピングするよう、設計されてよい。

【0151】

上述の撮像フィルタの例は、主としてメモリ定義（メモリビュー）の視点から記述されている。これを限定として解釈するべきではない。サイズ、挙動、アクセシビリティの観点から記述したシステムのメモリモデルに加えて、又はこれの代わりに、制御、通信、処理ビュー（及びサブビュー）を同様に使用して、システムを記述又は定義してよい。

【0152】

従って、ソフトウェアプログラミングモデル内において、効果的なシステムの記述をサポートするために、全てのモデルは、処理、メモリ、通信及び制御並びにこれらの間の及び／又はこれらの内部でのアクセシビリティのサイズ、挙動、アクセシビリティを記述するか又は暗黙的に解釈するプロセスをサポートする必要があり得る。

【0153】

例示的な使用のケース：有限インパルス応答フィルタ

別の例として、等式2によって特徴付けられる例示的な有限インパルス応答（FIR）フィルタを考える。

【0154】

【数2】

$$y[t] = \sum_{i=0}^{i=N-1} c_i x[t-i]$$

10

20

等式2

【0155】

ここで  $t$  は時間であり、  $c_i$  は係数であり、  $x[t]$  は入力サンプルであり、  $N$  はフィルタ長であり、  $y[t]$  は出力サンプルである。

30

【0156】

FIRフィルタを使用した、図8の方法の記述

このタイプのシステム（FIRフィルタ）では、データストリーム入力は典型的にはサンプル毎に、即ち1度に1サンプルずつ受信される。FIRフィルタはその長さによって特徴付けられ、これは、FIRフィルタが出力サンプルを生成するために使用する入力サンプルの数に等しい。FIRフィルタのデータ要件（例えば長さ）を満たすためにデータの十分なサンプルを受信すると、上記データに対してFIRフィルタの計算が実施され、フィルタリングされたデータサンプル出力が生成される。データをより迅速に処理するために、一般的なスキームは、フィルタ処理を複数の段階及び／又はパイプライン化されたセグメントに分割することである。ロック图形態の単一のFIRフィルタプロセスを図13に示す。ロック图形態の、段階及びパイプライン並列処理を示す多数のプロセスを用いたFIRフィルタを、図14に示す。

40

【0157】

MPIをサポートするANSI C言語ベースのソフトウェアプログラミングモデルを用いて、図12、13に示すスレッドプロセスを記述するためのプログラムは、以下のように記述できる：

```

/* fir_filter_kernel.c

/* example hx3xxx pseudo code for FIR filter

#include <mpx.h>

```

50

```

#include <math.h>

#include "fir_filter_system.h"

// initialize variables

int 1d_sample_buffer[ length_fir_filter + 3 ];

// initialize 1D circular sample buffer on 1d_sample_buffer void init_1D_circ_sa

m_buf( .... )

{ .... }

// update 1D circular sample address on 1d_sample_buffer void update_1D_circ_sa

m_address( .... )

{ .... }

// FIR filter function with calculations written with sample based pointers

// for efficiency. This is unnatural. Performs function while receiving

// next sample of data and sending out previously calculated sample result.

void fir_filter( .... )

{ .... }

mpx_cell fir_filter_kernel ( .... )

{ // begin mpx_cell..

// initialize

init_1D_circ_sam_buf( .... );

while (1)

{ // begin while

MPX_Recv( .... ); // non-blocking sample receive

fir_filter( .... ); //perform filter on current data

MPX_Send ( .... ); // non-blocking sample send of results

update_1D_circ_sam_address( .... );

} // end while

} // end mpx_cell

```

10

20

30

40

50

コード部分I : `f i r _ f i l t e r _ k e r n e l . c` fir フィルターカーネルのコード例

【0158】

従って、コード部分Jのシステムは、「`f i r _ f i l t e r _ k e r n e l . c`」処理スレッドで構成されるFIRフィルタのパイプライン相及びアルゴリズム相両方の並列処理を示す図14の構文的表現を表し、以下のように書くことができる：

```

/* fir_filter_system.c

/* example hx3xxx pseudo code for FIR filter system

#include <mpx.h>

#include <math.h>

#include "fir_filter_system. h"

mpx_cell fir_filter_system ( .... )

{ // begin mpx_cell..

// system defined through MPX_PARALLEL

```

```

if (MPX_RANK == MPX_PARALLEL)

{ // begin MPX_PARALLEL

distribution_and_collection: di_co_sys( .... );

fir_filter_phasesegment_00: fir_filter_kernel( .... );

fir_filter_phasesegment_01: fir_filter_kernel( .... );

fir_filter_phasesegment_10: fir_filter_kernel( .... );

.....

} // end MPX_PARALLEL

} // end mpx_cell

```

10

コード部分 J : fir\_filter\_system.c fir フィルタシステムのコード例

【0159】

以下のコード部分 K は、図 15 と一致した方法で循環バッファを用いて F I R 計算を実装する。

【0160】

「void fir\_filter( . . . . )」関数は、以下のように書くことができる：

```

// apply FIR filter to current sample data

// calculate filter using circular data buffer

// "1d_sample_buffer"

// assumptions:

// a. "begin" and "result" are indices into 1d_sample

// buffer [N+2] and are known to be in the range 0

// to N+2. "begin" is the index of the newest

// sample and (result-1) is the index of the oldest

// sample.

// b. "filter [N]" array variable contains filter

// coefficients/

```

20

```

// initialize variables

int i;

int end;

int ind;

long temp_result;

// process part 1

// calculates the filter from newest sample to oldest

// sample or the end of the data buffer

// "1d_sample_buffer"

```

40

```

// determine the "end" condition for the

// processing of part 1

if (begin > 3) {

end = N+3;

}

else {

end = (N + begin);

}

```

50

```

// processing of filter for "process part 1"

ind = 0;

for( i = begin; i < end; i=i+1 )

{ // begin for i = 0..

temp_result += ( long ) 1d_sample_buffer [ i ] * filter [ ind ];

ind += 1;

} // end for i = 0..

```

10

```

// process part 2, if necessary

// calculates the remaining data for the filter

// continuing from newest to oldest if process 1 did

// not perform all the processing

if (begin > 3)

{ // begin if begin..

for ( i = 0; i < (result) ; i=i+1 )

{ // begin for i = 0..

temp_result += ( long ) 1d_sample_buffer [ i ] * filter [ ind ];

ind += 1;

} // end for i = 0..

} // end if begin..

```

20

```

1d_sample_buffer[result] = temp_result;

```

コード部分 K : f i r \_ f i l t e r 関数

【 0 1 6 1 】

この実装形態では、「1d\_sample\_buffer」は、図15に示した経時的メモリにおける構造と同様に演算できる。

【 0 1 6 2 】

撮像フィルタの例に関して上述したように、論理的には、ANSI C ソフトウェアプログラミングモデルを有するMPIは、雑多なメモリ及び適合可能な通信スキームの全要件をサポートできる。実行モデルは、ソフトウェアプログラミングモデルの要件を満たす能力を提供でき、またソフトウェアプログラミングモデルは、可変リアルタイムパフォーマンスを標的とすることができますスケーラブルなコードをサポートできる。

【 0 1 6 3 】

これもまた上述のように、現行のアプローチでは、標的ハードウェアの特徴の外挿をサポートするソフトウェアプログラミングモデルは、システムの効率的な記述を可能とすることができないか、又は促進しない。

【 0 1 6 4 】

この例示的な FIR フィルタの例では、議論の焦点は、通信構造のプロパティ及びメモリプロパティとのインタラクティブ性からシステムを記述し、またシステム要件から処理を記述することに当てられている。これは、通信構造のプロパティ、即ち：通信をサポートするために使用される構造のサイズ；処理をサポートするために使用される構造のサイズ；処理をサポートするための構造の挙動；メモリをサポートするための構造の挙動；処理をサポートするための構造のアクセシビリティ；及びメモリをサポートするための構造のアクセシビリティを定義することを伴い得る。この通信ビューが定義されると、メモリ、制御及び処理プロパティを引き出すか又は明確に定義できる。例示的な一実施形態では、これは以下の方法で実施できる。

【 0 1 6 5 】

通信構造のサイズの定義

30

40

50

図14のFIRフィルタ例において示すように、システムに関して最も自然なメモリ構造をサポートするために、循環サンプルバッファアドレス指定スキームが生成され得る。通信構造のサイズは、フィルタのサイズ、即ち現在のデータのフィルタ処理に必要な行数（このケースでは1N）と、処理の現在の結果をキャプチャするための更なるサンプルと、次のデータのサンプルを同時に受信するための更なるサンプルと、FIRフィルタ処理の過去に計算された結果を送信するための更なるサンプルとを加算した数によって定義できる。従ってこの例示的なアプリケーションに関して、通信構造のサイズは、「N+3」として定義又は指定できる。

#### 【0166】

##### 通信構造の挙動の定義：

通信構造のサイズに加えて、所定の時点における構造の挙動を明確に定義する必要がある。この特定のケースでは、通信の挙動は、過去に受信された処理済みのデータと、利用可能な、即ち到着済みの新規のデータとに対して定義される。具体的には、この例示的実施形態では、現在の処理のために使用されることになる、「現在のデータ」として表示される（通信メモリの）セクションが存在し、そのサイズは「N」サンプル超であり、また、次のデータのサンプルを受信するセクション（又はサンプル空間）が存在し、過去に計算された結果を保持するセクション（又はサンプル空間）が存在し、最後に、処理から現在の結果を収集するセクションが存在する。現在の処理が完了し、過去に計算された結果が送信された後、受信されたばかりの次のデータのサンプルが、今度は現在のデータの第1のサンプルとなるように、通信の挙動を更新できる。そして現在の結果は、送信されるべき過去に計算された結果となり、現在の結果はその位置を再割り当てされる。従って、これら通信（メモリ）セクションをこのように回転式で使用することにより、通信構造の挙動を定義でき、又は特徴付けることができる。

10

20

30

40

#### 【0167】

##### 通信構造のアクセシビリティの定義

各通信セクションは、定義されたアクセシビリティを有する必要がある。この特定の例示的なケースでは、現在のデータに関しては、このデータは標準的な1次元アレイの形態でアクセス可能である必要がある。上述の通信構造の挙動に従って、新規のデータのサンプルが到着して又は受信されて新規のデータの第1のサンプルとなり、データの最も古い又は最後のサンプルが脱落する度に、ユーザ／プログラマの視点からのデータの自然な書き込み及びアクセスをサポートするために、物理アドレスへの1次元アクセスを更新してよい。他の3つの通信のセクション（上述）は、データ及びフィルタリングの結果の受信並びに結果の送信をサポートする、データのサンプル空間を効果的に実装できる。

#### 【0168】

##### メモリプロパティ（サイズ、挙動、アクセシビリティ）の定義

通信構造のサイズ、挙動、アクセシビリティが定義されると、メモリ間又はメモリ内、制御、及び処理プロパティを、そのシステム又は別のシステム内のインタラクティブ性に基づいて引き出すことができ、又は明確に定義できる。この特定のケースでは、システムの入力プロパティを、通信構造のサイズ、挙動、アクセシビリティの定義から引き出すことができる。

#### 【0169】

ここでもまた、次のステップは、ソフトウェアプログラミングモデル内でシステムのプロパティを効果的に表現することであってよく、これを行うには、MPI等のAPIを生成又は拡張してANSI Cをサポートすること、C++で特定のクラス構造を生成すること等を含むがこれらに限定されない、多数の方法が存在する。しかしながら上述のように、具体的な語彙的表現は重要ではない。寧ろ重要なのは、プログラミングモデルがこれらの（動的な）システムの定義を認識すること、即ちツールフローがシステムの定義を解釈でき、続いてシステムを標的の実行モデル及び下層のハードウェアアーキテクチャに効果的にマッピングできることである。

#### 【0170】

50

例示的なコードであるコード部分I、fir\_filter\_kernel.cは、制御モデル、メモリモデル、補助通信構造及び処理に明らかにアプローチし、またそのように解釈される必要があり得、これは上述のように、システムを直感的に表現でき、システムを定義でき、又は効率的にシステムを解釈できるような方法で、制御、通信、処理及びメモリ構造の間で動的インターフェイスを定義できない。

【0171】

FIRフィルタの例を用いて続けると、fir\_filter\_kernel.cは以下のように上書きできる：

```

/* fir_filter_kernel.c

/* example pseudo code for FIR filter incorporating system

// property defintion

#include <mpx.h>

#include <math.h>

#include "filter_system.h"

// initialize communication memory

struct com_fir {

int com [N];

int receive;

int send;

int result;

}

com_fir com;

// FIR filter function with calculations written naturally as for(i)

// and performs function while receiving next sample of data and

// sending previously calculated result.

void fir_filter( .... )

{.... } 30

mpx_cell fir_filter_kernel( .... )

{ // begin mpi_cell..

// receive initialization of FIR filter properties of generic FIR filter

// kernel including type (size and amount) of input and output for

// MPX_FIFO_IN and MPX_FIFO_OUT

MPX_Recv( .... ) ;

while(1)

{ // begin while

// non-blocking sample receive or data sample receive and partial

// accumulation

MPX_Recv( com.receive,....,MPX_FIFO_FIR |

MPX_NONBLOCKING           |

MPX_FIFO_IN );

fir filter( .... ); //perform FIR filter across current data in

// "com"

// non-blocking send of resulting sample or sample data

// and partial accumulation

MPX_Send( com.send,....,MPX_FIFO_FIR | 40

MPX_NONBLOCKING           |

MPX_FIFO_OUT );

}

}

50

```

```

MPX_NONBLOCKING ... |

MPX_FIFO_OUT );

} // end while

} // end mpx_cell

```

コード部分 L : fir\_filter\_kernel.c 一実施形態によるシステムのプロパティの定義を組み込んだ、fir フィルタカーネルの更新されたコード例

【0172】

コード部分 L の更新されたコード例に示すように、プログラム文「int com[N];」は変数を宣言しており、これは、この時点ではプログラミングモデルによってサポートされている、上述のサイズ、挙動、アクセシビリティプロパティを備える通信構造として使用される。これはコード部分 L 中の、「MPX\_Recv(com, ..., MPX\_FIFO\_FIR | MPX\_NONBLOCKING | MPX\_FIFO\_IN);」及び「MPX\_Send(com, ..., MPX\_FIFO\_FIR | MPX\_NONBLOCKING | MPX\_FIFO\_OUT);」という例示的な MPI 構造体によって示される。

【0173】

ここで、コード部分 K の「void fir\_filter(...);」関数を自然な形態で書くことができ、以下のように、その処理において高い演算効率を達成できる：

```

// apply FIR filter to current sample data

int40 temp = 0;

for( i = 0; i < FILTER_LENGTH; i++ )

{ // begin i = begin..

temp += (long) com.com[ i ] * filter[ i ];

} // end for i = 0..

com.result = temp >> SCALE;

```

コード部分 M : 更新された fir\_filter 関数

【0174】

ここで「com」通信メモリは、図 16 に示した経時的メモリにおける構造と同様に演算できる。

【0175】

最後に、プログラム文「MPX\_Recv( com.receive, ..., MPX\_FIFO\_FIR | MPX\_NONBLOCKING | MPX\_FIFO\_IN); // non-blocking sample receive or data sample receive and partial accumulate」は、挙動及びアクセシビリティのプロパティを自動的に更新する単回更新を提供できる。これは、受信されるべき次のデータのサンプル、処理するための現在のデータ、収集されるべき現在の結果をセットアップする。

【0176】

上述の FIR フィルタの例の例示的な 1 つの変形例では、FIR フィルタの一部はスレッドで実施され、計算のために FIR の部分累算を受信する必要があり、計算が完了すると、適切なデータサンプルを有する別のスレッドへ転送する。例示的なコード部分 N は、サンプルデータ及び部分累算を受信するスレッドを示し、これにコード部分 O が続き、これは部分 FIR フィルタカーネル、及び図 17 に示すような代表的な通信メモリ構造の使用を示し、図 14 の FIR 相 / セグメントの中段のブロックに対応する。

10

20

30

40

50

```

/* fir_filter_kernel.c

/* example pseudo code for FIR filter incorporating system

// property definition

// it receives partial_result, sampled data, and sends sampled data

```

```

#include <mpx.h>

#include <math.h>

#include "filter_system.h"

```

10

```

// initialize communication memory

struct com_fir {

int com[FILTER_LENGTH];

int receive;

int40 result_partial;

}

com_fir com;

```

```

// FIR filter function with calculations written naturally as

//for (i)

// and performs function while receiving next sample of data and

// sending previously calculated result.

void fir_filter( .... )

{.... }

```

20

```

mpx_cell fir_filter_kernel ( .... )

{ // begin mpi_cell..

// receive initialization of FIR filter properties of generic FIR filter

// kernel including type (size and amount) of input and

// output for MPX_FIFO_IN and MPX_FIFO_OUT

MPX_Recv( .... );

```

30

```

while (1)

{ // begin while

// non-blocking sample receive or data sample receive and

// partial accumulation

MPX_Recv( com. receive |

com. result_partial,....,MPX_FIFO_FIR | ...

MPX_NONBLOCKING ... |

MPX_FIFO_IN );

```

40

```

fir_filter( .... ); //apply FIR filter across

//current data in "com.com"

// non-blocking send of resulting sample or sample data

// and partial accumulation

MPX_Send ( com.com [N-1] | com.result_partial , ...., ...

MPX_FIFO_FIR | ... MPX_NONBLOCKING |

MPX_FIFO_OUT );

```

```

} // end while

```

50

```

} // end mpx_cell

```

コード部分N：サンプリングされたデータ及び部分累算転送をサポートする通信モデル構造のコンテキスト内の、部分フィルタカーネル組み込みシステムのプロパティの定義の例

```

// perform part of a FIR filter on current sample data

// supporting receiving partial accumulation and

// forwarding partial accumulation

for( i = 0; i < FILTER_LENGTH; i++ )

{ // begin i = begin..

com.result_partial += (long)com.com[ i ] * filter[ i ];

} // end for i = 0..

//not needed: com. result = temp >> SCALE;

```

10

コード部分O：部分累算をサポートする、自然な形態で書かれたFIRフィルタカーネルの一部

【0177】

サンプルのみを受信し、部分累算結果と共にサンプルを送信するためのコード、並びにサンプル及び部分累算を受信して最終的なFIRフィルタ結果を生成するためのコードは、提供された2つのFIRコードの例の変形例として書くことができ、ここでは簡潔にするためにこれを提示しない。本出願に開示される技術のこのような具体的な実装形態は、プログラミング技術を有する者の能力の範囲内である。多数の他のフィルタタイプも同様の様式で再構成でき、他のアルゴリズム及びプロセスについても同様である。換言すると、上述の例は単なる例示及び例証であり、本発明の範囲を制限することを意図したものではない。

20

【0178】

従って、上で開示されている技術の実施形態は、マルチプロセッサシステム上でのソフトウェアの並列実行に関する従来技術のアプローチを上回る有意な効率を提供できる。

30

【0179】

コード部分Mに比べて、コード部分Oは、整数に適合するためのアキュムレータのリスケールを必要としない。

【0180】

撮像フィルタの例に関して上述したように、ツールフロー内において、コンパイラは、システムの挙動を解釈するよう、及び定義されたシステムの機能性をサポートするために、ハードウェアリソースをより効果的にマッピングするよう、設計されてよい。

40

【0181】

上述のFIRフィルタの例は、主として通信定義（通信ビュー）の視点から記述されている。ここでもまた、これを限定として解釈するべきではない。サイズ、挙動、アクセシビリティの観点から記述したシステムの通信モデルに加えて、又はこれの代わりに、制御、メモリ、処理ビュー（及びサブビュー）を同様に使用して、システムを記述又は定義してよい。

【0182】

システム設計の効率的な捕捉に続いて、ハードウェアからのより効率的な操作を達成するために、定義されたシステムプロパティをサポートするための新規のプログラム可能なハードウェア特徴部分が生成されている。これらの特徴部分は、処理要素、データ経路、アドレス生成、制御フロー等を含んでよいがこれらに限定されない。これらの特徴部分は、所定の演算サイクルにおいて（実質的に）最大の演算及びエネルギー効率を達成すること、並びに多くの計算負荷が高いアプリケーションにおいてオーバヘッド（セットアップ、インデックスレジスタ更新等）をゼロ近くまで低減することを目的としている。

50

## 【0183】

## ハードウェア要素

以下は、改善されたシステムを提供する、様々な新規のハードウェア要素を説明する。

## 【0184】

ハードウェアの設計は、標的とされたシステムアプリケーションに関して、エネルギー効率の良い様式で実施できるよう、密接に連結され得る。循環データバッファリングを、モジュロアドレッシング及び（以下に説明する）D M R F I F O 技術をハードウェア反復ループと共に用いて行ってよく、これによりループにおけるアドレス指定が自動化される。（以下に説明する）H y p e r O p は、従来の技術が必要とする高い最適化コストを要することなく、高度な並列処理を制御する方法を提供する。（以下に説明する）マルチデータ経路ハードウェアは、実際のアルゴリズム数学セクションのより良好な並列処理を、純粋なA S I C 、非プログラマブルソリューションと略同じ程度に効率的な様式で可能とする。自動反復バッファリングは、フェッチ（及び復号化）電力を削減する。限定されたアドレス空間は、データ及び命令の両方に關して、効率的なアドレス指定及び読み出し／書き込み動作を提供する。データの再整列及びアキュムレータ転送は、データ移動オーバヘッドを低減するため、及びアルゴリズムをより迅速に実行できるよう、多数のP E を1つに結合して、追加のリソースを動作させるための機構を提供する。

10

## 【0185】

## 目標

ハードウェアシステムのいずれの工学的実装の目標は、システムに必要な機能性を最小のコスト関数で提供することである。このコスト関数は多数の態様を含み、ここで最も重要なもののうちのいくつかは、実際のハードウェアコスト、システム全体を実装するための時間／コスト、使用コスト（電力及び面積）等である。これは様々な方法でトレードオフを克服する多数のオプションを何度も利用できる。前の節において、提示された様々なソリューションは、G P P 、G P U 、D S P 、F P G A 、メニーコア／マルチコア、A S I C を含んでいた。これらのタイプのハードウェアを用いて利用可能な既存のシステムの実装は、複雑性、使いやすさ、プログラム可能性、柔軟性、コスト、電力の点で大きく異なる。与えられた例のうち、所定のシステムに關して最も電力効率が良いのはA S I C である。しかしながら、A S I C は最も柔軟性のないものでもあり、また開発の時間及びコストに關して最も犠牲の大きいものである。その他のものはより柔軟性を提供するが、大抵比較的低いコスト／時間及び増大された電力においてトレードオフを有している。本出願において記載するハードウェアの目標は、純粋なA S I C ハードウェアソリューションの電力効率に依然としてアプローチしながら、特定のタイプの計算負荷のための従来の手段によって高度にプログラム可能なハードウェアプラットフォームを提供することである。

20

30

## 【0186】

## 概念

この目標に挑戦し、到達するために、提示されている他のソリューションの実質的に全てから概念を借用する。これらの概念の革新的な修正及び組織化は、より迅速な実装（市場に出るまでの時間）を可能とするために望まれる高度なプログラム可能性を依然として提供しながら、電力効率に關して純粋なハードウェアソリューションにアプローチする電力効率の良い実装を可能とする。使用されるソフトウェア技術は、ハードウェアを補助するパフォーマンス及び電力最適化を提供するアーキテクチャに密接に連結される。

40

## 【0187】

ここでの主要な焦点は、低電力で高スループットを提供するために実行ユニット又は処理要素（P E ）をどのように設計するかを説明することである。これは、処理のためにデータがP E へと及びP E から流れるファブリックを提供するデータメモリルータ（D M R ）における、メモリ及び通信システムに連結される。

## 【0188】

## 処理要素

50

従来技術（GPP、GPU、マルチコア、DSP等）における処理要素（PE）は複数の命令アーキテクチャを有し、これら命令アーキテクチャは、従来の完全に符号化された命令、又は多数の演算ユニットの制御のための多数のスロットを有する超長命令語（VLW）であった。これらのアーキテクチャにおけるデータ経路に関して、従来技術のうちのいくつかは、様々な程度の独立性によって並列に演算を行うことができる多数の演算ユニットを含む。スーパースケーラ型の実装において混合される多数の命令ストリームをサポートできるものもあれば、シングルスレッド化されるものもある。

#### 【0189】

ここで提示する革新的なPEのアーキテクチャは、従来の完全に符号化された命令及びサブ命令のためのVLW型スロットのハイブリッドである。これは極めて柔軟かつ効率的な命令アーキテクチャであり、乗算器、ALUユニット、アドレス生成器等といった多数の演算ユニット及びこれらを相互接続するための機構を有する多種多様なデータ経路をサポートできる。命令ストリームの実行をスケジューリングするために多くのハードウェアを必要とするスーパースケーラアーキテクチャの動的スケジューリングとは異なり、このアーキテクチャは、命令ストリームを生成するソフトウェアツール（コンパイラ、アセンブラー等）によって提供される静的スケジューリングを提供する。この静的スケジューリングは、静的スケジューリングを例えればGPPのランダムな命令ストリームに関してあまり最適でないものとするいくつかの制限を有しているものの、適切な最適化コンパイラ及びソフトウェア開発ツールと連結される場合、DSP及び画像処理のための高度に構造化されたリアルタイム型アルゴリズムにとって完全に十分であり、大いに改善された実行時の電力効率を提供する。

10

20

30

#### 【0190】

PEは、演算ユニットが実行される多数のパイプラインステージで構成される。主要な演算ユニットは、命令フェッチ、復号化／発行、オペランドフェッチ、実行ユニット及びライトバック（フェッチに連結される）である。使用される公称9ステージパイプラインを図18に示し、演算ユニットがパイプラインのどこで動作するかが示されている。

#### 【0191】

このパイプライン構造は寧ろ、今日の基準に照らしても浅く、これは目的を有している。個々のユニット及び特徴の設計を、低電力設計を可能とする固有の設計点に重点を置いて、以下の節で議論する。読者は情報が多数のセクションに亘って情報が広がる傾向にあることに気付くだろう。というのは、特徴及びアーキテクチャが共に動作する多数の機能性ユニットを横断して、固有の全体的なハードウェア設計を生成するからである。大半のものよりも少ないステージを有するパイプラインは、パフォーマンスを向上させ電力を削減するために行われるハードウェア最適化の一部である。より小さく、より単純なハードウェアを用いて、パイプラインを、浅いパイプラインによってでさえ高いパフォーマンレベルで実行されるよう構築できる。

30

#### 【0192】

##### 実行パイプライン

##### 基本的なパイプライン