(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-235555

(P2008-235555A)

(43) 公開日 平成20年10月2日(2008.10.2)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12 501P

テーマコード (参考)

審査請求 未請求 請求項の数 7 O L (全 14 頁)

(21) 出願番号

特願2007-72706 (P2007-72706)

(22) 出願日

平成19年3月20日 (2007.3.20)

(71) 出願人 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者

町田 洋弘

長野県長野市小島田町80番地 新光電気

工業株式会社内

(54) 【発明の名称】電子装置の製造方法及び基板及び半導体装置

## (57) 【要約】 (修正有)

【課題】基板本体とその上部に絶縁層を介して形成される導電パターンとをバンプを用いて接続する構造を有する電子装置の製造方法及び基板及び半導体装置に関し、低コスト化及び製造工程の簡単化を図りつつ信頼性の向上を図る手段を提供する。

【解決手段】半導体チップ101Aに形成された電極パッド103上に突起部を有するバンプ104を形成する工程と、突起部の一部を半導体チップ101A上に形成された絶縁層105の上面に露出させる工程と、絶縁層105の上面及び先端部104Dの露出した部分に導電層107Aを形成する工程と、導電層107Aの先端部104Dと対向した突出部分を研削口一ル112により除去して導電層107Aから露出させる工程と、導電層107Aを給電層とした電解メッキにより導電層を形成すると共にこれをパターニングする工程とを有する。

【選択図】図3G

本発明の一実施例である半導体装置の製造方法を説明する断面図(その7)

**【特許請求の範囲】****【請求項 1】**

基板本体に形成された電極パッド上に、突起部を有するバンプを形成する第1の工程と、

前記基板本体上に絶縁層を形成すると共に、前記突起部の一部を前記絶縁層の上面に露出させる第2の工程と、

前記絶縁層の上面及び前記突起部の露出した部分に導電層を形成する第3の工程と、

前記導電層の前記突起部と対向した突出部分を機械加工により除去し、前記突起部を前記導電層から露出させる第4の工程と、

前記導電層を給電層とした電解メッキにより配線層を形成すると共に、該配線層をパターニングして前記バンプに接続した導電パターンを形成する第5の工程と、

10

を有することを特徴とする電子装置の製造方法。

**【請求項 2】**

前記基板本体は、半導体基板であることを特徴とする請求項1記載の電子装置の製造方法。

**【請求項 3】**

前記第4の工程で実施される機械加工は、研削加工であることを特徴とする請求項1又は2記載の電子装置の製造方法。

**【請求項 4】**

前記研削加工で用いる研削砥石の切削位置は、前記導電層の前記突起部と非対向位置の高さよりも高く、かつ、前記導電層の前記突起部との対向位置の高さよりも低く設定されていることを特徴とする請求項3記載の電子装置の製造方法。

20

**【請求項 5】**

前記第1の工程では、前記バンプがボンディングワイヤにより形成されることを特徴とする請求項1乃至4のいずれか1項記載の電子装置の製造方法。

**【請求項 6】**

電極パッドが形成された基板本体と、

前記電極パッド上に形成された、突起部を有するバンプと、

前記基板本体上に形成された絶縁層と、

該絶縁層上に形成された導電層と、

該導電層上に形成されると共に前記バンプに接続された導電パターンとを有し、

30

前記突起部の先端面と前記導電層の上面とが面一とされていることを特徴とする基板。

**【請求項 7】**

電極パッドが形成された半導体チップと、

前記電極パッド上に形成された、突起部を有するバンプと、

前記半導体チップ上に形成された絶縁層と、

該絶縁層上に形成された導電層と、

該導電層上に形成されると共に前記バンプに接続された導電パターンとを有する半導体装置であって、

前記突起部の先端面と前記導電層の上面とが面一とされていることを特徴とする半導体装置。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は電子装置の製造方法及び基板及び半導体装置に係り、特に基板本体とその上部に絶縁層を介して形成される導電パターンとをバンプを用いて接続する構造を有する電子装置の製造方法及び基板及び半導体装置に関する。

**【背景技術】****【0002】**

例えば、半導体基板或いはガラス基板等の基板上に電極及び導電パターン等を形成した

50

電子機器が種々提供されている。その一種として、チップサイズパッケージと呼ばれる半導体装置が提供されている（例えば、特許文献1参照）。

【0003】

このチップサイズパッケージは、半導体基板であるウエハーをダイシングした半導体チップのデバイス形成面上に、パッシベーション層（保護層）を介して再配線（パッケージングのための配線）を形成した構造を有している。

【0004】

また、特許文献1に開示されたチップサイズパッケージを製造するには、先ず半導体ウエハーの半導体チップ領域上に複数の電極を形成し、この各電極にバンプを形成する。

【0005】

ここで、バンプはボンディング装置を用いてボンディングワイヤにより形成される。具体的な形成手順としては、先ずボンディング装置はキャピラリから延出されたボンディングワイヤを電極パッドへ接合し、続いてボンディングワイヤを繰り出しながらキャピラリを上昇させ、そして繰り出されたボンディングワイヤを切断することによりバンプを形成する。

【0006】

このため、上記のボンディングワイヤにより形成されるバンプは、形成される面（電極パッド）からの高さにばらつきが生じてしまい、そのままではバンプに接続される再配線を形成することが困難となってしまう。このため、次工程として、形成された各バンプに対して一括して加重をかけ、バンプの上部を実質的に平坦化する処理（レベリング処理）を行う。

【0007】

続いて、バンプが形成された半導体ウエハーを樹脂によって覆うと共に、この樹脂を研磨することによりバンプの上面を樹脂から露出させる。そして、この樹脂から露出した各バンプに半田ボールを形成し、次に半導体ウエハーを半導体チップ領域ごとに個々分割処理（ダイシング処理）することによりチップサイズパッケージが製造される。

【特許文献1】特開2002-313985号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、上記の特許文献1に係る方法では、バンプの高さばらつきを是正するために各バンプに対して一括して加重をかけてバンプの上部を平坦化するレベリング処理が必要になり、製造工程が複雑化してしまうという問題があった。

【0009】

また、上記の特許文献1に係る方法では、バンプを覆うように絶縁層を形成しているため、バンプを露出するために絶縁層を研磨する研磨工程が必要となってしまう。また、当該研磨工程の後に再配線を形成するためには、例えば無電解メッキ法を用いる場合には絶縁層の表面を荒らす処理（いわゆるデスマニア処理）が必要になり、メッキ層を形成するための処理が複雑になってしまう。このため、半導体装置の製造コストアップの原因となってしまう。

【0010】

また、スパッタリング法やCVD法などにより導電層を形成することも可能であるが、これらの方法は真空処理容器を有する高価な成膜装置が必要となるため、製造コストのアップにつながり、現実的ではない。

【0011】

本発明は上記の点に鑑みてなされたものであり、低コストで製造可能な信頼性の高い電子装置の製造方法及び基板及び半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

上記の課題を解決するために本発明では、次に述べる各手段を講じたことを特徴とする

10

20

30

40

50

ものである。

【0013】

請求項1記載の発明に係る電子装置の製造方法は、

基板本体に形成された電極パッド上に、突起部を有するバンプを形成する第1の工程と

、

前記基板本体上に絶縁層を形成すると共に、前記突起部の一部を前記絶縁層の上面に露出させる第2の工程と、

前記絶縁層の上面及び前記突起部の露出した部分に導電層を形成する第3の工程と、

前記導電層の前記突起部と対向した突出部分を機械加工により除去し、前記突起部を前記導電層から露出させる第4の工程と、

前記導電層を給電層とした電解メッキにより配線層を形成すると共に、該配線層をパターニングして前記バンプに接続した導電パターンを形成する第5の工程とを有することを特徴とするものである。

【0014】

また、請求項2記載の発明は、

請求項1記載の電子装置の製造方法において、

前記基板本体は、半導体基板であることを特徴とするものである。

【0015】

また、請求項3記載の発明は、

請求項1又は2記載の電子装置の製造方法において、

前記第4の工程で実施される機械加工は、研削加工であることを特徴とするものである

。

【0016】

また、請求項4記載の発明は、

請求項3記載の電子装置の製造方法において、

前記研削加工で用いる研削砥石の切削位置は、前記導電層の前記突起部と非対向位置の高さよりも高く、かつ、前記導電層の前記突起部との対向位置の高さよりも低く設定されていることを特徴とするものである。

【0017】

また、請求項5記載の発明は、

請求項1乃至4のいずれか1項記載の電子装置の製造方法において、

前記第1の工程では、前記バンプがボンディングワイヤにより形成されることを特徴とするものである。

【0018】

また、請求項6記載の発明に係る基板は、

電極パッドが形成された基板本体と、

前記電極パッド上に形成された、突起部を有するバンプと、

前記基板本体上に形成された絶縁層と、

該絶縁層上に形成された導電層と、

該導電層上に形成されると共に前記バンプに接続された導電パターンとを有し、

前記突起部の先端面と前記導電層の上面とが面一とされていることを特徴とするものである。

【0019】

また、請求項7記載の発明は、

電極パッドが形成された半導体チップと、

前記電極パッド上に形成された、突起部を有するバンプと、

前記半導体チップ上に形成された絶縁層と、

該絶縁層上に形成された導電層と、

該導電層上に形成されると共に前記バンプに接続された導電パターンとを有する半導体装置であって、

10

20

30

40

50

前記突起部の先端面と前記導電層の上面とが面一とされていることを特徴とするものである。

【発明の効果】

【0020】

本発明によれば、絶縁層の上面及び突起部の露出部分の上部に導電層を形成し、その突起部と対向した突出部分を機械加工により除去することにより突起部を導電層から露出させるため、各突起部の基板本体からの高さは均一となると共に導電層の上面と面一の状態となる。よって、従来必要とされたレベリング処理が不要になると共に、バンプの突起部を絶縁層から露出させるための研磨工程も不要となり、製造工程の簡単化及び製造コストの低減を図ることができる。

10

【0021】

また、導電層の突起部と対向した突出部分を機械加工により除去した時点で各突起部先端は導電層の上面と面一の状態となる。このため、第4の工程を実施した後に、直ちに導電パターンを形成することが可能となり、これによっても製造工程の簡単化を図ることができる。

【発明を実施するための最良の形態】

【0022】

次に、本発明を実施するための最良の形態について図面と共に説明する。

【0023】

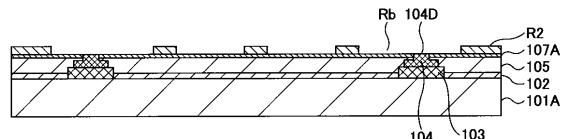

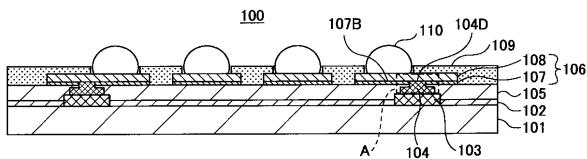

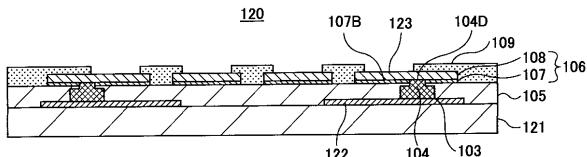

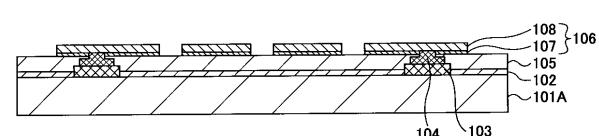

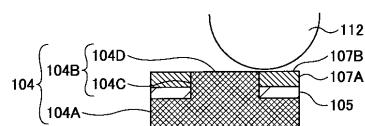

図1Aは、本発明の一実施例である半導体装置100を示す断面図である。図1Aを参考するに、本実施例による半導体装置100の概略は、電極パッド103が形成された半導体チップ101の保護層(パッセーション層)102上に、絶縁層105と導電パターン106が積層されて形成された構造となっている。

20

【0024】

この場合、上記の導電パターン106はいわゆる再配線と呼ばれる場合があり、半導体チップ101のパッケージング用いられるものである。絶縁層105は、例えばエポキシ系の樹脂より構成される。導電パターン106は、例えば、ともにCuよりなる第1の導電パターン107と第2の導電パターン108が積層された構成とされている。

【0025】

絶縁層105上に形成された導電パターン106は、電極パッド103上に形成された、例えばAuよりなるバンプ104の突起部(後述)に接続されている。すなわち、導電パターン106は、バンプ104を介して半導体チップ101の電子回路に接続される。バンプ104は、例えばワイヤボンディング装置を用いて、ボンディングワイヤにより形成される。

30

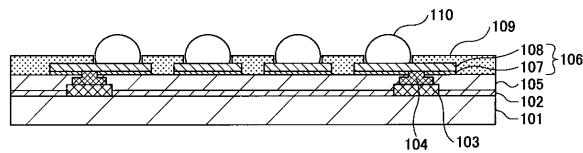

【0026】

また、導電パターン106上には、はんだバンプ110が形成されている。また、はんだバンプ110の周囲には、絶縁層105と導電パターン106の一部を覆うようにソルダーレジスト層(絶縁層)109が形成されている。

【0027】

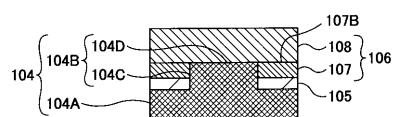

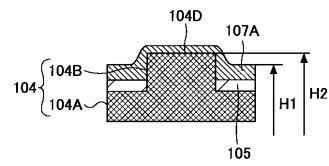

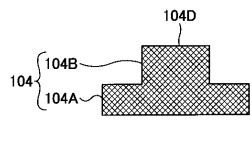

図1Bは、上記の半導体装置100のA部(バンプ104付近)を拡大して示している。同図に示すように、バンプ104は、電極パッド103と接続(接合)されるバンプ本体104Aと、このバンプ本体104Aから突出する突起部104Bにより構成されている。

40

【0028】

この上記のバンプ104は、ワイヤボンディング装置を用いて、例えばAuよりなるボンディングワイヤにより形成される。前記ワイヤボンディング装置は、ボンディングワイヤの電極パッド103への接合と、当該接合後のボンディングワイヤの切断を連続的に行うことで、バンプ104に接合されるバンプ本体104Aと、バンプ本体104Aから突出する突起部104Bを形成する。

【0029】

50

本実施例による半導体装置 100においては、上記の突起部 104B は、突起部 104B の先端に形成される扁平した先端部 104D と、この先端部 104D とバンプ本体 104Aとの間の接続部 104C よりなるように形成されている。本実施例による半導体装置 100 では、上記の突起部 104B が導電パターン 106 に挿入された構造とされるとともに、挿入された突起部 104B の先端部 104D が第 1 の導電パターン 107 の上面 107B と面一（同一平面）となっていることを特徴としている。

#### 【0030】

この構成とすることにより、第 1 の導電パターン 107 及び先端部 104D の上部に形成される第 2 の導電パターン 108 を段差のない均一でかつ平坦な導電層とすることができる。これにより、第 2 の導電パターン 108 の電気的特性の安定化を図ることができると共に、これに形成されるはんだバンプ 110 高さの均一化を図ることができる。また、突起部 104B の先端部 104D が第 1 の導電パターン 107 の上面 107B と面一（同一平面）となることにより、微細配線化が可能となる。10

#### 【0031】

一方、図 2 は、本発明の一実施例である回路基板 120 を示している。尚、図 2 において、図 1A, 1B に示した構成と対応する構成については同一符号を付すと共にその説明の一部を省略する。

#### 【0032】

本実施例による回路基板 120 の概略は、表面電極 122 が形成されたガラス基板 121 上に、絶縁層 105 と導電パターン 106 が積層されて形成された構造となっている。20

また、ガラス基板 121 の上面に形成された上面電極 122 上の所定位置にはバンプ 104 が形成されている。

#### 【0033】

本実施例においても絶縁層 105 はエポキシ系等の樹脂より構成され、また導電パターン 106 は Cu よりなる第 1 の導電パターン 107 と第 2 の導電パターン 108 とが積層された構成とされている。

#### 【0034】

絶縁層 105 上に形成された導電パターン 106 は、表面電極 122 上に形成されたバンプ 104 の先端部 104D に接続されている。すなわち、導電パターン 106 は、バンプ 104 を介して上面電極 122 に接続される。また、絶縁層 105 と導電パターン 106 の上部にはソルダーレジスト層（絶縁層）109 が形成されており、その所定箇所は開口されて導電パターン 106 が露出し、外部電極 123 が形成されている。30

#### 【0035】

本実施例による回路基板 120 においても、突起部 104B の先端部 104D と第 1 の導電パターン 107 の上面 107B とが面一（同一平面）となるよう構成されている。この構成とすることにより、第 1 の導電パターン 107 及び先端部 104D の上部に形成される第 2 の導電パターン 108 を凹凸のない平滑なパターンとすることができます、電気的特性の安定化を図ることができる。

#### 【0036】

尚、上記した各実施例では第 1 の導電パターン 107 及び第 2 の導電パターン 108 をいずれも Cu により形成した例を示したが、Cu 以外の材料により構成することも可能である。また、第 1 の導電パターン 107 と第 2 の導電パターン 108 とを異なる金属材料（合金材料）よりなる構成とし、導電パターン 106 を異なる材料の積層構造としてもよい。40

#### 【0037】

次に、本発明の一実施例である電子装置の製造方法について、図 3A ~ 図 3M 及び図 4A ~ 図 4D を用いて説明する。

#### 【0038】

尚、以下の説明においては、電子装置として図 1A に示した半導体装置 100 を例に挙げ、この半導体装置 100 の製造方法について説明するものとする。また、以下の説明に50

用いる図3A～図3M及び図4A～図4Dにおいて、先の説明に用いた図1A、図1B、図2に示した構成と対応する構成については同一符号を付し、その説明を一部省略するものとする。

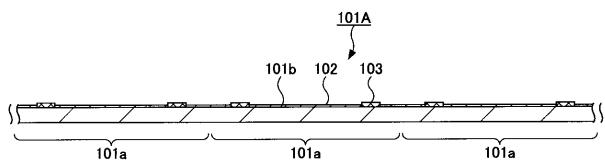

#### 【0039】

半導体装置100を製造するには、先ず図3Aに示す工程において、公知の方法を用いて、電子回路が形成された領域101aを複数（例えば格子状に）有する半導体基板101A（ウエハー等。以下、単に基板101Aという）を製造する。

#### 【0040】

上記の領域101aは、1個の半導体チップ101に相当する領域である。この領域101aの電子回路が形成されたデバイス形成面101bには、電極パッド103が形成されている。また、デバイス形成面101bの電極パッド103以外の部分には、例えばSiN(Si<sub>3</sub>N<sub>4</sub>)よりなる保護層（パッシベーション層）102が形成され、これによりデバイス形成面101bの保護が図られている。10

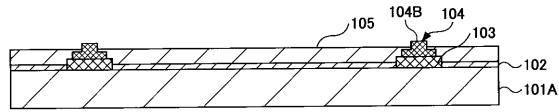

#### 【0041】

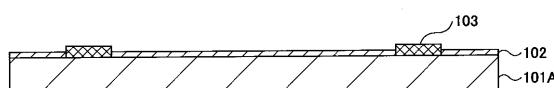

図3Bは、図3Aに示す基板101Aの1つの領域101aを拡大して示している。尚、図3B以下の図については、図示及び説明の便宜上、この1つの領域101aを拡大して示すものとする。

#### 【0042】

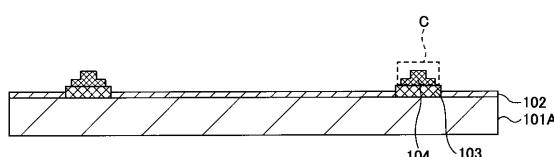

図3Cに示す工程では、電極パッド103上に、例えばワイヤボンディング装置を用いてバンプ104を形成する。このバンプ104は、Auよりなるボンディングワイヤにより形成される。20

#### 【0043】

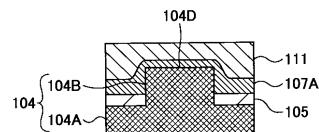

図4Aは、図3CのC部（バンプ104）を拡大して示している。上記のワイヤボンディング装置は、ボンディングワイヤの電極パッド103への接合と、当該接合後のボンディングワイヤの切断を連続的に行うことで、電極パッド103に接合されるバンプ本体104Aと、バンプ本体104Aから突出する突起部104Bを形成する。

#### 【0044】

次に、図3Dに示す工程において、基板101A上（保護層102上）に、例えばエポキシ系の樹脂材料よりなる絶縁層105を形成する。絶縁層105は、例えばラミネート（貼り付け）により、または塗布により形成される。この際、絶縁層105の上面からバンプ104の突起部104Bが露出するよう、絶縁層105は形成される。30

#### 【0045】

このため、上記の絶縁層105は、例えばNCFと呼ばれる、フィラーなどの硬度調整材料が殆ど添加されていない柔らかい樹脂材料が用いられることが好ましい。上記の柔らかい樹脂材料を用いることで、絶縁層105から突起部104Bを確実に露出させることができる。また、絶縁層105の厚さも、絶縁層105の形成時に突起部104Bが確実に絶縁層105の上面から突出するよう選定されている。

#### 【0046】

尚、絶縁層105は上記の材料に限定されず、様々な絶縁材料（樹脂材料）を用いて形成することが可能である。例えば、絶縁層105として、いわゆる通常用いられるビルドアップ樹脂（フィラー入りのエポキシ樹脂）や、ACFと呼ばれる樹脂材料を用いてもよい。

#### 【0047】

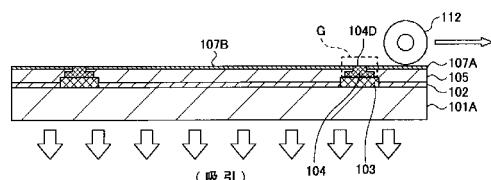

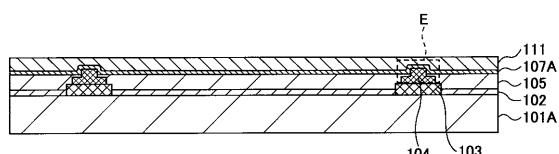

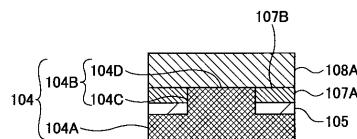

次に、図3Eに示す工程において、絶縁層105上に、例えば薄い銅箔よりなる導電層107Aを貼り付ける。この導電層107Aは、例えばCuよりなる支持層111と積層された状態で（導電層107Aが支持層111で支持された状態で）絶縁層105に貼り付けられる。

#### 【0048】

図4Bは、図3EのE部（バンプ104付近）を拡大して示している。同図に示すように、本工程において導電層107Aは、バンプ104によって押し上げられることにより40

支持層 111 側に盛り上がった状態となる。

【0049】

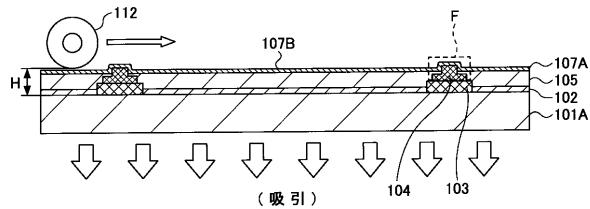

次に、導電層 107A を支持していた支持層 111 を除去する。図 3F は支持層 111 が除去された状態を示している。また、図 4C は図 3F の F 部（バンプ 104 付近）を拡大して示している。支持層 111 を除去することにより、絶縁層 105 の上部には導電層 107A のみが形成された状態となる。この際、導電層 107A のバンプ 104 と対向していない位置（非対向位置）は平坦面とされているが、バンプ 104 と対向する位置（対向位置）では前記のように絶縁層 105 はバンプ 104 により押し上げられて盛り上がった状態となっている。

【0050】

また、図 4C に示される矢印 H1 は、基板 101A の上面から導電層 107A の非対向位置における上面までの高さを示している。また、同図に示される矢印 H2 は、基板 101A の上面からバンプ 104 の先端部 104D までの高さを示している。本実施例では、この各高さ H1, H2 が、 $H1 < H2$  となるよう構成されている。

【0051】

上記のように支持層 111 が除去されると、基板 101A の上面に対して機械加工である研削処理が行われる。図 3F は、基板 101A が研削装置に装着された状態を示している。この装着状態で、基板 101A は図示しない吸着テーブルに吸引されることにより固定される。続いて、研削ロール 112 を用い、この研削ロール 112 を図中矢印方向に移動することにより研削処理が実施される。

【0052】

研削ロール 112 は砥粒を焼き固めたものであり、これを回転させながら移動させることにより、被加工物の表面に対して研削処理を行うことができる。本実施例では、この研削ロール 112 の研削が行われる位置（研削位置という）の基板 101A の上面からの高さ（これを H とする）は、導電層 107A の非対向位置における基板 101A の上面から上面 107B までの高さ H1（以下、上面高さ H1 という）と等しいかそれより若干高く、かつバンプ 104 の先端部 104D の基板 101A の上面からの高さ H2（以下、突起高さ H2 という）よりは低い高さに設定されている（ $H1 = H < H2$ ）。

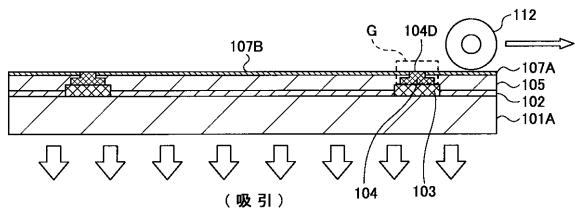

【0053】

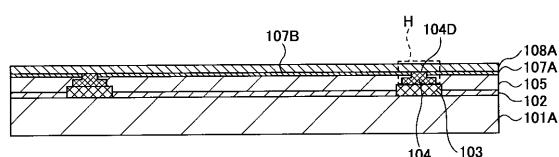

このように研削ロール 112 の研削位置を設定し、この研削ロール 112 を図 3F に示す位置から図 3G に示す位置まで移動させることにより、導電層 107A のバンプ 104（突起部 104B）と対向することにより盛り上がった部分は、研削ロール 112 により切削される。

【0054】

この際、前記のように研削位置 H は上面高さ H1 よりも高く突起高さ H2 より低いため（ $H1 = H < H2$ ）、導電層 107A の上面 107B に対しては殆ど研削処理は行われない。これに対し、導電層 107A の上面 107B よりも盛り上がった対向位置においては、導電層 107A 及び突起部 104B が研削ロール 112 により研削される（除去される）。

【0055】

図 3G は、上記のように研削ロール 112 による研削処理が行われた状態を示している。また図 4D は、図 3G の G 部（バンプ 104 付近）を拡大して示している。各図に示すように、上記した条件で研削ロール 112 で研削加工を行うことにより、対向位置における導電層 107A 及びバンプ 104 の先端部 104D は研削処理により除去される。これにより、バンプ 104 の先端部 104D は導電層 107A から露出し、かつ、その露出した先端部 104D と導電層 107A の上面 107B とは凹凸のない面一な面となる。

【0056】

先に説明した図 3C の固定で基板 101A には複数のバンプ 104 が形成されるが、研削位置 H が一定とされた研削ロール 112 により全てのバンプ 104 に対して切削処理が実施されるため、各バンプ 104 の先端部 104D の突起高さ H2（基板 101A の上面

10

20

30

40

50

からの高さ)は全て等しくなる。このように本実施例では、従来行われていたレベリング処理を実施することなく、全てのバンプ104の突起高さH2を等しくすることができる。

#### 【0057】

ワイヤボンディング法(ボンディングワイヤ)を用いて形成されるバンプ104は、生産性は高いが比較的高さのばらつきの大きいことが知られている。このようなバンプ104であっても、本実施例に係る製造方法を用いることにより、簡単な工程で容易にバンプ104の突起高さH2を等しくすることができ、製造される半導体装置100の信頼性を高めることができる。尚、導電層107Aは、後述する電解メッキの工程において、給電層(シード層)として用いられる。

10

#### 【0058】

次に、図3H～図3Jに示す工程において、導電層107Aを給電層(シード層)とした電解メッキにより、バンプ104に接続される導電パターン106を形成する。

#### 【0059】

この導電パターン106を形成する方法としては、例えば、いわゆるサブトラクティブ法と、セミアディティブ法があるが、本実施例ではサブトラクティブ法を用いた例について説明する。

#### 【0060】

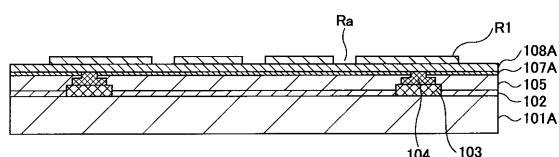

先ず、図3Hに示す工程において、導電層107Aを給電層とした電解メッキにより、導電層107A及び先端部104D上に、例えばCuよりなる導電層108Aを積層する。前記のように先端部104Dは導電層107Aの上面107Bと面一であるため、ここで形成されたる導電層108Aは凹凸のない平坦な良好な層となる。尚、図4Eは、図3HのH部(バンプ104付近)を拡大して示している。

20

#### 【0061】

次に、図3Iに示す工程において、導電層108A上に開口部Raを有するマスクパターンR1を形成する。マスクパターンR1は、塗布またはフィルムの貼り付けによるレジスト層の形成と、該レジスト層のフォトリソグラフィ法を用いたパターニングにより、形成することができる。

#### 【0062】

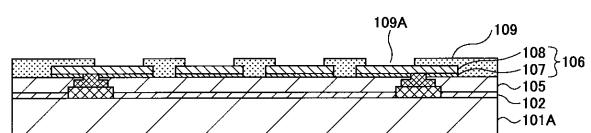

次に、図3Jに示す工程において、マスクパターンR1をマスクにした、導電層107A, 108Aのパターンエッチングを行うことにより、第1の導電層107と第2の導電層108が積層され、かつバンプ104に接続された導電パターン106が形成される。

30

#### 【0063】

例えば、上記の第1の導電パターン107は厚さが2～3μm、第2の導電パターン108は厚さが30～40μm程度に形成されるが、上記の数値は一例であり、本発明はこれらの数値に限定されるものではない。

#### 【0064】

上記の導電パターン106を形成するにあたっては、上記の導電層107Aを給電層とすることで電解メッキを用いることが容易となっている。例えば、給電層(シード層)を無電解メッキにより形成する場合には、絶縁層の表面を荒らす処理(いわゆるデスマニア処理)が必要になり、メッキ層を形成するための処理が複雑になってしまう。また、スパッタリング法で給電層を形成する場合には、真空処理容器を有する高価な成膜装置が必要となるため、製造コストのアップにつながってしまう。

40

#### 【0065】

これに対して本実施例による方法では、デスマニア処理や真空室でのスパッタリング処理が不要となり、単純な方法で容易に給電層(導電層107A)を形成することが可能となる。このため、上記の方法によれば半導体装置を製造する方法が単純となり製造コストが抑制される。

#### 【0066】

次に、図3Kに示す工程において、必要に応じて、導電パターン106(Cu)の表面

50

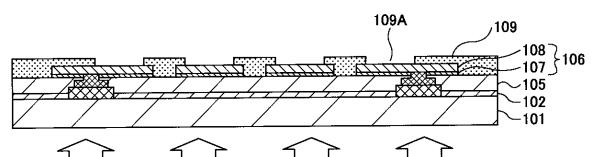

の粗化処理を施した後、絶縁層 105 上に、開口部 109A を有するソルダーレジスト層（絶縁層）109を形成する。開口部 109A からは、導電パターン 106 の一部が露出するようとする。

#### 【0067】

次に、図 3 L に示す工程において、必要に応じて基板 101A の裏面研削を行い、基板 101A を所定の厚さとする。

#### 【0068】

次に、図 3 M に示す工程において、必要に応じて開口部 109A から露出する導電パターン 106 上にはんだバンプ 110 を形成する。さらに、基板 101A のダイシングを行って半導体チップを個片化し、これにより図 1 A に示した半導体装置 100 を製造することができる。

10

#### 【0069】

ところで、上記の製造方法では、導電パターン 106 をサブトラクティブ法により形成しているが、導電パターン 106 をセミアディティブ法を用いて形成してもよい。この場合、例えば、上記の製造方法において図 3 A ~ 図 3 G に示した工程を実施した後、図 3 H ~ 図 3 J の工程に換えて、以下に説明する工程を実施すればよい。

#### 【0070】

即ち、図 5 に示すように、導電層 107A 上に開口部 Rb を有するマスクパターン R2 を形成する。このマスクパターン R2 は、塗布またはフィルムの貼り付けによるレジスト層の形成と、該レジスト層のフォトリソグラフィ法を用いたパターニングにより形成することができる。

20

#### 【0071】

次に、導電層 107A を給電層（シード層）とする電解メッキを実施し、開口部 Rb から露出する導電層 107A 上に第 2 の導電パターンを形成する。その後、マスクパターン R2 を剥離し、更にマスクパターン R2 を剥離することで露出する余剰な給電層 107A をエッティングにより除去し、これにより図 3 J に示す導電パターン 106 を形成することができる。

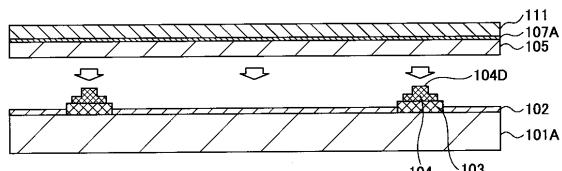

#### 【0072】

また、上記の製造方法では、図 3 D ~ 図 3 E の工程において、基板 101A 上に絶縁層 105 を形成した後、絶縁層 105 上に導電層 107A を貼り付けているが、予め絶縁層 105 と導電層 107A を積層したものを基板 101A に貼り付けてもよい。

30

#### 【0073】

この場合、例えば、上記の製造方法において図 3 A ~ 図 3 C に示した工程を実施した後、図 3 D ~ 図 3 E の工程に換えて、以下に説明する工程を実施すればよい。

#### 【0074】

即ち、図 6 に示すように、支持層 111 に積層された絶縁層 105 と導電層 107A を基板 101A に貼り付けてもよい。この後、先に説明した図 3 F 以下の工程を実施することで、半導体装置 100 を形成することができる。

#### 【0075】

以上、本発明を好ましい実施例について説明したが、本発明は上記の特定の実施例に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。具体的には、基板 101A として半導体基板に代えてガラス基板や多層配線基板を用いることも可能であり、よってこれらの基板を用いる各種電子装置への定期用が可能となる。

40

#### 【図面の簡単な説明】

#### 【0076】

【図 1 A】図 1 A は、本発明の一実施例である半導体装置を示す断面図である。

【図 1 B】図 1 B は、図 1 A におけるバンプ近傍を拡大して示す断面図である。

【図 2】図 2 は、本発明の一実施例である回路基板を示す断面図である。

【図 3 A】図 3 A は、本発明の一実施例である半導体装置の製造方法を説明する断面図（

50

その 1 ) である。

【図 3 B】図 3 B は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 2 )である。

【図 3 C】図 3 C は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 3 )である。

【図 3 D】図 3 D は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 4 )である。

【図 3 E】図 3 E は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 5 )である。

【図 3 F】図 3 F は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 6 )である。 10

【図 3 G】図 3 G は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 7 )である。

【図 3 H】図 3 H は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 8 )である。

【図 3 I】図 3 I は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 9 )である。

【図 3 J】図 3 J は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 10 )である。

【図 3 K】図 3 K は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 11 )である。 20

【図 3 L】図 3 L は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 12 )である。

【図 3 M】図 3 M は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 13 )である。

【図 4 A】図 4 A は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 14 )である。

【図 4 B】図 4 B A は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 15 )である。

【図 4 C】図 4 C A は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 16 )である。 30

【図 4 D】図 4 D は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 17 )である。

【図 4 E】図 4 E は、本発明の一実施例である半導体装置の製造方法を説明する断面図(その 18 )である。

【図 5】図 5 は、本発明の一実施例である半導体装置の製造方法の変形例を説明するための断面図(その 1 )である。

【図 6】図 6 は、本発明の一実施例である半導体装置の製造方法の変形例を説明するための断面図(その 2 )である。

#### 【符号の説明】

##### 【0 0 7 7】

1 0 0 半導体装置

1 0 1 半導体チップ

1 0 1 A 基板

1 0 1 a 領域

1 0 1 b デバイス面

1 0 2 保護層

1 0 3 電極パッド

1 0 4 バンプ

1 0 4 A バンプ本体

40

50

1 0 4 B 突起部

1 0 4 C 接続部

1 0 4 D 先端部

1 0 5 絶縁層

1 0 6 導電パターン

1 0 7 第1の導電パターン

1 0 7 A 導電層

1 0 8 第2の導電パターン

1 0 8 A 導電層

1 0 9 ソルダーレジスト層

1 1 0 はんだバンプ

10

【図1A】

本発明の一実施例である半導体装置を示す断面図

【図1B】

図1Aにおけるバンプ近傍を拡大して示す断面図

【図2】

本発明の一実施例である回路基板を示す断面図

【図3A】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その1)

【図3B】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その2)

【図3C】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その3)

【図3D】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その4)

【図3E】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その5)

【図3F】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その6)

【図3G】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その7)

【図3H】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その9)

【図3I】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その9)

【図3K】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その11)

【図3L】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その12)

【図3J】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その10)

【図3M】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その13)

【図4C】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その16)

【図4A】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その14)

【図4D】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その17)

【図4B】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その15)

【図4E】

本発明の一実施例である半導体装置の製造方法を説明する断面図(その18)

【図6】

本発明の一実施例である

半導体装置の製造方法の変形例を説明するための断面図(その2)

【図5】

本発明の一実施例である

半導体装置の製造方法の変形例を説明するための断面図(その1)