(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4613562号

(P4613562)

(45) 発行日 平成23年1月19日(2011.1.19)

(24) 登録日 平成22年10月29日(2010.10.29)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| G02F 1/1368 (2006.01) | GO2F 1/1368    |

| G02F 1/133 (2006.01)  | GO2F 1/133 550 |

| G02F 1/1333 (2006.01) | GO2F 1/1333    |

| G09F 9/00 (2006.01)   | GO9F 9/00 366G |

| G09F 9/30 (2006.01)   | GO9F 9/30 338  |

請求項の数 3 (全 10 頁)

(21) 出願番号 特願2004-279908 (P2004-279908)

(22) 出願日 平成16年9月27日 (2004.9.27)

(65) 公開番号 特開2006-91708 (P2006-91708A)

(43) 公開日 平成18年4月6日 (2006.4.6)

審査請求日 平成19年8月13日 (2007.8.13)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094363

弁理士 山本 幸久

(74) 代理人 100118290

弁理士 吉井 正明

(74) 代理人 100120640

弁理士 森 幸一

(72) 発明者 中村 和夫

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 内野 勝秀

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表示回路と受光回路とを有する画素がマトリクス状に配されており、

表示回路は、

液晶素子とサンプリングトランジスタとを含み、

サンプリングトランジスタは、主電極端の一方が表示用信号線に接続されており、主電

極端の他方が液晶素子の一方の電極に接続されており、制御電極端が表示用走査線に接続

されており、表示用走査線により選択されたとき表示用信号線から入力された映像信号に

応じて液晶素子を駆動し、以ってマトリクス状の画素に映像を表示し、

受光回路は、薄膜トランジスタで構成された受光素子と、逆バイアス状態の薄膜トラン

ジスタに入射する光量に応じて薄膜トランジスタに流れる光リーク電流を増幅して受光信

号電流を生成する増幅部と、表示回路が動作していないときに選択され光リーク電流を増

幅部に取り入れる入力スイッチと、表示回路が動作していないときに選択され受光信号電

流を増幅部から出力用信号線に読み出す出力スイッチとを含むアクティブマトリクス型液

晶表示装置。

## 【請求項 2】

増幅部は、カレントミラー回路を構成する一対の入力トランジスタと出力トランジスタ

とを含み、入力トランジスタと出力トランジスタのサイズ比に応じて光リーク電流を増幅

した値が出力用信号線に流れる受光信号電流の値となる請求項 1 に記載のアクティブマト

リクス型液晶表示装置。

**【請求項 3】**

受光回路は、表示回路が動作している間は入力スイッチ及び出力スイッチとともにオフし、表示回路が動作しなくなったとき、先ず入力スイッチをオンして入力トランジスタに対する光リーク電流の供給を開始し、入力トランジスタの制御電極容量への充電が完了したとき出力スイッチをオンする請求項2に記載のアクティブマトリクス型液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はアクティブマトリクス型の液晶表示装置に関する。より詳しくは、各画素ごとに配された表示回路に加え、情報入力用の受光回路を各画素に備えたアクティブマトリクス型液晶表示装置の画素回路構成に関する。

10

**【背景技術】****【0002】**

アクティブマトリクス型の液晶表示装置は低消費電力であり小型化が可能である。これらの特徴から、アクティブマトリクス型の液晶表示装置（LCD）は従来の典型的なディスプレイであるCRTを凌駕しつつあり、多方面のディスプレイに用いられている。特に近年では、通信環境の発達などにより、低消費電力及び小型などの特長を生かしてLCDはモバイル端末のディスプレイとして広く普及している。

**【発明の開示】****【発明が解決しようとする課題】**

20

**【0003】**

モバイル機器ではディスプレイなどの出力機器デバイスの他入力デバイスも必要である。入力デバイスとしては従来から抵抗薄膜型のタッチパネルが使われている。しかしながら、タッチパネルは接触点における電位変化を検出する方式のため、2箇所以上の接触点を同時に検出することは原理的に不可能である。このため、タッチパネルはゲーム用途などに対応しきれない場合がある。またディスプレイデバイスの表示面上にタッチパネルを設置するため必然的に機器の厚さの増加及びディスプレイの輝度低下を招く問題がある。

**【0004】**

また近年では、入力デバイスとしてCCDカメラあるいはCMOSカメラが付属している携帯電話機が広く普及している。さらには、個人認証用に指紋センサーを内蔵する携帯電話機も登場している。しかしながら、これら入力デバイスとしてのセンサーは画像表示部とは一体になっていないため、機器の実装密度の増加を招くという課題があった。

30

**【課題を解決するための手段】****【0005】**

上述した従来の技術の課題に鑑み、本発明はアクティブマトリクス型液晶表示装置に対し出力デバイスとしての機能に加え入力デバイスとしての機能を付加することで、応用機器の一層の小型化を達成することを目的とする。かかる目的を達成するために以下の手段を講じた。即ち本発明にかかるアクティブマトリクス型液晶表示装置は、走査線の列と、信号線の列と、各走査線と各信号線が交差する部分にマトリクス状に配された画素とを備え、各画素は、液晶素子と、薄膜トランジスタで構成された表示回路と、同じく薄膜トランジスタで構成された受光回路とを含み、前記表示回路は、該走査線により選択された時該信号線から入力された映像信号に応じて該液晶素子を駆動し、以ってマトリクス状の画素に映像を表示し、前記受光回路は、該表示回路が動作していないときに選択され、画素に入射する光量に応じた受光信号を別の信号線に出力することを特徴とする。

40

**【0006】**

好ましくは、前記受光回路は、該画素に形成された受光素子に入射する光量を検出して、対応する受光信号を出力する。又前記受光回路は、受光素子として薄膜トランジスタを用い、該薄膜トランジスタを逆バイアスの状態にセットするセット部と、逆バイアスの状態下入射する光量に応じて該受光素子に流れる光リーク電流を增幅して受光信号を生成する増幅部とを含む。又、前記受光回路は、入射する光量に応じて該受光素子に流れる光リ

50

ーク電流を該増幅部に取り入れる入力スイッチと、取り入れた光リーク電流を増幅して得られた受光信号を該増幅部から信号線に読み出す出力スイッチとを含み、該入力スイッチと出力スイッチは互いに独立したタイミングでオンオフ制御する。この場合、前記受光回路は、該表示回路が動作している間該入力スイッチ及び出力スイッチをともにオフし、該表示回路が動作しなくなった時先ず該入力スイッチをオンして該増幅部に対する光リーク電流の供給を開始し、次に該光リーク電流の供給が安定した時点で該出力スイッチをオンする。一態様では、前記液晶素子は、光反射型である。他の態様では、前記液晶素子は、光透過型である。好ましくは、前記薄膜トランジスタは、多結晶シリコン薄膜を活性層とする。或いは、前記薄膜トランジスタは、非晶質シリコン薄膜を活性層としても良い。

## 【発明の効果】

10

## 【0007】

本発明によれば、アクティブマトリクス型液晶表示装置の各画素内に表示回路と受光回路を薄膜トランジスタなどで集積形成している。表示回路は映像信号に応じて液晶素子を駆動することで、画像表示出力が可能になる。一方受光回路は、薄膜トランジスタに逆バイアス電圧を印加した状態で入射光量に応じた光リーク電流を流し、さらにこれを増幅することにより、画像情報の入力を可能にしている。本発明による液晶表示装置は、タッチパネルなどを用いなくとも光学的に座標位置検出が可能で、且つ2箇所以上の同時座標検出も原理的に可能である。また、座標検出用としてディスプレイ上に別途位置検出装置を設置する必要がないため、高輝度な画像表示を得ることができる。また、座標検出以外の応用として、画素単位の光検出に基づいたスキャナを実現できる。これにより、付加価値の高い液晶表示装置を提供することが可能である。特に本発明では、受光回路が受光電流制御と增幅出力制御を各々独立に行うことで、受光感度を改善している。なお、本発明は画素に液晶素子を用いているが、これに代えて有機EL素子などの自発光素子を用いたアクティブマトリクス型表示装置にも応用可能である。

20

## 【発明を実施するための最良の形態】

## 【0008】

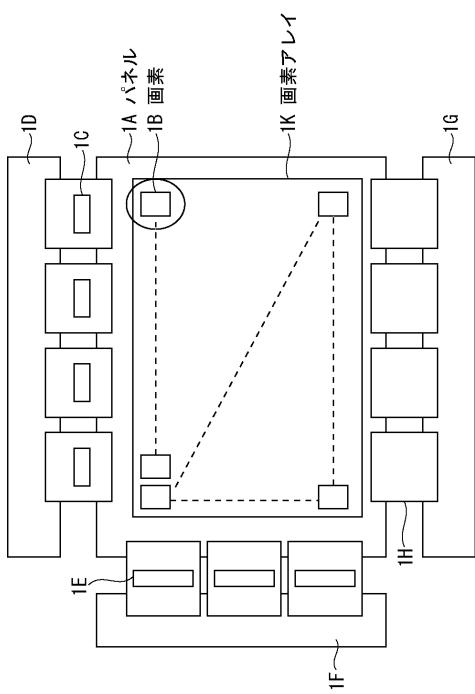

以下図面を参照して本発明の実施の形態を詳細に説明する。図1は本発明にかかるアクティブマトリクス型液晶表示装置の構成を示す模式的な全体平面図である。図示するように、本液晶表示装置はパネル1Aとこれを駆動する周辺の回路とで構成されている。パネル1Aは画素1Bをマトリクス状に集積形成した画素アレイ1Kを備えている。これを周辺から囲むように配された回路群は、映像信号線駆動用集積回路1C、映像信号制御回路1D、走査線駆動集積回路1E、走査線制御回路1F、受光信号処理基板1G、受光信号伝達用フレキシブルケーブル1Hなどを含んでいる。本実施形態では、映像信号線駆動用集積回路1Cはフレキシブルケーブルに搭載されている。映像信号制御回路1Dはこの映像信号線駆動用集積回路1Cを搭載したフレキシブルケーブルを介してパネル1Aに接続されている。同様に走査線制御回路1Fは走査線駆動集積回路1Eを搭載したフレキシブルケーブルを介してパネル1Aに接続されている。

30

## 【0009】

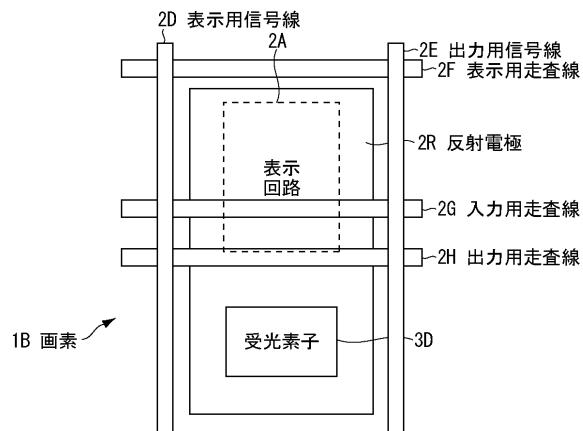

図2は、図1に示した画素1Bの構成を示す模式的な平面図である。図示するように、画素1Bは、走査線の列と信号線の列とが交差する部分に配されている。信号線は1画素当たり2本配されており、表示用信号線2Dと出力用信号線2Eがある。表示用信号線2Dは図1に示した映像信号線駆動用集積回路1Cに接続している。一方出力用信号線2Eは図1に示した受光信号処理基板1Gに接続されている。走査線の方は1画素当たり3本配されており、表示用走査線2F、入力用走査線2G、出力用走査線2Hがある。これらの走査線2F、2G、2Hは図1に示した走査線駆動集積回路1Eに接続されている。

40

## 【0010】

画素1Bは、液晶素子と、薄膜トランジスタで構成された表示回路2Aと、同じく薄膜トランジスタで構成された受光回路とを含んでいる。本実施形態は反射型であり、液晶素子は反射電極2Rとこれに対向する透明電極との間に挟まれた液晶で構成されている。表示回路2Aは、表示用走査線2Fにより選択されたとき表示用信号線2Dから入力された

50

映像信号に応じて液晶素子を駆動し、以ってマトリクス状の画素に映像を表示する。一方受光回路は、表示回路 2 A が動作していないときに選択され、画素 1 B に入射する光量に応じた受光信号を出力用信号線 2 E に出力する。

#### 【0011】

本実施形態では、受光回路は画素 1 B に形成された受光素子 3 D に入射する光量を検出して、対応する受光信号を出力する。本実施形態では受光素子 3 D として薄膜トランジスタを用いている。さらにこの薄膜トランジスタを逆バイアスの状態にセットするセット部と、逆バイアスの状態下入射する光量に応じて受光素子 3 D に流れる光リーク電流を増幅して受光信号を生成する増幅部とを含む。受光回路は、入射する光量に応じて受光素子 3 D に流れる光リーク電流を増幅部に取り入れる入力スイッチと、取り入れた光リーク電流を増幅して得られた受光信号を増幅部から出力用信号線 2 E に読み出す出力スイッチとを含む。入力スイッチと出力スイッチは互いに独立したタイミングでそれぞれ入力用走査線 2 G 及び出力用走査線 2 H によりオンオフ制御される。受光回路は、表示回路 2 A が動作しなくなったときまず入力スイッチをオンして増幅部に対する光リーク電流の供給を開始し、次に光リーク電流の供給が安定した時点で出力スイッチをオンする。なお、表示回路 2 A は反射電極 2 R の下部に配されている。一方受光素子 3 D は外部からの光を取り込むため、反射電極 2 R に形成された開口部と整合するように配されている。10

#### 【0012】

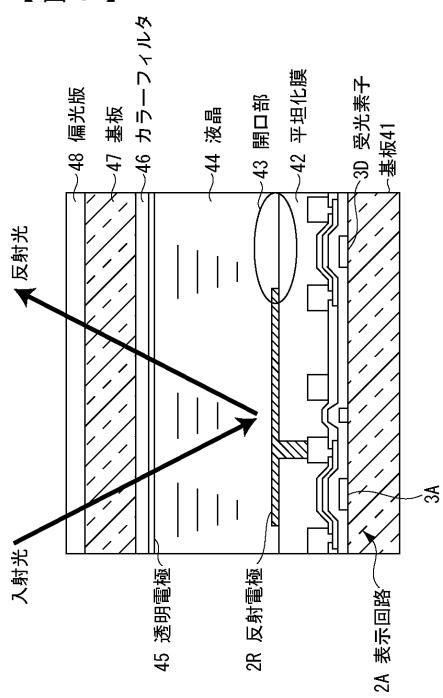

図 3 は、図 2 に示した画素 1 個分の液晶表示装置の断面構造を示す模式図である。図示するように、液晶表示装置は下側の基板 4 1 と上側の基板 4 7との間に液晶 4 4 を挟持したフラットパネル構成となっている。下側の基板 4 1 には表示回路 2 A や受光素子 3 D が形成されている。図示するように表示回路 2 A は薄膜トランジスタ 3 A などで構成されている。受光素子 3 D も同様に下側の基板 4 1 に形成された薄膜トランジスタからなる。これらの薄膜トランジスタは例えば多結晶シリコン薄膜を活性層としている。場合によっては多結晶シリコン薄膜にかえて非晶質シリコン薄膜を活性層としてもよい。薄膜トランジスタで構成された表示回路 2 A や受光素子 3 D は平坦化膜 4 2 で被覆されており、その上に反射電極 2 R が形成されている。この反射電極 2 R は平坦化膜 4 2 に形成されたコントクトホールを介して表示回路 2 A に接続している。一方受光素子 3 D の上方には反射電極 2 R を切り欠いて開口部 4 3 が形成されている。20

#### 【0013】

一方上側の基板 4 7 の内面にはカラーフィルタ 4 6 や透明電極 4 5 が形成されており、外面には偏光板 4 8 が形成されている。上側の基板 4 7 に配された透明電極 4 5 と下側の基板 4 1 に配された反射電極 2 Rとの間に液晶 4 4 が保持されており、画素単位で光反射型の液晶素子を構成している。この液晶素子は表示回路 2 A から反射電極 2 R に書き込まれる映像信号のレベルに応じて、液晶 4 4 の透過率を変調する。これにより画素単位で反射光量を変調し、以って画像を表示する。30

#### 【0014】

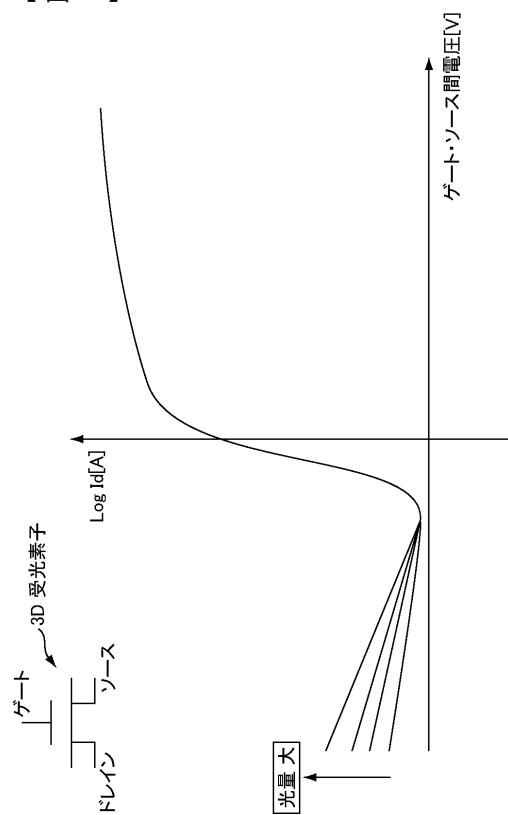

図 4 は、受光素子 3 D として用いる薄膜トランジスタの電流 - 電圧特性を示すグラフである。横軸に、ゲート・ソース間電圧を取り、縦軸にドレイン電流を対数で取ってある。ゲート・ソース間電圧が正の値を取る順バイアス状態では、薄膜トランジスタの閾値を超えた後ゲート・ソース間電圧に応じてドレイン電流  $I_d$  が流れる。一方ゲート・ソース間電圧が負の値を取る逆バイアス状態では、基本的にドレイン電流  $I_d$  は流れない。ただし、逆バイアス時には外部から入射した光の光励起により光リーク電流が流れる。この光リーク電流は外部から入射した光量が大きくなる程電流量が増大する。本発明は、この薄膜トランジスタの光励起によるドレイン電流の変化を利用して、光検出を行う。順バイアスにおけるドレイン電流に比べ、逆バイアスにおける光リーク電流は絶対量が少ない。そこで本発明は、光リーク電流を増幅して光検出を行っている。40

#### 【0015】

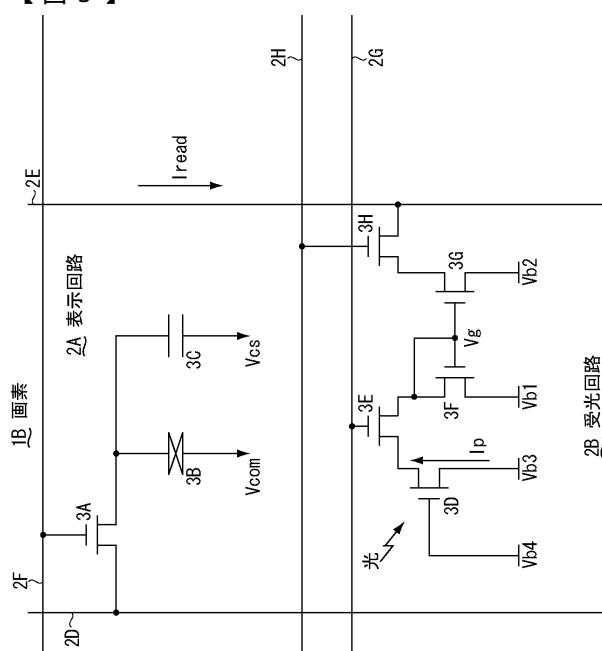

図 5 は、図 2 に示した画素の具体的な構成を示す回路図である。図示するように、画素 1 B は表示回路 2 A と受光回路 2 B とで構成されている。表示回路 2 A が表示用信号線 2

D と表示用走査線 2 F とが交差する部分に配されている。表示回路 2 A は基本的にサンプリングトランジスタ 3 A で構成されている。このサンプリングトランジスタ 3 A は N 型の薄膜トランジスタである。サンプリングトランジスタ 3 A のゲートは表示用走査線 2 F に接続され、ドレインは表示用信号線 2 D に接続されている。サンプリングトランジスタ 3 A のソースには、液晶素子 3 B と保持容量 3 C の一端が接続されている。液晶素子 3 B の他端は所定の電源電圧 V com に接続されている。また保持容量 3 C の他端は所定の電位 V cs に接続されている。図 3 を参照して説明したように、液晶素子 3 B はトランジスタ 3 A 側に接続した反射電極とこれに対向する透明電極と両者の間に保持された液晶層とで構成されている。

## 【0016】

10

一方受光回路 2 B は、出力用信号線 2 E と走査線 2 G, 2 H とが交差する部分に配されている。一方の走査線 2 G は入力用であり、他方の走査線 2 H は出力用である。入力用走査線 2 G は入力スイッチとなる入力トランジスタ 3 E のゲートに接続されている。一方出力用走査線 2 H は、出力スイッチとなるトランジスタ 3 H のゲートに接続されている。入力トランジスタ 3 E のドレインには受光素子となる受光トランジスタ 3 D のドレインが接続されている。受光トランジスタ 3 D のゲートには、逆バイアスゲート電圧源 V b 4 が接続されており、逆バイアスセット部を構成する。受光トランジスタ 3 D のソースには、受光電流生成用電圧源 V b 3 が接続されている。

## 【0017】

20

一対のトランジスタ 3 F 及び 3 G でカレントミラー回路を構成しており、増幅部となっている。受光トランジスタ 3 D により生成された光リーク電流 I p は、入力トランジスタ 3 E を介して、一方のトランジスタ 3 F のドレインとゲートに入力され、そのソースを介してバイアス電源 V b 1 に流れ込む。他方のトランジスタ 3 G のゲートは、トランジスタ 3 F のドレインとゲートに接続され、そのソースはバイアス電源 V b 2 に接続され、そのドレインは出力トランジスタ 3 H を介して出力用信号線 2 E に接続される。出力用信号線 2 E に流れる受光信号電流 I read はカレントミラー回路を構成するトランジスタ 3 F と 3 G のサイズ比に応じて光リーク電流 I p を増幅した値となる。

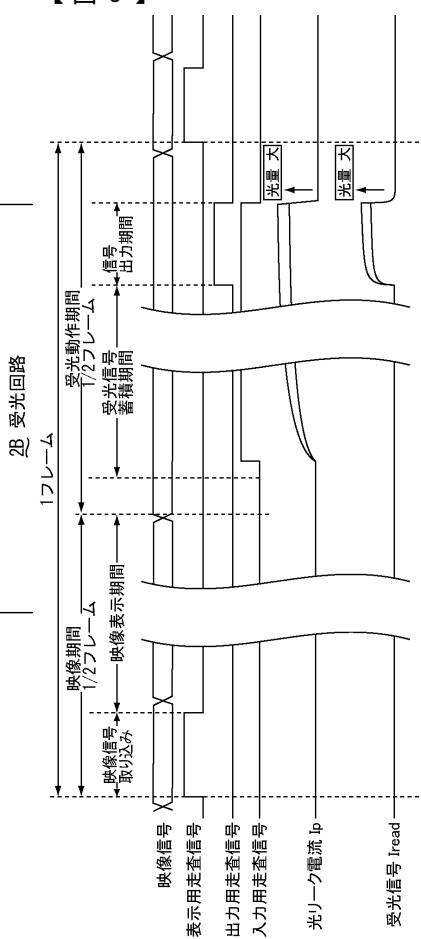

## 【0018】

図 6 は、図 5 に示した画素回路の動作説明に供するタイミングチャートである。本実施形態では、1 フレームの前半を表示動作期間（映像期間）とし、後半を受光動作期間として、時分割的な制御を行っている。タイミングチャートは、映像信号、表示用走査信号、出力用走査信号、入力用走査信号などの波形を表している。これと対応させて光リーク電流 I p 及び受光信号電流 I read の変化も表してある。なお映像信号は外部システムから入力用信号線 2 D に供給され、表示用走査信号は表示用走査線 2 F に供給され、出力用走査信号は出力用走査線 2 H に供給され、入力用走査信号は入力用走査線 2 G に供給される。

30

## 【0019】

40

まず表示動作であるが、表示用走査信号をハイレベルにして、サンプリングトランジスタ 3 A をオンする。これにより表示用信号線 2 D から供給された映像信号がサンプリングトランジスタ 3 A により取り込まれ、対応する液晶素子 3 B に書き込まれる。これにより、液晶素子 3 B は書き込まれた映像信号のレベルに応じて液晶層の透過率を変調し、所望の画像を表示する。サンプリングトランジスタ 3 A により取り込まれた映像信号は、保持容量 3 C にも保持される。これにより 1 フレームの 2 分の 1 に相当する映像表示期間中、安定して画像を表示することができる。

## 【0020】

50

後半の受光動作期間では、まず入力用走査信号をハイレベルにして光リーク電流 I p を入力トランジスタ 3 E を介してカレントミラー回路の一方のトランジスタ 3 F へと流し込む。このときトランジスタ 3 F のゲート電圧 V g は、光リーク電流 I p によりゲート容量が充電されることにより上昇する。そして、ゲートに対する充電が完了し I p が飽和した所で、出力用走査信号をハイレベルにする。これにより出力トランジスタ 3 H がオンし、

出力用信号線 2 E に受光信号 I read を流し込む。この期間では、入力トランジスタ 3 E と出力トランジスタ 3 H が共にオン状態であるため、受光信号 I read は、トランジスタ 3 F と 3 G により構成されるカレントミラー回路により、光リーク電流 I p を増幅した値となる。

#### 【 0 0 2 1 】

本発明では、受光期間中にカレントミラー回路の動作点を決定するため、常に光電流を流す構成となっており、受光感度が上昇する。またカレントミラー回路により光リーク電流をアナログ的に増幅するので、諧調表現も可能である。さらに、画素内で表示回路と受光回路が完全に分離されているので、実施形態で示した 1 フレームを均等に映像表示期間と受光検出期間に分離する方式だけでなく、例えば受光動作は垂直プランギング期間に行う構成も可能であり、タイミング上の制約も少ない。

10

#### 【 0 0 2 2 】

以上説明したように、本発明ではアクティブマトリクス型液晶表示装置の画素内に表示回路と受光回路を形成している。受光期間中に受光トランジスタのゲートに逆バイアスを印加することで光励起電流を生成することができる。更にこの光励起電流をカレントミラーレードで増幅することにより、映像表示と画像検出の両方が可能な表示装置を形成することができる。本発明の表示パネルでは、タッチパネル等を別途用いなくとも座標位置検出が可能で、且つ複数点の同時座標検出が可能である。また座標検出用に表示パネルに重ねて位置検出デバイスを設置する必要がないため、高輝度な画像を得ることができる。また座標位置検出以外にも、光検出を応用したスキャナをパネルに一体形成できるので、高付加価値を有する液晶表示装置を提供することができる。

20

#### 【 0 0 2 3 】

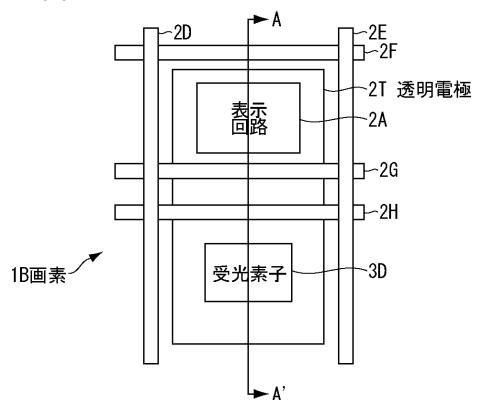

図 7 は、本発明にかかる液晶表示装置の他の実施形態を示す模式図であり、1 画素分の平面図となっている。理解を容易にするため、図 2 に示した先の実施形態と対応する部分には対応する参照番号を付してある。異なる点は、図 2 に示した先の実施形態が光反射型の液晶素子を組み込んでいるのに対し、本実施形態は光透過型の液晶素子を用いていることである。図示するように、画素 1 B は、信号線 2 D , 2 E と走査線 2 F , 2 G , 2 H とが交差する部分に配されており、表示回路 2 A と受光素子 3 D を含む受光回路とに分かれている。表示回路 2 A と受光素子 3 D を囲むように、液晶素子の透明電極 2 T が形成されている。

30

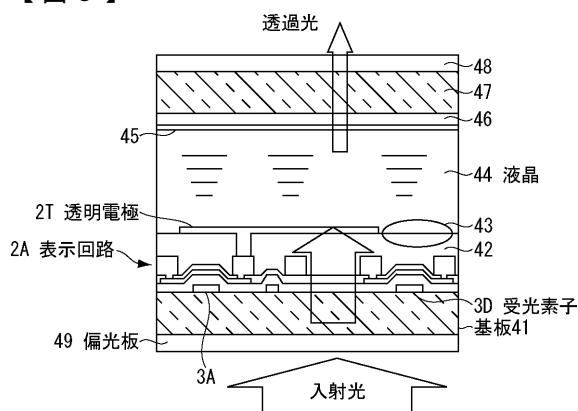

#### 【 0 0 2 4 】

図 8 は、図 7 に示した 1 画素分の液晶表示装置の A - A' 線に沿った断面構造を示している。図示するように、本液晶表示装置は、下側の基板 4 1 と上側の基板 4 7 と両者の間に保持された液晶 4 4 とで構成されている。下側の基板 4 1 の外面には偏光板 4 9 が配されている一方、内面には表示回路 2 A や受光素子 3 D が集積形成されている。表示回路 2 A や受光素子 3 D は平坦化膜 4 2 で被覆されており、その上に透明電極 2 T が形成されている。この透明電極 2 T は表示回路 2 A によって駆動される。

#### 【 0 0 2 5 】

上側の基板 4 7 の外面には偏光板 4 8 が配されている一方、内面にはカラーフィルタ 4 6 や透明電極 4 5 が形成されている。下側の基板 4 1 に配された透明電極 2 T と上側の基板 4 7 に配された透明電極 4 5 との間に保持された液晶 4 4 で透過型の液晶素子が構成されている。この液晶素子は表示回路 2 A を介して透明電極 2 T に印加される映像信号のレベルに応じて透過率が変化する。これに応じて下側の基板 4 1 から入射した光が変調され、透過光となって上側の基板 4 7 から出射される。一方、受光素子 3 D の上から透明電極 2 T が除かれており、外部から入射した光の検出を行うことができる。

40

#### 【 図面の簡単な説明 】

#### 【 0 0 2 6 】

【 図 1 】本発明にかかる液晶表示装置の全体構成を示すブロック図である。

【 図 2 】図 1 に示した液晶表示装置の 1 画素分を示す平面図である。

【 図 3 】同じく 1 画素分を示す断面図である。

50

【図4】本発明にかかる液晶表示装置に組み込まれる受光素子の電流電圧特性を示すグラフである。

【図5】本発明にかかる液晶表示装置に形成される画素回路の具体的な構成例を示す回路図である。

【図6】図5に示した画素回路の動作説明に供するタイミングチャートである。

【図7】本発明にかかる液晶表示装置の他の実施形態を示す模式的な平面図である。

【図8】同じく他の実施形態の断面図である。

【符号の説明】

【0027】

1A・・・パネル、1B・・・画素、2A・・・表示回路、2B・・・受光回路、2D 10

・・・表示用信号線、2E・・・出力用信号線、2F・・・表示用走査線、2G・・・入

力用走査線、2H・・・出力用走査線、3A・・・サンプリングトランジスタ、3B

・・液晶素子、3D・・・受光素子、3E・・・入力トランジスタ、3F・・・カレントミ

ラートトランジスタ、3G・・・カレントミラートランジスタ、3H・・・出力トランジス

タ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 浅井 伸利

東京都品川区北品川6丁目7番35号 ソニー株式会社内

審査官 鈴木 俊光

(56)参考文献 特開平10-090655(JP,A)

特開2000-259346(JP,A)

特表2001-504992(JP,A)

特開2001-109394(JP,A)

特開2004-153327(JP,A)

特開平11-125841(JP,A)

特開平08-181348(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |          |

|--------|----------|

| G 02 F | 1 / 1368 |

| G 02 F | 1 / 133  |

| G 02 F | 1 / 1333 |

| G 09 F | 9 / 00   |

| G 09 F | 9 / 30   |

| G 01 J | 1 / 44   |

| H 01 L | 31 / 10  |