(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6120919号

(P6120919)

(45) 発行日 平成29年4月26日(2017.4.26)

(24) 登録日 平成29年4月7日(2017.4.7)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 1 5 Z

A 6 3 F 7/02 3 3 4

請求項の数 1 (全 30 頁)

(21) 出願番号 特願2015-147351 (P2015-147351)

(22) 出願日 平成27年7月27日 (2015.7.27)

(62) 分割の表示 特願2013-141846 (P2013-141846)

原出願日 平成25年7月5日 (2013.7.5)

(65) 公開番号 特開2015-213795 (P2015-213795A)

(43) 公開日 平成27年12月3日 (2015.12.3)

審査請求日 平成28年5月10日 (2016.5.10)

(73) 特許権者 391010943

株式会社藤商事

大阪府大阪市中央区内本町一丁目1番4号

(74) 代理人 100100376

弁理士 野中 誠一

(72) 発明者 矢次 讓

大阪府大阪市中央区内本町一丁目1番4号

株式会社藤商事内

(72) 発明者 内山 保

大阪府大阪市中央区内本町一丁目1番4号

株式会社藤商事内

審査官 進藤 利哉

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

所定のスイッチ信号に起因して抽選処理を実行し、抽選結果に対応した遊技制御動作を実行する遊技機であって、

前記抽選処理を含んだ遊技制御動作を実行する主制御手段は、制御プログラムや固定データを不揮発的に記憶するROMと、作業データを揮発的に記憶するRAMと、抽選処理用の乱数値を生成する乱数生成手段と、システムクロックを受けて動作するCPUと、が内蔵されたワンチップマイコンを有して構成され、

前記乱数生成手段は、システムクロック又はその他の外部クロックに基づいて更新動作を繰り返して数値を更新する数値更新手段と、前記スイッチ信号がON遷移した場合に、数値更新手段の出力値を記憶可能なラッチ手段と、ラッチ手段の記憶値を取得可能な乱数取得手段と、を有し、

前記スイッチ信号のON/OFF状態を記憶する信号取得手段、及び前記乱数取得手段は、CPUから任意にアクセス可能に構成されると共に、前記乱数取得手段の記憶値は、CPUに読み出されることでクリアされるよう構成され、

前記ラッチ手段の記憶値を前記乱数取得手段に取得させて記憶させる第1手段と、第1手段が機能した後、前記乱数取得手段の記憶値がクリアされたか否かに拘わらず、前記ラッチ手段の記憶値を前記乱数取得手段に取得させて上書き記憶させる第2手段と、を有し、

前記信号取得手段の記憶値を定期的に判定し、前記信号取得手段の記憶値が遷移したこ

とに対応して、その時の前記乱数取得手段の記憶値を、前記抽選処理用の乱数値として使用するよう構成されている遊技機。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、遊技動作に起因する抽選処理によって大当たり状態を発生させる遊技機に関し、特に、CPUの遊技制御負担を軽減化して、所望のセキュリティ動作を実現できる遊技機に関するもの。

【背景技術】

【0002】

パチンコ機などの弾球遊技機は、遊技盤に設けた図柄始動口と、複数の表示図柄による一連の図柄変動様式を表示する図柄表示部と、開閉板が開閉される大入賞口などを備えて構成されている。そして、図柄始動口に設けられた検出スイッチが遊技球の通過を検出すると入賞状態となり、遊技球が賞球として払出された後、図柄表示部では表示時間変動される。その後、7-7-7などの所定の態様で図柄が停止すると大当たり状態となり、大入賞口が繰返し開放されて、遊技者に有利な遊技状態を発生させている。

【0003】

このような遊技状態を発生させるか否かは、図柄始動口に遊技球が入賞したことを条件に実行される大当たり抽選で決定されており、上記の図柄変動動作は、この抽選結果を踏まえたものとなっている。

【0004】

この大当たり抽選処理では、遊技球の入賞を示すスイッチ信号の変化に対応して取得される乱数値RNDを、所定の抽選値Hitと対比して当否判定をしている。なお、乱数値RNDを、単一の数値Hitと対比して当否を決定する場合に限らず、複数の抽選値Hit<sub>1</sub>・・・Hit<sub>n</sub>を有する場合や、上限判定値Hit<sub>H</sub>と下限判定値Hit<sub>L</sub>とで当選範囲を規定する場合もある。例えば、乱数値RNDが、下限判定値Hit<sub>L</sub>以上であって、上限判定値Hit<sub>H</sub>未満である場合には(Hit<sub>L</sub> ≤ RND < Hit<sub>H</sub>)、当選状態であると判定している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010-207288号公報

【特許文献2】特開2012-075706号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところが、この種の遊技機では、当否判定に使用する抽選値が、制御プログラムと共にROMに記憶されているので、遊技機を取得すれば容易に把握できるとい問題がある。そこで、従来から各種の違法対策が提案されているが(例えば、特許文献1、特許文献2)、セキュリティレベルを極端に上げると、違法対策としては有効でも、セキュリティ処理のために本来の遊技動作に支障を与えることになる。

【0007】

すなわち、大当たり抽選処理などの主要な制御動作は、8ビットCPUで実行すべきことが義務付けられ、しかも、この制御動作のためのメモリ空間も限られているので、無闇にセキュリティ処理を強化すると、本来の遊技動作に支障が生じるので、複雑高度な遊技制御を実現できないことになる。

【0008】

また、CPUの制御負担を増加させることなく、抽選処理に必要な乱数値について、これを高速で更新できると共に、セキュリティ上や遊技制御上の所望のタイミングで取得できる構成も望まれる。

10

20

30

40

50

## 【0009】

本発明は、上記の問題点に鑑みてなされたものであって、C P Uの遊技制御負担を軽減化して、所望のセキュリティ動作を実現でき、しかも、高速で更新可能な乱数値を所望のタイミングで取得できる遊技機を提供することを目的とする。

## 【課題を解決するための手段】

## 【0010】

上記の目的を達成するため、本発明は、所定のスイッチ信号に起因して抽選処理を実行し、抽選結果に対応した遊技制御動作を実行する遊技機であって、前記抽選処理を含んだ遊技制御動作を実行する主制御手段は、制御プログラムや固定データを不揮発的に記憶するR O Mと、作業データを揮発的に記憶するR A Mと、抽選処理用の乱数値を生成する乱数生成手段と、システムクロックを受けて動作するC P Uと、が内蔵されたワンチップマイコンを有して構成され、前記乱数生成手段は、システムクロック又はその他の外部クロックに基づいて更新動作を繰り返して数値を更新する数値更新手段と、前記スイッチ信号がON遷移した場合に、数値更新手段の出力値を記憶可能なラッチ手段と、ラッチ手段の記憶値を取得可能な乱数取得手段と、を有し、前記スイッチ信号のON/OFF状態を記憶する信号取得手段、及び前記乱数取得手段は、C P Uから任意にアクセス可能に構成されると共に、前記乱数取得手段の記憶値は、C P Uに読み出されることでクリアされるよう構成され、前記ラッチ手段の記憶値を前記乱数取得手段に取得させて記憶させる第1手段と、第1手段が機能した後、前記乱数取得手段の記憶値がクリアされたか否かに拘わらず、前記ラッチ手段の記憶値を前記乱数取得手段に取得させて上書き記憶させる第2手段と、を有し、前記信号取得手段の記憶値を定期的に判定し、前記信号取得手段の記憶値が遷移したことに対応して、その時の前記乱数取得手段の記憶値を、前記抽選処理用の乱数値として使用するよう構成されている。10

## 【0011】

本発明のワンチップマイコンは、コンピュータ機能を発揮する単一の電子素子を意味し、それ以上の限定的な意味を持つものではない。何れにしても、本発明では、ワンチップマイコンに内蔵された乱数生成手段が抽選処理用の乱数値を生成するので、C P Uの遊技制御負担を増加させることなく、乱数値を高速更新することができる。また、ワンチップマイコンの外部に生成手段を配置する場合に比べて、格段にセキュリティレベルを上げることもできる。30

## 【発明の効果】

## 【0017】

上記した通り、本発明によれば、C P Uの遊技制御負担を軽減化して、所望のセキュリティ動作を実現でき、しかも、高速で更新可能な乱数値を所望のタイミングで取得できる。。

## 【図面の簡単な説明】

## 【0018】

【図1】実施例に示すパチンコ機の斜視図である。

【図2】図1のパチンコ機の遊技盤を図示した正面図である。

【図3】図1のパチンコ機の全体構成を示すブロック図である。40

【図4】ワンチップマイコンの内部回路を示す回路図である。

【図5】乱数生成回路の回路構成を示すブロック図である。

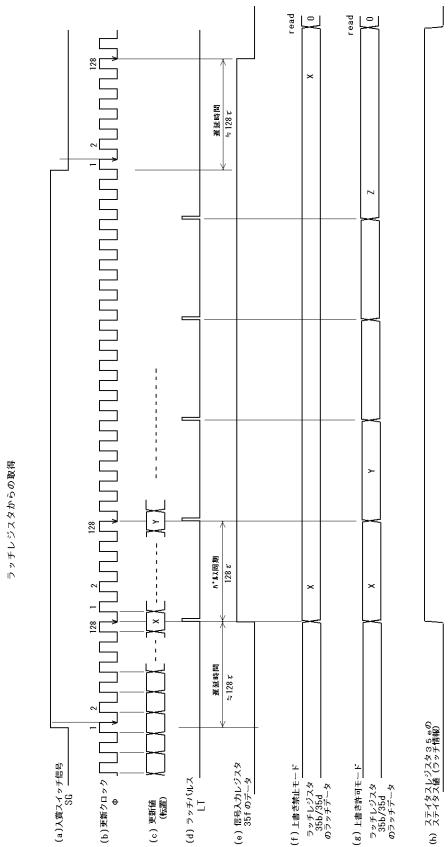

【図6】乱数生成回路の動作内容を示すタイムチャートその他である。

【図7】C P Uの動作内容を示すタイムチャートである。

【図8】C P Uの動作内容を示す別のタイムチャートである。

【図9】主制御部のメイン処理を説明するフローチャートである。

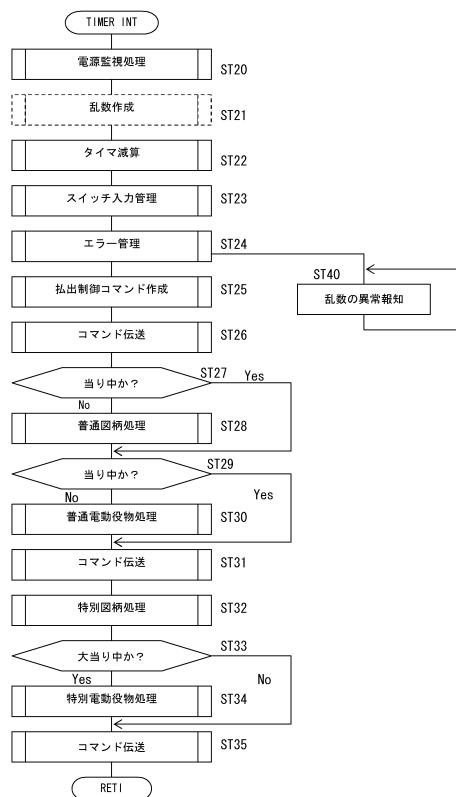

【図10】主制御部のタイマ割込み処理を説明するフローチャートである。

【図11】別の実施例を説明する図面である。

## 【発明を実施するための形態】

## 【0019】

10

20

30

40

50

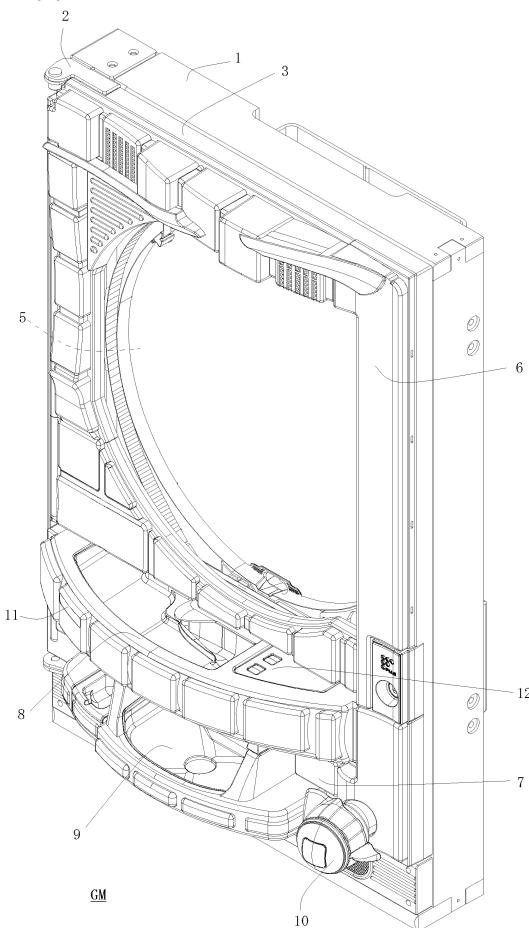

以下、本発明の実施例について詳細に説明する。図1は、本実施例のパチンコ機GMを示す斜視図である。このパチンコ機GMは、島構造体に着脱可能に装着される矩形枠状の木製外枠1と、外枠1に固着されたヒンジ2を介して開閉可能に枢着される前枠3とで構成されている。この前枠3には、遊技盤5が、裏側からではなく表側から着脱自在に装着され、その前側には、ガラス扉6と前面板7とが夫々開閉自在に枢着されている。

#### 【0020】

ガラス扉6の外周には、LEDランプなどによる電飾ランプが、略C字状に配置されている。前面板7には発射用の遊技球を貯留する上皿8が装着され、前枠3の下部には、上皿8から溢れ出し又は抜き取った遊技球を貯留する下皿9と、発射ハンドル10とが設けられている。発射ハンドル10は発射モータと連動しており、発射ハンドル10の回動角度に応じて動作する打撃槌によって遊技球が発射される。10

#### 【0021】

上皿8の外周面には、チャンスボタン11が設けられている。このチャンスボタン11は、遊技者の左手で操作できる位置に設けられており、遊技者は、発射ハンドル10から右手を離すことなくチャンスボタン11を操作できる。このチャンスボタン11は、通常時には機能していないが、ゲーム状態がボタンチャンス状態となると内蔵ランプが点灯されて操作可能となる。なお、ボタンチャンス状態は、必要に応じて設けられるゲーム状態である。

#### 【0022】

上皿8の右部には、カード式球貸し機に対する球貸し操作用の操作パネル12が設けられ、カード残額を3桁の数字で表示する度数表示部と、所定金額分の遊技球の球貸しを指示する球貸しスイッチと、ゲーム終了時にカードの返却を指令する返却スイッチとが設けられている。20

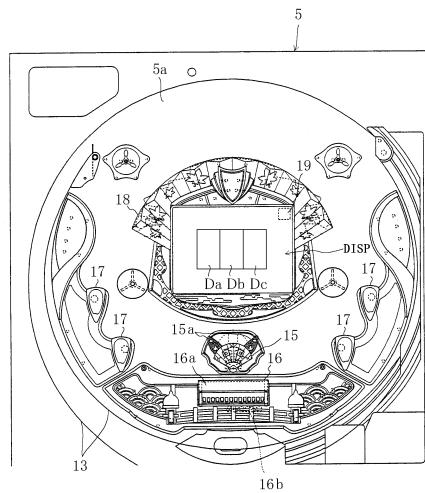

#### 【0023】

図2に示すように、遊技盤5には、金属製の外レールと内レールとからなるガイドレール13が環状に設けられ、その内側の遊技領域5aの略中央には、液晶カラーディスプレイDIPSが配置されている。また、遊技領域5aの適所には、図柄始動口15、大入賞口16、複数個の普通入賞口17（大入賞口16の左右に4つ）、通過口であるゲート18が配設されている。これらの入賞口15～18は、それぞれ内部に検出スイッチを有しており、遊技球の通過を検出できるようになっている。30

#### 【0024】

液晶ディスプレイDIPSは、大当たり状態に係わる特定図柄を変動表示すると共に背景画像や各種のキャラクタなどをアニメーション的に表示する装置である。この液晶ディスプレイDIPSは、中央部に特別図柄表示部Da～Dcと右上部に普通図柄表示部19を有している。そして、特別図柄表示部Da～Dcでは、大当たり状態の招来を期待させるリーチ演出が実行されたり、特別図柄表示部Da～Dc及びその周りでは、当否結果を不確定に報知する予告演出などが実行される。

#### 【0025】

普通図柄表示部19は普通図柄を表示するものであり、ゲート18を通過した遊技球が検出されると、普通図柄が所定時間だけ変動し、遊技球のゲート18の通過時点において抽出された抽選用乱数値により決定される停止図柄を表示して停止するようになっている。40

#### 【0026】

図柄始動口15は、左右1対の開閉爪15aを備えた電動式チューリップで開閉されるよう例えれば構成され、普通図柄表示部19の変動後の停止図柄が当たり図柄を表示した場合には、開閉爪15aが所定時間だけ、若しくは、所定個数の遊技球を検出するまで開放されるようになっている。

#### 【0027】

図柄始動口15に遊技球が入賞すると、特別図柄表示部Da～Dcの表示図柄が所定時間だけ変動し、図柄始動口15への遊技球の入賞タイミングに応じた抽選結果に基づいて50

決定される停止図柄で停止する。なお、特別図柄表示部 D a ~ D c 及びその周りでは、一連の図柄演出の間に、予告演出が実行される場合がある。

#### 【 0 0 2 8 】

大入賞口 1 6 は、例えば前方に開放可能な開閉板 1 6 a で開閉制御されるが、特別図柄表示部 D a ~ D c の図柄変動後の停止図柄が「 7 7 7 」などの大当たり図柄のとき、「 大当たりゲーム 」と称する特別遊技が開始され、開閉板 1 6 a が開放されるようになっている。なお、特別遊技のラウンド数として、8 ラウンド、1 6 ラウンドなど各種の遊技態様が設けられている。ここで、規定ラウンド数が多いほど遊技者に有利である。

#### 【 0 0 2 9 】

大入賞口 1 6 の開閉板 1 6 a が開放された後、所定時間が経過し、又は所定数（例えば 10 10 個）の遊技球が入賞すると開閉板 1 6 a が閉じる。このような動作は、最大で上記した規定ラウンド数の特別遊技が継続され、遊技者に有利な状態に制御される。なお、特別図柄表示部 D a ~ D c の変動後の停止図柄が特別図柄のうちの特定図柄であった場合には、特別遊技の終了後のゲームが高確率状態（以下、確変状態という）となるという特典が付与される。

#### 【 0 0 3 0 】

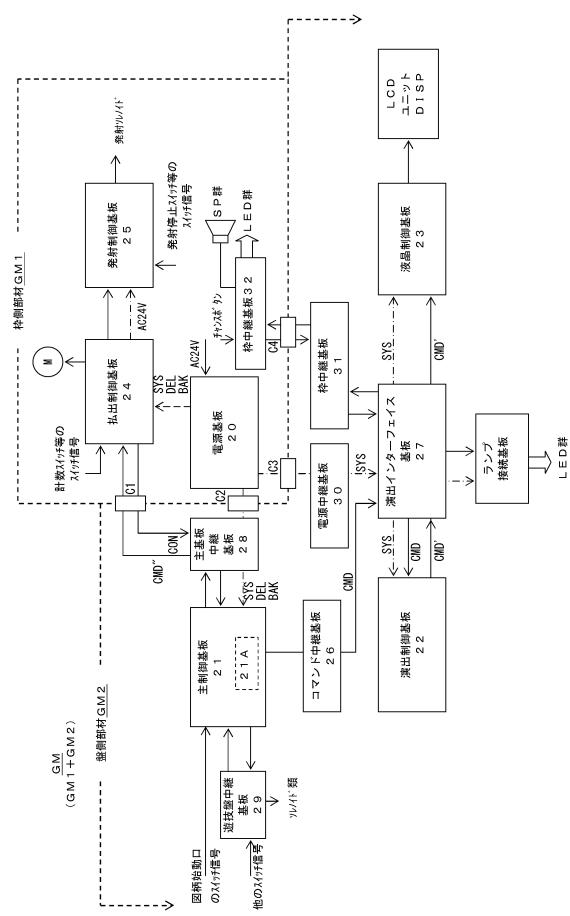

図 3 は、上記した各動作を実現するパチンコ機 G M の全体回路構成を示すブロック図である。図中の一点破線は、主に、直流電圧ラインを示している。

#### 【 0 0 3 1 】

図示の通り、このパチンコ機 G M は、A C 2 4 V を受けて各種の直流電圧やシステムリセット信号（電源リセット信号）S Y S などを出力する電源基板 2 0 と、遊技制御動作を中心統括的に担う主制御基板 2 1 と、主制御基板 2 1 から受けた制御コマンド C M D に基づいてランプ演出及び音声演出を実行する演出制御基板 2 2 と、演出制御基板 2 2 から受けた制御コマンド C M D ' に基いて液晶ディスプレイ D I S P を駆動する液晶制御基板 2 3 と、主制御基板 2 1 から受けた制御コマンド C M D " に基いて払出モータ M を制御して遊技球を払い出す払出制御基板 2 4 と、遊技者の操作に応答して遊技球を発射させる発射制御基板 2 5 と、を中心に構成されている。

#### 【 0 0 3 2 】

但し、この実施例では、主制御基板 2 1 が出力する制御コマンド C M D は、コマンド中継基板 2 6 と演出インターフェイス基板 2 7 を経由して、演出制御基板 2 2 に伝送される。また、演出制御基板 2 2 が出力する制御コマンド C M D ' は、演出インターフェイス基板 2 7 を経由して、液晶制御基板 2 3 に伝送され、主制御基板 2 1 が出力する制御コマンド C M D " は、主基板中継基板 2 8 を経由して、払出制御基板 2 4 に伝送される。

#### 【 0 0 3 3 】

これら主制御基板 2 1 、演出制御基板 2 2 、液晶制御基板 2 3 、及び払出制御基板 2 4 には、ワンチップマイコンを備えるコンピュータ回路がそれぞれ搭載されている。そこで、これらの制御基板 2 1 ~ 2 4 に搭載された回路、及びその回路によって実現される動作を機能的に総称して、本明細書では、主制御部 2 1 、演出制御部 2 2 、液晶制御部 2 3 、及び払出制御部 2 4 と言うことがある。なお、演出制御部 2 2 、液晶制御部 2 3 、及び払出制御部 2 4 の全部又は一部がサブ制御部である。

#### 【 0 0 3 4 】

ところで、このパチンコ機 G M は、図 3 の破線で囲む枠側部材 G M 1 と、遊技盤 5 の背面に固定された盤側部材 G M 2 とに大別されている。枠側部材 G M 1 には、ガラス扉 6 や前面板 7 が枢着された前枠 3 と、その外側の木製外枠 1 とが含まれており、機種の変更に拘わらず、長期間にわたって遊技ホールに固定的に設置される。一方、盤側部材 G M 2 は、機種変更に対応して交換され、新た盤側部材 G M 2 が、元の盤側部材の代わりに枠側部材 G M 1 に取り付けられる。なお、枠側部材 1 を除く全てが、盤側部材 G M 2 である。

#### 【 0 0 3 5 】

図 3 の破線枠に示す通り、枠側部材 G M 1 には、電源基板 2 0 と、払出制御基板 2 4 と、発射制御基板 2 5 と、枠中継基板 3 2 とが含まれており、これらの回路基板が、前枠 3

10

20

30

40

50

の適所に各々固定されている。一方、遊技盤 5 の背面には、主制御基板 2 1、演出制御基板 2 2、液晶制御基板 2 3 が、液晶ディスプレイ D I S P やその他の回路基板と共に固定されている。そして、枠側部材 G M 1 と盤側部材 G M 2 とは、一箇所に集中配置された接続コネクタ C 1 ~ C 4 によって電気的に接続されている。

#### 【 0 0 3 6 】

電源基板 2 0 は、接続コネクタ C 2 を通して、主基板中継基板 2 8 に接続され、接続コネクタ C 3 を通して、電源中継基板 3 0 に接続されている。そして、主基板中継基板 2 8 は、電源基板 2 0 から受けたシステムリセット信号 S Y S 、 R A M クリア信号 D E L 、電圧降下信号、バックアップ電源 B A K 、 D C 1 2 V 、 D C 3 2 V を、そのまま主制御部 2 1 に出力している。同様に、電源中継基板 3 0 も、電源基板 2 0 から受けたシステムリセット信号 S Y S や、交流及び直流の電源電圧を、そのまま演出インターフェイス基板 2 7 に出力している。なお、演出インターフェイス基板 2 7 は、受けたシステムリセット信号 S Y S を、そのまま演出制御部 2 2 と液晶制御部 2 3 に出力している。10

#### 【 0 0 3 7 】

一方、払出制御基板 2 4 は、中継基板を介することなく、電源基板 2 0 に直結されており、主制御部 2 1 が受けると同様の、システムリセット信号 S Y S 、 R A M クリア信号 D E L 、電圧降下信号、バックアップ電源 B A K を、他の電源電圧と共に直接的に受けている。

#### 【 0 0 3 8 】

ここで、電源基板 2 0 が出力するシステムリセット信号 S Y S は、電源基板 2 0 に交流電源 2 4 V が投入されたことを示す電源リセット信号であり、この電源リセット信号によって各制御部 2 1 ~ 2 4 のワンチップマイコンその他の I C 素子が電源リセットされるようになっている。20

#### 【 0 0 3 9 】

主制御部 2 1 及び払出制御部 2 4 が、電源基板 2 0 から受ける R A M クリア信号 D E L は、各制御部 2 1 , 2 4 のワンチップマイコンの内蔵 R A M の全領域を初期設定するか否かを決定する信号であって、係員が操作する初期化スイッチ S W T の O N / O F F 状態に対応した値を有している。

#### 【 0 0 4 0 】

主制御部 2 1 及び払出制御部 2 4 が、電源基板 2 0 から受ける電圧降下信号は、交流電源 2 4 V が降下し始めたことを示す信号であり、この電圧降下信号を受けることによって、各制御部 2 1 、 2 4 では、停電や営業終了に先立って、必要な終了処理を開始するようになっている。また、バックアップ電源 B A K は、営業終了や停電により交流電源 2 4 V が遮断された後も、主制御部 2 1 と払出制御部 2 4 のワンチップマイコンの内蔵 R A M のデータを保持する D C 5 V の直流電源である。したがって、主制御部 2 1 と払出制御部 2 5 は、電源遮断前の遊技動作を電源投入後に再開できることになる（電源バックアップ機能）。このパチンコ機では少なくとも数日は、各ワンチップマイコンの R A M の記憶内容が保持されるよう設計されている。30

#### 【 0 0 4 1 】

一方、演出制御部 2 2 と液晶制御部 2 3 には、上記した電源バックアップ機能が設けられていない。しかし、先に説明した通り、演出制御部 2 2 と液晶制御部 2 3 には、電源中継基板 3 0 と演出インターフェイス基板 2 7 を経由して、システムリセット信号 S Y S が共通して供給されており、他の制御部 2 1 , 2 4 と、ほぼ同期したタイミングで電源リセット動作が実現される。40

#### 【 0 0 4 2 】

図示の通り、主制御部 2 1 は、主基板中継基板 2 8 を経由して、払出制御部 2 5 に制御コマンド C M D ” を送信する一方、払出制御部 2 5 からは、遊技球の払出動作を示す賞球計数信号や、払出動作の異常に係わるステータス信号 C O N を受信している。ステータス信号 C O N には、例えば、補給切れ信号、払出不足エラー信号、下皿満杯信号が含まれる。50

## 【0043】

また、主制御部21は、直接的に、或いは、遊技盤中継基板29を経由して、遊技盤5の各遊技部品に接続されている。そして、遊技盤上の各入賞口16～18に内蔵された検出スイッチのスイッチ信号を受ける一方、電動式チューリップなどのソレノイド類を駆動している。図示の通り、入賞スイッチ信号SGは、直接、主制御部21に伝送され、その他のスイッチ信号は、遊技盤中継基板29を経由して、主制御部21に伝送されている。

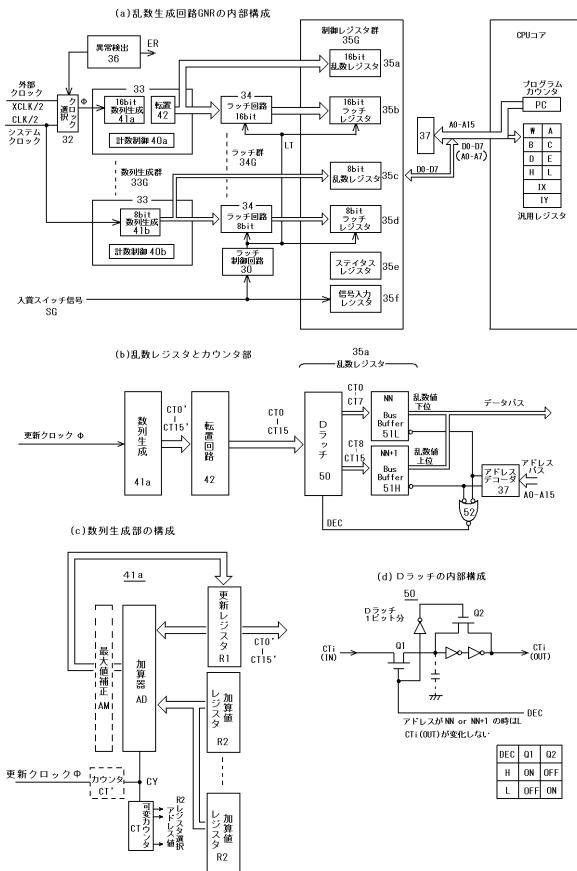

## 【0044】

図4は、主制御部21のワンチップマイコン21Aの内部構成の一部を図示したものである。ここでは、図柄始動口15の検出スイッチSWから入賞スイッチ信号SGを受ける部分も含めて図示している。図示の通り、ワンチップマイコン21Aは、Z80CPU(Zilog社)相当のCPUコア(以下CPUという)と、Z80CTC(counter timer circuit)相当のカウンタ・タイマ回路CTCと、ROM及びRAMのメモリ回路と、ウォッチドッグタイマWDTと、乱数生成回路GNRと、入力ポートINPとを内蔵して構成されている。

## 【0045】

図4に示す通り、検出スイッチSWからの入賞スイッチ信号SGは、バッファ回路BUFを経由して、ワンチップマイコン21Aの乱数生成回路GNRに供給されている。また、入力ポートINPには、大入賞口16や普通入賞口17やゲート18などの検出スイッチからのスイッチ信号が供給されている。

## 【0046】

ところで、バッファ回路BUFは、オープンコレクタ型の出力部を有し、入力側が12Vにプルアップされ、出力側が5Vにプルアップされている。そして、遊技球が図柄始動口15を通過して検出スイッチSWが入賞状態(ON状態)となると、バッファ回路BUFは、正論理のON信号として、入賞スイッチ信号SGを出力する。

## 【0047】

ここで、入賞スイッチ信号SGのパルス幅(遊技球の通過時間T)は、遊技球の通過速度と、遊技球を検知する検出スイッチSWの検出範囲とで規定される。例えば、検出スイッチSWによる遊技球の検出範囲がhである場合に、初速度0の遊技球がt=0から自然落下すると仮定すると、t=Tのタイミングの落下速度Vが、 $V = g T$ となり(g:重力加速度)、 $1/2 m V^2 = m g h$ の関係から、パルス幅T=SQR(2h/g)となり、仮にh=3mmであればパルス幅はT=24.7mS、h=5mmであればT=31.9mSとなる。

## 【0048】

図4及び図5(a)に示す通り、乱数生成回路GNRは、入賞スイッチ信号SGなどのスイッチ信号を受けてラッチパルスLTを出力するラッチ制御回路30と、システムクロックCLK及び外部クロックXCLKを2分周する分周回路31と、2分周された2種類のクロック信号の何れか一方を更新クロックとして選択する選択回路32と、更新クロックに基づいて動作するN個の数列生成部33からなる数列生成群33Gと、ラッチ制御回路30から受けるラッチパルスLTに基づいて数列生成部33の生成値を取得する複数のラッチ回路34からなるラッチ群34Gと、各部の動作を規定する制御パラメータや各部の動作状態を示す動作ステータスを保持する制御レジスタ群35Gと、数列生成部33の動作異常を検出する異常検出回路36と、を含んで構成されている。

## 【0049】

なお、図4には図5には記載していないが、乱数生成回路GNRの各部の動作は、ワンチップマイコン21AのCPUコアとは別の専用プロセッサによって制御されている。但し、本明細書でCPUと称する場合には、ワンチップマイコン21AのCPUコアを意味し、専用プロセッサを意味しない。

## 【0050】

ラッチ制御回路30は、複数M個のスイッチ信号が供給可能に構成され、M種類のラッチパルスLTが独立的に出力可能に構成されている。そして、このラッチ制御回路30の

10

20

30

40

50

構成に対応して、ラッチ群 3 4 G を構成するラッチ回路 3 4 の個数は、数列生成部 3 3 の個数の M 倍である N × M 個である。また、この N × M 個のラッチ回路 3 4 に対応して、ラッチ回路 3 4 からラッチデータを受けるラッチレジスタ 3 5 ( 図 5 ( a ) の 3 5 b , 3 5 d 参照 ) も合計 N × M 個存在する。

#### 【 0 0 5 1 】

したがって、本実施例の乱数生成回路 G N R によれば、図柄始動口 1 5 や普通入賞口 1 7 のスイッチ信号を含んだ合計 M 種類のスイッチ信号に基づいて、M × N 個の乱数値を生成することもでき、抽選処理の豊富化によって遊技内容を豊富化することができる。但し、この実施例では、便宜上、ラッチ制御回路 3 0 に供給されるスイッチ信号は、入賞スイッチ信号 S G だけであると簡素化している。

10

#### 【 0 0 5 2 】

上記した通り、ラッチ群 3 4 G を構成する N × M 個のラッチ回路 3 4 は、数列生成群 3 3 G を構成する N 個の数列生成部 3 3 と、M 種類のスイッチ信号とに対応している。そして、制御レジスタ群 3 5 G には、N × M 個のラッチ回路 3 4 に対応して、N × M 個のラッチレジスタ ( 3 5 b , 3 5 d など ) が設けられ、N 個の数列生成部 3 3 に対応して N 個の乱数レジスタ ( 3 5 a , 3 5 c など ) が設けられている。

#### 【 0 0 5 3 】

例えば、図 5 ( a ) に示す乱数レジスタ 3 5 a や乱数レジスタ 3 5 c は、合計 N 個の乱数レジスタの一部であり、また、図 5 ( a ) に示すラッチレジスタ 3 5 b やラッチレジスタ 3 5 d は、合計 N × M 個のラッチレジスタの一部である。

20

#### 【 0 0 5 4 】

そして、C P U は、ラッチレジスタ 3 5 b やラッチレジスタ 3 5 d など、所望のラッチレジスタをアクセスすることで、ラッチ回路 3 4 にラッチされた数列生成部 3 3 の生成値を取得できるように構成されている。なお、この実施例では、ラッチレジスタ ( 3 5 b や 3 5 d など ) の記憶値が C P U に読み出されると、ラッチレジスタ ( 3 5 b や 3 5 d など ) の記憶値は、自動的にゼロクリアされるよう構成されている。

#### 【 0 0 5 5 】

また、本実施例の制御レジスタ群 3 5 G には、N 個の乱数レジスタ ( 3 5 a や 3 5 c など ) を含むので、C P U が、乱数レジスタ 3 5 a や乱数レジスタ 3 5 c などの乱数レジスタをアクセスすることで、N 個の数列生成部 3 3 が生成する数値列の瞬時値を、何時でも把握できることになる。したがって、本実施例によれば、ラッチレジスタ ( 3 5 b , 3 5 d など ) をアクセスして抽選用乱数値を特定できるだけでなく、乱数レジスタ ( 3 5 a , 3 5 c など ) をアクセスして抽選用乱数値を特定することもできる。

30

#### 【 0 0 5 6 】

また、C P U は、制御レジスタ群 3 5 G に適宜な制御パラメータを書込むことで、乱数生成回路 G N R の動作内容を制御することができる。また、異常検出回路 3 6 やラッチ制御回路 3 0 の動作状態など、乱数生成回路 G N R の内部動作状態は、制御レジスタ群 3 5 G の一部であるステイタスレジスタ 3 5 e のステイタス値を C P U が読み出すことで把握可能に構成されている。

40

#### 【 0 0 5 7 】

ここで、ステイタスレジスタ 3 5 e のステイタス値には、N 個の数列生成部 3 3 についての N ビットのエラー情報が含まれている。そのため、C P U は、ステイタスレジスタ 3 5 e のステイタス値 ( エラー情報 ) を読み出すことで、全ての数列生成部 3 3 について、その異常の有無を確認することができる。

#### 【 0 0 5 8 】

また、この N ビットのステイタス値 ( エラー情報 ) は、C P U の読み出し動作に対応してゼロクリアされ、正常状態を示す値 ( = 0 ) に変更されるよう構成されている。そのため、C P U は、ステイタスレジスタ 3 5 e のステイタス値 ( エラー情報 ) を、例えば、定期的に繰り返し読み出すことで、異常事態が自然復帰したか、或いは、自然復帰しない致命的な異常事態であるかを判断することができる。なお、異常検出回路 3 6 が検出する数

50

列生成部 33 の異常には、動作停止などの深刻なエラーだけでなく、更新クロック の周波数のずれなどの軽微なエラーも含まれている。

#### 【 0 0 5 9 】

また、ステイタスレジスタ 35e のステイタス値には、 $N \times M$  個のラッチレジスタ ( 35b や 35d など ) が、ラッチデータを保持しているか否かのラッチ情報も含まれている。このラッチ情報は、 $N \times M$  個のラッチレジスタ毎に、ラッチデータの有無が 1 ビット ( 0 / 1 ) で規定され、合計で  $N \times M$  ビットとなる。

#### 【 0 0 6 0 】

そして、このステイタス値 ( ラッチ情報 ) は、読み書き可能に構成されており、CPU は、ステイタスレジスタ 35e から所定のラッチレジスタ ( 35b や 35d など ) に対するラッチ情報を読み出すことで、そのラッチレジスタが有意なデータを保持しているか否かを判定することができる。10

#### 【 0 0 6 1 】

そして、有意なデータを保持しているラッチレジスタ ( 35b や 35d など ) から、CPU がラッチデータを読み出すことで、CPU は、抽選処理用の乱数値を取得できることになる。なお、ラッチレジスタ ( 35b や 35d など ) から、ラッチデータを読み出すと、当該ラッチレジスタのデータが自動的にゼロクリアされることは前記した通りである。

#### 【 0 0 6 2 】

ところで、ラッチ情報についてのステイタス値は、書き込み可能にも構成されており、所定のラッチレジスタについてのステイタス値 ( ラッチ情報 ) として、ゼロを書き込むことで、当該ラッチレジスタのラッチデータを意図的にゼロクリアすることもできるよう構成されている。20

#### 【 0 0 6 3 】

この構成は、ラッチレジスタ ( 35b や 35d など ) から、抽選用の乱数値を取得する場合であって、且つ、ラッチレジスタを上書き禁止モード ( 図 6 ( f ) ) で機能させる場合に特に意義を有する。なお、上書き禁止モードでは、後述するように、ラッチレジスタ ( 35b や 35d など ) がゼロクリアされていない限り、その後のラッチパルス LT に拘わらず、ラッチデータを取得できない。一方、抽選用の乱数値を読み出すと、ラッチレジスタが自動的にゼロクリアされるので、その後は、次のラッチパルス LT に同期してラッチデータが一度だけ取得される。30

#### 【 0 0 6 4 】

そのため、抽選用の乱数値が読み出された後も、入賞スイッチ信号 SG が ON レベルを維持する場合には、ラッチレジスタには、同じ入賞スイッチ信号 SG に対する次のラッチデータが書き込まれ、その後の上書きが禁止されることになる。なお、入賞スイッチ信号 SG のパルス幅が 20 ~ 30 ms であると仮定すると、このような事態は当然に発生し、今回の入賞スイッチ信号 SG が OFF レベルに戻った後も、ラッチレジスタが上書き禁止状態を継続することになる。なお、この上書き禁止状態では、当該ラッチレジスタに対するステイタスレジスタ 35e のステイタス値 ( ラッチ情報 ) は ON 状態 (= 1 ) である。

#### 【 0 0 6 5 】

そこで、例えば、今回の入賞スイッチ信号 SG が OFF 状態に遷移したタイミングで、CPU が、当該ラッチレジスタに対するステイタスレジスタ 35e のステイタス値 ( ラッチ情報 ) として、ゼロを書き込むことで、当該ラッチレジスタのデータをゼロクリアすれば、その後のラッチ動作が可能となり、上記の弊害を解消することができる。40

#### 【 0 0 6 6 】

図 5 に戻って説明を続けると、図 5 ( a ) に示す通り、入賞スイッチ信号 SG は、ラッチ制御回路 30 だけでなく、制御レジスタ群 35G を構成する信号入力レジスタ 35f にも供給されており、CPU は、信号入力レジスタ 35f をアクセスすることで、いつでも、入賞スイッチ信号 SG のレベルを把握できるようになっている。なお、信号入力レジスタ 35f は、この実施例では、入賞スイッチ信号 SG の ON / OFF 状態を記憶する RS フリップフロップで構成されている ( 図 6 ( B ) 、図 6 ( C ) 参照 )。50

**【 0 0 6 7 】**

次に、数列生成群 3 3 G を構成する N 個の数列生成部 3 3 は、詳細には、X 個の 8 ビット長の数列生成部 C T 8 と、Y 個の 16 ビット長の数列生成部 C T 16 とに区分され (N = X + Y) 、各々、更新クロック の立上りエッジに同期して数値列を更新している。また、全 N 個の数列生成部 3 3 は、任意に設定された数値範囲で数値列を生成する可変長の数列生成部 V C T と、規定の数値範囲 (0 ~ 2<sup>n</sup> - 1) で数値列を生成する固定長の数列生成部 F C T とに各々細分されている。

**【 0 0 6 8 】**

ここで、8 ビット固定長の数列生成部 F C T<sub>8</sub> は、0 ~ 255 の数値範囲の数値列を生成し、16 ビット固定長の数列生成部 F C T<sub>16</sub> は、0 ~ 65535 の数値範囲の数値列を生成するが、ランダムな初期値から出発して、所定の出現パターンに基づき、飛び飛びの数値を探りながら、2<sup>8</sup> 個又は 2<sup>16</sup> 個の数値を出現させて固定の数値範囲を一巡する。そして、その後は、別の初期値から出発して、別の出現パターンに基づいて同じ動作を繰り返す。

10

**【 0 0 6 9 】**

このような固定長の数列生成部 F C T は、ワンチップマイコン 21A が電源リセットされると、直ちに、ランダムな初期値から更新動作を開始する。そして、C P U が W D T などに基づいて異常リセットされても更新動作が停止されることなく、上記のランダムな更新動作を繰り返すので、数値列を推定することが事実上不可能となっている。すなわち、何らかの方法で、数値列の出現パターンや初期値を知ることができ、且つ、大当たり抽選の抽選値 H i t を知ることができた場合に、意図的に C P U を異常リセットさせても無駄であり、仮に、ワンチップマイコン 21A を電源リセットさせても、電源リセットから C P U が数列生成部 3 3 の数値を取得するまでの時間は、正確には一定化しないので、意図的に大当たり状態を出現させることは不可能である。

20

**【 0 0 7 0 】**

以上、固定長の数列生成部 F C T について説明したが、可変長の数列生成部 V C T は、規定の制御レジスタ 35 に任意に設定した最大値を上限値として、0 ~ 最大値の任意の数値範囲で数値列を生成する。数値列の生成動作は、固定長の数列生成部 F C T と同じであり、可変長の数列生成部 V C T についても、ランダムな初期値から出発して、所定の出現パターンに基づき飛び飛びの数値を探りながら、設定された数値範囲を一巡する。そして、その後は、別の初期値から出発して、別の出現パターンに基づいて同じ動作を繰り返す。

30

**【 0 0 7 1 】**

可変長の数列生成部 V C T は、ワンチップマイコン 21A が電源リセットされない限り、C P U が異常リセットされても更新動作が停止されることなく、上記のランダムな更新動作を繰り返す。この点では、固定長の数列生成部 F C T の動作と同じである。しかし、ワンチップマイコン 21A が電源リセットされた場合には、可変長の数列生成部 V C T は、規定の制御レジスタ 35 に最大値を設定した後に更新動作を開始する点で、固定長の数列生成部 F C T より、ややセキュリティレベルが下がる。

**【 0 0 7 2 】**

40

但し、その反面、可変長の数列生成部 V C T によれば、生成する数値列の数値範囲を適宜に設定して、抽選処理における当選確率を正確に規定できる利点がある。可変長の数列生成部 V C T によれば、生成する数値列の数値範囲の最大値を、例えば 199 に設定するだけで、当選確率を正確に 1 / 200 にすることができる。また、固定長の数列生成部 F C T は更新クロック を受ける毎に、その立上りエッジに同期して数値列を更新するが、可変長の数列生成部 V C T は、規定個数 (適宜な素数で規定) の更新クロック を受けるまでは、それまでの数値を維持し、最後の更新クロック の立上りエッジに同期して数値列を更新するので、この意味でのランダム性が高まる。

**【 0 0 7 3 】**

そこで、本実施例では、可変長の数列生成部 V C T と固定長の数列生成部 F C T のこれ

50

らの特徴を考慮して、大当たり抽選用の乱数値 RND としては、16 ビット固定長の数列生成部 FCT<sub>16</sub> を使用し、大当たり状態において非確変当りか確変当りかを規定する図柄抽選や、特別遊技のラウンド数などの細部についての抽選決定には、8 ビット可変長の数列生成部 VCT<sub>8</sub> を使用している。なお、何ら限定されないが、本実施例では 8 ビット可変長の数列生成部 VCT<sub>8</sub> は、最大値を 199 に設定することで、0 ~ 199 の数値範囲としている。

#### 【0074】

先に説明した通り、可変長の数列生成部 VCT は、固定長の数列生成部 FCT よりややセキュリティレベルが下がるが、8 ビット可変長の数列生成部 VCT<sub>8</sub> は、大当たり抽選に当選した後の細部決定に使用されるに過ぎないので、本実施例によれば、8 ビット可変長の数列生成部 VCT<sub>8</sub> を使用しても、16 ビット固定長の数列生成部 FCT<sub>16</sub> による極めて高いセキュリティレベルが確実に維持される。10

#### 【0075】

図 5 (c) に示す通り、固定長の数列生成部 FCT<sub>16</sub> / FCT<sub>8</sub> は、更新レジスタ R1 と、各々適宜な加算値を保持する複数の加算値レジスタ R2 ··· R2 と、複数の加算値レジスタ R2 ··· R2 の何れか一個を選択するアドレス情報を生成するカウンタ CT と、選択された加算値レジスタ R2 と更新レジスタ R1 の各保有値を加算する加算器 AD とを有して構成されている。ここで、加算値レジスタ R2 ··· R2 の個数は  $2^X$  個であり、カウンタ CT の Y 個の出力ビットのうち、任意に選択された X ビット ( $Y > X$ ) が、加算値レジスタ R2 ··· R2 を選択するアドレス情報として使用される。20

#### 【0076】

なお、図 5 (c) では、説明の便宜上、ハードウェアとして加算器 AD や  $2^X$  個の加算値レジスタ R2 ··· R2 が存在するよう記載しているが、好適には、加算器 AD の機能は、専用プロセッサによって実現される。また、実際の加算値レジスタ R2 は、乱数生成回路 GNR のメモリ（不図示）に記憶された加算値で代用される。

#### 【0077】

そして、加算器 AD の加算結果が、更新レジスタ R1 に保存されるよう構成されており、選択される加算値レジスタ R2 は、更新クロック に同期して変更される。また、加算器 AD は、16 ビット長又は 8 ビット長の加算器であり、更新クロック に同期して機能している。したがって、更新レジスタ R1 の値が DA1 で、その時に選択された加算値レジスタ R2 の値が DA2 である場合には、R1 = DA1 + DA2 の演算が、16 ビット長又は 8 ビット長の加算演算として実行される。30

#### 【0078】

本実施例では、各加算値レジスタ R2 ··· R2 の保有値を適宜に設定することで、 $2^8$  個又は  $2^{16}$  個の更新クロック を受けると、それまでに生成された数値列が数値範囲 (0 ~  $2^{16}$  - 1 又は  $2^8$  - 1) を一巡するよう構成されている。そして、更新レジスタ R1 は、電源投入時や、 $2^8$  個又は  $2^{16}$  個の更新クロック を受けた後に、適宜な初期値に変更されることで、『ランダムな初期値から出発して、所定の出現パターンに基づき飛び飛びの数値を探りながら、設定された数値範囲を一巡する動作』を実現している。また、 $2^8$  個又は  $2^{16}$  個の更新クロック を受けた後に、カウンタ CT の Y 個の出力ビットのうち ( $Y > X$ ) 、選択される X ビットが適宜に変更されることで、加算値レジスタ R2 ··· R2 の選択順序が変わり、出現パターンが変更される。40

#### 【0079】

可変長の数列生成部 VCT<sub>16</sub> / VCT<sub>8</sub> についても基本構成は同じであるが、更新タイミングを規定するカウンタ CT' が付加されている（破線部参照）。カウンタ CT は、更新クロック を規定回数（適宜な素数に設定）受けることを条件に、そのキャリ信号 CY によって加算器 AD を動作させており、この結果、規定個数の更新クロック を受けるまでは、それまでの数値を維持する変則動作が実現される。

#### 【0080】

また、可変長の数列生成部 VCT<sub>16</sub> / VCT<sub>8</sub> には、加算結果が設定された数値範囲50

(0 ~ MAX)に含まれるよう補正部AMが設けられ(破線部参照)、加算器ADの出力ビットのうち、上限値MAXを超えない必要ビット部分だけが使用される。そして、加算結果SUMが上限値MAXを超える場合には、SUM - MAXの補正演算が実行される。

#### 【0081】

以上、数列生成部33について、内部構成の一例を極めて簡略化して説明したが、実際には、セキュリティレベルを上げるべく更に複雑な構成になっている。

#### 【0082】

図5(a)に示す通り、16ビット固定長の数列生成部41aには、専用プロセッサに制御されて16ビット長の数値のビット並びを適宜に入れ替える転置回路42が接続されている。そして、固定長の数列生成部FC<sub>T</sub>41aや転置回路42は、16ビットの転置パターンやランダムな初期値を付与する計数制御部40aに制御されて動作している。なお、計数制御部40aは、制御レジスタ群35Gの所定の制御レジスタに設定された制御パラメータに基づいて動作し、数列生成部41aの異常状態は、ステイタスレジスタ35eのステイタス値(エラー情報)として記憶される。

#### 【0083】

図5(a)に示す通り、転置回路42の出力は、16ビットラッチ回路34と共に、制御レジスタ群35Gの乱数レジスタ35aにも供給されており、CPUは何時でも乱数レジスタ35aの16ビット値を取得できるようになっている。

#### 【0084】

8ビット可変長の数列生成部41b(VCT<sub>8</sub>)についても同様であり、8ビット可変長の数列生成部41b(VCT<sub>8</sub>)は、計数制御部40bに制御されて、所定の数値範囲(0 ~ 199)で数値列を生成し、一巡毎にランダムな初期値に基づいて更新動作を繰り返している。この計数制御部40bも、制御レジスタ群35Gの所定の制御レジスタに設定された制御パラメータ(最大値など)に基づいて数列生成部41bの更新動作を制御し、数列生成部41bの異常状態は、ステイタスレジスタ35eのステイタス値(エラー情報)として記憶される。

#### 【0085】

また、8ビット長の数列生成部41bの出力は、8ビットラッチ回路34と共に、制御レジスタ群35Gの乱数レジスタ35cにも供給されており、CPUは何時でも乱数レジスタ35cの数値を取得できるようになっている。

#### 【0086】

図4に示す通り、分周回路31には、CPUの動作を規定するシステムクロックCLKだけでなく、システムクロックCLKとは無関係に動作する外部クロックXCLKが供給可能に構成されている。2つのクロック信号CLK, XCLKは、何れも分周回路31で2分周されて選択回路32に供給され、制御レジスタ35への設定値に基づいて、何れか一方のクロック信号が、16ビット固定長の数列生成部41a(FC<sub>T</sub><sub>16</sub>)用の更新クロックとして選択される。なお、16ビット可変長の数列生成部VCT<sub>16</sub>や、8ビット長の数列生成部FC<sub>T</sub><sub>8</sub>/VCT<sub>8</sub>については、システムクロックCLKが更新クロックとして使用される。

#### 【0087】

ところで、本実施例では、16ビット固定長の数列生成部41a(FC<sub>T</sub><sub>16</sub>)が、外部クロックXCLKを使用している状態で、異常検出回路36が数列生成部FC<sub>T</sub><sub>16</sub>の異常動作を検知すると、外部クロックXCLKに代えて、自動的にシステムクロックCLKを使用するよう構成されている。そのため、外部クロックXCLKに異常が生じても、数列生成部FC<sub>T</sub><sub>16</sub>が更新動作を継続できるだけでなく、外部クロックXCLKを悪用した不正行為を未然防止することができる。先に説明した通り、数列生成部FC<sub>T</sub><sub>16</sub>の異常動作は、更新クロックの停止だけでなく、例えば、外部クロックXCLKの周波数の異常な低下なども含まれる。

#### 【0088】

10

20

30

40

50

何れにしても、外部クロック XCLK は、システムクロック CLK と非同期とすべきであるが、その周波数は、内部動作の安定化の観点から、システムクロック CLK と同程度の周波数とすべきであり、好ましくは、システムクロック CLK の周波数の 0.8 ~ 1.6 倍の程度の周波数に設定される。なお、特に限定されないが、実施例の場合には、システムクロック CLK の周波数は 20 MHz 程度である。

#### 【0089】

本実施例では、上記の通り、外部クロック XCLK が使用可能であるが、セキュリティ上の観点から数列生成部 FCT<sub>1~6</sub> の更新動作をシステムクロック CLK に同期させないため、外部クロック XCLK を更新クロック として使用するのが好適である。一方、外部クロック XCLK の発振回路を省略する簡易構成を探りたいとの観点からは、システムクロック CLK を更新クロック に使用するのが好適である。10

#### 【0090】

そこで、本実施例では、遊技機の機種毎に何れの動作態様を探るかを、任意に選択できるようジャンパー線 J1, J2 を設け（図 4 参照）、以下の 3 つの動作態様 (a) ~ (c) を任意に選択可能にしている。

#### 【0091】

例えば、ジャンパー線 J2 を切断する機種 (a) では、外部クロック XCLK が数列生成部 FCT<sub>1~6</sub> 用の更新クロック に選択され、ジャンパー線 J1 を切断する機種 (b) では、システムクロック CLK が更新クロック に選択されるよう制御レジスタ 35 に制御パラメータが設定される。また、ジャンパー線 J1, J2 を維持した状態で、外部クロック XCLK を供給することなく、その入力端子 IN をプルダウンする機種 (c) では（破線部参照）、外部クロック XCLK が数列生成部 FCT<sub>1~6</sub> 用の更新クロック に選択されるよう、制御レジスタ 35 に制御パラメータが設定される。なお、この第 3 の機種 (c) では、外部クロック XCLK が供給されていない以上、実際には、バイパス経路 Bypass を通過したシステムクロック CLK が使用されるのは勿論である。20

#### 【0092】

第 3 の機種 (c) では、万一、バイパス経路 Bypass 上の配線パターンなどに異常が生じた場合でも、数列生成部 FCT<sub>1~6</sub> の異常動作を検出した異常検出回路 36 によって、自動的にノーマル経路 Normal のシステムクロック CLK が使用されるので、引き続き数列生成部 FCT<sub>1~6</sub> を正常に動作させることができる。この場合、動作移行時に周波数の変化がないので極めて自然な移行動作を実現することができる。そこで、本実施例は、第 3 の機種 (c) として構成されている。したがって、全ての数列生成部 33 の更新クロック は、システムクロック CLK を 2 分周したものとなる。30

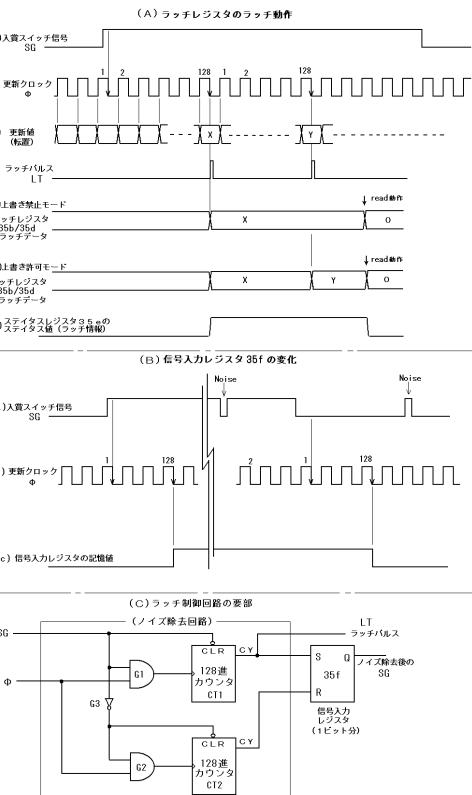

#### 【0093】

次に、図 5 と図 6 に基づいてラッチ制御回路 30 と、ラッチレジスタ (35b や 35d など) の動作について説明する。なお、このラッチ制御回路 30 には、複数のスイッチ信号が供給可能であるが、先に説明した通り、入賞スイッチ信号 SG だけが供給されているとする (M = 1)。但し、他のスイッチ信号が供給されている場合 (M = 1) でも以下と同様の動作が実現される。

#### 【0094】

図 6A に示す通り、この実施例では、入賞スイッチ信号 SG の ON / OFF レベルは、更新クロック の立下りエッジで判定され（図 6A (b) 参照）、更新クロック の立上りエッジで、全 N 個の数列生成部 33 の生成値が、各々の出現パターンに基づいて更新される（図 6A (c) 参照）。なお、数列生成部 33 の種類毎に、数値列の数値範囲や更新タイミングが異なるだけでなく、出現する数値列の出現パターンや、出現パターンの初期値が各々相違するので、N 個の数列生成部 33 の数値列は、原則として各々相違する。40

#### 【0095】

このような数列生成部 33 の更新動作に並行して、ラッチ制御回路 30 は、入賞スイッチ信号 SG が連続して所定時間 ON レベルを維持するか否かを判定しており、例えば、更新クロック で計測して 128 回連続して ON レベルを維持することを条件にラッチバル50

SLTを出力するよう構成されている(図6A(d)参照)。本実施例は、このような判定動作を設けているので、スパイク状のノイズを入賞スイッチ信号SGであると誤認するおそれがない。

#### 【0096】

本実施例の場合、図4に示すバイパス経路Bypassを通過する20MHz程度のシステムクロックCLKが2分周されて更新クロックとなるので、更新クロックは10MHz程度である。したがって、ラッチパルスLTが出力される場合には、少なくとも、入賞スイッチ信号SGが連続して $128 / 10^6 = 128 \mu\text{s}$ 程度、継続してONレベルを維持したことが担保され、ノイズによる影響を排除することができ、また、ノイズを悪用した不正遊技を排除することができる。

10

#### 【0097】

このようにしてラッチ制御回路30で生成されたラッチパルスLTは、ラッチ群34Gを構成するN×M個のラッチ回路34に供給され、各ラッチ回路34は、自らに対応する数列生成部33の生成値を、ラッチパルスLTに同期して取得保持し、これをそのままN×M個のラッチレジスタ(図5の35bや35dなど)に出力する(図6A(e)(f)参照)。

#### 【0098】

但し、本実施例の場合、更新クロックは、10MHz程度であり、入賞スイッチ信号SGのパルス幅Tは、30mS程度であるため、数列生成部33の生成値がラッチ回路34にラッチされた後も、引き続き入賞スイッチ信号SGはON状態を維持することになる。したがって、その後も、128μS程度の時間間隔で、繰り返しラッチパルスLTがラッチ回路に出力される。

20

#### 【0099】

このような動作を考慮して、本実施例では、ラッチレジスタ(35bや35d)を上書き禁止モード(図6A(e))で使用するか、上書き許可モード(図6A(f))で使用するかを、任意に選択可能に構成している。上書き禁止モードとは、ラッチレジスタ(35bや35dなど)のラッチデータが、CPUに読み取られてクリアされるまでは、ラッチ回路34の出力データを受け付けない動作モードを意味する。このような動作モードを探る場合には、CPUによるラッチレジスタの数値取得タイミングが遅れた場合でも、入賞スイッチ信号SGのONエッジに近接したタイミングにおける数列生成部33の生成値を取得できる意義がある。なお、図6A(e)には、最初に取得された数値Xが抽選用乱数値に使用されることを示している。そして、数値Xが取得されたことで、ラッチレジスタ(35bや35d)がゼロクリアされ、ステータスレジスタ35eのステータス値もゼロとなる(図6A(g))。

30

#### 【0100】

これに対して上書き許可モードとは、ラッチ回路34の出力データが常に受け付けられる動作モードであり、ラッチ回路34がラッチパルスLTを受ける毎に、ラッチレジスタ(35bや35dなど)が、新規の数値を取得し直す動作モードを意味する。このような動作モードを探る場合には、CPUの取得タイミングが遅れた場合、入賞スイッチ信号SGのONエッジから大きく(例えば数10mS程度)離れたタイミングの数値を取得することになる。

40

#### 【0101】

この場合には、例え、違法遊技者が、最適タイミング狙って入賞スイッチ信号SGをON動作させたとしても、実際に取得される数値を、違法遊技者の意図する値に近づけることはできない点が利点である。なお、図6A(f)には、最初に取得された数値Xが、次に、数値Yに置き換わり、その後も次々と変化して、最終的にラッチされた数値が抽選用乱数値に使用されることを示している。なお、図示例では、数値Yが取得されたことで、ラッチレジスタ(35bや35d)がゼロクリアされ、ステータスレジスタ35eのステータス値もゼロとなることを示している(図6A(g))。

#### 【0102】

50

上書き禁止モードも、上書き許可モードも、各々、十分に意義を有しているが、本実施例では、ラッチレジスタ（図5の35bや35dなど）を使用することなく、16ビット乱数レジスタ35aと8ビット乱数レジスタ35cに基づいて、抽選用乱数値を特定している。それは、ラッチレジスタ（図5の35bや35dなど）がゼロクリアされた後も、ラッチパルスLTに基づいて、ラッチレジスタにラッチデータが保存されることに対応して、ステイタスレジスタ35eのステイタス値がセットされ、このステイタス値を、新規の入賞スイッチ信号SGであると誤認するおそれがあるためである。

#### 【0103】

但し、この問題は、入賞スイッチ信号SGのONエッジを監視するだけで十分に解消できるので、上書きモードや上書き禁止モードで機能するラッチレジスタの意義が否定される訳ではなく、各々、優れた効果を発揮することに変わりはない。10

#### 【0104】

以上を確認した上で、乱数レジスタ35a, 35cに基づいて、抽選用乱数値を特定する実施例について説明する。なお、実施例では、乱数レジスタ35a, 35cに基づいて抽選用乱数値を特定するが、16ビットラッチ回路34の出力を受けるラッチレジスタ35b（一個又は複数個）、及び／又は、8ビットラッチ回路34の出力を受けるラッチレジスタ35d（一個又は複数個）を、CPUがアクセスして抽選用乱数値を特定してもよく、むしろ、その方が典型的である。

#### 【0105】

何れにしても、16ビット長の乱数レジスタ35aは、図5(b)に示す通り、16ビット長のDラッチ50と、各8ビット長のバスバッファ51L, 51Hと、負論理ORゲート52と、を有して構成されている。乱数レジスタ35aは、このように、1バイト単位で数値を保持するが、この構成に関連して、乱数レジスタ35aには、連続する2つのアドレス値NN, NN+1が付番されている。20

#### 【0106】

なお、これらの点は、16ビット長のラッチレジスタ35bについても同様であり、16ビット長のDラッチと、各8ビット長のバスバッファ2個と、負論理ORゲートとを有して構成され、連続する2つのアドレス値NN', NN'+1が付番されている。なお、乱数レジスタ35aやラッチレジスタ35bが、2バイトデータを1バイト毎に扱うのは、Z80相当のCPUのデータバスD0-D7が1バイト幅であるためであり、また、CPUに内蔵された汎用レジスタ群W, A, B, C, D, E, H, Lが各々1バイトデータを扱う構成になっているためである（図5(a)参照）。30

#### 【0107】

なお、汎用レジスタ群のうち、IX, IYのデータ幅は16ビット長であり、プログラムカウンタPCからアドレスバスA0-A15に出力されるアドレスデータも16ビット長である。そして、上記したアドレス値NN, NN'は、アドレスバスA0-A15を経由してアドレスデコーダ37に供給されることで、適宜なデコード信号DECが生成され、何れかの制御レジスタ35がデコード信号DECによって選択されることになる。なお、この実施例では、アドレスバスA0-A15の下位8ビットA0-A7が、データバスD0-D7と共に用されている。40

#### 【0108】

さて、図5(b)に示す乱数レジスタ35aに説明を戻すと、NN番地と、NN+1番地に付番されたバスバッファ51L, 51Hは、アドレスデコーダ37が出力する選択信号によって選択される。なお、一方の選択信号は、アドレスバスA0-A15の値が、NNの場合にアクティブルベル(Lレベル)となり、他方の選択信号は、アドレスバスA0-A15の値が、NN+1の場合にアクティブルベル(Lレベル)となる。そして、2つの選択信号は、負論理ORゲート52に供給されるので、負論理ORゲート52が出力するデコード信号DECは、2つの選択信号の何れか、或いは、双方がLレベルの時にLレベルとなる。

#### 【0109】

10

20

30

40

50

D ラッチ 5 0 は、図 5 ( c ) に示す回路構成を 16 個設けて構成されている。そして、D ラッチ 5 0 は、転置回路 4 2 が output する転置処理後の数値 C T 0 - C T 15 とデコード信号 D E C とを受けて動作している。具体的には、デコード信号 D E C を共通的に受ける 16 個の M O S トランジスタ Q 1 と、 N O T ゲート ( 16 個 ) を経由してデコード信号 D E C を受ける 16 個の M O S トランジスタ Q 2 と、 M O S トランジスタ Q 2 のソース端子とドレイン端子を接続する N O T ゲート ( 2 × 16 個 ) とを有して構成されている。

#### 【 0 1 1 0 】

D ラッチ 5 0 は、上記の通りに構成されているので、デコード信号 D E C が H レベルの場合には、トランジスタ Q 1 が O N 状態で、トランジスタ Q 2 が O F F 状態となり、逆に、デコード信号 D E C が L レベルの場合には、トランジスタ Q 1 が O F F 状態で、トランジスタ Q 2 が O N 状態となる。

10

#### 【 0 1 1 1 】

そのため、デコード信号 D E C が H レベルの場合には、転置回路 4 2 の出力である 16 ビット長の数値 C T i ( I N ) が、トランジスタ Q 1 と 2 つの N O T ゲートを通過して、そのレベルのままで出力信号 C T i ( O U T ) となる。一方、デコード信号 D E C が L レベルになると、トランジスタ Q 1 が O F F 状態となるので、転置回路 4 2 の出力は伝送されず、M O S トランジスタ Q 1 の浮遊容量に蓄積されている直前の入力データが、トランジスタ Q 2 を通過して出力される。

#### 【 0 1 1 2 】

したがって、この回路構成によれば、デコード信号 D E C を L レベルに遷移させることで、バスバッファ 5 1 L , 5 1 H に伝送する数値 C T i を固定化することができる。言い換えると、デコード信号 D E C = L の状態で、 C P U がバスバッファ 5 1 L , 5 1 H をアクセスすれば、同一の数値の上位バイトと下位バイトを安定して取得できることになる。

20

#### 【 0 1 1 3 】

以上、16 ビット長の乱数レジスタ 3 5 a について説明したが、8 ビット長の乱数レジスタ 3 5 c の回路構成も、基本的に乱数レジスタ 3 5 a と同じである。すなわち、乱数レジスタ 3 5 c は、8 ビット長の D ラッチと、8 ビット長のバスバッファと、負論理 O R ゲートと、を有して構成されている。但し、乱数レジスタ 3 5 c は、転置回路を経由することなく 8 ビット長の数列生成部 4 1 b の値を受けており、これを保持するバスバッファが単一個であることに対応して、乱数レジスタ 3 5 c には、単一のアドレス値が付番されている。

30

#### 【 0 1 1 4 】

続いて、ラッチパルス L T ( 図 6 A ( d ) ) を出力するラッチ制御回路 3 0 の要部について説明する。ラッチ制御回路 3 0 は、図 6 C に示すノイズ除去回路を含んで構成されており、ノイズ除去回路は、2 つの 128 進カウンタ C T 1 , C T 2 と、入賞スイッチ信号 S G を正論理と負論理で受ける 2 つの A N D ゲート G 1 , G 2 と、 N O T ゲート G 3 とで構成されている。ここで、2 つの A N D ゲート G 1 , G 2 には、各々、更新クロック が供給されている。

#### 【 0 1 1 5 】

そして、カウンタ C T 1 のキャリ出力 C Y は、ラッチパルス L T として各ラッチ回路 3 4 に供給され、各カウンタ C T 1 , C T 2 のキャリ出力 C Y , C Y は、信号入力レジスタ 3 5 f のセット端子 S とリセット端子 R とに供給されている。図 6 C に示す通り、本実施例では、信号入力レジスタ 3 5 f の 1 ビット分は、 R S フリップフロップで構成されている。

40

#### 【 0 1 1 6 】

そして、入賞スイッチ信号 S G は、 A N D ゲート G 1 と共に、カウンタ C T 1 のクリア端子 C L R に供給されているので、入賞スイッチ信号 S G が L レベルであると、カウンタ C T 1 のカウント値はゼロ状態を維持することになる。一方、入賞スイッチ信号 S G は、 N O T ゲート G 3 を経由して、 A N D ゲート G 2 と共に、カウンタ C T 2 のクリア端子に供給されている。

50

## 【0117】

本実施例のノイズ除去回路（図6C）は、上記の通りに構成されているので、入賞スイッチ信号SG = Hであれば、カウンタCT1が更新クロックに基づいてカウントアップされ、128個目の更新クロックを受けると、ラッチパルスL Tたるキャリ信号CYが出力される。そして、その後も、128個目の更新クロックを受ける毎に、ラッチパルスL Tが繰り返し出力される（図6A（d）参照）。

## 【0118】

また、カウンタCT1のキャリ信号CYは、信号入力レジスタ35f（RSフリップフロップ）のセット端子Sにも供給されているので、連続して128個の更新クロックを受けることを条件に、信号入力レジスタ35fの記憶値がHレベルとなる。なお、図6Bは、入賞スイッチ信号SGと、更新クロックと、信号入力レジスタ35fの記憶値との関係を図示したものである。10

## 【0119】

ところで、このようなカウンタCT1のカウント動作中に、入賞スイッチ信号SG = Lとなると、カウンタ動作が初期状態に戻るので、結局、更新クロック128個分の間、入賞スイッチ信号SGが継続してHレベルであることを条件に、信号入力レジスタ35fがHレベルになり、ラッチパルスL Tが出力されることになる。したがって、入賞スイッチ信号SGに誤認される可能性のあるスパイクノイズの影響が排除される。図6Bには、入賞スイッチ信号SG = Lの状態で、Hレベルのノイズが重畠される状態を図示しているが、このようなHレベルのノイズによってラッチパルスL Tが出力されたり、信号入力レジスタ35fの記憶値が変化するおそれはない。20

## 【0120】

次に、信号入力レジスタ35fに記憶された入賞スイッチ信号SGも、やがて、数10mS後にはLレベルに戻る。そして、入賞スイッチ信号SGがOFFレベルに遷移した後は、カウンタCT2が計数動作を開始して、128個目の更新クロックを受けると、カウンタCT2からキャリ信号CYが出力される。このキャリ信号CYは、信号入力レジスタ35f（RSフリップフロップ）のリセット端子Rに供給されているので、カウンタCT2からのキャリ信号CYの出力に同期して、信号入力レジスタ35fの記憶値がLレベルに戻ることになる。

## 【0121】

このように、本実施例では、入賞スイッチ信号SGがHレベルである場合だけでなくLレベルである場合にも、それが所定時間（更新クロック128個分）継続することを条件に、信号入力レジスタ35fに取得するので、ノイズによる悪影響を確実に排除することができる。30

## 【0122】

すなわち、入賞スイッチ信号SGがONレベルになった後に、スパイクノイズが重畠しても、入賞スイッチ信号SGがOFFレベルになったと誤認されるおそれがなく、したがって、入賞スイッチ信号SGのON遷移から、相当遅れて信号入力レジスタ35fがアクセスされても、その遅れが大きく（例えば30mS以上で）ない限り、入賞スイッチ信号SGを読み落とすことがない。なお、図6Bには、入賞スイッチ信号SG = Hの状態で、Lレベルのノイズが重畠される状態を図示しているが、このようなLレベルのノイズによって、信号入力レジスタ35fの記憶値が変化するおそれはない。40

## 【0123】

以上、ノイズの影響を排除して入賞スイッチ信号SGのレベルを把握できる構成を説明したが、本実施例では、CPUのソフトウェア処理を全く使用することなく、ノイズ除去効果を達成することに大きな価値がある。

## 【0124】

すなわち、プログラム処理によって上記と同様の動作を実現することは可能ではあるが、そのような手法を探るとCPUの処理負担が増して肝心の遊技制御に悪影響が及ぶ。また、この種の遊技機では、主制御部のROMの使用容量に厳しい制限があるので、ROM50

の記憶容量を無駄使いすることも問題があるが、本実施例によれば、ROMの記憶容量を全く消費することなく、上記した優れた耐ノイズ性能を発揮する。

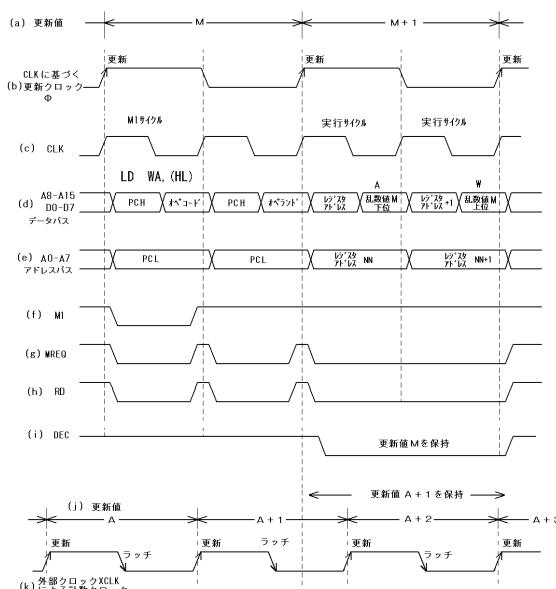

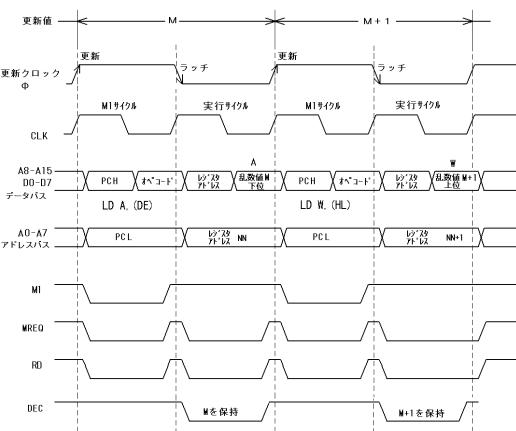

#### 【0125】

続いて、図7に基づいて、CPUが、16ビット長の乱数レジスタ35aの数値を読み出すread動作について説明する。図7(b)は、システムクロックCLKが2分周されて生成された更新クロックを示しており、更新クロックの立上りエッジで、16ビット長の固定長の数列生成部FC<sub>T16</sub>である数列生成部41a(図5(a)参照)が更新されることを示している。図7(a)は、数列生成部41aの数値を示しており、説明の便宜上、出現パターンが単純なインクリメント更新(+1)であって、M → M+1と更新されることにしている。

10

#### 【0126】

また、以下の説明では、一例として、16ビットデータのロード命令LD WA,(HL)について説明する。なお、このロード命令の実行に先行して、HLレジスタには、乱数レジスタ35aの先頭アドレス値である16ビットデータNNが記憶されている。

#### 【0127】

ロード命令LD WA,(HL)は、HLレジスタが指示するアドレス値NNに付番されたレジスタの記憶値(乱数レジスタ35aの下位1バイト記憶値)をAレジスタに取得すると共に、NN+1に付番されたレジスタの記憶値(乱数レジスタ35aの上位1バイト記憶値)をWレジスタに取得する命令である。このロード命令は、1バイト長のオペコードと、1バイト長のオペランドに区分される2バイト命令であり、システムクロックCLKを4サイクル使用して実行を終えるよう構成されている。

20

#### 【0128】

すなわち、図7(c)～図7(e)に示す通り、第1サイクル(M1サイクル)で、この命令(LD WA,(HL))の1バイト目が記憶されているメモリのアドレス値(プログラムカウンタPC<sub>H</sub>・PC<sub>L</sub>の値)がアドレスバスA0-A15に出力され、CPUにオペコードが取得された後、第2サイクルで、この命令の2バイト目が記憶されているメモリのアドレス値(プログラムカウンタPC<sub>H</sub>・PC<sub>L</sub>の値)がアドレスバスA0-A15に出力されてCPUにオペランドが取得される。

#### 【0129】

そして、その後の第3サイクルでは、アドレスバスA0-A15に16ビットアドレス値NNが出力されて、乱数レジスタ35aの下位1バイト記憶値がAレジスタに取得され、第4サイクルでは、アドレスバスA0-A15に16ビットアドレス値NN+1が出力されて、乱数レジスタ35aの上位1バイト記憶値がWレジスタに取得される。なお、図7(f)～図7(h)は、CPUからコントロールバスに出力される制御信号であり、各々、M1サイクルであることを示すM1信号(f)、メモリリクエスト信号MR EQ(g)、メモリリード信号RD(h)を示している。

30

#### 【0130】

また、図7(i)は、乱数レジスタ35aの負論理ORゲート52から出力されるデコード信号DECを示している。先に説明した通り、デコード信号DECは、アドレスバスA0-A15に出力されるアドレス値NNのアドレスデコード値と、アドレス値NN+1のアドレスデコード値の負論理OR値であるから、上記した4サイクルの命令実行中の第3サイクルと第4サイクルだけがLレベルとなり、それ以外のタイミングでは、Hレベルとなる。

40

#### 【0131】

そのため、乱数レジスタ35aのDラッチ50は、上記した4サイクル動作中の第2サイクルまではON状態であって、転置回路42からの数値CT<sub>i</sub>をバスバッファ51L, 51Hに伝えるが、その後の第3サイクルと第4サイクルは、OFF状態となって、転置回路42からの数値CT<sub>i</sub>を遮断することになる。したがって、第2サイクルの終了時における転置回路42の出力値が、第3サイクルと第4サイクルの間は、変化することなく維持されることになる。

50

**【 0 1 3 2 】**

このように、本実施例では、乱数レジスタ 35a に D ラッチ 50 を設け、その ON/OFF 状態をデコード信号 DEC で制御するので、16 ビット長の乱数レジスタ 35a などの制御レジスタに付番されたアドレス情報を、連続してアドレスバス A0 - A15 に出力する限り、その時の数値を正確に取得することができる。したがって、例えば、+1 の出現パターンを探っている 16 ビット長の数値列が、数値 01FFFH の状態から 0200H に更新されるタイミングで、乱数レジスタ 35a がアクセスされたとしても、CPU に取得される値は、01FFFH か 0200H である正常な数値を転置させた値であり、02FFFH のような中途半端な数値が転置されて取得されるおそれはない。

**【 0 1 3 3 】**

10

なお、この動作は、更新クロック をシステムクロック CLK から生成するのではなく、外部クロック XCLK から生成した場合も同様に保障される。すなわち、図 7(j) に示すように、より高速で、システムクロックと同期しない更新クロック を使用した場合でも、デコード信号 DEC による D ラッチの開閉制御によって、正常な数値である A + 1 を転置させた値を取得することができる。

**【 0 1 3 4 】**

これに対して、制御レジスタに付番されたアドレス情報を、アドレスバス A0 - A15 に連続して出力しないロード命令を使用すると上記のような安定動作が保証されない。図 8 は、ロード命令 LD A,(DE) とロード命令 LD W,(HL) を連続される場合を例示している。なお、これらの命令に先行して、D E レジスタにはアドレス値 NN が格納され、HL レジスタにはアドレス値 NN + 1 が格納されている。また、説明の都合上、16 ビット長の数値列は、+1 の出現パターンを探っていることにする。

20

**【 0 1 3 5 】**

このような状態で、ロード命令 LD A,(DE) と、ロード命令 LD W,(HL) とを連続させても、ロード命令 LD A,(DE) の実行後に、不可避的にロード命令 LD W,(HL) の命令フェッチサイクル (M1) が入るので、デコード信号 DEC を L レベルに維持させることができず、その結果として、M や M + 1 のような正常なアドレス値を転置させた値ではなく、数値 M の下位バイトと、数値 M + 1 の上位バイトを組み合わせた中途半端な数値が転置されて CPU に取得されることになる。

**【 0 1 3 6 】**

30

このような場合には、特に、発生する数値列の数値範囲 (0 ~ MAX) が、固定範囲 (0 ~ 2<sup>16</sup>) でない場合 (MAX < 2<sup>16</sup> - 1) には、不合理な乱数値 RND を取得してしまうおそれもある。例えば、数値列の上限値 MAX が MAX = 1150H の場合に、仮に、10FFFH から 1134H への更新時に乱数値が取得されると、取得された乱数値は、11FFFH となって上限値 MAX を超えてしまう。

**【 0 1 3 7 】**

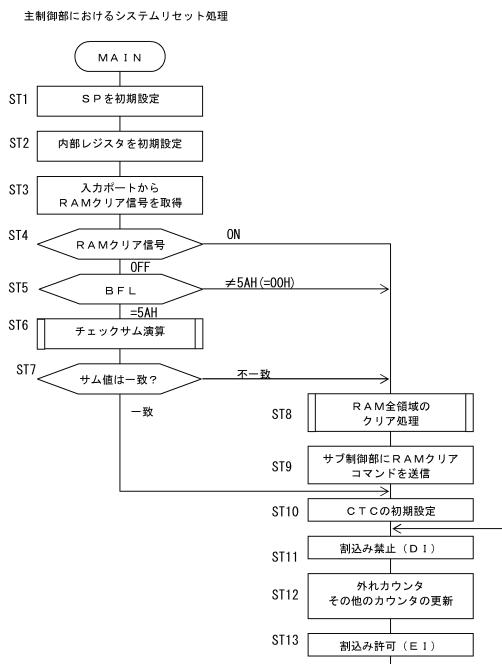

以上、乱数生成回路 GNR について詳細に説明したので、続いて、図 4 に示す CPU によって実行される主制御部 21 の遊技動作を説明する。図 9 及び図 10 は、主制御部 21 の制御プログラムを示すフローチャートであり、電源電圧の復旧や投入に基づいて起動されるシステムリセット処理 (図 9) と、所定時間毎 (4mS) に起動されるマスク可能なタイマ割込み処理 (図 10) とで構成されている。

40

**【 0 1 3 8 】**

以下、図 9 を参照しつつ、システムリセット処理プログラム (メイン処理) について説明する。メイン処理が開始されるのは、停電状態からの復旧時のように初期化スイッチ SWT が OFF 状態で電源が ON 状態になる場合と、遊技ホールの開店時のように、初期化スイッチ SWT が ON 操作されて電源が ON 状態になる場合とがある。なお、ウォッチドッグタイマ WDT が起動して CPU が強制的にリセットされる場合もある。

**【 0 1 3 9 】**

何れの場合でも、Z80CPU は、最初に、CPU 内部のスタックポインタ SP の値を、スタック領域の最終アドレスに対応して初期設定する (ST1)。次に、ワンチップマ

50

イコンの乱数生成回路 G N R の制御レジスタ群 3 5 G を含んだ各種レジスタの値を初期設定する ( S T 2 )。

#### 【 0 1 4 0 】

ステップ S T 2 の初期設定処理が終われば、入力ポート I N P から R A M クリア信号 D E L を取得する ( S T 3 )。R A M クリア信号 D E L とは、ワンチップマイコン 2 1 A の内蔵 R A M の全領域を初期設定するか否かを決定する信号であって、係員が操作する初期化スイッチ S W T の O N / O F F 状態に対応した値を有している。

#### 【 0 1 4 1 】

次に R A M クリア信号 D E L のレベルが判定されるが ( S T 4 )、R A M クリア信号 D E L が O N 状態であったと仮定すると、内蔵 R A M の全領域がゼロクリアされる ( S T 8 )。次に、R A M 領域がゼロクリアされたことを報知するための制御コマンドを出力する ( S T 9 )。

#### 【 0 1 4 2 】

次に、タイマ割込み動作 ( 図 1 0 ) を起動する割込み信号 I N T を出力する C T C を初期設定する ( S T 1 0 )。そして、C P U を割込み禁止状態にセットした状態で ( S T 1 1 )、必要なカウンタがあれば、これについて更新処理を実行し ( S T 1 2 )、その後、C P U を割込み許可状態に戻して ( S T 1 3 )、ステップ S T 1 1 に戻る。

#### 【 0 1 4 3 】

但し、本実施例では、乱数生成回路 G N R から多数の乱数値を取得できるので、ステップ S T 1 1 ~ S T 1 3 の処理を全て排除することができる。そのため、S T 1 1 ~ S T 1 3 の分だけ、R O M の記憶容量を節約することができ、他の制御処理を豊富化することができる。

#### 【 0 1 4 4 】

次に、ステップ S T 4 の判定処理に戻って説明すると、C P U がウォッチドッグタイマ W D T などによって強制的にリセットされた場合や、停電状態からの復旧時には、R A M クリア信号 D E L は O F F 状態である。そして、このような場合には、ステップ S T 4 の判定に続いて、バックアップフラグ B F L の内容が判定される ( S T 5 )。バックアップフラグ B F L とは、電源監視処理 ( S T 2 0 ) においてバックアップ処理が実行されたことを示すデータであり、この実施例では、電源遮断時にバックアップフラグ B F L が 5 A H とされ、電源復帰後のステップ S T 2 0 の処理でゼロクリアされる。

#### 【 0 1 4 5 】

そのため、電源投入時や、停電状態からの復旧時である場合には、バックアップフラグ B F L の内容が 5 A H の筈である。但し、何らかの理由でプログラムが暴走状態となり、ウォッチドッグタイマによる C P U リセット動作が生じたような場合には、バックアップフラグ B F L = 0 0 H である。したがって、B F L = 5 A H ( 通常は B F L = 0 0 H ) となる場合には、ステップ S T 5 からステップ S T 8 の処理に移行させて遊技機の動作を初期状態に戻す。

#### 【 0 1 4 6 】

一方、バックアップフラグ B F L = 5 A H であれば、チェックサム値を算出するためのチェックサム演算を実行する ( S T 6 )。ここで、チェックサム演算とは、内蔵 R A M のワーク領域を対象とする 8 ビット加算演算である。そして、チェックサム値が算出されたら、この演算結果を、R A M の S U M 番地の記憶値と比較をする ( S T 7 )。

#### 【 0 1 4 7 】

S U M 番地には、電圧低下時に実行される電源監視処理 ( S T 2 0 ) において、同じチェックサム演算によるチェックサム値が記憶されている。なお、記憶された演算結果は、内蔵 R A M の他のデータと共に、バックアップ電源によって維持されている。したがって、本来は、ステップ S T 7 の判定によって両者が一致する筈である。

#### 【 0 1 4 8 】

しかし、電源低下時にチェックサム演算の実行できなかった場合や、実行できても、その後、メイン処理のチェックサム演算 ( S T 6 ) の実行時までの間に、ワーク領域のデー

10

20

30

40

50

タが破損している場合もあり、このような場合にはステップ S T 7 の判定結果は不一致となる。

#### 【 0 1 4 9 】

そこで、判定結果の不一致によりデータ破損が検出された場合には、ステップ S T 8 の処理に移行させて R A M クリア処理を実行し、遊技機の動作を初期状態に戻す。一方、ステップ S T 7 の判定において、チェックサム演算( S T 8 )によるチェックサム値と、 S U M 番地の記憶値とが一致する場合には、上記したステップ S T 1 0 の処理に移行することになる。

#### 【 0 1 5 0 】

続いて、上記したメイン処理を中断させて、 4 m S 毎に開始されるタイマ割込み処理プログラム( 図 1 0 )を説明する。タイマ割込みが生じると、 C P U のレジスタを保存することなく、直ちに電源監視処理を実行する( S T 2 0 )。これは、タイマ割込み処理が起動されるタイミングが、ステップ S T 1 3 の直後に固定されているためである。

10

#### 【 0 1 5 1 】

電源監視処理( S T 2 0 )では、電源基板 2 0 から供給されている電圧降下信号のレベルを判定し、異常レベルであれば、バックアップフラグ B A K F L G を 5 A H に設定し、チェックサム値を算出して、 S U M 番地に記憶した上で、電源が遮断されるのを待つ。

#### 【 0 1 5 2 】

次に、普通図柄処理 S T 2 8 における抽選処理で使用される当り用カウンタ R G を更新する乱数作成処理を実行する( S T 2 1 )。当り用カウンタ R G は、所定数値範囲内でインクリメント( + 1 )され、更新後のカウンタの値は、当り判定用乱数値として当否抽選処理で活用される。具体的には、当り用カウンタ R G の値は、遊技球がゲート 1 8 を通過した場合に、普通図柄処理( S T 1 8 )における当り抽選処理で当り用カウンタ R G が使用される。

20

#### 【 0 1 5 3 】

ところで、特別図柄処理( S T 3 2 )における大当たり抽選処理に使用される抽選用乱数値 R N D については、乱数生成回路 G N R から取得するので、ソフトウェア処理で更新されることはない。したがって、この意味でも、本実施例では、 R O M の記憶容量を節約することができ、他の制御処理を豊富化することができる。

#### 【 0 1 5 4 】

30

なお、本明細書では、乱数生成回路 G N R に関する説明の便宜上、当り用カウンタ R G について、ステップ S T 2 1 の処理で更新しているが、本実施例の乱数生成回路 G N R からは、更新クロック を共通化するものの、数値が全く関連しない多数の乱数値を取得できるので、実際には、ステップ S T 2 1 の処理を排除するのが好ましく、そうすれば、 R O M の記憶容量を更に節約することができる。

#### 【 0 1 5 5 】

何れにしても、次に、遊技動作の時間を管理しているタイマについてタイマ減算処理を行う( S T 2 2 )。減算されるタイマは、大入賞口 1 6 の開放時間や、その他の遊技演出時間を管理するものである。

#### 【 0 1 5 6 】

40

このようなタイマ減算処理が終わると、図柄始動口 1 5 やゲート 1 8 の検出スイッチを含む各種スイッチ類のスイッチ信号を取得して記憶する( S T 2 3 )。なお、図柄始動口 1 5 に関する入賞スイッチ信号 S G は、乱数生成回路 G N R の信号入力レジスタ 3 5 f をアクセスして取得する。一方、その他の検出スイッチによるスイッチ信号は、ワンチップマイコンの入力ポート I N P から取得する。但し、入賞スイッチ信号 S G 以外のスイッチ信号についても、乱数生成回路 G N R の信号入力レジスタ 3 5 f を経由させることができ、その方が好ましいことは前述した通りである。

#### 【 0 1 5 7 】

そして、何れのスイッチ信号も、今回の取得値と前回の取得値とを対比して、 O N 状態に遷移したか、或いは、 O F F 状態に遷移したかが判定され記憶される。従来の遊技機で

50

は、ノイズ対策として、スイッチ信号のON遷移やOFF遷移の判定に、複数回の割込み処理に跨った重複判定を要したが、本実施例では、乱数生成回路G NRにノイズ除去回路(図6C)を設けているので、入賞スイッチ信号SGについての重複判定は全く不要である。

#### 【0158】

すなわち、従来は、割込み処理毎に繰り返し判定して、例えばOFF ON ONと推移したことを条件に、入賞スイッチ信号SGがON遷移したと判定していたが、本実施例では、単純にOFF ONの変化をステップST23の処理で確認できれば、それだけで、入賞スイッチ信号SGがON遷移したと判定することができる。なお、信号入力レジスタ35fを経由させれば、他のスイッチ信号についても同様の判定で足りることになる。

10

#### 【0159】

このように、本実施例では、スイッチ信号がON遷移した $2 \times$ 後には、そのスイッチ信号がON遷移したと判定できるので、例えば、制御内容を複雑高度化するべく、割込み周期を大幅に長く設定しても( $>>4\text{mS}$ )、入賞スイッチ信号SGやその他のスイッチ信号を読み落とすおそれがない。また、重複判定をしなくて良い分だけ、制御プログラムを簡素化でき、その分だけROMの消費量を抑制できる。

#### 【0160】

さて、このようなスイッチ入力処理(ST23)が終わると、エラー管理処理を実行する(ST24)。エラー管理処理とは、遊技球の補給が停止したり、遊技球が詰まっているかなど、機器内部に異常が生じていないかの判定を意味する。

20

#### 【0161】

また、乱数生成回路G NRに異常が発生していないかの判定を意味する。先に説明した通り、N個全ての数列生成部33...33について、その異常の有無は、ステータスレジスタ35eに記憶されている。したがって、CPUは、ステータスレジスタ35eを読み出すだけで、数列生成部33が正常に動作しているかを判定することができる。そして、ステータスレジスタ35eを読み出す毎に、ステータス値は正常レベルに戻るので、複数回の割込み処理で、数列生成部33に異常が認められる場合には、その異常を報知して制御動作を停止するようにしている(ST40)。

#### 【0162】

エラー管理処理(ST24)が終われば、次に、払出制御部33向けの制御コマンドを作成した後(ST25)、この段階で生成されている制御コマンドを該当するサブ制御部に伝送する(ST26)。

30

#### 【0163】

続いて、現在が当り中の動作モードでないことを条件に、普通図柄処理を実行する(ST28)。普通図柄処理とは、普通電動役物を作動させるか否かの判定を意味し、ステップST23のスイッチ入力結果によって遊技球がゲートを通過していると判定された場合に、乱数生成処理(ST21)で更新された当り用カウンタRGを、当り当選値と対比する。そして、対比結果が当選状態であれば当り中の動作モードに変更する。また、当り中となれば、普通電動役物の作動に向けた処理を行う(ST30)。

#### 【0164】

次に、必要な制御コマンドを該当するサブ制御部に伝送し(ST31)、特別図柄処理を行う(ST32)。特別図柄処理とは、大入賞口16など特別電動役物を作動させるか否かの判定であり、大当たり抽選処理を含んだ処理である。

40

#### 【0165】

具体的な処理としては、ステップST23のスイッチ入力結果によって入賞スイッチ信号SGがON遷移したと判定された場合には、乱数生成回路G NRの乱数レジスタ35aの数値を取得して、大当たり抽選用の乱数値RNDとして記憶する。この場合の取得処理としては、单一の命令(フェッチサイクルが单一)で、2バイトデータを取得できるロード命令が使用される。例えば、図7に説明したロード命令LD AW,(HL)が使用され、これに先行して、乱数レジスタ35aを特定するレジスタ番号NN, NN+1についてのロード命

50

令 LD HL,NN が使用される。

#### 【 0 1 6 6 】

また、乱数レジスタ 35c の数値を取得して、図柄抽選用の乱数値 RND' として記憶する。先に説明した通り、この実施例では、大当たり抽選用の乱数値 RND は、数値範囲 (0 ~ 65535) の 16 ビットデータであり、図柄抽選用の乱数値 RND' は、数値範囲 (0 ~ 199) の 8 ビットデータである。したがって、乱数レジスタ 35c のアクセスは、1 バイト用のロード命令である LD A,(DE) が使用される。

#### 【 0 1 6 7 】

そして、このタイミングで、図柄演出処理（図柄表示部 Da ~ Dc の図柄変動処理）が終了しており、且つ、抽選保留状態の先行する入賞スイッチ信号 SG が存在しない場合には、乱数値 RND に基づいて大当たり抽選処理を実行し、乱数値 RND' に基づいて図柄抽選を実行する（ST32）。大当たり抽選処理の当選状態では、図柄抽選処理によって確変当たりか否か、及び、特別遊技のラウンド数が決定され、大当たり抽選処理の外れ状態では、図柄抽選処理によって外れ図柄が決定される。10

#### 【 0 1 6 8 】

また、ステップ ST32 の処理では、変動動作後の停止図柄の特定を含んで、変動パターンコマンドが抽選決定される。変動パターンコマンドとは、演出制御部 22 に伝送される演出動作用の制御コマンドであり、画像制御部 23 における図柄変動動作を規定したものである。この変動パターンコマンドは、大当たり抽選の当否結果だけでなく、リーチ演出などの演出動作の総時間を特定してコマンドバッファに格納される。なお、コマンドバッファに格納された変動パターンコマンドは、その後のステップ ST35 のタイミングで演出制御部 22 に伝送される。20

#### 【 0 1 6 9 】

一方、このタイミングが、図柄演出処理中であれば、大当たり抽選処理が待機状態（抽選保留状態）となり、実行中の図柄演出が終了し、これに続く大当たり抽選に伴う図柄演出が終了すれば、そのタイミングにおけるステップ ST32 の処理として、保存状態の大当たり抽選用の乱数値 RND や、乱数値 RND' を使用した抽選処理が実行される。

#### 【 0 1 7 0 】

何れにしても、特別図柄処理（ST32）の大当たり抽選処理によって当選状態となれば、大当たり中の動作モードに変わり、大入賞口など特別電動役物の作動に向けた処理を行う（ST34）。

#### 【 0 1 7 1 】

次に、ステップ ST32 の処理で生成された変動パターンコマンドが演出制御部 22 に伝送され（ST35）、タイマ割込みが終わる。その結果、メインルーチン（不図示）の処理に戻ることになるが、所定時間（4mS）経過すると、再度ステップ ST11 の処理が開始されるので、ステップ ST20 ~ 35 の処理は、4mS 毎に繰り返されることになる。

#### 【 0 1 7 2 】

以上説明した実施例では、入賞スイッチ信号 SG の ON 遷移を信号入力レジスタ 35f の値に基づいて判定し（ST23）、入賞スイッチ信号 SG が ON 遷移した場合には、各々、単一の命令で、乱数レジスタ 35a, 35c から 2 種類の乱数値 RND, RND' を取得しており（ST32）、ラッチレジスタ 35b, 35d やステイタスレジスタ 35e をアクセスしない点で、プログラム負担が最小化されている。しかも、入賞スイッチ信号 SG の ON 遷移した直近のタイミングにおける数列生成部 33 の生成値を取得できる点でも優れている。40

#### 【 0 1 7 3 】

しかし、このような構成に限定されるものではなく、適宜に変更可能である。例えば、上書き禁止モードや上書き許可モードに設定されたラッチレジスタ（35b, 35d など）から、複数種類の乱数値 RND, RND' … を取得するのも好適である。なお、この場合にも 16 ビット長のラッチレジスタ（35b）については、LD WA,(HL) などの命令50

で、2バイト長の乱数値を一気に取得される。

**【0174】**

また、入賞スイッチ信号SGのON遷移については、必ずしも、信号入力レジスタ35fの値に基づいて判定する必要はなく、例えば、ステイタスレジスタ35eのステイタス値（ラッチ情報）に基づいて判定しても良い。すなわち、本実施例では、信号入力レジスタ35fに対すると同様の確実なノイズ対策を施した上で、ラッチパルスLTが出力されるので（図6A（d）参照）、ステイタスレジスタ35eに加えて、信号入力レジスタ35fをアクセスする必要は特にならない。

**【0175】**

但し、入賞スイッチ信号SGのON状態が継続されている状態で、ラッチレジスタ（35b, 35dなど）を重複してアクセスしてしまう動作を防止するには、入賞スイッチ信号SGのONエッジに対応してラッチレジスタ（35b, 35dなど）をアクセスするのが好ましい。すなわち、入賞スイッチ信号SGのONエッジを検出するために、ステイタスレジスタ35eに加えて、信号入力レジスタ35fをアクセスするのが好ましい。

**【0176】**

なお、信号入力レジスタ35fをアクセスする構成を探る場合には、入賞スイッチ信号SGのOFFエッジを検出時に、ステイタスレジスタ35eのステイタス値（ラッチ情報）をクリアすることもでき、ラッチレジスタ（35b, 35dなど）を上書き禁止モードで使用しても、何の問題も生じない。

**【0177】**

以上、本発明の実施例について詳細に説明したが、具体的な回路構成やプログラム処理は、適宜に変更可能であり、特に本発明を限定するものではない。例えば、図5（b）の回路構成では、Dラッチ50は、ORゲート52の出力によって制御されているが、ORゲート52を省略して、制御信号MR EQや制御信号RDによってDラッチ50を制御しても良い。

**【0178】**

また、16ビット固定長／可変長の数列生成部FCT<sub>1~6</sub>や、8ビット固定長／可変長の数列生成部VCT<sub>8</sub>の用途は、上記したものに限定されず、各種の活用が可能である。例えば、特別図柄抽選処理（ST32）において、先の実施例で使用した数列生成部VCT<sub>8</sub>と同一又は別の数列生成部VCT<sub>8</sub>を使用して、その数列生成部VCT<sub>8</sub>が生成する数値に基づいて、変動パターンコマンドを抽選決定することができる。

**【0179】**

この場合、変動パターンコマンドの個数と、数列生成部VCT<sub>8</sub>が生成する数値列の数値範囲を同一に設定すれば、各変動パターンの当選率を同一にすることができる。逆に、変動パターンコマンドの個数より数列生成部VCT<sub>8</sub>の数値範囲を広げれば、各変動パターンの当選率を非同一にすることで、変動パターン毎に、当選率を適宜に振分け設定することもできる。

**【0180】**

また、このような振分け抽選を想定すると、16ビット可変長の数列生成部FCT<sub>1~6</sub>が生成する数値に基づいて、変動パターンコマンドの決定や、非確変当りか確変当りかを規定する図柄抽選を実行するのも好適である。数列生成部FCT<sub>1~6</sub>を使用すると、生成される数値範囲が広いので、例えば、1000程度の数値範囲の乱数値に基づいて、細かな振分け抽選が可能になる。

**【0181】**

また、図10の実施例では、説明の便宜上、ソフトウェアカウンタ（当り用カウンタRG）に基づいて、普通図柄処理（ST28）を実施したが、乱数生成回路GNRからの取得値を使用するのが好適であることは先に説明した通りである。

**【0182】**

この場合、普通図柄処理ST28での抽選処理で使用される乱数値として、数列生成部CCT<sub>8</sub>や数列生成部CCT<sub>1~6</sub>が生成する固定長／可変長の数値が活用される。そして、8

10

20

30

40

50

ビット可変長や 16 ビット可変長の数値は、例えば、普通図柄表示部 19 に表示する普通図柄を決定する用途や、その他の用途で使用される。

#### 【 0183 】

その他の用途としては、例えば、電動式チューリップ（電チュー）の開放パターンの抽選決定が考えられる。この場合、電チューの開放パターンとして、開放回数（3 回 / 4 回）や、開放時間（3 秒 / 5 秒）などを適宜に組み合わせた多数の種類が用意され、普通図柄処理 ST28 での当選時に、その何れかが抽選決定される。

#### 【 0184 】

また、実施例では、信号入力レジスタ 35f の記憶値に基づいて、入賞スイッチ信号 SG の ON / OFF 状態を判定したが、入賞スイッチ信号 SG を、通常の入力ポート INP に供給する構成を探れば、入力ポート INP からの取得値に基づいて、入賞スイッチ信号 SG の ON / OFF 状態を判定することができる。10

#### 【 0185 】

このような場合には、必ずしも、乱数生成回路 GNR に入賞スイッチ信号 SG を供給する必要はなく、入賞スイッチ信号 SG が ON 状態であると判定される場合に、乱数レジスタ 35a, 35c の数値を取得して抽選用乱数値とすれば良い。なお、入力ポート INP から取得した入賞スイッチ信号 SG が、ON 状態又は OFF 状態であると判定するに当って、ノイズ対策として、複数回の割込み処理において、入賞スイッチ信号 SG が同一レベルであることを条件としても良い。

#### 【 0186 】

何れにしても、乱数生成回路 GNR に入賞スイッチ信号 SG を供給しない構成を探ると、ラッチ回路 34G やラッチレジスタ 35b, 35d は機能しないが、本実施例では、数列生成部 41a, 41b の出力を受ける乱数レジスタ 35a, 35c が設けられているので問題が生じない。20

#### 【 0187 】

ところで、図 10 に示す実施例では、特別図柄処理（ST32）において、乱数生成回路 GNR の乱数レジスタ 35a, 35c の数値を取得して抽選処理を実行したが、乱数レジスタ 35a, 35c に代えて、ラッチレジスタ 35b, 35d の数値を活用しても良いのは勿論である。そして、この場合には、図 10 に示す実施例と同様、図柄始動口 15 に関する入賞スイッチ信号 SG は、乱数生成回路 GNR の信号入力レジスタ 35f をアクセスして取得するのが好ましい（ST23 参照）。30

#### 【 0188 】

図 11 は、ラッチレジスタ 35b, 35d の数値を取得して抽選処理を実行する実施例を説明する図面であり、図 6(A) と図 6(B) のタイムチャートを、上書き禁止モード及び上書き許可モードについて纏めたものである。なお、図示例では、入賞スイッチ信号 SG が OFF 状態となってから、ラッチレジスタ 35b, 35d の値が、CPU に取得されるが（図 11 の右端下部 read 参照）、特に限定されない。

#### 【 0189 】

以上を踏まえて説明すると、入賞スイッチ信号 SG（図 11(a)）が ON 状態であると、ラッチパルス LT は、例えば、更新クロック の 128 個 (= 128) 毎に出力される（図 11(d)）。また、入賞スイッチ信号 SG の ON / OFF レベルは、例えば、更新クロック の 128 個分程度（128）の遅延時間を経て、信号入力レジスタ 35f に記憶される。なお、更新クロック の周波数が 10MHz であれば、遅延時間は、ほぼ 12.8 μs である。40

#### 【 0190 】

そのため、信号入力レジスタ 35f を定時的に繰り返しアクセスして、その記憶値の ON エッジを確認し、直ちに、ラッチレジスタ 35b, 35d のラッチデータを読み出す構成を探る場合（図 10 の ST23, ST32 参照）には、入賞スイッチ信号 SW の ON エッジに極めて近いタイミング (+ 12.8 μs) の乱数値を取得することができる。この点は、動作モードが、上書き禁止モードであるか、上書き許可モードであるかに拘わらず50

、図11(f)や図11(g)に示す数列生成部41の更新値(数値Xや数値Y)が、抽選用の乱数値としてCPUに取得される。

#### 【0191】

なお、図11(d)、図11(e)、図11(f)の関係から確認される通り、上書き禁止モードでは、CPUの乱数値を取得タイミングが如何に遅れても、最初のラッチパルスLTのタイミングの更新値Xが取得される。

#### 【0192】

なお、ここでは、信号入力レジスタ35fを定期的に繰り返しアクセスして、その記憶値のONエッジを確認して特別図柄処理(ST32)を実行する構成を説明したが、何ら限定されず、信号入力レジスタ35fの記憶値のOFFエッジを確認することを条件に、特別図柄処理(ST32)を実行しても良い。10

#### 【0193】

上書き禁止モードを探る場合には、このような構成でも、入賞スイッチ信号SWのONエッジに極めて近いタイミング(+12.8μS)の乱数値(数値X)を取得することができる。一方、上書き許可モードを探る場合には、入賞スイッチ信号SWのOFFエッジに極めて近いタイミングの乱数値(数値Z)を取得することができる。

#### 【0194】

そして、信号入力レジスタ35fの記憶値のOFFエッジを確認する構成を探る場合には、上書き禁止モードであるか、上書き許可モードであるかに拘わらず、入賞スイッチ信号SG(図11(a))が確実に立下った後に、ステータスレジスタのステータス値(ラッチ情報)がOFFレベルとなるので(図11(h)のreadタイミング参照)、入賞スイッチ信号SGのON時間が如何に長くても、ラッチレジスタ(35b, 35dなど)を重複してアクセスしてしまうおそれがない。すなわち、CPUによる乱数取得タイミング(図11のread)の後は、ラッチパルスLTが出力されることないので、ステータスレジスタ35eのステータス値(ラッチ情報)が改めてON状態となることはなく、したがって、乱数取得処理の重複実行のおそれがない。20

#### 【0195】

また、本発明の適用は、弾球遊技機に限定されるものではなく、回胴遊技機を含む各種の遊技機に適用可能である。

#### 【符号の説明】

#### 【0196】

|         |           |

|---------|-----------|

| G M     | 遊技機       |

| 2 1     | 主制御手段     |

| 2 1 A   | ワンチップマイコン |

| S G     | スイッチ信号    |

| C L K   | システムクロック  |

| X C L K | 外部クロック    |

| G N R   | 乱数生成手段    |

| 3 3 G   | 数値更新手段    |

| 3 4 G   | ラッチ手段     |

| 3 0     | パルス出力手段   |

| 3 5 f   | 信号取得手段    |

| 3 5 b   | 乱数取得手段    |

203040

【 図 1 】

【 四 3 】

【 図 2 】

【 図 4 】

【図5】

【 四 6 】

【図7】

【四 8】

【図9】

【図10】

【図11】

---

フロントページの続き

(56)参考文献 特開2010-17337(JP,A)

特開2006-20880(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 6 3 F      7 / 0 2

A 6 3 F      5 / 0 4