(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6803859号

(P6803859)

(45) 発行日 令和2年12月23日(2020.12.23)

(24) 登録日 令和2年12月3日(2020.12.3)

(51) Int.Cl.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>G06F</b> | <b>13/24</b> | <b>(2006.01)</b> | G06F | 13/24 | 310Z |

| <b>G06F</b> | <b>15/78</b> | <b>(2006.01)</b> | G06F | 15/78 | 599  |

| <b>G06F</b> | <b>13/10</b> | <b>(2006.01)</b> | G06F | 13/10 | 330A |

|             |              |                  | G06F | 13/10 | 330B |

|             |              |                  | G06F | 13/24 | 310F |

請求項の数 19 (全 19 頁) 最終頁に続く

(21) 出願番号 特願2017-565127 (P2017-565127)

(86) (22) 出願日 平成28年5月6日 (2016.5.6)

(65) 公表番号 特表2018-518773 (P2018-518773A)

(43) 公表日 平成30年7月12日 (2018.7.12)

(86) 國際出願番号 PCT/GB2016/051310

(87) 國際公開番号 WO2016/203193

(87) 國際公開日 平成28年12月22日 (2016.12.22)

審査請求日 平成31年4月26日 (2019.4.26)

(31) 優先権主張番号 1510597.6

(32) 優先日 平成27年6月16日 (2015.6.16)

(33) 優先権主張国・地域又は機関

英國(GB)

(73) 特許権者 513183153

ノルディック セミコンダクタ アーエス

アー

N o r d i c S e m i c o n d u c t o

r A S A

ノルウェー王国、エヌ-7004 トロン

ハイム、オットー ニールセンス ヴェー

グ 12

(74) 代理人 110001807

特許業務法人磯野國際特許商標事務所

(72) 発明者 ルステン、ヨール オライ

ノルウェー王国、7052 トロントハイ

ム、オットー ニールセンス ヴェーグ

12、ノルディック セミコンダクタ ア

ーエスアー 内

最終頁に続く

(54) 【発明の名称】 イベント発生装置

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサと、

複数個の周辺機器と、

プログラマブル周辺機器相互接続器と、

イベント発生装置と、

ソフトウェアを記憶するメモリと、を備えたマイクロコントローラであって、

前記イベント発生装置は、前記プロセッサによってアドレス可能なイベント発生レジスタを備え、

前記イベント発生装置は、前記プログラマブル周辺機器相互接続器に接続され、

前記イベント発生装置は、前記イベント発生レジスタの内容に対する所定の変更を検出することができて、このような所定の変更を検出すると前記プログラマブル周辺機器相互接続器にイベントを伝えるように設定され、

前記周辺機器の各々は、前記プログラマブル周辺機器相互接続器に接続され、

前記周辺機器の各々は、それぞれのタスクを実行することによって前記プログラマブル周辺機器相互接続器からのタスク信号に対処するように構成され、

前記プログラマブル周辺機器相互接続器は、各々が前記イベント発生装置のイベントを前記周辺機器の一つに属するタスクにマッピングさせる複数のマッピング関係を格納できるマッピングメモリにアクセスするように構成され、

前記プログラマブル周辺機器相互接続器は、前記イベント発生装置のイベントから前記

10

20

周辺機器の一つに属するタスクへのマッピング関係が前記マッピングメモリに格納されているとき、前記プログラマブル周辺機器相互接続器がタスク信号を前記周辺機器に送信することによって前記イベント発生装置からのイベントの信号に対処するように構成され、

前記プログラマブル周辺機器相互接続器は、前記マッピングメモリが前記イベント発生装置の一つのイベントから二つ以上の異なるタスクへのマッピング関係を格納しているとき、前記イベントの信号を受信してから所定の最大時間内に前記二つ以上のタスク信号をそれぞれ送信するように構成され、

前記ソフトウェアは、(i) 前記イベント発生装置の一つのイベントから少なくとも二つの異なる周辺機器タスクへのマッピング関係を前記マッピングメモリに格納し、(ii) 前記イベント発生レジスタの前記内容に対する前記所定の変更を行うための、前記プロセッサによって実行可能な命令を含み、10

前記イベント発生装置は、タイミング機構を有さず、

前記イベント発生装置は、入力については、(i) クロック入力、および一つ以上の入力レジスタだけから入力するか、(ii) クロック入力、一つ以上の入力レジスタ、および一つ以上のタスク回線だけから入力するか、のいずれかであり、

前記イベント発生装置は、出力については、(i) 前記プログラマブル周辺機器相互接続器への一つ以上のイベント回線だけに出力するか、(ii) 前記プログラマブル周辺機器相互接続器への一つ以上のイベント回線、および前記プロセッサへの一つ以上の割り込み回線だけに出力するか、(iii) 前記プログラマブル周辺機器相互接続器への一つ以上のイベント回線、および一つ以上の出力レジスタだけに出力するか、(iv) 前記プログラマブル周辺機器相互接続器への一つ以上のイベント回線、前記プロセッサへの一つ以上の割り込み回線、および一つ以上の出力レジスタだけに出力するか、のいずれかである20

ことを特徴とするマイクロコントローラ。

#### 【請求項 2】

前記所定の最大時間は、10マイクロ秒以下である

ことを特徴とする、請求項1に記載のマイクロコントローラ。

#### 【請求項 3】

前記プログラマブル周辺機器相互接続器は、それぞれの前記二つ以上のタスク信号を同時に送信するように設定される

ことを特徴とする、請求項1または2に記載のマイクロコントローラ。30

#### 【請求項 4】

起こり得るすべてのマッピング関係について、前記プログラマブル周辺機器相互接続器がイベントの信号を受信してから前記イベントにマッピングされた二つ以上のタスク信号を送信するまでに一定の時間遅延が存在する

ことを特徴とする、請求項3に記載のマイクロコントローラ。

#### 【請求項 5】

イベントを前記プログラマブル周辺機器相互接続器に伝えるように構成された、イベント発生を行う一つ以上の周辺機器を備え、前記プログラマブル周辺機器相互接続器は、第一周辺機器のイベントと第二周辺機器のタスクとの間のマッピング関係が前記マッピングメモリに格納されていると、前記第一周辺機器からの前記イベントの信号に対処して前記第二周辺機器にタスク信号を送信することによってチャンネルを形成するように設定される40

ことを特徴とする、請求項1乃至請求項4のいずれかに記載のマイクロコントローラ。

#### 【請求項 6】

前記イベント発生装置は、複数の異なるイベントを伝えるように設定される

ことを特徴とする、請求項1乃至請求項5のいずれかに記載のマイクロコントローラ。

#### 【請求項 7】

前記イベント発生装置は、前記プロセッサによってアドレス可能な複数のイベント発生レジスタを有しており、各イベント発生レジスタは、それぞれ異なるイベントと関係付けられる50

ことを特徴とする、請求項 6 に記載のマイクロコントローラ。

【請求項 8】

前記イベント発生装置は、前記プログラマブル周辺機器相互接続器からタスク信号を受信できる

ことを特徴とする、請求項 1 乃至請求項 7 のいずれかに記載のマイクロコントローラ。

【請求項 9】

前記プログラマブル周辺機器相互接続器は、イベントおよびタスクごとのそれぞれの回線によって前記周辺機器および前記イベント発生装置に接続される

ことを特徴とする、請求項 1 乃至請求項 8 のいずれかに記載のマイクロコントローラ。

【請求項 10】

前記イベント発生装置は、前記プロセッサによってアドレス可能で前記イベント発生装置のイベントと関係付けられた、少なくとも一つのイベントレジスタを備える

ことを特徴とする、請求項 1 乃至請求項 9 のいずれかに記載のマイクロコントローラ。

【請求項 11】

前記イベントレジスタは、前記イベント発生レジスタとは別個であり、前記イベント発生装置は、前記イベント発生レジスタの内容に対して所定の変更が行われると前記イベントレジスタの内容に対して所定の変更がもたらされるように構成される

ことを特徴とする、請求項 10 に記載のマイクロコントローラ。

【請求項 12】

イベントを伝えるときに割り込みを前記プロセッサに送信するための回路を備える

ことを特徴とする、請求項 1 乃至請求項 11 のいずれかに記載のマイクロコントローラ

。

【請求項 13】

各々が割り込み回線群によって前記プロセッサに接続された複数のイベント発生装置を備え、各割り込み回線群がそれぞれ異なる割り込み優先レベルを有する

ことを特徴とする、請求項 1 乃至請求項 12 のいずれかに記載のマイクロコントローラ

。

【請求項 14】

プロセッサと、

複数の周辺機器と、

プログラマブル周辺機器相互接続器と、

割り込み発生装置と、を備えたマイクロコントローラであって、

前記周辺機器のうちのイベント発生周辺機器は、前記プログラマブル周辺機器相互接続器にイベントを伝えるように構成され、

前記割り込み発生装置は、前記プログラマブル周辺機器相互接続器からタスク信号を受信すると、前記プロセッサに割り込みを送信するように設定され、

前記プログラマブル周辺機器相互接続器は、( i ) 前記イベント発生周辺機器のイベントと( ii ) 前記割り込み発生装置との間のマッピング関係を格納できるマッピングメモリにアクセスするように構成され、

前記プログラマブル周辺機器相互接続器は、前記イベント発生周辺機器のイベントと前記割り込み発生装置のタスクとの間のマッピング関係が前記マッピングメモリに格納されていると、前記タスクの実行を求めるタスク信号を前記割り込み発生装置に送信して前記割り込み発生装置に前記プロセッサへの割り込みを送信されることによって前記イベント発生周辺機器からの前記イベントの信号に対処するように構成され、

前記割り込み発生装置は、タイミング機構を有さず、

前記割り込み発生装置は、入力については、( i ) クロック入力、および一つ以上の入力レジスタだけから入力するか、( ii ) クロック入力、一つ以上の入力レジスタ、および一つ以上のタスク回線だけから入力するか、のいずれかである

ことを特徴とするマイクロコントローラ。

【請求項 15】

10

20

30

40

50

前記割り込み発生装置は、イベント発生レジスタの内容に対する所定の変更を検出するように設定され、当該の所定の変更を検出すると、前記プログラマブル周辺機器相互接続器にイベントを伝えるイベント発生装置もある

ことを特徴とする、請求項14に記載のマイクロコントローラ。

#### 【請求項16】

前記割り込み発生装置は、前記タスク信号を受信してから所定の最大時間内に前記割り込みを送信するように設定される

ことを特徴とする、請求項14または15に記載のマイクロコントローラ。

#### 【請求項17】

前記割り込み発生装置は、前記タスク信号の受信後に一定時間遅延してから前記割り込みを送信するように設定される

10

ことを特徴とする、請求項14乃至請求項16のいずれかに記載のマイクロコントローラ。

#### 【請求項18】

各々が割り込み回線群によって前記プロセッサに接続された複数の割り込み発生装置を備え、各割り込み回線群がそれぞれ異なる割り込み優先レベルを有する

ことを特徴とする、請求項14乃至請求項17のいずれかに記載のマイクロコントローラ。

#### 【請求項19】

前記プロセッサによって実行可能であって、前記イベント発生周辺機器のイベントから前記割り込み発生装置のタスクへのマッピング関係を前記マッピングメモリに格納する命令を含むソフトウェアを格納するメモリを備える

20

ことを特徴とする、請求項14乃至請求項18のいずれかに記載のマイクロコントローラ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、マイクロコントローラに関する。

##### 【背景技術】

##### 【0002】

マイクロコントローラは、多くの場合、無線デバイスなどのタイミングが重要な用途に使用される。一つ以上の周辺機器に関する二つのタスクがマイクロコントローラのプロセッサから原則として同時に起動されることが重要となり得る場合がある。当該デバイスは、例えば、シリアルインターフェース経由の通信を起動すると共に、正確に同時にタイマをスタートさせる必要があることがある。この処理は、通常、最初のタスクを起動するようプロセッサに命令し、その直後に他のタスクを起動するようプロセッサに命令することによって行われる。しかしながら、たとえこれらの処理が隣り合うソフトウェア命令を使用して実行されたとしても、プロセッサが、最初のタスクをトリガした後であるが二番目のタスクをトリガする前に割り込みを受信することが起こり得る。これは、望ましくない動作につながることがある。

30

##### 【0003】

この問題は、緊急時には特定の割り込みをマスクしたり、異なる割り込みには異なる優先順位を設定したりすることによって、ある程度軽減することができる。しかし、これらの手法のいずれも完全ではなく、ソフトウェアもその分だけ複雑になる。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0004】

本発明は、上述した手法の代わりとなる手法を提供するものである。

##### 【課題を解決するための手段】

##### 【0005】

40

50

第一の態様からみると、本発明は、

プロセッサと、

複数の周辺機器と、

プログラマブル周辺機器相互接続器と、

イベント発生装置と、

ソフトウェアを格納するメモリと、を備えたマイクロコントローラを提供するものであ

つて、

前記イベント発生装置は、前記プロセッサによってアドレス可能なイベント発生レジス

タを備え、

前記イベント発生装置は、前記プログラマブル周辺機器相互接続器に接続され、

10

前記イベント発生装置は、前記イベント発生レジスタの内容に対する所定の変更を検出

することができて、このような所定の変更を検出すると前記プログラマブル周辺機器相互

接続器にイベントを伝えるように設定され、

前記周辺機器の各々は、前記プログラマブル周辺機器相互接続器に接続され、

前記周辺機器の各々は、それぞれのタスクを実行することによって前記プログラマブル

周辺機器相互接続器からのタスク信号に対処するように構成され、

前記プログラマブル周辺機器相互接続器は、各々が前記イベント発生装置のイベントを

前記周辺機器の一つに属するタスクにマッピングさせる複数のマッピング関係を格納でき

るマッピングメモリにアクセスするように構成され、

前記プログラマブル周辺機器相互接続器は、前記イベント発生装置のイベントから前記

周辺機器の一つに属するタスクへのマッピング関係が前記マッピングメモリに格納されて

いるとき、前記プログラマブル周辺機器相互接続器がタスク信号を前記周辺機器に送信す

ることによって前記イベント発生装置からのイベントの信号に対処するように構成され、

20

前記プログラマブル周辺機器相互接続器は、前記マッピングメモリが前記イベント発生

装置の一つのイベントから二つ以上の異なるタスクへのマッピング関係を格納しているとき、

前記イベントの信号を受信してから所定の最大時間内に前記二つ以上のタスクの信号

をそれぞれ送信するように構成され、

前記ソフトウェアは、( i ) 前記イベント発生装置の一つのイベントから少なくとも二

つの異なる周辺機器タスクへのマッピング関係を前記マッピングメモリに格納し、( ii )

前記イベント発生レジスタの前記内容に対する前記所定の変更を行うための、前記プロ

セッサによって実行可能な命令を含む。

30

#### 【 0 0 0 6 】

したがって、本発明によれば、前記ソフトウェアが実行されると、二つ以上の周辺機器

タスクがアトミックに、かつ、所定の最大時間枠内にトリガされることが当業者であれば

理解されるであろう。単一のプロセッサ書き込み命令のみを使用して前記周辺機器タスク

を起動するので、二つの前記周辺機器タスクをトリガすることがプロセッサ割り込みによ

って中断されるリスクは存在しない。

#### 【 0 0 0 7 】

前記所定の最大時間は、任意の値を有することができるが、10マイクロ秒以下である

のが好ましく、より好ましくは1マイクロ秒以下であって、最も好ましくは0.1マイク

ロ秒以下である。前記所定の最大時間は、二つ以上のタスクが実用上同時にトリガされる

ものとみなすことができるよう、十分に小さいことが好ましい。前記所定の最大時間は

、100プロセッサクロックサイクル未満であってもよく、より好ましくは10または5

クロックサイクル未満であってもよい。いくつかの実施形態においては、1プロセッサク

ロックサイクル未満であってもよい。前記所定の最大時間は、すべてのマッピング関係に

対して一定であることが好ましい。前記プログラマブル周辺機器相互接続器は、それ

ぞの前記二つ以上のタスク信号を同時（例えば、前記プログラマブル周辺機器相互接続器

または前記プロセッサに供給されるクロック信号の1サイクル内）に送信するように設定さ

れることが好ましい。この場合は、起こり得るすべてのマッピング関係について、前記ブ

ログラマブル周辺機器相互接続器がイベントの信号を受信してから当該イベントにマッピ

40

50

ングされた二つ以上のタスク信号を送信するまでに一定の時間遅延が存在することが好ましい。

#### 【0008】

前記プログラマブル周辺機器相互接続器は、例えば、本出願人による国際公開WO 2013/088121号に記載されているように、既に公知である。いくつかの好ましい実施形態において、前記プログラマブル周辺機器相互接続器は、その内容全体が参照により本明細書に組み込まれた国際公開WO 2013/088121号に記載されているプログラマブル周辺機器相互接続器と、必須ではないが、実質的に同一である。

#### 【0009】

前記プログラマブル周辺機器相互接続器は、周辺機器間チャンネルのプログラミングもサポートすることが好ましい。いくつかの実施形態において、前記マイクロコントローラは、イベントを前記プログラマブル周辺機器相互接続器（PPI）に伝えるように構成された、イベント発生が可能な一つ以上の周辺機器も備える。前記プログラマブル周辺機器相互接続器は、第一周辺機器のイベントと第二周辺機器のタスクとの間のマッピング関係を格納することができ、第一周辺機器のイベントと第二周辺機器のタスクとの間のマッピング関係がメモリに格納されると、相互接続が第一周辺機器からのイベントの信号に対処して第二周辺機器にタスク信号を送信することによってチャンネルを形成できるように設定されることが好ましい。このようにして、前記プログラマブル周辺機器相互接続器は、イベント発生周辺機器とインターフェースをとるのと同じように、前記イベント発生装置と適宜インターフェースをとってもよい。いくつかの実施形態において、前記イベント発生装置は、一種のイベント発生周辺機器とみなしてもよい。

10

#### 【0010】

前記周辺機器は、何らか特定のタイプのものに限定されず、例えば、タイマ、U A R T、電圧比較器、暗号エンジン、アナログデジタル変換器（A D C）、デジタルアナログ変換器（D A C）、無線送信機、無線受信機などの周辺機器を含んでもよい。当業者によく知られているように、何らかの入力、状態変化、基準を満たすなどが発生すると、例えば、タイマが目標値に到達すると、周辺機器からイベントが知らされてもよい。前記タスクは、インターフェースを介してデータを送信するなど、前記周辺機器によって実行できる何らかの機能または動作であってもよい。

20

#### 【0011】

前記イベント発生装置は、単一タイプのイベントのみを伝えるように設けてもよいが、複数の異なるイベントを伝えられるのが好ましい。これらのイベントは、それぞれ異なるイベント回線を介するかそれぞれ異なるイベントレジスタを使用して知らされてもよい。前記イベント発生装置は、前記プロセッサによってアドレス可能な複数のイベント発生レジスタを有してもよい。各イベント発生レジスタは、それぞれ異なるイベントと関係付けられてもよい。前記異なるイベントは、例えば、前記イベント発生レジスタのアドレスを識別子として使用したり何か別の所定の一連の識別子を使用したりすることによって、格納されたマッピング関係の中で一意的に識別され得ることが好ましい。

30

#### 【0012】

従来の周辺機器のようにイベントが当該周辺機器における何らかの状態変化（例えば、何らかの動作の完了）を表すのとは違って、前記イベント発生装置からのイベントは、固有の意味を有さない代わりに、前記プロセッサ（または他の構成要素）が当該イベントを前記イベント発生レジスタに書き込むことによって意味が付与されることが理解されるであろう。

40

#### 【0013】

前記PPIは、イベント信号およびタスク信号を送信できる、イベントおよびタスクごとのそれぞれの回線、すなわち、各イベントまたはタスクごとに一つの回線、によって前記周辺機器および／または前記イベント発生装置に接続してもよい。前記イベント信号およびタスク信号は、パルスまたは符号化された値であってもよい。入力回線は、前記PPI内部の一つ以上のマルチプレクサに、例えば、チャンネルごとに一つのマルチプレクサ

50

に、接続されてもよい。出力回線は、前記 PPI 内部の一つ以上のデマルチプレクサから、例えば、チャンネルごとに一つのデマルチプレクサから、出されてもよい。前記 PPI は、メモリに格納されたマッピング関係に従ってチャンネルのマルチプレクサおよびデマルチプレクサを設定したり制御したりするように構成してもよい。

#### 【0014】

いくつかの実施形態において、前記 PPI は、例えば、メモリマップド I/O (MMIO) を使用するアドレスバスを介するなど、バスを介して、前記周辺機器および / または前記イベント発生装置のタスクレジスタか、前記イベントレジスタか、または両者にアクセスしてもよい。したがって、前記 PPI は、関係付けられた前記イベントレジスタの内容変更を通じてイベント信号を受信してもよいし、および / または、関係付けられた前記タスクレジスタの内容を変更することによってタスク信号を送信してもよい。前記 PPI は、前記プロセッサも接続されるバス（例えば、アドレスバス、データバス、および制御バスから成るシステムバス）に接続してもよい。同じバスで、前記周辺機器および / または前記イベント発生装置を前記プロセッサに接続してもよい。前記 PPI は、例えば、定期的にポーリングするなど周期的に前記イベントレジスタを読み出したり、前記イベント発生周辺機器または前記イベント発生装置からの割り込みを受信したりして、イベントレジスタの内容変更を検出してもよい。前記 PPI は、割り込みを受信すると、対応するイベントレジスタの内容を読み出してもよい。

10

#### 【0015】

イベントレジスタまたはタスクレジスタは、単一ビット（つまり、フラグまたはバイナリ信号を伝えるために）を含んでもよいし、例えば 8、16 または 32 ビットなど複数のビットを含んでもよい。

20

#### 【0016】

前記イベント発生装置は、イベント信号回線を介して前記プログラマブル周辺機器相互接続器（PPI）にイベントを伝えてよい。あるいは、レジスタに対する変更を通じて前記イベントを伝えてよく、この場合に前記 PPI は前記変更を検出するため、周期的に前記レジスタをポーリングするように構成されてもよい。このレジスタは、前記イベント発生レジスタそれ自体であってもよいし、前記イベント発生装置用の別個のイベントレジスタであってもよい。

30

#### 【0017】

いくつかの実施形態において、マッピング関係内のタスク識別情報は、国際公開 WO 2013/088121 号に記載されているように、前記タスクと関係付けられた、タスクレジスタのアドレスである。しかしながら、これは必須ではなく、タスク受信側周辺機器のタスク識別情報は、例えば、(i) 周辺機器識別子と、(ii)（前記周辺機器に存在するか否か分からぬ）関係付けられたタスクレジスタのアドレスとは無関係な、タスク識別子または信号回線識別子と、を含んでもよい。

#### 【0018】

タスク受信側周辺機器は、前記プロセッサによってアドレス可能でタスクと関係付けられたタスクレジスタを備え、前記タスクレジスタの内容変更が発生すると当該タスクを実行するように構成されてもよい。したがって、第一周辺機器のイベントと第二周辺機器のタスクとの間のマッピング関係は、(i) 前記第一周辺機器の前記イベントの識別情報と、(ii) 前記タスクと関係付けられたタスクレジスタのアドレスと、を含んでもよい。前記 PPI は、第一周辺機器のイベントと第二周辺機器のタスクとの間のマッピング関係がメモリに格納されていれば、前記第一周辺機器から前記イベント信号を受信すると前記第二周辺機器にタスク信号を送信することによってチャンネルを形成するように構成されてもよい。

40

#### 【0019】

イベント発生側周辺機器は、前記プロセッサによってアドレス可能でイベントと関係付けられたイベントレジスタを備えてよい。前記イベントレジスタは、前記周辺機器と関係付けられて集積回路上で直接隣接した論理回路に配置されてもよいが、これは必須では

50

なく、前記周辺機器の他の構成要素からある程度離れて据え付けられてもよい。これはタスクレジスタにもあてはまる。前記した両レジスタは、任意の適切なメモリ構造を備えていてもよい。前記周辺機器は、イベントを伝えるとき、例えば、イベントを伝えるときは常に前記イベントレジスタにバイナリ「1」を書き込むことによって、前記イベントレジスタの内容を変更してもよい。

#### 【0020】

いくつかの実施形態において、マッピング関係にある第一周辺機器のイベント識別情報は、前記イベントと関係付けられたイベントレジスタのアドレスである。このようにすれば、二つのレジスタアドレス、すなわち、イベントレジスタアドレスおよびタスクレジスタアドレスをメモリに格納するだけで、チャンネルを構成することができる。前記プロセッサで実行されるソフトウェアは、機能呼出しを介してこの格納処理を実行するかもしれないし、当該マッピング関係が格納されている前記メモリにアドレスを直接に書き込むかもしれない。必須ではないが、前記第一周辺機器の前記イベント識別情報は、存在するか否か分からぬ、関係付けられたイベントレジスタのアドレスとは無関係な、周辺機器識別子およびイベント、または信号回線識別子を含むことができる。10

#### 【0021】

前記イベント発生装置は、前記プロセッサによってアドレス可能で前記イベント発生装置のイベントと関係付けられた少なくとも一つのイベントレジスタを備えることが好ましい。いくつかの実施形態において、前記イベント発生レジスタは、前記イベントレジスタである。他の実施形態において、前記イベントレジスタは、前記イベント発生レジスタとは別個である（すなわち、異なるアドレスを有する）。前記イベント発生装置は、前記イベント発生レジスタに対して所定の変更が行われると前記イベントレジスタに対して所定の変更をもたらすことができるように構成してもよい。いくつかの実施形態において、前記イベント発生レジスタは、前記イベント発生装置用のタスクレジスタであってもよい。前記イベント発生装置は、複数のイベント発生レジスタおよび複数のイベントレジスタを備えてもよい。各イベント発生レジスタは、前記イベント発生レジスタの一つに対して変更が行われると前記イベントレジスタのうち関係付けられた一つに対して変更をもたらすように、前記イベントレジスタのそれぞれと関係付けられてもよい。20

#### 【0022】

前記イベント発生装置は、例えば、特定のイベントを伝える前に、おそらく所定の順番で、二つの異なるイベント発生レジスタ内の所定の変更を必要とするような、二つ以上のイベント発生レジスタを一つのイベントと関係付ける論理回路を含んでもよい。換言すれば、前記イベント発生装置は、二つ以上のイベント発生レジスタに関する基準が満たされると、またはその場合のみ、イベント信号を送信する論理回路を含んでもよい。このような論理回路は、固定（すなわち、配線接続）されてもよいし、プログラマブルであってもよい。30

#### 【0023】

いくつかの実施形態において、前記イベント発生装置は、前記プログラマブル周辺機器相互接続器からタスク信号を（例えば、タスク回線を介して、または前記イベント発生レジスタの内容に対して変更を行うことによって）受信し、前記プログラマブル周辺機器相互接続器にイベントを伝えることによって対処することができる。こうすれば、より詳細を以下に説明するように、前記イベント発生装置が、イベントを伝えるときに割り込みも前記プロセッサに送信するように構成される場合に、有用であり得る。40

#### 【0024】

前記イベント発生装置のイベントは、前記イベント発生周辺機器のイベントが識別されるのと同じように、例えば、関係付けられたイベントレジスタのアドレスによって、または前記イベントに特有の何か他の識別子によって、マッピング関係内で識別してもよい。

#### 【0025】

前記PPIは、一つ以上のマッピング関係を使用して周辺機器間の接続を規定するようにプログラムされるか構成されるという意味においてプログラマブルである。前記PPI50

は、ソフトウェア命令を実行するために自らの処理装置を備えてもよいが、必ずしもそうする必要はない。

#### 【0026】

前記マッピングメモリにあるマッピング関係は、任意の適切な書式で記載されてもよい。いくつかの実施形態において、イベントレジスタのアドレスおよびタスクレジスタのアドレス、またはこれらのレジスタへのポインタが、配列や表やデータベース内の関連項目として格納されてもよい。例えば、前記PP1は、各々が異なるチャンネルに対応する多くの行と、イベントレジスタを識別する第一列およびタスクレジスタを識別する第二列からなる二つの列を有する表を保持してもよい。このような配列や表は論理的構築物であってもよく、メモリ内のデータの何らかの特定の物理的位置に必ずしも限定される必要はないことが理解されるであろう。前記PP1は、タスクレジスタのアドレスを格納するための第一レジスタ群およびイベントレジスタのアドレスを格納するための第二レジスタ群を備えてもよい。各群には等しい数のレジスタが存在してもよい。第一レジスタ群のレジスタは、第二レジスタ群の対応するレジスタによって管理されるデマルチプレクサに接続されるマルチプレクサを管理することによって、チャンネルを規定してもよい。10

#### 【0027】

前記メモリは、例えば、シリコンチップの別個の領域または異なるチップ上にあるなど、前記PP1から独立していてもよいが、アクセス時間を短縮できる、前記PP1と一体化された構成要素であることが好ましい。前記メモリは、揮発性（例えば、RAM）であっても、不揮発性（例えば、EEPROMまたはフラッシュ）であってもよい。前記マッピング関係は、前記プロセッサによってアドレス可能なことが好ましい一つ以上のレジスタに格納されることが好ましい。前記PP1によって形成される各チャンネルは、相互に関係付けられた一つのイベントエンドポイントレジスタおよび一つのタスクエンドポイントレジスタを有してもよく、これらは、それぞれ、イベントレジスタのアドレスおよびタスクレジスタのアドレスを格納するのに適切である。一部の前記チャンネルは、これらのレジスタを使用して他のタイプのイベント識別子および／またはタスク識別子を格納してもよい。20

#### 【0028】

一つ以上の前記マッピング関係が、前記PP1によって、前記プロセッサによって、またはこれらの両方によって前記メモリに書き込まれてもよい。前記プロセッサは、前記PP1に適切な前記マッピング関係を格納するよう命令することによって、周辺機器間のチャンネルを間接的に確立してもよい。30

#### 【0029】

前記PP1は、一つ以上の検索表を含むかアクセスできることが好ましく、この検索表を用いてマッピング関係からレジスタアドレスを検索して、このレジスタアドレスに対応する特定のイベント回線かタスク回線（またはイベントポートかタスクポート）を決定することができる。次に、前記PP1は、（例えば、マルチプレクサまたはデマルチプレクサを適宜管理することによって）チャンネルの入力または出力として当該の回線またはポートを選択してもよい。前記検索表は、任意の適切な書式であればよく、必ずしもメモリ内の物理的な表として実装する必要はない。40

#### 【0030】

前記PP1は、例えば、1、8、16、32またはそれ以上の任意の数のチャンネルをサポートしてもよい。チャンネルは、前記PP1へのイベント入力ポート（回線）と前記PP1からのタスク出力ポート（回線）との間の何らかの物理的な（例えば、電気的な）接続または論理的な接続であってもよい。チャンネルは、（例えば、複数の論理ゲートを用いてチャンネル経路に沿って枝分かれやフォーク状分岐を規定するなど）一つ以上の入力と一つ以上の出力につなげることができる。

#### 【0031】

前記PP1は、チャンネルを有効および／または無効にできる機構を備えることが好ましい。前記PP1は、一つのビットが各チャンネルと関係付けられるビットフィールドレ50

ジスタを備え、前記ビットフィールドレジスタ内の関係付けられたビットが所定の値（例えば、バイナリ 1）に設定された場合にチャンネルを有効にするように構成されてもよい。

#### 【 0 0 3 2 】

イベント発生周辺機器は、二つ以上のイベントレジスタを有してもよい。同様に、タスク受信側周辺機器は、二つ以上のタスクレジスタを有してもよい。

#### 【 0 0 3 3 】

既に説明したように、前記 P P I は、おそらく別々のタスク受信側周辺機器に、二つ以上のタスク信号を送信することによって一つのイベント信号に対処するように構成可能である。いくつかの実施形態では、これを、各々が（例えば、イベントレジスタアドレスによって特定される）イベントを（例えば、それぞれのタスクレジスタアドレスによって特定される）それぞれ別のタスクにマッピングする、複数のマッピング関係を前記マッピングメモリに格納することによって達成してもよい。他の実施形態では、これを、一つのイベントを二つ以上のタスクに直接にマッピングする単一のマッピング関係を格納することによって、例えば、一つの列が前記イベント用であり二つ以上の別の列がそれぞれのタスク用である三つ以上の列を含む表を前記マッピングメモリに格納することによって、達成してもよい。

10

#### 【 0 0 3 4 】

前記イベント発生装置は、前記 P P I への一つ以上のイベント回線、前記プロセッサへのゼロ個以上の割り込み回線、およびゼロ個以上のレジスタ以外の出力は全く有さないことが好ましい。当該装置は、クロック入力、一つ以上のレジスタ、およびゼロ個以上のタスク回線以外の入力は全く有さないことが好ましい。当該装置は、通常、従来の周辺機器よりも遙かに単純である。当該装置は、構成要素の数またはゲートの数という観点で、前記マイクロコントローラにある任意の他の周辺機器よりも小さいことが好ましい。当該装置は、（タイマ周辺機器とは異なり）タイミング機構は全く有しないことが好ましい。当該装置は、（例えば、任意のデータを受信し送信するための、他の構成要素やデバイスへの接続を有する、シリアルインターフェースやデジタルアナログ変換器とは異なり）ゼロ個以上のイベントレジスタ、タスクレジスタ、および構成レジスタ以外のデータ入力機構は全く有しないことが好ましい。

20

#### 【 0 0 3 5 】

30

前記イベント発生装置は、イベントを伝えるときに割り込みを前記プロセッサに送信するための回路を備えてよい。前記割り込みは、マスク可能割り込みであってもマスク不可能割り込みであってもよい。当該割り込みは、特定のイベントを伝えるときに前記プロセッサへの割り込みの送信を有効および／または無効にするための入力を有してもよい。前記イベント発生装置は、前記イベント発生レジスタの内容に対する変更を検出すると割り込みを前記プロセッサに送信するよう前記イベント発生装置を構成するための一つ以上の構成レジスタを備えてよい。当該装置は、マスク可能割り込みおよびマスク不可能割り込みをそれぞれ構成するための別個の構成レジスタを備えてよい。

#### 【 0 0 3 6 】

割り込みを前記プロセッサに送信する能力は、前記イベント発生装置が前記プログラマブル周辺機器相互接続器からタスク信号を受信するための入力端子を備えるときに特に有用である。この結果、周辺機器にイベントが発生すると前記イベント発生装置が割り込みを前記プロセッサに送信することができるよう、前記プログラマブル周辺機器相互接続器をプログラムすることができる。これは、前記周辺機器が割り込み自体を送信できない場合、または前記周辺機器には限られた数の割り込み（例えば、一つの割り込み）しか割り当てられなかった場合、つまり、前記周辺機器からのすべての割り込みは限られた数の割り込みサービスルーティン（例えば、一つの割り込みサービスルーティン）で処理する必要がある場合に、有用であり得る。前記周辺機器は、自分の代わりに前記 P P I および前記イベント発生装置を用いて割り込みを前記プロセッサに送信することによって、前記プロセッサに送信することが可能な（例えば、異なる割り込み番号をもつ）異なる割り込

40

50

みの数を効果的に増やすことができる。こうすれば、割り込みサービスルーティンのプログラミングを簡単にすることができます。また、異なる優先レベルでの割り込みをサポートするプロセッサに対して、前記イベント発生装置を使用することなく前記周辺機器が利用可能であった割り込みレベルの数よりも多い複数の異なる割り込みレベルで周辺機器が当該プロセッサへの割り込みを行うことを可能にすることもできる。

#### 【0037】

例えば、ある周辺機器が、100マイクロ秒ごとに発生する「NEW VALUE」と呼ばれる一つのイベントおよび何か誤りがあるときのみに伝える「ERROR」と呼ばれる別のイベントを有しているとする。しかしながら、当該周辺機器は、一本しか前記プロセッサへの割り込み回線を有さないので、「ERROR」イベントが発生してもより高い優先順位で割り込むことはできない。しかしながら、当該周辺機器からの「ERROR」イベントの信号によって前記PP1が前記イベント発生装置のタスク回線を有効にするよう10に当該周辺機器と前記イベント発生装置との間のPP1チャンネルを構成し、そのタスク回線を介して信号を受信すると高優先順位の割り込みを前記プロセッサに送信するように前記イベント発生装置を設定することによって、当該周辺機器には、「ERROR」割り込みを高優先順位で前記プロセッサに送信する能力を付与することができる。こうすれば、前記プロセッサは、前記「ERROR」イベントに迅速に対処することができる。

#### 【0038】

いくつかの実施形態において、前記マイクロコントローラは、各々が割り込み回線群によって前記プロセッサに接続された複数のイベント発生装置を備え、各割り込み回線群がそれぞれ異なる割り込み優先レベルを有していてもよい。あるいは、一つのイベント発生装置は、第一優先レベルで割り込みを送信するのに使用できる一つ以上のタスク（またはイベント）と、第二優先レベルで割り込みを送信するのに使用できる一つ以上の他のタスク（またはイベント）と、を有してもよい。前記タスク（またはイベント）と前記割り込み優先レベルとの間の関連性は、固定してもよいし、（例えば、前記イベント発生装置の一つ以上のレジスタ値に従って）設定可能であってもよい。

#### 【0039】

前記プログラマブル周辺機器相互接続器に接続された装置を使用してプロセッサ割り込みを発生するこの着想は、それ自体の権利として新規的かつ進歩的であり、したがって、別の態様からみると、本発明は、

プロセッサと、

複数の周辺機器と、

プログラマブル周辺機器相互接続器と、

割り込み発生装置と、を備えたマイクロコントローラを提供するものであって、

前記周辺機器のうちのイベント発生周辺機器は、前記プログラマブル周辺機器相互接続器にイベントを伝えるように構成され、

前記割り込み発生装置は、前記プログラマブル周辺機器相互接続器からタスク信号を受信すると、前記プロセッサに割り込みを送信するように設定され、

前記プログラマブル周辺機器相互接続器は、(i)第一周辺機器のイベントと(ii)前記割り込み発生装置すなわち第二周辺機器のタスクとの間のマッピング関係を格納できるメモリにアクセスするように構成され、

前記プログラマブル周辺機器相互接続器は、第一周辺機器のイベントと前記割り込み発生装置のタスクとの間のマッピング関係がメモリに格納されていると、前記タスク宛のタスク信号を前記割り込み発生装置に送信することによって前記第一周辺機器からの前記イベントの信号に対処するように構成される。

#### 【0040】

先行する態様および実施形態のいずれかの任意の特徴は、この態様の特徴であってもよい。特に、前記割り込み発生装置は、イベント発生装置であってもよい。したがって、イベント発生レジスタの内容に対する所定の変更を検出するように設定され、当該の所定の変更を検出すると、前記プログラマブル周辺機器相互接続器にイベントを伝えてもよい。

10

20

30

40

50

これは、前述したようなイベント発生装置であってもよい。前記割り込み発生装置は、本明細書に記載された前記イベント発生装置の特徴のいずれかを有してもよい。前記プログラマブル周辺機器相互接続器（PPI）は、前述した前記PPIの特徴のいずれかを有してもよい。

#### 【0041】

前記割り込み発生装置は、タスク回線によって前記プログラマブル周辺機器相互接続器に接続され、前記タスク回線を介して前記タスク信号を送信してもよい。その代わりに、前記割り込み発生装置は、前記プログラマブル周辺機器相互接続器によって監視されるタスクレジスタに書き込んでもよい。

#### 【0042】

前記イベント発生周辺機器は、イベント回線を介して前記プログラマブル周辺機器相互接続器にイベントを伝えるように構成してもよい。その代わりに、前記イベント発生周辺機器は、前記プログラマブル周辺機器相互接続器によって監視されるイベントレジスタに書き込んでもよい。

10

#### 【0043】

前記割り込み発生装置は、タスク信号を受信するとすぐに、できれば前記タスク信号を受信してから所定の最大時間内か、タスク信号の受信後に一定時間遅延してから前記割り込みを送信するように設定されることが好ましい。

#### 【0044】

前記マイクロコントローラは、前記プロセッサによって実行可能であって、前記イベント発生周辺機器のイベントから前記割り込み発生装置のタスクへのマッピング関係を前記マッピングメモリに格納する命令を含むソフトウェアを格納するメモリを備えてもよい。

20

#### 【0045】

前記した態様のいずれかにおいて、前記イベント発生レジスタ（単数または複数）は前記イベント発生装置の一部であるが、前記マイクロコントローラでの物理的な位置を限定するものではないことが理解されるであろう。前記イベント発生レジスタは、例えば、バスを介して前記プロセッサからアドレス可能であることが好ましい。当該レジスタは、前記プロセッサによって書き込んだり読み出したりできることが好ましい。各イベント発生レジスタは、メモリの連続領域を占有してもよいし、複数の位置にわたって分散してもよい。本明細書で参照するレジスタは、（おそらく、より大きなビットフィールド内の）单一ビット長のみであってもよいし、複数のビット（例えば、32ビットワード）を含んでもよい。

30

#### 【0046】

前記マイクロコントローラは、RAMおよび／またはフラッシュメモリなどの、揮発性および／または不揮発性メモリから成ることが好ましい。前記メモリの一部は、プログラムコードを格納してもよい。

#### 【0047】

前記プロセッサは、任意の適切なプロセッサであればよい。いくつかの実施形態においては、ARM（登録商標）のCortex（登録商標）シリーズのプロセッサなど、ARM（登録商標）からのプロセッサである。前記マイクロコントローラは、プロセッサバスおよび周辺機器用バスなど、複数のバスを備えてよい。前記イベント発生装置は、一つ以上のバスに接続されることが好ましい。

40

#### 【0048】

前記マイクロコントローラは、動作するためには、当然ながら、例えば水晶発振機、コンデンサなど、いくつかのオフチップ構成要素を必要としてもよいが、集積デバイスであることが好ましい。これらの構成要素は、前記マイクロコントローラの一部とみなすこともできるし、前記マイクロコントローラと区別できるものとみなすことともできる。

#### 【0049】

前記割り込み発生装置や前記イベント発生装置は、前記マイクロコントローラ内で、前記プロセッサと区別できる、別個のハードウェアモジュールであることが好ましい。前記

50

割り込み発生装置や前記イベント発生装置は、本明細書に記載された機能を提供するように設定され、トランジスタ、抵抗、コンデンサなどを含むアナログおよび／またはデジタル構成要素を備えてもよい。前記マイクロコントローラは、当然ながら、タスク回線やイベント回線によって前記プログラマブル周辺機器相互接続器に接続されない他の周辺機器を有してもよい。

#### 【0050】

いくつかの実施形態において、前記マイクロコントローラは、無線送受信機を備える。これは、ラジオオンチップデバイスであってもよい。

#### 【0051】

ここで、ほんの一例として、以下の添付図面を参照しながら、本発明の特定の好ましい実施形態を記載することにする。 10

#### 【図面の簡単な説明】

#### 【0052】

【図1】本発明を具現化する最初のシステムの構成要素を示す概略図である。

【図2】周辺機器レジスタ同士のマッピング関係を格納するメモリ構造を示す表である。

【図3】本発明を具現化する二番目のシステムでPPIに接続された数個の周辺機器の概略図である。 20

【図4】PPI内部の特定のチャンネルに関する構成要素の概略図である。

【図5】イベント発生装置を示す概略図である。

#### 【発明を実施するための形態】

#### 【0053】

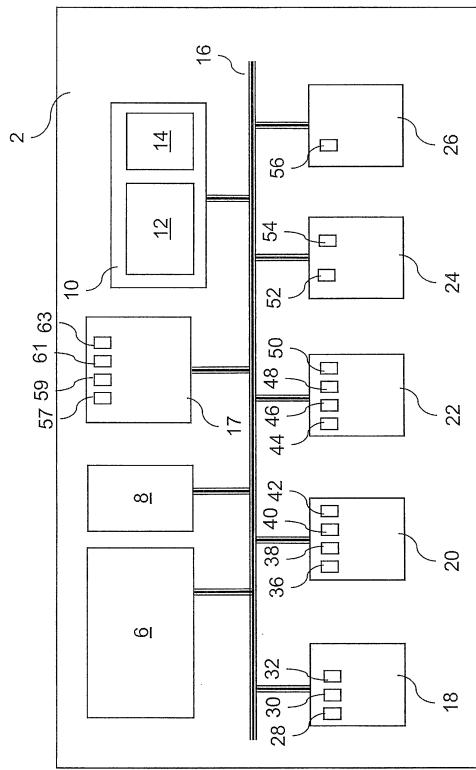

図1は、中央処理装置(CPU)6と、メインメモリ8と、論理エリア12および内部メモリ14を有するPPI10と、を備えるマイクロコントローラ(MCU)2(例えば、集積回路またはマルチチップモジュール)を示す。CPU6とPPI10とは、共にバス16に接続される。

#### 【0054】

バス16にはイベント発生装置17および五つの典型的な周辺機器、すなわち、タイマ18、デジタルアナログ変換器(DAC)20、UART22、ハードウェア暗号エンジン24、電圧比較器26も接続される。 30

#### 【0055】

タイマ18は、出力イベントレジスタ28と、オーバーフローイベントレジスタ30と、入力タスクレジスタ32と、を有する。DAC20は、二つの変換終了イベントレジスタ36、38および二つのトリガタスクレジスタ40、42を有する。UART22は、RX受信イベントレジスタ44と、TX完了イベントレジスタ46と、RXトリガタスクレジスタ48と、TXトリガタスクレジスタ50と、を有する。ハードウェア暗号化エンジン24は、暗号化完了イベントレジスタ52およびトリガタスクレジスタ54を有し、電圧比較器26は、単一コンパレータ出力イベントレジスタ56を有する。一部のレジスタは単一ビットレジスタであり、それ以外のレジスタはマルチビット値を保持することができる。当然ながら、他の実施形態は異なる周辺機器を有し、これらの周辺機器は、任意の数のイベントレジスタまたはタスクレジスタを有してもよい。 40

#### 【0056】

イベント発生装置17は、第一イベントレジスタ57と、第二イベントレジスタ59と、第一タスクレジスタ61と、第二タスクレジスタ63と、を有する。当然ながら、他の実施形態は、異なる数のイベントレジスタまたはタスクレジスタを有してもよい。この実施形態では、イベント発生装置17は、第一タスクが第一イベントをトリガし、第二タスクが第二イベントをトリガするように設定される。他の実施形態では、タスクをイベントにマッピングする、より複雑な論理回路が存在してもよい。

#### 【0057】

周辺機器18～26およびイベント発生装置17のレジスタは、メインメモリ8およびPPIメモリ14からなるメモリアドレス空間を共有し、メモリマップドI/Oを使用し 50

て PPI 論理回路 12、および選択的に CPU6、からこれらのメモリをアクセスすることができる。

#### 【0058】

バス 16 は、図示したように単一バスであってもよいし、二つ以上の別個のバスで形成してもよい。

#### 【0059】

使用中に、CPU6 は、例えば、DAC 変換が完了した後に UART22 がデータを伝送するように、DAC20 変換終了イベントの一つを UART22 トリガタスクにつなぐチャンネルを生成するように PPI10 に命令してもよい。PPI10 は、この命令を受信すると、メモリ 14 に保持された表に新たなエントリを作成して、DAC20 変換終了レジスタ 36 のアドレスと UART22 トリガタスクレジスタ 48 のアドレスとを結び付ける。10

#### 【0060】

CPU6 は、例えば、イベント発生装置 17 の第一イベントレジスタ 57 を UART22 の TX トリガタスクレジスタ 50 につなげるチャンネル、およびイベント発生装置 17 の同じ第一イベントレジスタ 57 をタイマ 18 の入力タスクレジスタ 32 につなげる別のチャンネルを生成するよう PPI10 に命令することもあり得る。こうすれば、CPU6 は、イベント発生装置 17 の第一タスクレジスタ 61 に「1」のビットを書き込むことによって、UART22 が传送を開始するのと同時にタイマ 18 をスタートさせることができる。この処理は、アトミックである、すなわち、CPU6 割り込みによって割り込まれない。20

#### 【0061】

図 2 は、PPI のメモリ 14 に格納され得る典型的な論理データ構造を示す。これは多くの行を有し、各々が、マッピング番号と、イベントレジスタアドレスと、タスクレジスタアドレスと、を含む。

#### 【0062】

PPI 論理回路 12 は、表にリストされたあらゆるイベントレジスタを周期的にポーリングして、レジスタにおける値が変化したときを決定するように構成される。変化を検出すると、PPI 論理回路 12 は、表内で特定のイベントレジスタにマッピングされたすべてのタスクレジスタにその新たな値（またはバイナリ「1」など所定の値）を書き込む。30

#### 【0063】

PPI 論理 12 回路は、選択的に、イベントレジスタ内の新たな値について何らかの処理を行い、その値ではなく、前記処理の結果を一つ以上のタスクレジスタに書き込むように構成してもよい。例えば、イベントレジスタがマルチビット値を含む場合、PPI 論理回路 12 は、以前の値よりも大きいかどうかを判定し、メモリ 14 内のマッピング関係に従って、一つのビットを单一ビットタスクレジスタに書き込むこともあり得る。PPI10 は、（もしいれば）どの処理を CPU6 に実行させるかについて命令されることもある。処理のタイプは、別の列としてマッピング表内に格納してもよい。

#### 【0064】

CPU6 は、チャンネルを無効化したい場合、PPI のメモリ 14 に格納された表内の関連するエントリを消去させることによって直接的にこれを実施できる。（当然ながら、状況次第では命令してもよいが）周辺機器に直接に命令する必要はない。40

#### 【0065】

図 3～図 5 は、PPI10 が、イベント信号およびタスク信号ごとにそれぞれ個別の回線によって周辺機器 18～26 およびイベント発生装置 17 に接続された一連の実施形態に関する。これは、前述のようなメモリマップド入出力を使用する代わりの手段として行ってもよいし、MCU2 が両方の通信モードをサポートする（例えば、CPU6 がレジスタを介して周辺機器と情報を交換できて、PPI10 が専用線を介して周辺機器と情報を交換できるようにする）ことも考えられる。

#### 【0066】

10

20

30

40

50

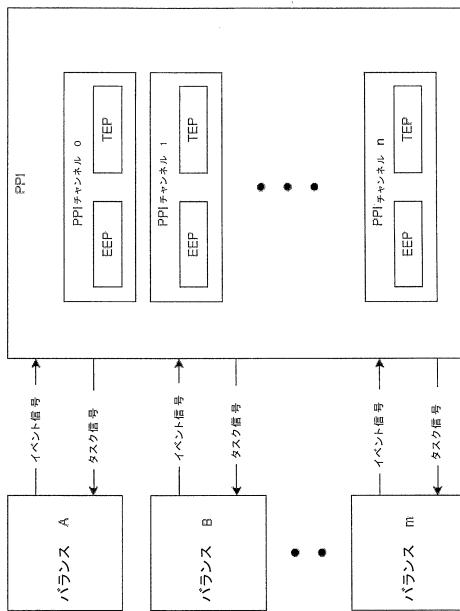

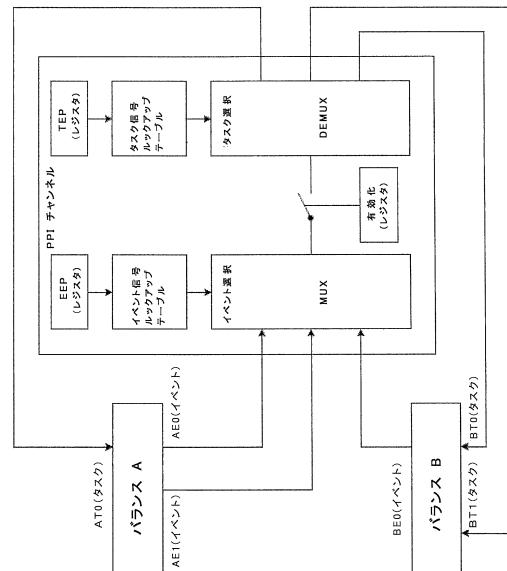

図3は、(上述と同じPPI10であっても異なるPPIであってもよい)PPIに接続されたm個の周辺機器を示している。イベント発生装置17は、これらの目的のための別の周辺機器とみなすことができる。PPIは、相互に関係付けられたイベントエンドポイントレジスタ(EEP)およびタスクエンドポイントレジスタ(TEP)を各々が有するn個のチャンネルを提供する。これらのレジスタは、各々、周辺機器の一つにあるレジスタのアドレスを保持することができる。

#### 【0067】

図4は、これらのn個のチャンネルの一つと関係付けられた構成要素により詳細を提供する。チャンネルの各々は、同様の構成要素群を有する。チャンネルのEEPは、周辺機器イベントレジスタアドレス群と、当該チャンネルと関係付けられてPPI内のマルチブレクサ(MUX)への複数の入力の一つに関連する内部イベント回線識別子と、を相互参照するイベント信号検索表に結び付けられる。PPIは、EEPに含有されるアドレスと関係付けられた入力を選択するようMUXを設定するように構成される。

#### 【0068】

同様に、チャンネルのTEPは、周辺機器タスクレジスタアドレス群と、当該チャンネルと関係付けられてPPI内のデマルチブレクサ(DEMUX)からの複数の出力の一つに関連する内部タスク回線識別子と、を相互参照するタスク信号検索表に結び付けられる。PPIは、TEPに含有されるアドレスと関係付けられた出力を選択するようDEMUXを設定するように構成される。

#### 【0069】

二つの周辺機器A、Bが、チャンネルのMUXに接続される。これらのうちの一つは、イベント発生装置であってもよい。周辺機器Aは、各々がMUXへの独自の回線を有する二つのイベント信号AE0、AE1を提供することが可能である。周辺機器Bは、これもMUXへの回線を有する単一イベント信号BE0を提供することが可能である。同様の回線が、他のn-1個のチャンネル(図示せず)のマルチブレクサに接続されることになる。

#### 【0070】

チャンネルのDEMUXは三本の出力回線に接続されて、一本は周辺機器Aのタスク入力AT0につながり、二本は周辺機器Bの異なるタスク入力BT0、BT1につながる。

#### 【0071】

PPI内では、MUXからの出力は、スイッチを介してDEMUXへの入力に接続される。スイッチが閉じられると当該接続が形成され、MUXによって選択された周辺機器の一つからのイベント信号(例えば、パルス)がDEMUXに、そしてそこから周辺機器の一つに属する、選択されたタスク入力に渡される。スイッチの状態は、CPU(図示せず)によって書き込み可能なレジスタによって制御される。

#### 【0072】

いくつかの代替的な設定では、一つのチャンネルは、各々が当該チャンネルのMUXからの出力に接続された複数のデマルチブレクサを有してもよい。こうすれば、単一イベントが複数の周辺機器タスクをトリガするようにフォーク状に設定することができる。

#### 【0073】

PPIは、チャンネルから入力イベントを受信してから所定の最大時間内に複数のタスク信号を出すように設定される。いくつかの実施形態において、この時間遅延は、すべてのチャンネルに対して一定である。異なるチャンネルやフォーク状に分かれたチャンネルの信号は、並行して処理される。

#### 【0074】

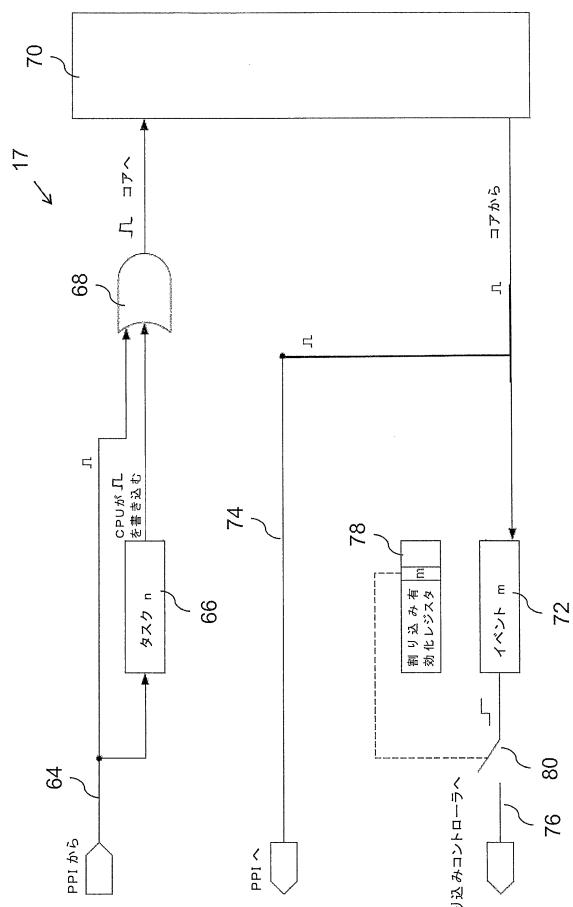

図5は、イベント発生装置17の内部を具象的に図示したものである。

#### 【0075】

特定のタスクnについて、イベント発生装置17は、タスクnをトリガするためにタスク信号を送信できる入力タスク回線64によってPPI10に接続される。イベント発生装置17は、CPU6で実行されるファームウェアがバイナリ「1」をタスクレジスタ6

10

20

30

40

50

6に書き込む場合、タスクをトリガするために信号を送信する、タスクnと関係付けられたタスクレジスタ66も有する。タスクレジスタ66の内容は、PPIがタスク回線64を介してタスク信号を送信するとイベント発生装置17によって自動的に更新されてもよい。PPIからのタスク回線64とタスクレジスタ66の状態を示す出力とは、論理ORゲート68で組み合わされて、イベント発生装置17のコア70に送信される。

#### 【0076】

簡単な実施形態では、コア70は、一対一のマッピングで各タスクnをそれぞれのイベントnに単純に接続する。より複雑な実施形態では、コア70は、例えば、「イベント1」を伝える前に「タスク1」と「タスク2」との両方をこの順番でトリガすることを要求するように、一つ以上のタスクを一つ以上のイベントと関係付ける論理回路を備えてよい。

10

#### 【0077】

コア70は、イベントmについてのイベント信号を出力することができる。これによって、関係付けられたイベントレジスタ72の内容が、（例えば、單一ビットレジスタの内容をバイナリ「0」からバイナリ「1」に変えることによって）イベントが伝えられたことを示すように変えられる。また、同じイベント信号は、分割されて、イベント出力回線74を介してPPI10に送信される。

#### 【0078】

イベントレジスタ72へのこの変更によって、信号が割り込み信号回線76を介してCPU6の割り込みコントローラに送られるように構成することもできる。この割り込み信号が送信されるか否かは、CPU6によって書き込むことができる、割り込み有効化レジスタ78の状態に依存する。イベントnに対応するビット位置にバイナリ「1」が書き込まれた場合、スイッチ80が閉じられ、割り込み信号が送信されることになる。

20

#### 【0079】

CPU6は、イベント発生装置17を、PPI10と組み合わせながら、多くの異なる形で使用することができる。

#### 【0080】

例えば、CPU6は、イベント発生装置17からイベントnに対する信号を受信すると二つ以上の周辺機器タスクをトリガするようにPPI10を構成してもよい。すると、CPU6は、イベント発生装置17のタスクレジスタ66に「1」のビットを書き込むことによって、イベント発生装置17に、n番目のイベント信号回線74を介してPPI10にイベント信号を送信させることができる。その結果、PPI10は、すべてのタスクを同時にかつアトミックにトリガすることになる。

30

#### 【0081】

別の例では、CPU6は、m番目の割り込み信号回線76を有効にして、周辺機器のイベントからイベント発生装置17に至るm番目の入力タスク回線へのチャンネルを確立する、PPI10用のマッピング関係を作成してもよい。すると、周辺機器は、当該周辺機器をPPI10に接続する適切なイベント回線を介して当該イベントをPPI10に伝えることによって、割り込みをCPU6に送信することができる。こうすれば、当該周辺機器は、CPU6への独自の割り込み回線に割り当てられた優先順位とは異なる優先順位でCPU6に割り込むことができる。

40

#### 【0082】

一つ以上の特定の実施形態を記載することによって本発明を説明してきたが、これらの実施形態に限定されるものではなく、添付する特許請求の範囲の範囲内において、多数の変形および変更が可能であることが当業者であれば理解されるであろう。

【図1】

【図2】

| マシンビング# | イベントレジスター | タスクレジスター |

|---------|-----------|----------|

| 1       | 0x100     | 0x500    |

| 2       | 0x300     | 0x620    |

| 3       | ...       | ...      |

| ...     | ...       | ...      |

【図3】

【図4】

【図5】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 6 F 13/24 3 1 0 A

審査官 松平 英

(56)参考文献 特開平07-105022(JP,A)

特開平05-307617(JP,A)

特開平08-044652(JP,A)

特表2015-503164(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 0 6 F 9 / 4 5 5 - 9 / 5 4

1 3 / 1 0 - 1 3 / 1 4

1 3 / 2 0 - 1 3 / 4 2

1 5 / 7 8