# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 12 March 2009 (12.03.2009) (10) International Publication Number WO 2009/032398 A1

- (51) International Patent Classification: *H01L 25/04* (2006.01)

- (21) International Application Number:

PCT/US2008/069516

- (22) International Filing Date: 9 July 2008 (09.07.2008)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data:

11/846,874 29 August 2007 (29.08.2007) US

- (71) Applicant (for all designated States except US): FREESCALE SEMICONDUCTOR, INC. [US/US]; 6501 William Cannon Drive, Austin, Texas 78735 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): TANG, Jinbang [CA/US]; 6353 W. Dublin Lane, Chandler, Arizona 85226 (US). FREAR, Darrel R. [US/US]; 14248 S. 12th Street, Phoenix, Arizona 85048 (US). LYTLE, William H. [US/US]; 2408 W. Flint Street, Chandler, Arizona 85224 (US).

- (74) Agents: KING, Robert L. et al.; 7700 W. Parmer Lane, MD: TX32/PL02, Austin, Texas 78729 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

### (54) Title: INTERCONNECT IN A MULTI-ELEMENT PACKAGE

(57) Abstract: A packaged semiconductor device (10) includes an interconnect layer (32) over a first side of a polymer layer (30), a semiconductor device (16, 18) surrounded on at least three sides by the polymer layer and coupled to the interconnect layer, a first conductive element (46, 58) over a second side of the polymer layer, wherein the second side is opposite the first side, and a connector block (20) within the polymer layer. The connector block (20) has at least one electrical path (22, 24, 26, 62, 64) extending from a first surface of the connector block to a second surface of the connector block. The at least one electrical path electrically couples the interconnect layer to the first conductive element. A method of forming the packaged semiconductor device is also described.

# INTERCONNECT IN A MULTI-ELEMENT PACKAGE

### Background

## <u>Field</u>

[0001] This disclosure relates generally to packages that have more than one element including at least one semiconductor device, and more specifically, to interconnect for such packages.

### Related Art

[0002] One technique for increasing density of functionality is to include multiple elements, such as integrated circuits into one package. This is an alternative to simply placing all of the functionality on a single integrated circuit because there are types of integrated circuits and semiconductor components that are difficult to make on the same integrated circuit or at least difficult to optimize on the same integrated circuit. Radio frequency (RF) circuits typically require a different process than logic. Also logic and analog may need to be optimized and use a different process. One of the techniques for placing multi-elements in the same package is redistributed chip package (RCP) which uses an organic fill around the elements and builds interconnect layers on a top side of the package where external contacts are also formed. This has been found to be a useful packaging technique which provides a very effective way of combining elements and connecting to them on a top side of the package.

[0003] There is, however, further benefit for increased utility of RCP.

# Brief Description of the Drawings

[0004] The present invention is illustrated by way of example and is not limited by the accompanying figures, in which like references indicate similar elements. Elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale.

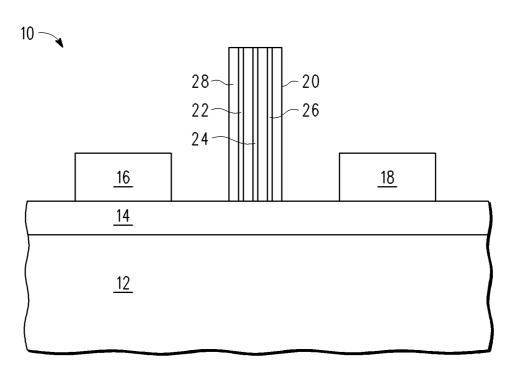

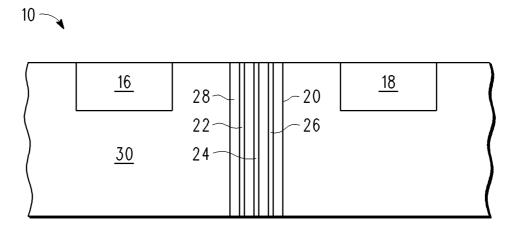

[0005] FIG. 1 is a cross section of a packaged semiconductor device at a stage in processing according to an embodiment;

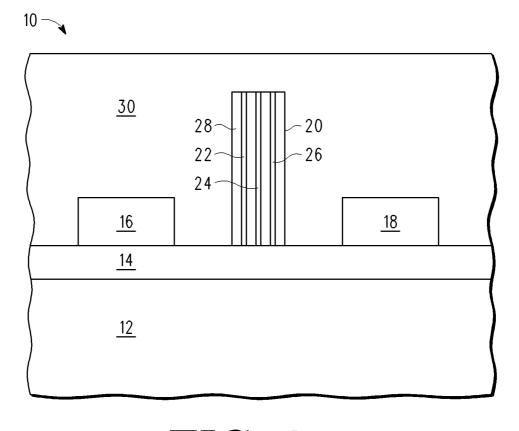

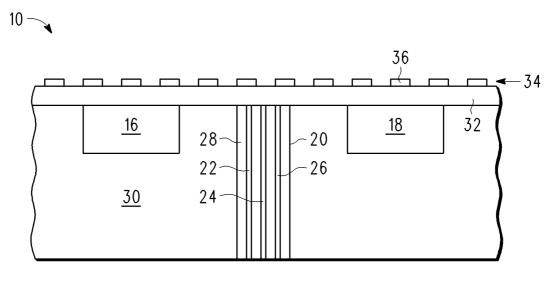

[0006] FIG. 2 is a cross section of the packaged semiconductor device of FIG. 1 at a subsequent stage in processing;

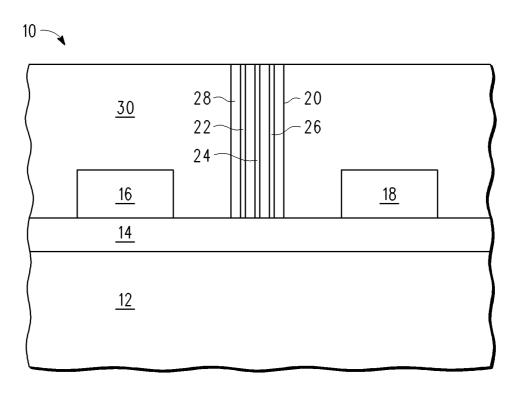

[0007] FIG. 3 is a cross section of the packaged semiconductor device of FIG. 2 at a subsequent stage in processing;

[0008] FIG. 4 is a cross section of the packaged semiconductor device of FIG. 3 at a subsequent stage in processing;

- [0009] FIG. 5 is a cross section of the packaged semiconductor device of FIG. 4 at a subsequent stage in processing;

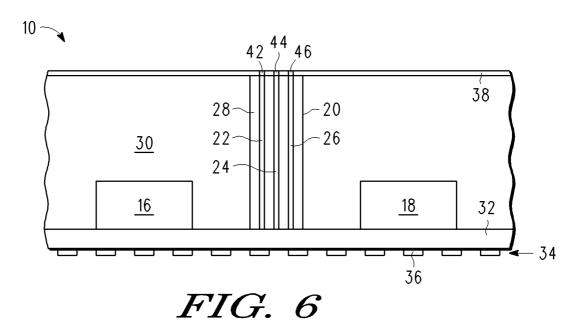

- [0010] FIG. 6 is a cross section of the packaged semiconductor device of FIG. 5 at a subsequent stage in processing;

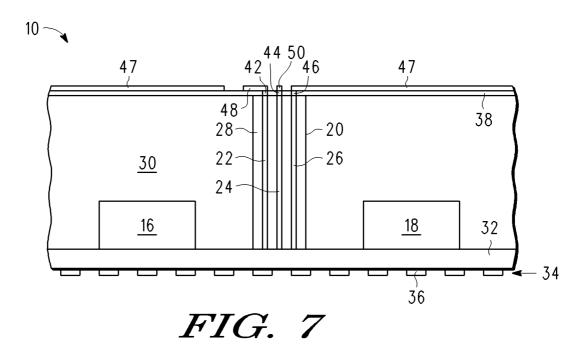

- [0011] FIG. 7 is a cross section of the packaged semiconductor device of FIG. 6 at a subsequent stage in processing;

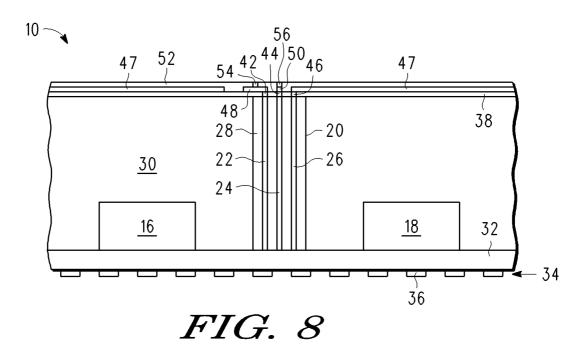

- [0012] FIG. 8 is a cross section of the packaged semiconductor device of FIG. 7 at a subsequent stage in processing;

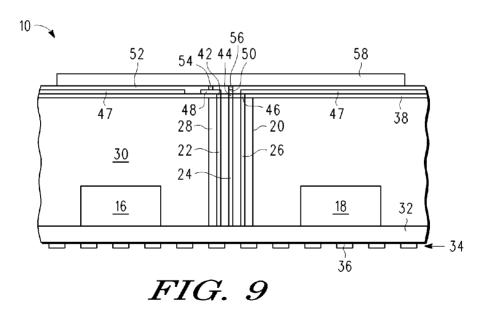

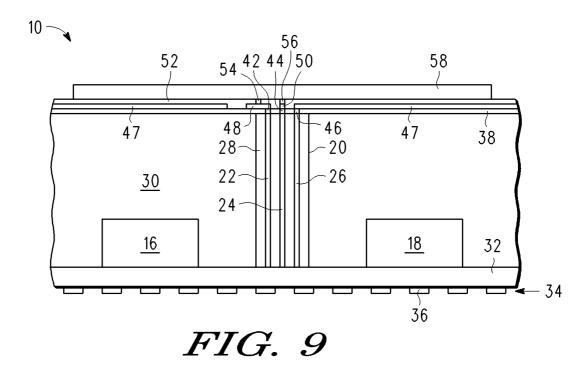

- [0013] FIG. 9 is a cross section of the packaged semiconductor device of FIG. 8 at a subsequent stage in processing;

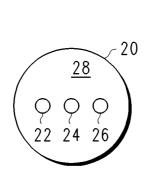

- [0014] FIG. 10 is a top view of a portion of the packaged device of FIGs. 1-9; and

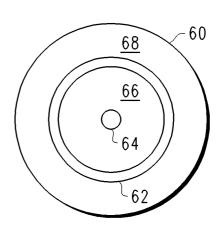

- [0015] FIG. 11 is a top view of an alternative for the portion of FIG. 10.

# **Detailed Description**

[0016] An RCP is built having multiple elements that are interconnected with external connections available on a top side. One of the elements is a connection block which provides the capability of extending from the top side to a back side because the connection block is prefabricated. The connection block, which can also be called a connector block, has the organic fill formed around in the same manner as the other elements in the RCP. The connection block thus allows electrical connection to be made from the interconnect on the top side to the back side without having to etch via holes and then filling the via holes to form vias. The distance from the top side to the back side, for practical production, is too long for forming and filling vias. One application of connection block is to place an antenna on the back side. Another is place a ground plane on the back side. This is better understood by reference to the drawings and the following description.

[0017] Shown in FIG. 1 is a package 10 comprising a carrier 12, a tape 14, an element 16, an element 18, and connection block 20. Carrier 12 is for providing mechanical support. Tape 14 is two-sided. Element 16 may be an integrated circuit, and element 18 may be an integrated circuit. On or the other could also be another type of element such as a passive

device or a discrete semiconductor device. Connection block 20 has a conductor 22, a conductor 24, and a conductor 26 that run vertically the length connection block 20 and are surrounded by a dielectric 28. Dielectric 28 is preferably an organic material similar to or the same as that used as the fill in making an RCP, but dielectric 28 could also be another material such as ceramic. Copper is a preferred material for conductors 22, 24, and 26 because of its relatively high conductivity and relatively low cost. More conductive material such as platinum, gold, or silver may be used but at a higher cost. The length of connection block 20 is chosen to be a little thicker than the thickness of the organic layer that surround the elements of the finished RCP. A common thickness for the organic layer surrounding the elements is about 0.65 millimeter (mm) but this may vary. In such case of 0.65 mm, connection block 20 and thus conductors 22, 24, and 26 are about 0.70 mm in length. Connection block 20 is preferably one mm or more in diameter. A smaller diameter may present difficulties in adhering reliably to tape 14 but may nonetheless be advantageous for some applications.

[0018] Shown in FIG. 2 is package 10 after deposition of an organic layer 30 which covers elements 16 and 18 and connection block 20. Organic layer 30 may be deposited to be about 0.80 mm for the example of connection block 20 being about 0.70 mm. Organic layer 30 may be considered a polymer layer.

[0019] Shown in FIG. 3 is package 10 after grinding organic layer 30 and a small portion of connection block 20 to expose conductors 22, 24, and 26. Organic layer 30 is then reduced, in this example, to 0.65 mm.

[0020] Shown in FIG. 4 is package 10 after removing carrier 12 and tape 14. FIG. 4 also has package 10 inverted from that of FIGs. 1-3. Elements 16 and 18 are exposed on the top side of package 10. The exposed surface of element 16 and the expose surface of element 18 are where contacts for elements 16 and 18 reside.

[0021] Shown in FIG. 5 is package 10 after forming an interconnect 32 in contact with connection block 20, element 16, and element 18. Interconnect 32 may be made of multiple conductive layers connected to elements 16 and 18 and connection block 20 using vias. On interconnect 32 is a plurality of pads 34 of which one is pad 36. Pads 34 are for receiving solder balls and are on a top side of package 10. Connection block 20 is exposed on a back side of package 10. In a conventional RCP which would not have connection block 20, processing could be complete except for the solder balls. Solder balls could be added at this point or at a subsequent convenient time.

[0022] Shown in FIG. 6 is package 10 after forming a dielectric layer 38 on the back side and forming vias 42, 44, and 46 through dielectric layer 38. Dielectric layer 38 is preferably the same material as organic layer 30 but could be another insulating material. Dielectric layer 38 may be 0.1 mm thick. Via 42 is in contact with conductor 22. Via 44 is contact with conductor 24. Via 46 is in contact with conductor 46. FIG. 6 also shows package 10 inverted from FIGs. 4 and 5. The side with pads 34 is still called the top side though and the side with dielectric layer 38 is still called the back side.

[0023] Shown in FIG. 7 is package 10 after forming a patterned conductive layer over dielectric layer 38 comprising a ground plane 47 in contact with via 40, a trace 48 on in contact with via 42, and a trace 50 in contact with via 44. Ground plane 47 surrounds traces 48 and 50. Trace 48 extends laterally from via 42 and is present for stability. Similarly, trace 50 extends laterally from via 44 in a different direction from that of trace 48 so that the lateral extension is not visible in the cross section of FIG. 7. The patterned conductive layer may be made by a conventional plating process in which a thin seed layer is deposited followed by photoresist which is patterned. Plating then ensues so that the conductive material, preferably copper although other metals may also be effective, grows in the areas not covered by the photoresist. The photoresist is removed. An etch back is performed to remove the seed layer in the areas where the conductive layer was not grown. The thickness of ground plane 47 and traces 48 and 50 may be about 0.10 mm.

[0024] Shown in FIG. 8 is package 10 after forming a dielectric layer 52 and vias 54 and 56 through dielectric layer 52. Dielectric layer 52 may be the same material as for dielectric layer 38. Via 54 is in contact with trace 48. Via 56 is contact with trace 50. Although via 56 is shown in the cross section of FIG. 8 in contact with trace 50, via 56 is preferably located over a wider portion of trace 50 than shown.

[0025] Shown in FIG. 9 is package 10 after forming an antenna 58 in contact with vias 54 and 56. Antenna 58 may be formed and patterned using the same plating technique described for ground plane 47 and traces 48 and 50. Antenna 58 may be 0.200 mm thick. With antenna 58 in contact with vias 54 and 56, antenna is coupled to conductors 22 and 24, respectively. Due to the high frequencies that may be involved, vias 54 and 56 may not have to be in actual contact with antenna 58, if sufficiently close to antenna 58, for antenna 58 to be coupled to conductor 22. Package 10 of FIG. 9 is a completed RCP that will have solder balls added later at a time closer to being mounted on a circuit board.

[0026] Shown in FIG. 10 is a top view of connection block 20 showing conductors 22, 24, and 26 in a line and dielectric 28 surrounding them in a circular shape. In this

configuration, connection block 20 is a cylinder with three inline conductors. Conductors 22, 24, and 26 could be in a different configuration. Also the shape could be different than circular, such as square, rectangular, or triangular.

[0027] Shown in FIG. 11 is an alternative connection block 60 comprising an outer insulating layer 68, a conductor ring 62, an inner conductor 64, and an insulating layer between conductor ring 62 and inner conductor 64. This forms a coaxial line which may be particularly beneficial when coupling to an antenna that is transmitting and receiving RF. Connection block 60 may replace connection block 20 with respect to the connection to antenna 58. If a ground plane were still desirable, the connection to the ground plane could be by another connection block or connection block 60 could be modified to have another conductor outside ring 62 for coupling to the ground plane.

[0028] Construction of a connection block such as connection block 20 or connection block 60 may be achieved using wire bond machines. A wire bond is commonly 25 microns in diameter. Three of those wire bonds can be placed into a cylindrical mold that is many times longer than that of connection block 20. The mold is filled with the desired dielectric such as the material used for dielectric 30. The resulting structure is then cut into pieces of the desired length of about .070 mm. Instead of an organic material, the surrounding dielectric may be a material such as ceramic. The rigidity of ceramic may be beneficial in the manufacturing process.

By now it should be appreciated that there has been provided a packaged [0029] semiconductor device having an interconnect layer, a semiconductor device, a first conductive element, and a connector block. The interconnect layer is over a first side of a polymer layer. The semiconductor device is surrounded on at least three sides by the polymer layer and is coupled to the interconnect layer. The first conductive element is over a second side of the polymer layer. The second side is opposite the first side. The connector block is within the polymer layer and has at least one electrical path extending from a first surface of the connector block to a second surface of the connector block, and electrically couples the interconnect layer to the first conductive element through the at least one electrical path. The connector block may comprise an insulating material surrounding the at least one electrical path. The connector block may have at least two coaxial electrical paths. The at least one electrical path may be a ground path and the first conductive element may be a ground plane. The at least one electrical path may be a signal path and the first conductive element may be an antenna. The packaged semiconductor device may further comprise a second conductive element and a second electrical path, wherein the second electrical path is a ground path and the second conductive element is a ground

plane. The packaged semiconductor device may further comprise a third electrical path, wherein the third electrical path is coupled to the antenna.

[0030] Also provided is a method for forming a packaged semiconductor device. The method includes surrounding a semiconductor device on at least three sides by a polymer layer. The method further includes forming an interconnect layer over a first side of the polymer layer and over the semiconductor device, wherein the semiconductor device is coupled to the interconnect layer. The method further includes forming a conductive element over a second side of the polymer layer, wherein the second side is opposite the first side. The method further includes electrically coupling the interconnect layer to the conductive element through a connector block within the polymer layer, having at least one electrical path. The forming the conductive element over a second side may comprise plating a conductive material to form an antenna. The step of surrounding may comprise attaching a semiconductor device to a temporary support structure, forming the polymer layer over the semiconductor device, and removing the temporary support structure after forming the polymer layer. The step of electrically coupling may comprise attaching the connector block to the temporary support structure before forming the polymer layer, removing a portion of the polymer layer to expose a surface of the connector block, forming the interconnect layer over the surface of the connector block while forming the interconnect layer over the first side of the polymer layer. The method may further comprise depositing a dielectric layer over the surface of the connector block, and forming a via in the dielectric layer, wherein the via is electrically coupled to the connector block and the conductive element. The at least one electrical path may be selected from the group consisting of a ground path and a signal path. The first conductive element may be selected from a group consisting of a ground plane and an antenna. The at least one electrical path may comprise at least two coaxial electrical paths.

[0031] Further described is a method for forming a packaged semiconductor device. The method includes attaching a semiconductor device to a temporary support structure. The method further includes attaching a connector block to the temporary support structure, wherein the connector block has at least one electrical path. The method further includes forming an encapsulant over the connector block and the semiconductor device. The method further includes removing a portion of the encapsulant to expose a top surface of the connector block. The method further includes forming an interconnect layer electrically coupled to the top surface of the connector block. The method further includes removing the temporary support structure to expose a bottom surface of the connector block. The method further includes electrically coupling a tangible element to the bottom surface of the

connector block. The step of electrically coupling a tangible element to the bottom surface of the connector block may comprise plating a conductive material to form an antenna. The step of electrically coupling a tangible element to the bottom surface of the connector block may further comprise depositing a dielectric layer over the bottom surface of the connector block, and forming a via in the dielectric layer, wherein the via is electrically coupled to the connector block and the antenna. The step of removing a portion of the encapsulant to expose a top surface of the connector block may comprise grinding the encapsulant. The temporary support structure may be selected from a group consisting of a tape and a carrier. The connector block may have at least two coaxial electrical paths.

[0032] Moreover, the terms "front," "back," "top," "bottom," "over," "under" and the like in the description and in the claims, if any, are used for descriptive purposes and not necessarily for describing permanent relative positions. It is understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments of the invention described herein are, for example, capable of operation in other orientations than those illustrated or otherwise described herein.

[0033] Although the invention is described herein with reference to specific embodiments, various modifications and changes can be made without departing from the scope of the present invention as set forth in the claims below. For example, dielectric layer 38 is shown as being formed after interconnect layer 32 whereas dielectric layer 38 may be deposited before interconnect layer 32 is formed. Also plating was described as the method for forming patterned metal layers, but other deposition techniques may be used. For example, the metal could be sputtered and then patterned with an etch. Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of the present invention. Any benefits, advantages, or solutions to problems that are described herein with regard to specific embodiments are not intended to be construed as a critical, required, or essential feature or element of any or all the claims.

[0034] The term "coupled," as used herein, is not intended to be limited to a direct coupling or a mechanical coupling.

[0035] Furthermore, the terms "a" or "an," as used herein, are defined as one or more than one. Also, the use of introductory phrases such as "at least one" and "one or more" in the claims should not be construed to imply that the introduction of another claim element by the indefinite articles "a" or "an" limits any particular claim containing such introduced claim element to inventions containing only one such element, even when the same claim includes

the introductory phrases "one or more" or "at least one" and indefinite articles such as "a" or "an." The same holds true for the use of definite articles.

[0036] Unless stated otherwise, terms such as "first" and "second" are used to arbitrarily distinguish between the elements such terms describe. Thus, these terms are not necessarily intended to indicate temporal or other prioritization of such elements.

# **CLAIMS**

### What is claimed is:

- 1. A packaged semiconductor device comprising:

- an interconnect layer over a first side of a polymer layer;

- a semiconductor device surrounded on at least three sides by the polymer layer and coupled to the interconnect layer;

- a first conductive element over a second side of the polymer layer, wherein the second side is opposite the first side; and

- a connector block within the polymer layer, having at least one electrical path extending from a first surface of the connector block to a second surface of the connector block, and electrically coupling the interconnect layer to the first conductive element through the at least one electrical path.

- 2. The packaged semiconductor device of claim 1, wherein the connector block comprises an insulating material surrounding the at least one electrical path.

- 3. The packaged semiconductor device of claim 1, wherein the connector block has at least two coaxial electrical paths.

- 4. The packaged semiconductor device of claim 1, wherein the at least one electrical path is a ground path and the first conductive element is a ground plane.

- 5. The packaged semiconductor device of claim 1, wherein the at least one electrical path is a signal path and the first conductive element is an antenna.

- 6. The packaged semiconductor device of claim 5, further comprising a second conductive element and a second electrical path, wherein the second electrical path is a ground path and the second conductive element is a ground plane.

- 7. The packaged semiconductor device of claim 6, further comprising a third electrical path, wherein the third electrical path is coupled to the antenna.

- 8. A method for forming a packaged semiconductor device, the method comprising: surrounding a semiconductor device on at least three sides by a polymer layer;

forming an interconnect layer over a first side of the polymer layer and over the semiconductor device, wherein the semiconductor device is coupled to the interconnect layer;

- forming a conductive element over a second side of the polymer layer, wherein the second side is opposite the first side; and

- electrically coupling the interconnect layer to the conductive element through a connector block within the polymer layer, having at least one electrical path.

- 9. The method of claim 8, wherein forming the conductive element over a second side comprises plating a conductive material to form an antenna.

- 10. The method of claim 8, wherein:

surrounding a semiconductor device on at least three sides by the polymer layer, comprises:

attaching a semiconductor device to a temporary support structure; forming the polymer layer over the semiconductor device; and removing the temporary support structure after forming the polymer layer; and

electrically coupling the interconnect layer, comprises:

attaching the connector block to the temporary support structure before forming the polymer layer;

removing a portion of the polymer layer to expose a surface of the connector block; and

forming the interconnect layer over the surface of the connector block while forming the interconnect layer over the first side of the polymer layer.

11. The method of claim 10, further comprising:

depositing a dielectric layer over the surface of the connector block; and forming a via in the dielectric layer, wherein the via is electrically coupled to the connector block and the conductive element.

- 12. The method of claim 8, wherein the at least one electrical path is selected from the group consisting of a ground path and a signal path.

- 13. The method of claim 8, wherein the first conductive element is selected from a group consisting of a ground plane and an antenna.

14. The method of claim 8, wherein the at least one electrical path comprises at least two coaxial electrical paths.

15. A method for forming a packaged semiconductor device, the method comprising: attaching a semiconductor device to a temporary support structure; attaching a connector block to the temporary support structure, wherein the connector block has at least one electrical path;

forming an encapsulant over the connector block and the semiconductor device; removing a portion of the encapsulant to expose a top surface of the connector block; forming an interconnect layer electrically coupled to the top surface of the connector block;

removing the temporary support structure to expose a bottom surface of the connector block; and

electrically coupling a tangible element to the bottom surface of the connector block.

- 16. The method of claim 15, wherein electrically coupling a tangible element to the bottom surface of the connector block, comprises plating a conductive material to form an antenna.

- 17. The method of claim 16, wherein electrically coupling a tangible element to the bottom surface of the connector block further comprises:

depositing a dielectric layer over the bottom surface of the connector block; and forming a via in the dielectric layer, wherein the via is electrically coupled to the connector block and the antenna.

- 18. The method of claim 15, wherein the removing a portion of the encapsulant to expose a top surface of the connector block comprises grinding the encapsulant.

- 19. The method of claim 15, wherein the temporary support structure is selected from a group consisting of a tape and a carrier.

- 20. The method of claim 15, wherein the connector block has at least two coaxial electrical paths.

FIG. 1

FIG. 2

2/5

FIG. 3

FIG. 4

FIG. 5

FIG. 11

International application No. **PCT/US2008/069516**

### A. CLASSIFICATION OF SUBJECT MATTER

### H01L 25/04(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC H01L 25/04

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Korean Utility models and applications for Utility models since 1975.

Japanese Utility models and applications for Utility models since 1975.

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) e-KIPASS (KIPO internal); semiconductor, package, interconnect, connector

### C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------|-----------------------|

|           | LIC 2005 1/7707 A1 (Dana) 04 Ana 2005                                              |                       |

| A         | US 2005-167797 A1 (Bong) 04 Aug. 2005 see abstract, Claims 1~30, Figs. 1~6         | 1~20                  |

|           | US 2002-155692 A1 (Kong) 24 Oct. 2002                                              |                       |

| A         | see abstract, Claims 1~15, Figs. 1~3                                               | 1~20                  |

|           | US 6,593,644 B2 (Chiu et al.) 15 Jul. 2003                                         |                       |

| A         | see abstract, Claims 1~15, Figs. 1~15                                              | 1 ~ 20                |

|           | US 6,753,600 B1 (Ho) 22 Jun. 2004                                                  |                       |

| A         | see abstract, Claims 1~21, Figs. 1~2                                               | 1 ~ 20                |

|           | US 2005-161789 A1 (Towle et al.) 28 Jul. 2005                                      | 1 20                  |

| A         | see abstract, Claims 1~29, Figs. 1~3                                               | 1 ~ 20                |

|           |                                                                                    |                       |

|           |                                                                                    |                       |

|           |                                                                                    |                       |

|           |                                                                                    |                       |

|  |  | Further documents are | listed in the | continuation | of Box C. |

|--|--|-----------------------|---------------|--------------|-----------|

|--|--|-----------------------|---------------|--------------|-----------|

See patent family annex.

- \* Special categories of cited documents:

- 'A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international

- 'L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

Date of the actual completion of the international search

30 JANUARY 2009 (30.01.2009)

Date of mailing of the international search report

30 JANUARY 2009 (30.01.2009)

Name and mailing address of the ISA/KR

Korean Intellectual Property Office Government Complex-Daejeon, 139 Seonsa-ro, Seogu, Daejeon 302-701, Republic of Korea

Facsimile No. 82-42-472-7140

Authorized officer

BAK, JUNYUNG

Telephone No. 82-42-481-5729

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No.

# PCT/US2008/069516

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                                                                                                  | Publication<br>date                                                                                                                                                                                          |

|----------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| US 2005-167797 A1                      | 04.08.2005       | CN 1649204 A<br>TW 259562 B                                                                                                                                                                              | 03.08.2005<br>01.08.2006                                                                                                                                                                                     |

| US 2002-0155692 A1                     | 24. 10. 2002     | SG 136801 A1<br>US 2002-0160598 A1<br>US 6444576 B1<br>US 6538333 B2<br>US 6569762 B2                                                                                                                    | 29.11.2007<br>31.10.2002<br>03.09.2002<br>25.03.2003<br>27.05.2003                                                                                                                                           |

| US 6593644 B2                          | 15.07.2003       | AU 2002-256271 A8 CN 1314117 C CN 1505838 A CZ 20032834 A3 EP 1405343 A2 HU 0303965 A2 JP 2004-536449 T KR 2004-0030542 A PL 368078 A1 TW 586196 A US 2002-153603 A1 W0 2002-086971 A2 W0 2002-086971 A3 | 05. 11. 2002<br>02. 05. 2007<br>16. 06. 2004<br>18. 02. 2004<br>07. 04. 2004<br>01. 03. 2004<br>02. 12. 2004<br>09. 04. 2004<br>21. 03. 2005<br>01. 05. 2004<br>24. 10. 2002<br>31. 10. 2002<br>27. 02. 2003 |

| US 6753600 B1                          | 22.06.2004       | None                                                                                                                                                                                                     |                                                                                                                                                                                                              |

| US 2005-161789 A1                      | 28.07.2005       | CN 1977200 A<br>EP 1789827 A1<br>JP 2008-500591<br>US 7369718<br>WO 2006-012195 A1                                                                                                                       | 06.06.2007<br>30.05.2007<br>10.01.2008<br>06.05.2008<br>02.02.2006                                                                                                                                           |