(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7372505号

(P7372505)

(45)発行日 令和5年11月1日(2023.11.1)

(24)登録日 令和5年10月24日(2023.10.24)

(51)国際特許分類

G 0 1 R 31/3187(2006.01)

G 0 1 R 31/28 (2006.01)

H 0 1 L 21/822(2006.01)

H 0 1 L 27/04 (2006.01)

F I

G 0 1 R 31/3187

G 0 1 R 31/28 V

H 0 1 L 27/04 T

請求項の数 3 (全13頁)

(21)出願番号 特願2019-522635(P2019-522635)

(86)(22)出願日 平成29年7月17日(2017.7.17)

(65)公表番号 特表2019-523429(P2019-523429)

A)

(43)公表日 令和1年8月22日(2019.8.22)

(86)国際出願番号 PCT/US2017/042403

(87)国際公開番号 WO2018/014024

(87)国際公開日 平成30年1月18日(2018.1.18)

審査請求日 令和2年7月11日(2020.7.11)

(31)優先権主張番号 15/211,782

(32)優先日 平成28年7月15日(2016.7.15)

(33)優先権主張国・地域又は機関

米国(US)

前置審査

(73)特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

- 5474 ダラス メイル ステイション

3999 ピーオーボックス 655474

(74)代理人 100098497

弁理士 片寄 恒三

ロバート フロイド ペイン

アメリカ合衆国 75002 テキサス州

ルーカス, ブライアーデール ドライブ

1700

(72)発明者 ランパート ヤコブ ヘルマン

オランダ王国 フォールスコーテン, エ

ヌエル-2251 エイブイ, ルーコー

最終頁に続く

(54)【発明の名称】 電子回路のビルトインセルフテストのためのシステム及び方法

## (57)【特許請求の範囲】

## 【請求項1】

集積回路であって、

少なくとも第1及び第2の入力端子を有するマルチプレクサであって、

前記第1の入力端子において第1の入力信号を受信し、

前記第2の入力端子において第2の入力信号を受信し、

選択信号を受信し、

前記選択信号の第1の組み合わせに応答して前記第1の入力信号を出力し、

前記選択信号の第2の組み合わせに応答して前記第2の入力信号を出力し、

前記選択信号の第3の組み合わせに応答して前記第1及び第2の入力信号のアナログ加

算を出力する、

ように結合される、前記マルチプレクサと、

前記マルチプレクサに結合されるトランスマッタであって、

前記第2の入力信号を前記マルチプレクサに提供し、

第1の制御信号に応答して前記第2の入力信号の振幅を選択的に変更する、

ように結合される、前記トランスマッタと、

前記トランスマッタに結合される位相シフタであって、第2の制御信号に応答して前記

トランスマッタへのクロック信号の位相を選択的に変更するように構成され、前記クロック

信号の前記位相を選択的に変えることにより第2の入力信号の位相が選択的に調節可能

である、前記位相シフタと、

前記マルチプレクサに結合される少なくとも1つのレシーバ回路であって、前記マルチプレクサの出力に応答して少なくとも1つのローカル信号を提供するように構成される、前記少なくとも1つのレシーバ回路と、

前記少なくとも1つのレシーバ回路に結合される誤り検出器であって、前記少なくとも1つのローカル信号が前記少なくとも1つのレシーバ回路の予期される出力に合致するか否かを示すために少なくとも1つの比較信号を生成するように構成される、前記誤り検出器と、

前記誤り検出器に結合される制御ユニットであって、前記誤り検出器からの少なくとも1つの比較信号に応答して前記第1の入力信号と前記選択信号と前記第1及び第2の制御信号とを提供するように構成される、前記制御ユニットと、

を含む、集積回路。

### 【請求項2】

請求項1に記載の集積回路であって、

前記第2の入力信号が所定のテスト信号パターンである、集積回路。

### 【請求項3】

請求項2に記載の集積回路であって、

前記所定のテスト信号パターンが擬似ランダムバイナリシーケンスパターンである、集積回路。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本願は、概して電子回路に関し、更に特定して言えば、電子回路のビルトインセルフテストに関する。

#### 【背景技術】

#### 【0002】

集積回路( I C )は、セルフテストを実施するように構成される付加的なハードウェア及びソフトウェアと共に設計及び構築され得る。ビルトインセルフテスト( B I S T )システムは、集積回路が、それ自体の機能及びオペレーションをテストすることを可能にする。幾つかの場合において、集積回路は、その機能性を検証するための外部の自動化されたセルフテスト機器を必要としない。典型的に、B I S Tシステムは、I Cの内部回路にわたって動くためにテスト信号パターンを生成し、その後、応答が所定の予期される応答に合致するかを判定するため、種々の内部構成要素から応答を収集する。高データレートのI Cは、特に、注意深い特徴付け、製造テスト、及びインシステムデバッグ能力から利点を得ることができる。特殊で高価な( 例えば、典型的なコストが \$ 1 0 0 k を超える )ビット誤りレシオテスター及びオシロスコープが必要とされる場合、このような制約は、市販の、低成本の自動化テスト機器( A T E )を用いる能力を制限する。

#### 【0003】

多くのデジタルデータ通信応用例において、通信は双方向であり、トランスマッタ及びレシーバの組み合わせを含むI Cが、通信リンクの両端において用いられる。この組み合わせはトランシーバとしても知られている。トランシーバにおいて、「ループバック」テスト機能が、機能的な「デバイス速度での」テストを提供する。B I S Tは、レシーバにループバックされ得るトランスマッタに対するテストパターンを生成し得る。これにより、トランシーバI C内のデバイス速度でのレシーバ機能のテストが可能となる。集積回路を用いる他のデジタル通信応用例において、通信は、アップストリームトランスマッタがダウンストリームレシーバに通信する单一方向である。一つの一般的な例は、ディスプレイデバイスのためのビデオインターフェースであり、これは、伝送能力のない「受信オンリー」デバイスである。他のデバイスは、プロセッサ、ビデオコントローラ、フィールドプログラマブルゲートアレイ( F P G A )、又は特定用途向け集積回路( A S I C )を含み、これらは、データをディスプレイデバイスに送る。

#### 【0004】

10

20

30

40

50

トランシーバシステムにおいて、ループバック B I S T 機能は、バス / フェイル指示のみを提供し、デバイスマージン測定値を提供しない。ループバック機能において、「ループ」がデバイス内で完了するので、レシーバが実際に受信する信号の直接測定は実際的ではない。最も近い測定値は、典型的に、デバイスのパッド / ピンの外部でなされ得る。これらのパッド / ピンは、プローブされ得るが、付加的な信号劣化（例えば、めっきスタブ（s t u b s）、ボンドワイヤ、及び / 又は非理想終端により生じる反射）は測定されない。スタンドアロンのレシーバでは、ノイズ及びテスト結果をスキューリングする他の干渉を導入し得る外部接続を用いてテストがなされるので、デバイス速度でレシーバ機能をテストする際に課題がある。高速通信システムでは、誤りのない、ロバストなリンクのために電気的信号のシグナルインテグリティが重要である。

10

#### 【 0 0 0 5 】

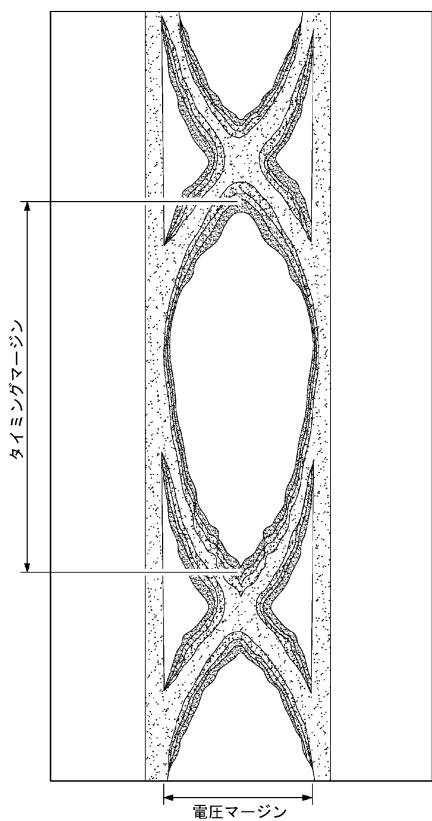

図 1 は、通信リンクの性能を評価するために有用な、例示の「データアイ」ダイアグラムを示す。データアイダイアグラム測定において、タイミング及び電圧マージンが直接測定され得る。これは、典型的に、パッケージングされた I C の外部境界又はテスト接続（例えば、ピン、ボール、又はパッド）に接続される高速オシロスコープを用いてなされる。アイが垂直方向に一層「開く」ほど、より大きな電圧マージン（アイの振幅として測定される）がレシーバに利用可能となる。同様に、「アイ」が水平方向においてより開く、より大きなタイミングマージン（アイの幅として測定される）がレシーバに利用可能となる。

20

#### 【 0 0 0 6 】

この測定には幾つかの欠点がある。一つは、この測定は高価なオシロスコープを用い、高価なオシロスコープはテスト環境において利用不能であり得、同様に、完成した又はアセンブルされたシステムにおいて利用不能であり得る。別の欠点は、パッケージングされた I C の外部境界を測定することにより、データアイダイアグラムは、デバイスの内部機能の全体像を提供しないことである。

#### 【 0 0 0 7 】

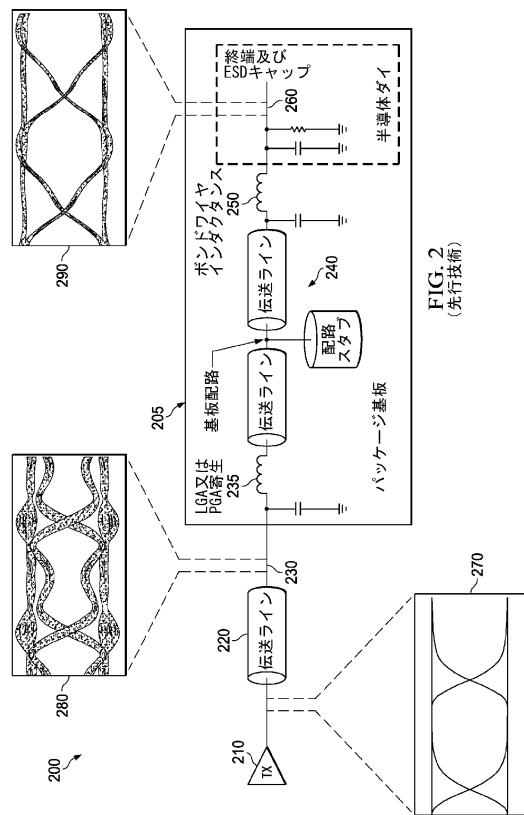

図 2 は、テスト及び測定の従来の方法を備える例示の回路 2 0 0 を示す。回路 2 0 0 は、データのみ（例えば、ディスプレイユニット）を受信するように構成されるレシーバ回路 2 0 5 を含む。回路 2 0 0 は更に、トランスマッタ 2 1 0 を含む。トランスマッタ 2 1 0 は、データをレシーバ 2 0 5 にダウンストリームで送信するように構成される任意の回路であり得る。トランスマッタ 2 1 0 からのデータは、伝送ライン 2 2 0 （例えば、回路基板上の回路経路）を介して進む。データは、レシーバ 2 0 5 回路パッケージのエントランスポイント 2 3 0 においてレシーバ 2 0 5 により受信される。エントランスポイント 2 3 0 は、ピングリッドアレイ（P G A）、ランドグリッドアレイ（L G A）、及び同様のその他の I C パッケージ接続など、任意の回路接続であり得る。I C パッケージは、信号経路において寄生インダクタンス及び静電容量 2 3 5 を導入する。信号は更に、レシーバ 2 0 5 の内部配路 2 4 0 を介して進み、ボンドワイヤインダクタンス 2 5 0 などの種々の要因に起因して、更に信号異常を導入し得る。信号は、最終的に I C において終端ポイント 2 6 0 において受信される。終端ポイント 2 6 0 は、更に、レシーバにおける、静電放電（E S D）保護回路、I C ボンドパッド、及び I C 能動回路要素に起因して、寄生容量を入力信号に導入し得る。

30

#### 【 0 0 0 8 】

従来のテスト方法において、終端ポイント 2 6 0 におけるレシーバ 2 0 5 の内部で電圧及びタイミングマージンを測定することなく、トランスマッタの出口ポイント（exit points）及びレシーバの入口ポイント（entry points）において信号がテストされる。例えば、信号がトランスマッタ 2 1 0 の出力において初期的にテストされる場合、それは理想的なデータアイダイアグラム 2 7 0 を図示し得る。しかし、測定が入り口ポイント 2 3 0 及び終端ポイント 2 6 0 においてなされる場合、データアイダイアグラムは、それぞれ、アイダイアグラム 2 8 0 及び 2 9 0 に示すように表され得る。これは、I C パッケージ及び / 又は I C ダイの非理想性及び電気的挙動に起因する、更なる信号損失、反射、フィルタ

40

50

リング、及び等化によるものである。データアイダイアグラムは、各信号ポイントにおいて電圧及び時間に対して異なるマージンを提供する。図示されるように、従来のテスト方法は、レシーバの電圧及びタイミングマージン上でデータを提供することができない。

【発明の概要】

【0009】

ビルトインセルフテストを備えるデバイスの記載される例において、マルチプレクサが、少なくとも第1及び第2の入力端子を有し、第1の入力端子において第1の入力信号を受け取り、第2の入力端子において第2の入力信号を受け取り、選択信号を受信するよう結合される。また、マルチプレクサは、選択信号の第1の組み合わせに応答して第1の入力信号を、選択信号の第2の組み合わせに応答して第2の入力信号を、及び選択信号の第3の組み合わせに応答して第1及び第2の入力信号のアナログ加算を出力するよう結合される。

10

【図面の簡単な説明】

【0010】

【図1】(従来技術)例示の「データアイ」ダイアグラムである。

【0011】

【図2】(従来技術)テスト及び測定の従来の方法を備える例示の回路を図示する。

【0012】

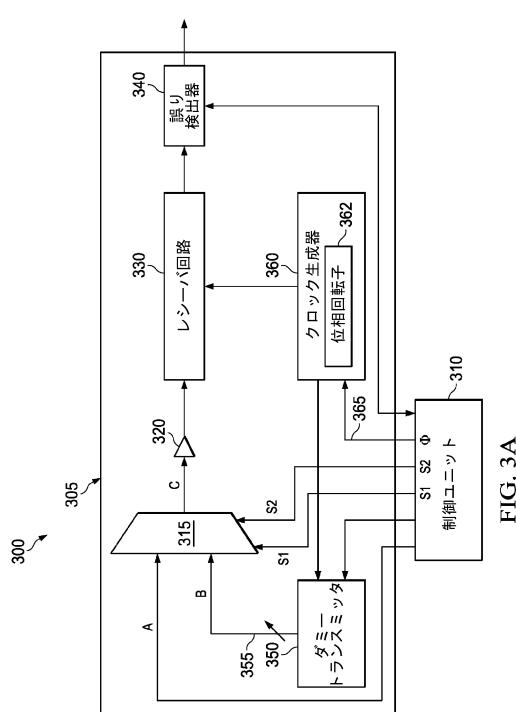

【図3A】一実施例に従った例示のビルトインセルフテストシステムのブロック図である。

20

【0013】

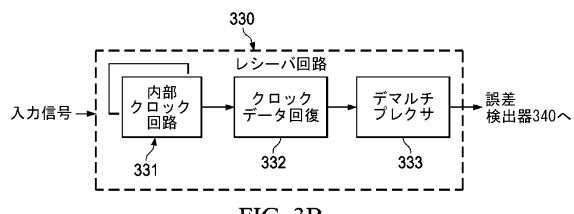

【図3B】図3Aのシステムのレシーバ回路の一例のブロック図である。

【0014】

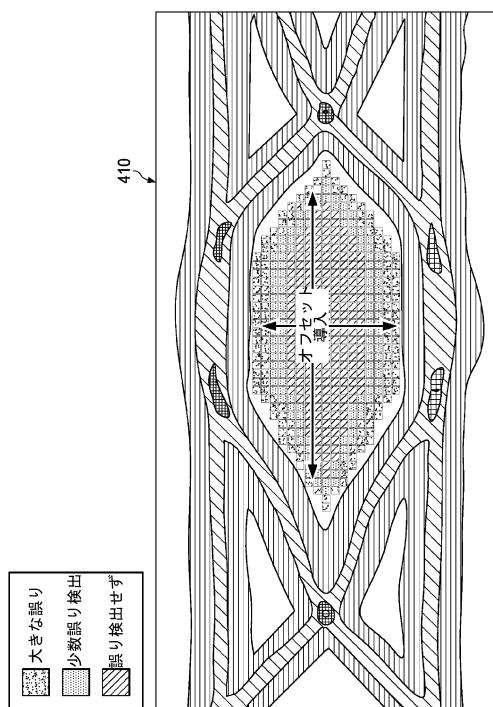

【図4A】一実施例に従ったレシーバのビルトインセルフテスト機能の例示のデータアイダイアグラムである。

【0015】

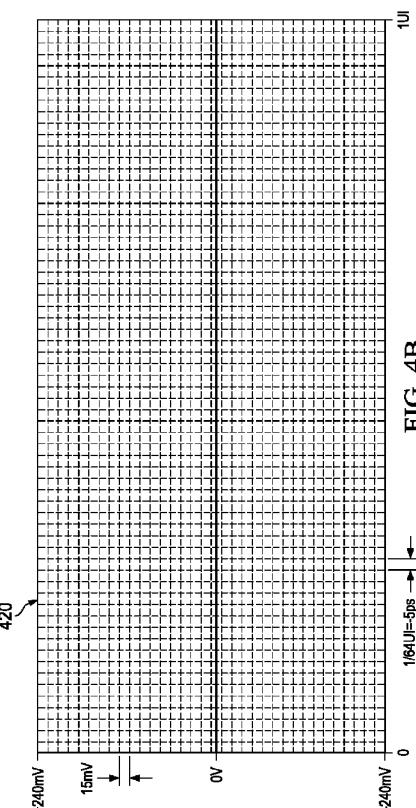

【図4B】図4Aの例示のデータアイダイアグラムのためのタイミング及び電圧スケールのグラフである。

【0016】

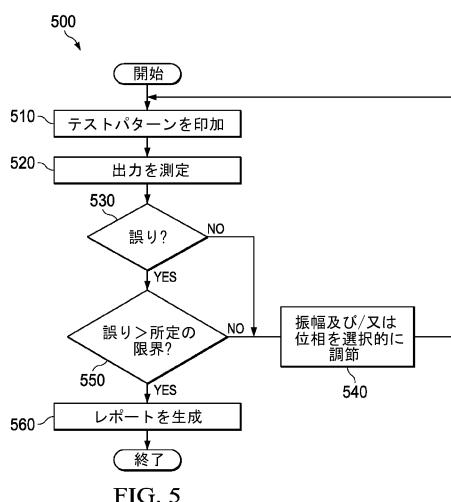

【図5】一実施例に従ったビルトインセルフテストシステムを用いるデバイスの電圧及びタイミングマージンを測定するための例示のプロセスのフローチャートである。

30

【発明を実施するための形態】

【0017】

I Cパッケージ(ここで、レシーバが実際の信号を感知する)の内部のシグナルインテグリティを測定するため、例示の実施例は、たとえI Cパッケージの高速データレートが外部テストハードウェアの能力を超える場合でも、I Cパッケージ内部の電圧及びタイミングマージンを測定する。

【0018】

集積回路をテストするためのシステム及び方法の記載される例において、システムは、内部プログラマブル入力を提供するように構成されるトランスマッタを含み、これは、誤りを識別し、デバイスの電圧及びタイミングマージンを正確に判定するために、入力テスト信号の振幅及びクロック位相を変更する機能を備える。

40

【0019】

図3Aは、一実施例に従った例示のビルトインセルフテストシステム300を示す。BIST300は、レシーバ305及び制御ユニット310を含む。制御ユニット310は、レシーバ305の種々の機能をテストし、機能性、電圧、及びタイミングマージンに関するデータ、及び本明細書に記載するようなレシーバ305の種々のその他の態様を提供するように構成される任意のコンピューティングデバイスであり得る。この例では、レシーバ305の種々の構成要素は、単一の集積回路ダイ上に形成される。

【0020】

レシーバ305は、特殊用途のマルチプレクサ315を含む。この例では、マルチプレ

50

クサ315は、(a)それぞれ、第1及び第2の入力信号を受信するための2つの入力端子A及びB、及び、(b)それらの入力信号に応答して出力信号を出力するための出力端子Cを有する。また、マルチプレクサ315は、この例では制御ユニット310から2つの選択信号を受信するための2つの選択端子S1及びS2を有する。

#### 【0021】

第1の例において、(それぞれ、入力端子A及びBにおける)第1及び第2の入力信号はデジタル信号である。第2の例において、第1及び第2の入力信号(それぞれ、入力端子A及びBにおける)はアナログ信号である。図3Aの例において図示されるように、(a)(入力端子Aにおける)第1の入力信号は、レシーバ305の集積回路ダイ外部のソースである制御ユニット310から受信され、及び(b)(入力端子Bにおける)第2の入力信号は、レシーバ305の集積回路ダイ内(の内部)のソースであるダミートランスマッタ350から受信される。

10

#### 【0022】

マルチプレクサ315は、下記の表1に示すように、(端子S1及びS2における)選択信号に応答して(端子Cにおいて)出力信号を出力する。

20

Table 1

| S1 | S2 | C   |

|----|----|-----|

| 0  | 0  | X   |

| 0  | 1  | A   |

| 1  | 0  | B   |

| 1  | 1  | A+B |

#### 【0023】

従って、「11」のバイナリ値を有する(端子S1及びS2における)選択信号に応答して、マルチプレクサ315は、(a)(端子A及びBからの)入力信号のアナログ加算を実施し、(b)アナログ加算を端子Cにおいて出力信号として出力し、そのため、たとえ(端子A及びBからの)入力信号がデジタル信号であっても、端子Cにおける出力信号(これは、それらの入力信号のアナログ加算である)は連続的アナログ信号である。マルチプレクサ315とは異なり、従来のマルチプレクサは、その選択信号に応答してその入力信号の一つのみを出力し得る。

30

#### 【0024】

「00」のバイナリ値を有する(端子S1及びS2における)選択信号に応答して、マルチプレクサ315は、表1に示すような「X値」を有するように端子Cを操作する。「X値」は、特定の実装の必要性に従って、浮遊値(例えば、高インピーダンス)、接地されたゼロ値、フルされた高値、又はその他の値など、「無効」状態である。

40

#### 【0025】

更に、表1に示すように「01」のバイナリ値を有する(端子S1及びS2における)選択信号に応答して、マルチプレクサ315は、端子Aからの入力信号と同じ値を有するように端子Cを操作する。同様に、表1に示すように「10」のバイナリ値を有する(端子S1及びS2における)選択信号に応答して、マルチプレクサ315は、端子Bからの入力信号と同じ値を有するように端子Cを操作する。

#### 【0026】

(端子S1及びS2における)選択信号の特定の値が、表1における例によって示されているが、マルチプレクサ315は、他の例においてそれらの選択信号の異なる値に応答して所望の出力Cを生成するために構成され得る。例えば、(a)第1の代替の実施例に

50

おいて、「00」のバイナリ値を有する（端子S1及びS2における）選択信号に応答して、マルチプレクサ315は、「X値」を有する代わりに、端子Aからの入力信号と同じ値を有するように端子Cを操作し、（b）第2の代替の実施例において、「00」のバイナリ値を有する（端子S1及びS2における）選択信号に応答して、マルチプレクサ315は、「X値」を有する代わりに、端子Bからの入力信号と同じ値を有するように端子Cを操作し、（c）第3の代替の実施例において、「00」のバイナリ値を有する（端子S1及びS2における）選択信号に応答して、マルチプレクサ315は、「X値」を有する代わりに、マルチプレクサ315の第3の端子D（図3Aには示していない）からの入力信号と同じ値を有するように、端子Cを操作する。

#### 【0027】

10

また、この第3の代替の実施例において、「11」のバイナリ値を有する（端子S1及びS2における）選択信号に応答して、マルチプレクサ315は、（a）（端子A、B、及びDからの）入力信号のアナログ加算を実施し、（b）アナログ加算を端子Cにおいて出力信号として出力し、そのため、たとえ（端子A、B、及びDからの）入力信号がデジタル信号であっても、端子Cにおける出力信号（これは、それらの入力信号のアナログ加算である）は、連続的アナログ信号である。

#### 【0028】

レシーバ305は、端子Cから他の信号レシーバ回路330への出力信号を駆動するように結合される入力バッファ／ドライバ320を更に含む。誤り検出器340が、回路330の出力を受信し、その出力を所定の入力信号（例えば、制御ユニット310からのテスト信号）と比較し、及びその比較の結果を制御ユニット310に（及び任意選択でレシーバ305の集積回路ダイ内又はその外部の他のユニットに）提供するように、結合される。例えば、少なくとも一つの実施例において、誤り検出器340は、（a）制御ユニット310からの予期される出力信号の所定のパターンを受信し、（b）その所定のパターンを回路330の出力と比較し、（c）その比較の結果を制御ユニット310に（及び任意選択でレシーバ305の集積回路ダイ内又はその外部の他のユニットに）提供する。第1の例において、誤り検出器340の出力は、その比較のバイナリパス／フェイル指示（及び任意選択でレシーバ305の集積回路ダイ内又はその外部の他のユニットへの）である。第2の例において、誤り検出器340の出力は、その比較の詳細なレポートである。

#### 【0029】

30

クロック生成器360が、レシーバ305オペレーションのためのクロック信号を提供するように結合される。明確にするため、図3Aは、レシーバ305内の回路330及びダミートラニスミッタ350のみに接続されるクロック生成器360を示すが、クロック生成器360は更に、レシーバ305内の他の構成要素に結合される。図3Aに示すように、クロック生成器360は、集積された位相回転子（シフタ）362を含む。別の例において、位相シフタは、クロック生成器360の外部にある。クロック生成器360は、所望の速度で動作するようにレシーバ305に対してクロック周波数を生成する。制御ユニット310は、所望の周波数（例えば、データアイダイアグラムの中心周波数）で内部クロックをフリーズさせ、レシーバ305のタイミングマージン、及び本願において説明されるような別のものを判定するために内部クロック信号の位相を変更／回転させるための制御信号など、制御信号ライン365を介して種々の制御信号をクロック生成器360に提供するように結合される。位相シフタがクロック生成器360の外部にある場合、制御ユニット310は、適切な位相シフト制御信号をその外部位相シフタに提供するように結合される。

#### 【0030】

40

ダミートラニスミッタ350は、所定のテスト信号パターンを生成するように構成可能（例えば、プログラム可能）である。図3Aに示すように、ダミートラニスミッタ350は、それらの所定のテスト信号パターンを、マルチプレクサ315及びバッファ／ドライバ320を介してレシーバ回路330に出力するように結合される。より具体的には、ダミートラニスミッタ350は、それらの所定のテスト信号パターンを、マルチプレクサ3

50

15の入力端子Bに接続される信号線355を介して出力する。所定のテスト信号パターンは、一連の論理「1」(例えば、正の電圧)、論理「0」(例えば、負の電圧)、又は、種々の状況下でレシーバ305の機能性をテストするように構成されるその他の所定の信号パターンなど、擬似ランダムバイナリシーケンス(「PRBS」)パターンの任意の形態であり得る。テスト信号パターンの振幅は、その構成(例えば、プログラミング)に従って、それが制御ユニット310から受信する適切な制御信号に応答してダミートランスマッタ350により継続的に可変(調節可能)であり、これにより、有利にも、レシーバ305オペレーションの微調整が可能となる。従って、本明細書において上述するように、制御ユニット310は、誤り検出器340から出力される比較結果を監視する。それらの比較結果(及び任意選択でその他の要因)に応答して、制御ユニット310は、適切な制御信号をダミートランスマッタ350に出力し、ダミートランスマッタ350は、それへの応答においてテスト信号パターンの振幅を調節(継続的に増大/低減)し、それにより、レシーバ305にその最適キャパシティ内で機能させるため、電圧マージンを判定する。

#### 【0031】

レシーバ305のタイミングマージンは、クロック生成器360からのその内部クロックの位相を調節することにより判定可能である。例えば、制御ユニット310は、初期的に、クロック生成器360に、特定の周波数(例えば、理想的なデータアイダイアグラムの中央)で内部クロックの位相をフリーズさせ、その後、内部クロックを位相を回転/変更させるために適切な制御信号を出力し得、そのため、制御ユニット310は、誤り検出器340から出力される比較結果を監視することによりそれらの位相回転/変更のインパクトを判定し、それにより、レシーバ305のタイミングマージンを測定する。位相シフタが(上記の別の例において述べたように)クロック生成器360の外部にある場合、制御ユニット310は適切な制御信号を出力して、外部位相シフタに、レシーバ回路330に対する任意のクロック位相を生成させ、その後、レシーバ305のタイミングマージンを判定するために種々の方向に(例えば、進んだ又は遅れた)位相を調節させる。

#### 【0032】

制御ユニット310は更に、マルチプレクサ315の入力端子Aを介して構成可能な(例えば、プログラム可能な)テスト信号パターンを直接的に出力するように結合される。(制御ユニット310から入力端子Aを介する)それらのテスト信号パターンは、本明細書において上述するように「11」のバイナリ値を有するようにマルチプレクサ315の端子S1及びS2を適切に制御する制御ユニット310によって、(ダミートランスマッタ350からの入力端子Bを介する)他のテスト信号パターンと組み合わされ得る。このようにしてそれらのテスト信号パターンを適切に組み合わせることにより、制御ユニット310は、その構成(例えば、プログラミング)に従って、(ダミートランスマッタ350からの入力端子Bを介する)他のテスト信号パターンの振幅を調節し、そのため、制御ユニット310は、誤り検出器340から出力される比較結果を監視することによりそれらの振幅調節のインパクトを判定する。

#### 【0033】

更に、本明細書において上述したように、制御ユニット310は、(a)ダミートランスマッタ350に、マルチプレクサ315の入力端子Bにおけるテスト信号パターンの振幅を調節させ、(b)クロック生成器360に、レシーバ305の内部クロック信号の位相を変更/回転させるために、適切な制御信号を出力するように構成される。従って、レシーバ305を、テスト信号パターン、振幅、及びクロック位相の種々の組み合わせ下で動作させることにより、制御ユニット310は、レシーバ305の一層完全な機能的プロファイルを判定する。例えば、このようなテストの間、誤り検出器340から出力される比較結果を監視することにより、制御ユニット305は、レシーバ305の機能的マージンを判定するために、データアイダイアグラム(例えば、電圧及びタイミング)を生成し得る。

#### 【0034】

10

20

30

40

50

図3Bは、レシーバ回路330(図3A)の一例を示す。この例では、レシーバ回路330は、バッファ／ドライバ320からの信号に応答して、(種々の内部機能ユニットに対して)ローカルクロック信号を提供するように結合される内部クロック回路331を含む。クロックデータ回復ユニット332が、回路331の出力からのデータ及びクロック信号を回復せしめるように結合される。デマルチプレクサ333が、ユニット332の出力をデマルチプレクスすることにより、レシーバ回路330出力信号を誤り検出器340に提供するように結合される。明確にするため、図3Bは、その構成要素間の単一信号線を示すが、それらの構成要素は、レシーバ305において用いられる多数のビットラインに基づいて、複数の信号線により接続され得る。更に、レシーバ回路330及びレシーバ305は、多くの他の内部要素(図示せず)を含み得る。

10

#### 【0035】

図4Aは、一実施例に従った、レシーバ305などのレシーバのBIS-T機能の例示のデータアイダイアグラム410を示す。データアイダイアグラム410におけるアイの「開口」は、テスト信号パターンのクロック位相及び振幅に対する種々のオフセットを用いて測定され得る。例えば、(a)テストパターンの振幅が変更されるとき、アイは、垂直方向に拡大／後退し得、(b)クロックの位相が変更されるとき、アイは水平方向に拡大／後退し得る。図4Aに示すように、アイの中央部分は、レシーバ(例えば、レシーバ305)の許容可能な稼働範囲を提供し得る。クロック位相及びテスト振幅がアイの端部に向かって押されるにつれて、レシーバの機能的マージン(電圧及びタイミング)の詳細な図を提供するための誤り率が増大し得る。

20

#### 【0036】

レシーバにおける誤り検出器(例えば、誤り検出器340)は、予期される受信データパターンを実際の受信したデータパターンに対して比較し得る。レシーバへの入力が、誤り検出器により予期されるものと同じパターンである場合、誤り検出器は、誤りなしの指示を出力する。最終的に、ダミートラニスミッタ350により導入されるオフセットのレベルが増大するにつれて、オフセットが入力信号より大きくなり、レシーバ感度が損なわれ、誤りが誤り検出器によって検出される。誤り検出器の出力を監視し、テストパターンの振幅を調節することにより、レシーバの感度が判定され得る。

#### 【0037】

図4Aに示すように、アイの「中間」において、レシーバ感度及び利用可能な信号は、ダミートラニスミッタ350により導入されるいかなるオフセットをも克服するために充分である。初期的に、信号振幅の端部が近づくにつれてわずかな誤りが誤り検出器によって検出される。導入されたオフセットの振幅が増大するとき、大きい数の誤りが生成される。この調節を用いて、レシーバ感度は、フルに判定及び特徴付けられ得る。

30

#### 【0038】

図4Bは、例示のデータアイダイアグラム410(図4A)に対するタイミング及び電圧スケール420を示す。3.2Gbpsのデータ速度では、(各々約4.88psの)64タイミングユニットステップが、312.5psのビットユニットインターバル(UI)にわたり、マージンテストのために有用である。同様に、(各々15mVの)32振幅ステップは、+/-240mVの総電圧レンジにわたり、電圧マージンテストのために有用である。レシーバ305をこれらのオフセットの種々の組み合わせ下で動作させることにより、誤りのないデータが誤り検出器340により受信されるかを判定するために、制御ユニット310は、多数のタイミング及び電圧オフセットポイント(受信信号のデータアイの内部)を測定する。例えば、制御ユニット310は、クロックデータ回復ユニット332(図3B)の機能性を評価するためにこれらの測定を用いる。周波数及び電圧のステップ又は「スライス」は、タイミング及び電圧ドメイン両方における感度測定のために有用であり、それにより、制御ユニット310に、データアイダイアグラムの「アイ」プロファイルを生成させる。クロックの位相を適切にプログラミングすること、及び(ダミートラニスミッタ350により提供される)垂直の感度測定を付加することにより、制御ユニット310は、「アイ」の全プロファイルをマッピングする。レシーバ305の所与

40

50

のプロファイルを生成するため、この例は、15mV及び4.88psを用いるが、所与のデバイスの電圧及びクロックレーティングに基づいて、任意の数及びサイズのステップを用いることができる。

#### 【0039】

図5は、一実施例に従ったBISTを用いるデバイス（例えば、レシーバ305）の電圧及びタイミングマージンを測定するための例示のプロセス500を示す。510において初期的に、制御ユニット310は、所定のテストパターンをレシーバ305に印加する。本明細書において図3Aに関連して上述したように、所定のパターンは、ダミートランスマッタ350からの擬似ランダムバイナリシーケンスを印加すること、制御ユニット310からのテストパターンを印加すること、及び/又はそれらの組み合わせを含み得る。520において、制御ユニット310は、（直接的に又は誤り検出器340を介して）レシーバ回路330の出力を測定して、出力が、予期される出力信号の所定のパターンに合致するかを判定する。少なくとも一つの例において、誤り検出器340は、制御ユニット310から所定のパターンを受信し、レシーバ回路330の出力がその所定のパターンに合致するかを判定する。530において、制御ユニット310は、（例えば、誤り検出器340比較の結果を受信することにより）レシーバ回路330の出力が誤りを含むか否かを判定する。

10

#### 【0040】

制御ユニット310が、レシーバ回路330の出力が如何なる誤りを含まないと（530において）判定する場合、制御ユニット310は、（540において）所定のステップ（例えば、図4A及び4Bに関連して本明細書において上述したタイミングユニットステップ及び振幅ステップ）を用いて、テスト信号の振幅及び/又はクロックの位相を選択的に調節する。本明細書において上述したように、制御ユニット310は、レシーバ305のために用いられるべき測定モデルに基づいて、個別に又はそれらの組み合わせで及び/又は任意選択で他のオフセットと共に、テスト信号の振幅及び/又はクロックの位相を選択的に調節することができる。（540において）このようにして振幅及び/又は位相を調節した後、制御ユニット310は、このような調節された振幅及び/又は位相を備えた（及び任意選択でこのような他のオフセットを備えた）（510において）テストパターンを次の測定のためにレシーバ305に印加する。

20

#### 【0041】

制御ユニット310が、レシーバ回路330の出力が誤りを含むと判定する（530において）場合、制御ユニット310は、誤りの数が所定の限界を超えるか否かを（550において）判定する。所定の限界は、データアイダイアグラムの「構造」に基づき得る。例えば、印加されたオフセットが「アイ」をその外側限界（水平及び/又は垂直）まで伸張する場合、誤りの数が増大し得る。

30

#### 【0042】

また、所定の限界は、デバイス（例えば、レシーバ305）レーティング及び信号許容誤り限界に基づき得る。例えば、デバイスが或る精度に基づく応用例に用いられる場合、少數の誤りでも許容不能であり得、そのため、所定の誤り限界は、控えめに見積もって小さい数に設定され得る。或いは、デバイスが或る高許容誤り応用例のために用いられる場合、所定の誤り限界がたっぷりと大きな数に設定され得る。

40

#### 【0043】

制御ユニット310が、誤りの数が所定の限界を超えると判定する（550において）場合、制御ユニット310は、（a）所定のステップを用いてテスト信号の振幅及び/又はクロックの位相を（540において）選択的に調節し、（b）このような調節された振幅及び/又は位相を備えた（及び任意選択でこのような他のオフセットを備えた）テストパターンを（510において）次の測定のためにレシーバ305に印加する。或いは、制御ユニット310が、（550において）誤りの数が所定の限界を超えると判定する場合、このような数はレシーバ305レンジの外側境界を示し得、そのため、制御ユニット310は、レポートを（560において）生成する。少なくとも一つの例において、レポ

50

ートは、測定されたデータアイダイアグラム、及び( a )テストパターンの種々の段階におけるデータアイダイアグラムの形状及び形態、及び( b )それらの段階における信号振幅及び/又はクロック位相の値、を含む関連パラメータを含む。

【 0 0 4 4 】

本発明の特許請求の範囲内で、説明した例示の実施例に改変が成され得、他の実施例が可能である。例えば、オペレーションは、必ずしも本明細書において説明される特定の順になされる必要はない。また、いくつかのオペレーションが幾つかの実施例において必ずしも必要とされるわけではない。

10

20

30

40

50

【図面】

【図 1】

FIG. 1

(先行技術)

【図 2】

FIG. 2

(先行技術)

10

20

30

40

【図 3 A】

FIG. 3A

【図 3 B】

FIG. 3B

50

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

【図 5】

FIG. 5

10

20

30

40

50

---

フロントページの続き

ブパーク 7

審査官 小川 浩史

(56)参考文献 米国特許出願公開第2005/0193290(US, A1)

特開2014-174131(JP, A)

米国特許出願公開第2001/0016929(US, A1)

特開2023-101589(JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 01 R 31/28 - 31/3193

H 01 L 27/04