(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6695874号

(P6695874)

(45) 発行日 令和2年5月20日(2020.5.20)

(24) 登録日 令和2年4月24日(2020.4.24)

(51) Int.Cl.

H01L 33/00 (2010.01)

H05B 45/00 (2020.01)

F 1

H01L 33/00

H05B 37/02J

J

請求項の数 15 (全 16 頁)

(21) 出願番号 特願2017-521215 (P2017-521215)

(86) (22) 出願日 平成27年10月9日 (2015.10.9)

(65) 公表番号 特表2017-539079 (P2017-539079A)

(43) 公表日 平成29年12月28日 (2017.12.28)

(86) 國際出願番号 PCT/EP2015/073347

(87) 國際公開番号 WO2016/062557

(87) 國際公開日 平成28年4月28日 (2016.4.28)

審査請求日 平成30年9月27日 (2018.9.27)

(31) 優先権主張番号 14189606.8

(32) 優先日 平成26年10月21日 (2014.10.21)

(33) 優先権主張国・地域又は機関

歐州特許庁 (EP)

(73) 特許権者 516043960

シグニファイ ホールディング ビー ヴ

イ

S I G N I F Y H O L D I N G B. V

.オランダ国 5656 アーネー アイン

トホーフェン ハイ テク キャンパス

48

High Tech Campus 48

, 5656 AE Eindhoven,

The Netherlands

(74) 代理人 100163821

弁理士 柴田 沙希子

最終頁に続く

(54) 【発明の名称】発光回路のセグメント駆動

## (57) 【特許請求の範囲】

## 【請求項 1】

発光回路に接続するように適応された、前記発光回路を駆動するためのドライバであつて、前記ドライバは、

初期時間間隔の間に全ての発光回路を迂回するバイパス電流信号を導くためのバイパススイッチング回路であり、前記初期時間間隔の間は前記ドライバに供給するための主電源信号の振幅は初期範囲にあり、前記主電源信号の前記初期範囲の振幅は、発光を開始する第1の発光回路の最小電圧振幅よりも小さい前記バイパススイッチング回路であり、バイパス電流スイッチを含み、且つ前記バイパス電流スイッチを制御するためのバイパス制御回路を含む前記バイパススイッチング回路であって、前記バイパス制御回路が、バイパス制御スイッチと、3つの抵抗器並びに第1及び第2の中間接点を含むバイパス電圧分割器とを含み、前記バイパス電流スイッチの制御電極が前記バイパス電圧分割器の前記第1の中間接点に結合され、前記バイパス制御スイッチの制御電極が前記バイパス電圧分割器の前記第2の中間接点に結合される前記バイパススイッチング回路と、

第1の時間間隔の間に前記第1の発光回路を通じて第1の電流信号を導くための第1のスイッチング回路であり、前記主電源信号の振幅は前記第1の時間間隔の間は第1の範囲にあり、前記主電源信号の前記第1の範囲の振幅は前記主電源信号の前記初期範囲の振幅よりも大きい前記第1のスイッチング回路であり、第1の電流スイッチを含み、且つ前記第1の電流スイッチを制御するための第1の制御回路を含む前記第1のスイッチング回路であって、前記第1の制御回路が、第1の制御スイッチと、3つの抵抗器並びに第1及び

10

20

第2の中間接点を含む第1の電圧分割器とを含み、前記第1の電流スイッチの制御電極が前記第1の電圧分割器の前記第1の中間接点に結合され、前記第1の制御スイッチの制御電極が前記第1の電圧分割器の前記第2の中間接点に結合される前記第1のスイッチング回路と、

第2の時間間隔の間に前記第1の発光回路及び第2の発光回路の直列接続を通じて第2の電流信号を導くための第2のスイッチング回路であり、前記主電源信号の振幅は前記第2の時間間隔の間は第2の範囲にあり、前記主電源信号の前記第2の範囲の振幅は前記主電源信号の前記第1の範囲の振幅よりも大きい前記第2のスイッチング回路であり、第2の電流スイッチを含み、且つ前記第2の電流スイッチを制御するための第2の制御回路を含む前記第2のスイッチング回路であって、前記第2の制御回路が、第2の制御スイッチと、3つの抵抗器並びに第1及び第2の中間接点を含む第2の電圧分割器とを含み、第2の電流スイッチの制御電極が前記第2の電圧分割器の前記第1の中間接点に結合され、第2の制御スイッチの制御電極が前記第2の電圧分割器の前記第2の中間接点に結合される前記第2のスイッチング回路と、

前記バイパス電流信号が少なくとも形状において前記主電源信号にほぼ追従するように、前記初期時間間隔の間に前記バイパス電流信号の振幅を適応させるための適応回路とを含む、ドライバ。

#### 【請求項2】

前記適応回路は、前記第1の電流信号が少なくとも形状において前記主電源信号にほぼ追従するように、前記第1の時間間隔の間に前記第1の電流信号の振幅を適応させ、且つ/又は前記第2の電流信号が少なくとも形状において前記主電源信号にほぼ追従するように、前記第2の時間間隔の間に前記第2の電流信号の振幅を適応させ、

前記主電源信号は主電源電圧である、請求項1に記載のドライバ。

#### 【請求項3】

入力電力を受信する入力部を更に有し、

前記バイパススイッチング回路は、前記入力部間に接続され、前記適応回路との直列接続を介して、前記入力部を短絡するように適応され、第1発光回路又は第2発光回路を流れることなく、前記バイパス電流を直接前記入力部間へガイドするように適応された、請求項1に記載のドライバ。

#### 【請求項4】

前記適応回路は、前記主電源信号の振幅から導かれた情報に応じて振幅を適応させ、

前記主電源信号の振幅が相対的に小幅に変化している場合は、対応する電流信号の振幅は相対的に小幅に適応され、

前記主電源信号の振幅が相対的に大幅に変化している場合は、対応する電流信号の振幅は相対的に大幅に適応される、請求項1又は2に記載のドライバ。

#### 【請求項5】

前記適応回路は、前記主電源信号の各範囲の振幅が増加している場合は各電流信号の振幅を増加させ、前記主電源信号の各範囲の振幅が減少している場合は各電流信号の振幅を減少させる、請求項1又は2に記載のドライバ。

#### 【請求項6】

前記適応回路は前記主電源信号の振幅から導かれた情報に応じて前記電流信号の振幅を整形し、

前記主電源信号の振幅が相対的に小幅に変化している場合は、前記適応回路は対応する電流信号の振幅を相対的に小幅に整形し、

前記主電源信号の振幅が相対的に大幅に変化している場合は、対応する電流信号の振幅を相対的に大幅に整形する、請求項1又は2に記載のドライバ。

#### 【請求項7】

前記適応回路は各電流信号の振幅を整形し、各電流信号の整形された振幅が各範囲の前記主電源信号の振幅の形状と実質的に同一である、請求項1又は2に記載のドライバ。

#### 【請求項8】

10

20

30

40

50

前記バイパス電圧分割器の3つの抵抗器のうちの1つ以上の値が前記初期範囲を規定し、前記第1の電圧分割器の3つの抵抗器のうちの1つ以上の値が前記第1の範囲を規定し、前記第2の電圧分割器の3つの抵抗器のうちの1つ以上の値が第2の範囲を規定する、請求項1乃至7のいずれか一項に記載のドライバ。

**【請求項9】**

前記適応回路が、規定信号に応じて、前記バイパス電流信号、前記第1の電流信号及び前記第2の電流信号の振幅を規定する電流源を備え、前記適応回路が更に、前記主電源信号の振幅の検出に応じて前記規定信号を前記電流源に供給する規定回路を備える、請求項1に記載のドライバ。

**【請求項10】**

前記電流源が抵抗器を含み、前記規定信号が電圧信号を含む、請求項9に記載のドライバ。

10

**【請求項11】**

前記電流源が更に前記抵抗器に直列結合された1つ以上の電圧規定コンポーネントを含む、請求項10に記載のドライバ。

**【請求項12】**

前記規定回路が、2つの抵抗器及び1つの中間接点を含む入力電圧分割器と、反転トランジスタと、3つの抵抗器並びに第1及び第2の中間接点を含むインターフェース電圧分割器と、負の伝達を有するプログラマブルレギュレータと、2つの抵抗器を含む出力抵抗回路網と、出力トランジスタとを含み、前記反転トランジスタの制御電極が前記主電源入力電圧の瞬時の振幅の前記検出のために前記入力電圧分割器の前記中間接点に結合され、前記反転トランジスタの主電極が前記インターフェース電圧分割器の前記第1の中間接点に結合され、前記プログラマブルレギュレータの制御入力が前記インターフェース電圧分割器の前記第2の中間接点に結合され、前記プログラマブルレギュレータの出力が前記出力トランジスタの主電極に結合され、前記プログラマブルレギュレータの制御入力及び出力が前記出力抵抗回路網の2つの抵抗器のうちの1つに結合され、前記出力トランジスタの制御電極が前記電流源に結合される、請求項9に記載のドライバ。

20

**【請求項13】**

請求項1に記載のドライバと、第1及び第2の発光回路とを含む、デバイス。

**【請求項14】**

30

発光回路を駆動するためのドライバを制御するための方法であって、前記ドライバは、初期時間間隔の間に全ての発光回路を迂回するバイパス電流信号を導くためのバイパススイッチング回路であり、前記初期時間間隔の間は前記ドライバに供給するための主電源信号の振幅は初期範囲にあり、前記主電源信号の前記初期範囲の振幅は、発光を開始する第1の発光回路の最小電圧振幅よりも小さい前記バイパススイッチング回路であり、バイパス電流スイッチを含み、且つ前記バイパス電流スイッチを制御するためのバイパス制御回路を含む前記バイパススイッチング回路であって、前記バイパス制御回路が、バイパス制御スイッチと、3つの抵抗器並びに第1及び第2の中間接点を含むバイパス電圧分割器とを含み、前記バイパス電流スイッチの制御電極が前記バイパス電圧分割器の前記第1の中間接点に結合され、前記バイパス制御スイッチの制御電極が前記バイパス電圧分割器の前記第2の中間接点に結合される前記バイパススイッチング回路と、

40

第1の時間間隔の間に前記第1の発光回路を通じて第1の電流信号を導くための第1のスイッチング回路であり、前記主電源信号の振幅は前記第1の時間間隔の間は第1の範囲にあり、前記主電源信号の前記第1の範囲の振幅は前記主電源信号の前記初期範囲の振幅よりも大きい前記第1のスイッチング回路であり、第1の電流スイッチを含み、且つ前記第1の電流スイッチを制御するための第1の制御回路を含む前記第1のスイッチング回路であって、前記第1の制御回路が、第1の制御スイッチと、3つの抵抗器並びに第1及び第2の中間接点を含む第1の電圧分割器とを含み、前記第1の電流スイッチの制御電極が前記第1の電圧分割器の前記第1の中間接点に結合され、前記第1の制御スイッチの制御電極が前記第1の電圧分割器の前記第2の中間接点に結合される前記第1のスイッチング

50

回路と、

第2の時間間隔の間に前記第1の発光回路及び第2の発光回路の直列接続を通じて第2の電流信号を導くための第2のスイッチング回路であり、前記主電源信号の振幅は前記第2の時間間隔の間は第2の範囲にあり、前記主電源信号の前記第2の範囲の振幅は前記主電源信号の前記第1の範囲の振幅よりも大きい前記第2のスイッチング回路であり、第2の電流スイッチを含み、且つ前記第2の電流スイッチを制御するための第2の制御回路を含む前記第2のスイッチング回路であって、前記第2の制御回路が、第2の制御スイッチと、3つの抵抗器並びに第1及び第2の中間接点を含む第2の電圧分割器とを含み、第2の電流スイッチの制御電極が前記第2の電圧分割器の前記第1の中間接点に結合され、第2の制御スイッチの制御電極が前記第2の電圧分割器の前記第2の中間接点に結合される前記第2のスイッチング回路と、

を含み、前記方法は、

前記バイパス電流信号が少なくとも形状において前記主電源信号に追従するように、前記初期時間間隔の間に前記バイパス電流信号の振幅を適応させるステップを有する、方法。

## 【請求項15】

前記方法は、

前記第1の電流信号が少なくとも形状において前記主電源信号にほぼ追従するように、前記第1の時間間隔の間に前記第1の電流信号の振幅を適応させるステップ、及び／又は

前記第2の電流信号が少なくとも形状において前記主電源信号にほぼ追従するように、前記第2の時間間隔の間に前記第2の電流信号の振幅を適応させるステップを更に有し、

前記主電源信号は主電源電圧である、請求項14に記載の方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、発光回路を駆動するためのドライバに関する。本発明は更にドライバを備えたデバイス及び方法に関する。

## 【0002】

斯かる発光回路の例は発光ダイオード回路である。斯かるデバイスの例はランプである。

## 【背景技術】

## 【0003】

U S 2 0 1 2 / 0 2 6 2 0 7 5 A 1 は、低いライン電流高調波を提供する多段シーケンシャル電流調整器を開示する。斯かる低いライン電流高調波によって比較的小さい全高調波ひずみがもたらされるが、これを更に減らす必要がある。

## 【0004】

U S 2 0 1 2 / 0 1 7 6 8 2 6 A 1 は、入力A C電圧に基づいてスイッチS 1～S Mがオフにされるタップリニアドライバを開示する。負荷群L G 1は何れのスイッチによっても制御されない。スイッチS 1はオフにされる第1のスイッチであり、電流が負荷群L G 1及びL G 2を流れることを可能にする。

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

従来技術では、入力電圧が発光回路をオンにする最低電圧未満である場合は電流が流れない。斯かるゼロ電流は主電源の非ゼロ電圧とマッチせず、その結果、高調波ひずみが生じる。

## 【0006】

本発明の目的は改良されたドライバを提供することである。本発明の更なる目的はデバイス及び改善された方法を提供することである。

## 【課題を解決するための手段】

10

20

30

40

50

## 【0007】

- 第1の態様によれば、発光回路を駆動するためのドライバが提供され、ドライバは、

- 初期時間間隔の間に全ての発光回路を迂回するバイパス電流信号を導くためのバイパススイッチング回路であって、初期時間間隔の間はドライバに供給するための主電源信号の振幅が初期範囲にあり、かつ発光を開始する第1の発光回路(91)の最小電圧振幅よりも小さいバイパススイッチング回路と、

- 第1の時間間隔の間に第1の発光回路を通じて第1の電流信号を導くための第1のスイッチング回路であって、主電源信号の振幅は第1の時間間隔の間は第1の範囲にあり、主電源信号の第1の範囲の振幅は主電源信号の初期範囲の振幅よりも大きい第1のスイッチング回路と、

- 第2の時間間隔の間に第1の発光回路及び第2の発光回路の直列接続を通じて第2の電流信号を導くための第2のスイッチング回路であって、主電源信号の振幅は第2の時間間隔の間は第2の範囲にあり、主電源信号の第2の範囲の振幅は主電源信号の第1の範囲の振幅よりも大きい第2のスイッチング回路と、

- バイパス電流、第1の電流及び第2の電流のうちの少なくとも1つが少なくとも形状において主電源信号にほぼ追従するように、初期時間間隔の間にバイパス電流信号の振幅を適応させ、第1の時間間隔の間に第1の電流信号の振幅を適応させ、第2の時間間隔の間に第2の電流信号の振幅を適応させるための適応回路と、を含む。

10

## 【0008】

- ドライバは、第1の時間間隔の間に第1の発光回路を通じて第1の電流信号を導く第1のスイッチング回路を含む。この第1の時間間隔は、ドライバに供給するための主電源信号の振幅が第1の範囲にある時間間隔である。第1のスイッチング回路は、U S 2 0 1 2 / 0 2 6 2 0 7 5 A 1に見られるような切替可能な電流源を含む、又は第1の電流信号を個別の電流源(スイッチング回路ごとの1つの個別の電流源)又は汎用電流源(2つ以上のスイッチング回路のための1つの汎用電流源)に導く。主電源信号は、例えば50Hz正弦波電圧信号又は60Hz正弦波電圧信号の整流バージョンである。

20

## 【0009】

- ドライバは、第2の時間間隔の間に第1の発光回路及び第2の発光回路の組み合わせを通じて第2の電流信号を導く第2のスイッチング回路を含む。この第2の時間間隔は、主電源信号の振幅が第1の範囲とは異なる第2の範囲にある時間間隔である。第2のスイッチング回路は、U S 2 0 1 2 / 0 2 6 2 0 7 5 A 1に見られるような切替可能な電流源を含む、又は第2の電流信号を個別の電流源(スイッチング回路ごとの1つの個別の電流源)若しくは汎用電流源(2つ以上のスイッチング回路のための1つの汎用電流源)に導く。主電源信号の第2の範囲の振幅は主電源信号の第1の範囲の振幅よりも大きい。第1の発光回路及び第2の発光回路の組み合わせは、例えば直列組み合わせである。

30

## 【0010】

- ドライバの全高調波ひずみを減らすために、ドライバはバイパススイッチング回路及び適応回路を備える。バイパススイッチング回路は初期時間間隔の間にバイパス電流信号を導く。この初期時間間隔は主電源信号の振幅が初期範囲にある時間間隔である。バイパススイッチング回路は、切替可能な電流源を含む、又はバイパス電流信号を個別の電流源(スイッチング回路ごとの1つの個別の電流源)又は汎用電流源(2つ以上のスイッチング回路のための1つの汎用電流源)に導く。主電源信号の初期範囲の振幅は主電源信号の第1の範囲の振幅よりも小さい。適応回路は、初期時間間隔の間にバイパス電流信号の振幅を適応させ、第1の時間間隔の間に第1の電流信号の振幅を適応させ、第2の時間間隔の間に第2の電流信号の振幅を適応させる。

40

## 【0011】

- そのため、U S 2 0 1 2 / 0 2 6 2 0 7 5 A 1と比較して、主電源信号の周期の大部分において電流信号が取り出され、この電流信号は時間間隔ごとに一定ではないが、この時間間隔の間に適応される。結果として、ドライバの全高調波ひずみを更に減らすことができる。これは大きな改善である。

50

**【 0 0 1 2 】**

ドライバの一実施形態は、バイパス電流信号が第1の発光回路を通過せず、かつ第2の発光回路を通過しないことにより規定される。初期時間間隔の間、発光回路は光を発しておらず、バイパス電流信号が取り出されて、例えば全高調波ひずみが減る。第1の時間間隔の間、第1の発光回路は光を発しており、第2の発光回路は光を発していない。第2の時間間隔の間、第1及び第2の発光回路の両方が光を発している。第3の発光回路等及び第3の時間間隔等が排除されるべきではない。

**【 0 0 1 3 】**

ドライバの一実施形態は、前記適応が主電源信号の振幅から導かれた情報に応じた適応を含むことにより規定される。好ましくは、初期時間間隔の間のバイパス電流信号の振幅、第1の時間間隔の間の第1の電流信号の振幅及び第2の時間間隔の間の第2の電流信号の振幅は、主電源信号の（瞬時の）振幅から導かれた情報に応じて適応される。例えば、主電源信号の振幅が比較的小幅（大幅）に変化している場合は、対応する電流信号の振幅は比較的小幅（大幅）に適応される。10

**【 0 0 1 4 】**

ドライバの一実施形態は、前記適応が、主電源信号の各範囲の振幅が増加している場合は各電流信号の振幅の増加を含み、主電源信号の各範囲の振幅が減少している場合は各電流信号の振幅の減少を含む適応を含むことにより規定される。好ましくは、主電源信号の各範囲の振幅が増加している（減少している）場合は、各電流信号の振幅も増加（減少）される。20

**【 0 0 1 5 】**

ドライバの一実施形態は、前記適応が主電源信号の振幅から導かれた情報に応じて電流信号の振幅を整形することを含むことにより規定される。好ましくは、初期時間間隔の間のバイパス電流信号の振幅、第1の時間間隔の間の第1の電流信号の振幅及び第2の時間間隔の間の第2の電流信号の振幅は、主電源信号の（瞬時の）振幅から導かれた情報に応じて整形される。例えば、主電源信号の振幅が第1（第2）の形状を有する場合は、対応する電流信号の振幅にも第1（第2）の形状が与えられる。

**【 0 0 1 6 】**

ドライバの一実施形態は、前記適応が各電流信号の振幅を整形することを含み、各電流信号の整形された振幅が主電源信号の各範囲の振幅の形状とほぼ同一であることにより規定される。好ましくは、最小の全高調波ひずみを得るために、各電流信号の振幅の形状は主電源信号の各範囲の振幅の形状とほぼ同一である。ここでほぼ同一とは、形状の両始点又は両終点が一致するように始点及び終点を拡大縮小した後、形状より下の面が20%未満、好ましくは10%未満、最も好ましくは5%未満異なるべきであることを意味する。30

**【 0 0 1 7 】**

ドライバの一実施形態は、バイパススイッチング回路がバイパス電流スイッチを含み、かつバイパス電流スイッチを制御するためのボーダー制御回路を含み、第1のスイッチング回路が第1の電流スイッチを含み、かつ第1の電流スイッチを制御するための第1の制御回路を含み、第2のスイッチング回路が第2の電流スイッチを含み、かつ第2の電流スイッチを制御するための第2の制御回路を含むことにより規定される。バイパス電流スイッチはバイパス電流信号を導く。第1の電流スイッチは第1の電流信号を導く。第2の電流スイッチは第2の電流信号を導く。ボーダー制御回路は初期範囲を規定する。第1の制御回路は第1の範囲を規定する。第2の制御回路は第2の範囲を規定する。ボーダーという言葉は、発光回路が光を発する時間の間の相互接続期間を表すことを意図する。40

**【 0 0 1 8 】**

ドライバの一実施形態は、ボーダー制御回路がボーダー制御スイッチと、3つの抵抗器及び第1及び第2の中間接点を含むボーダー電圧分割器とからなり、バイパス電流スイッチの制御電極が第1の中間接点に結合され、ボーダー制御スイッチの制御電極が第2の中間接点に結合され、第1の制御回路が、第1の制御スイッチと、3つの抵抗器及び第1及び第2の中間接点を含む第1の電圧分割器とからなり、第1の電流スイッチの制御電極が50

第1の中間接点に結合され、第1の制御スイッチの制御電極が第2の中間接点に結合され、第2の制御回路が、第2の制御スイッチと、3つの抵抗器及び第1及び第2の中間接点を含む第2の電圧分割器とからなり、第2の電流スイッチの制御電極が第1の中間接点に結合され、第2の制御スイッチの制御電極が第2の中間接点に結合されることにより規定される。これは、各スイッチング回路が、例えばトランジスタ等の2つのスイッチと、1つの3つの抵抗器からなる電圧分割器とから構成されるという事実により、単純で、低費用かつロバストな実施形態である。

#### 【0019】

ドライバの一実施形態は、初期範囲を規定するボーダー電圧分割器の3つの抵抗器のうちの1つ以上の値、第1の範囲を規定する第1の電圧分割器の3つの抵抗器のうちの1つ以上の値、及び第2の範囲を規定する第2の電圧分割器の3つの抵抗器のうちの1つ以上の値により規定される。これは、各スイッチング回路において、3つの抵抗器からなる電圧分割器が範囲を規定するという事実により、単純で、低費用かつロバストな実施形態である。

10

#### 【0020】

ドライバの一実施形態は、適応回路が、規定信号に応じて、バイパス電流信号、第1の電流信号及び第2の電流信号の振幅を規定する電流源を備え、適応回路が更に、主電源信号の振幅の検出に応じて規定信号を電流源に供給する規定回路を備えることにより規定される。これは、各電流信号の振幅を規定するために1つの汎用電流源が全てのスイッチング回路のために使用されるという事実により、単純で、低費用かつロバストな実施形態である。

20

#### 【0021】

ドライバの一実施形態は、電流源が抵抗器を含み、規定信号が電圧信号を含むことにより規定される。これは、抵抗器が単純で、低費用かつロバストであるという事実により、単純で、低費用かつロバストな実施形態である。

#### 【0022】

ドライバの一実施形態は、電流源が更に抵抗器に直列結合された1つ以上の電圧規定コンポーネントを含むことにより規定される。これは、ダイオード又はツェナーダイオード等の電圧規定コンポーネントが単純で、低費用かつロバストであるという事実により、単純で、低費用かつロバストな実施形態である。

30

#### 【0023】

電流源のより複雑な実施形態が排除されるべきではない。従って、電流源の多くの他の実施形態も考えられる。

#### 【0024】

ドライバの一実施形態は、規定回路が、2つの抵抗器及び1つの中間接点を含む入力電圧分割器と、反転トランジスタと、3つの抵抗器並びに第1及び第2の中間接点を含むインターフェース電圧分割器と、負の伝達を有するプログラマブルレギュレータと、2つの抵抗器を含む出力抵抗回路網と、出力トランジスタとを含み、反転トランジスタの制御電極が前記検出のために入力電圧分割器の中間接点に結合され、反転トランジスタの主電極がインターフェース電圧分割器の第1の中間接点に結合され、プログラマブルレギュレータの制御入力がインターフェース電圧分割器の第2の中間接点に結合され、プログラマブルレギュレータの出力が出力トランジスタの主電極に結合され、プログラマブルレギュレータの制御入力及び出力が出力抵抗回路網の2つの抵抗器のうちの1つに結合され、出力トランジスタの制御電極が電流源に結合されることにより規定される。当然のことながら、反転トランジスタ及び負の伝達を有するプログラマブルレギュレータの組み合わせは正の伝達を有する。従って、例えば非反転トランジスタ及び正の伝達を有するプログラマブルレギュレータの組み合わせ等の規定回路の多くの他の実施形態も考えられる。

40

#### 【0025】

第2の態様によれば、上で規定されたドライバを含み、更に発光回路を含むデバイスが提供される。発光回路は、例えばあらゆる種類及び組み合わせの1つ以上の発光ダイオード

50

ドを含む発光ダイオード回路を含む。

**【0026】**

第3の態様によれば、発光回路を駆動するドライバを制御するための方法が提供され、ドライバは、

- 初期時間間隔の間にバイパス電流信号を導くためのバイパススイッチング回路であって、初期時間間隔の間はドライバに供給するための主電源信号の振幅が初期範囲にあるバイパススイッチング回路と、

- 第1の時間間隔の間に第1の発光回路を通じて第1の電流信号を導くための第1のスイッチング回路であって、主電源信号の振幅は第1の時間間隔の間は第1の範囲にあり、主電源信号の第1の範囲の振幅は主電源信号の初期範囲の振幅よりも大きい第1のスイッチング回路と、

- 第2の時間間隔の間に第1の発光回路及び第2の発光回路の直列接続を通じて第2の電流信号を導くための第2のスイッチング回路であって、主電源信号の振幅は第2の時間間隔の間は第2の範囲にあり、主電源信号の第2の範囲の振幅は主電源信号の第1の範囲の振幅よりも大きい第2のスイッチング回路と、を含み、

方法は、初期時間間隔の間にバイパス電流信号の振幅を適応させ、第1の時間間隔の間に第1の電流信号の振幅を適応させ、第2の時間間隔の間に第2の電流信号の振幅を適応させるステップを含む。

**【0027】**

洞察は、発光回路のセグメント駆動は全高調波ひずみに関与するというものである。基本的な思想は、第1の発光回路を流れる第1の電流信号と第1及び第2の発光回路の組み合わせを流れる第2の電流信号とに加えて、バイパス電流が導入されるべきであること、及び前記電流の各1つを流れている間に適応させ、全高調波ひずみを減らすことができるということである。

**【0028】**

改良されたドライバを提供する課題は解決されている。更なる利点は政府規制がより容易に満たされ得ることである。

**【0029】**

本発明のこれら及び他の態様は、以下に説明される実施形態から明らかとなり、以下に説明される実施形態を参照して理解されるであろう。

**【図面の簡単な説明】**

**【0030】**

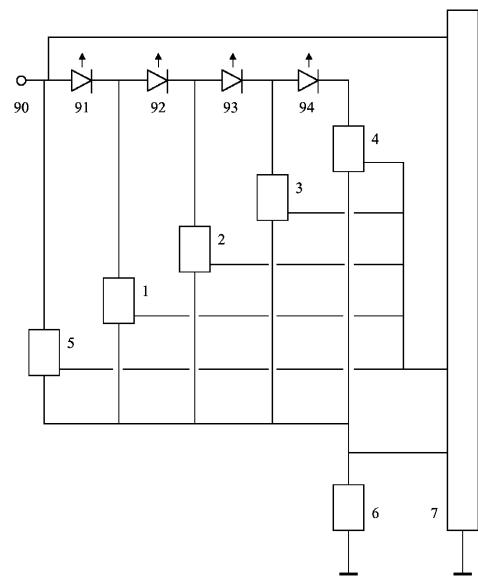

**【図1】**図1は、ドライバの一実施形態を示す。

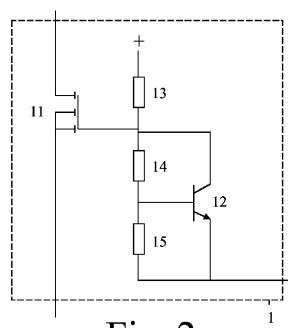

**【図2】**図2は、第1のスイッチング回路の一実施形態を示す。

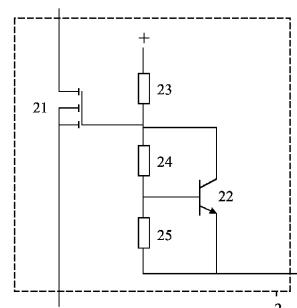

**【図3】**図3は、第2のスイッチング回路の一実施形態を示す。

**【図4】**図4は、バイパススイッチング回路の一実施形態を示す。

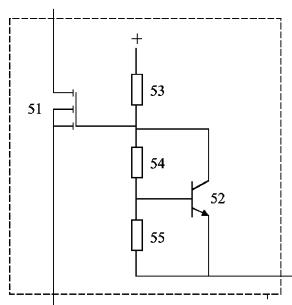

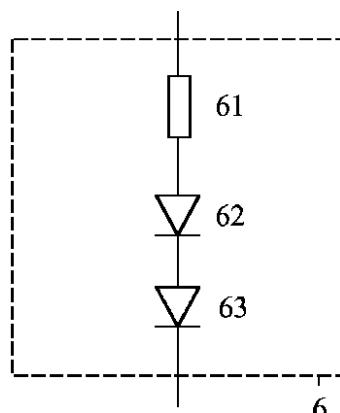

**【図5】**図5は、電流源の一実施形態を示す。

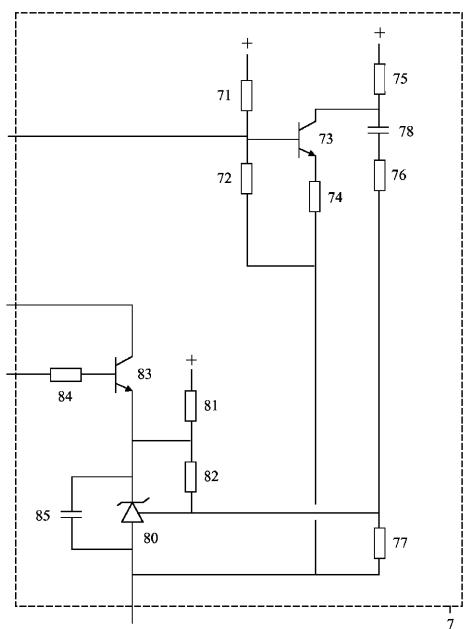

**【図6】**図6は、規定回路の一実施形態を示す。

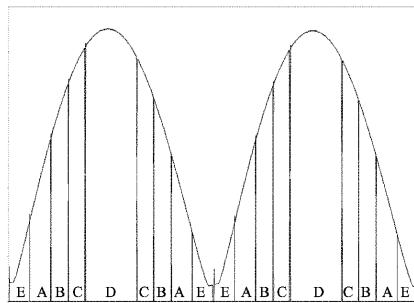

**【図7】**図7は、電流信号の振幅を示す。

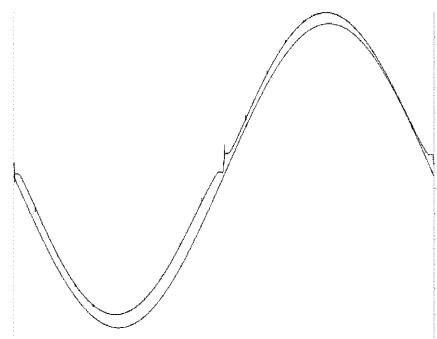

**【図8】**図8は、電流及び電圧信号の振幅を示す。

**【発明を実施するための形態】**

**【0031】**

図1には、ドライバ1～7の一実施形態が示されている。このドライバ1～7は、例えば4つの発光ダイオード回路等の4つの発光回路91～94を駆動することができる。これらの4つの発光回路91～94は互いに直列に結合される。発光回路91は更に、例えば整流された50Hz正弦波電圧信号又は整流された60Hz正弦波電圧信号等の主電源信号を受信する主電源端子90に結合される。主電源端子90は更に、適応回路6、7の第1の端子と、適応回路6、7の第2及び第3の端子に更に結合されたバイパススイッチング回路5とに結合される。第1及び第2の発光回路91、92間の相互接続部は更に、適応回路6、7の第2及び第3の端子に更に結合された第1のスイッチング回路1に結合

10

20

30

40

50

される。第2及び第3の発光回路92、93間の相互接続部は更に、適応回路6、7の第2及び第3の端子に更に結合された第2のスイッチング回路2に結合される。第3及び第4の発光回路93、94間の相互接続部は更に、適応回路6、7の第2及び第3の端子に更に結合された第3のスイッチング回路3に結合される。第4の発光回路94は更に、適応回路6、7の第2及び第3の端子に更に結合された第4のスイッチング回路4に結合される。

#### 【0032】

図2には、第1のスイッチング回路1の一実施形態が示されている。第1のスイッチング回路1は、例えばMOSFET等の第1のスイッチングトランジスタ等の例えは第1の電流スイッチ11と、例えば第1の電流スイッチ11を制御するための第1の制御回路12～15とからなる。第1の制御回路12～15は、例えばバイポーラトランジスタ等の第1の制御トランジスタ等の第1の制御スイッチ12と、例えば3つの抵抗器及び第1及び第2の中間接点を含む第1の電圧分割器13～15とからなる。第1の電流スイッチ11の制御電極は抵抗器13及び14間の第1の中間接点に結合され、第1の制御スイッチ12の制御電極は抵抗器14及び15間の第2の中間接点に結合される。抵抗器13は更に電圧源に結合され、抵抗器15は更に第1の制御スイッチ12の第1の主電極に結合される。第1の制御スイッチ12の第2の主電極は第1の中間接点に結合される。

#### 【0033】

図3には、第2のスイッチング回路2の一実施形態が示されている。第2のスイッチング回路2は、例えばMOSFET等の第2のスイッチングトランジスタ等の例えは第2の電流スイッチ21と、例えば第2の電流スイッチ21を制御するための第2の制御回路22～25とからなる。第2の制御回路22～25は、例えばバイポーラトランジスタ等の第2の制御トランジスタ等の第2の制御スイッチ22と、例えば3つの抵抗器及び第1及び第2の中間接点を含む第2の電圧分割器23～25とからなる。第2の電流スイッチ21の制御電極は抵抗器23及び24間の第1の中間接点に結合され、第2の制御スイッチ22の制御電極は抵抗器24及び25間の第2の中間接点に結合される。抵抗器23は更に電圧源に結合され、抵抗器25は更に第2の制御スイッチ22の第1の主電極に結合される。第2の制御スイッチ22の第2の主電極は第1の中間接点に結合される。

#### 【0034】

図4には、バイパススイッチング回路5の一実施形態が示されている。バイパススイッチング回路5は、例えばMOSFET等のボーダースイッチングトランジスタ等の例えはバイパス電流スイッチ51と、例えばバイパス電流スイッチ51を制御するためのボーダー制御回路52～55とからなる。ボーダー制御回路52～55は、例えばバイポーラトランジスタ等のボーダー制御トランジスタ等のボーダー制御スイッチ52と、例えば3つの抵抗器及び第1及び第2の中間接点を含むボーダー電圧分割器53～55とからなる。バイパス電流スイッチ51の制御電極は抵抗器53及び54間の第1の中間接点に結合され、ボーダー制御スイッチ52の制御電極は抵抗器54及び55間の第2の中間接点に結合される。抵抗器53は更に電圧源に結合され、抵抗器55は更にボーダー制御スイッチ52の第1の主電極に結合される。ボーダー制御スイッチ52の第2の主電極は第1の中間接点に結合される。

#### 【0035】

第3及び第4のスイッチング回路3及び4は、電圧分割器の1つ以上の値を別にすれば、図2～4に示されたスイッチング回路1、2及び5と同様に実現される。

#### 【0036】

適応回路6、7は、例えば、規定信号に応じて、バイパススイッチング回路5を流れるバイパス電流信号の(瞬時の)振幅、第1のスイッチング回路1を流れる第1の電流信号の(瞬時の)振幅、第2のスイッチング回路2を流れる第2の電流信号の(瞬時の)振幅、第3のスイッチング回路3を流れる第3の電流信号の(瞬時の)振幅、及び第4のスイッチング回路4を流れる第4の電流信号の(瞬時の)振幅を規定する電流源6を備える。適応回路6、7は更に、主電源信号の(瞬時の)振幅の検出に応答して規定信号を電流源

10

20

30

40

50

6に供給するための規定回路7を備える。

**【0037】**

図5には、電流源6の一実施形態が示されている。電流源6は、抵抗器61と、例えばダイオード又はツェナーダイオード等の2つの電圧規定コンポーネント62、63との直列結合を含む。規定信号はこの場合電圧信号を含む。電流源6はバイパス電流スイッチ51の第1の主電極に結合され、バイパス電流スイッチ51の第2の主電極は主電源端子90に結合される。電流源6は第1の電流スイッチ11の第1の主電極に結合され、第1の電流スイッチ11の第2の主電極は第1及び第2の発光回路91、92間の相互接続部に結合される。電流源6は第2の電流スイッチ21の第1の主電極に結合され、第2の電流スイッチ21の第2の主電極は第2及び第3の発光回路92、93間の相互接続部に結合される。同様に、電流源6は図面等に示されていない第3及び第4の電流スイッチの第1の主電極に結合される。電流源6は更に接地に結合される。

10

**【0038】**

図6には、規定回路7の一実施形態が示されている。規定回路7は、例えば2つの抵抗器と、適応回路6、7の第1の端子を構成する中間接点とからなる入力電圧分割器71、72を備え、第1の端子は主電源端子90に結合される。規定回路7は更に、例えば反転トランジスタ73を備える。反転トランジスタ73の制御電極は入力電圧分割器71、72の中間接点に結合され、主電源信号の(瞬時の)振幅が検出される。抵抗器71は更に電圧源に結合され、抵抗器72は更に接地に結合される。反転トランジスタ73の第1の主電極は抵抗器74を介して接地に結合される。反転トランジスタ73の第2の主電極は、3つの抵抗器と、第1及び第2の中間接点とからなるインターフェース電圧分割器75～77の第1の中間接点に結合される。抵抗器75は更に電圧源に結合され、抵抗器77は更に接地に結合される。抵抗器75及び76の間に、主電源周波数用の短絡回路と考えられるコンデンサ78がある。第1の中間接点は、このコンデンサ78と抵抗器75の間にあり、抵抗器76及び77間の第2の中間接点は負の伝達を有するプログラマブルレギュレータ80の制御入力に結合される。プログラマブルレギュレータ80の出力は出力トランジスタ83の第1の主電極に結合される。プログラマブルレギュレータ80の制御入力及び出力は、出力抵抗回路網81、82の抵抗器82の異なる側に結合される。プログラマブルレギュレータ80は更に接地に結合される。抵抗器81は更に電圧源に結合される。出力トランジスタ83の制御電極は抵抗器84を介して電流源6に結合される。出力トランジスタ83の第2の主電極は、第1、第2及びボーダー制御スイッチ12、22及び52の第1の主電極(並びに図面には示されていない第3及び第4の制御スイッチの第1の主電極)に結合される。プログラマブルレギュレータ80と並列に、フィルタリングのためのコンデンサ85がある。出力トランジスタ83の第2の主電極は適応回路6、7の第2の端子を構成する。抵抗器84の一方の側は出力トランジスタ83の制御電極に結合され、他方の側は適応回路6、7の第3の端子を構成する。

20

30

**【0039】**

図7には、電流信号、例えば初期時間間隔Eの間にバイパススイッチング回路5を流れるバイパス電流信号、第1の時間間隔Aの間に第1のスイッチング回路1を流れる第1の電流信号、第2の時間間隔Bの間に第2のスイッチング回路2を流れる第2の電流信号、第3の時間間隔Cの間に第3のスイッチング回路3を流れる第3の電流信号、及び第4の時間間隔Dの間に第4のスイッチング回路4を流れる第4の電流信号の振幅が示されている。

40

**【0040】**

図8には、電流及び電圧信号、例えば整流器回路の入力における入力電圧信号(滑らかな線で表された電圧信号)及び整流器回路の入力を流れる入力電流信号(小さな凸凹のある線で表された電流信号)の振幅が示されている。整流器回路の出力は主電源端子90に結合され、例えば整流された50Hz正弦波電圧信号又は整流された60Hz正弦波電圧信号等の主電源信号を供給し、初期時間間隔Eの間にバイパス電流信号を供給し、次に第1の時間間隔Aの間に第1の電流信号を供給し、次に第2の時間間隔Bの間に第2の電流

50

信号を供給し、次に第3の時間間隔Cの間に第3の電流信号を供給し、次に第4の時間間隔Dの間に第4の電流信号を供給する。

**【0041】**

ドライバ1～7は次のように機能する。各発光回路91～94は、発光を開始するのにその接点間に例えば60ボルトの最小電圧振幅を必要とする。主電源信号が60ボルト未満の電圧振幅（初期時間間隔Eの間の初期範囲）を有する限りは、ボーダー制御回路52～55はバイパス電流スイッチ51を導電状態にし、バイパス電流信号が主電源端子90、バイパス電流スイッチ51及び電流源6を通って接地に流れる。このバイパス電流信号の振幅は以下で更に考察されるように電流源6により規定される。光は発されない。

**【0042】**

主電源信号が60ボルト～120ボルトの電圧振幅（第1の時間間隔Aの間の第1の範囲）を有すると、ボーダー制御回路52～55はバイパス電流スイッチ51を非導電状態にし、第1の制御回路12～15は第1の電流スイッチ11を導電状態にし、第1の電流信号が主電源端子90、第1の発光回路91、第1の電流スイッチ11及び電流源6を通って接地に流れる。この第1の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1の発光回路91は光を発している。

10

**【0043】**

主電源信号が120ボルト～180ボルトの電圧振幅（第2の時間間隔Bの間の第2の範囲）を有すると、第1の制御回路12～15は第1の電流スイッチ11を非導電状態にし、第2の制御回路22～25は第2の電流スイッチ21を導電状態にし、第2の電流信号が主電源端子90、第1及び第2の発光回路91、92、第2の電流スイッチ21及び電流源6を通って接地に流れる。この第2の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1及び第2の発光回路91、92は光を発している。

20

**【0044】**

主電源信号が180ボルト～240ボルトの電圧振幅（第3の時間間隔Cの間の第3の範囲）を有すると、第2のスイッチング回路2は非活性化され、第3のスイッチング回路3は活性化され（ボーダー、第1及び第2のスイッチング回路5、1及び2については上述されている）、第3の電流信号が主電源端子90、第1、第2及び第3の発光回路91～93、第3のスイッチング回路3及び電流源6を通って接地に流れる。この第3の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1、第2及び第3の発光回路91～93は光を発している。

30

**【0045】**

主電源信号が240ボルト～300ボルト及び300ボルト～240ボルトの電圧振幅（第4の時間間隔Dの間の第4の範囲）を有する限りは、第3のスイッチング回路3は非活性化され、第4のスイッチング回路4は活性化され（上述されている）、第4の電流信号が主電源端子90、第1、第2、第3及び第4の発光回路91～94、第4のスイッチング回路4及び電流源6を通って接地に流れる。この第4の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1、第2、第3及び第4の発光回路91～94は光を発している。

40

**【0046】**

主電源信号が240ボルト～180ボルトの電圧振幅（第3の時間間隔Cの間の第3の範囲）を有すると、第4のスイッチング回路4は非活性化され、第3のスイッチング回路3は活性化され、第3の電流信号が主電源端子90、第1、第2及び第3の発光回路91～93、第3のスイッチング回路3並びに電流源6を通って接地に流れる。この第3の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1、第2及び第3の発光回路91～93は光を発している。

**【0047】**

主電源信号が180ボルト～120ボルトの電圧振幅（第2の時間間隔Bの間の第2の範囲）を有すると、第3のスイッチング回路3は非活性化され、第2のスイッチング回路2は活性化され、第2の電流信号が主電源端子90、第1及び第2の発光回路91、92

50

、第2のスイッチング回路2並びに電流源6を通って接地に流れる。この第2の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1及び第2の発光回路91、92は光を発している。

#### 【0048】

主電源信号が120ボルト～60ボルトの電圧振幅（第1の時間間隔Aの間の第1の範囲）を有すると、第2のスイッチング回路2は非活性化され、第1のスイッチング回路1は活性化され、第1の電流信号が主電源端子90、第1の発光回路91、第1のスイッチング回路1及び電流源6を通って接地に流れる。この第1の電流信号の振幅は以下で更に考察されるように電流源6により規定される。第1の発光回路91は光を発している。

#### 【0049】

主電源信号が60ボルト未満の電圧振幅（初期時間間隔Eの間の初期範囲）を有する限りは、第1のスイッチング回路1は非活性化され、バイパススイッチング回路5は活性化され、バイパス電流信号が主電源端子90、バイパススイッチング回路5及び電流源6を通って接地に流れる。このバイパス電流信号の振幅は以下で更に考察されるように電流源6により規定される。光は発されない。

#### 【0050】

これらの範囲を実現するために、各スイッチング回路の各上部抵抗器は220kに等しい値を有し、各下部抵抗器は68kに等しい値を有し、各スイッチング回路5、1、2、3、4の各中央の抵抗器は特にこの順序で10k、100k、180k、270k及び390kに等しい値を有する。これらの範囲を実現する他の値及び他のやり方が排除されるべきではない。同様に、例示的な60ボルト以外の電圧値及び他の段階値が排除されるべきではない。

#### 【0051】

そのため、バイパススイッチング回路5は初期時間間隔Eの間にバイパス電流信号を導く。主電源信号の振幅は初期時間間隔Eの間は初期範囲にある。第1のスイッチング回路1は、第1の時間間隔Aの間に第1の発光回路91を通じて第1の電流信号を導く。主電源信号の振幅は第1の時間間隔Aの間は第1の範囲にある。主電源信号の第1の範囲の振幅は主電源信号の初期範囲の振幅よりも大きい。第2のスイッチング回路2は、第2の時間間隔Bの間に第1の発光回路91及び第2の発光回路92の組み合わせを通じて第2の電流信号を導く。主電源信号の振幅は第2の時間間隔Bの間は第2の範囲にある。主電源信号の第2の範囲の振幅は主電源信号の第1の範囲の振幅よりも大きい。

#### 【0052】

従来技術の状況では、電流信号の振幅は固定された一定の値を有していた。本発明によれば、ドライバ1～7は初期時間間隔Eの間にバイパス電流信号の振幅を適応させ、第1の時間間隔Aの間に第1の電流信号の振幅を適応させ、第2の時間間隔Bの間に第2の電流信号の振幅を適応させる等の適応回路6、7を備える。結果として、ドライバ1～7の全高調波ひずみを更に減らすことができる。

#### 【0053】

好ましくは、例えば前記適応は、主電源信号の（瞬時の）振幅から導かれた情報に応じた適応を含む。及び／又は、前記適応は、主電源信号の各範囲の振幅が増加している場合は各電流信号の振幅の増加を含み、主電源信号の各範囲の振幅が減少している場合は各電流信号の振幅の減少を含む適応を含む。

#### 【0054】

好ましくは、例えば前記適応は、主電源信号の（瞬時の）振幅から導かれた情報に応じて電流信号の振幅を整形することを含む。及び／又は、前記適応は、各電流信号の振幅を整形することを含み、各電流信号の整形された振幅は主電源信号の各範囲の振幅の形状とほぼ同一である。これによって全高調波ひずみが最小になり、例えば図5及び図6に示された適応回路6、7の実施形態によってこれは実現される。

#### 【0055】

適応回路6、7は、規定信号に応答して電流信号の振幅を規定する電流源6と、主電源

10

20

30

40

50

信号の（瞬時の）振幅の検出に応答して規定信号を電流源 6 に供給する規定回路 7 となる。この検出は入力電圧分割器 7 1、7 2 を介して行われる。反転トランジスタ 7 2 は（抵抗器 7 4 ~ 7 7 との併用により）この検出を反転させる。反転された検出はプログラマブルレギュレータ 8 0 の制御入力に（抵抗器 7 5 ~ 7 7 を介して）供給される。このプログラマブルレギュレータ 8 0 は負の伝達を有するという事実により、このプログラマブルレギュレータ 8 0 の出力における出力電圧は主電源信号の振幅に追従する。プログラマブルレギュレータ 8 0 の出力は出力トランジスタ 8 3 の第 1 の主電極（エミッタ）に結合されるという事実、及び出力トランジスタ 8 3 の制御電極（ベース）から第 1 の主電極（エミッタ）まで一定電圧が存在するという事実により、出力トランジスタ 8 3 の制御電極（ベース）における電圧は主電源信号の振幅に追従する。電流源 6 は抵抗器 6 1 を含むという事実により、電流源 6 により規定される電流信号の振幅は主電源信号の振幅に追従する。結果として、図 8 に示されるように、滑らかな線で表された入力電圧信号の振幅及び小さな凸凹のある線で表された入力電流信号の振幅は形状が相対的に同一になり、最小の全高調波ひずみが実現される。

#### 【0056】

ドライバは電磁干渉フィルターの調整及びチューニングを必要としない。ドライバは 0.99 超の高力率を有し、磁気コンポーネントを必要としない。ドライバはフィードフォワード回路として動作し、遅延及び不安定性を示すフィードバック回路としては動作しない。ドライバはほぼ純粋な負荷抵抗を呈し、位相シフトは導入されない。

#### 【0057】

最小限の状況では、2つの発光回路、1つのバイパススイッチング回路、第1及び第2のスイッチング回路並びに適応回路がある。より拡張された状況では、より多くの発光回路及びより多くのスイッチング回路が存在する。

#### 【0058】

電流源、規定回路、及びスイッチング回路は例示的に示されており、多くの他の実施形態が考えられ、排除されるべきではない。電流源は、例えばデジタル制御された電流源であり、規定回路は、規定信号がデジタル信号等のプロセッサである。

#### 【0059】

第1及び第2の要素は、第3の要素を介して間接的に結合することができ、第3の要素を介在させずに直接結合することもできる。

#### 【0060】

要約すると、ドライバ 1 ~ 7 は、発光回路 9 1 ~ 9 4 を順次駆動するために各時間間隔の間に各電流信号を導くための各スイッチング回路 1、2 を含む。各時間間隔は、主電源信号の振幅は各時間間隔の間は各範囲にあるという事実により規定される。適応回路 6、7 は、各時間間隔の間に各電流信号の振幅を適応させ、全高調波ひずみを減らす。前記適応は、主電源信号の振幅から導かれた情報に応じた適応を含み、また、主電源信号の振幅から導かれた情報に応じて電流信号の振幅を整形することを含む。好ましくは、各電流信号の整形された振幅は主電源信号の各範囲の振幅の形状とほぼ同一である。適応回路 6、7 は、電流源 6 及び規定回路 7 となる。

#### 【0061】

本発明が添付図面及び上記の説明の中で詳細に例示され説明されてきたが、斯かる例示及び説明は制限的ではなく説明的又は例示的と見なされるべきであり、本発明は開示された実施形態に限定されない。特許請求の範囲に記載の本発明を実施する際、図面、本開示、及び添付の特許請求の範囲を検討することにより、開示された実施形態に対する他の改変形態が当業者によって理解され、もたらされ得る。特許請求の範囲では、「c o m p r i s i n g（含む）」という語は他の要素又はステップを排除せず、不定冠詞「a」又は「a n」は複数形を排除しない。或る手段が互いに異なる従属請求項の中で列挙されているという単なる事実は、それらの手段の組み合わせが有利に使用され得ないことを示すものではない。特許請求の範囲の中の如何なる参照符号も、範囲を限定するものとして解釈すべきではない。

【図1】

Fig. 1

【図2】

Fig. 2

【図3】

Fig. 3

【図4】

Fig. 4

【図5】

Fig. 5

【図6】

Fig. 6

【図7】

Fig. 7

【図8】

Fig. 8

---

フロントページの続き

(72)発明者 カールマン ヘンリクス マリウス ジョセフ マリア

オランダ国 5656 アーエー アイントホーフェン ハイ テク キャンパス 5

(72)発明者 カート ラルフ

オランダ国 5656 アーエー アイントホーフェン ハイ テク キャンパス 5

審査官 百瀬 正之

(56)参考文献 特開2006-244848(JP,A)

特開2013-179288(JP,A)

米国特許出願公開第2013/0293129(US,A1)

特開2012-227181(JP,A)

特開2013-161937(JP,A)

特開平11-191964(JP,A)

特表2012-529124(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64

H05B 45/00