## (12) 发明专利

(10) 授权公告号 CN 112673466 B

(45) 授权公告日 2024.02.23

(21) 申请号 201980058845.7

(22) 申请日 2019.08.29

(65) 同一申请的已公布的文献号

申请公布号 CN 112673466 A

(43) 申请公布日 2021.04.16

(30) 优先权数据

2018-169878 2018.09.11 JP

(85) PCT国际申请进入国家阶段日

2021.03.09

(86) PCT国际申请的申请数据

PCT/JP2019/033935 2019.08.29

(87) PCT国际申请的公布数据

W02020/054447 JA 2020.03.19

(73) 专利权人 株式会社电装

地址 日本爱知县

(72) 发明人 赤井智喜 利田祐麻 妹尾贤

大河原淳(74) 专利代理机构 永新专利商标代理有限公司

72002

专利代理人 吕文卓

(54) 发明名称

半导体装置

(57) 摘要

将IGBT用第1沟槽(13a)中的最靠FWD用沟槽(13b)侧的沟槽(133a)的中心与FWD用第1沟槽(13b)中的最靠IGBT用沟槽侧(13a)的沟槽(133b)的中心之间的距离设为分离单元间距(W1)。将IGBT用第1沟槽彼此(131a)的中心间的最小距离设为IGBT用第1沟槽间距(D1a),将相邻的IGBT用第2沟槽(132b)彼此的中心间的最小距离设为IGBT用第2沟槽间距(D2a),将相邻的FWD用第1沟槽(131b)彼此的中心间的最小距离设为FWD用第1沟槽间距(D1b),将相邻的FWD用第2沟槽(132b)彼此的中心间的最小距离设为FWD用第2沟槽间距(D2b)。并且,分离单元间距(W1)比各沟槽间距(D1a、D2a、D1b、D2b)窄。

(51) Int.CI.

H01L 21/76 (2006.01)

H01L 21/8234 (2006.01)

H01L 27/06 (2006.01)

H01L 29/739 (2006.01)

H01L 29/78 (2006.01)

H01L 29/861 (2006.01)

H01L 29/868 (2006.01)

H01L 29/872 (2006.01)

(56) 对比文件

JP 2012151470 A, 2012.08.09

JP 2016197678 A, 2016.11.24

US 2018108737 A1, 2018.04.19

JP 2016225560 A, 2016.12.28

US 2017352747 A1, 2017.12.07

JP 2010263149 A, 2010.11.18

WO 2016114131 A1, 2016.07.21

CN 103311272 A, 2013.09.18

JP 2012049499 A, 2012.03.08

CN 103258846 A, 2013.08.21

JP 2010135677 A, 2010.06.17

(续)

审查员 许晓燕

权利要求书6页 说明书12页 附图11页

CN 112673466 B

[转续页]

[接上页]

(56) 对比文件

CN 105679814 A, 2016.06.15

CN 106463504 A, 2017.02.22

CN 103733344 A, 2014.04.16

US 2018047725 A1, 2018.02.15

CN 107534053 A, 2018.01.02

CN 104160512 A, 2014.11.19

US 2006286751 A1, 2006.12.21

JP 2017011171 A, 2017.01.12

JP 2009021557 A, 2009.01.29

JP 2014063960 A, 2014.04.10

Benedikt Gburek\*, Veit

Wagner. Influence of the semiconductor thickness on the charge carrier mobility in P3HT organic field-effect transistors in top-gate architecture on flexible substrates. *Organic Electronics*. 2011, 全文.

翟东媛;赵毅;蔡银飞;施毅;郑有炓.沟槽形状对硅基沟槽式肖特基二极管电学特性的影响. *物理学报*. 63(12) ,全文.

1. 一种半导体装置,在共通的半导体衬底(10)上形成有IGBT区域(1)和FWD区域(2),其特征在于,

具备:

第1导电型的漂移层(11);

第2导电型的基体层(12),形成在上述漂移层上;

多个沟槽栅构造,具有在将上述基体层贯通的沟槽(13a、13b)的壁面形成的栅极绝缘膜(14)和在上述栅极绝缘膜上形成的栅极电极;

第1导电型的发射极区域(19),在上述基体层的表层部以与形成于上述IGBT区域的上述沟槽相接的方式形成;

第2导电型的集电极层(16),隔着上述漂移层而形成在上述基体层侧的相反侧;

第1导电型的阴极层(17),隔着上述漂移层而形成在上述基体层的相反侧并且与上述集电极层邻接;

第1电极,与上述基体层及上述发射极区域电连接;以及

第2电极,与上述集电极层及上述阴极层电连接;

上述集电极层上的区域被设为上述IGBT区域,上述阴极层上的区域被设为上述FWD区域;

上述沟槽是形成于上述IGBT区域的配置作为上述栅极电极的第1栅极电极(15a)的IGBT用沟槽(13a),和形成于上述FWD区域且配置独立于上述第1栅极电极而被控制的作为上述栅极电极的第2栅极电极(15b)的FWD用沟槽(13b);

上述IGBT用沟槽是在第1方向上延伸的IGBT用第1沟槽(131a)和在第2方向上延伸的IGBT用第2沟槽(132a)相连通而得到的格子状,上述第1方向沿着上述半导体衬底的面方向上的一个方向,上述第2方向与上述半导体衬底的面方向上的上述第1方向交叉;

上述FWD用沟槽是在上述第1方向上延伸的FWD用第1沟槽(131b)和在上述第2方向上延伸的FWD用第2沟槽(132b)相连通而得到的格子状;

将上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽(133a)的中心与上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽(133b)的中心之间设为分离单元区域(3a)并且将上述分离单元区域的上述第2方向上的距离设为分离单元间距(W1),将相邻的上述IGBT用第1沟槽彼此的中心间的最小距离设为IGBT用第1沟槽间距(D1a),将相邻的上述IGBT用第2沟槽彼此的中心间的最小距离设为IGBT用第2沟槽间距(D2a),将相邻的上述FWD用第1沟槽彼此的中心间的最小距离设为FWD用第1沟槽间距(D1b),将相邻的上述FWD用第2沟槽彼此的中心间的最小距离设为FWD用第2沟槽间距(D2b);

上述分离单元间距比上述IGBT用第1沟槽间距、上述IGBT用第2沟槽间距、上述FWD用第1沟槽间距、上述FWD用第2沟槽间距窄。

2. 如权利要求1所述的半导体装置,其特征在于,

在上述分离单元区域,形成有沿上述第1方向延伸的伪沟槽(23);

在上述伪沟槽(23),配置有伪绝缘膜(24)和伪电极(25)。

3. 一种半导体装置,在共通的半导体衬底(10)上形成有IGBT区域(1)和FWD区域(2),其特征在于,

具备:

第1导电型的漂移层(11)；

第2导电型的基体层(12),形成在上述漂移层上；

多个沟槽栅构造,具有在将上述基体层贯通的沟槽(13a、13b)的壁面形成的栅极绝缘膜(14)和在上述栅极绝缘膜上形成的栅极电极；

第1导电型的发射极区域(19),在上述基体层的表层部以与形成于上述IGBT区域的上述沟槽相接的方式形成；

第2导电型的集电极层(16),隔着上述漂移层而形成在上述基体层侧的相反侧；

第1导电型的阴极层(17),隔着上述漂移层而形成在上述基体层的相反侧并且与上述集电极层邻接；

第1电极,与上述基体层及上述发射极区域电连接;以及

第2电极,与上述集电极层及上述阴极层电连接；

上述集电极层上的区域被设为上述IGBT区域,上述阴极层上的区域被设为上述FWD区域；

上述沟槽是形成于上述IGBT区域的配置作为上述栅极电极的第1栅极电极(15a)的IGBT用沟槽(13a),和形成于上述FWD区域且配置独立于上述第1栅极电极而被控制的作为上述栅极电极的第2栅极电极(15b)的FWD用沟槽(13b)；

上述IGBT用沟槽是在第1方向上延伸的IGBT用第1沟槽(131a)和在第2方向上延伸的IGBT用第2沟槽(132a)相连通而得到的格子状,上述第1方向沿着上述半导体衬底的面方向上的一个方向,上述第2方向与上述半导体衬底的面方向上的上述第1方向交叉；

上述FWD用沟槽是在上述第1方向上延伸的FWD用第1沟槽(131b)和在上述第2方向上延伸的FWD用第2沟槽(132b)相连通而得到的格子状；

将上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽(133a)的中心与上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽(133b)的中心之间设为分离单元区域(3a),并且将上述分离单元区域的上述第2方向上的距离设为分离单元间距(W1)；

在上述分离单元区域,形成有沿上述第1方向延伸的1个伪沟槽(23)；

在上述伪沟槽(23),配置有伪绝缘膜(24)和伪电极(25)；

将相邻的上述IGBT用第1沟槽彼此的中心间的最小距离设为IGBT用第1沟槽间距(D1a),将相邻的上述IGBT用第2沟槽彼此的中心间的最小距离设为IGBT用第2沟槽间距(D2a),将相邻的上述FWD用第1沟槽彼此的中心间的最小距离设为FWD用第1沟槽间距(D1b),将相邻的上述FWD用第2沟槽彼此的中心间的最小距离设为FWD用第2沟槽间距(D2b),将上述伪沟槽的中心与和该伪沟槽相邻的上述IGBT用第1沟槽的中心之间的距离设为分离用第1沟槽间距(L1),将上述伪沟槽的中心与和该伪沟槽相邻的上述FWD用第1沟槽的中心之间的距离设为分离用第2沟槽间距(L2)；

上述分离单元间距比上述IGBT用第1沟槽间距、上述IGBT用第2沟槽间距、上述FWD用第1沟槽间距、上述FWD用第2沟槽间距的至少1个大；

上述分离用第1沟槽间距以及上述分离用第2沟槽间距比上述IGBT用第1沟槽间距、上述IGBT用第2沟槽间距、上述FWD用第1沟槽间距、上述FWD用第2沟槽间距窄。

4. 一种半导体装置,在共通的半导体衬底(10)上形成有IGBT区域(1)和FWD区域(2),其特征在于,

具备：

第1导电型的漂移层(11)；

第2导电型的基体层(12),形成在上述漂移层上；

多个沟槽栅构造,具有在将上述基体层贯通的沟槽(13a,13b)的壁面形成的栅极绝缘膜(14)和在上述栅极绝缘膜上形成的栅极电极；

第1导电型的发射极区域(19),在上述基体层的表层部以与形成于上述IGBT区域的上述沟槽相接的方式形成；

第2导电型的集电极层(16),隔着上述漂移层而形成在上述基体层侧的相反侧；

第1导电型的阴极层(17),隔着上述漂移层而形成在上述基体层的相反侧并且与上述集电极层邻接；

第1电极,与上述基体层及上述发射极区域电连接；以及

第2电极,与上述集电极层及上述阴极层电连接；

上述集电极层上的区域被设为上述IGBT区域,上述阴极层上的区域被设为上述FWD区域；

上述沟槽是形成于上述IGBT区域的配置作为上述栅极电极的第1栅极电极(15a)的IGBT用沟槽(13a),和形成于上述FWD区域且配置独立于上述第1栅极电极而被控制的作为上述栅极电极的第2栅极电极(15b)的FWD用沟槽(13b)；

上述IGBT用沟槽是在第1方向上延伸的IGBT用第1沟槽(131a)和在第2方向上延伸的IGBT用第2沟槽(132a)相连通而得到的格子状,上述第1方向沿着上述半导体衬底的面方向上的一个方向,上述第2方向与上述半导体衬底的面方向上的上述第1方向交叉；

上述FWD用沟槽是在上述第1方向上延伸的FWD用第1沟槽(131b)和在上述第2方向上延伸的FWD用第2沟槽(132b)相连通而得到格子状；

将上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽(133a)的中心与上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽(133b)的中心之间设为分离单元区域(3a),并且将上述分离单元区域的上述第2方向上的距离设为分离单元间距(W1)；

在上述分离单元区域,形成有沿上述第1方向延伸的多个伪沟槽(23)；

在上述伪沟槽(23),配置有伪绝缘膜(24)和伪电极(25)；

将相邻的上述IGBT用第1沟槽彼此的中心间的最小距离设为IGBT用第1沟槽间距(D1a),将相邻的上述IGBT用第2沟槽彼此的中心间的最小距离设为IGBT用第2沟槽间距(D2a),将相邻的上述FWD用第1沟槽彼此的中心间的最小距离设为FWD用第1沟槽间距(D1b),将相邻的上述FWD用第2沟槽彼此的中心间的最小距离设为FWD用第2沟槽间距(D2b),将上述伪沟槽的中心与和该伪沟槽相邻的上述IGBT用第1沟槽的中心之间的距离设为分离用第1沟槽间距(L1),将上述伪沟槽的中心与和该伪沟槽相邻的上述FWD用第1沟槽的中心之间的距离设为分离用第2沟槽间距(L2),将相邻的上述伪沟槽彼此的中心间的最大距离设为分离用第3沟槽间距(L3)；

上述分离单元间距比上述IGBT用第1沟槽间距、上述IGBT用第2沟槽间距、上述FWD用第1沟槽间距、上述FWD用第2沟槽间距的至少1个大；

上述分离用第1沟槽间距、上述分离用第2沟槽间距以及上述分离用第3沟槽间距比上述IGBT用第1沟槽间距、上述IGBT用第2沟槽间距、上述FWD用第1沟槽间距、上述FWD用第2沟

槽间距窄。

5. 如权利要求1所述的半导体装置,其特征在于,

将上述IGBT区域中的与上述分离单元区域不同的区域设为IGBT单元区域(1a),将上述FWD区域中的与上述分离单元区域不同的区域设为FWD单元区域(2a);

上述分离单元区域的基体层,与上述IGBT单元区域以及上述FWD单元区域的基体层相比,每单位体积的杂质质量较高。

6. 一种半导体装置,在共通的半导体衬底(10)上形成有IGBT区域(1)和FWD区域(2),其特征在于,

具备:

第1导电型的漂移层(11);

第2导电型的基体层(12),形成在上述漂移层上;

多个沟槽栅构造,具有在将上述基体层贯通的沟槽(13a,13b)的壁面形成的栅极绝缘膜(14)和在上述栅极绝缘膜上形成的栅极电极;

第1导电型的发射极区域(19),在上述基体层的表层部以与形成于上述IGBT区域的上述沟槽相接的方式形成;

第2导电型的集电极层(16),隔着上述漂移层而形成在上述基体层侧的相反侧;

第1导电型的阴极层(17),隔着上述漂移层而形成在上述基体层的相反侧并且与上述集电极层邻接;

第1电极,与上述基体层及上述发射极区域电连接;以及

第2电极,与上述集电极层及上述阴极层电连接;

上述集电极层上的区域被设为上述IGBT区域,上述阴极层上的区域被设为上述FWD区域;

上述沟槽是形成于上述IGBT区域的配置作为上述栅极电极的第1栅极电极(15a)的IGBT用沟槽(13a),和形成于上述FWD区域且配置独立于上述第1栅极电极而被控制的作为上述栅极电极的第2栅极电极(15b)的FWD用沟槽(13b);

上述IGBT用沟槽是在第1方向上延伸的IGBT用第1沟槽(131a)和在第2方向上延伸的IGBT用第2沟槽(132a)相连通而得到的格子状,上述第1方向沿着上述半导体衬底的面方向上的一个方向,上述第2方向与上述半导体衬底的面方向上的上述第1方向交叉;

上述FWD用沟槽是在上述第1方向上延伸的FWD用第1沟槽(131b)和在上述第2方向上延伸的FWD用第2沟槽(132b)相连通而得到格子状;

将上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽(133a)的中心与上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽(133b)的中心之间设为分离单元区域(3a),将上述IGBT区域中的与上述分离单元区域不同的区域设为IGBT单元区域(1a),将上述FWD区域中的与上述分离单元区域不同的区域设为FWD单元区域(2a);

上述分离单元区域的基体层,与上述IGBT单元区域以及上述FWD单元区域的基体层相比,每单位体积的杂质质量较高;

在上述分离单元区域,形成有使上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽和上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽相连通的连通沟槽(134);

在上述连通沟槽,配置有将上述第1栅极电极和上述第2栅极电极绝缘的绝缘膜(135)。

7. 如权利要求5所述的半导体装置,其特征在于,

上述分离单元区域的基体层比上述IGBT单元区域以及上述FWD单元区域的基体层形成得深。

8. 如权利要求5所述的半导体装置,其特征在于,

上述分离单元区域的基体层,与上述IGBT单元区域以及上述FWD单元区域的基体层相比,杂质浓度较高。

9. 如权利要求1所述的半导体装置,其特征在于,

在上述分离单元区域,形成有使上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽和上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽相连通的连通沟槽(134);

在上述连通沟槽,配置有将上述第1栅极电极和上述第2栅极电极绝缘的绝缘膜(135)。

10. 一种半导体装置,在共通的半导体衬底(10)上形成有IGBT区域(1)和FWD区域(2),其特征在于,

具备:

第1导电型的漂移层(11);

第2导电型的基体层(12),形成在上述漂移层上;

多个沟槽栅构造,具有在将上述基体层贯通的沟槽(13a,13b)的壁面形成的栅极绝缘膜(14)和在上述栅极绝缘膜上形成的栅极电极;

第1导电型的发射极区域(19),在上述基体层的表层部以与形成于上述IGBT区域的上述沟槽相接的方式形成;

第2导电型的集电极层(16),隔着上述漂移层而形成在上述基体层侧的相反侧;

第1导电型的阴极层(17),隔着上述漂移层而形成在上述基体层的相反侧并且与上述集电极层邻接;

第1电极,与上述基体层及上述发射极区域电连接;以及

第2电极,与上述集电极层及上述阴极层电连接;

上述集电极层上的区域被设为上述IGBT区域,上述阴极层上的区域被设为上述FWD区域;

上述沟槽是形成于上述IGBT区域的配置作为上述栅极电极的第1栅极电极(15a)的IGBT用沟槽(13a),和形成于上述FWD区域且配置独立于上述第1栅极电极而被控制的作为上述栅极电极的第2栅极电极(15b)的FWD用沟槽(13b);

上述IGBT用沟槽是在第1方向上延伸的IGBT用第1沟槽(131a)和在第2方向上延伸的IGBT用第2沟槽(132a)相连通而得到的格子状,上述第1方向沿着上述半导体衬底的面方向上的一个方向,上述第2方向与上述半导体衬底的面方向上的上述第1方向交叉;

上述FWD用沟槽是在上述第1方向上延伸的FWD用第1沟槽(131b)和在上述第2方向上延伸的FWD用第2沟槽(132b)相连通而得到格子状;

将上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽(133a)的中心与上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽(133b)的中心之间设为分离单元区域(3a);

在上述分离单元区域,形成有使上述IGBT用第1沟槽中的最靠上述FWD用沟槽侧的沟槽与上述FWD用第1沟槽中的最靠上述IGBT用沟槽侧的沟槽相连通的连通沟槽(134);

在上述连通沟槽,配置有将上述第1栅极电极与上述第2栅极电极绝缘的绝缘膜(135)。

11. 如权利要求1~10中任一项所述的半导体装置,其特征在于,

在上述漂移层与上述基体层之间,形成有第2导电型的电场缓和区域(26);

在上述电场缓和区域与上述基体层之间,形成有第1导电型的阻挡区域(27);

在上述基体层的表层部,形成有与上述第1电极连接并且与上述阻挡区域连接的第1导电型的柱区域(28)。

## 半导体装置

[0001] 关联申请的相互参照

[0002] 本申请基于2018年9月11日申请的日本专利申请第2018-169878号,这里通过参照而援引其记载内容。

### 技术领域

[0003] 本发明涉及在共通的半导体衬底上形成有具有绝缘栅构造的绝缘栅双极型晶体管(以下称作IGBT)元件和续流二极管(以下称作FWD)元件的半导体装置。

### 背景技术

[0004] 以往,作为在逆变器等中使用的开关元件,例如,提出了在共通的半导体衬底上形成有具有IGBT元件的IGBT区域和具有FWD元件的FWD区域的半导体装置(例如,参照专利文献1)。

[0005] 具体而言,该半导体装置中,在构成N-型的漂移层的半导体衬底的表层部形成基体(base)层,以将基体层贯通的方式形成有多个沟槽。并且,在各沟槽中,依次形成有栅极绝缘膜及栅极电极。由此,构成了沟槽栅构造。此外,在基体层的表层部,以与沟槽相接的方式形成有N+型的发射极区域。在半导体衬底的背面侧,形成有P+型的集电极层及N+型的阴极层。

[0006] 并且,在半导体衬底的成为表面侧的一面侧,形成有与基体层及发射极区域电连接的上部电极。在半导体衬底的成为背面侧的另一面侧,形成有与集电极层及阴极层电连接的下部电极。

[0007] 在这样的半导体装置中,将在半导体衬底的背面侧形成有集电极层的区域设为IGBT区域,将形成有阴极层的区域设为FWD区域。另外,在FWD区域,通过做成上述结构,由N型的阴极层及漂移层和P型的基体层构成具有PN结的FWD元件。

[0008] 此外,上述半导体装置中,形成于IGBT区域的沟槽由在一个方向上延伸的第1沟槽和以将相邻的第1沟槽相连的方式在与一个方向交叉的方向上延伸的第2沟槽相连通而成为格子状。

[0009] 这样的半导体装置中,由于沟槽为格子状,因此例如与沟槽为条状的情况相比,等位线避开沟槽而形成从而等位线不易向半导体衬底的一面侧进入。因此,在IGBT区域,不易发生电场集中,能够实现耐压的提高。

[0010] 现有技术文献

[0011] 专利文献

[0012] 专利文献1:日本特开2016-82097号公报

### 发明内容

[0013] 此外,在上述那样的半导体装置中,还希望还提高FWD区域的耐压。因此,在FWD区域,也可以考虑将沟槽设为格子状。但是,若将FWD区域的沟槽设为格子状并将IGBT区域的

沟槽和FWD区域的沟槽相连,则配置在IGBT区域的栅极电极和配置在FWD区域的栅极电极被电连接。该情况下,配置在FWD区域的栅极电极与配置在IGBT区域的栅极电极成为相同电位,因此有FWD元件的特性变动的可能性。

[0014] 因而,为了提高FWD区域的耐压并且抑制FWD元件的特性变动,例如可以考虑将FWD区域的沟槽设为格子状并且不使FWD区域的沟槽与IGBT区域的沟槽相连通。但是,在该结构下,在形成于各区域的格子状沟槽之间的区域,有沟槽密度变低的可能性,有该区域的耐压变低的可能性。

[0015] 本发明的目的在于,提供能够提高耐压的半导体装置。

[0016] 根据本发明的1个观点,在共通的半导体衬底上形成有IGBT区域和FWD区域,具备:第1导电型的漂移层;第2导电型的基体层,形成在漂移层上;多个沟槽栅构造,具有在将基体层贯通的沟槽的壁面形成的栅极绝缘膜和在栅极绝缘膜上形成的栅极电极;第1导电型的发射极区域,在基体层的表层部以与形成于IGBT区域的沟槽相接的方式形成;第2导电型的集电极层,隔着漂移层而形成在基体层侧的相反侧;第1导电型的阴极层,隔着漂移层而形成在基体层的相反侧并且与集电极层邻接;第1电极,与基体层以及发射极区域电连接;以及第2电极,与集电极层以及阴极层电连接。并且,集电极层上的区域被设为IGBT区域,阴极层上的区域被设为FWD区域,沟槽是形成于IGBT区域的配置作为栅极电极的第1栅极电极的IGBT用沟槽和形成于FWD区域且配置独立于第1栅极电极而被控制的作为栅极电极的第2栅极电极的FWD用沟槽,IGBT用沟槽是在第1方向上延伸的IGBT用第1沟槽和在第2方向上延伸的IGBT用第2沟槽相连通而得到的格子状,第1方向沿着半导体衬底的面方向上的一个方向,第2方向与半导体衬底的面方向上的第1方向交叉,FWD用沟槽是在第1方向上延伸的FWD用第1沟槽和在第2方向上延伸的FWD用第2沟槽相连通而得到的格子状。

[0017] 并且,根据本发明的1个观点,将IGBT用第1沟槽中的最靠FWD用沟槽侧的沟槽的中心与FWD用第1沟槽中的最靠IGBT用沟槽侧的沟槽的中心之间设为分离单元区域并且将分离单元区域的第2方向上的距离设为分离单元间距,将相邻的IGBT用第1沟槽彼此的中心间的最小距离设为IGBT用第1沟槽间距,将相邻的IGBT用第2沟槽彼此的中心间的最小距离设为IGBT用第2沟槽间距,将相邻的FWD用第1沟槽彼此的中心间的最小距离设为FWD用第1沟槽间距,将相邻的FWD用第2沟槽彼此的中心间的最小距离设为FWD用第2沟槽间距,分离单元间距比IGBT用第1沟槽间距、IGBT用第2沟槽间距、FWD用第1沟槽间距、FWD用第2沟槽间距窄。

[0018] 由此,在分离单元区域,与分离单元间距为各沟槽间距以上的情况相比,能够提高沟槽密度。因此,在分离单元区域中等位线也难以向基体层侧进入,在分离单元区域也能够抑制电场集中的发生。因而,能够提高分离单元区域的耐压,所以能够提高半导体装置的耐压。

[0019] 此外,根据本发明的其他观点,将IGBT用第1沟槽中的最靠FWD用沟槽侧的沟槽的中心与FWD用第1沟槽中的最靠IGBT用沟槽侧的沟槽的中心之间设为分离单元区域,并且将分离单元区域的第2方向上的距离设为分离单元间距,在分离单元区域,形成有沿第1方向延伸的1个伪沟槽,在伪沟槽中,配置有伪绝缘膜和伪电极,将相邻的IGBT用第1沟槽彼此的中心间的最小距离设为IGBT用第1沟槽间距,将相邻的IGBT用第2沟槽彼此的中心间的最小距离设为IGBT用第2沟槽间距,将相邻的FWD用第1沟槽彼此的中心间的最小距离设为FWD用

第1沟槽间距,将相邻的FWD用第2沟槽彼此的中心间的最小距离设为FWD用第2沟槽间距,将伪沟槽的中心与和该伪沟槽相邻的IGBT用第1沟槽的中心之间的距离设为分离用第1沟槽间距,将伪沟槽的中心与和该伪沟槽相邻的FWD用第1沟槽的中心之间的距离设为分离用第2沟槽间距,分离单元间距比IGBT用第1沟槽间距、IGBT用第2沟槽间距、FWD用第1沟槽间距、FWD用第2沟槽间距的至少1个大,分离用第1沟槽以及分离用第2沟槽间距比IGBT用第1沟槽间距、IGBT用第2沟槽间距、FWD用第1沟槽间距、FWD用第2沟槽间距窄。

[0020] 此外,根据本发明的其他观点,将IGBT用第1沟槽中的最靠FWD用沟槽侧的沟槽的中心与FWD用第1沟槽中的最靠IGBT用沟槽侧的沟槽的中心之间设为分离单元区域,并且将分离单元区域的第2方向上的距离设为分离单元间距,在分离单元区域,形成有沿第1方向延伸的多个伪沟槽,在伪沟槽中,配置有伪绝缘膜和伪电极,将相邻的IGBT用第1沟槽彼此的中心间的最小距离设为IGBT用第1沟槽间距,相邻的IGBT用第2沟槽彼此的中心间的最小距离设为IGBT用第2沟槽间距,将相邻的FWD用第1沟槽彼此的中心间的最小距离设为FWD用第1沟槽间距,将相邻的FWD用第2沟槽彼此的中心间的最小距离设为FWD用第2沟槽间距,将伪沟槽的中心与和该伪沟槽相邻的IGBT用第1沟槽的中心之间的距离设为分离用第1沟槽间距,将伪沟槽的中心与和该伪沟槽相邻的FWD用第1沟槽的中心之间的距离设为分离用第2沟槽间距,将相邻的伪沟槽彼此的中心间的最大距离设为分离用第3沟槽间距,分离单元间距比IGBT用第1沟槽间距、IGBT用第2沟槽间距、FWD用第1沟槽间距、FWD用第2沟槽间距的至少1个大,分离用第1沟槽间距、分离用第2沟槽间距以及分离用第3沟槽间距比IGBT用第1沟槽间距、IGBT用第2沟槽间距、FWD用第1沟槽间距、FWD用第2沟槽间距窄。

[0021] 根据这些观点,各分离用间距比各沟槽间距窄。因此,在分离单元区域,即使分离单元间距被设为各沟槽间距以上,也能够提高沟槽密度。因此,在分离单元区域中等位线也难以向基体层侧进入,在分离单元区域也能够抑制电场集中的发生。因而,能够提高分离单元区域的耐压,所以能够提高半导体装置的耐压。

[0022] 此外,根据本发明的其他观点,将IGBT用第1沟槽中的最靠FWD用沟槽侧的沟槽的中心与FWD用第1沟槽中的最靠IGBT用沟槽侧的沟槽的中心之间设为分离单元区域,将IGBT区域中的与分离单元区域不同的区域设为IGBT单元区域,将FWD区域中的与分离单元区域不同的区域设为FWD单元区域,分离单元区域的基体层相比于IGBT单元区域以及FWD单元区域的基体层而言每单位体积的杂质质量较高。

[0023] 由此,在分离单元区域中,与IGBT单元区域以及FWD单元区域相比,成为基体层与漂移层之间的耗尽层向集电极层以及阴极层侧延伸的状态。因而,在分离单元区域,等位线难以向基体层侧进入,在分离单元区域能够抑制电场集中的发生。因而,能够提高分离单元区域的耐压,所以能够提高半导体装置的耐压。

[0024] 此外,根据本发明的其他观点,将IGBT用第1沟槽中的最靠FWD用沟槽侧的沟槽的中心与FWD用第1沟槽中的最靠IGBT用沟槽侧的沟槽的中心之间设为分离单元区域,在分离单元区域,形成有使IGBT用第1沟槽中的最靠FWD用沟槽侧的沟槽与FWD用第1沟槽中的最靠IGBT用沟槽侧的沟槽相连通的连通沟槽(134),在连通沟槽中,配置有将第1栅极电极与第2栅极电极绝缘的绝缘膜。

[0025] 由此,在分离单元区域,通过形成连通沟槽从而能够提高沟槽密度。因此,在分离单元区域中等位线也难以向基体层侧进入,在分离单元区域能够抑制电场集中的发生。因

而,能够提高分离单元区域的耐压,所以能够提高半导体装置的耐压。

[0026] 另外,对各构成要素等赋予的带括号的参照标记表示该构成要素等与后述实施方式中记载的具体构成要素等的对应关系的一例。

## 附图说明

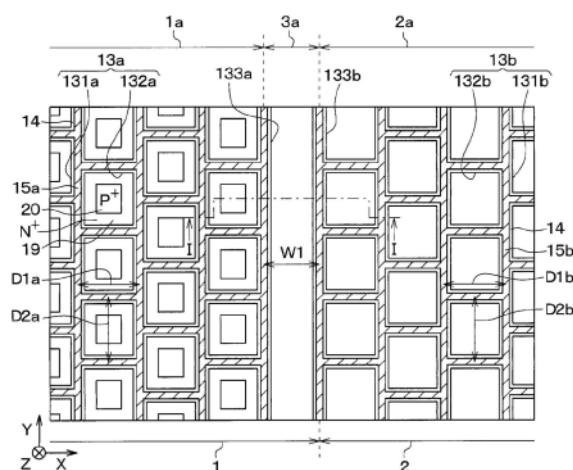

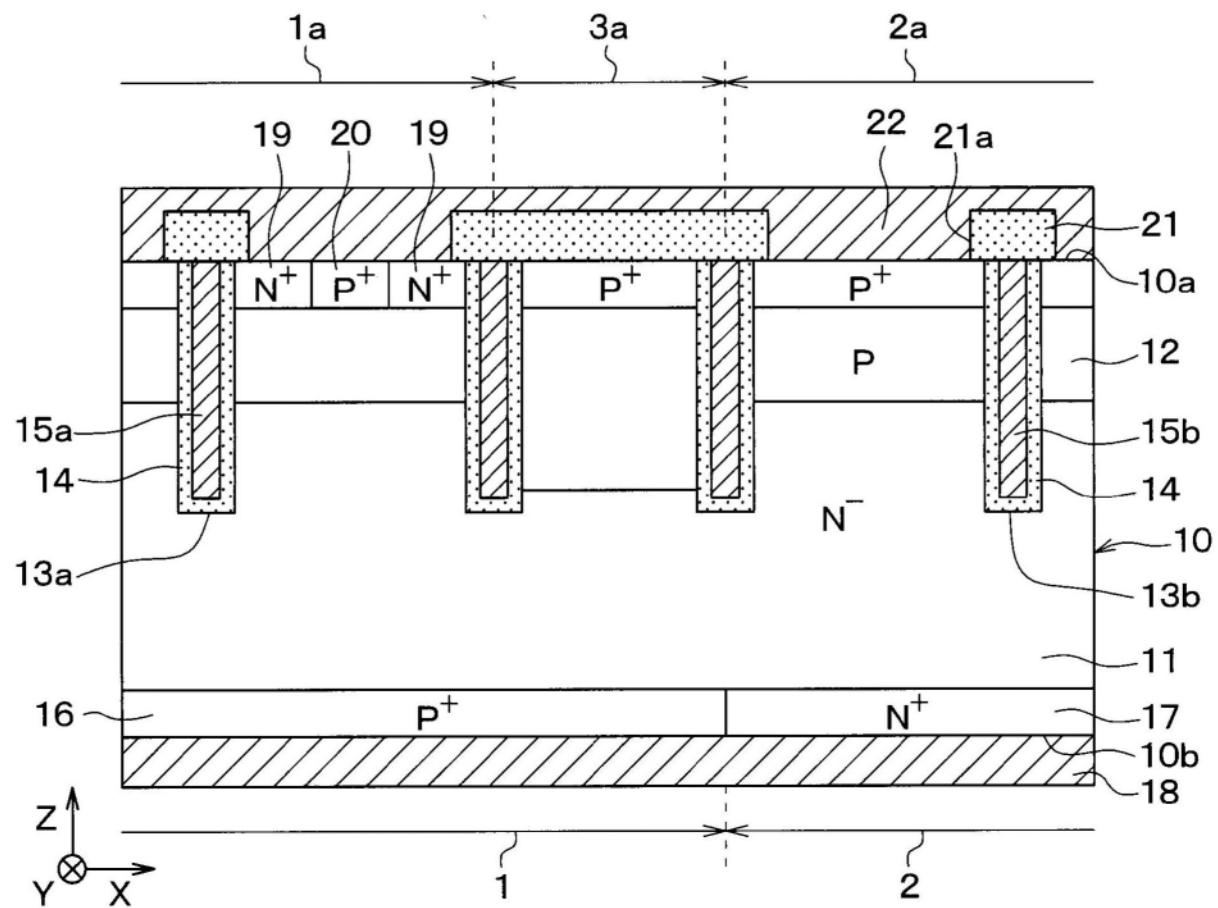

- [0027] 图1是第1实施方式的半导体装置的截面图。

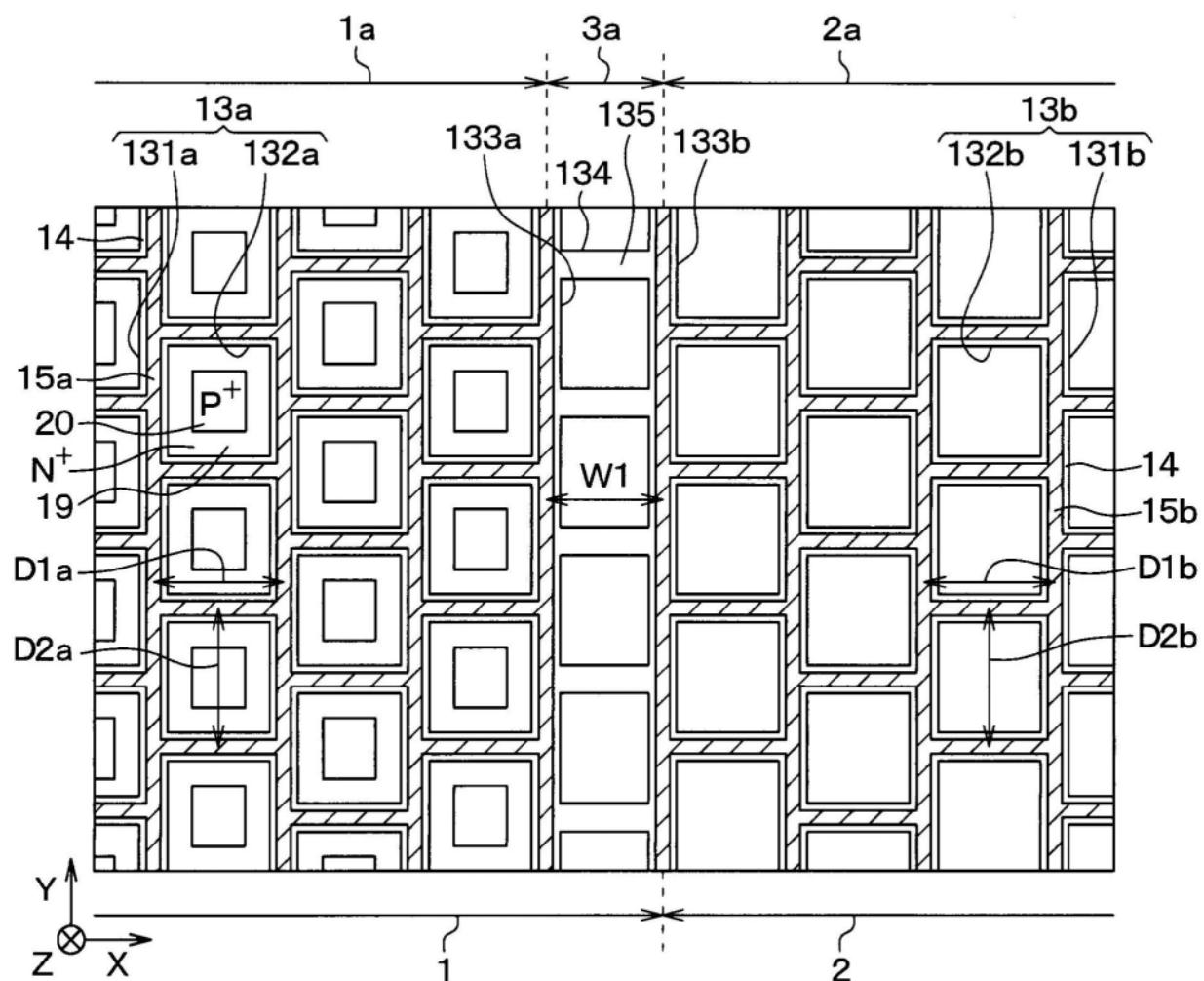

- [0028] 图2是图1所示的半导体装置的平面图。

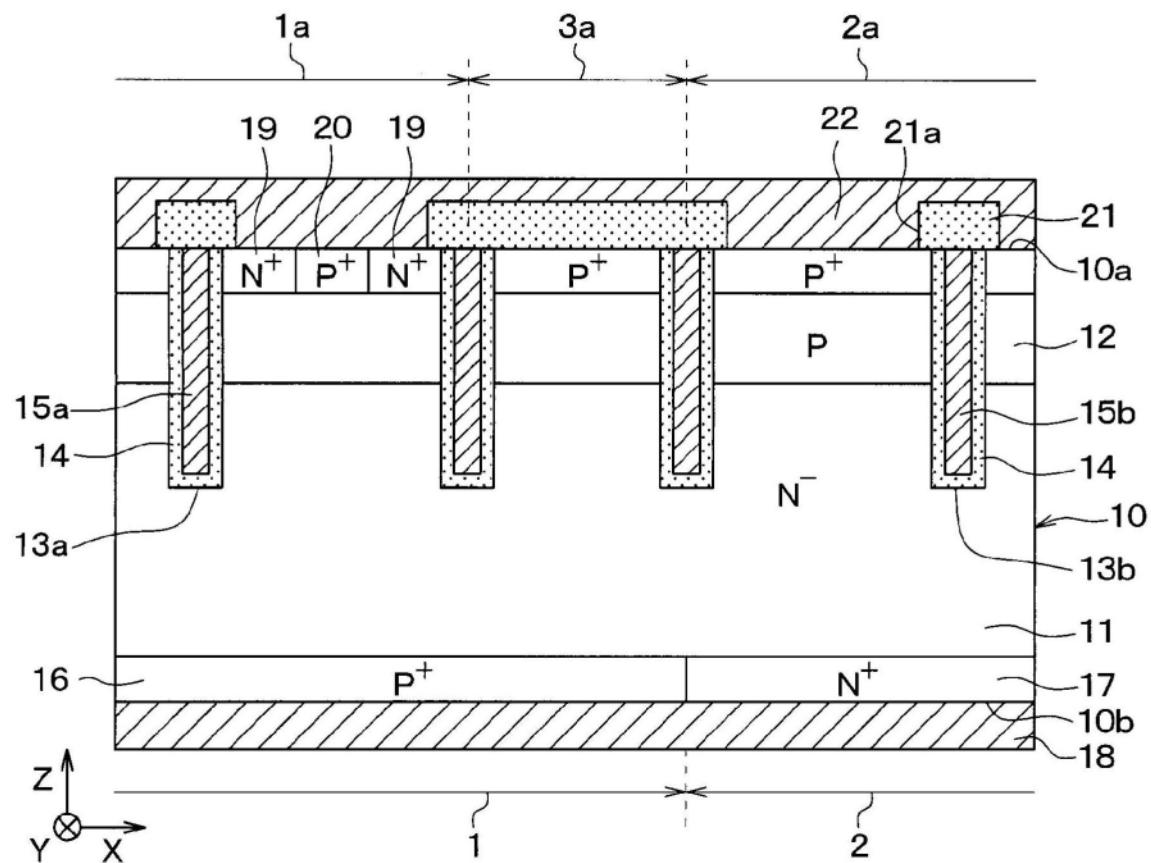

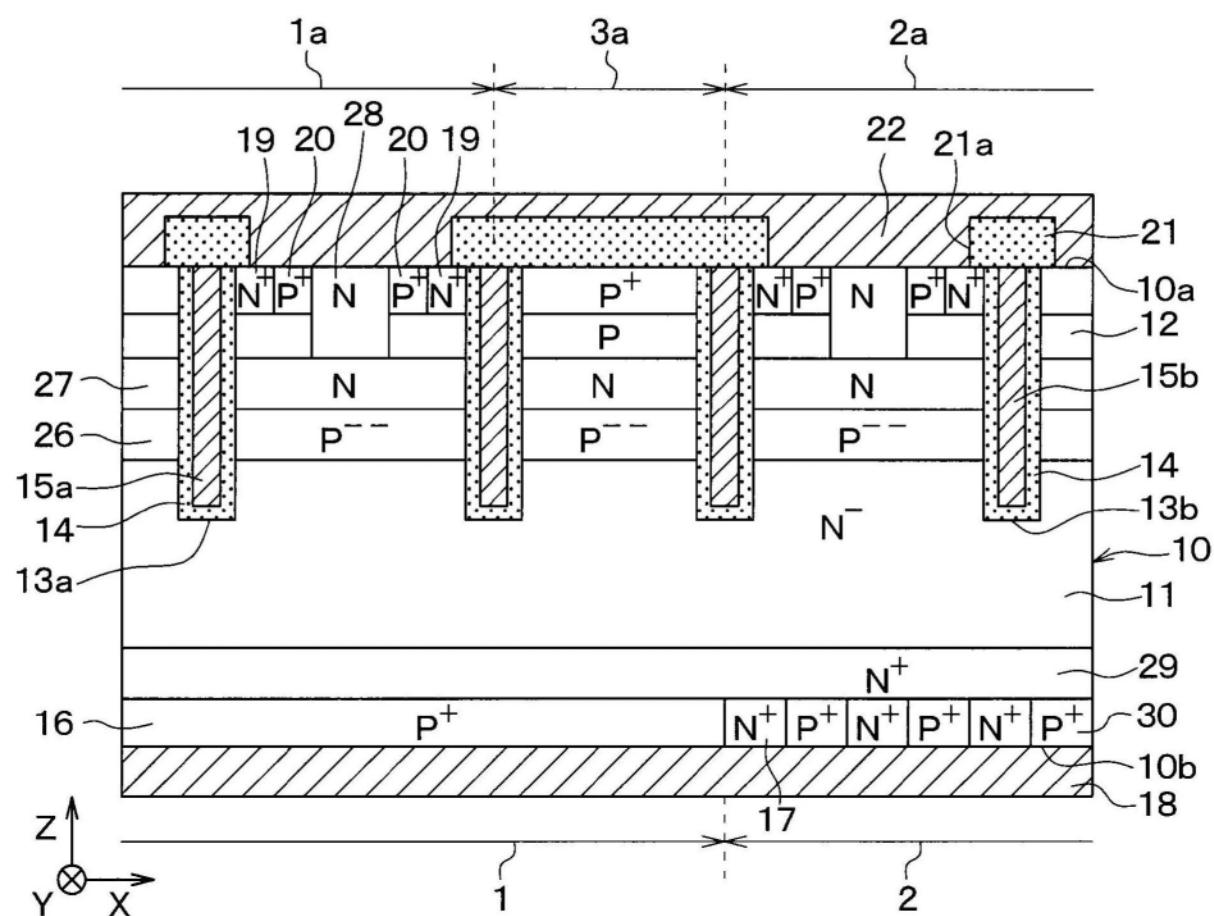

- [0029] 图3是第2实施方式的半导体装置的截面图。

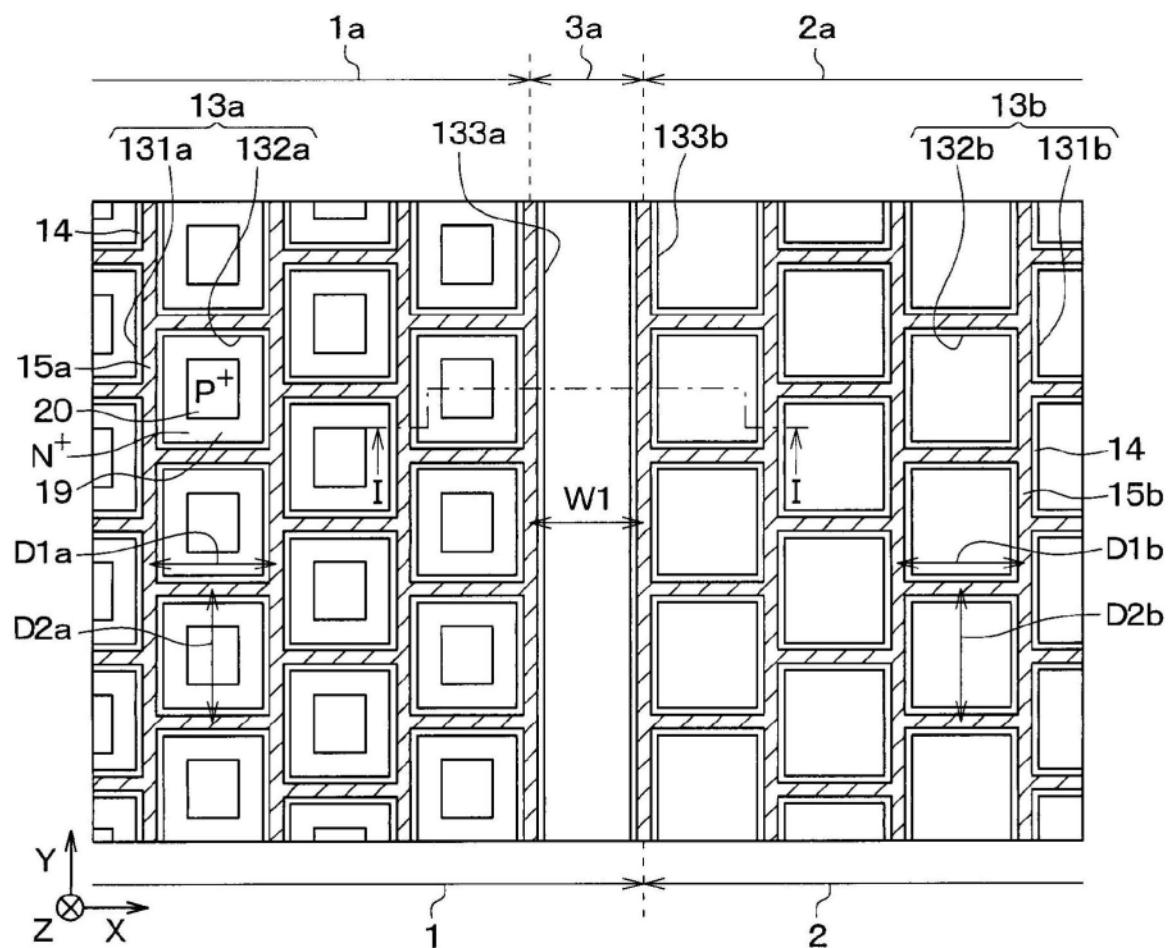

- [0030] 图4是图3所示的半导体装置的平面图。

- [0031] 图5是第2实施方式的变形例的半导体装置的平面图。

- [0032] 图6是第2实施方式的变形例的半导体装置的平面图。

- [0033] 图7是第3实施方式的半导体装置的平面图。

- [0034] 图8是第4实施方式的半导体装置的截面图。

- [0035] 图9是第5实施方式的半导体装置的平面图。

- [0036] 图10是第6实施方式的半导体装置的截面图。

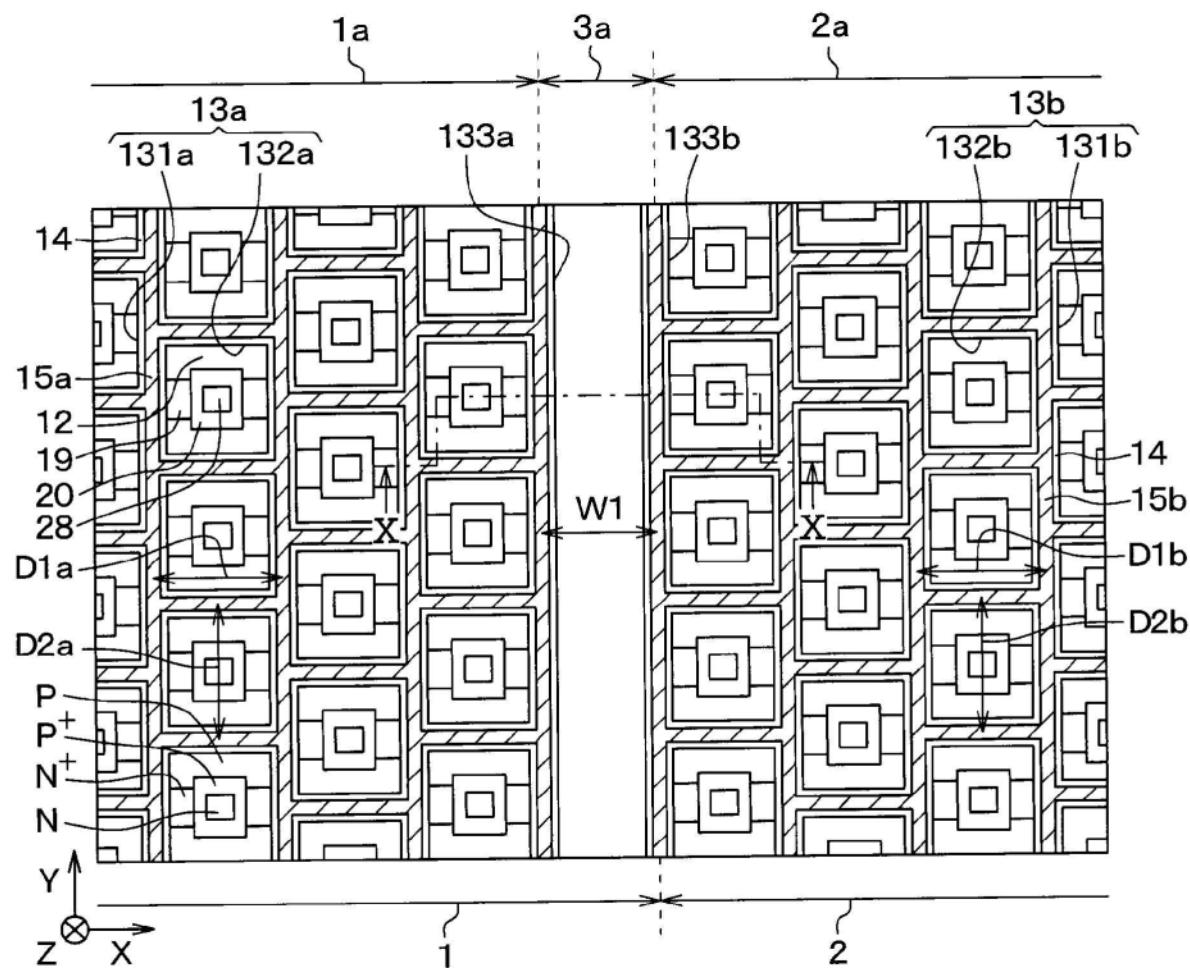

- [0037] 图11是第6实施方式的半导体装置的平面图。

## 具体实施方式

[0038] 以下,基于附图说明本发明的实施方式。另外,在以下各实施方式中,对于相同或等同的部分赋予同一标记而进行说明。

[0039] (第1实施方式)

[0040] 对第1实施方式进行说明。另外,本实施方式的半导体装置例如适于用作逆变器、DC/DC变换器等的电源电路中使用的功率开关元件。

[0041] 如图1所示,半导体装置在共通的半导体衬底10上形成有具有IGBT元件的IGBT区域1和具有FWD元件的FWD区域2。即,本实施方式的半导体装置被设为RC(Reverse Conducting的简写)–IGBT。

[0042] 具体而言,半导体装置具有构成N-型的漂移层11的半导体衬底10。另外,在本实施方式中,半导体衬底10由硅衬底构成。并且,在漂移层11上形成有P型的基体层12。另外,所谓漂移层11上,换言之是半导体衬底10的一面10a侧。

[0043] 在半导体衬底10,以将基体层12贯通而到达漂移层11的方式形成有沟槽13a、13b。并且,各沟槽13a、13b被将各沟槽13a、13b的壁面覆盖而形成的栅极绝缘膜14和在该栅极绝缘膜14之上形成的由多晶硅等构成的第1、第2栅极电极15a、15b填埋。由此,构成沟槽栅构造。

[0044] 此外,隔着漂移层11而在基体层12的相反侧形成有P+型的集电极层16及N+型的阴极层17。并且,在本实施方式中,IGBT区域1和FWD区域2根据在半导体衬底10的另一面10b侧形成的层是集电极层16还是阴极层17而被划分。即,本实施方式中,集电极层16上的部分设为IGBT区域1,阴极层17上的部分设为FWD区域2。

[0045] 隔着集电极层16及阴极层17而在漂移层11的相反侧(即,半导体衬底10的另一面10b),形成有与集电极层16及阴极层17电连接的下部电极18。即,形成有在IGBT区域1中作

为集电极电极发挥功能、在FWD区域2中作为阴极电极发挥功能的下部电极18。本实施方式中,下部电极18相当于第2电极。

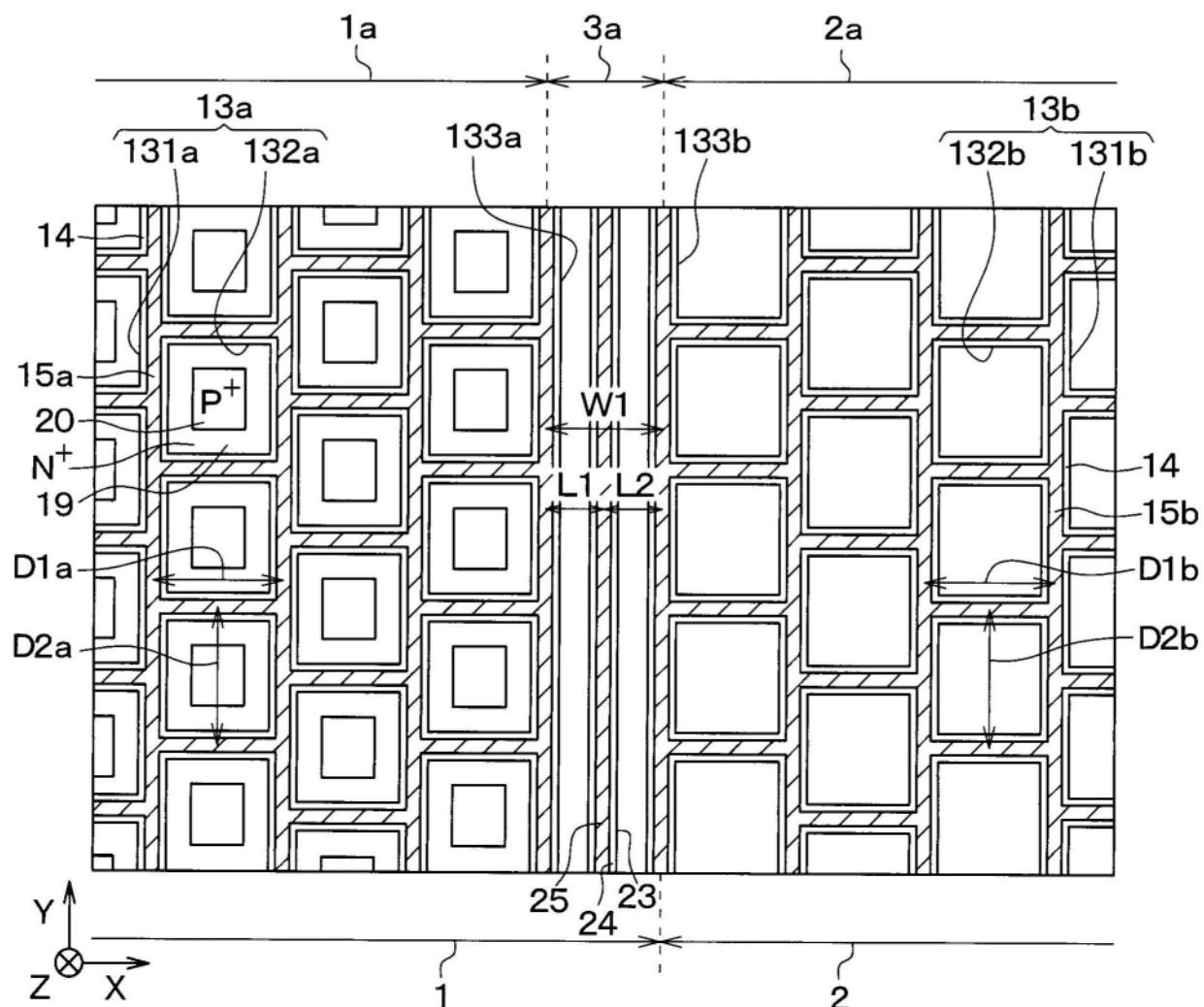

[0046] 这里,参照图1及图2说明本实施方式的沟槽13a、13b的形状(即,沟槽栅构造的形状)。另外,以下,将半导体衬底10的面方向上的一个方向作为X轴方向,将半导体衬底10的面方向上的与X轴方向正交的一个方向作为Y轴方向,将与X轴方向及Y轴方向正交的方向作为Z轴方向。图1中,纸面左右方向为X轴方向,纸面垂直方向为Y轴方向,纸面上下方向为Z轴方向。图2中,纸面左右方向为X轴方向,纸面上下方向为Y轴方向,纸面垂直方向为Z轴方向。本实施方式中,Y轴方向相当于第1方向,X轴方向相当于第2方向。此外,在后述的各图中,也适当示出了X轴方向、Y轴方向、Z轴方向。并且,图2省略后述的层间绝缘膜21及上部电极22而表示,虽不是截面图,但为了容易理解而对第1、第2栅极电极15a、15b施加了阴影。此外,在后述的与图2对应的各图中,也将层间绝缘膜21及上部电极22省略,对第1、第2栅极电极15a、15b施加了阴影。

[0047] 在半导体衬底10,在IGBT区域1形成有IGBT用沟槽13a,在FWD区域2形成有FWD用沟槽13b,各沟槽13a、13b以Z轴方向为深度方向而被下挖。

[0048] IGBT用沟槽13a由沿Y轴方向延伸的IGBT用第1沟槽131a和沿X轴方向延伸的IGBT用第2沟槽132a连通而构成,为格子状。另外,本实施方式中,IGBT用第1沟槽131a沿X轴方向形成有3条以上的多条,相邻的IGBT用第1沟槽131a彼此的间隔相等。此外,IGBT用第2沟槽132a沿Y轴方向形成有3条以上的多条,相邻的IGBT用第2沟槽132a彼此的间隔相等。

[0049] FWD用沟槽13b由沿Y轴方向延伸的FWD用第1沟槽131b和沿X轴方向延伸的FWD用第2沟槽132b连通而构成,为格子状。

[0050] 另外,本实施方式中,FWD用第1沟槽131b沿X轴方向形成有3条以上的多条。并且,相邻的FWD用第1沟槽131b彼此的间隔相等,并且与相邻的IGBT用第1沟槽131a彼此的间隔也相等。此外,FWD用第2沟槽132b沿Y轴方向形成有3条以上的多条。并且,相邻的FWD用第2沟槽132b彼此的间隔相等,并且与相邻的IGBT用第2沟槽132a彼此的间隔也相等。

[0051] 此外,本实施方式中,相对于1个IGBT用第1沟槽131a向相反侧突出的2个IGBT用第2沟槽132a沿Y轴方向错开而配置。即,相对于1个IGBT用第1沟槽131a向相反侧突出的2个IGBT用第2沟槽132a非对称。同样地,相对于1个FWD用第1沟槽131b向相反侧突出的2个FWD用第2沟槽132b沿Y轴方向错开而配置。即,相对于1个FWD用第1沟槽131b向相反侧突出的2个FWD用第2沟槽132b非对称。

[0052] 本实施方式中,像这样形成了IGBT用沟槽13a及FWD用沟槽13b。并且,在IGBT用沟槽13a与FWD用沟槽13b之间,没有形成沿X轴方向延伸的沟槽。即,本实施方式中,IGBT用沟槽13a与FWD用沟槽13b不连通,为分离的状态。因此,埋入在IGBT用沟槽13a中的第1栅极电极15a和埋入在FWD用沟槽13b中的第2栅极电极15b为分离的状态,为电绝缘的状态。

[0053] 并且,埋入在IGBT用沟槽13a中的第1栅极电极15a经由未图示的栅极布线而与施加规定的栅极电压的栅极驱动电路连接。另一方面,埋入在FWD用沟槽13b中的第2栅极电极15b例如与后述的上部电极22连接,被维持为上部电极22的电位。

[0054] 另外,关于IGBT用沟槽13a以及FWD用沟槽13b,更详细而言,将配置有第1栅极电极15a的沟槽设为IGBT用沟槽13a,将配置有第2栅极电极15b的沟槽设为FWD用沟槽13b。即,本实施方式中,如图1所示,在集电极层16与阴极层17的边界上也形成有沟槽,在该沟槽中如

图2所示那样配置有第2栅极电极15b。因此,该沟槽成为FWD用沟槽13b。

[0055] 以下,将IGBT用沟槽13a中的最靠FWD用沟槽13b侧的也称作IGBT用端部沟槽133a。此外,将FWD用沟槽13b中的最靠IGBT用沟槽13a侧的也称作FWD用端部沟槽133b。另外,本实施方式中,FWD用端部沟槽133b构成为,X轴方向上的中心与集电极层16和阴极层17的边界大致一致。

[0056] 此外,以下,将IGBT用端部沟槽133a的中心与FWD用端部沟槽133b的中心之间的区域也称作分离单元区域3a。此外,将IGBT区域1中的与分离单元区域3a不同的区域也称作IGBT单元区域1a,将FWD区域2中的与分离单元区域3a不同的区域也称作FWD单元区域2a。

[0057] 另外,所谓IGBT用端部沟槽133a的中心,是IGBT用端部沟槽133a的X轴方向的中心,所谓FWD用端部沟槽133b的中心,是FWD用端部沟槽133b的X轴方向的中心。并且,本实施方式中,FWD用端部沟槽133b的中心与集电极层16和阴极层17的边界大致一致。因此,IGBT区域1包含分离单元区域3a,FWD区域2全部成为FWD单元区域2a。

[0058] 此外,将IGBT用端部沟槽133a的中心与FWD用端部沟槽133b的中心之间的距离设为分离单元间距W1。即,将分离单元区域3a的沿X轴方向的距离设为分离单元间距W1。

[0059] 此外,将沿着X轴方向相邻的IGBT用第1沟槽131a彼此的中心间的距离设为IGBT用第1沟槽间距D1a。将沿着Y轴方向相邻的IGBT用第2沟槽132a彼此的中心间的距离设为IGBT用第2沟槽间距D2a。另外,所谓IGBT用第1沟槽131a的中心,是IGBT用第1沟槽131a的X轴方向的中心,所谓IGBT用第2沟槽132a的中心,是IGBT用第2沟槽132a的Y轴方向的中心。

[0060] 同样地,将沿X轴方向相邻的FWD用第1沟槽131b彼此的中心间的距离设为FWD用第1沟槽间距D1b。将沿Y轴方向相邻的FWD用第2沟槽132b的中心间的距离设为FWD用第2沟槽间距D2b。另外,所谓FWD用第1沟槽131b的中心,是FWD用第1沟槽131b的X轴方向的中心,所谓FWD用第2沟槽132b的中心,是FWD用第2沟槽132b的Y轴方向的中心。

[0061] 此外,本实施方式中,如上述那样,相邻的IGBT用第1沟槽131a彼此的间隔与相邻的FWD用第1沟槽131b彼此的间隔相等。因此,IGBT用第1沟槽间距D1a与FWD用第1沟槽间距D1b相等。此外,相邻的IGBT用第2沟槽132a彼此的间隔与相邻的FWD用第2沟槽132b彼此的间隔相等。因此,IGBT用第2沟槽间距D2a和FWD用第2沟槽间距D2b相等。

[0062] 并且,本实施方式中,分离单元间距W1比各沟槽间距D1a、D2a、D1b、D2b窄。因此,本实施方式的分离单元区域3a,例如与分离单元间距W1为IGBT用第1沟槽间距D1a以及FWD用第1沟槽间距D1b以上的情况相比,沟槽密度变高。

[0063] 以上是本实施方式的沟槽13a、13b的结构。

[0064] 并且,各IGBT单元区域1a中,在基体层12的表层部,分别形成有比漂移层11高杂质浓度的N+型的发射极区域19以及比基体层12高杂质浓度的P+型的接触区域20。具体而言,本实施方式中,发射极区域19沿着IGBT用沟槽13a形成。即,发射极区域19当从半导体衬底10的面方向的法线方向观察时形成为框状。并且,接触区域20形成为,与发射极区域19邻接并且被发射极区域19包围,形成在从IGBT用沟槽13a离开了的位置。另外,所谓基体层12的表层部,换言之是半导体衬底10的一面10a侧。

[0065] 此外,在FWD单元区域2a以及分离单元区域3a,在基体层12的表层部,形成有与形成于IGBT单元区域1a的接触区域20同样的接触区域20。另外,本实施方式中,在分离单元区域3a没有形成发射极区域19。即,在IGBT用端部沟槽133a的分离单元区域3a侧,没有形成发

射极区域19。即,本实施方式中,使得分离单元区域3a不再作为IGBT元件进行动作。由此,能够抑制在IGBT动作时配置在FWD用端部沟槽133b中的第2栅极电极15b发生栅极干扰、FWD元件的特性变动。

[0066] 在半导体衬底10的一面10a上,形成有由BPSG (Borophosphosilicate Glass的简写) 等构成的层间绝缘膜21。并且,在层间绝缘膜21上,形成有穿过形成于层间绝缘膜21的接触孔21a而与发射极区域19及接触区域20(即,基体层12) 电连接的作为第1电极的上部电极22。即,在层间绝缘膜21上,形成有在IGBT区域1中作为发射极电极发挥功能、在FWD区域2中作为阳极电极发挥功能的上部电极22。

[0067] 另外,在分离单元区域3a,在与图1不同的截面中,在层间绝缘膜21形成有使接触区域20露出的接触孔21a。更详细而言,虽未特别图示,但本实施方式的半导体装置以将上述IGBT区域1及FWD区域2包围的方式配置有外周区域。并且,在分离单元区域3a,在外周区域的附近在层间绝缘膜21中形成有接触孔,接触区域20穿过该接触孔21a而与上部电极22电连接。

[0068] 因此,如后述那样使二极管动作时,由于分离单元区域3a的接触孔21a形成在外周区域的附近,所以载流子不易经由分离单元区域3a向上部电极22流动,分离单元区域3a不易进行二极管动作。由此,能够抑制当二极管动作时配置在IGBT用端部沟槽133a中的第1栅极电极15a发生栅极干扰、IGBT元件的特性变动。

[0069] 并且,通过如上述那样构成,在FWD单元区域2a中,将基体层12及接触区域20作为阳极,将漂移层11、阴极层17作为阴极,构成具有PN结的FWD元件。

[0070] 以上是本实施方式的半导体装置的结构。另外,本实施方式中,N型、N+型、N-型相当于第1导电型,P型、P+型相当于第2导电型。此外,本实施方式中,如上述那样,半导体衬底10具有集电极层16、阴极层17、漂移层11、基体层12、发射极区域19、接触区域20。

[0071] 接着,简单说明上述半导体装置的动作。

[0072] 首先,半导体装置若下部电极18被施加比上部电极22高的电压,则在基体层12与漂移层11之间形成的PN结成为逆导通状态而形成耗尽层。并且,当第1栅极电极15a被施加了不到绝缘栅构造的阈值电压Vth的低电平(例如,0V)的电压时,在上部电极22与下部电极18之间不流通电流。

[0073] 并且,为了使IGBT元件为导通状态,在下部电极18被施加比上部电极22高的电压的状态下,向第1栅极电极15a施加绝缘栅构造的阈值电压Vth以上的高电平的电压。由此,在基体层12中的与配置第1栅极电极15a的IGBT用沟槽131a相接的部分,形成反型层。并且,从发射极区域19经由反型层将电子向漂移层11供给从而从集电极层16将空穴向漂移层11供给,通过电导率调制而漂移层11的电阻值下降从而成为导通状态。

[0074] 此外,当使IGBT元件为截止状态、使FWD元件为导通状态(即,使FWD元件进行二极管动作)时,切换向上部电极22和下部电极18施加的电压,向上部电极22施加比下部电极18高的电压。并且,向第1栅极电极15a施加不到绝缘栅构造的阈值电压Vth的低电平(例如,0V)的电压。由此,在基体层12中的与IGBT用第1沟槽131a相接的部分不形成反型层,空穴被从基体层12供给并且电子被从阴极层17供给从而FWD元件进行二极管动作。

[0075] 然后,当使FWD元件从导通状态成为截止状态时,进行向下部电极18施加比上部电极22高的电压的逆电压施加。即,当从在FWD元件中流通正向电流的状态将该电流切断时,

进行向下部电极18施加比上部电极22高的电压的逆电压施加。由此,FWD元件成为恢复状态后成为截止状态。

[0076] 此时,在半导体装置中,等位线避开各沟槽13a、13b地弯曲形成。并且,在本实施方式中,使分离单元间距W1比各沟槽间距D1a、D2a、D1b、D2b窄。因此,与使分离单元间距W1为各沟槽间距D1a、D2a、D1b、D2b以上的情况相比,分离单元区域3a的沟槽密度变高。因而,在分离单元区域3a,等位线也不易向基体层12侧进入,在分离单元区域3a也能够抑制电场集中的发生。因而,能够提高分离单元区域3a的耐压,从而能够提高半导体装置的耐压。

[0077] 如以上说明的那样,在本实施方式中,分离单元间距W1比各沟槽间距D1a、D2a、D1b、D2b窄。因此,在分离单元区域3a,与分离单元间距W1为各沟槽间距D1a、D2a、D1b、D2b以上的情况相比,沟槽密度变高。由此,在分离单元区域3a中等位线也不易向基体层12侧进入,在分离单元区域3a也能够抑制电场集中的发生。因而,能够提高分离单元区域3a的耐压,从而能够提高半导体装置的耐压。

[0078] (第2实施方式)

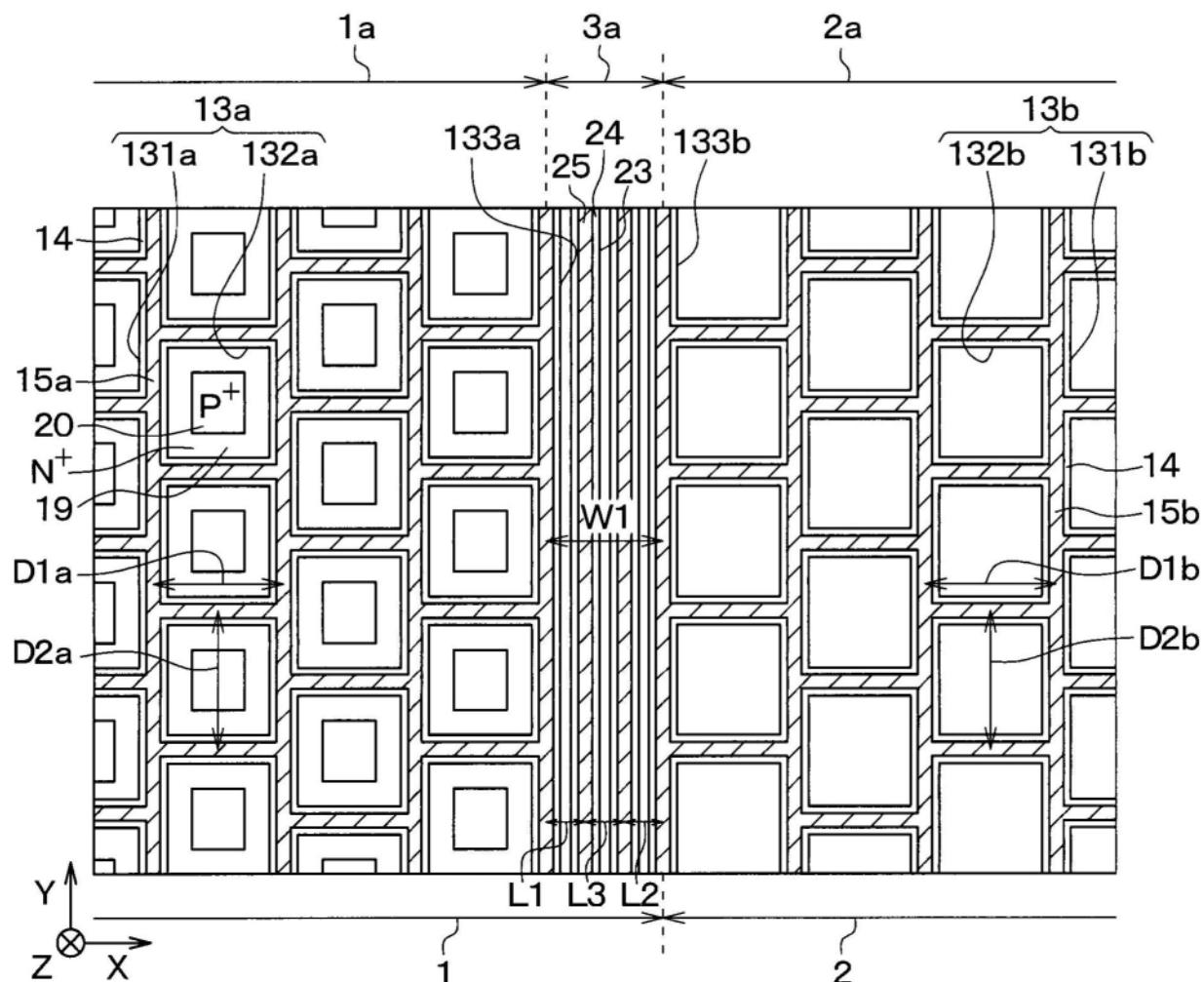

[0079] 对第2实施方式进行说明。本实施方式相对于第1实施方式在分离单元区域3a形成了伪沟槽。其他与第1实施方式相同所以这里省略说明。

[0080] 本实施方式中,如图3及图4所示,在分离单元区域3a,形成有沿Y轴方向延伸并与IGBT用沟槽13a及FWD用沟槽13b分离的1个伪沟槽23。本实施方式中,该伪沟槽23形成得比IGBT用沟槽13a及FWD用沟槽13b深。

[0081] 并且,伪沟槽23被将伪沟槽23的壁面覆盖而形成的伪绝缘膜24和在该伪绝缘膜24之上形成的由多晶硅等构成的伪电极25填埋。另外,本实施方式的伪电极25在与图1不同的截面中与上部电极22电连接。

[0082] 这里,在本实施方式中,将伪沟槽23的中心与IGBT用端部沟槽133a的中心之间的距离设为分离用第1沟槽间距L1。此外,将伪沟槽23的中心与FWD用端部沟槽133b的中心之间的距离设为分离用第2沟槽间距L2。另外,伪沟槽23的中心是伪沟槽23的X轴方向的中心。此外,分离单元间距W1成为分离用第1沟槽间距L1与分离用第2沟槽间距L2之和。

[0083] 并且,在本实施方式中,分离用第1沟槽间距L1以及分离用第2沟槽间距L2比各沟槽间距D1a、D2a、D1b、D2b窄,并且分离单元间距W1比各沟槽间距D1a、D2a、D1b、D2b窄。另外,在本实施方式中,分离用第1沟槽间距L1与分离用第2沟槽间距L2相等。

[0084] 如以上说明的那样,在本实施方式中,在分离单元区域3a形成有伪沟槽23。因此,在分离单元区域3a,能够进一步提高沟槽密度,能够进一步实现耐压的提高。

[0085] 此外,伪沟槽23形成得比IGBT用沟槽13a以及FWD用沟槽13b深。因此,与伪沟槽23被设为与IGBT用沟槽13a以及FWD用沟槽13b相同深度的情况相比,在分离单元区域3a,等位线更不易向基体层12侧进入。因而,能够进一步提高分离单元区域3a的耐压。

[0086] (第2实施方式的变形例)

[0087] 对上述第2实施方式的变形例进行说明。在上述第2实施方式中,也可以如图5所示,在分离单元区域3a,多个伪沟槽23沿X轴方向排列形成。该情况下,将IGBT用端部沟槽133a的中心与和IGBT用端部沟槽133a相邻的伪沟槽23的中心之间的距离设为分离用第1沟槽间距L1。此外,将FWD用端部沟槽133b的中心与和FWD用端部沟槽133b相邻的伪沟槽23的中心之间的距离设为分离用第2沟槽间距L2。并且,将相邻的伪沟槽23彼此的中心间的距离

设为分离用第3沟槽间距L3。该情况下,分离用第1~第3沟槽间距L1~L3比各沟槽间距D1a、D2a、D1b、D2b窄。

[0088] 此外,在这样的变形例中,也可以进一步形成多个伪沟槽23。该情况下,将相邻的伪沟槽23彼此的中心间的最大距离设为分离用第3沟槽间距L3即可。

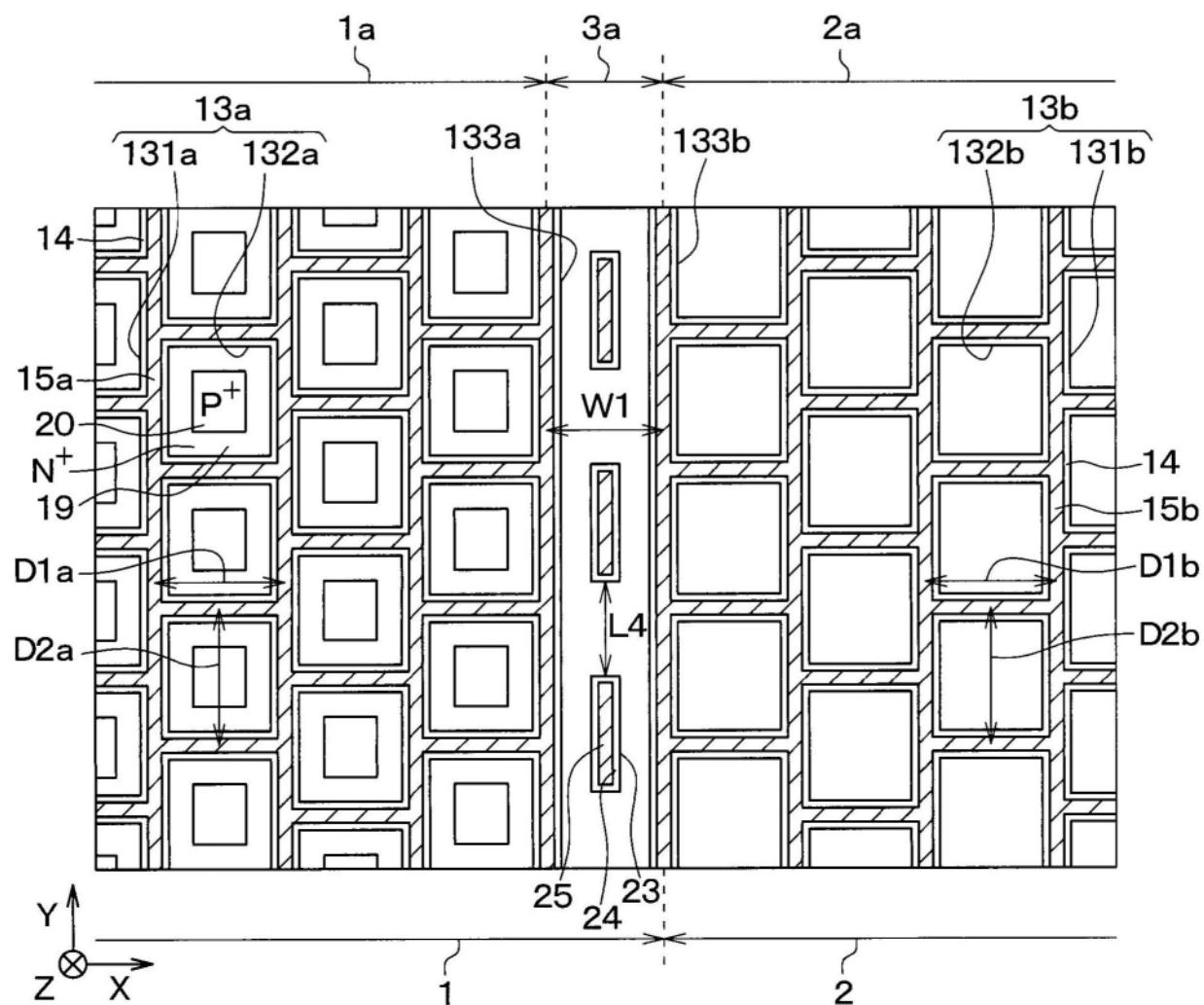

[0089] 进而,在上述第2实施方式中,也可以如图6所示,伪沟槽23沿Y轴方向分离为多个。另外,在设为这样的结构的情况下,若沿Y轴方向将相邻的伪沟槽23的间隔设为分离用第4沟槽间距L4,则伪沟槽23构成为,分离用第4沟槽间距L4也比各沟槽间距D1a、D2a、D1b、D2b窄。由此,能够实现分离单元区域3a的沟槽密度的提高,能够得到与上述第2实施方式同样的效果。

[0090] (第3实施方式)

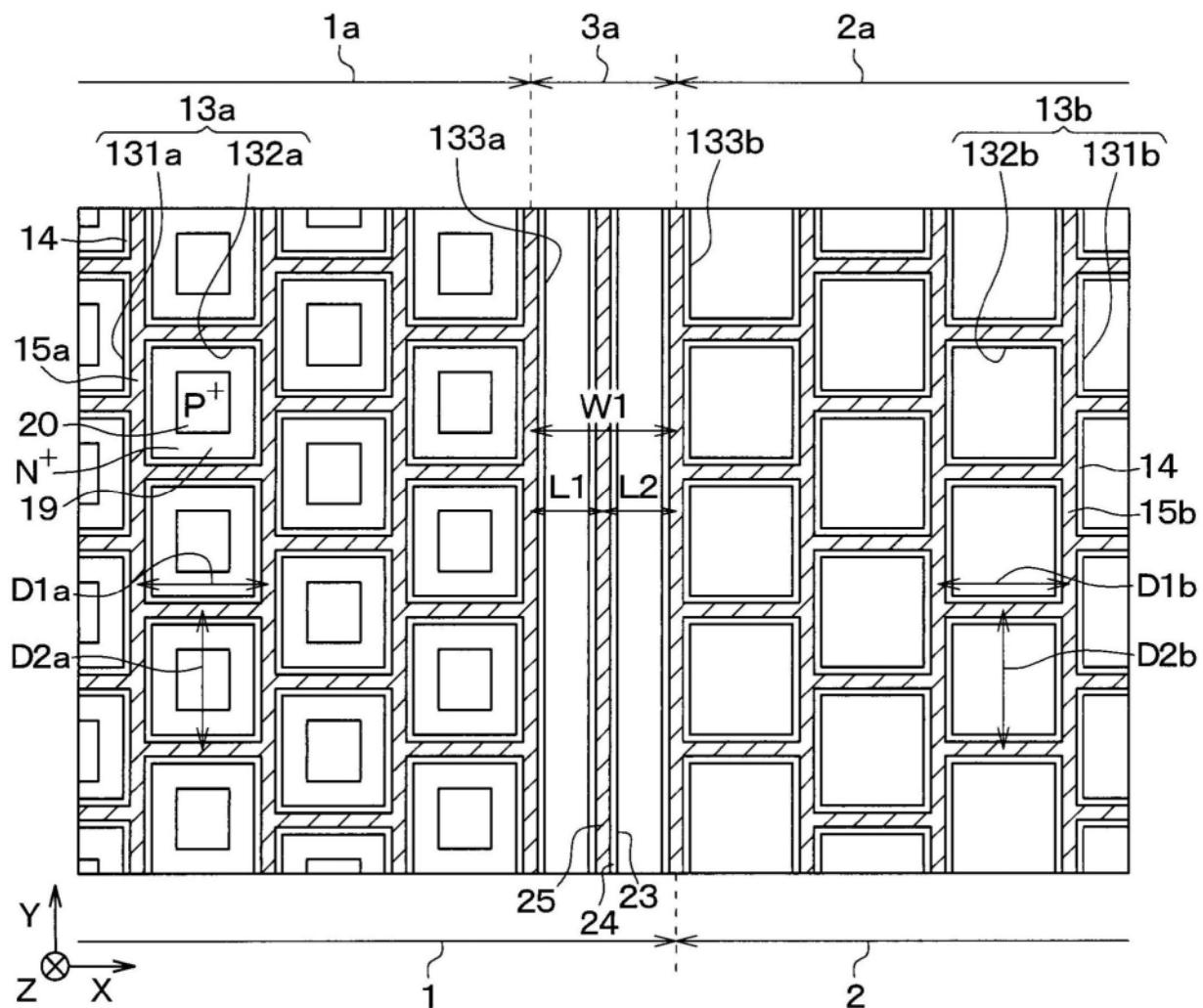

[0091] 对第3实施方式进行说明。第3实施方式相对于第2实施方式改变了分离单元间距W1与各沟槽间距D1a、D2a、D1b、D2b的关系。其他与第1实施方式相同所以这里省略说明。

[0092] 在本实施方式中,如图7所示,分离单元间距W1比各沟槽间距D1a、D2a、D1b、D2b宽。但是,分离用第1沟槽间距L1以及分离用第2沟槽间距L2分别比各沟槽间距D1a、D2a、D1b、D2b窄。

[0093] 如以上说明的那样,如果分离用第1、第2沟槽间距L1、L2比各沟槽间距D1a、D2a、D1b、D2b窄,则分离单元间距W1也可以比各沟槽间距D1a、D2a、D1b、D2b宽。这样的半导体装置也由于分离单元区域3a的沟槽密度提高从而能够得到与上述第2实施方式同样的效果。

[0094] 另外,虽未特别图示,但本实施方式还能够适当与上述第2实施方式的变形例组合。该情况下,例如,在采用图5的结构的情况下,使分离用第1~第3沟槽间距L1~L3比各沟槽间距D1a、D2a、D1b、D2b窄即可。

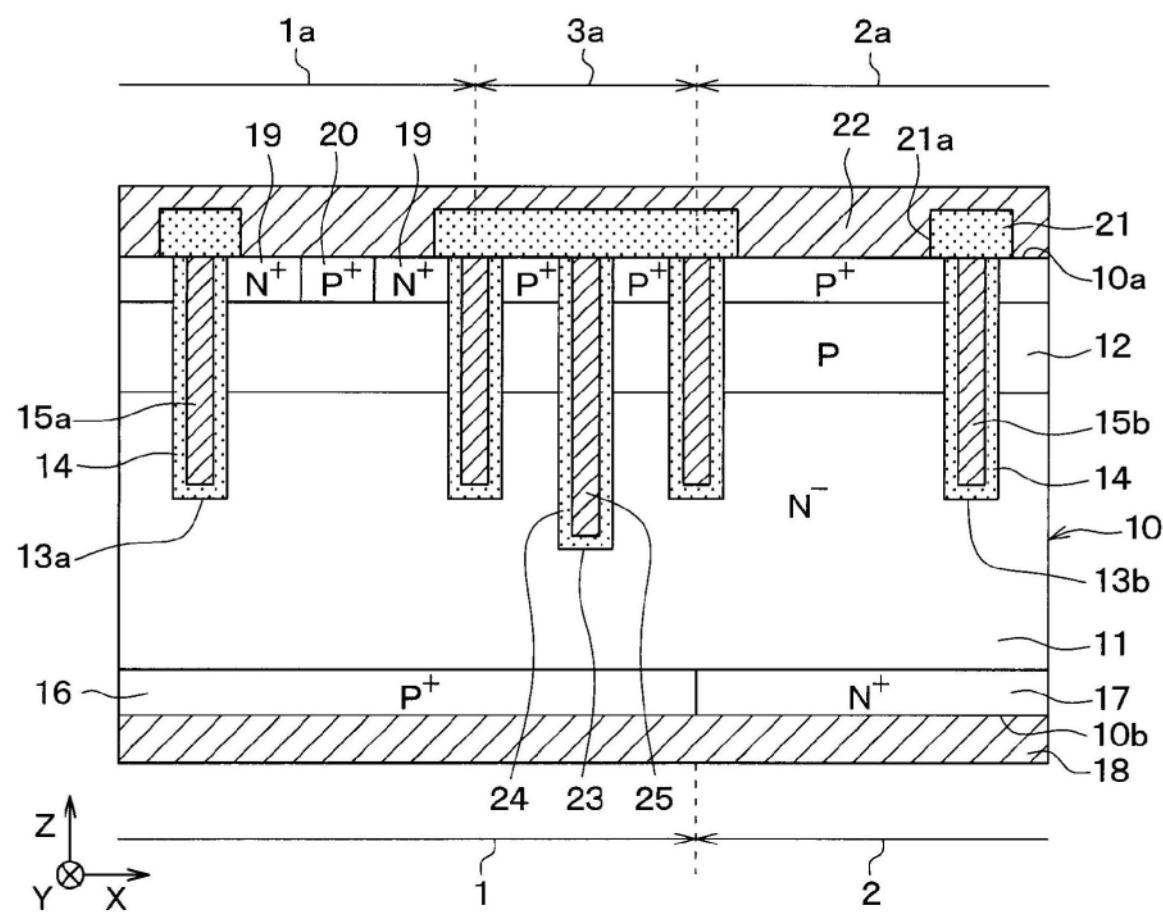

[0095] (第4实施方式)

[0096] 对第4实施方式进行说明。第4实施方式相对于第1实施方式改变了分离单元区域3a的基体层12的结构。其他与第1实施方式相同所以这里省略说明。

[0097] 在本实施方式中,如图8所示,在分离单元区域3a,基体层12的深度形成得比IGBT单元区域1a及FWD单元区域2a深。即,分离单元区域3a构成为,与IGBT单元区域1a及FWD单元区域2a相比,基体层12中的每单位体积的杂质量变高。

[0098] 另外,这样的半导体装置的基体层12例如如下那样制造。即,基体层12通过向半导体衬底10离子注入P型杂质并进行热处理而形成。该情况下,在构成分离单元区域3a的部分,通过加大离子注入时的加速电压、或者多次进行离子注入,从而与IGBT单元区域1a及FWD单元区域2a相比将基体层12较深地形成。

[0099] 如以上说明的那样,本实施方式中,在分离单元区域3a,与IGBT单元区域1a及FWD单元区域2a相比将基体层12形成得更深。因此,在分离单元区域3a,与IGBT单元区域1a及FWD单元区域2a相比,基体层12与漂移层11之间的耗尽层成为向半导体衬底10的另一面10b侧延伸了的状态。因而,在分离单元区域3a,等位线更不易向基体层12侧进入,能够抑制在分离单元区域3a发生电场集中。

[0100] (第4实施方式的变形例)

[0101] 对上述第4实施方式的变形例进行说明。在上述第4实施方式中,分离单元区域3a中的基体层12也可以比IGBT单元区域1a及FWD单元区域2a中的基体层12高杂质浓度。由此,

等位线更不易向基体层12侧进入,在分离单元区域3a能够抑制发生电场集中。另外,在这样的结构下,分离单元区域3a中的基体层12也可以与IGBT单元区域1a及FWD单元区域2a中的基体层12深度相同。

[0102] 此外,在上述第4实施方式中,分离单元间距W1也可以为各沟槽间距D1a、D2a、D1b、D2b以上。这样的半导体装置也能够通过改变分离单元区域3a的基体层12而抑制电场集中发生,从而能够实现耐压的提高。

[0103] (第5实施方式)

[0104] 对第5实施方式进行说明。第5实施方式相对于第1实施方式在分离单元区域3a形成了连通沟槽。其他与第1实施方式相同所以这里省略说明。

[0105] 在本实施方式中,如图9所示,在分离单元区域3a,形成有将IGBT用端部沟槽133a和FWD用端部沟槽133b相连的连通沟槽134。具体而言,连通沟槽134沿着X轴方向延伸而形成,并且形成有多个。并且,IGBT用端部沟槽133a和FWD用端部沟槽133b经由各连通沟槽134而连通。即,本实施方式中,IGBT用沟槽13a和FWD用沟槽13b一体形成。

[0106] 并且,在连通沟槽134中,配置有将第1栅极电极15a和第2栅极电极15b绝缘的绝缘膜135。

[0107] 如以上说明的那样,在本实施方式中,在分离单元区域3a形成有连通沟槽134。因此,能够进一步提高分离单元区域3a的沟槽密度。因而,能够进一步抑制分离单元区域3a中的电场集中发生。

[0108] (第5实施方式的变形例)

[0109] 对上述第5实施方式的变形例进行说明。上述第5实施方式中,分离单元间距W1也可以设为各沟槽间距D1a、D2a、D1b、D2b以上。作为这样的半导体装置,也通过在分离单元区域3a形成连通沟槽134,从而与没有形成连通沟槽134的情况相比能够抑制电场集中发生,因此能够实现耐压的提高。

[0110] 此外,在上述第5实施方式中,连通沟槽134可以仅形成有1个。作为这样的半导体装置,也与没有形成连通沟槽134的情况相比,能够提高沟槽密度。

[0111] 进而,在上述第5实施方式中,如果第1栅极电极15a与第2栅极电极15b绝缘,则第1栅极电极15a及第2栅极电极15b也可以一部分延伸到连通沟槽134内。

[0112] (第6实施方式)

[0113] 对第6实施方式进行说明。第6实施方式相对于第1实施方式形成了柱(pillar)区域、阻挡(barrier)区域、电场缓和区域。其他与第1实施方式相同所以这里省略说明。

[0114] 本实施方式中,如图10及图11所示,在IGBT单元区域1a、分离单元区域3a、FWD单元区域2a中,在漂移层11与基体层12之间,形成有比基体层12低杂质浓度的P<sup>+</sup>型的电场缓和区域26。并且,在IGBT单元区域1a、FWD单元区域2a、分离单元区域3a中,在电场缓和区域26与基体层12之间,形成有比漂移层11高杂质浓度的N型的阻挡区域27。另外,各沟槽13a、13b形成为,将基体层12、阻挡区域27、电场缓和区域26贯通并到达漂移层11。

[0115] 此外,在本实施方式中,在IGBT单元区域1a及FWD单元区域2a中,形成有发射极区域19。具体而言,在IGBT单元区域1a,发射极区域19相对于形成该IGBT单元区域1a的1个单元的一对IGBT用第1沟槽131a分别沿着位于大致中央部的部分形成。同样,在FWD单元区域2a,发射极区域19相对于形成该FWD单元区域2a的1个单元的一对FWD用第1沟槽131b分别沿

着位于大致中央部的部分形成。

[0116] 此外,在IGBT单元区域1a及FWD单元区域2a,在基体层12的表层部,以被接触区域20包围的方式形成有N型的柱区域28。柱区域28到达阻挡区域27,以与阻挡区域27连接的方式形成。柱区域28相对于上部电极22被肖特基连接。

[0117] 并且,在本实施方式中,在IGBT单元区域1a及FWD单元区域2a,如上述那样形成有发射极区域19、接触区域20、柱区域28,所以在半导体衬底10的一面10a,基体层12也成为露出的状态。

[0118] 此外,在漂移层11中的与基体层12侧相反侧(即,半导体衬底10的另一面10b侧),形成有比漂移层11高杂质浓度的N型的场阻挡(field stop)层(以下称作FS层)29。该FS层29用于通过防止耗尽层的扩展而实现耐压和稳态损失的性能提高,并且控制从半导体衬底10的另一面10b侧注入的空穴的注入量。

[0119] 进而,在本实施方式中,成为在阴极层17局部地形成有P+型的注入区域30的状态。本实施方式中,注入区域30形成有多个且形成为格子状,但也可以仅设为1个,也可以设为沿Y轴方向延伸的条状,也可以不规则地形成。另外,该注入区域30与接触区域20为相同的杂质浓度。

[0120] 在以上说明的本实施方式中,阻挡区域27经由柱区域28而维持为上部电极22的电位。因此,该半导体装置中,当使FWD元件导通时,由基体层12与阻挡区域27之间的PN结构成的二极管不易导通,通过使上部电极22的电位上升而导通。因而,能够使二极管动作稳定。

[0121] 此外,在本实施方式的半导体装置中,在阻挡区域27与漂移层11之间,形成有P型的电场缓和区域26。因此,与没有形成电场缓和区域26的情况相比,通过在电场缓和区域26与漂移层11之间构成的PN结,等位线不易向各沟槽13a、13b之间进入,能够进一步实现耐压的提高。

[0122] (其他实施方式)

[0123] 本发明依据实施方式进行了描述,但应理解的是本发明不限于该实施方式及构造。本发明也包含各种各样的变形例及等同范围内的变形。除此以外,各种各样的组合及形态、进而在它们中仅包含一要素、其以上或其以下的其他组合及形态也落入本发明的范畴及思想范围。

[0124] 例如,上述各实施方式中,说明了将第1导电型设为N型并将第2导电型设为P型的例子,但也能将第1导电型设为P型并将第2导电型设为N型。

[0125] 此外,在上述各实施方式中,也可以是,在分离单元区域3a,以与IGBT用沟槽13a相接的方式形成发射极区域19,使该发射极区域19也与上部电极22连接。

[0126] 进而,上述各实施方式中,在分离单元区域3a,也可以在从外周区域离开了的位置形成有接触孔21a。例如,上述第1实施方式中,在图1中,也可以形成有使分离单元区域3a的接触区域20露出的接触孔21a。

[0127] 此外,在上述各实施方式中,集电极层16与阴极层17的边界也可以形成在其他位置。例如,集电极层16与阴极层17的边界也可以形成在IGBT用端部沟槽133a的正下方,也可以形成在IGBT用端部沟槽133a与FWD用端部沟槽133b之间的中央部。即,分离单元区域3a也可以仅包含在FWD区域2内,也可以包含在IGBT区域1及FWD区域2。

[0128] 进而,在上述第1、第2、第4~第6实施方式中,例如也可以是,相邻的IGBT用第1沟

槽131a彼此的间隔不同,IGBT用第1沟槽间距D1a按每部分而不同。同样,相邻的IGBT用第2沟槽132a彼此的间隔、相邻的FWD用第1沟槽131b彼此的间隔、相邻的FWD用第2沟槽132b彼此的间隔也可以不同。在这样的结构的情况下,分离单元间距W1比各沟槽间距D1a、D2a、D1b、D2b的最小距离窄即可。

[0129] 此外,在上述第1~第5实施方式中,也可以还在FWD区域2也形成有发射极区域19。并且,上述第6实施方式中,也可以在FWD区域2不形成发射极区域19。

[0130] 进而,上述第2实施方式中,伪电极25也可以不与上部电极22等连接而设为浮置状态。

[0131] 此外,也可以将上述各实施方式适当组合。例如,上述第4实施方式可以与上述第2、第3实施方式适当组合。此外,上述第5实施方式可以与上述第2~第4实施方式适当组合。进而,上述第6实施方式可以与上述第2~第5实施方式适当组合。并且,也可以将组合各实施方式而得到的形态彼此进一步组合。

图1

图2

图3

图4

图5

图6

图7

图8

图10

图11