i 4 8 6 9 **3**

**SPRUSON & FERGUSON**

### AUSTRALIA

#### PATENTS ACT 1990

#### PATENT REQUEST: STANDARD PATENT

I/We, the Applicant(s)/Nominated Person(s) specified below, request I/We be granted a patent for the invention disclosed in the accompanying standard complete specification.

#### [70,71] Applicant(s)/Nominated Person(s):

NEC Corporation, incorporated in Japan, of 7-1, Shiba 5-chome, Minato-ku, Tokyo, JAPAN

#### [54] Invention Title:

Driver Circuit for Long Luminescence Life Display Device and Method of Driving Such Device

# [72] Inventor(s):

Motoyoshi Komoda and Minoru Katsumata

#### [74] Address for service in Australia:

Spruson & Ferguson, Patent Attorneys Level 33 St Martins Tower 31 Market Street Sydney New South Wales Australia (Code SF)

[31] Appl'n No(s):

Details of Basic Application(s):[33] Country:[32] Application Date:JP2 October 1991

91-282117

· · · ·

.....

•::•:

::::

.....

DATED this TWENTY FOURTH day of SEPTEMBER 1992

NEC Corporation

1. G. Sin Cy:

Registered Patent Attorney

IRN: 221001

INSTR CODE: 57995

\$ 032390 250992

### **SPRUSON & FERGUSON**

#### Australia

#### Patents Act 1990

## NOTICE OF ENTITLEMENT

I, John Gordon Hinde, of Spruson & Ferguson, St Martins Tower, 31 Market Street, Sydney, New South Wales 2000, Australia, being the patent attorney for the Applicant(s)/Nominated Person(s) in respect of an application entitled:

> Driver Circuit for Long Luminescence Life Display Device and Method of Driving Such Device

state the following:-

The Applicant(s)/Nominated Person(s) has/have entitlement from the actual inventor(s) as follows:-

The Applicant(s)/Nominated Person(s) is/are the assignee(s) of the actual inventor(s).

The Applicant(s)/Nominated Person(s) is/are the applicant(s) of the basic application(s) listed on the Patent Request. The basic application(s) listed on the Patent Request is/are the application(s) first made in a Convention Country in respect of the invention.

DATED this

16th

day of December

1992

John Gordon Hinde

IRN: 221001

INSTR CODE: 57995

2

KRS/665P

#### (11) Document No. AU-B-25372/92 (12) PATENT ABRIDGMENT (19) AUSTRALIAN PATENT OFFICE (10) Acceptance No. 648693 (54) Title DRIVER CIRCUIT FOR LONG LUMINESCENCE LIFE DISPLAY DEVICE AND METHOD OF DRIVING SUCH DEVICE International Patent Classification(s) (51)<sup>5</sup> H05B 033/08 (22) Application Date : 25.09.92 (21) Application No. : 25372/92 Priority Data (30) (31) Number (32) Date (33) Country JP JAPAN 3-282117 02.10.91 (43) Publication Date : 08.04.93 (44) Publication Date of Accepted Application : 28.04.94 (71) Applicant(s) NEC CORPORATION (72) inventor(s) MOTOYOSHI KOMODA: MINORU KATSUMATA Attorney or Agent (74) SPRUSÓN & FERGUSON, GPO Box 3898, SYDNEY NSW 2001 Prior Art Documents (56) US 4845489 EP 277254 Claim (57) A driver circuit for applying a driving voltage 1. to a display device, comprising:

110225372

. . ./2

first clock generator means for generating a first clock pulse having a first frequency;

second clock generator means for generating a second clock pulse having a second frequency lower than the first frequency;

gate means for receiving the first and second clock pulses and allowing the first clock pulse to pass when the second clock pulse is present;

high voltage pulse generation means for generating a high voltage pulse in synchronism with the pulse output from the gate means;

voltage multiplication rectifying means for performing a voltage multiplication rectifying of the high voltage pulse to obtain a high voltage output; and

# (11) AU-B-25372/92 (10) 648693

reset means for resetting the voltage multiplication rectifying means when the second clock pulse is off.

6. A method of driving a display device, comprising the steps of:

generating a first clock pulse having a first frequency;

generating a second clock pulse having a second frequency lower than the first frequency;

allowing the first clock pulse to pass responsive to the second clock pulse;

generating a high voltage pulse in synchronism with the passed first clock pulse;

performing a voltage multiplication rectifying of the high voltage pulse to obtain a high voltage output; and

resetting the voltage multiplication rectifying operation when the second clock pulse is off.

6486

----

AUSTRALIA PATENTS ACT 1990

COMPLETE SPECIFICATION

FOR A STANDARD PATENT

## ORIGINAL

Name and Address of Applicant:

. . .

*....*

.....

••••••

•••••

NEC Corporation 7-1, Shiba 5-chome Minato-ku Tokyo JAPAN

Actual Inventor(s):

Motoyoshi Komoda and Minoru Katsumata

Address for Service:

Spruson & Ferguson, Patent Attorneys Level 33 St Martins Tower, 31 Market Street Sydney, New South Wales, 2000, Australia

Invention Title:

Driver Circuit for Long Luminescence Life Display Device and Method of Driving Such Device

The following statement is a full description of this invention, including the best method of performing it known to me/us:-

# DRIVER CIRCUIT FOR LONG LUMINESCENCE LIFE DISPLAY DEVICE AND METHOD OF DRIVING SUCH DEVICE

١

# BACKGROUND OF THE INVENTION

The present invention relates to a driver circuit for driving a display device, and more particularly to a driver circuit for properly driving electroluminescence (hereinafter referred to as "EL") elements to be used for a back light of a display part of a portable device. Description of the Related Arts

Conventionally, when FL elements are used for a display part of a pertable device, an AC voltage of approximately several 10 V to several 100 V with a frequency of approximately 50 Hz to 1 KHz is required for driving the EL elements, and thus a circuit for generating this AC voltage from a DC power source is required.

In a conventional driver circuit for the EL elements, a so-called inverter circuit for generating an AC voltage by using an oscillator circuit including a transistor and a transformer is used.

As described above, in the conventional EL element driver circuit, in order to generate the AC voltage of approximately several 10 V to several 100 V with the frequency of approximately 50 Hz to 1 KHz, the cscillator circuit including the transistor and the transformer is used, and an oscillating frequency of the inverter circuit using this oscillator circuit is the same as a driving frequency of the EL elements.

In the EL element driver circuit of such a construction, when the oscillating frequency is determined to

20

25

15

5

such a low frequency of approximately 50 Hz to 1 KHz, the transformer used becomes large and thus heavy and such a large and heavy transformer is not suitable for a portable device. Further, on the contrary, when the oscillating frequency is determined to a high frequency such as several 10 KHz to several 100 KHz, the transformer can be small-sized and light-weighted. However, by a property of the EL elements that the higher the driving frequency of the EL elements, the lower the luminescence life of the EL elements, it is impossible to satisfy both the small-sizing and light-weighting of the EL element driver circuit and the luminescence life of the EL elements.

Further, when the inverter circuit is operated at a frequency around 1 KHz, a vibration of the transformer comes into the ear of a user and gives an unpleasant feeling to the user of the portable device.

# SUMMARY OF THE INVENTION

It is therefore an object of the present invention to provide a display driver circuit in view of the aforementioned defects of the prior art, which is capable of achieving a long luminescence life of EL elements by determining a driving frequency to a low frequency and a small size and a light weight by without using a transformer.

In accordance with one aspect of the present invention, there is provided a driver circuit for applying a driving voltage to a display device, comprising first clock generator means for generating a first clock pulse having a first frequency; second clock generator means for generating a second clock pulse having a second frequency lower than the

10

5

.

15

20

25

first frequency; gate means for receiving the first and second clock pulses and allowing the firs  $\iota$  clock pulse to pass when the second clock pulse is present; high voltage pulse generation means for generating a high voltage pulse in synchronism with the pulse output from the gate means; voltage multiplication rectifying means for performing a voltage multiplication rectifying of the high voltage pulse to obtain a high voltage output; and reset means for resetting the voltage multiplication rectifying means when the second clock pulse is off.

In accordance with another aspect of the present invention, there is provided a method of driving a display device, comprising the steps of generating a first clock pulse having a first frequency; generating a second clock pulse having a second frequency lower than the first frequency; allowing the first clock pulse to pass responsive to the second clock pulse; generating a high voltage pulse in synchronism with the passed first clock pulse; performing a voltage multiplication rectifying of the high voltage pulse to obtain a high voltage output; and resetting the voltage multiplication rectifying operation when the second clock pulse is off.

## BRIEF DESCRIPTION OF THE DRAWINGS

The objects, features and advantages of the present invention will become more apparent from the consideration of the following detailed description, taken in conjunction with the accompanying drawings, in which:

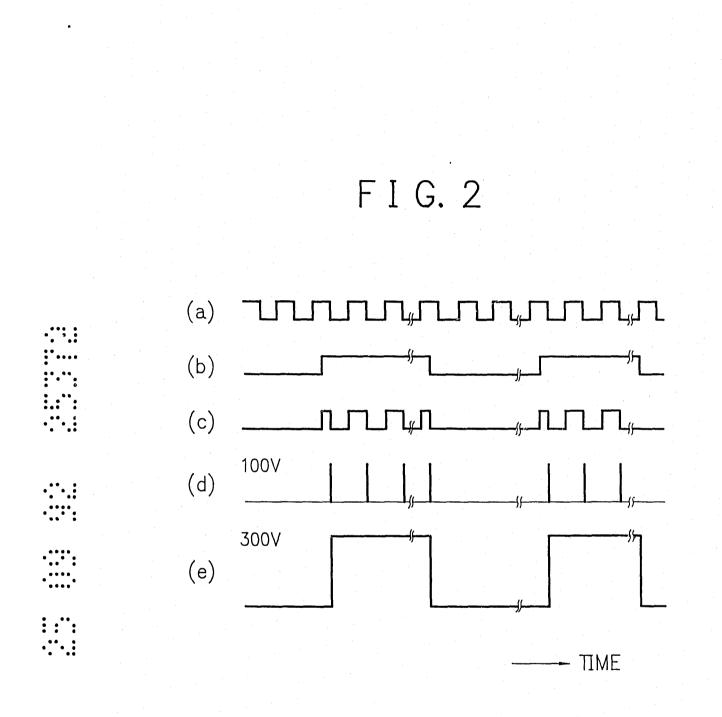

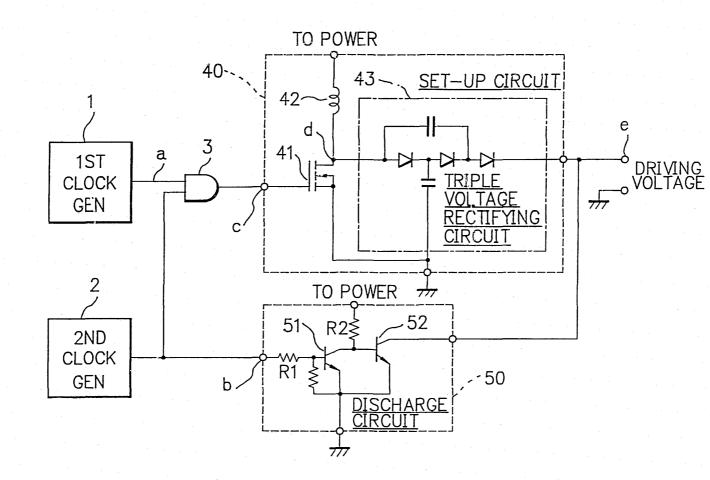

Fig. 1 is a circuit diagram of a driver circuit for a display device according to the present invention; and

- 3 -

25

5

10

15

20

Figs. 2a to 2e are timing charts showing waveforms of signals shown in Fig. 1.

- 4 -

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring now to the drawings, there is shown in Fig. 1 one embodiment of a driver circuit for a display device according to the present invention, and Figs. 2a to 2e show waveforms of signals at predetermined points <u>a</u>to<u>e</u> in the driver circuit shown in Fig, 1.

As shown in Fig. 1, the driver circuit includes a first clock generator circuit 1, a second clock generator circuit 2, an AND gate circuit 3, a voltage rising or stepup circuit 40 and a discharge circuit 50.

The first clock generator circuit 1 for generating a voltage of a high frequency outputs a first clock pulse <u>a</u> having a frequency of approximately 250 KHz to the AND gate circuit 3, and the second clock generator circuit 2 for generating a clock of a low frequency for lighting EL (electroluminescence) elements outputs a second clock pulse <u>b</u> having a frequency of approximately 200 Hz to the AND gate circuit 3 and the discharge circuit 50. Only when the first clock pulse <u>a</u> is a high (H) level and a second clock pulse <u>b</u> is the high level, the AND gate circuit 3 outputs the first clock pulse <u>a</u> to the step-up circuit 40.

25

The step-up circuit 40 includes an N-channel MOSFET 41, a coil or an inductance 42 and a triple voltage rectifying circuit 43. That is, an output clock pulse <u>c</u> of the AND gate circuit 3 is input to the gate of the N-channel MOSFET 41. The inductance 42 connected between a power source (not shown) and the drain of the N-channel MOSFET 41

10

5

15

20

::::

via a node <u>d</u>. The triple voltage rectifying circuit 43 is connected between the drain of the N-channel MOSFET 41 via the node <u>d</u> and an output terminal <u>e</u>. The source of the Nchannel MOSFET 41 is grounded. In this case, in place of the triple voltage rectifying circuit 43, an n times voltage rectifying circuit may be provided.

The discharge circuit 50 acts as a reset circuit for the triple voltage rectifying circuit 43 and includes first and second transistors 51 and 52 and first and second resistors R1 and R2. That is, the second clock pulse <u>b</u> output from the second clock generator circuit 2 is input to the base of the first transistor 51 via the first resistor R1. The base of the second transistor 52 is connected with the collector of the first transistor 51 and the power source via the second resistor R2. The collector of the second transistor 52 is coupled with the output terminal <u>e</u>. The emitters of the first and second transistors 51 and 52 are grounded.

Next, the operation of the above-described driver circuit shown in Fig. 1 will now be described in connection with Figs. 2a to 2e.

First, the first clock pulse <u>a</u> output from the first clock generator circuit 1 and the second clock pulse <u>b</u> output from the second clock generator circuit 2 are input to the AND gate circuit 3, and, only when the first clock pulse <u>a</u> is the high level and the second clock pulse <u>b</u> is the high level, the first clock pulse <u>a</u> is output from the AND gate circuit 3 to the step-up circuit 40.

In the step-up circuit 40, when the output clock pulse c of the AND gate circuit 3 is the high level, the N-

.

5

10

15

a 12

.

20

25

channel MOSFET 41 is switched on, and a current flows in the inductance 42 connected between the power source and the drain of the N-channel MOSFET 41. In turn, when the output clock pulse <u>c</u> of the AND gate circuit 3 is a low (L) level, the N-channel MOSFET 41 is switched off, and no current flows in the inductance 42.

- 6 -

At a moment when the N-channel MOSFET 41 is switched off, the inductance 42 generates a counter-electromotive voltage and thus a high voltage impulse having a voltage of approximately 100 V is generated at the node <u>d</u>. This impulse is rectified by the triple voltage rectifying circuit 43 to obtain and output an DC voltage of approximately 300 V to the output terminal <u>e</u>.

On the other hand, when the second clock pulse <u>b</u> output from the second clock generator circuit 2 is the low level and the first clock pulse <u>a</u> is not output from the AND gate circuit 3 to the step-up circuit 40, the first transistor 51 of the discharge circuit 50 is turned off and thus the second transistor 52 is switched on. Hence, the electric charge accumulated in a capacitor of the triple voltage rectifying circuit 43 and the EL elements is discharged, and the voltage for driving the EL elements at the output terminal e is immediately fallen to 0 V.

Accordingly, as described above, an AC voltage having a frequency of approximately 200 Hz with a peak value of approximately 300 V (approximately 100 V rms) is applied to the EL elements, as shown in Fig. 2e.

In this embodiment, although the present invention has been described in connection with the driver circuit for the display device such as the EL elements, the present

5

10

15

20

25

invention is not restricted to this driver circuit.

- 7 -

According to the present invention, as described above, since the frequency of the clock pulse input to the step-up circuit is raised and the operation period of the step-up circuit is lowered, a clock in an audio band for generating a high voltage is not required, and noises offensive to the ear can be removed. Further, an inverter is not required and thus a small-sizing and a light-weighting of a driver circuit can be achieved.

Further, since the driving frequency of the EL elements can be lowered at the operation period of the stepup circuit, in particular, the drop of the luminescence life of the EL elements can be prevented and the long luminescence life of the same can be obtained. Hence, such EL elements can be used in optimum as a back light of a display part of a portable device.

While the present invention has been described with reference to the particular illustrative embodiments, it is not to be restricted by those embodiments but only by the appended claims. It is to be appreciated that those skilled in the art can change or modify the embodiments without departing from the scope and spirit of the present invention.

5

10

. .

15

20

The claims defining the invention are as follows: WHAT IS CLAIMED IS :

1. A driver circuit for applying a driving voltage to a display device, comprising:

- 8 -

first clock generatur means for generating a first clock pulse having a first frequency;

second clock generator means for generating a second clock pulse having a second frequency lower than the first frequency;

gate means for receiving the first and second clock pulses and allowing the first clock pulse to pass when the second clock pulse is present;

high voltage pulse generation means for generating a high voltage pulse in synchronism with the pulse output from the gate means;

voltage multiplication rectifying means for performing a voltage multiplication rectifying of the high voltage pulse to obtain a high voltage output; and

reset means for resetting the voltage multiplication rectifying means when the second clock pulse is off.

2. The driver circuit as claimed in claim 1, wherein the gate means is an AND gate, and the AND gate outputs the first clock pulse when both the first and second clock pulses are a high level.

3. The driver circuit as claimed in claim 1, wherein the high voltage pulse generation means includes a coil connected to a power source and a MOSFET connected to the coil, and the output of the gate means is input to the MOSFET.

10

15

5

•••••

....

4. The driver circuit as claimed in claim 1, wherein the voltage multiplication rectifying means is a triple voltage rectifying circuit.

- 9 -

5. The driver circuit as claimed in claim 1, wherein the reset means includes:

first transistor means having a base and a collector for inputting the second clock pulse at the base from the second clock generator means; and

second transistor means having a base connected to the collector of the first transistor means and a power source via a resistor and a collector connected to an output terminal of the driver circuit.

6. A method of driving a display device, comprising the steps of:

generating a first clock pulse having a first frequency;

generating a second clock pulse having a second frequency lower than the first frequency;

allowing the first clock pulse to pass responsive to the second clock pulse;

generating a high voltage pulse in synchronism with the passed first clock pulse;

performing a voltage multiplication rectifying of the high voltage pulse to obtain a high voltage output; and resetting the vol ge multiplication rectifying operation when the second clock pulse is off. DATED this TWENTY-THIRD day of SEPTEMBER 1992 NEC Corporation Patent Attorneys for the Applicant

SPRUSON & FERGUSON

5

5

10

**.** .

**:**•••••

••••

·:•.;

:::;

# Driver Circuit for Long Luminescence Life Display Device and Method of Driving Such Device <u>Abstract of the Disclosure</u>

A driver circuit for a display device is described, in which first 5 and second clock pulse generator circuits (1,2) generate first and second clock pulses (a,b) to a gate circuit (3) for allowing the first clock pulse to pass when the first and second clock pulses are a high level. From the output (c) of the gate circuit (3), a combination of a transistor (41) and an inductance (42) generate a high voltage pulse 10(d). The high voltage pulse (d) is rectified in a triple voltage rectifying circuit (43) to output a high voltage output (e) for driving the display device such as EL elements, and the high voltage output can be reset by a low frequency pulse output from a discharge circuit (50). a result, no inverter is required, and a small-sized and As 15light-weighted driver circuit is achieved with a long luminescence life of the EL elements and without noises offensive to the ear.

Fig. 1

···.:

.....

....

Ý

FIG. 1

25372/92