(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5094529号

(P5094529)

(45) 発行日 平成24年12月12日(2012.12.12)

(24) 登録日 平成24年9月28日(2012.9.28)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36 |         |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 4 1 E |

| <b>G09G</b> | <b>3/34</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 2 1 F |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/34 | J       |

|             |              |                  | G09G | 3/20 | 6 2 3 C |

請求項の数 6 (全 45 頁) 最終頁に続く

(21) 出願番号

特願2008-114019 (P2008-114019)

(22) 出願日

平成20年4月24日 (2008.4.24)

(65) 公開番号

特開2008-293003 (P2008-293003A)

(43) 公開日

平成20年12月4日 (2008.12.4)

審査請求日

平成23年2月25日 (2011.2.25)

(31) 優先権主張番号

特願2007-116435 (P2007-116435)

(32) 優先日

平成19年4月26日 (2007.4.26)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 荒澤 亮

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 福留 貴浩

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】 液晶表示装置の駆動方法、液晶表示装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

画素電極に電圧を印加することで階調を表現する液晶表示装置の駆動方法であって、

1 フレーム期間を n 個 (n : 整数, 3 ≤ n) のサブフレーム期間に分割し、

前記 n 個のサブフレーム期間のうち第 m サブフレーム期間 (m : 整数, 2 ≤ m ≤ n) 以外のサブフレーム期間において、前記液晶表示装置の外部から入力される信号に対応した信号電圧を前記画素電極に印加し、

前記 n 個のサブフレーム期間のうち第 m サブフレーム期間において、液晶の応答量に対する不足又は過剰の応答量を補償するための補償電圧を前記信号電圧に加えて前記画素電極に印加し、

任意の 1 フレーム期間の第 n サブフレーム期間に印加される電圧と、前記任意の 1 フレーム期間の次の 1 フレーム期間の第 1 サブフレーム期間に印加される電圧との差が小さくなるように、前記補償電圧を加える前記第 m サブフレーム期間を選択することを特徴とする液晶表示装置の駆動方法。

## 【請求項 2】

画素電極に電圧を印加することで階調を表現する液晶表示装置の駆動方法であって、

1 フレーム期間を n 個 (n : 整数, 3 ≤ n) のサブフレーム期間に分割し、

前記 n 個のサブフレーム期間のうち第 1 サブフレーム期間以外のサブフレーム期間を k 個 (k : 整数, 1 ≤ k ≤ n - 1) 選択し、

前記選択された k 個のサブフレーム期間以外の n - k 個のサブフレーム期間において、

10

20

前記液晶表示装置の外部から入力される信号に対応した信号電圧を前記画素電極に印加し、

前記選択された  $k$  個のサブフレーム期間において、液晶の応答量に対する不足又は過剰の応答量を補償するための補償電圧を前記信号電圧に加えて前記画素電極に印加し、

任意の 1 フレーム期間の第  $n$  サブフレーム期間に印加される電圧と、前記任意の 1 フレーム期間の次の 1 フレーム期間の第 1 サブフレーム期間に印加される電圧との差が小さくなるように、前記補償電圧を加える前記  $k$  個のサブフレーム期間を選択することを特徴とする液晶表示装置の駆動方法。

#### 【請求項 3】

請求項 1 または請求項 2 において、

10

前記  $n$  個のサブフレーム期間のうちの第 1 サブフレーム期間においては、バックライトを消灯することを特徴とする液晶表示装置の駆動方法。

#### 【請求項 4】

請求項 1 乃至 3 のいずれか一において、

前記  $n$  個のサブフレーム期間のうちの第 1 サブフレーム期間においては、前記信号電圧に代えてオーバードライブ電圧を印加することを特徴とする液晶表示装置の駆動方法。

#### 【請求項 5】

請求項 1 乃至 4 のいずれか一に記載の液晶表示装置の駆動方法を用いた液晶表示装置。

#### 【請求項 6】

請求項 5 に記載の液晶表示装置を用いた電子機器。

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、画質を向上させるための液晶表示装置の駆動方法、及び当該駆動方法を用いた液晶表示装置、電子機器に関する。

##### 【背景技術】

##### 【0002】

近年、従来のブラウン管を用いた表示装置の液晶表示装置への置き換えや、小型電子機器への液晶表示装置の採用が急速に進んでいる。ここで、液晶表示装置とは、基板間の液晶分子に電圧を印加することで液晶分子の配向方向を変化させ、それにより生じる光学特性の変化を利用した表示装置をいう。

30

##### 【0003】

代表的な液晶表示装置としては、例えば、ツイステッドネマティック (TN) 方式を用いたものが挙げられる。TN 方式を用いた表示素子は、2 つの基板間にネマティック液晶を挟みこみ、液晶分子の長軸が 2 つの基板間で 90° 連続的にねじれた構成を有している。したがって、この状態の表示素子の液晶分子に入射した光の偏光方向は、液晶分子のねじれに沿って 90° 变化することになる。

##### 【0004】

ここで、液晶分子に電圧を印加した場合、あるしきい値電圧  $V_{th}$  以上の電圧を印加する事で液晶分子の長軸を電場方向に傾けることができる。すなわち、液晶分子のねじれの様子を 90° から変化させることができる。このとき、このねじれに従って、液晶分子に入射した光の偏光方向も変化することになる。これを光シャッターとして用いるのが TN 方式である。

40

##### 【0005】

上記 TN 方式をアクティブマトリクス駆動することにより、パッシブマトリクス駆動と比較して動画表示性能に優れた表示装置が実現できる。ここで、アクティブマトリクス駆動とは、各画素に作り込んだトランジスタを用いて画素を駆動する方式をいう。

##### 【0006】

このように、TN 方式とアクティブマトリクス駆動とを組み合わせることにより、表示装置としての一応の性能は確保された。しかしながら、従来のブラウン管を用いた表示裝

50

置と比較した場合には、満足な画質が得られているとはいひ難い状況であった。近年では画質向上のために、高速に応答する液晶材料の開発が進められ（例えば、特許文献1参照）、また、OCB（ベンド配向）方式、IPS方式といった、TN方式に変わる方式が採用されるようになっている（例えば、特許文献2参照）。

#### 【0007】

また、上記とは異なるアプローチも検討されている。例えば、オーバードライブ駆動がそれである（例えば、特許文献3参照）。オーバードライブ駆動とは、液晶分子の応答速度を向上するために、一時的に高い電圧を印加する駆動方式である。これにより、所望の輝度に到達するまでの時間を短縮することができ、動画性能が向上する。

【特許文献1】特開平5-17408号公報

10

【特許文献2】特開平7-84254号公報

【特許文献3】特開平7-104715号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0008】

オーバードライブ駆動を用いることにより、確かに液晶分子の応答速度は向上する。しかしながら、応答速度と引き換えに、消費電力の増大の問題が生じる。

#### 【0009】

また、現象の詳細については未だ解明されていないが、オーバードライブ直後には印加電圧の揺らぎが生じるという問題もある。印加電圧の揺らぎが生じた場合には、所望の階調表示が困難になる。特に高階調表示を行う場合において、印加電圧の揺らぎの影響は無視することができない。

20

#### 【0010】

また、オーバードライブ駆動には、表示階調とオーバードライブ電圧との関係を規定した参照表（ルックアップテーブル）が不可欠であるため、当該参照表を格納するための記憶装置が必要である。つまり、高階調表示になるにつれて、いたずらに記憶装置が肥大化してしまうという問題が生じる。

#### 【0011】

上記問題点に鑑み、本発明は、動画性能を含めた画質向上のための液晶表示装置の駆動方法、及び当該駆動方法を用いた液晶表示装置を提供することを課題とする。

30

#### 【課題を解決するための手段】

#### 【0012】

本発明では、1フレーム期間をn（n：整数、n≥3）の期間（以下、サブフレーム期間と記す）に分割する。すなわち、180Hz以上の周波数にて駆動を行う。また、液晶の応答速度に起因する輝度の損失を補償するように液晶に電圧を印加する。ここで、補償された電圧は第1サブフレーム期間以外のサブフレーム期間に印加されることが好ましい。

#### 【0013】

本発明の液晶表示装置の駆動方法の一は、画素電極に電圧を印加することで階調を表現する液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数、3≤n）のサブフレーム期間に分割し、n個のサブフレーム期間のうち第mサブフレーム期間（m：整数、2≤m≤n）以外のサブフレーム期間において、液晶表示装置外部から入力される信号に対応した信号電圧を画素電極に印加し、n個のサブフレーム期間のうち第mサブフレーム期間において、液晶の応答遅れに起因して生じる目標階調からのずれを補償する補償電圧を信号電圧に加えて画素電極に印加することを特徴としている。前記信号電圧は所望の階調に相当する電圧である。前記すれば、所望の階調と、前記第mサブフレーム期間以外のサブフレーム期間において、前記信号電圧を画素電極に印加することにより得られる階調との差に相当する。

40

#### 【0014】

上記においては、対象とする1フレーム期間の第nサブフレーム期間に印加される電圧

50

と、対象とする 1 フレーム期間の次の 1 フレーム期間の第 1 サブフレーム期間に印加される電圧との差が小さくなるように、補償電圧を加える第 m サブフレーム期間を選択することが好ましい。また第 1 フレーム期間の第 n サブフレーム期間に印加される電圧と、第 2 フレーム期間の第 1 サブフレーム期間に印加される電圧との差が小さくなるように、第 1 フレーム期間の第 m サブフレーム期間が出現する順番を決定することが好ましい。第 2 フレームは第 1 フレームの次のフレームである。

#### 【 0 0 1 5 】

本発明の液晶表示装置の駆動方法の他の一は、画素電極に電圧を印加することで階調を表現する液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( $n : 整数, 3 \leq n$ ) のサブフレーム期間に分割し、n 個のサブフレーム期間のうち第 1 サブフレーム期間以外のサブフレーム期間を k 個 ( $k : 整数, 1 \leq k \leq n - 1$ ) 選択し、選択された k 個のサブフレーム期間以外の  $n - k$  個のサブフレーム期間において、液晶表示装置外部から入力される信号に対応した信号電圧を画素電極に印加し、選択された k 個のサブフレーム期間において、液晶の応答遅れに起因して生じる目標階調からのずれを補償する電圧を信号電圧に加えて画素電極に印加することを特徴としている。前記信号電圧は所望の階調に相当する電圧である。前記すれば、所望の階調と、前記  $n - k$  個のサブフレーム期間において、前記信号電圧を画素電極に印加することにより得られる階調との差に相当する。

10

#### 【 0 0 1 6 】

上記においては、対象とする 1 フレーム期間の第 n サブフレーム期間に印加される電圧と、対象とする 1 フレーム期間の次の 1 フレーム期間の第 1 サブフレーム期間に印加される電圧との差が小さくなるように、補償電圧を加える k 個のサブフレーム期間を選択することが好ましい。また第 1 フレーム期間の第 n サブフレーム期間に印加される電圧と、第 2 フレーム期間の第 1 サブフレーム期間に印加される電圧との差が小さくなるように、第 1 フレーム期間の k 個のサブフレーム期間が出現する順番を決定することが好ましい。第 2 フレームは第 1 フレームの次のフレームである。

20

#### 【 0 0 1 7 】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( $n : 整数, n \geq 3$ ) のサブフレーム期間に分割し、複数のサブフレーム期間のうち第 1 サブフレーム期間以外のサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

30

#### 【 0 0 1 8 】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( $n : 整数, n \geq 3$ ) のサブフレーム期間に分割し、第 n サブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

#### 【 0 0 1 9 】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( $n : 整数, n \geq 3$ ) のサブフレーム期間に分割し、第  $n - 1$  サブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

40

#### 【 0 0 2 0 】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( $n : 整数, n \geq 3$ ) のサブフレーム期間に分割し、対象となる 1 フレーム期間の次の 1 フレーム期間における信号電圧に応じて、対象となる 1 フレーム期間の第  $n - 1$  サブフレーム期間又は第 n サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧

50

を加えた電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

#### 【0021】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の輝度を得る液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数，n3）のサブフレーム期間に分割し、対象となる1フレーム期間の次の1フレーム期間における信号電圧が、対象となる1フレーム期間の信号電圧以上の場合には、第nサブフレーム期間を選択し、対象となる1フレーム期間の次の1フレーム期間における信号電圧が、対象となる1フレーム期間の信号電圧より小さい場合には、第n-1サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。10

#### 【0022】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の輝度を得る液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数，n3）のサブフレーム期間に分割し、対象となる1フレーム期間の次の1フレーム期間における信号電圧が、対象となる1フレーム期間の信号電圧より大きい場合には、第nサブフレーム期間を選択し、対象となる1フレーム期間の次の1フレーム期間における信号電圧が、対象となる1フレーム期間の信号電圧以下の場合には、第n-1サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。20

#### 【0023】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数，n3）のサブフレーム期間に分割し、複数のサブフレーム期間のうち第1サブフレーム期間以外のサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、信号電圧に補償電圧を加えた電圧を印加するサブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。30

#### 【0024】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数，n3）のサブフレーム期間に分割し、第nサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、第nサブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。40

#### 【0025】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数，n3）のサブフレーム期間に分割し、第n-1サブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、第n-1サブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

#### 【0026】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の階調を得る液晶表示装置の駆動方法であって、1フレーム期間をn個（n：整数，n3）50

3 ) のサブフレーム期間に分割し、対象となる 1 フレーム期間の次の 1 フレーム期間における信号電圧に応じて、対象となる 1 フレーム期間の第 n - 1 サブフレーム期間又は第 n サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、選択されたサブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

#### 【 0 0 2 7 】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の輝度を得る液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( n : 整数 , n 10 3 ) のサブフレーム期間に分割し、対象となる 1 フレーム期間の次の 1 フレーム期間における信号電圧が、対象となる 1 フレーム期間の信号電圧以上の場合には、第 n サブフレーム期間を選択し、対象となる 1 フレーム期間の次の 1 フレーム期間における信号電圧が、対象となる 1 フレーム期間の信号電圧より小さい場合には、第 n - 1 サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、選択されたサブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

#### 【 0 0 2 8 】

本発明の液晶表示装置の駆動方法の他の一は、電圧を画素電極に印加することで、所望の輝度を得る液晶表示装置の駆動方法であって、1 フレーム期間を n 個 ( n : 整数 , n 20 3 ) のサブフレーム期間に分割し、対象となる 1 フレーム期間の次の 1 フレーム期間における信号電圧が、対象となる 1 フレーム期間の信号電圧より大きい場合には、第 n サブフレーム期間を選択し、対象となる 1 フレーム期間の次の 1 フレーム期間における信号電圧が、対象となる 1 フレーム期間の信号電圧以下の場合には、第 n - 1 サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、選択されたサブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加し、補償電圧は、液晶の立ち上がり時間に起因して生じる目標階調とのずれを補償するための電圧であることを特徴とするものである。

#### 【 0 0 2 9 】

なお、本発明の液晶表示装置の駆動方法において、n 個のサブフレーム期間のうちの第 1 サブフレーム期間においては、バックライトを消灯することとしても良い。また、n 個のサブフレーム期間のうちの第 1 サブフレーム期間においては、信号電圧に代えてオーバードライブ電圧を印加することとしても良い。ここで、オーバードライブ電圧とは、液晶の応答を高速化するために一時的に加えられる電圧であって、直前の一フレーム期間からオーバードライブ電圧印加対象の一フレーム期間にかけての液晶の配向状態の変化がより大きくなる方向に加えられるものをいう。言い換えれば、オーバードライブ電圧とは、ある一フレーム期間に液晶に印加される電圧 V<sub>a</sub> における液晶の応答量 ( x<sub>a</sub> ) と、次の一フレーム期間に液晶に印加される電圧 V<sub>b</sub> における液晶の応答量 ( x<sub>b</sub> ) の差の絶対値 ( | x<sub>b</sub> - x<sub>a</sub> | ) が大きくなる方向に一時的に加えられる電圧である。ここで、所定の電圧 ( V ) における液晶の応答量とは、電圧を加えない状態 ( V<sub>0</sub> ) から所定の電圧 ( V ) を加えて十分な時間が経過した状態にかけての液晶の配向状態の変化量 ( S<sub>V</sub> - v<sub>0</sub> ) をいうものとする。つまり、液晶の応答量は、輝度又は表示階調と同様の意味を表すものである。例えば、低輝度側から高輝度側へと表示階調が変化する場合には、目的とする輝度よりさらに高輝度側に液晶が変化するような電圧 ( つまりオーバードライブ電圧 ) を印加することで、液晶の応答速度を向上することができる。

#### 【 0 0 3 0 】

本発明の液晶表示装置の駆動方法を用いることにより、画質が優れた液晶表示装置を提供することができる。なお、本発明の駆動方法を用いた液晶表示装置は、保持容量を十分に小さくすることが可能である。例えば、容量素子を形成するための容量配線を画素部に

10

20

30

40

50

有さない構成の液晶表示装置を提供することもできる。

【0031】

さらに、上記液晶表示装置を用いた様々な電子機器を提供することができる。

【発明の効果】

【0032】

本発明の駆動方法を用いることにより、高い動画性能を実現することが出来る。また、オーバードライブ駆動における問題点を解決することができるため、より高画質を実現することが出来る。

【発明を実施するための最良の形態】

【0033】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いることとする。

【0034】

(実施の形態1)

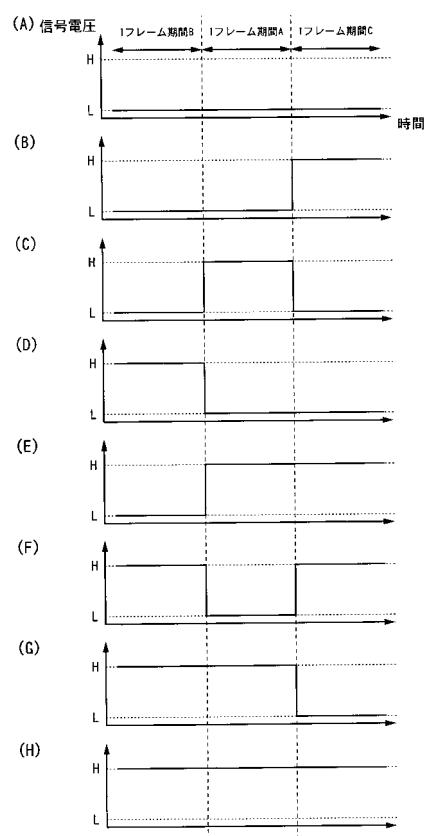

本実施の形態では、本発明の駆動方法とその原理を図1乃至図3を用いて以下に説明する。

【0035】

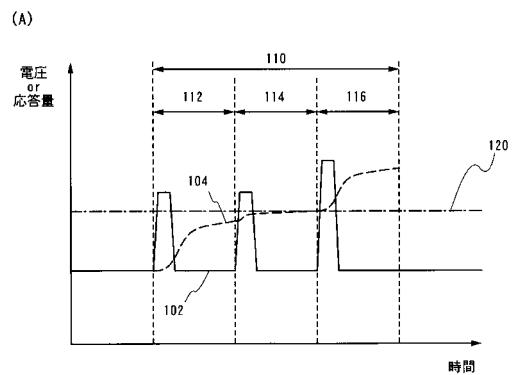

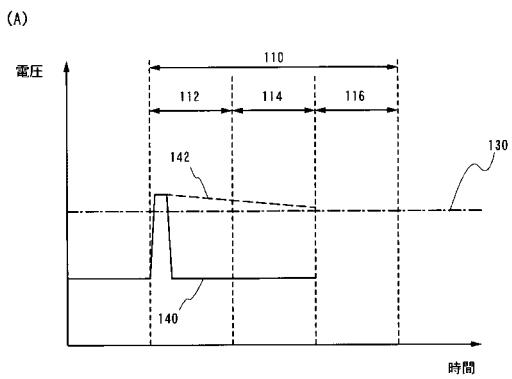

図1(A)に本発明の液晶表示装置の駆動方法を用いた場合の1画素への書き込み期間中に印加される電圧102(実線)と、液晶の応答量104(破線)との関係を示す。ここで、液晶の応答量は液晶表示素子の表示階調に対応している。また、横軸は時間を示しており、縦軸は電圧又は応答量を示している。なお、アクティブマトリクス駆動を用いた液晶表示装置においては、画素の選択期間のみにおいて画素電極に信号電圧が入力され、その後の期間は保持容量によって入力された電圧が保持される(例えば、図10参照)。

【0036】

はじめに、1フレーム期間をn個のサブフレーム期間(n:整数、n>3)に分割する。本実施の形態においては簡単のため、1フレーム期間110を3個のサブフレーム期間(第1サブフレーム期間112、第2サブフレーム期間114、第3サブフレーム期間116)に分割した場合について説明するが、本発明はこれに限られるものではない。なお、液晶表示装置では一般に60Hzで画面の書き換えが行われるから、1フレーム期間は1/60秒となる。本実施の形態では1フレーム期間をさらに3個のサブフレーム期間に分割するから、180Hzでの駆動となる。すなわち、1サブフレーム期間は1/180秒である。いうまでもなく、1フレーム期間をn個のサブフレーム期間に分割する場合には、 $60 \times n$ Hzでの駆動となり、1サブフレーム期間は1/(60×n)秒となる。

【0037】

3個のサブフレーム期間に対応させて、外部からの映像信号を画素電極に入力する。まず、第1サブフレーム期間112と第2サブフレーム期間114において同じ信号(信号電圧)をそれぞれ入力する。なお、第1サブフレーム期間112及び第2サブフレーム期間114において入力される信号(信号電圧)として、外部からの映像信号をそのまま用いても良いし、映像信号に何らかの補正を行った信号、例えば、補正を行った信号などを用いても良い。信号電圧は所望の階調に相当する電圧である。

【0038】

このように、同じ信号を2回入力することにより、1回だけの入力の場合と比較して、液晶の応答速度を向上することが出来る。ここで重要なのは、信号を2回入力すると言う点であるから、第1サブフレーム期間112及び第2サブフレーム期間114において画素電極に入力される入力信号は同じ信号である必要はないが、本実施の形態においては簡単のため、同じ信号を2回入力するものとする。入力信号を異ならせる一例としては、第1サブフレーム期間112に入力される信号を第2サブフレーム期間114に入力される

10

20

30

40

50

信号より大きくする（又は、小さくする）ことが挙げられる。このように、いわゆるオーバードライブの如き駆動をさせて、動作速度をさらに向上させても良い。この場合、オーバードライブのみを用いて駆動する場合と比較して、動画性能を含めた画質の向上を図ることができる。なお、1フレーム期間110を3個以上のサブフレーム期間に分割する場合には、それに伴い信号入力の回数も増加することはいうまでもない。

#### 【0039】

第1サブフレーム期間112と第2サブフレーム期間114において同じ信号をそれぞれ入力した後、第3サブフレーム期間116に信号を入力する。ここで画素電極に入力される信号は、目標とする液晶の応答量（又は階調）に対して不足している（又は過剰の）応答量（又は階調）を補う信号であることが好ましい。例えば、第1サブフレーム期間112においては液晶分子の応答速度の関係上、常に一定の応答量不足（過剰）が存在するため、所望の階調を表示できない。この応答量不足（過剰）を補うような信号を第3サブフレーム期間116に入力することで、1フレーム期間110における平均の階調120（平均応答量とも呼ぶ）を、所望の値に近づけることができる。10

#### 【0040】

なお、本実施の形態においては、電圧を正の方向に加えて応答量の不足分を補う場合、つまり補償電圧が正の場合について示しているが、本発明はこれに限られるものではない。応答量が小さくなる方向に変化する場合には、補償電圧を負にすることで対応できる。

#### 【0041】

図1（B）に、不足分の応答量の算出方法及び第3サブフレーム期間116に入力する信号の算出方法の一例を模式的に示す。ここでは簡単のため、図1（A）における1画素への書き込み期間中に印加される電圧（実線）は省略した。図1（B）に示されるように、第1サブフレーム期間112における不足分の応答量は概ね三角形100の形状で表される。ここで三角形100の面積は、（目標とする応答量と初期応答量との差）×（1サブフレーム期間の長さ）×1/2であるから、これが不足分の応答量に対応する。不足分の応答量を算出した後、当該不足分の応答量を補うための電圧を求める。電圧と応答量との関係は、液晶表示装置の様々なパラメータによって変化するから、あらかじめ調査しておくことが望ましい。第3サブフレーム期間116において画素電極に入力される信号電圧は、（第1サブフレーム期間112又は第2サブフレーム期間114における信号電圧）+（不足分の応答量に対応する電圧）である。20

#### 【0042】

なお、上記の算出方法はあくまでも一例に過ぎず、本発明はこれに限定されるものではない。本実施の形態においては、不足分の応答量を三角形に近似して計算したが、近似を用いずに時間と応答量の関数から積分によって求めて良い。もちろん、長方形や台形などの形状に近似して求めて良い。

#### 【0043】

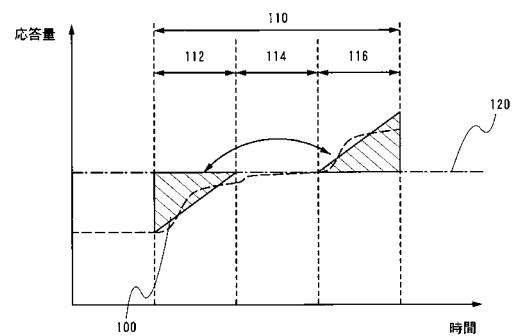

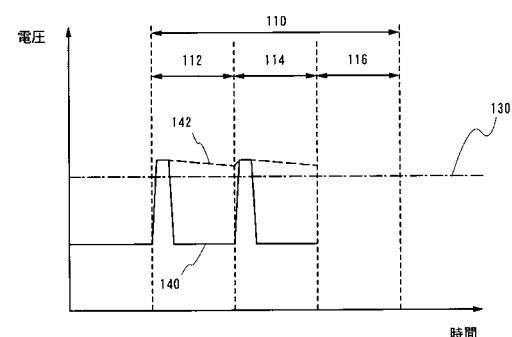

次に、1フレーム期間を複数のサブフレーム期間に分割しない駆動方法を用いた場合の液晶の応答量と、本発明の如く1フレーム期間を複数のサブフレーム期間に分割する駆動方法を用いて同じ信号を複数回入力した場合の液晶の応答量を図2に示して比較する。なお、簡単のため、図2においては第1サブフレーム期間及び第2サブフレーム期間（及びそれに対応する期間）のみについて比較するものとする。40

#### 【0044】

図2（A）は、1フレーム期間110を複数のサブフレーム期間に分割しない、従来の駆動方法を用いた場合の液晶（TN液晶）の応答量（破線）を示すものである。なお、図2中において、実線は1画素への書き込み期間中に印加される電圧を表している。図2（A）において、液晶の応答量は時間とともに増大してゆくが、第2サブフレーム期間に対応する期間の終盤に差し掛かっても所望の輝度には到達していない。つまり、目的の輝度130（目的の応答量とも呼ぶ）に到達するまでに1サブフレームより長い時間が掛かっていることがわかる。

#### 【0045】

50

図2(B)は、1フレーム期間110を複数のサブフレーム期間に分割する駆動方法を用いて、同じ信号を2回入力した場合の液晶の応答量(破線)を示すものである。図2(B)から、第2サブフレーム期間114において再び信号が入力されると、それまでとは異なる速さで応答量が変化することが分かる。つまり、図2(B)の場合、図2(A)の場合と比較してより早く目的の応答量130に近づくことになる。

#### 【0046】

このように同じ信号を複数回入力することにより、それまでとは異なる速さで応答量が変化するという現象の詳細は不明であるが、その要因のひとつとして、液晶表示装置の駆動方式に起因するものが挙げられる。ある画像を表示する場合において、画素のトランジスタが導通状態となると、画素電極に信号が入力され、液晶に電圧が印加される。その後、画素のトランジスタが非導通状態となることで当該画素の容量素子は入力信号を保持し続け、ある画像を表示し続けることが可能となる。しかしながら、実際には、非導通状態が選択されている場合においても画素のトランジスタには僅かに電流が流れ続ける。したがって、当初の電圧を1フレーム期間保持し続けることは困難であり、結果として液晶に印加される電圧は時間と共に低下することになる。

10

#### 【0047】

また、保持容量が小さい場合にはこの傾向が顕著になる。液晶表示装置の構造上、画素の開口率を一定以上に保つためには、保持容量を一定以上に大きくすることは困難である。つまり、保持容量が保持可能な電荷量には一定の制限が出てくる。保持可能な電荷量が小さい場合には、僅かなリーク電流の発生により、液晶に印加される電圧は大幅に減少してしまうことになる。

20

#### 【0048】

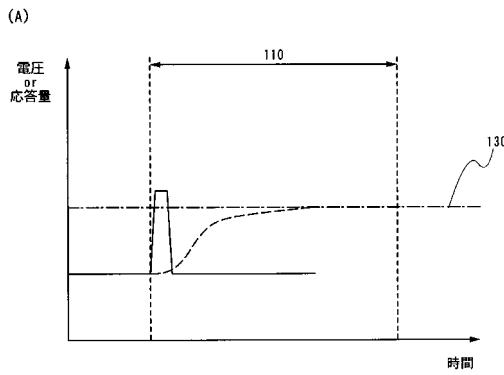

これを図示すると、図3(A)のようになる。図3(A)はある画素への入力信号と、当該画素の容量素子が保持する電圧との関係を示すものである。ここで、横軸は時間を示しており、縦軸は電圧を示している。実線は入力信号の電圧140、破線は容量素子が保持する電圧142を示す。なお、簡単のため、図3においては第1サブフレーム期間112及び第2サブフレーム期間114(及びそれに対応する期間)のみについて示している。図3(A)に示すように、信号の入力が終了すると、時間の経過と共に容量素子に蓄積された電荷量は減少してゆき、当初の電圧を保つことが出来なくなる。

#### 【0049】

30

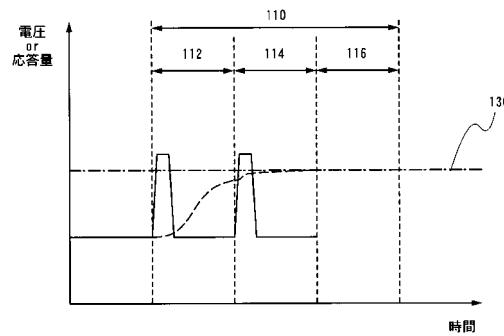

これに対して、同じ信号を複数回入力する場合の、画素への入力信号と当該画素の容量素子が保持する電圧との関係を図3(B)に示す。図3(A)と同様に、実線は入力信号の電圧140、破線は容量素子が保持する電圧142を示している。まず、第1サブフレーム期間112において画素電極に信号が入力されると、図3(A)の場合と同様に、容量素子に電荷が蓄積される。この場合においても、信号の入力が終了すると、時間の経過と共に容量素子に蓄積された電荷量は減少してゆく。次に、第2サブフレーム期間114において、画素電極には再度同じ信号が入力される。これにより、液晶に印加される電圧を引き上げることができる。即ち、目的の応答量(輝度)への到達に要する時間を短縮することができる。

#### 【0050】

40

また、1フレーム期間における映像を第1サブフレーム期間112において入力し、複数回同じデータの書き込みを繰り返す(リフレッシュする)ことにより、60Hz駆動の場合と比較して、少なくとも1/3以下の期間で一画面の映像を確定させることができる。60Hz駆動の場合には、1/60秒で画面が書き換えられるのに対して、180Hz駆動の場合には、1/180秒で画面が書き換えられるためである。つまり、画面上に異なる画像(例えば、ある1フレームにおける画像と、次の1フレームにおける画像)が混在して表示される期間を短縮することができる。これにより、画像を素早く書き込み、素早く確定させることができるために、一画像内での輝度ばらつきが極めて小さくなり、動画ぼけが改善され、画質を向上させることができる。

#### 【0051】

50

図3(A)と図3(B)の比較から分かるように、単純に複数回の信号入力という動作のみで、いわゆる応答速度の向上を実現できる。なお、ここでは複数回の信号入力による応答速度向上が発生する原因として、保持容量やトランジスタのリーク電流の問題を挙げたが、そのほかにも複数の要因が存在している可能性はある。例えば、液晶リークの問題等が考えられる。

#### 【0052】

次に、後半のサブフレーム(本実施の形態においては第3サブフレーム116)において補償電圧を加える場合の効果を簡単に説明する。

#### 【0053】

後半のサブフレームにおいては、液晶の応答量は所望の表示階調に到達しているとみなすことができる。すなわち、階調を補償するために必要な液晶の応答量はごく僅かで済む。液晶の応答量がごく僅かであれば、応答に必要な時間もまたごく僅かで済むことになる。つまり、応答速度の向上が実現されるのである。

#### 【0054】

本実施の形態に示すように、1フレーム期間をn個(n:整数, n>3)のサブフレーム期間に分割して、第1乃至第n-1サブフレーム期間においては信号電圧を印加し、第nサブフレーム期間においては、信号電圧に補償電圧を加えた電圧を印加することにより、応答速度の向上及び正確な階調表示を実現できる。また、簡単な演算によって補償電圧を決定することができるため、オーバードライブ駆動と比較して簡易な構成で画質の向上を図ることができるという利点を有する。

10

20

#### 【0055】

また、本実施の形態の駆動方法を用いることにより、保持容量を小さくすることも可能である。つまり、1フレーム期間に複数回の信号書き込みを行うことにより、リーク電流による電圧低下の影響を受けにくくなるため、従来必要とされていた保持容量より小さな容量を用いることが可能となる。保持容量を小さくすることにより、開口率及び動画性能が高い液晶表示装置を提供することが可能である。特に、開口と重なる容量を必要としない程度にまで書き込み回数を増加させる(つまり、多くのサブフレーム期間に分割する)ことで、最大の開口率を有し且つ動画性能に優れた液晶表示装置を提供することも可能である。また、保持容量を十分に小さくすることが可能な条件では、保持容量用の容量配線を有さない構成(例えば、図10における容量配線906を有さない構成)とすることもできる。

30

#### 【0056】

なお、本実施の形態においては、補償電圧を加えるサブフレーム期間を第nサブフレーム期間としたが、本発明はこれに限られない。液晶の応答量が所望の表示階調に到達しているとみなせるサブフレーム期間であれば、本発明の効果を得ることができる。例えば、n個(n:整数, n>3)のサブフレーム期間に分割した場合には、第mサブフレーム期間(m:整数, n/2 < m < n)に補償電圧を加える構成としても良い。

#### 【0057】

##### (実施の形態2)

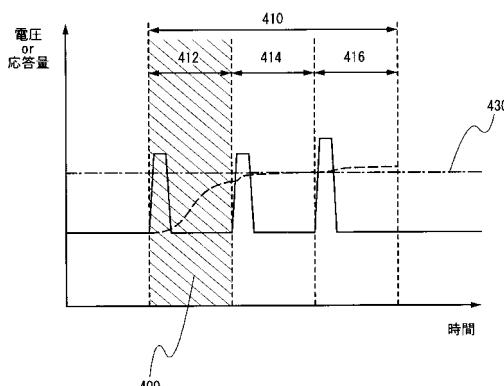

本実施の形態では、実施の形態1にて説明した方法とは異なる駆動方法について図4を用いて説明する。

40

#### 【0058】

はじめに、1フレーム期間をn個のサブフレーム期間(n:整数, n>3)に分割する(図4参照)。本実施の形態においては簡単のため、1フレーム期間410を3個のサブフレーム期間(第1サブフレーム期間412、第2サブフレーム期間414、第3サブフレーム期間416)に分割した場合について説明するが、本発明はこれに限られるものではない。なお、液晶表示装置では一般に60Hzで画面の書き換えが行われるから、1フレーム期間は1/60秒となる。本実施の形態では1フレーム期間をさらに3個のサブフレーム期間に分割するから、180Hzでの駆動となる。すなわち、1サブフレーム期間は1/180秒である。いうまでもなく、1フレーム期間をn個のサブフレーム期間に分

50

割する場合には、 $60 \times n \text{ Hz}$ での駆動となり、1サブフレーム期間は $1 / (60 \times n)$ 秒となる。

#### 【0059】

3個のサブフレーム期間に対応させて、外部からの映像信号を画素電極に入力する。まず、第1サブフレーム期間412と第2サブフレーム期間414において同じ信号（信号電圧）をそれぞれ入力する。なお、第1サブフレーム期間412及び第2サブフレーム期間414において入力される信号（信号電圧）として、外部からの映像信号をそのまま用いても良いし、映像信号に何らかの補正を行った信号、例えば、補正を行った信号などを用いても良い。信号電圧は所望の階調に相当する電圧である。

#### 【0060】

複数回の信号入力により得られる効果等は実施の形態1と同様であるため、ここでは省略する。

#### 【0061】

第1サブフレーム期間412と第2サブフレーム期間414において同じ信号をそれぞれ入力した後、第3サブフレーム期間416の信号を入力する。ここで画素電極に入力される信号は、目標とする液晶の応答量430（又は階調）に対して不足している（又は過剰の）応答量（又は階調）を補う信号であることが好ましい。実施の形態1においては、第1サブフレーム期間における応答量の不足分（過剰分）を補うように第3サブフレーム期間416に信号を入力する例を示したが、本実施の形態においては第2サブフレーム期間414における応答量の不足分（過剰分）を補うように第3サブフレーム期間416に信号を入力する。

#### 【0062】

なお、本実施の形態においては、電圧を正の方向に加えて応答量の不足分を補う場合、つまり補償電圧が正の場合について示しているが、本発明はこれに限られるものではない。応答量が小さくなる方向に変化する場合には、補償電圧を負にすることで対応できる。

#### 【0063】

ここで、第1サブフレーム期間412における応答量の不足分と、第2サブフレーム期間414における応答量の不足分とを比較した場合、第1サブフレーム期間412における応答量の不足分のほうが大きいため、実施の形態1で用いる駆動方法と比較して、表示される階調の精度が低下するという問題が発生する。

#### 【0064】

そこで、本実施の形態では、第1サブフレーム期間412をバックライト消灯期間400とする。つまり、応答の過渡状態にある第1サブフレーム期間412を黒表示とし、第2サブフレーム期間414及び第3サブフレーム期間416のみを用いて表示を行うこととする。このように、応答の過渡状態にある第1サブフレーム期間412を表示に関与させないことで、表示される階調の精度を大きく向上させることができる。また、各フレーム期間中に黒画面を挿入することにより、ブラウン管の如きインパルス駆動を実現することができるため、より一層の動画性能の向上が可能となる。

#### 【0065】

また、第2サブフレーム期間414における応答量の不足分のみを補うように信号を入力するため、第2サブフレーム期間414において表示される階調と第3サブフレーム期間416において表示される階調との差が小さく、ちらつきの原因を低減することができる。

#### 【0066】

不足分の応答量の算出方法等については実施の形態1と同様であるため、ここでは省略する。なお、第2サブフレーム期間414における応答量の不足分は比較的小さいものであるから、近似方法の違いによる影響も小さく、より簡易な方法を用いて算出することができる。

#### 【0067】

本実施の形態に示すように、1フレーム期間をn個（n：整数，n ≥ 3）のサブフレー

10

20

30

40

50

ム期間に分割して、第1乃至第n-1サブフレーム期間においては同じ信号電圧を印加し、第nサブフレーム期間においては、信号電圧に補償電圧を加えた電圧を印加することにより、応答速度の向上及び正確な階調表示を実現できる。また、簡単な演算によって補償電圧を決定することができるため、オーバードライブ駆動と比較して簡易であるという利点を有する。もちろん、オーバードライブの如き駆動をさせて、動作速度をさらに向上させても構わない。この場合、第1サブフレーム期間においては、上記信号電圧に代えてオーバードライブ電圧を印加することが好ましい。

#### 【0068】

また、本実施の形態の駆動方法を用いることにより、保持容量を小さくすることも可能である。つまり、1フレーム期間に複数回の信号書き込みを行ことにより、リーク電流による電圧低下の影響を受けにくくなるため、従来必要とされていた保持容量より小さなものを用いることが可能となる。保持容量を小さくすることにより、開口率及び動画性能が高い液晶表示装置を提供することが可能である。特に、開口と重なる容量を必要としない程度にまで書き込み回数を増加させる(つまり、多くのサブフレーム期間に分割する)ことで、最大の開口率を有し且つ動画性能に優れた液晶表示装置を提供することも可能である。保持容量を十分に小さくすることが可能な条件では、保持容量用の容量配線を有さない構成(例えば、図10における容量配線906を有さない構成)とすることもできる。

10

#### 【0069】

また、本実施の形態の駆動方法では、応答の過渡状態にある第1サブフレーム期間412を表示に関与させないことで、表示される階調の精度を大きく向上させることができる。また、各フレーム期間中に黒画面を挿入することにより、ブラウン管の如きインパルス駆動を実現することができるため、より一層の動画性能の向上が可能となる。さらに、開口と重なる容量を必要としない程度にまで書き込み回数を増加させる(つまり、多くのサブフレーム期間に分割する)ことで、最大の開口率を有し且つ動画性能に優れた液晶表示装置を提供することも可能である。また、第2サブフレーム期間414における応答量の不足分のみを補うように信号を入力するため、第2サブフレーム期間414において表示される階調と第3サブフレーム期間416において表示される階調との差が小さく、ちらつきの原因を低減することもできる。

20

#### 【0070】

なお、本実施の形態においては、第2サブフレーム期間414の応答量の不足分を第3サブフレーム期間416で補う構成としているが、本発明の構成はこれに限られるものではない。例えば、1フレーム期間をn個(n:整数, n>3)のサブフレーム期間に分割した場合には、第1サブフレーム期間以外のサブフレーム期間についての応答量の不足分(例えば、2サブフレーム期間及び第3サブフレーム期間についての応答量の不足分)を補う構成とすることもできる。液晶の応答量の不足分は前半のサブフレーム期間において特に大きいものであるから、バックライトを消灯させるサブフレーム期間の直後のサブフレーム期間についての応答量の不足分を補う構成とすることが好ましい。また、補償電圧を加えるサブフレーム期間についても適宜選択することができる。

30

#### 【0071】

本実施の形態は、実施の形態1と組み合わせて用いることができる。

40

#### 【0072】

##### (実施の形態3)

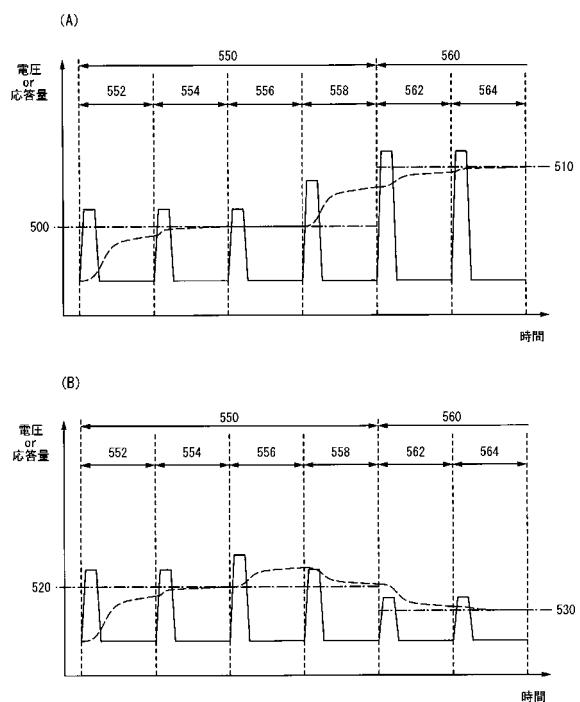

本実施の形態では、本発明の他の駆動方法について図5を用いて説明する。

#### 【0073】

はじめに、1フレーム期間をn個のサブフレーム期間(n:整数, n>3)に分割する(図4参照)。本実施の形態においては簡単のため、1フレーム期間を4個のサブフレーム期間に分割した場合について説明するが、本発明はこれに限られるものではない。もちろん、1フレーム期間を3個のサブフレーム期間に分割した場合にも適用できる。なお、液晶表示装置では一般に60Hzで画面の書き換えが行われるから、1フレーム期間は1/60秒となる。本実施の形態では1フレーム期間をさらに4個のサブフレーム期間に分

50

割するから、 $240\text{ Hz}$ での駆動となる。すなわち、1サブフレーム期間は $1/240$ 秒である。いうまでもなく、1フレーム期間を $n$ 個のサブフレーム期間に分割する場合には、 $60 \times n\text{ Hz}$ での駆動となり、1サブフレーム期間は $1/(60 \times n)$ 秒となる。

#### 【0074】

4個のサブフレーム期間に対応させて、外部からの映像信号を画素電極に入力する。まず、第1サブフレーム期間と第2サブフレーム期間において同じ信号（信号電圧）をそれぞれ入力する。なお、第1サブフレーム期間及び第2サブフレーム期間において入力される信号（信号電圧）として、外部からの映像信号をそのまま用いても良いし、映像信号に何らかの補正を行った信号、例えば、補正を行った信号などを用いても良い。信号電圧は所望の階調に相当する電圧である。

10

#### 【0075】

複数回の信号入力により得られる効果等は実施の形態1と同様であるため、ここでは省略する。

#### 【0076】

第1サブフレーム期間と第2サブフレーム期間において同じ信号をそれぞれ入力した後、第3サブフレーム期間及び第4サブフレーム期間の信号を入力する。本実施の形態においては、第3サブフレーム期間及び第4サブフレーム期間の一方には信号電圧を印加し、他方には信号電圧に補償電圧を加えた電圧を印加する。第3サブフレーム期間及び第4サブフレーム期間のどちらに信号電圧を印加し、どちらに信号電圧に補償電圧を加えた電圧を印加するかは、補償電圧を加える対象とする1フレーム期間と次の1フレーム期間との信号電圧の関係によって決定することが好ましい。

20

#### 【0077】

例えば、次の1フレーム期間における信号電圧が、補償電圧の印加対象となっている1フレーム期間の信号電圧より大きい場合には、第4サブフレーム期間において信号電圧に補償電圧を加えた電圧を印加し、次の1フレーム期間における信号電圧が、補償電圧の印加対象となっている1フレーム期間の信号電圧より小さい場合には、第3サブフレーム期間において信号電圧に補償電圧を加えた電圧を印加するように駆動させても良い。

#### 【0078】

上記のような駆動方法を用いる場合の印加電圧と応答量との関係を図5に示す。図5(A)は、第2フレーム期間560(第1サブフレーム期間562、第2サブフレーム期間564、第3サブフレーム期間以降は省略)における信号電圧が、第1フレーム期間550(第1サブフレーム期間552、第2サブフレーム期間554、第3サブフレーム期間556、第4サブフレーム期間558)の信号電圧より大きい場合を示すものである。このように、応答量がより大きい方向へ変化する場合には、第4サブフレーム期間558において信号電圧に補償電圧を加えた電圧を印加することが好ましい。このような駆動方法とすることで、第1フレーム期間550と第2フレーム期間560の表示が切り替わる際に、液晶の応答量の変化を小さくすることができるため、液晶の応答遅れに起因する画質の低下を防止できる。

30

#### 【0079】

同様に図5(B)は、第2フレーム期間560における信号電圧が、第1フレーム期間550の信号電圧より小さい場合を示すものである。このように、応答量がより小さい方向へ変化する場合には、第3サブフレーム期間556において信号電圧に補償電圧を加えた電圧を印加することが好ましい。このような駆動方法とすることで、第1フレーム期間550と第2フレーム期間560の表示が切り替わる際に、液晶の応答量の変化を小さくすることができるため、液晶の応答遅れに起因する画質の低下を防止できる。

40

#### 【0080】

上記の駆動方法は、補償電圧の印加対象となっている1フレーム期間と次の1フレーム期間の信号電圧の関係によって、信号電圧に補償電圧を加えた電圧を印加するサブフレーム期間を決定するものであるが、本発明はこれに限られない。例えば、補償電圧の印加対象となっている1フレーム期間と次の1フレーム期間の信号電圧及び補償電圧の関係によ

50

って決定しても良い。また、補償電圧の印加対象となっている1フレーム期間と次の1フレーム期間の目標応答量の関係によって決定しても良い。なお、図5(A)は、第2フレーム期間560における目標応答量510が第1フレーム期間550における目標応答量500より大きくなっている場合に該当し、図5(B)は、第2フレーム期間560における目標応答量530が第1フレーム期間550における目標応答量520より小さくなっている場合に該当する。

#### 【0081】

なお、不足分の応答量の算出方法等については実施の形態1と同様であるため、ここでは省略する。

#### 【0082】

なお、本実施の形態においては、電圧を正の方向に印加して応答量の不足分を補う場合、つまり補償電圧が正の場合について示しているが、本発明はこれに限られるものではない。応答量が小さくなる方向に変化する場合には、補償電圧を負にして対応できる。

10

#### 【0083】

本実施の形態に示すように、1フレーム期間をn個(n:整数, n>3)のサブフレーム期間に分割して、次の1フレーム期間における信号電圧が対象となる1フレーム期間の信号電圧より大きい(または信号電圧以上の)場合には第nサブフレーム期間を選択し、次の1フレーム期間における信号電圧が対象となる1フレーム期間の信号電圧以下の(または信号電圧より小さい)場合には第n-1サブフレーム期間を選択し、選択されたサブフレーム期間において、信号電圧に補償電圧を加えた電圧を画素電極に印加し、選択されたサブフレーム期間以外のサブフレーム期間において、信号電圧と同一の電圧を画素電極に印加することにより、応答速度の向上及び正確な階調表示を実現できる。また、簡単な演算によって補償電圧を決定することができるため、オーバードライブ駆動と比較して簡易であるという利点を有する。もちろん、オーバードライブの如き駆動をさせて、動作速度をさらに向上させても構わない。この場合、第1サブフレーム期間においては、上記信号電圧に代えてオーバードライブ電圧を印加することが好ましい。

20

#### 【0084】

また、本実施の形態の駆動方法を用いることにより、保持容量を小さくすることも可能である。つまり、1フレーム期間に複数回の信号書き込みを行ことにより、リーケ電流による電圧低下の影響を受けにくくなるため、従来必要とされていた保持容量より小さなものを用いることが可能となる。保持容量を小さくすることにより、開口率及び動画性能が高い液晶表示装置を提供することができる。特に、開口と重なる容量を必要としない程度にまで書き込み回数を増加させる(つまり、多くのサブフレーム期間に分割する)ことで、最大の開口率を有し且つ動画性能に優れた液晶表示装置を提供することも可能である。保持容量を十分に小さくすることが可能な条件では、保持容量用の容量配線を有さない構成とすることもできる。

30

#### 【0085】

また、本実施の形態の駆動方法では、次の1フレーム期間における液晶の応答量(目標値)に応じて補償電圧を印加するサブフレームを選択するため、次の1フレーム期間における応答時間を短縮することができる。したがって、応答速度をより一層向上させることができる。なお、選択されるサブフレーム期間が異なる場合には、補償電圧の値も異なることに留意が必要である。例えば、図5に示す場合においては、図5(B)の場合と比較して、図5(A)の場合に印加される補償電圧の値が小さい。これは、図5(A)の場合では第4サブフレーム期間のみで応答量の不足分を補う必要があるのに対して、図5(B)の場合には第3サブフレーム期間及び第4サブフレーム期間を用いて応答量の不足分を補えば良いためである。

40

#### 【0086】

なお、本実施の形態の駆動方法においても、実施の形態2に示したバックライトを消灯する構成を採用することができる。応答の過渡状態にある第1サブフレーム期間を表示に

50

関与させないことで、表示される階調の精度を大きく向上させることができる。また、各フレーム期間中に黒画面を挿入することにより、ブラウン管の如きインパルス駆動を実現することができるため、より一層の動画性能の向上が可能となる。さらに、開口と重なる容量を必要としない程度にまで書き込み回数を増加させる（つまり、多くのサブフレーム期間に分割する）ことで、最大の開口率を有し且つ動画性能に優れた液晶表示装置を提供することも可能である。また、第2サブフレーム期間における応答量の不足分のみを補うように信号を入力するため、第2サブフレーム期間において表示される階調と第3サブフレーム期間において表示される階調との差が小さく、ちらつきの原因を低減することもできる。

#### 【0087】

10

本実施の形態は、実施の形態1及び実施の形態2と適宜組み合わせて用いることができる。

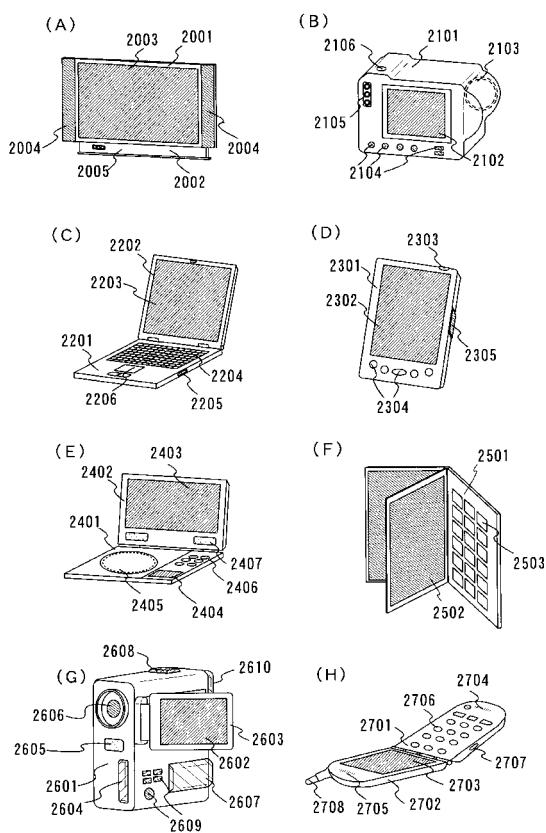

#### 【0088】

##### （実施の形態4）

本実施の形態においては、実施の形態3において説明された補償電圧の印加パターンについて、いくつかの場合に分けて説明する。具体的には、対象とする1フレーム期間A（補償電圧を印加する対象となる1フレーム期間）と、直前の1フレーム期間B、及び直後の1フレーム期間Cの信号電圧の大小関係によって、補償電圧を印加するサブフレーム期間を選択する様子について説明する。

#### 【0089】

20

図24は、対象とする1フレーム期間Aと、直前の1フレーム期間B、及び直後の1フレーム期間Cの信号電圧の大小関係をいくつかのパターンに分けて示したものである。ここでは簡単のため、高電圧（以下、Hiと記載する。）と低電圧（以下、Loと記載する。）の2値によって表される信号電圧について示しているが、多値の場合であっても同様に扱うことができる。

#### 【0090】

図24（A）は各フレーム期間における信号電圧がLo、Lo、Loと変化しない場合について示している。図24（B）には各フレーム期間における信号電圧がLo、Lo、Hiの場合を、図24（C）にはLo、Hi、Loの場合を、図24（D）にはHi、Lo、Loの場合を、図24（E）にはLo、Hi、Hiの場合を、図24（F）にはHi、Lo、Hiの場合を、図24（G）にはHi、Hi、Loの場合を示す。また、図24（H）には各フレーム期間における信号電圧がHi、Hi、Hiと変化しない場合について示す。

30

#### 【0091】

図24（A）、（B）、（G）、（H）においては、対象とする1フレーム期間Aと直前の1フレーム期間Bとの信号電圧に差がない。このような場合には、対象とする1フレーム期間Aにおいて補償電圧を加える必要はない。

#### 【0092】

40

図24（C）、（E）においては、対象とする1フレーム期間Aの信号電圧が直前の1フレーム期間Bと比較して高くなっている。このような場合には液晶の立ち上がり遅れが生じるため、正の補償電圧を加えることが必要になる。

#### 【0093】

ここで、対象とする1フレーム期間Aと直後の1フレーム期間Cとの信号電圧を比較してみる。図24（C）の場合においては、直後の1フレーム期間Cの信号電圧が対象とする1フレーム期間Aと比較して低くなっている。図24（C）の場合には、補償電圧として正の電圧を加えることになるから、補償電圧を加えるサブフレーム期間としては最後のサブフレーム期間を避けることが好ましい。より具体的には、例えば、1フレーム期間をn個のサブフレーム期間に分割した場合には、第1サブフレーム期間及び第nサブフレーム期間以外のサブフレーム期間を選択して補償電圧を加えることが好ましいといえる。図24（E）のように、対象とする1フレーム期間Aと直後の1フレーム期間Cとの信号電

50

圧に差がない場合も、同様である。

**【0094】**

なお、本実施の形態においては、2値の場合を用いて説明しているため、直後の1フレーム期間Cの信号電圧が対象とする1フレーム期間Aと比較して高くなる場合については示していないが、多値の場合においてはこのような状況が存在し得る。この場合には、最後のサブフレーム期間を含むサブフレーム期間を選択して補償電圧を加えることが好ましい。1フレーム期間をn個のサブフレーム期間に分割した場合には、第nサブフレーム期間を少なくとも含むサブフレーム期間を一又は複数選択して補償電圧を加えることが好ましいといえる。

**【0095】**

図24(D)、(F)においては、対象とする1フレーム期間Aの信号電圧が直前の1フレーム期間Bと比較して低くなっている。このような場合には液晶の立ち下がり遅れが生じるため、負の補償電圧を加えることが必要になる。

**【0096】**

正の補償電圧を加える場合と同様に、対象とする1フレーム期間Aと直後の1フレーム期間Cとの信号電圧を比較してみる。図24(F)の場合においては、直後の1フレーム期間Cの信号電圧が対象とする1フレーム期間Aと比較して高くなっている。図24(F)の場合には、補償電圧として負の電圧を加えることになるから、補償電圧を加えるサブフレーム期間としては最後のサブフレーム期間を避けることが好ましい。より具体的には、例えば、1フレーム期間をn個のサブフレーム期間に分割した場合には、第1サブフレーム期間及び第nサブフレーム期間以外のサブフレーム期間を選択して補償電圧を加えることが好ましいといえる。図24(D)のように、対象とする1フレーム期間Aと直後の1フレーム期間Cとの信号電圧に差がない場合も、同様である。

**【0097】**

なお、本実施の形態においては、2値の場合を用いて説明しているため、直後の1フレーム期間Cの信号電圧が対象とする1フレーム期間Aと比較して低くなる場合については示していないが、多値の場合においてはこのような状況が存在し得る。この場合には、最後のサブフレーム期間を含むサブフレーム期間を選択して補償電圧を加えることが好ましい。1フレーム期間をn個のサブフレーム期間に分割した場合には、第nサブフレーム期間を少なくとも含むサブフレーム期間を一又は複数選択して補償電圧を加えることが好ましいといえる。

**【0098】**

まとめると、以下のようになる。

**補償電圧が正の場合**

- ・直後の1フレーム期間における信号電圧が、対象とする1フレーム期間における信号電圧より低い場合（及び、差がない場合）：最初のサブフレーム期間、及び最後のサブフレーム期間以外のサブフレーム期間を選択して補償電圧を加える。

- ・直後の1フレーム期間における信号電圧が、対象とする1フレーム期間における信号電圧より高い場合：最後のサブフレーム期間を含むサブフレーム期間を選択して補償電圧を加える。

**補償電圧が負の場合**

- ・直後の1フレーム期間における信号電圧が、対象とする1フレーム期間における信号電圧より高い場合（及び、差がない場合）：最初のサブフレーム期間、及び最後のサブフレーム期間以外のサブフレーム期間を選択して補償電圧を加える。

- ・直後の1フレーム期間における信号電圧が、対象とする1フレーム期間における信号電圧より低い場合：最後のサブフレーム期間を含むサブフレーム期間を選択して補償電圧を加える。

**【0099】**

以上において示したように、対象とする1フレーム期間の第nサブフレーム期間に印加される電圧と、対象とする1フレーム期間の次の1フレーム期間の第1サブフレーム期間

10

20

30

40

50

に印加される電圧との差が小さくなるように、サブフレーム期間を選択して補償電圧を加えることで、液晶の応答遅れの影響を大きく低減させることができる。

#### 【0100】

本実施の形態は実施の形態1乃至3と適宜組み合わせて用いることができる。

#### 【0101】

##### (実施の形態5)

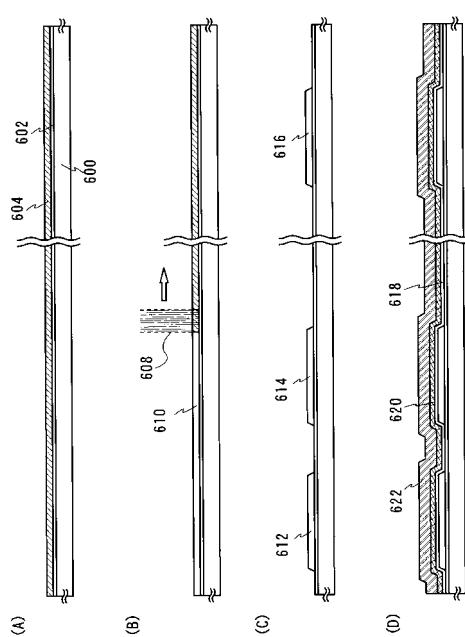

本発明の液晶表示装置に用いることができるアクティブマトリクス基板の作製方法の一例を図6乃至図8を用いて説明する。なお、本実施の形態では結晶性半導体膜を用いた場合について説明するが、非晶質半導体膜、単結晶半導体膜を用いてもよい。

#### 【0102】

まず図6(A)に示すように、基板600上に下地膜602を成膜する。基板600には、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、ステンレス基板等を用いることができる。また、PET、PES、PENに代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。

10

#### 【0103】

下地膜602は基板600中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、半導体膜中に拡散し、半導体素子の特性に悪影響を与えることを防止するために設ける。よってアルカリ金属やアルカリ土類金属の半導体膜への拡散を抑制することができる窒化珪素や、窒素を含む酸化珪素といった絶縁性材料を用いて形成する。本実施の形態では、プラズマCVD法を用いて窒素を含む酸化珪素膜を10nm～400nm(好ましくは50nm～300nm)の膜厚になるように形成する。

20

#### 【0104】

次に下地膜602上に半導体膜604を形成する。半導体膜604の膜厚は25nm～100nm(好ましくは30nm～60nm)とする。なお半導体膜604は、非晶質半導体であっても良いし、多結晶半導体であっても良い。また半導体としては、シリコン(Si)だけではなくシリコンゲルマニウム(SiGe)等を用いることもできる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01～4.5atm%程度であることが好ましい。

30

#### 【0105】

次に図6(B)に示すように、半導体膜604に線状レーザー608を照射し、結晶化を行なう。本実施の形態のようなレーザー結晶化を行なう場合には、レーザーに対する半導体膜604の耐性を高めるために、500、1時間程度の加熱処理工程をレーザー結晶化の工程の前に加えてもよい。

#### 【0106】

レーザー結晶化の工程には、例えば、連続発振のレーザー(CWレーザー)や、擬似的なCWレーザー(発振周波数が10MHz以上、好ましくは80MHz以上のパルス発振レーザー)等を用いることができる。

#### 【0107】

具体的には、連続発振のレーザーとして、Arレーザー、Krレーザー、CO<sub>2</sub>レーザー、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、ルビーレーザー、アレキサンンドライトレーザー、Ti:サファイアレーザー、ヘリウムカドミウムレーザー等が挙げられる。

40

#### 【0108】

また擬似的なCWレーザーとして、Arレーザー、Krレーザー、エキシマレーザー、CO<sub>2</sub>レーザー、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、ルビーレーザー、アレキサンンドライトレーザー、Ti:サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのようなパルス発振レーザー等が挙げられる。

#### 【0109】

50

このようなパルス発振レーザーは、発振周波数を増加させると、連続発振レーザーと同等の効果を示すようになる。

#### 【0110】

例えれば連続発振が可能な固体レーザーを用いる場合、基本波の第2高調波乃至第4高調波を照射することで、大粒径の結晶を得ることができる。代表的には、YAGレーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を用いることができる。パワー密度は0.01～100MW/cm<sup>2</sup>程度（好ましくは0.1～10MW/cm<sup>2</sup>）とすれば良い。

#### 【0111】

上述の如き半導体膜604へのレーザー光の照射により、結晶性がより高められた結晶性半導体膜610が形成される。10

#### 【0112】

次に、図6(C)に示すように結晶性半導体膜610を選択的にエッチングすることで、島状半導体膜612、614、616を形成する。

#### 【0113】

次に、島状半導体膜612、614、616のそれぞれに、しきい値制御のための不純物元素を導入する。本実施の形態においてはジボラン(B<sub>2</sub>H<sub>6</sub>)をドープすることによってボロン(B)を導入する。

#### 【0114】

次に、島状半導体膜612、614、616を覆うように絶縁膜618を形成する。絶縁膜618としては、例えは酸化珪素、窒化珪素、または窒素を含んだ酸化珪素(SiO<sub>x</sub>N<sub>y</sub>:x>y>0)等を用いることができる。また、成膜方法としては、プラズマCVD法や、スパッタ法などを用いることができる。20

#### 【0115】

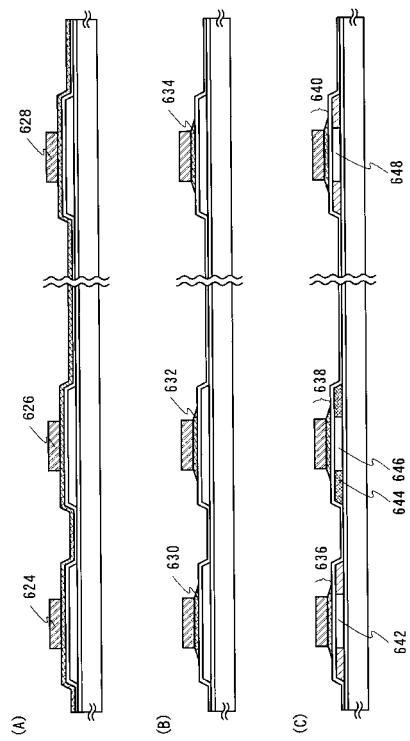

次に、絶縁膜618上に第1の導電膜620、第2の導電膜622を成膜した後、当該導電膜620、622を選択的にエッチングすることで、ゲート電極636、638、640を形成する(図6(D)、図7)。

#### 【0116】

第1の導電膜620、第2の622としては、アルミニウム(A1)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、ネオジム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt)、金(Au)、銀(Ag)、銅(Cu)、マグネシウム(Mg)、スカンジウム(Sc)、コバルト(Co)、亜鉛(Zn)、ニオブ(Nb)、シリコン(Si)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In)、錫(Sn)から選択された一つ又は複数の元素、または、前記元素を成分として含有する化合物や合金材料(例えは、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、アルミネオジム(A1-Nd)、マグネシウム銀(Mg-Ag)など)、もしくは、これらの化合物を組み合わせた物質などを用いることができる。その他にも、シリサイド(例えは、アルミシリコン、モリブデンシリコン、ニッケルシリサイド)や、窒素を含有する化合物(例えは、窒化チタン、窒化タンタル、窒化モリブデン)、リン(P)等の不純物元素をドーピングしたシリコン(Si)等を用いてよい。3040。なお、本実施の形態においては、第1の導電膜620、第2の導電膜622の二層構造としたが、単層でも良いし、三層以上の積層構造であっても良い。

#### 【0117】

本実施の形態では、ゲート電極636、638、640は以下のようにして形成される。まず、第1の導電膜620として、例えは窒化タンタル膜を10～50nm、代表的には30nmの膜厚で形成する。そして、第1の導電膜620上に第2の導電膜622として、例えはタングステン膜を200～400nm、代表的には370nmの膜厚で形成し、第1の導電膜620及び第2の導電膜622の積層膜を形成する(図6(D))。

#### 【0118】

次に、第2の導電膜622を異方性エッティングによりパターニングし、上層ゲート電極624、626、628を形成する(図7(A))。次いで、第1の導電膜620を等方性エッティングによりパターニングし、下層ゲート電極630、632、634を形成する(図7(B))。以上の工程によりゲート電極636、638、640が形成される。

#### 【0119】

ゲート電極636、638、640は、ゲート配線の一部として形成してもよいし、別に形成したゲート配線にゲート電極636、638、640を接続する構成としてもよい。

#### 【0120】

そして、ゲート電極636、638、640や、選択的に形成したレジスト等をマスクとして用い、島状半導体膜612、614、616のそれぞれに導電性(n型またはp型の導電性)を付与する不純物を添加して、ソース領域、ドレイン領域、低濃度不純物領域等を形成する。

#### 【0121】

まず、フォスフィン( $\text{PH}_3$ )を用いて、リン(P)を島状半導体膜612、616に導入する。導入の条件としては、加速電圧を60～120kV、ドーズ量を $1 \times 10^{13}$ ～ $1 \times 10^{15}$ atoms·cm<sup>-2</sup>とすることが好ましい。この不純物導入によって、後のnチャネル型TFT678及び682のチャネル形成領域642及び648が形成される(図7(C))。

#### 【0122】

また、ジボラン( $\text{B}_2\text{H}_6$ )を用いて島状半導体膜614にボロン(B)を導入する。導入の条件としては、印加電圧60～100kV、ドーズ量 $1 \times 10^{13}$ ～ $5 \times 10^{15}$ atoms·cm<sup>-2</sup>とすることが好ましい。これにより、後のpチャネル型TFT680のソース領域またはドレイン領域644、及びチャネル形成領域646が形成される(図7(C))。

#### 【0123】

次に、絶縁膜618を選択的にエッティングしてゲート絶縁膜650、652、654を形成する。

#### 【0124】

ゲート絶縁膜650、652、654を形成した後、nチャネル型TFT678及び682となる島状半導体膜中に、フォスフィン( $\text{PH}_3$ )を用いて、印加電圧40～80kV、ドーズ量 $1.0 \times 10^{15}$ ～ $2.5 \times 10^{16}$ atoms·cm<sup>-2</sup>でリン(P)を導入する。これによりnチャネル型TFTの低濃度不純物領域658、662、及びソース領域またはドレイン領域656、660が形成される(図8(A))。

#### 【0125】

本実施の形態においては、ソース領域またはドレイン領域656、660のそれぞれに $1 \times 10^{19}$ ～ $5 \times 10^{21}$ atoms·cm<sup>-3</sup>の濃度でリン(P)が含まれる。また、低濃度不純物領域658、662のそれぞれに $1 \times 10^{18}$ ～ $5 \times 10^{19}$ atoms·cm<sup>-3</sup>の濃度でリン(P)が含まれる。さらに、ソース領域またはドレイン領域644には、 $1 \times 10^{19}$ ～ $5 \times 10^{21}$ atoms·cm<sup>-3</sup>の濃度でボロン(B)が含まれる。

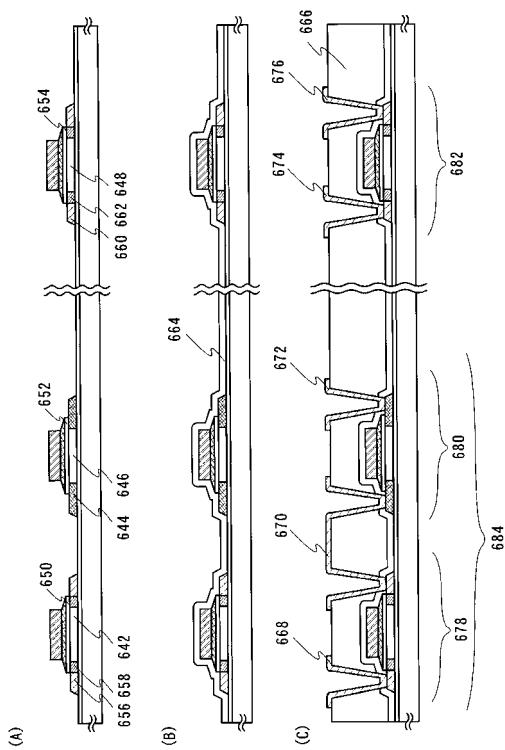

#### 【0126】

次に、島状半導体膜612、614、616、ゲート電極636、638、640を覆うように、第1層間絶縁膜664を形成する(図8(B))。

#### 【0127】

第1層間絶縁膜664としては、プラズマCVD法またはスパッタ法を用いて、シリコンを含む絶縁膜、例えば酸化珪素膜、窒化珪素膜、窒素を含む酸化珪素膜( $\text{SiO}_x\text{N}_y$ : $x > y > 0$ )などを単層もしくは積層して形成することが好ましい。勿論、第1層間絶縁膜664の作製方法及び材料は上記に限定されるものではない。例えば、他の絶縁膜を単層または積層構造として用いても良い。

10

20

30

40

50

## 【0128】

次に、第1層間絶縁膜664を覆って、平坦化膜として機能する第2層間絶縁膜666を形成する(図8(C))。

## 【0129】

第2層間絶縁膜666としては、感光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジストまたはベンゾシクロブテン)、珪素(Si)と酸素(O)との結合(Si-O-Si結合)で骨格構造が構成されるシロキサン等を用いることができる。第2層間絶縁膜666は、単層構造としても良いし、積層構造としても良い。感光性の有機材料としては、ポジ型感光性有機樹脂やネガ型感光性有機樹脂を用いることができる。

10

## 【0130】

本実施の形態では、第2層間絶縁膜666としてシロキサンをスピンドルコート法で形成する。

## 【0131】

次に、第1層間絶縁膜664及び第2層間絶縁膜666をエッチングして、島状半導体膜612、614、616に到達するコンタクトホールを形成する。

## 【0132】

なお、第2層間絶縁膜666上に第3層間絶縁膜を形成し、第1層間絶縁膜乃至第3層間絶縁膜にコンタクトホールを形成してもよい。第3層間絶縁膜としては、水分や酸素などを透過させにくい膜を用いることが好ましい。代表的には、スパッタ法またはCVD法により形成される窒化珪素膜、酸化珪素膜、酸素を含む窒化珪素膜(SiN<sub>x</sub>O<sub>y</sub>膜:x>y>0、またはSiO<sub>x</sub>N<sub>y</sub>膜:x>y>0)、炭素を主成分とする薄膜(例えばDLC膜、CN膜)等を用いることができる。

20

## 【0133】

第2層間絶縁膜666上にコンタクトホールを介して、第3の導電膜を形成し、当該第3の導電膜を選択的にエッチングして、電極または配線668、670、672、674、676を形成する。

## 【0134】

第3の導電膜としては、アルミニウム(Al)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タンゲステン(W)、ネオジム(Nd)、クロム(Cr)、ニッケル(Ni)、白金(Pt)、金(Au)、銀(Ag)、銅(Cu)、マグネシウム(Mg)、スカンジウム(Sc)、コバルト(Co)、亜鉛(Zn)、ニオブ(Nb)、シリコン(Si)、リン(P)、ボロン(B)、ヒ素(As)、ガリウム(Ga)、インジウム(In)、錫(Sn)から選択された一つ又は複数の元素、または、前記元素を成分として含有する化合物や合金材料(例えば、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化珪素を添加したインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、アルミネオジム(Al-Nd)、マグネシウム銀(Mg-Ag)など)、もしくは、これらの化合物を組み合わせた物質などを用いることができる。その他にも、シリサイド(例えば、アルミシリコン、モリブデンシリコン、ニッケルシリサイド)や、窒素を含有する化合物(例えば、窒化チタン、窒化タンタル、窒化モリブデン)、リン(P)等の不純物元素をドーピングしたシリコン(Si)等を用いてもよい。

30

## 【0135】

本実施の形態では、チタン膜(Ti)、窒化チタン膜、シリコン-アルミニウム合金膜(Al-Si)、チタン膜(Ti)をそれぞれ60nm、40nm、300nm、100nmに積層したのち、所望の形状になるように選択的にエッチングして電極または配線668、670、672、674、676を形成する。

40

## 【0136】

なお、電極または配線668、670、672、674、676を、ニッケル(Ni)、コバルト(Co)、鉄(Fe)のうち少なくとも1種の元素、及び炭素(C)を含むアルミニウム合金膜で形成してもよい。このようなアルミニウム合金膜を用いることにより

50

、電極等がシリコン(Si)と接触した場合にも、シリコンと電極材料の相互拡散を防止できるという利点がある。また、このようなアルミニウム合金膜は、透明導電膜、例えばインジウム錫酸化物(ITO)を用いて形成された導電膜と接触しても酸化還元反応が起こらないという特徴を有し、両者を直接接触させることができるので、さらに、このようなアルミニウム合金膜は、比抵抗が小さく、耐熱性にも優れているので、配線材料としては好適である。

#### 【0137】

また、電極または配線668、670、672、674、676としては、電極と配線とを同時に形成した構成を用いても良いし、電極と配線とを別々に形成してそれらを接続させた構成を用いても良い。

10

#### 【0138】

上記一連の工程によってnチャネル型TFT678及びpチャネル型TFT680を含むCMOS回路684、及びnチャネル型TFT682を含むアクティブマトリクス基板を形成することができる(図8(C))。なお、本発明に用いることができるアクティブマトリクス基板の作製方法は、上述の作製工程に限定されない。例えば、非晶質半導体膜を用いたTFT、単結晶半導体膜を用いたTFTを形成する工程を採用しても良い。また、トップゲート型のTFTに限らず、ボトムゲート型のTFT用いることとしても良い。

#### 【0139】

また、本発明の液晶表示装置に用いることができるアクティブマトリクス基板は、駆動回路を一体で有する構成には限られない。例えば、駆動回路(もしくはその一部)を単結晶基板上に形成し、そのICチップをCOG(Chip On Glass)で接続してガラス基板上に配置してもよい。また、ICチップをTAB(Tape Auto Bonding)やプリント基板を用いてガラス基板と接続してもよい。

20

#### 【0140】

本実施の形態は、実施の形態1乃至4のいずれとも、適宜組み合わせて用いることができる。

#### 【0141】

##### (実施の形態6)

本実施の形態では、本発明の駆動方法を用いた液晶表示装置の作製工程について、図9乃至図11を用いて説明する。

30

#### 【0142】

本実施の形態で説明する液晶表示装置の作製方法は画素TFTを含む画素部とその周辺に設けられる駆動回路部のTFTを同時に作製する方法である。ただし、簡単のため、駆動回路に関しては基本単位であるCMOS回路のみを示す。

#### 【0143】

まず、実施の形態5に記載の方法等を用いてアクティブマトリクス基板を作製する。ここで、本実施の形態においては、実施の形態5に記載の方法を用いて作製したアクティブマトリクス基板を用いて説明を行うが、本発明の液晶表示装置の作製方法はこれに限られるものではない。

40

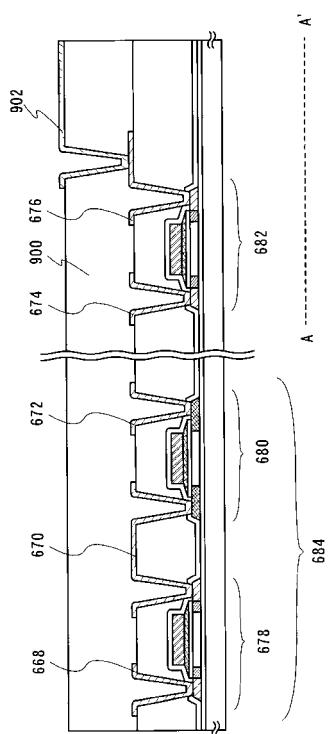

#### 【0144】

まず、実施の形態5にしたがい、電極または配線668、670、672、674、676の形成までの工程を行う(図8(C))。なお、以下の図面において、実施の形態5と同じものについては同じ符号を用いて表すこととする。

#### 【0145】

次に、第2層間絶縁膜666、及び、電極または配線668、670、672、674、676上に第3層間絶縁膜900を形成する(図9)。なお第3層間絶縁膜900は、第2層間絶縁膜666と同様の材料を用いて形成することが可能である。

#### 【0146】

次に、フォトマスクを用いてレジストマスクを形成し、第3層間絶縁膜900の一部を

50

ドライエッティングにより除去してコンタクトホールを形成する。コンタクトホール形成においては、エッティングガスとして四フッ化炭素( $\text{CF}_4$ )、酸素( $\text{O}_2$ )、ヘリウム( $\text{He}$ )を、それぞれ50 sccm、50 sccm、30 sccmの流量で用いた。なお、コンタクトホールの底部は電極または配線676に達している。

#### 【0147】

レジストマスクを除去した後、全面に第4の導電膜を成膜する。次いで、第4の導電膜を選択的にエッティングして、電極または配線676に電気的に接続される画素電極902を形成する(図9)。反射型の液晶表示装置を作製する場合には、画素電極902はスペッタ法によりAg(銀)、Au(金)、Cu(銅)、W(タンゲステン)、Al(アルミニウム)等の光反射性を有する金属材料を用いて形成すればよい。透過型の液晶表示装置を作製する場合は、インジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物、酸化亜鉛(ZnO)、酸化スズ( $\text{SnO}_2$ )などの透明導電膜を用い、画素電極902を形成することができる。

#### 【0148】

なお、本発明は反射型・透過型に限られず適用することができる。例えば、画素の一部が反射型であり、他の一部が透過型である、いわゆる半透過型の液晶表示装置に本発明を適用しても良い。反透過型の液晶表示装置は、外部からの光が大きい場合には反射型として、そうではない場合には透過型として用いることができるため、輝度の確保・消費電力の低減が容易という利点がある。

#### 【0149】

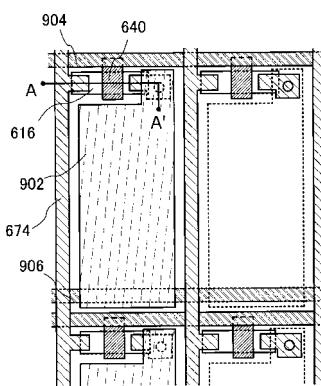

画素TFTを含む画素部の一部を拡大した上面図を図10に示す。図10は画素電極の形成途中を示しており、左側の画素においては画素電極が形成されているが、右側の画素においては画素電極が形成されていない。なお、図10におけるA-A'は、図9の画素部のA-A'に対応しており、図9と対応する部分には同じ符号を用いている。

#### 【0150】

図10に示すように、ゲート電極640はゲート配線904に接続されている。また、電極または配線674はソース配線と一体形成されている。さらに、容量配線906が形成されており、第1層間絶縁膜664、画素電極902、及び容量配線906とから保持容量が形成されている。なお、本実施の形態においては、保持容量を設ける構成を示すが、本発明を用いることにより、保持容量を小さくすることも可能である。したがって、あえて容量配線を設けない構成とすることで画素の開口率を向上することができる。特に、透過型の液晶表示装置において、その効果は著しい。

#### 【0151】

以上の工程により、トップゲート型の画素TFT(nチャネル型TFT)682、トップゲート型のnチャネル型TFT678及びトップゲート型のpチャネル型TFT680からなるCMOS回路684、及び画素電極902が、基板600の上に形成された。本実施の形態では、トップゲート型TFTを形成する例を示したが、ボトムゲート型TFTを形成しても良い。

#### 【0152】

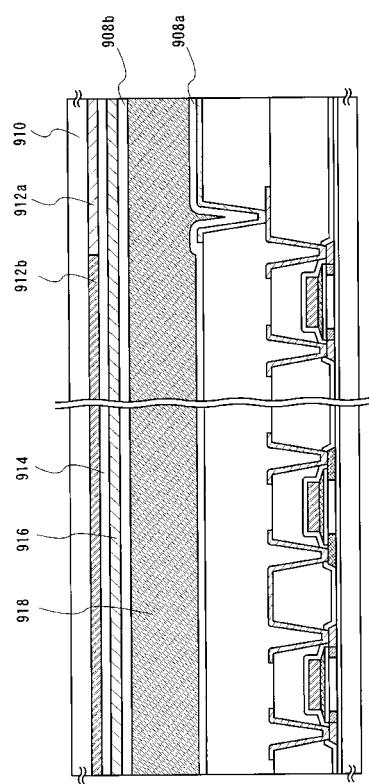

次に、画素電極902を覆うように、配向膜908aを形成する。なお、配向膜908aは、液滴吐出法、スクリーン印刷法、オフセット印刷法等を用いて形成すればよい。その後、配向膜908aの表面にラビング処理を行う。

#### 【0153】

次に、基板600と貼り合わせるための対向基板910を用意する。ここで、対向基板910には、着色層912a、遮光層(ブラックマトリクス)912b、及びオーバーコート層914からなるカラーフィルタを設け、さらに光透過性の電極や光反射性の電極からなる対向電極916と、配向膜908bを形成する(図11)。対向基板910は基板600と同じ大きさ又は同じ形のものを用いることもできる。ここで、同じ大きさ、同じ形とは、厳密に同じである必要はなく、パネルを構成するに足りる程度の大きさ、形を言うものとする。

10

20

30

40

50

**【 0 1 5 4 】**

次に、上記工程により得た基板 600 と対向基板 910 をシール材を介して貼り合わせる。ここで、両基板の間隔を一定に保つために、配向膜 908a と配向膜 908b との間にスペーサを設けても良い。その後、両基板の間に液晶 918 を注入し、封止材を用いて封止することで液晶表示装置が完成する(図 11)。

**【 0 1 5 5 】**

なお、本発明の液晶表示装置には、TN (Twisted Nematic) 方式、IPS (In-Plane-Switching) 方式、FFS (Fringe Field Switching) 方式、MVA (Multi-domain Vertical Alignment) 方式、PVA (Patterned Vertical Alignment) 方式、ASM (Axially Symmetric aligned Micro-cell) 方式、OCB (Optical Compensated Birefringence) 方式、FLC (Ferroelectric Liquid Crystal) 方式、AFLC (AntiFerroelectric Liquid Crystal) 方式等を用いることができる。10

**【 0 1 5 6 】**

本実施の形態は、実施の形態 1 乃至 5 と適宜組み合わせて用いることができる。

**【 0 1 5 7 】****(実施の形態 7 )**

本実施の形態においては、SOI (Silicon on Insulator) 基板を用いた液晶表示装置について以下に説明する。なお、本実施の形態に係る SOI 基板は、単結晶半導体基板から、異種基板(以下、「ベース基板」ともいう)に転写して形成するものである。20

**【 0 1 5 8 】**

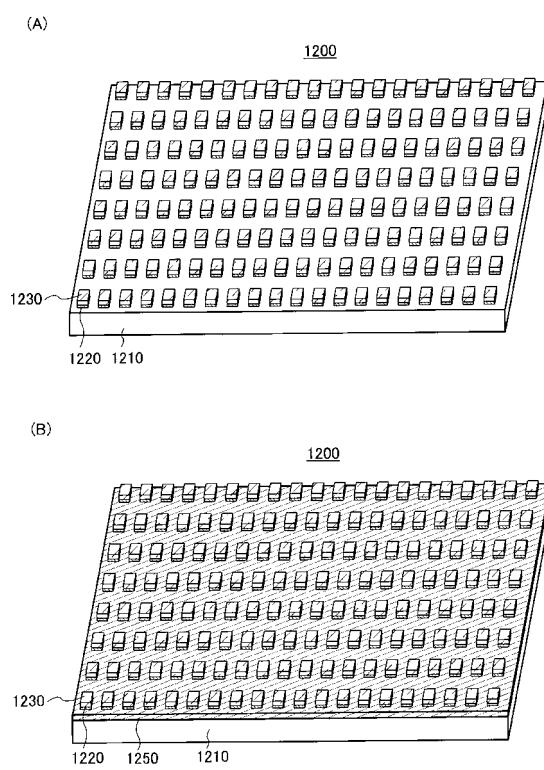

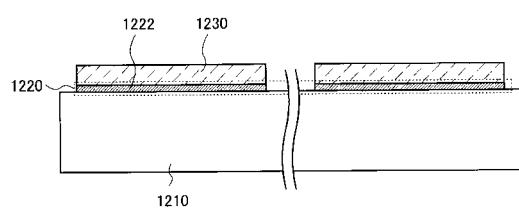

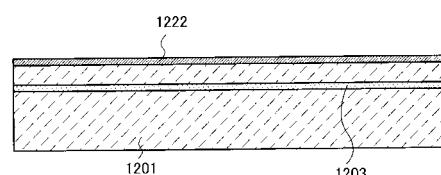

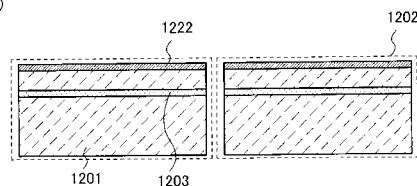

図 12 に、本発明に用いる SOI 基板の斜視図を示す。また、図 13 及び図 14 に、本発明に用いる SOI 基板の断面図を示す。

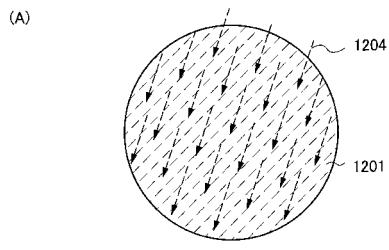

**【 0 1 5 9 】**

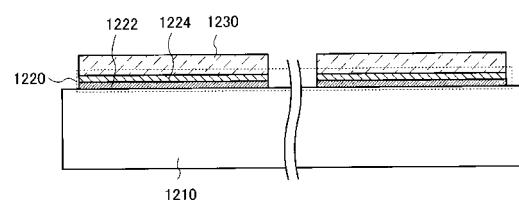

図 12(A)、図 13(A)、及び図 13(B)において、SOI 基板 1200 は、ベース基板 1210 の一表面上に、絶縁層 1220 及び SOI 層 1230 が順次積層された積層体が複数設けられた構成を有する。SOI 層 1230 は、絶縁層 1220 を介してベース基板 1210 上に設けられている。つまり、1 枚のベース基板 1210 上に複数の SOI 層が設けられ、1 枚の SOI 基板 1200 を形成している。なお、図 13 では、便宜上、2 つの SOI 層 1230 のみを示す。30

**【 0 1 6 0 】**

SOI 層 1230 は単結晶半導体であり、代表的には単結晶シリコンが適用される。その他、水素イオン注入剥離法などをを利用して単結晶半導体基板若しくは多結晶半導体基板から剥離可能であるシリコン、ゲルマニウムや、ガリウムヒ素、インジウムリンなどの化合物半導体である結晶性半導体層を適用することもできる。

**【 0 1 6 1 】**

SOI 層 1230 の形状は特に限定されないが、矩形状(正方形を含む)とすると加工が容易になり、ベース基板 1210 にも集積度良く貼り合わせることができ好ましい。また、ディスプレイ等の表示装置のパネルとする場合は、SOI 層 1230 のアスペクト比が 4 : 3 となるようにすることが好ましい。SOI 層 1230 を所望のパネルサイズ程度とすることで、完成する SOI 基板を用いて製造した表示パネルを組み込んで各種表示装置を製造する際に、パネル毎に歩留まりを管理することができる。また、個々のパネルを分断する際に、素子にダメージが入るのを防止することができる。よって、歩留まりの向上を図ることができる。さらに、SOI 層 1230 を所望のパネルサイズ程度とすることで、各パネル毎の素子を 1 つの SOI 層で形成することができ、特性のばらつきを抑えることが可能になる。40

**【 0 1 6 2 】**

ベース基板1210は絶縁表面を有する基板または絶縁基板を用いる。具体的には、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイヤ基板が挙げられる。好ましくはガラス基板を用いるのがよく、例えば第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)といわれる大面積のマザーガラス基板を用いることができる。大面積のマザーガラス基板をベース基板1210として用いることで、SOI基板の大面積化が実現できる。また、個々のSOI層を所望のパネルサイズとすることで、1枚のベース基板で製造できる表示パネルの数(面取り数)を増大させることができる。したがって、該表示パネルを組み込んで製造する最終製品(表示装置)の生産性を向上させることができる。

10

#### 【0163】

ベース基板1210とSOI層1230の間には、絶縁層1220が設けられている。絶縁層1220は単層構造としても積層構造としてもよいが、ベース基板1210と接合する面(以下、「接合面」ともいう)は、平滑面を有し親水性表面となるようにする。図13(A)は絶縁層1220として接合層1222を形成する例を示している。平滑面を有し親水性表面を形成できる接合層1222としては、酸化シリコン層が適している。特に、有機シランを用いて化学気相成長法により作製される酸化シリコン層が好ましい。有機シランとしては、テトラエトキシシラン(略称;TEOS:化学式Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>)、テトラメチルシラン(TMS:化学式Si(CH<sub>3</sub>)<sub>4</sub>)、トリメチルシラン((CH<sub>3</sub>)<sub>3</sub>SiH)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(O<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)、トリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

20

#### 【0164】

上記平滑面を有し親水性表面を形成する接合層1222は、膜厚5nm乃至500nmの範囲で設けることが好ましい。接合層1222の膜厚を上記範囲内とすることで、被成膜表面の表面荒れを平滑化すると共に、当該膜の成長表面の平滑性を確保することが可能である。また、接合する基板(図13(A)ではベース基板1210)との歪みを緩和することができる。なお、ベース基板1210にも、接合層1222と同様の酸化シリコン層を設けてよい。絶縁表面を有する基板若しくは絶縁基板であるベース基板1210にSOI層1230を接合するに際し、接合を形成する面の一方若しくは双方に、好ましくは有機シランを原材料として成膜した酸化シリコン層でなる接合層を設けることで強固な接合を形成することができる。

30

#### 【0165】

図13(B)は絶縁層1220を積層構造とする例を示している。具体的には、絶縁層1220として接合層1222及び窒素含有絶縁層1224の積層構造を形成する例を示している。なお、ベース基板1210との接合面には接合層1222が形成されるようするため、SOI層1230と接合層1222との間に窒素含有絶縁層1224が設けられた構成とする。窒素含有絶縁層1224は、窒化シリコン層、窒化酸化シリコン層又は酸化窒化シリコン層を用いて単層構造又は積層構造で形成する。例えば、SOI層1230側から酸化窒化シリコン層、窒化酸化シリコン層を積層して窒素含有絶縁層1224とすることができる。接合層1222はベース基板1210と接合を形成するために設けるのに対し、窒素含有絶縁層1224は、可動イオンや水分等の不純物がSOI層1230に拡散して汚染されることを防ぐために設けている。

40

#### 【0166】

なお、酸化窒化シリコン層とは、その組成として、窒素よりも酸素の含有量が多いものを示し、濃度範囲として酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、珪素が25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化シリコン層とは、その組成として、酸素よりも窒素の含有量が多いものを示し、酸素が5原子%以上30原子%以下、窒素

50

が 20 原子%以上 55 原子%以下、珪素が 25 原子%以上 35 原子%以下、水素が 10 原子%以上 25 原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) や、水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が 100 原子%を超えない値をとる。

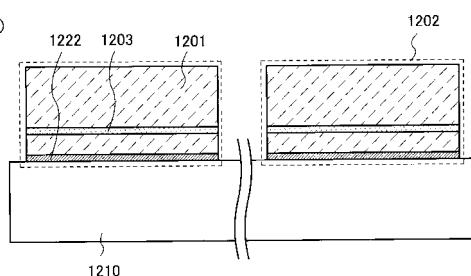

#### 【0167】

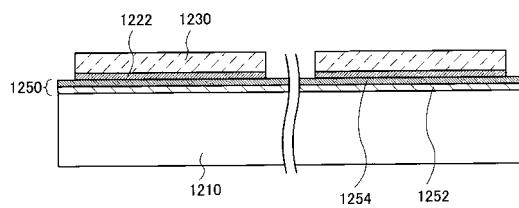

図 12 (B)、図 14 (A)、及び 14 (B) は、ベース基板 1210 に接合層を含む絶縁層 1250 を形成する例を示している。絶縁層 1250 は、単層構造でも積層構造でもよいが、SOI 層 1230 との接合面は平滑面を有し親水性表面を形成するようにする。なお、ベース基板 1210 と接合層との間には、ベース基板 1210 として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属などの可動イオンの拡散を防ぐため、バリア層が設けられていることが好ましい。

#### 【0168】

図 14 (A) は、絶縁層 1250 としてバリア層 1252、接合層 1254 の積層構造を形成する例を示している。接合層 1254 としては、接合層 1222 と同様の酸化シリコン層を設ければよい。また、SOI 層 1230 に適宜接合層を設けてもよい。図 14 (A) では、SOI 層 1230 にも接合層 1222 を設ける例を示している。このような構成とすることで、ベース基板 1210 及び SOI 層 1230 を接合させる際に接合層同士で接合を形成するため、より強固な接合を形成することができる。バリア層 1252 は、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層又は窒化酸化シリコン層を用いて単層構造又は積層構造で形成する。好ましくは、窒素を含有する絶縁層を用いて形成する。

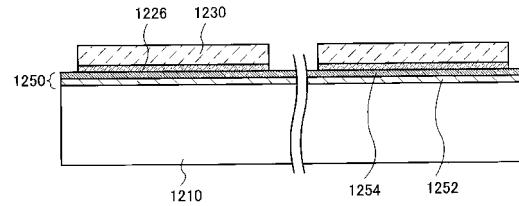

#### 【0169】

図 14 (B) は、ベース基板 1210 に接合層を設ける例を示している。具体的には、ベース基板 1210 に絶縁層 1250 としてバリア層 1252 と接合層 1254 の積層構造を設けている。また、SOI 層 1230 には酸化シリコン層 1226 を設けている。ベース基板 1210 に SOI 層 1230 を接合する際には、酸化シリコン層 1226 が接合層 1254 と接合を形成する。酸化シリコン層 1226 は、熱酸化法により形成されたものが好ましい。また、酸化シリコン層 1226 としてケミカルオキサイドを適用することもできる。ケミカルオキサイドは、例えばオゾン含有水で半導体基板表面を処理することで形成することができる。ケミカルオキサイドは半導体基板の表面の平坦性を反映して形成されるので好ましい。

#### 【0170】

次に、SOI 基板の製造方法について説明する。ここでは、図 13 (A) に示す SOI 基板の製造方法の例について、図 15 乃至図 17 を用いて説明する。

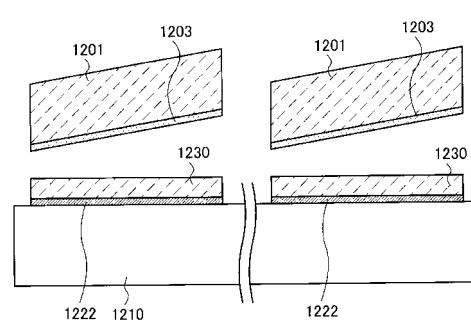

#### 【0171】

まず、半導体基板 1201 を準備する (図 15 (A)、図 17 (A) 参照)。半導体基板 1201 としては、市販の半導体基板を用いればよく、例えばシリコン基板やゲルマニウム基板、ガリウムヒ素やインジウムリンなどの化合物半導体基板が挙げられる。市販のシリコン基板としては、直径 5 インチ (125 mm)、直径 6 インチ (150 mm)、直径 8 インチ (200 mm)、直径 12 インチ (300 mm) サイズのものが代表的であり、その形状は円形のものが多い。また、膜厚は 1.5 mm 程度まで適宜選択できる。

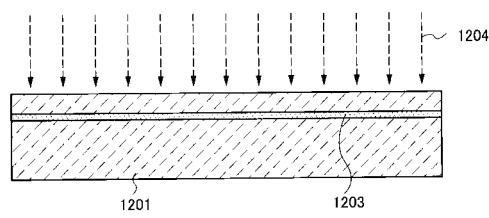

#### 【0172】

次に、半導体基板 1201 の表面から電界で加速されたイオン 1204 を所定の深さに打ち込み、イオンドーピング層 1203 を形成する (図 15 (A)、図 17 (A) 参照)。イオン 1204 の打ち込みは、後にベース基板に転置する SOI 層の膜厚を考慮して行われる。好ましくは、SOI 層の膜厚が 5 nm 乃至 500 nm、より好ましくは 10 nm 乃至 200 nm の厚さとなるようにする。イオンを打ち込む際の加速電圧及びイオンのドーズ量は、転置する SOI 層の膜厚を考慮して適宜選択する。イオン 1204 は、水素、

10

20

30

40

50

ヘリウム、又はフッ素等のハロゲンのイオンを用いることができる。なお、イオン 1204 としては、水素、ヘリウム、又はハロゲン元素から選ばれたソースガスをプラズマ励起して生成された一の原子又は複数の同一の原子からなるイオン種を用いることが好ましい。水素イオンを打ち込む場合には、 $H^+$ 、 $H_2^+$ 、 $H_3^+$  イオンを含ませると共に、 $H_3^+$  イオンの割合を高めておくとイオンの打ち込み効率を高めることができ、打ち込み時間を短縮することができるため好ましい。また、このような構成とすることで、剥離を容易に行うことができる。

#### 【 0173 】

なお、所定の深さにイオンドーピング層 1203 を形成するために、イオン 1204 を高ドーズ条件で打ち込むことが必要となる場合がある。このとき、条件によっては半導体基板 1201 の表面が粗くなってしまう。そのため、半導体基板のイオンが打ち込まれる表面に、保護層として窒化シリコン層又は窒化酸化シリコン層などを膜厚 50 nm 乃至 200 nm の範囲で設けておいてもよい。10

#### 【 0174 】

次に、半導体基板 1201 に接合層 1222 を形成する（図 15（B）、図 17（B）参照）。接合層 1222 は、半導体基板 1201 がベース基板と接合を形成する面に形成する。ここで形成する接合層 1222 としては、上述のように有機シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層が好ましい。その他に、シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層を適用することもできる。化学気相成長法による成膜では、半導体基板 1201 に形成したイオンドーピング層 1203 から脱ガスが起こらない程度の温度が適用される。例えば、350 以下の成膜温度が適用される。なお、単結晶半導体基板または多結晶半導体基板などの半導体基板から SOI 層を剥離する加熱処理は、化学気相成長法による成膜温度よりも高い加熱処理温度が適用される。20

#### 【 0175 】

次に、半導体基板 1201 を所望の大きさ、形状に加工する（図 15（C）、図 17（C）参照）。図 17（C）では、円形の半導体基板 1201 を分断して、矩形の半導体基板 1202 を形成する例を示している。この際、接合層 1222 及びイオンドーピング層 1203 も分断される。つまり、所望の大きさ、形状を有し、所定の深さにイオンドーピング層 1203 が形成され、表面（ベース基板との接合面）に接合層 1222 が形成された半導体基板 1202 が得られる。30

#### 【 0176 】

半導体基板 1202 は、表示装置のパネルサイズとすることが好ましい。パネルサイズは組み込まれる最終製品等によって適宜選択すればよい。例えば、画面サイズ対角 2.4 インチの携帯電話機に適用する場合、画面サイズ対角 2.4 インチに画面額縁サイズを考慮したパネルサイズとする。また、半導体基板 1202 の形状も最終製品等、用途によって適宜選択すればよいが、ディスプレイ等の表示装置に適用する場合、アスペクト比 3 : 4 程度の矩形とすることが好ましい。また、半導体基板 1202 を矩形状にすると、後の製造工程における加工が容易になり、さらに半導体基板 1201 から効率的に切り出すことも可能になるため好ましい。半導体基板 1201 の分断は、ダイサー或いはワイヤソー等の切断装置、レーザー切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いて行うことができる。40

#### 【 0177 】

なお、半導体基板表面に接合層を形成するまでの工程順序は、適宜入れ替えることが可能である。図 15 及び図 17 では半導体基板にイオンドーピング層を形成し、半導体基板の表面に接合層を形成した後、半導体基板を所望のパネルサイズに加工する例を示している。これに対し、例えば、半導体基板を所望のパネルサイズに加工した後、所望のパネルサイズの半導体基板にイオンドーピング層を形成し、所望のパネルサイズの半導体基板の表面に接合層を形成することもできる。

#### 【 0178 】

10

20

30

40

50

次に、ベース基板 1210 と半導体基板 1202 を貼り合わせる。図 16 (A) には、ベース基板 1210 と半導体基板 1202 の接合層 1222 が形成された面とを密着させ、ベース基板 1210 と接合層 1222 を接合させて、ベース基板 1210 と半導体基板 1202 を貼り合わせる例を示す。なお、接合を形成する面（接合面）は十分に清浄化しておくことが好ましい。ベース基板 1210 と接合層 1222 を密着させることにより接合が形成される。この接合にはファンデルワールス力が作用しており、ベース基板 1210 と半導体基板 1202 とを圧接することで、水素結合による強固な接合を形成することが可能である。

#### 【0179】

また、ベース基板 1210 と接合層 1222 との良好な接合を形成するために、接合面を活性化しておいてもよい。例えば、接合を形成する面の一方又は双方に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行うことで接合面を活性化することもできる。このような表面処理により、400 以下の温度であっても異種材料間の接合を形成することが容易となる。

#### 【0180】

また、接合層 1222 を介してベース基板 1210 と半導体基板 1202 を貼り合わせた後は、加熱処理又は加圧処理を行うことが好ましい。加熱処理又は加圧処理を行うことで接合強度を向上させることが可能となる。加熱処理の温度は、ベース基板 1210 の耐熱温度以下であることが好ましい。加圧処理においては、接合面に垂直な方向に圧力が加わるように行い、ベース基板 1210 及び半導体基板 1202 の耐圧性を考慮して行う。

#### 【0181】

次に、加熱処理を行い、イオンドーピング層 1203 を劈開面として半導体基板 1202 の一部をベース基板 1210 から剥離する（図 16 (B) 参照）。加熱処理の温度は接合層 1222 の成膜温度以上、ベース基板 1210 の耐熱温度以下で行うことが好ましい。例えば、400 乃至 600 の加熱処理を行うことにより、イオンドーピング層 1203 に形成された微小な空洞の体積変化が起こり、イオンドーピング層 1203 に沿って劈開することが可能となる。接合層 1222 はベース基板 1210 と接合しているので、ベース基板 1210 上には半導体基板 1202 と同じ結晶性の SOI 層 1230 が残存することとなる。

#### 【0182】

以上で、ベース基板 1210 上に接合層 1222 を介して SOI 層 1230 が設けられた SOI 構造が形成される。なお、本実施の形態にて説明した SOI 基板は、1 枚のベース基板上に接合層を介して複数の SOI 層が設けられた構造であるが、これに限られない。

#### 【0183】

なお、剥離により得られる SOI 層は、その表面を平坦化するため、化学的機械的研磨（Chemical Mechanical Polishing : CMP）を行うことが好ましい。また、CMP 等の物理的研磨手段を用いず、SOI 層の表面にレーザービームを照射して平坦化を行ってもよい。なお、レーザービームを照射する際は、酸素濃度が 10 ppm 以下の窒素雰囲気下で行うことが好ましい。これは、酸素雰囲気下でレーザービームの照射を行うと SOI 層表面が荒れる恐れがあるからである。また、得られた SOI 層の薄膜化を目的として、CMP 等を行ってもよい。

#### 【0184】

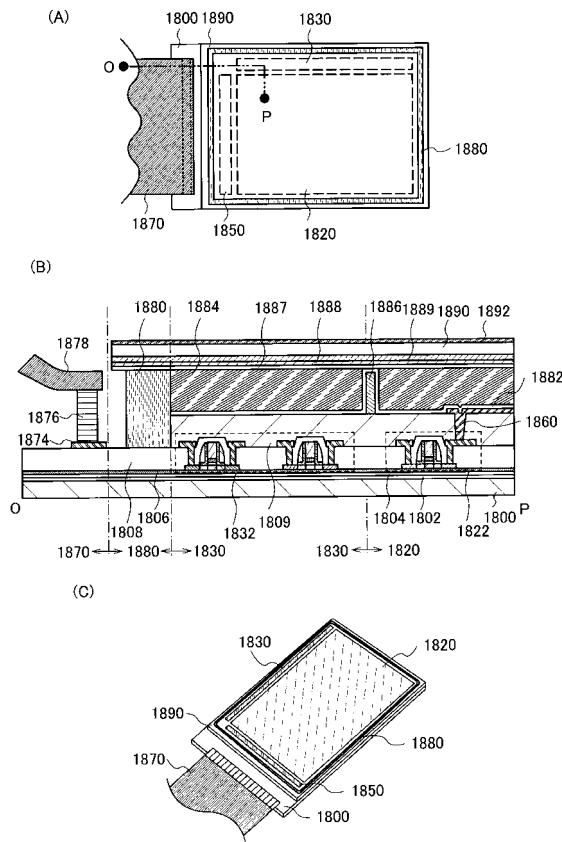

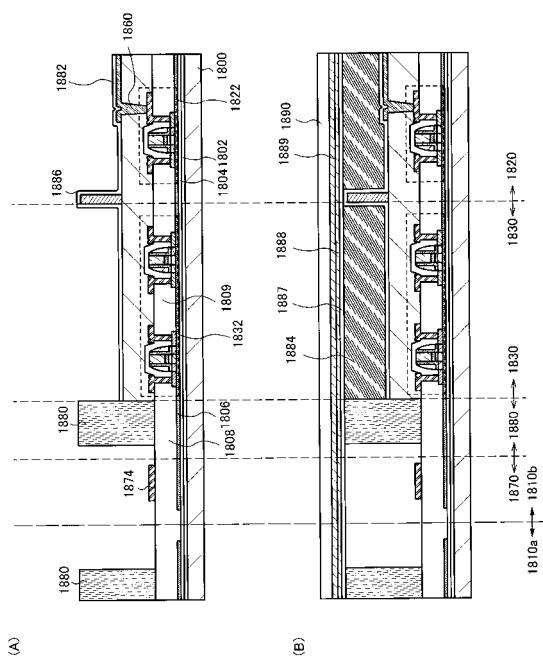

以上のようにして作製した SOI 基板を用いて液晶表示装置を製造することができる。図 18 (A) は上面の模式図であり、図 18 (B) は図 18 (A) の線分 O P における断面図であり、図 18 (C) は液晶表示装置の斜視図である。

#### 【0185】

本実施の形態に係る液晶表示装置は、第 1 の基板 1800 上に設けられた表示部 182

10

20

30

40

50

0と、第1の駆動回路部1830と、第2の駆動回路部1850と、を有する。表示部1820、第1の駆動回路部1830及び第2の駆動回路部1850は、シール材1880によって、第1の基板1800と第2の基板1890との間に封止されている。また、第1の基板1800上には、第1の駆動回路部1830及び第2の駆動回路部1850に外部からの信号や電位を伝達する外部入力端子が接続される端子領域1870が設けられる。

#### 【0186】

図18(B)に示すように、表示部1820にはトランジスタを有する画素回路部1828が設けられている。また、第1の駆動回路部1830にはトランジスタを有する周辺回路部1838が設けられている。第1の基板1800と、画素回路部1828及び周辺回路部1838との間には、下地絶縁層として機能する絶縁層1802、絶縁層1804、接合層1806が順次積層されている。画素回路部1828及び周辺回路部1838、或いはその上層には層間絶縁層として機能する絶縁層1808、絶縁層1809が設けられている。画素回路部1828に形成されたトランジスタのソース電極又はドレイン電極は、絶縁層1809に形成された開口を介して、画素電極1860と電気的に接続される。なお、画素回路部1828はトランジスタを用いた回路が集積されているが、ここでは便宜上1つのトランジスタの断面図を示している。同様に、周辺回路部1838にもトランジスタを用いた回路が集積されているが、便宜上2つのトランジスタの断面図を示している。

#### 【0187】

画素回路部1828及び周辺回路部1838上には、画素電極1860を覆うように形成された配向膜1882と、配向膜1887とで挟持された液晶層1884が設けられている。液晶層1884は、スペーサ1886により距離(セルギャップ)が制御されている。配向膜1887上には、対向電極1888、カラーフィルター1889を介して第2基板1890が設けられている。第1の基板1800及び第2の基板1890はシール材1880によって固着されている。

#### 【0188】

また、第2の基板1890の外側には、偏光板1892が配設されている。なお、本実施の形態では反射型の液晶表示装置を示すため、第2の基板1890に偏光板を設ける例を示す。例えば透過型の液晶表示装置とする場合は、第1の基板1800及び第2の基板1890の双方に偏光板を設ければよい。

#### 【0189】

また、端子領域1870には、端子電極1874が設けられている。該端子電極1874は、異方性導電層1876によって、外部入力端子1878と電気的に接続されている。

#### 【0190】

次に、図18で示した液晶表示装置の製造方法の一例に関して説明する。

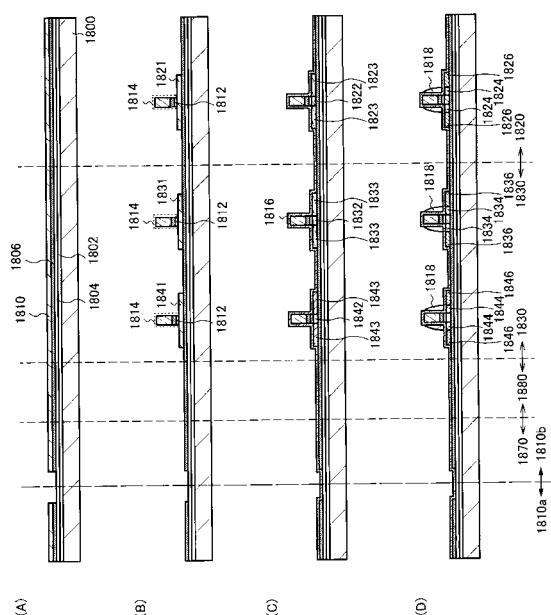

#### 【0191】

まず、SOI基板を準備する(図19(A)参照)。ここでは、図13(A)に類似したSOI基板を適用する例を示す。

#### 【0192】

ベース基板である基板1800上には、絶縁層1802、絶縁層1804及び接合層1806を介して複数のSOI層1810が設けられている。SOI層1810は所望のパネルサイズに加工されている。ここでは、便宜的に1つのSOI層を含むパネル形成領域1810bを用いて液晶表示装置を製造する例を説明するが、隣接するパネル形成領域1810aにも同時に製造することが可能である。

#### 【0193】

基板1800としては、絶縁表面を有する基板または絶縁基板を用いる。例えば、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイヤ基板等を

10

20

30

40

50

用いることができる。ここでは、ガラス基板を用いるものとする。

#### 【0194】

絶縁層1802、絶縁層1804は、ガラス基板からアルカリ金属若しくはアルカリ土類金属などの可動イオンの拡散を防ぐために設ける。具体的には、上述のバリア層と同様の絶縁層を設ければよい。なお、絶縁層1802及び絶縁層1804の少なくとも一層は、窒化シリコン層又は窒化酸化シリコン層の窒素を含有する絶縁層を設けることが好ましい。また、接合層1806には、酸化シリコン層を設ければよい。

#### 【0195】

本実施の形態では、基板1800上に絶縁層1802、絶縁層1804を形成し、SOI層を剥離する半導体基板側に接合層1806を形成し、基板1800及び半導体基板を貼り合わせた後、半導体基板の一部を剥離してSOI層1810を形成する例を示す。具体的には、基板1800の絶縁層1804が形成された面と、半導体基板の接合層1806が形成された面とを密着させ、絶縁層1804と接合層1806とを接合させて、基板1800と半導体基板を貼り合わせる。半導体基板には、所定の深さに水素、ヘリウム又はハロゲンのイオンを打ち込んだイオンドーピング層を形成しておく。そして、加熱処理を行い、半導体基板に形成されたイオンドーピング層を劈開面として半導体基板の一部を剥離し、SOI層1810を得る。ここでは、半導体基板側に接合層1806を形成するため、該接合層1806はSOI層1810と同程度の大きさとなる。つまり、隣接するパネル形成領域1810a及びパネル形成領域1810bとの間で、SOI層1810と同様に接合層1806も分離している。また、絶縁層1802、絶縁層1804はベース基板である基板1800上に形成するため、隣接するパネル形成領域1810a及びパネル形成領域1810bで連続する層となる。なお、適用するSOI基板については特に限定されず、上述の図13及び図14のいずれの構造を適用してもよい。例えば、ベース基板側に接合層を設けてもよいし、半導体基板と接合層との間に熱酸化膜等の絶縁層を設けてもよい。

#### 【0196】

次に、SOI層1810を選択的にエッチングして、表示部1820に第1のSOI層1821を形成する。また、第1の駆動回路部1830に第2のSOI層1831、第3のSOI層1841を形成する。そして、第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841上に、ゲート絶縁層1812を介してゲート電極1814を形成する(図19(B)参照)。

#### 【0197】

第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841は、SOI層1810を選択的にエッチングして所望の形状に加工する。ここではSOI層1810を複数の島状に加工し、分離させる。準備したSOI基板のSOI層よりも、第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841の膜厚を薄くしたい場合には、該SOI層をエッチングして薄膜化してもよい。また、SOI層の一部を変質させて、該変質した部分を選択的にエッチングして薄膜化してもよい。ここでSOI層の変質とは、例えば酸化処理、窒化処理等を示す。また、第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841は、適宜エッチング条件等を制御して、端部が垂直に近いテーパ形状となるように形成してもよいし、緩やかなテーパ形状となるように形成してもよい。例えば、テーパ角が45°以上95°未満、好ましくは60°以上95°未満となるような形状としてもよいし、テーパ角が45°未満の緩やかな形状としてもよい。

#### 【0198】

なお、完成するトランジスタの閾値電圧を制御するため、第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841に低濃度の一導電型を付与する不純物元素を添加してもよい。この場合、トランジスタのチャネル形成領域にも不純物元素が添加されることになる。なお、ここで添加する不純物元素は、ソース領域又はドレイン領域として機能する高濃度不純物領域及びLDD領域として機能する低濃度不純物領域よりも

10

20

30

40

50

低い濃度で添加する。

**【0199】**

ゲート電極1814は、基板全面に導電層を形成した後、該導電層を選択的にエッチングして所望の形状に加工する。ここでは、ゲート電極1814として導電層の積層構造を形成した後、選択的にエッチングして、分離した導電層が第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841をそれぞれ横断するように加工している。

**【0200】**

ゲート電極1814を形成する導電層は、CVD法やスパッタリング法により、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銅(Cu)、又はニオブ(Nb)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電層を形成した後、当該導電層を選択的にエッチングして形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。

**【0201】**

なお、ここではゲート電極1814を2層の導電層の積層構造で形成する例を図示するが、ゲート電極は単層構造でも3層以上の積層構造でもよい。また、導電層の側面をテープ形状としてもよい。ゲート電極を導電層の積層構造とする場合、下層の導電層の幅を大きくしてもよいし、各層の側面を異なる角度のテープ形状としてもよい。

10

**【0202】**

第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841と、ゲート電極1814との間には、ゲート絶縁層1812を形成する。ゲート絶縁層1812は、CVD法、スパッタリング法、ALD法等を用いて、酸化シリコン、酸化窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタルなどの材料を用いて形成することができる。また、第1のSOI層1821、第2のSOI層1831及び第3のSOI層1841をプラズマ処理により固相酸化又は固相窒化して形成することもできる。その他、CVD法等により絶縁層を形成した後、当該絶縁層をプラズマ処理により固相酸化又は固相窒化して形成してもよい。

20

**【0203】**

なお、図19(B)では、ゲート絶縁層1812とゲート電極1814の側端部が揃うように加工される例を示すが、特に限定されず、ゲート電極1814のエッチングにおいてゲート絶縁層1812を残すように加工してもよい。

30

**【0204】**

また、ゲート絶縁層1812に高誘電率物質(high-k材料といわれる)を用いる場合には、ゲート電極1814を多結晶シリコン、シリサイド、金属若しくは金属窒化物で形成する。好ましくは金属若しくは金属窒化物で形成することが望ましい。例えば、ゲート電極1814のうちゲート絶縁層1812と接する導電層を金属窒化物材料で形成し、その上の導電層を金属材料で形成する。この組み合わせを用いることによって、ゲート絶縁層を薄膜化した場合でもゲート電極に空乏層が広がってしまうことを防止でき、微細化した場合にもトランジスタの駆動能力を損なうことを防止できる。

40

**【0205】**

次に、ゲート電極1814上に絶縁層1816を形成する。そして、ゲート電極1814をマスクとして一導電型を付与する不純物元素を添加する(図19(C)参照)。ここでは、第1の駆動回路部1830に形成された第2のSOI層1831及び第3のSOI層1841に相異なる導電型を付与する不純物元素を添加する例を示す。また、表示部1820に形成された第1のSOI層1821には第2のSOI層1831と同じ導電型を付与する不純物元素を添加する例を示す。

**【0206】**

表示部1820に形成された第1のSOI層1821には、ゲート電極1814をマス

50

クとして自己整合的に一対の不純物領域 1823 と、当該一対の不純物領域 1823 の間に位置するチャネル形成領域 1822 が形成される。

#### 【0207】

第 1 の駆動回路部 1830 に形成された第 2 の SOI 層 1831 には、ゲート電極 1814 をマスクとして自己整合的に一対の不純物領域 1833 と、当該一対の不純物領域 1833 の間に位置するチャネル形成領域 1832 が形成される。第 3 の SOI 層 1841 には、ゲート電極 1814 をマスクとして自己整合的に一対の不純物領域 1843 と、当該一対の不純物領域 1843 の間に位置するチャネル形成領域 1842 が形成される。不純物領域 1833 及び不純物領域 1843 は、相異なる導電型の不純物元素が添加されている。

10

#### 【0208】

一導電型を付与する不純物元素としては、ボロン (B)、アルミニウム (Al)、ガリウム (Ga) 等の p 型を付与する元素、リン (P)、ヒ素 (As) 等の n 型を付与する元素を用いることができる。本実施の形態では、表示部 1820 に形成された第 1 の SOI 層 1821、第 1 の駆動回路部 1830 に形成された第 2 の SOI 層 1831 に n 型を付与する元素、例えばリンを添加する。また、第 3 の SOI 層 1841 に p 型を付与する元素、例えばボロンを添加する。なお、第 1 の SOI 層 1821、第 2 の SOI 层 1831 に不純物元素を添加する際は、レジストマスク等を用いて第 3 の SOI 層 1841 を選択的に覆えばよい。同様に、第 3 の SOI 層 1841 に不純物元素を添加する際は、レジストマスク等を用いて第 1 の SOI 層 1821、第 2 の SOI 層 1831 を選択的に覆えばよい。

20

#### 【0209】

絶縁層 1816 は、CVD 法、スパッタリング法、ALD 法等を用いて、酸化シリコン或いは酸化窒化シリコン、又は窒化シリコン或いは窒化酸化シリコンなどの材料を用いて形成することができる。一導電型を付与する不純物元素を添加する際に、絶縁層 1816 を通過させて添加する構成とすることで、SOI 層に与えるダメージを低減することができる。

#### 【0210】

次に、ゲート電極 1814 の側面にサイドウォール絶縁層 1818 を形成する。そして、ゲート電極 1814 及びサイドウォール絶縁層 1818 をマスクとして一導電型を付与する不純物元素を添加する(図 19 (D) 参照)。なお、第 1 の SOI 層 1821、第 2 の SOI 層 1831 及び第 3 の SOI 層 1841 には、それぞれ先の工程(不純物領域 1823、不純物領域 1833 及び不純物領域 1843 を形成する工程)で添加した不純物元素と同じ導電型の不純物元素を添加する。また、先の工程で添加した不純物元素よりも高い濃度で添加する。

30

#### 【0211】

第 1 の SOI 層 1821 には、ゲート電極 1814 及びサイドウォール絶縁層 1818 をマスクとして自己整合的に一対の高濃度不純物領域 1826 と、一対の低濃度不純物領域 1824 が形成される。ここで形成される高濃度不純物領域 1826 はソース領域又はドレイン領域として機能し、低濃度不純物領域 1824 は LDD (Lightly Doped Drain) 領域として機能する。

40

#### 【0212】

第 2 の SOI 層 1831 には、ゲート電極 1814 及びサイドウォール絶縁層 1818 をマスクとして自己整合的に一対の高濃度不純物領域 1836 と、一対の低濃度不純物領域 1834 が形成される。ここで形成される高濃度不純物領域 1836 はソース領域又はドレイン領域として機能し、低濃度不純物領域 1834 は LDD 領域として機能する。第 3 の SOI 層 1841 には、ゲート電極 1814 及びサイドウォール絶縁層 1818 をマスクとして自己整合的に一対の高濃度不純物領域 1846 と、一対の低濃度不純物領域 1844 が形成される。なお、第 1 の SOI 層 1821、第 2 の SOI 層 1831 に不純物元素を添加する際は、レジストマスク等を用いて第 3 の SOI 層 1841 を選択的に覆え

50

ばよい。同様に、第3のSOI層1841に不純物元素を添加する際は、レジストマスク等を用いて第1のSOI層1821、第2のSOI層1831を選択的に覆えばよい。

#### 【0213】

サイドウォール絶縁層1818は、絶縁層1816を介してゲート電極1814の側面に設けられる。例えば、ゲート電極1814を埋め込むように形成した絶縁層を、垂直方向を主体とした異方性エッチングを行うことによって、ゲート電極1814の側面に自己整合的に形成することができる。サイドウォール絶縁層1818は、窒化シリコン或いは窒化酸化シリコン、又は酸化シリコン或いは酸化窒化シリコンなどの材料を用いて形成することができる。なお、絶縁層1816を酸化シリコン又は酸化窒化シリコンを用いて形成する場合、サイドウォール絶縁層1818を窒化シリコン又は窒化酸化シリコンを用いて形成することで、絶縁層1816をエッチングストッパーとして機能させることができる。また、絶縁層1816を窒化シリコン又は窒化酸化シリコンを用いて形成する場合は、サイドウォール絶縁層1818を酸化シリコン又は酸化窒化シリコンを用いて形成すればよい。このように、エッチングストッパーとして機能しうる絶縁層を設けることで、サイドウォール絶縁層を形成する際のオーバーエッチングによりSOI層がエッチングされてしまうのを防ぐことができる。10

#### 【0214】

次に、絶縁層1816の露出部をエッチングする(図20(A)参照)。絶縁層1816は、サイドウォール絶縁層1818及びゲート電極1814の間、サイドウォール絶縁層1818及び第1のSOI層1821の間、サイドウォール絶縁層1818及び第2のSOI層1831の間、並びにサイドウォール絶縁層1818及び第3のSOI層1841の間に残る。20

#### 【0215】

なお、ソース領域又はドレイン領域として機能する高濃度不純物領域を低抵抗化するため、シリサイド層を形成してもよい。シリサイド層としては、コバルトシリサイド若しくはニッケルシリサイドを適用すれば良い。SOI層の膜厚が薄い場合には、高濃度不純物領域が形成されたSOI層の底部までシリサイド反応を進めてフルシリサイド化しても良い。

#### 【0216】

次に、基板1800全面に絶縁層1808を形成した後、該絶縁層1808を選択的にエッチングして、表示部1820の第1のSOI層1821に形成された高濃度不純物領域1826に達する開口を形成する。また、第1の駆動回路部1830の第2のSOI層1831、第3のSOI層1841に形成された高濃度不純物領域1836、高濃度不純物領域1846にそれぞれ達する開口を形成する。そして、該開口を埋め込むように導電層1819を形成する。また、端子領域1870に端子電極1874を形成する(図20(B)参照)。30

#### 【0217】

絶縁層1808は、CVD法やスパッタリング法、ALD法、塗布法等により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の酸素若しくは窒素を含む無機絶縁材料や、DLC(ダイヤモンドライクカーボン)等の炭素を含む絶縁材料、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機絶縁材料またはシロキサン樹脂等のシロキサン材料を用いて形成する。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、絶縁層1808は、CVD法やスパッタリング法、ALD法を用いて絶縁層を形成した後、当該絶縁層に酸素雰囲気下又は窒素雰囲気下でプラズマ処理を行ってもよい。ここでは絶縁層1808は単層構造の例を示すが、2層以上の積層構造としてもよい。また、無機絶縁層や、有機絶縁層を組み合わせて形成してもよ4050

い。例えば、基板 1800 全面にパッシベーション層として機能できる窒化シリコン膜や窒化酸化シリコン膜を形成し、その上層に平坦化層として機能できるリンシリケートガラス (PSG) やボロンリンシリケートガラス (BPSG) を材料に用いた絶縁層を形成することができる。

#### 【0218】

導電層 1819 は、ソース電極又はドレイン電極として機能する電極として機能する。導電層 1819 は、絶縁層 1808 に形成された開口を介して、第 1 の SOI 層 1821 、第 2 の SOI 層 1831 又は第 3 の SOI 層 1841 と電気的に接続される。

#### 【0219】

導電層 1819 は、CVD 法やスパッタリング法を用いて、アルミニウム (Al) 、タングステン (W) 、チタン (Ti) 、タンタル (Ta) 、モリブデン (Mo) 、ニッケル (Ni) 、白金 (Pt) 、銅 (Cu) 、金 (Au) 、銀 (Ag) 、マンガン (Mn) 、ネオジム (Nd) 、炭素 (C) 、シリコン (Si) 等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電層を単層構造又は積層構造で形成した後、当該導電層を選択的にエッチングして形成することができる。アルミニウムを含む合金材料としては、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素とシリコンの一方又は両方とを含む合金材料があげられる。また、タングステンを含む化合物材料としては、例えばタングステンシリサイドが挙げられる。導電層 1819 は、例えば、バリア層とアルミニウムシリコン (Al - Si) 層とバリア層の積層構造、バリア層とアルミニウムシリコン (Al - Si) 層と窒化チタン (TiN) 層とバリア層の積層構造を採用することができる。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、ソース電極又はドレイン電極として機能する導電層を形成する材料として最適である。また、ソース電極又はドレイン電極として機能する導電層を、上層と下層にバリア層を設けた積層構造とすると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができるため好ましい。

#### 【0220】

端子領域 1870 に形成される端子電極 1874 は、後に形成される FPC 等の外部入力端子と第 1 の駆動回路部 1830 及び第 2 の駆動回路部 1850 とを電気的に接続させるための電極として機能する。ここでは、導電層 1819 と同一の材料を用いた同一層で端子電極 1874 を形成する例を示している。

#### 【0221】

以上で、表示部 1820 に第 1 の SOI 層 1821 を有するトランジスタが形成された画素回路部 1828 が形成される。また、第 1 の駆動回路部 1830 に第 2 の SOI 層 1831 を有するトランジスタ及び第 3 の SOI 層 1841 を有するトランジスタが形成された周辺回路部 1838 が形成される。

#### 【0222】

次に、表示部 1820 及び第 1 の駆動回路部 1830 上に絶縁層 1809 を形成する。そして、表示部 1820 上に形成された絶縁層 1809 を選択的にエッチングして、画素回路部 1828 に形成されたトランジスタの導電層 1819 に達する開口を形成する。その後、該開口を埋め込むように画素電極 1860 を形成する (図 20 (C) 参照)。

#### 【0223】

絶縁層 1809 は、表示部 1820 及び第 1 の駆動回路部 1830 の凹凸を平滑化して、平坦な表面を形成できる平坦化層を形成することができる。例えば、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機絶縁材料またはシロキサン樹脂等のシロキサン材料を用いて形成することができる。ここでは絶縁層 1809 は単層構造の例を示すが、2 層以上の積層構造としてもよい。積層構造にする場合、例えば、有機樹脂などを上層にし、酸化シリコン、窒化シリコンまたは酸化窒化シリコン等の無機絶縁層を下層にした積層構造、又は無機絶縁層で有機絶縁層を挟持

10

20

30

40

50

する構造とすることができます。なお、絶縁層 1809 は基板全面に形成した後、所望の領域（ここでは表示部 1820 及び第 1 の駆動回路部 1830）以外を選択的にエッティングして形成することができる。また、絶縁層 1809 は、各種印刷法（スクリーン印刷、平版印刷、凸版印刷、グラビア印刷等）、液滴吐出法、ディスペンサ法等を用いて選択的に形成することもできる。

#### 【0224】

画素電極 1860 は、本実施の形態では反射電極として機能する。よって、反射性のある導電性材料を用いて形成する。このような材料としては、タンタル（Ta）、タングステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、クロム（Cr）、銀（Ag）等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いることができる。なお、他に反射層を形成する場合、若しくは透過型液晶表示装置とする場合には、画素電極を透光性を有する導電材料を用いて形成すればよい。透光性を有する導電性材料としては、インジウム錫酸化物（ITO）、酸化シリコンを含むインジウム錫酸化物（ITSO）、酸化亜鉛（ZnO）、酸化インジウム亜鉛（IZO）、又はガリウムを添加した酸化亜鉛（GZO）等を用いることができる。

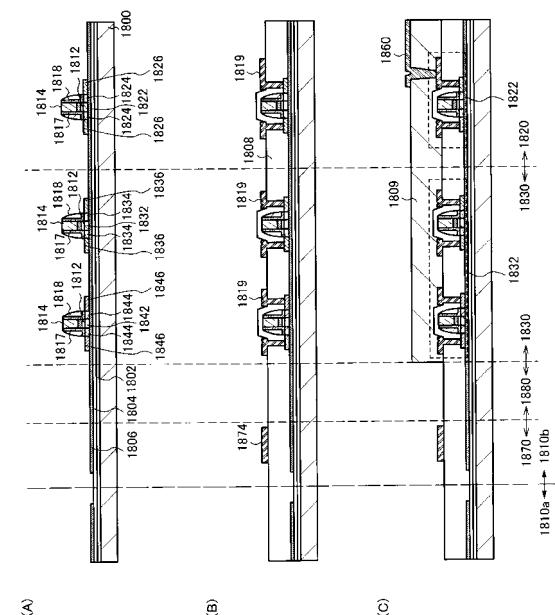

#### 【0225】

次に、スペーサ 1886 を形成した後、画素電極 1860 及びスペーサ 1886 を覆うように配向膜 1882 を形成する。次に、表示部 1820 及び第 1 の駆動回路部 1830、第 2 の駆動回路部 1850 を囲うようにシール材 1880 を形成する（図 21（A）参照）。

10

20

#### 【0226】

スペーサ 1886 は、エポキシ、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の有機絶縁材料、若しくは酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の無機絶縁材料を用いて、単層構造又は積層構造で形成することができる。本実施の形態ではスペーサ 1886 として柱状スペーサを形成するため、基板全面に絶縁層を形成した後、エッティング加工して所望の形状のスペーサを得る。なお、スペーサ 1886 の形状は特に限定されず、球状のスペーサを散布してもよい。スペーサ 1886 により、セルギャップを保持することができる。

#### 【0227】

配向膜 1882 は、利用する液晶の動作モードに対応して材料を選択すればよく、液晶を一定方向に配列させることができ可能な層を形成する。例えばポリイミド、ポリアミド等の材料を用いて形成し、配向処理を行うことで配向膜として機能させることができる。配向処理としては、ラビングや、紫外線等の光照射などを行えばよい。配向膜 1882 の形成方法は特に限定されないが、各種印刷法や液滴吐出法を用いると、絶縁層 1809 上に選択的に形成することができる。

30

#### 【0228】

シール材 1880 は、表示装置完成後、表示領域を少なくとも囲うように形成する。本実施の形態では、表示部 1820、第 1 の駆動回路部 1830 及び第 2 の駆動回路部 1850 の周辺を囲うように枠状のシールパターンを形成する。シール材 1880 としては、熱硬化樹脂や光硬化樹脂を用いることができる。なお、シール材にフィラーを含ませることでセルギャップを保持させることもできる。シール材 1880 は、後に対向電極、カラーフィルター等設けられた基板と封止する際に、光照射、加熱処理等を行って硬化を行う。

40

#### 【0229】

シール材 1880 に囲まれた領域に液晶層 1884 を形成する。また、カラーフィルター 1889、対向電極 1888、配向膜 1887 が順次積層された第 2 の基板 1890 と第 1 の基板 1800 を貼り合わせる（図 21（B）参照）。

#### 【0230】

液晶層 1884 は、所望の液晶材料を用いて形成する。例えば、液晶層 1884 は、シール材 1880 で形成された枠状のシールパターン内に液晶材料を滴下して形成すること

50

ができる。液晶材料の滴下は、ディスペンサ法や液滴吐出法を用いて行えばよい。なお、液晶材料は予め減圧下で脱気しておくか、滴下後に減圧下で脱気することが好ましい。また、液晶材料の滴下の際に不純物等混入しないように、不活性雰囲気下で行うことが好ましい。また、液晶材料を滴下して液晶層1884を形成した後、第1の基板1800及び第2の基板1890を貼り合わせるまでは、液晶層1884に気泡等入らないように減圧下で行うことが好ましい。

#### 【0231】

また、液晶層1884は、第1の基板1800と第2の基板1890を貼り合わせた後、シール材1880の枠状パターン内に、毛細管現象を利用して液晶材料を注入して形成することもできる。この場合、あらかじめシール材等に液晶の注入口となる部分を形成しておく。なお、液晶材料は、減圧下で注入を行うことが好ましい。10

#### 【0232】

第1の基板1800と第2の基板1890は、対向させて密着させた後、シール材1880を硬化させて貼り合わせることができる。このとき、第2の基板1890に設けられた配向膜1887と、第1の基板1800に設けられた配向膜1882とで、液晶層1884が挟持される構造となるように貼り合わせる。なお、第1の基板1800と第2の基板1890の貼り合わせ、及び液晶層1884の形成を行った後、加熱処理を行って液晶層1884の配向乱れを修正することも可能である。

#### 【0233】

第2の基板1890としては、透光性を有する基板を用いる。例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラス等の各種ガラス基板、石英基板、セラミック基板、サファイヤ基板等を用いることができる。20

#### 【0234】

第2の基板1890上には、貼り合わせる前に、カラーフィルター1889、対向電極1888、配向膜1887を順に形成しておく。なお、第2の基板1890には、カラーフィルター1889の他にブラックマトリクスを設けてもよい。また、カラーフィルター1889は第2の基板1890の外側に設けてもよい。また、モノカラー表示とする場合は、カラーフィルター1889を設けなくともよい。また、シール材を第2の基板1890側に設けてもよい。なお、シール材を第2の基板1890側に設ける場合は、液晶材料は第2の基板1890に設けられたシール材の枠状パターン内に滴下する。30

#### 【0235】

対向電極1888は、インジウム錫酸化物(ITO)、酸化シリコンを含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、又はガリウムを添加した酸化亜鉛(GZO)等の透光性を有する導電材料を用いて形成することができる。配向膜1887は、上記配向膜1882と同様に形成することができる。

#### 【0236】

以上により、第1の基板1800と第2の基板1890との間に、液晶層1884を含む表示部1820、第1の駆動回路部1830及び第2の駆動回路部1850が封止された構造が得られる。なお、表示部1820及び第1の駆動回路部1830、第2の駆動回路部1850に形成される回路部には、トランジスタの他、抵抗や、コンデンサなどを同時に作製してもよい。また、トランジスタの構造は特に限定されない。例えば、1つのSOI層に対して複数のゲートを設けたマルチゲート構造とすることもできる。40

#### 【0237】

次に、貼り合わせた第1の基板1800及び第2の基板1890を分断する。そして、第2の基板1890に偏光板1892を設け、端子電極1874に異方性導電層1876を介して外部入力端子1878を接続する(図22参照)。

#### 【0238】

なお、透過型の液晶表示装置とする場合は、第1の基板1800の外側(液晶層1884等を封止していない面側)にも偏光板を設ければよい。また、偏光板の他、位相差版、反射防止膜などの光学フィルムなどを設けてもよい。50

**【 0 2 3 9 】**

外部入力端子 1878 は外部からの信号（例えばビデオ信号、クロック信号、スタート信号、リセット信号等）や電位を伝達する役目を担う。ここでは、外部入力端子 1878 として FPC を接続する。なお、端子電極 1874 は、第 1 の駆動回路部 1830 及び第 2 の駆動回路部 1850 と電気的に接続されているものとする。

**【 0 2 4 0 】**

以上により液晶表示装置を得ることができる。なお、反射型の液晶表示装置の場合、外光（太陽光や室内光）などをを利用して表示を行うことができるが、冷陰極管又は LED 素子等の光源や導光板等で構成されるフロントライトや反射シート等を設けてもよい。フロントライトは表示装置の視認側に設けることができる。フロントライトを設けることで、十分な外光が得られない場合でも、鮮明な表示を行うことができる。10

**【 0 2 4 1 】**

また、透過型の液晶表示装置若しくは半透過型の液晶表示装置とする場合は、冷陰極管又は LED 素子等の光源や導光板や反射シート等で構成されるバックライトを設ける。バックライトは、表示装置の視認側と反対側（背面側）に設ける。透過型の液晶表示装置の場合は、光源からの光を視認側に透過させて、表示を行うことができる。

**【 0 2 4 2 】**

なお、本実施の形態は、実施の形態 1 乃至 6 と適宜組み合わせて用いることができる。

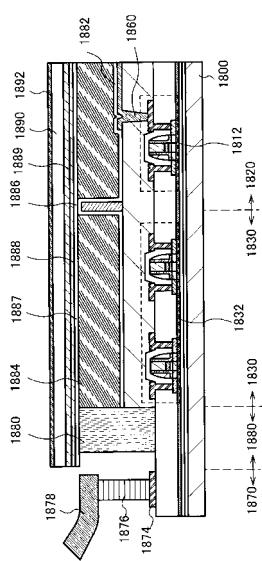

**【 0 2 4 3 】****（実施の形態 8 ）**

本発明の液晶表示装置を用いた電子機器について、図 23 を参照して説明する。20

**【 0 2 4 4 】**

本発明の液晶表示装置を用いた電子機器として、ビデオカメラやデジタルカメラなどのカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。

**【 0 2 4 5 】**

図 23 (A) はテレビ受像器又はパーソナルコンピュータのモニターである。筐体 2001、支持台 2002、表示部 2003、スピーカー部 2004、ビデオ入力端子 2005 等を含む。表示部 2003 には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現したテレビ受像器又はパーソナルコンピュータのモニターを提供することができる。30

**【 0 2 4 6 】**

図 23 (B) はデジタルカメラである。本体 2101 の正面部分には受像部 2103 が設けられており、本体 2101 の上面部分にはシャッターボタン 2106 が設けられている。また、本体 2101 の背面部分には、表示部 2102、操作キー 2104、及び外部接続ポート 2105 が設けられている。表示部 2102 には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現したデジタルカメラを提供することができる。40

**【 0 2 4 7 】**

図 23 (C) はノート型パーソナルコンピュータである。本体 2201 には、キーボード 2204、外部接続ポート 2205、ポインティングデバイス 2206 が設けられている。また、本体 2201 には、表示部 2203 を有する筐体 2202 が取り付けられている。表示部 2203 には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現したノート型パーソナルコンピュータを提供することができる。

**【 0 2 4 8 】**

10

20

30

40

50

図23(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。表示部2302にはアクティブマトリクス表示装置が設けられている。表示部2302には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現したモバイルコンピュータを提供することができる。

#### 【0249】

図23(E)は画像再生装置である。本体2401には、表示部2404、記録媒体読み込み部2405及び操作キー2406が設けられている。また、本体2401には、スピーカー部2407及び表示部2403それぞれを有する筐体2402が取り付けられている。表示部2403及び表示部2404それぞれには、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現した画像再生装置を提供することができる。

10

#### 【0250】

図23(F)は電子書籍である。本体2501には操作キー2503が設けられている。また、本体2501には複数の表示部2502が取り付けられている。表示部2502には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現した電子書籍を提供することができる。

#### 【0251】

図23(G)はビデオカメラであり、本体2601には外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、及び接眼部2610が設けられている、また、本体2601には、表示部2602を有する筐体2603が取り付けられている。表示部2602には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現したビデオカメラを提供することができる。

20

#### 【0252】

図23(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。表示部2703には、本発明の液晶表示装置が用いられている。本発明の液晶表示装置を有することにより、高速応答・高画質を実現した携帯電話を提供することができる。

30

#### 【0253】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。なお、本実施の形態は、実施の形態1乃至7と適宜組み合わせて用いることができる。

#### 【図面の簡単な説明】

#### 【0254】

【図1】本発明の駆動方法を示す図。

【図2】従来の駆動方法と本発明の駆動方法を比較した図。

【図3】従来の駆動方法と本発明の駆動方法を比較した図。

【図4】本発明の駆動方法を示す図。

【図5】本発明の駆動方法を示す図。

【図6】本発明のアクティブマトリクス基板の作製工程を示す図。

【図7】本発明のアクティブマトリクス基板の作製工程を示す図。

【図8】本発明のアクティブマトリクス基板の作製工程を示す図。

【図9】本発明の液晶表示装置の作製工程を示す図。

【図10】本発明の液晶表示装置の上面を示す図。

【図11】本発明の液晶表示装置の断面を示す図。

【図12】本発明のSOI基板を示す図。

【図13】本発明のSOI基板を示す図。

【図14】本発明のSOI基板を示す図。

10

20

30

40

50

【図15】本発明のSOI基板の作製工程を示す図。

【図16】本発明のSOI基板の作製工程を示す図。

【図17】本発明のSOI基板の作製工程を示す図。

【図18】本発明の液晶表示装置を示す図。

【図19】本発明の液晶表示装置の作製工程を示す図。

【図20】本発明の液晶表示装置の作製工程を示す図。

【図21】本発明の液晶表示装置の作製工程を示す図。

【図22】本発明の液晶表示装置を示す図。

【図23】本発明の電子機器を示す図。

【図24】信号電圧の大小関係をいくつかのパターンに分けて示した図。

10

## 【符号の説明】

## 【0255】

|     |                   |    |

|-----|-------------------|----|

| 100 | 三角形               |    |

| 110 | ベース基板             |    |

| 400 | バックライト消灯期間        |    |

| 500 | 目標応答量             |    |

| 510 | 目標応答量             | 20 |

| 520 | 目標応答量             |    |

| 530 | 目標応答量             |    |

| 600 | 基板                |    |

| 602 | 下地膜               |    |

| 604 | 半導体膜              |    |

| 608 | 線状レーザー            |    |

| 610 | 結晶性半導体膜           |    |

| 612 | 島状半導体膜            |    |

| 614 | 島状半導体膜            |    |

| 618 | 絶縁膜               |    |

| 620 | 導電膜               |    |

| 622 | 導電膜               |    |

| 624 | 上層ゲート電極           | 30 |

| 630 | 下層ゲート電極           |    |

| 636 | ゲート電極             |    |

| 640 | ゲート電極             |    |

| 642 | チャネル形成領域          |    |

| 644 | ドレイン領域            |    |

| 646 | チャネル形成領域          |    |

| 650 | ゲート絶縁膜            |    |

| 656 | ドレイン領域            |    |

| 658 | 低濃度不純物領域          |    |

| 664 | 層間絶縁膜             | 40 |

| 666 | 層間絶縁膜             |    |

| 668 | 配線                |    |

| 674 | 配線                |    |

| 676 | 配線                |    |

| 678 | nチャネル型TFT         |    |

| 680 | pチャネル型TFT         |    |

| 682 | 画素TFT (nチャネル型TFT) |    |

| 684 | C MOS回路           |    |

【図1】

(B)

【図2】

(B)

【図3】

(B)

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

(A)

(B)

【図14】

(A)

(B)

【図15】

(A)

(B)

(C)

【図16】

(A)

(B)

【図17】

(B)

(C)

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

---

フロントページの続き

(51)Int.Cl.

| F I                  |

|----------------------|

| G 0 9 G 3/20 6 2 1 M |

| G 0 9 G 3/20 6 6 0 V |

| G 0 2 F 1/133 5 7 5  |

| G 0 2 F 1/133 5 5 0  |

| G 0 9 G 3/20 6 4 1 P |

(56)参考文献 特開2003-241721(JP,A)

特開2006-267360(JP,A)

特開2002-116743(JP,A)

特開2006-301563(JP,A)

特開2004-309657(JP,A)

特開2004-253827(JP,A)

(58)調査した分野(Int.Cl., DB名)

|                           |

|---------------------------|

| G 0 9 G 3 / 0 0 - 3 / 3 8 |

| G 0 2 F 1 / 1 3 3         |