(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3813256号

(P3813256)

(45) 発行日 平成18年8月23日(2006.8.23)

(24) 登録日 平成18年6月9日(2006.6.9)

(51) Int.C1.

F 1

|             |              |                  |      |       |   |

|-------------|--------------|------------------|------|-------|---|

| <b>H03F</b> | <b>3/45</b>  | <b>(2006.01)</b> | H03F | 3/45  | B |

| <b>H03F</b> | <b>3/34</b>  | <b>(2006.01)</b> | H03F | 3/34  | C |

| <b>H03G</b> | <b>11/00</b> | <b>(2006.01)</b> | H03G | 11/00 | Z |

請求項の数 8 (全 19 頁)

(21) 出願番号

特願平8-236474

(22) 出願日

平成8年9月6日(1996.9.6)

(65) 公開番号

特開平10-84233

(43) 公開日

平成10年3月31日(1998.3.31)

審査請求日

平成15年9月4日(2003.9.4)

(73) 特許権者 595138889

日本バーブラウン株式会社

神奈川県横浜市港北区新横浜二丁目3番地

12 新横浜スクエアビル

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100071124

弁理士 今井 庄亮

(74) 代理人 100076691

弁理士 増井 忠式

(74) 代理人 100075236

弁理士 栗田 忠彦

(74) 代理人 100075270

弁理士 小林 泰

最終頁に続く

(54) 【発明の名称】関数演算回路用の波形整形回路

## (57) 【特許請求の範囲】

## 【請求項 1】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、前記出力端子と、前記非反転入力端子及び前記反転入力端子の内の一方である関係する入力端子と、に接続した波形整形回路手段を含み、該波形整形回路手段は、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧・電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧・電流変換手段と、

を備え、

前記波形整形手段は、1つのクリップ回路を構成し、

該クリップ回路は、1つのMOSトランジスタを含み、該MOSトランジスタは、ゲート電極を、前記演算増幅器の前記出力端子に接続し、ドレイン電極・ソース電極路を、前記第1及び第2電源電圧端子の内の所定の一方と前記演算増幅器の前記入力端子との間に

接続し、これにより前記MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、残りの第2部分が前記電圧-電流変換手段を構成し、

前記クリップ回路は、更に少なくとも1つのダイオード接続した追加のMOSトランジスタを含み、該追加MOSトランジスタは、ドレイン電極-ソース電極路を、前記演算増幅器の前記入力端子と前記MOSトランジスタの前記ドレイン電極-ソース電極路との間に、該電極路と直列に接続したこと、

を特徴とする波形整形回路。

### 【請求項2】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、前記出力端子と、前記非反転入力端子及び前記反転入力端子の内の一方向である関係する入力端子と、に接続した波形整形回路手段を含み、該波形整形回路手段は、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧-電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧-電流変換手段と、

を備え、

前記波形整形手段は、1対のクリップ回路から成るリミッタ回路を構成し、該リミット回路の前記1対のクリップ回路は、前記所定のしきい値として、互いに異なった第1と第2の所定のしきい値を有し、

前記クリップ回路は、1つのMOSトランジスタを含み、該MOSトランジスタは、ゲート電極を、前記演算増幅器の前記出力端子に接続し、ドレイン電極-ソース電極路を、前記第1及び第2電源電圧端子の内の一方向と前記演算増幅器の前記入力端子との間に接続し、これにより前記MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、残りの第2部分が前記電圧-電流変換手段を構成し、

前記クリップ回路は、更に少なくとも1つのダイオード接続した追加のMOSトランジスタを含み、該追加MOSトランジスタは、ドレイン電極-ソース電極路を、前記演算増幅器の前記入力端子と前記MOSトランジスタの前記ドレイン電極-ソース電極路との間に、該電極路と直列に接続したこと、

を特徴とする波形整形回路。

### 【請求項3】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、前記出力端子と、前記非反転入力端子及び前記反転入力端子の内の一方向である関係する入力端子と、に接続した波形整形回路手段を含み、該波形整形回路手段は、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧-電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧-電流変換手段と、

を備え、

10

20

30

40

50

前記波形整形手段は、1つのクリップ回路を構成し、

前記クリップ回路は、1対の第1と第2のMOSトランジスタを有する電流スイッチを含み、

該電流スイッチは、前記第1及び第2電源電圧端子と前記演算増幅器の前記入力端子との間に接続しており、かつ前記第1及び第2電源電圧端子の内的一方とその他の間に第1の電流路を有し、そして前記一方の電源電圧端子と前記演算増幅器の前記入力端子との間に第2の電流路を有し、

前記第1電流路は、前記第1MOSトランジスタのドレイン電極 - ソース電極路を含んでおり、該第1MOSトランジスタのゲート電極は前記演算増幅器の前記出力端子に接続し、

前記第2電流路は、前記第2MOSトランジスタのドレイン電極 - ソース電極路を含み、該第2MOSトランジスタのゲート電極は前記所定しきい値を受けるように接続し、

前記電流スイッチは、前記出力端子電圧と前記所定しきい値との間の大小関係に依存した前記第1電流路及び前記第2電流路の内的一方のみを開くように動作し、これによって、前記電流スイッチに含まれる前記第1MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、前記電流スイッチの残りの第2部分が前記電圧 - 電流変換手段を構成したこと、

を特徴とする波形整形回路。

#### 【請求項4】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、前記出力端子と、前記非反転入力端子及び前記反転入力端子の内的一方である関係する入力端子と、に接続した波形整形回路手段を含み、該波形整形回路手段は、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧 - 電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧 - 電流変換手段と、

を備え、

前記波形整形手段は、1対のクリップ回路から成るリミッタ回路を構成し、該リミット回路の前記1対のクリップ回路は、前記所定のしきい値として、互いに異なった第1と第2の所定のしきい値を有し、

前記クリップ回路は、1対の第1と第2のMOSトランジスタを有する電流スイッチを含み、

該電流スイッチは、前記第1及び第2電源電圧端子と前記演算増幅器の前記入力端子との間に接続しており、かつ前記第1及び第2電源電圧端子の内的一方とその他の間に第1の電流路を有し、そして前記一方の電源電圧端子と前記演算増幅器の前記入力端子との間に第2の電流路を有し、

前記第1電流路は、前記第1MOSトランジスタのドレイン電極 - ソース電極路を含んでおり、該第1MOSトランジスタのゲート電極は前記演算増幅器の前記出力端子に接続し、

前記第2電流路は、前記第2MOSトランジスタのドレイン電極 - ソース電極路を含み、該第2MOSトランジスタのゲート電極は前記所定しきい値を受けるように接続し、

前記電流スイッチは、前記出力端子電圧と前記所定しきい値との間の大小関係に依存した前記第1電流路及び前記第2電流路の内的一方のみを開くように動作し、これによって、前記電流スイッチに含まれる前記第1MOSトランジスタの内の前記ゲート電極を含む

10

20

30

40

50

第1部分が、前記電圧伝達手段を構成し、前記電流スイッチの残りの第2部分が前記電圧 - 電流変換手段を構成したこと、

を特徴とする波形整形回路。

【請求項5】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と非反転出力端子及び反転出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、

- A. 前記非反転出力端子と前記反転入力端子とに接続した第1の波形整形回路手段と、

- B. 前記反転出力端子と前記非反転入力端子とに接続した第2の波形整形回路手段と、

を含み、 10

前記第1及び第2の波形整形回路手段の各々は、関係する前記出力端子及び前記入力端子に関して、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧 - 電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧 - 電流変換手段と、 20

を備え、

前記波形整形手段は、1つのクリップ回路を構成し、

前記クリップ回路は、1つのMOSトランジスタを含み、該MOSトランジスタは、ゲート電極を、前記演算増幅器の前記出力端子に接続し、ドレイン電極 - ソース電極路を、前記第1及び第2電源電圧端子の内の所定の一方と前記演算増幅器の前記入力端子との間に接続し、これにより前記MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、残りの第2部分が前記電圧 - 電流変換手段を構成し、

前記クリップ回路は、更に少なくとも1つのダイオード接続した追加のMOSトランジスタを含み、該追加MOSトランジスタは、ドレイン電極 - ソース電極路を、前記演算増幅器の前記入力端子と前記MOSトランジスタの前記ドレイン電極 - ソース電極路との間に、該電極路と直列に接続したこと、 30

を特徴とする波形整形回路。

【請求項6】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と非反転出力端子及び反転出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、

- A. 前記非反転出力端子と前記反転入力端子とに接続した第1の波形整形回路手段と、

- B. 前記反転出力端子と前記非反転入力端子とに接続した第2の波形整形回路手段と、

を含み、 40

前記第1及び第2の波形整形回路手段の各々は、関係する前記出力端子及び前記入力端子に関して、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧 - 電流変換手段であって、前記出力端子電圧の大きさ 50

に対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧・電流変換手段と、

を備え、

前記波形整形手段は、1対のクリップ回路から成るリミッタ回路を構成し、該リミット回路の前記1対のクリップ回路は、前記所定のしきい値として、互いに異なった第1と第2の所定のしきい値を有し、

前記クリップ回路は、1つのMOSトランジスタを含み、該MOSトランジスタは、ゲート電極を、前記演算増幅器の前記出力端子に接続し、ドレイン電極・ソース電極路を、前記第1及び第2電源電圧端子の内の所定の一方と前記演算増幅器の前記入力端子との間に接続し、これにより前記MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、残りの第2部分が前記電圧・電流変換手段を構成し、

10

前記クリップ回路は、更に少なくとも1つのダイオード接続した追加のMOSトランジスタを含み、該追加MOSトランジスタは、ドレイン電極・ソース電極路を、前記演算増幅器の前記入力端子と前記MOSトランジスタの前記ドレイン電極・ソース電極路との間に、該電極路と直列に接続したこと、

を特徴とする波形整形回路。

#### 【請求項7】

関数演算回路に使用する波形整形回路であって、前記関数演算回路は、非反転入力端子及び反転入力端子と非反転出力端子及び反転出力端子とを有する演算増幅器を有しており

20

、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、

- A. 前記非反転出力端子と前記反転入力端子とに接続した第1の波形整形回路手段と、

- B. 前記反転出力端子と前記非反転入力端子とに接続した第2の波形整形回路手段と、

を含み、

前記第1及び第2の波形整形回路手段の各々は、関係する前記出力端子及び前記入力端子に関して、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

30

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧・電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧・電流変換手段と、

を備え、

前記波形整形手段は、1つのクリップ回路を構成し、

前記クリップ回路は、1対の第1と第2のMOSトランジスタを有する電流スイッチを含み、

40

該電流スイッチは、前記第1及び第2電源電圧端子と前記演算増幅器の前記入力端子との間に接続しており、かつ前記第1及び第2電源電圧端子の内の一方とその他方との間に第1の電流路を有し、そして前記一方の電源電圧端子と前記演算増幅器の前記入力端子との間に第2の電流路を有し、

前記第1電流路は、前記第1MOSトランジスタのドレイン電極・ソース電極路を含んでおり、該第1MOSトランジスタのゲート電極は前記演算増幅器の前記出力端子に接続し、

前記第2電流路は、前記第2MOSトランジスタのドレイン電極・ソース電極路を含み、該第2MOSトランジスタのゲート電極は前記所定しきい値を受けるように接続し、

前記電流スイッチは、前記出力端子電圧と前記所定しきい値との間の大小関係に依存し

50

た前記第1電流路及び前記第2電流路の内の方のみを開くように動作し、これによつて、前記電流スイッチに含まれる前記第1MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、前記電流スイッチの残りの第2部分が前記電圧-電流変換手段を構成したこと、

を特徴とする波形整形回路。

#### 【請求項8】

関数演算回路に使用する波形整形回路であつて、前記関数演算回路は、非反転入力端子及び反転入力端子と非反転出力端子及び反転出力端子とを有する演算増幅器を有しており、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記波形整形回路が、

- A. 前記非反転出力端子と前記反転入力端子とに接続した第1の波形整形回路手段と 10

- 、

- B. 前記反転出力端子と前記非反転入力端子とに接続した第2の波形整形回路手段と 、

- 、

- を含み、

前記第1及び第2の波形整形回路手段の各々は、関係する前記出力端子及び前記入力端子に関して、

イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、

ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧-電流変換手段であつて、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧-電流変換手段と、 20

を備え、

前記波形整形手段は、1対のクリップ回路から成るリミッタ回路を構成し、該リミット回路の前記1対のクリップ回路は、前記所定のしきい値として、互いに異なつた第1と第2の所定のしきい値を有し、

前記クリップ回路は、1対の第1と第2のMOSトランジスタを有する電流スイッチを含み、 30

該電流スイッチは、前記第1及び第2電源電圧端子と前記演算増幅器の前記入力端子との間に接続しており、かつ前記第1及び第2電源電圧端子の内の方とその他の間に第1の電流路を有し、そして前記一方の電源電圧端子と前記演算増幅器の前記入力端子との間に第2の電流路を有し、

前記第1電流路は、前記第1MOSトランジスタのドレイン電極-ソース電極路を含んでおり、該第1MOSトランジスタのゲート電極は前記演算増幅器の前記出力端子に接続し、

前記第2電流路は、前記第2MOSトランジスタのドレイン電極-ソース電極路を含み、該第2MOSトランジスタのゲート電極は前記所定しきい値を受けるように接続し、

前記電流スイッチは、前記出力端子電圧と前記所定しきい値との間の大小関係に依存した前記第1電流路及び前記第2電流路の内の方のみを開くように動作し、これによつて、前記電流スイッチに含まれる前記第1MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、前記電流スイッチの残りの第2部分が前記電圧-電流変換手段を構成したこと、 40

を特徴とする波形整形回路。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、クリップ又はリミット等を行う波形整形回路の分野に関し、特に関数演算回路に使用するのに適した波形整形回路に関するものである。 50

**【0002】****【従来の技術】**

電気回路における波形整形回路として、信号波形の上部又は下部の一方を制限するクリップ回路、あるいはそれらの双方を制限する1対のクリップ回路から成るリミッタ回路等がある。後者のリミッタ回路としては、ある回路の出力端子間即ち負荷に並列に、ダイオードとリミットレベルを定める電源との直列接続から各々成る1対の回路を、互いに並列にしかもそれらのダイオードの極性が反対になるように接続したものが知られている。

**【0003】**

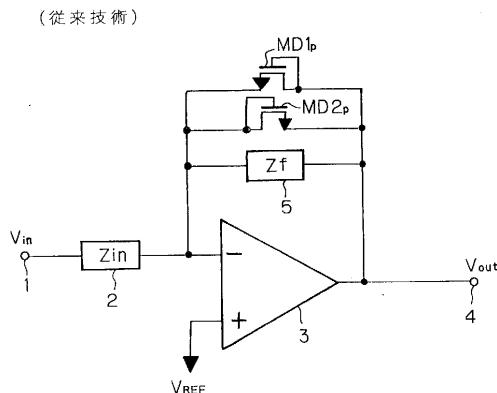

半導体集積回路においては、そのようなリミッタ回路を実現する場合、上記各ダイオードとして、MOSトランジスタをダイオード接続したもの（以下、MOSダイオードと呼ぶ）を使用することができる。また、リミッタ回路を配置する位置は、例えば演算増幅器を使用した関数演算回路においては、その演算増幅器の出力端子と接地との間即ち負荷に並列に設けたり、あるいはその演算増幅器の出力端子から非反転入力端子への帰還回路に並列に設けたりすることができる。この後者の回路は、図16に示しており、 $Z_{in}$ は入力回路インピーダンス、 $Z_f$ は帰還回路インピーダンスであり、上記のようにリミッタ回路を成す1対のN型MOSダイオードMD1<sub>p</sub>及びMD2<sub>p</sub>はこの帰還回路に並列になっている。この図に示したリミッタの場合、リミットレベルは、N型MOSダイオード自身のしきい値電圧により定まり、これにより演算増幅器の出力電圧は、基準電圧（演算増幅器の非反転入力端子の電位であり、例えば接地電位）の±しきい値電圧の範囲にリミットされる。

10

20

**【0004】****【発明が解決しようとする課題】**

上記のような演算増幅器に関連して使用するリミッタにおいては、リミット動作のオン・オフ・スイッチング速度は、リミッタ回路に並列の回路のインピーダンス、即ち、負荷インピーダンスもしくは図16の例では帰還回路インピーダンス $Z_f$ により影響を受け易い構成となっている。そのため、それら並列インピーダンスによっては、リミッタのスイッチング速度が低下するという問題がある。また、リミッタ動作のオン・オフ遷移状態、即ちリミッタのMOSダイオードのしきい値近傍においては、MOSダイオードの等価インピーダンスが、並列インピーダンス、即ち負荷インピーダンスもしくは帰還インピーダンスに作用を及ぼすため、それらインピーダンスの定数を変化させることになる。これにより、演算増幅器を使用した関数演算回路においては、その関数演算結果が不正確になるという問題がある。

30

**【0005】**

更に、上記リミッタにおいては、演算増幅器の出力電圧を直接リミットする構造であるため、負荷駆動力の高い出力電圧、即ち比較的大きい出力電流を扱う必要があり、従って大電流に耐えられるようMOSダイオードのゲート幅を大きくしなければならない。このことは、半導体集積回路で実現する場合には、より大きなチップ面積を必要とする、という問題がある。

**【0006】**

リミッタに関する上記問題は、クリップ回路においても同様にある。

40

**【0007】**

従って、本発明の目的は、演算増幅器を使用して実現した関数演算回路の帰還回路及びその負荷に対する影響もしくはそれらから受ける影響が最小限となる状態で、波形整形を行うことができる関数演算回路用の波形整形回路を提供することである。

**【0008】**

本発明の別の目的は、波形整形を行うためにより小さな電流しか扱わないで済む、関数演算回路用の波形整形回路を提供することである。

**【0009】****【課題を解決するための手段】**

上記の目的を実現するため、本発明によれば、非反転入力端子及び反転入力端子と出力端

50

子とを有する演算増幅器を備えた関数演算回路に使用する波形整形回路は、前記出力端子と、前記非反転入力端子及び前記反転入力端子の内の一方である関係する入力端子と、に接続した波形整形回路手段を含み、該波形整形回路手段は、イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧・電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧・電流変換手段と、を備える。

10

## 【0010】

また、本発明によれば、非反転入力端子及び反転入力端子と非反転出力端子及び反転出力端子とを有する演算増幅器を備えた関数演算回路に使用する波形整形回路は、A. 前記非反転出力端子と前記反転入力端子とに接続した第1の波形整形回路手段と、B. 前記反転出力端子と前記非反転入力端子とに接続した第2の波形整形回路手段と、を含み、前記第1及び第2の波形整形回路手段の各々は、関係する前記出力端子及び前記入力端子に関して、イ) 前記出力端子に接続した入力端と、該入力端とは電気的に絶縁された出力端とを有し、前記出力端子の電圧の大きさを、前記入力端から前記出力端へ、電気的絶縁状態で伝達する電圧伝達手段と、ロ) 前記電圧伝達手段の前記出力端に入力端が接続しており、前記演算増幅器の前記入力端子に出力端が接続した電圧・電流変換手段であって、前記出力端子電圧の大きさに対する所定のしきい値を有しており、前記電圧伝達手段から受けた前記出力端子電圧の大きさと前記所定のしきい値との間の大小関係に依存した大きさの電流を前記入力端子に供給する、前記の電圧・電流変換手段と、を備える。

20

## 【0011】

本発明によれば、前記波形整形手段は、1つのクリップ回路を構成したり、あるいは1対のクリップ回路から成るリミッタ回路を構成することができる。また、後者の場合、前記リミッタ回路の前記1対のクリップ回路は、前記所定のしきい値として、互いに異なった第1と第2の所定のしきい値を有するようになる。

## 【0012】

また、本発明によれば、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記クリップ回路は、1つのMOSトランジスタを含み、該MOSトランジスタは、ゲート電極を、前記演算増幅器の前記出力端子に接続し、ドレイン電極・ソース電極路を、前記第1及び第2電源電圧端子の内の所定の一方と前記演算増幅器の前記入力端子との間に接続し、これにより前記MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、残りの第2部分が前記電圧・電流変換手段を構成するようになる。また、前記クリップ回路は、更に少なくとも1つのダイオード接続した追加のMOSトランジスタを含み、該追加MOSトランジスタは、ドレイン電極・ソース電極路を、前記演算増幅器の前記入力端子と前記MOSトランジスタの前記ドレイン電極・ソース電極路との間に、該電極路と直列に接続するよう構成できる。

30

## 【0013】

また、本発明によれば、前記関数演算回路は、第1及び第2の電源電圧端子を有し、前記クリップ回路は、1対の第1と第2のMOSトランジスタを有する電流スイッチを含み、該電流スイッチは、前記第1及び第2電源電圧端子と前記演算増幅器の前記入力端子との間に接続し、かつ前記第1及び第2電源電圧端子の内の一方とその他の方との間に第1の電流路を有し、そして前記一方の電源電圧端子と前記演算増幅器の前記入力端子との間に第2の電流路を有し、前記第1電流路は、前記第1MOSトランジスタのドレイン電極・ソース電極路を含み、該第1MOSトランジスタのゲート電極は前記演算増幅器の前記出力端子に接続し、前記第2電流路は、前記第2MOSトランジスタのドレイン電極・ソース電極路を含み、該第2MOSトランジスタのゲート電極は前記所定しきい値を受けるよう接続し、前記電流スイッチは、前記出力端子電圧と前記所定しきい値との間の大小関係

40

50

に依存した前記第1電流路及び前記第2電流路の内の一方のみを開くように動作し、これによって、前記電流スイッチに含まれる前記第1MOSトランジスタの内の前記ゲート電極を含む第1部分が、前記電圧伝達手段を構成し、前記電流スイッチの残りの第2部分が前記電圧・電流変換手段を構成するようにできる。

#### 【0014】

本発明によれば、前記関数演算は、反転、加算、微分、積分の内の1つとすることができます。

#### 【0015】

#### 【発明の実施の形態】

次に、本発明の実施形態の幾つかについて、以下に図面を参照して詳細に説明する。

10

#### 【0016】

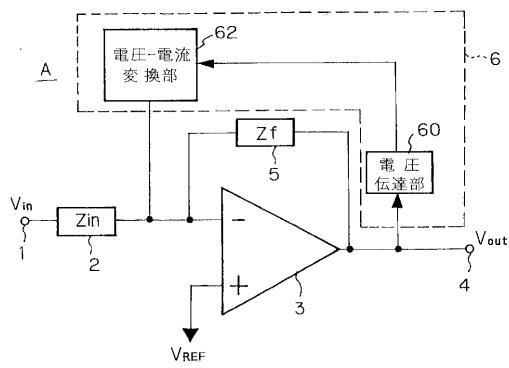

図1は、本発明による波形整形回路を備えた関数演算回路の第1の実施形態を示す回路図であり、これにおいて、波形整形回路は、その基本概念を示すためブロック図で示してある。詳しくは、この関数演算回路Aは、任意の関数演算を行う一般的な形式のものであって、入力電圧 $V_{in}$ を受ける入力端子1と、入力回路2と、差動入力／單一出力の演算増幅器（以下、オペアンプとも記す）3と、出力電圧 $V_{out}$ を発生する出力端子4と、帰還回路5と、を備えている。入力回路2は、入力端子1とオペアンプ3の反転入力端子（-）との間に接続していて、インピーダンス $Z_{in}$ を有している。オペアンプ3の非反転入力端子（+）は、基準電圧 $V_{REF}$ （例えば、接地電位）に接続しており、そしてその出力端子は、関数演算回路Aの出力端子4に接続している。帰還回路5は、オペアンプ3の出力端子と反転入力端子との間に接続していて、インピーダンス $Z_f$ を有している。インピーダンス $Z_{in}$ と $Z_f$ とは、周知のように、所望の関数演算に応じて定めることができる。

20

#### 【0017】

更に、関数演算回路Aは、本発明による波形整形回路6を備えており、これは、関数演算出力である $V_{out}$ に対し所望の波形整形を行うため、オペアンプ3の出力端子と反転入力端子との間に接続している。この波形整形回路6は、電圧伝達部60と、電圧・電流変換部62とから成っている。電圧伝達部60は、入力端がオペアンプの出力端子に接続した出力端が電圧・電流変換部62に接続していて、関数演算出力電圧 $V_{out}$ を、変換部62に“絶縁伝達”する、即ちその出力端子とは電気的に絶縁状態を保ちながら伝達する。その電気的絶縁状態とは、直流通並びに交流的の双方においてである。この絶縁伝達される電圧を受ける変換部62は、出力端がオペアンプの反転入力端子に接続していて、絶縁伝達された電圧の大きさとこの大きさに対する所定のしきい値 $V_{TH}$ との間の大小関係に依存した大きさの電流を、オペアンプの反転入力端子に供給する。しきい値 $V_{TH}$ は、所望の波形整形処理に応じて、その数並びに値を定めることができる。このしきい値 $V_{TH}$ の値の基準は、非反転入力端子の基準電圧 $V_{REF}$ である。波形整形処理の種類の例としては、上側又は下側のクリップ、またその他にリミット等がある。

30

#### 【0018】

本発明による波形整形回路6においては、電圧の絶縁伝達を行う伝達部60が、変換部62の入力端を、出力端子4に接続される負荷（図示せず）並びに帰還回路5から絶縁することにより、負荷インピーダンス並びに帰還インピーダンス $Z_f$ との相互干渉を低減する。これによって、負荷及び帰還回路のインピーダンスによる波形整形動作への影響を最小限にすることができる。また、伝達部60を設けることにより、電圧・電流変換部62は、出力電圧 $V_{out}$ 又は他の関数演算回路内の電圧／電流とは独立の電源を、波形整形処理に使用することができる。これは、波形整形の動作速度を高めるのに有利である。更に、変換部62は、オペアンプ3の出力端子側ではなく入力端子側に出力端が接続する構成であるため、波形整形動作の直接の対象となる信号を、オペアンプによる増幅前の信号とすることができます。これは、増幅後の信号を対象とするのに比べ、波形整形動作速度を更に高めるのに有利となり、また変換部62に必要な回路の能力（容量、サイズを含む）を低いものとするのに有利である。

40

#### 【0019】

50

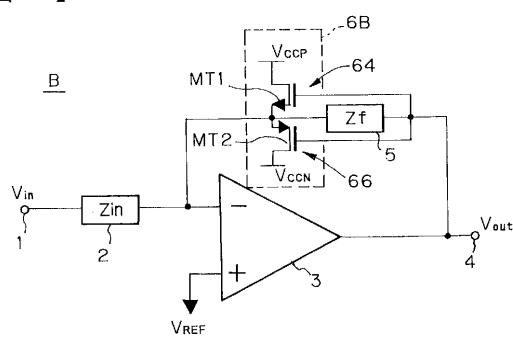

次に、図2を参照して、図1の関数演算回路Aのより具体化した第2の実施形態の関数演算回路Bについて説明する。尚、図2では、図1の回路の要素と同じ要素には、同じ参照符号を付してある。この点については、図2以降の図についてもそれより先の図に対し同様である。

#### 【0020】

図2の関数演算回路Bは、より具体化した波形整形回路6Bを備えている外は、図1の回路と同じであるため、波形整形回路6Bについてのみ詳細に説明する。この波形整形回路6Bは、1対のリミット(又はクリップ)回路64及び66から成るリミッタ回路を構成している。上側リミット(又は上側クリップ)を行うリミット回路64は、1つのN型MOSトランジスタMT1を備えていて、そのドレイン電極は正電源電圧端子V<sub>CCP</sub>に、ソース電極は反転入力端子に、そしてゲート電極は出力端子4に接続している。一方、下側リミット(又は下側クリップ)を行うリミット回路66は、1つのP型MOSトランジスタMT2を備えていて、そのソース電極は反転入力端子に、ドレイン電極は負電源電圧端子V<sub>CCN</sub>に、そしてゲート電極は出力端子4に接続している。MOSトランジスタMT1とMT2とは、それぞれオン・オフ・スイッチングのしきい値電圧V<sub>TH1</sub>とV<sub>TH2</sub>とを有している。従って、リミット回路6Bの上側リミットレベルV<sub>LM1</sub>は(V<sub>REF</sub>+V<sub>TH1</sub>)であり、下側リミットレベルV<sub>LM2</sub>は(V<sub>REF</sub>-V<sub>TH2</sub>)である。尚、MOSトランジスタのしきい値電圧は、調節可能であり、それは例えばソース・基板電圧を可変させることにより行える。1例として、しきい値電圧は、0.6~1.5ボルトの範囲である。尚、MOSトランジスタ自体のしきい値電圧を使用するこの実施形態では、しきい値の設定に追加の素子を必要とせず、従って回路の小型化に適している。10

#### 【0021】

ここで、リミット回路6Bの図1の波形整形回路6に対する対応関係について説明すると、MOSトランジスタMT1及びMT2の各々のゲート電極とその下の酸化物とが電圧伝達部60に対応していて、この伝達部60からの電圧は、MT1及びMT2の各々の酸化膜直下のソース・基板接合部に伝達される。MT1及びMT2の各々の残りの部分は、変換部62に対応している。また、変換部62内のしきい値は、MT1の酸化膜直下のソース・基板接合部によって与えられる。従って、リミッタ回路6Bは、波形整形回路6の1実施形態を構成している。20

#### 【0022】

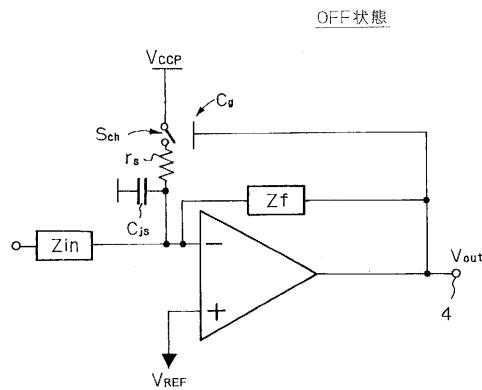

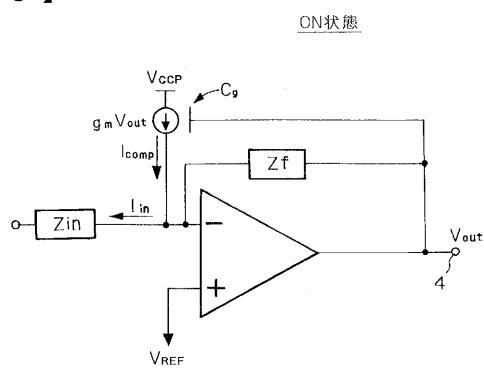

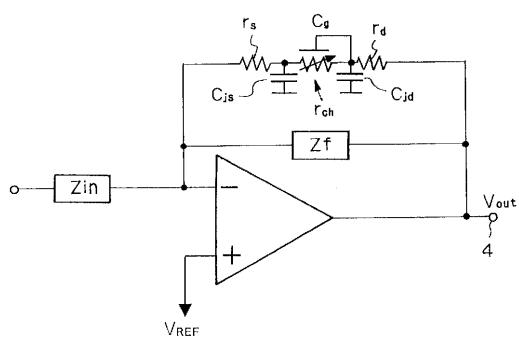

次に、関数演算回路Bの等価回路を示す図3~図5を参照して、リミッタ回路6B部分の動作について説明する。尚、上側リミット回路64と下側リミット回路66とは類似の動作をするため、図3~図5においては、上側リミット回路部分のみの等価回路を示しており、そしてそれらが示す等価回路は、図3がリミット回路のOFF状態、図4がOFF-ON遷移状態、図5がON状態を示している。また、図中、g<sub>m</sub>は、MOSトランジスタのトランスクンダクタンス、C<sub>g</sub>は、MOSゲート容量(ドレイン、ソース、基板全てに対する容量を含む)、S<sub>ch</sub>は、MOSトランジスタのチャンネル抵抗で実現されるスイッチ、r<sub>s</sub>はソース抵抗、C<sub>js</sub>は、ソース・基板接合間の容量である。30

#### 【0023】

まず初めに、図3のOFF状態等価回路を参照すると、上側リミット回路は、電源電圧端子V<sub>CCP</sub>と反転入力端子との間に直列に接続されたチャンネルスイッチS<sub>ch</sub>及びソース抵抗r<sub>s</sub>と、そして、出力端子4に一端が接続しそして他端がチャンネルスイッチS<sub>ch</sub>に関連するが絶縁状態を表すよう概念的に示したゲート容量C<sub>g</sub>と、そして更に、反転入力端子と基板との間に接続したソース・基板接合容量C<sub>js</sub>と、から成っているとみなせる。このとき、即ち、V<sub>out</sub><V<sub>LM1</sub>のとき、チャンネルスイッチS<sub>ch</sub>が開いているため(即ち、チャンネル抵抗が無限大であるため)、リミット動作は生じない。40

#### 【0024】

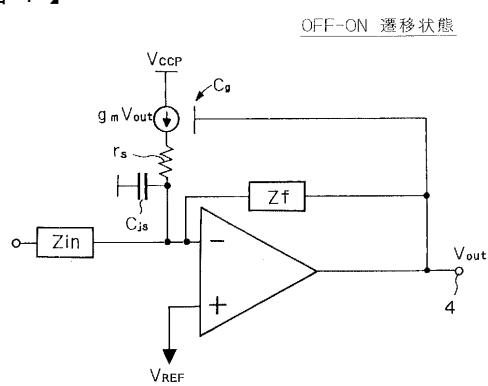

次に、図4のOFF-ON遷移状態の等価回路においては、チャンネルスイッチS<sub>ch</sub>が電流源g<sub>m</sub>V<sub>out</sub>に変化している点、またC<sub>g</sub>が電流源g<sub>m</sub>V<sub>out</sub>に関連している点を除けば、図3のOFF状態等価回路と同じである。この遷移状態においては、チャンネルは導通状50

態となって、電流源が  $r_s$  及び  $C_{js}$  を介して反転入力端子に接続している。

**【0025】**

図5のON状態等価回路においては、 $r_s$  及び  $C_{js}$  は流れる電流に対して無視し得る程度となって、電流源  $g_m V_{out}$  が反転入力端子に直接接続することになる。従って、電流源は、 $V_{out}$  に比例した大きさの補償電流  $I_{comp}$  を反転入力端子に供給することにより、入力電流  $I_{in}$  の過剰の増加分を相殺するように作用する。

**【0026】**

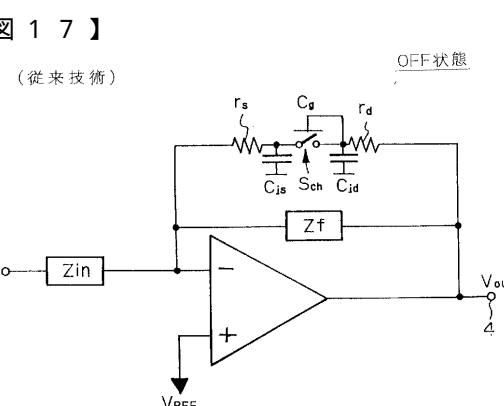

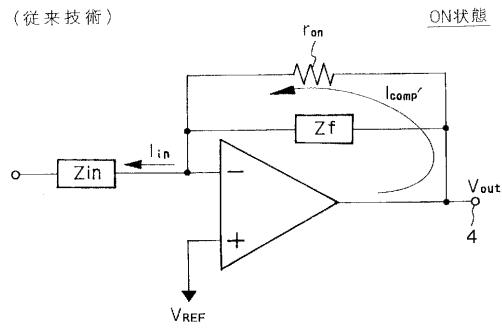

ここで、図2の本発明による関数演算回路Bのリミット回路6Bの特徴をより明確に理解できるようにするため、図16の従来回路の等価回路を示す図17～19を参照する。これらの図17～19においても、比較し易くするため、図16の1つのMOSダイオードMD1<sub>p</sub>から成る上側リミット回路のみの等価回路を、そのOFF状態(図17)、OFF-ON遷移状態(図18)、ON状態(図19)で示している。尚、これらの等価回路において、 $r_d$ はドレイン抵抗、 $C_{jd}$ はドレン - 基板接合間の容量であり、 $r_{ch}$ はチャネル抵抗であり、 $r_{on}$ はMOSダイオードのON抵抗であって  $r_s$  と  $r_d$  と  $r_{ch}$  との和に等しい。また、MOSダイオードであるため、本発明のような電流源  $g_m V_{out}$  は存在しない。

10

**【0027】**

まず初めに、OFF状態等価回路を示す図3と図17とを比較すると、双方とも  $S_{ch}$  が開いているため、図17では出力端子4と反転入力端子との間に  $r_d$  と  $C_{jd}$  とが加わっていても、それら双方の等価回路は同等である。次に、OFF-ON遷移状態等価回路を示す図4と図18とを比較すると、図18ではチャネルスイッチ  $S_{ch}$  からチャネル抵抗  $r_{ch}$  に変化している。この  $r_{ch}$  は、 $r_s$ 、 $r_d$  を含む抵抗の中で最も大きいものである。また、 $C_{jd}$  は、 $C_g$  の2倍以上の容量をもっている。従って、 $r_{ch}$  と  $C_{jd}$  とが、従来回路のターンオン・セトリング時間に影響を与える。これに対し、図4の本発明の回路では、 $C_{jd}$  も  $r_{ch}$  もないため、ターンオン・セトリング時間はより短くなる。最後に、ON状態等価回路を示す図5と図19とを比較すると、図19の従来回路では、補償電流  $I_{comp}'$  を、 $r_{on}$  と  $Z_f$  との並列接続を介してしかもそれをオペアンプが供給しているのに対し、図5の本発明回路では、オペアンプとは独立の電流源が補償電流  $I_{comp}$  をしかも反転入力端子に直接供給している。従って、従来回路では、補償電流  $I_{comp}'$  の大きさがオペアンプの電流供給能力に依存するが、本発明ではそのような制限はない。また、本発明回路では、補償電流  $I_{comp}$  の経路が、 $Z_f$  を含まずしかもON抵抗  $r_{on}$  が介在しないため、動作速度がより速くなる。以上の説明から判るように、図2の回路は、図16の回路と比べ、種々の利点を備えている。

20

**【0028】**

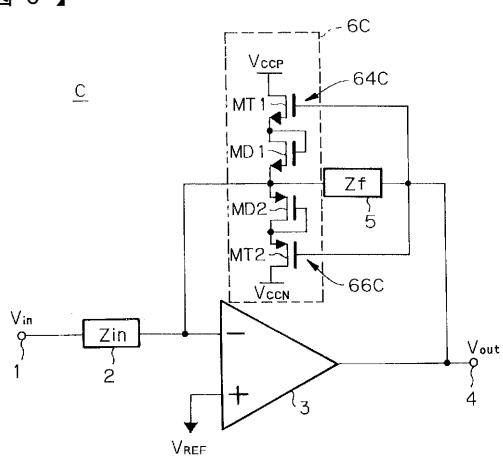

次に、図6は、図1の関数演算回路Aをより具体化した第3の実施形態の関数演算回路Cを示している。この回路Cにおいては、リミット回路6Cが図2のリミット回路6Bの変更例を成している点を除けば、図2の回路と同じである。従って、図2の回路との相違部分について特に説明すると、リミット回路6Cの目的は、上側リミットレベル  $V_{LM1}$  をより高く、そして下側リミットレベル  $V_{LM2}$  をより低く設定することであり、そのために上側と下側のリミット回路64C及び66Cに、各々1つのMOSダイオードMD1、MD2を追加している。即ち、MOSトランジスタMT1のソース電極とオペアンプ3の反転入力端子との間に、N型MOSダイオードを接続し、また反転入力端子とMOSトランジスタMT2のソース電極との間に、P型MOSダイオードを接続している。MOSダイオードMD1とMD2のON電圧をそれぞれ  $V_{ON1}$ 、 $V_{ON2}$  とすると、リミット回路6Cの上側リミットレベル  $V_{LM1}$  は  $(V_{REF} + V_{TH1} + V_{ON1})$  となり、下側リミットレベル  $V_{LM2}$  は  $(V_{REF} - V_{TH2} - V_{ON2})$  となる。

30

**【0029】**

尚、リミット回路6Cの図1の波形整形回路6に対する対応関係については、MOSトランジスタMT1及びMT2の各々のゲート電極とその下の酸化物とが電圧伝達部60に対応し、そしてこのMT1及びMT2の残りの部分とMOSダイオードMD1及びMD2が

40

50

変換部 6 2 に対応している。従って、リミッタ回路 6 C は、波形整形回路 6 の別の 1 つの実施形態を構成している。

#### 【 0 0 3 0 】

この図 6 の実施形態においては、各リミット回路に追加する M O S ダイオードは 1 つとしたが、必要に応じてそれより多い M O S ダイオードを追加してもよく、また更に必要に応じて上側と下側のリミット回路に追加する M O S ダイオードのそれぞれの数を異ならせてよい。

#### 【 0 0 3 1 】

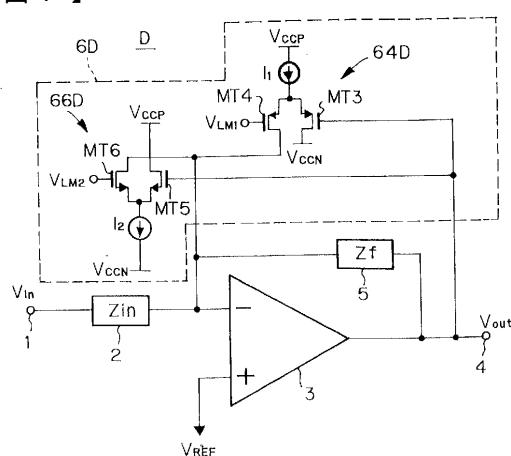

次に、図 7 は、図 1 の関数演算回路 A をより具体化した別の第 4 の実施形態の関数演算回路 D を示している。この回路 D においても、リミット回路 6 D が図 2 のリミット回路 6 B の変更例を成している点を除けば、図 2 の回路と同じである。従って、図 2 の回路との相違部分について特に説明すると、リミット回路 6 D の目的は、上側及び下側のリミットレベルをより自由にまたより簡単に設定できるようにすることであり、そのために上側と下側のリミット回路 6 4 D 及び 6 6 D の各々に、電流スイッチを使用している。詳しくは、上側リミット回路 6 4 D は、電流源  $I_1$  と、1 対の P 型 M O S トランジスタ M T 3 及び M T 4 とを備えていて、電流源  $I_1$  は、正電源電圧端子  $V_{CCP}$  と M T 3 及び M T 4 の各ソース電極との間に接続し、また M T 3 のドレイン電極は負電源電圧端子  $V_{CCN}$  に接続しゲート電極は出力端子 4 に接続している。一方、M T 4 のドレイン電極は、オペアンプ 3 の反転入力端子に接続し、そしてそのゲート電極は、上側リミットレベル ( $V_{LM1}$ ) 端子に接続している。この電流スイッチは、 $V_{out} < V_{LM1}$  のときには電流源  $I_1$  からの電流を  $V_{CCN}$  電源端子に導く第 1 電流経路を開き、そして  $V_{out} > V_{LM1}$  のときには、電流源  $I_1$  からの電流を反転入力端子に導く第 2 電流経路を開く。同様に、下側リミット回路 6 6 D は、1 対の N 型 M O S トランジスタ M T 5 及び M T 6 と、電流源  $I_2$  を備えている。M T 5 のドレイン電極は、正電源電圧端子  $V_{CCP}$  に接続し、ゲート電極は出力端子 4 に接続している。一方、M T 6 のドレイン電極は、反転入力端子に接続し、そしてそのゲート電極は、下側リミットレベル ( $V_{LM2}$ ) 端子に接続している。電流源  $I_2$  は、M T 5 及び M T 6 の各ソース電極と負電源電圧端子  $V_{CCN}$  との間に接続している。この電流スイッチは、 $V_{out} < V_{LM2}$  のときには電流源  $I_2$  の電流を  $V_{CCP}$  電源端子から引き出させる第 1 電流経路を開き、そして  $V_{out} > V_{LM2}$  のときには、電流源  $I_2$  の電流を反転入力端子から引き出させる第 2 電流経路を開く。

#### 【 0 0 3 2 】

また、図 7 のリミッタ回路 6 D と図 1 の波形整形回路 6 との対応関係については、1 対の電流スイッチの内の M O S トランジスタ M T 3 及び M T 5 の各々のゲート電極とその下の酸化物とが電圧伝達部 6 0 に対応し、そして電流スイッチの残りの部分全てが変換部 6 2 に対応している。従って、リミッタ回路 6 D も、波形整形回路 6 の更に別の 1 つの実施形態を構成している。

#### 【 0 0 3 3 】

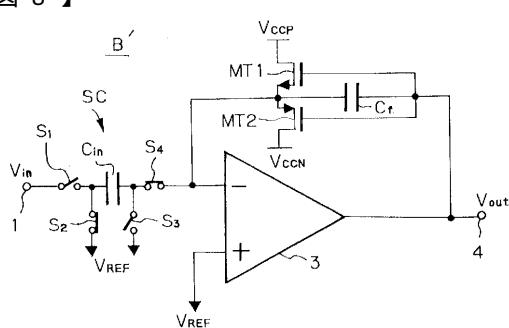

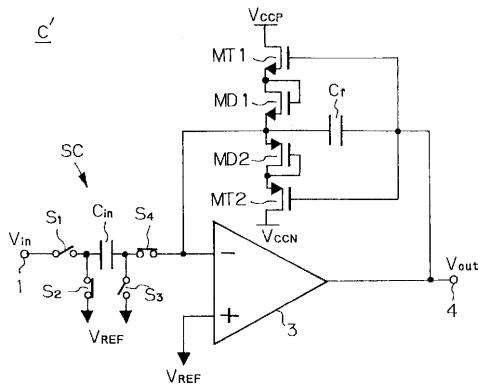

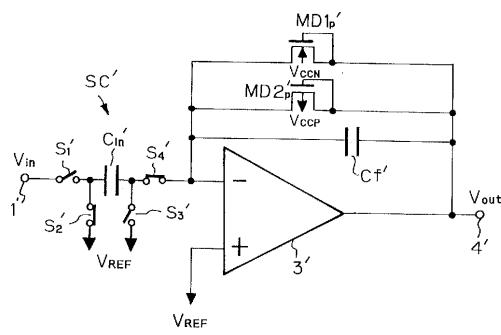

次に、図 8 ~ 1 0 を参照して、図 2 、図 6 、図 7 の関数演算回路 B , C , D をそれより具体化した積分回路 B ' , C ' , D ' について説明する。これら積分回路 B ' , C ' , D ' は、スイッチトキャパシタ型の積分回路を構成しており、対応の関数演算回路 B , C , D と異なっている点は、各々、入力回路 Z in としてスイッチトキャパシタ S C を使用し、そして帰還回路 Z f としてキャパシタ C f を使用している点である。スイッチトキャパシタ S C は、公知の構成のものであって、図示の通り、入力端子 1 と基準電圧  $V_{REF}$  との間に直列接続したアナログスイッチ S 1 及び S 2 と、これらスイッチの接合点と基準電圧  $V_{REF}$  との間に直列接続した入力キャパシタ C in 及びアナログスイッチ S 3 と、C in と S 3 との接合点とオペアンプの反転入力端子との間に接続したアナログスイッチ S 4 と、から成る構成である。図示からも判るように、アナログスイッチ S 1 及び S 3 は、クロック 1 で駆動し、そしてアナログスイッチ S 2 及び S 4 は、クロック 1 とは相補的なクロック 2 で駆動する。

#### 【 0 0 3 4 】

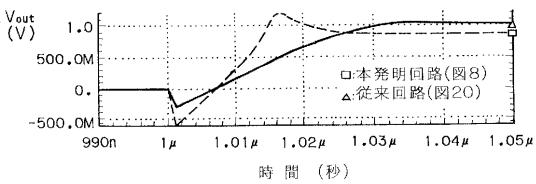

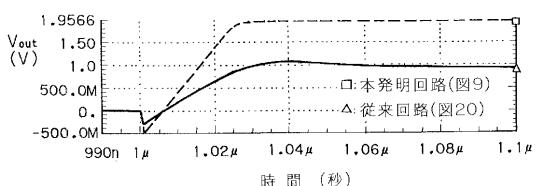

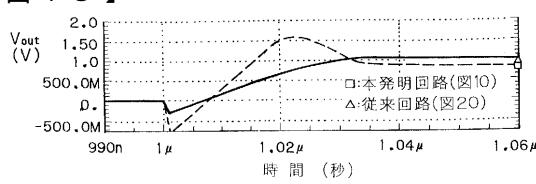

次に、図 1 1 ~ 図 1 3 を参照して、積分回路 B ' , C ' , D ' のリミッタのターンオン特性に

10

20

30

40

50

について説明する。尚、ターンオフ時の特性もこれと同様であるため、省略する。詳しくは、図11は積分回路B'、図12は積分回路C'、図13は積分回路D'の特性をそれぞれ示しており、また各図には、比較のため、図20の従来回路の特性も示している。この従来回路は、図16の従来回路構成でスイッチトキャパシタ型積分回路を実現したものである。また、これら特性図をシミュレーションにより得る際に使用した各値は、以下の通りである。尚、W/Lは、MOSトランジスタのゲート幅/ゲート長である。

### 【0035】

【表1】

|                     |                               |    |

|---------------------|-------------------------------|----|

| $V_{CCP}$ :         | 2.9 ボルト                       | 10 |

| $V_{CCN}$ :         | -2.1 ボルト                      |    |

| $V_{REF}$ :         | グランド                          |    |

| $C_{in}, C_{in'}$ : | 1 pF                          |    |

| $C_f, C_{f'}$ :     | 1 pF                          |    |

| M T 1 :             | $W/L = 200 \mu m / 0.6 \mu m$ |    |

| M T 2 :             | $W/L = 400 \mu m / 0.6 \mu m$ |    |

| M D 1 :             | $W/L = 200 \mu m / 0.6 \mu m$ |    |

| M D 2 :             | $W/L = 400 \mu m / 0.6 \mu m$ |    |

| M T 3 , M T 4 :     | $W/L = 400 \mu m / 0.6 \mu m$ |    |

| M T 5 , M T 6 :     | $W/L = 200 \mu m / 0.6 \mu m$ |    |

| $I_1, I_2$ :        | 100 $\mu A$                   | 20 |

また、シミュレーションにおける条件は、各特性図において、1  $\mu s$  時より前に  $C_{in}$  に充電が完了しており、そして 1  $\mu s$  時に 2 によりスイッチ  $S_2$  及び  $S_4$  が ON になる、という条件である。特性図中、点線が本発明回路の特性であり、実線が従来回路の特性である。

### 【0036】

図11から判るように、本発明回路では、従来回路と比べ、積分回路B'のスリューレートが大きくなるとともに、そのスイッチング後からリミッタ回路がセトリングするまでの時間が、約 1.025  $\mu s$  と短くなっている。従来回路では、1.05  $\mu s$  においても下降中でセトリングが完了していない。但し、本発明回路のリミットレベルは約 0.85 ボルトであるのに対し、従来回路では約 1.0 ボルトである。スリューレート向上の理由としては、本発明のリミッタ回路から積分回路の帰還回路又は負荷に与える影響が小さくなつたことである。また、セトリングまでの時間短縮の理由としては、逆に、積分回路の帰還回路又は負荷から本発明のリミッタ回路への影響が減少したこと、更に、オペアンプ出力とは独立の電流源がリミット動作に作用する、ということである。

### 【0037】

図12においても、上記と同様、スリューレート及びセトリングまでの時間の改善が得られており、特にセトリングまでの時間が、約 1.03  $\mu s$  と短くなっているが、従来回路では 1.1  $\mu s$  でもまだセトリングが完了していない。但し、本発明回路のリミットレベルは約 1.9 ボルトである。

### 【0038】

また、図13においても、上記と同様、スリューレート及びセトリングまでの時間の改善が得られている。即ち、従来回路では、1.06  $\mu s$  (図12では 1.1  $\mu s$ ) でもセトリングが完了していないのに対し、本発明回路では、ほぼ 1.05  $\mu s$  でセトリングしている。

### 【0039】

以上、本発明による関数演算回路の幾つかの実施形態について図示し説明したが、これら実施形態においては、以下のような種々の変更が可能である。第1に、上記各実施形態においては、波形整形回路としてリミッタ回路について例示したが、上側リミット回路又は下側リミット回路のどちらか一方を取り除くだけで、クリップ回路とすることができる。第2に、上記実施形態では、関数演算の1例として、積分について示したが、その他に、

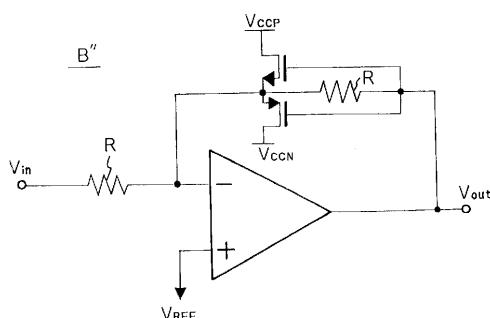

反転、積分以外のその他の関数演算、例えば、加減乗除、微分、対数、逆対数のような演算を行うように、入力回路インピーダンス  $Z_{in}$  及び帰還回路インピーダンス  $Z_f$  の組合せを選択することができる。1例として、図14に、図2の関数演算回路Bを具体化した1例である反転増幅器B"を示す。この場合、 $Z_{in}$  = 抵抗R、 $Z_f$  = 抵抗Rである。

#### 【0040】

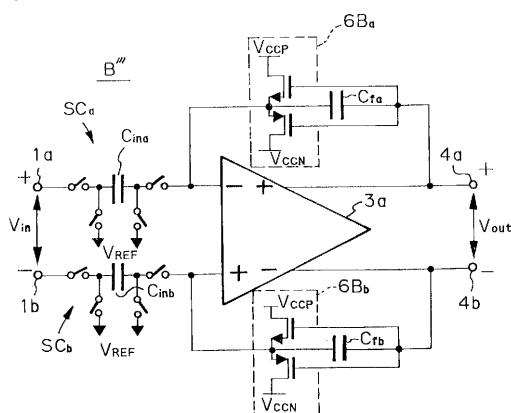

第3に、上記実施形態では、差動入力／单一出力型の関数演算回路について示したが、差動入力／差動出力型の関数演算回路に変更することもできる。1例として、図15に、図8の回路B'を差動入力／差動出力型にしたスイッチトキャパシタ型積分回路B'''を示す。この回路では、正入力端子1a及び負入力端子1b、正出力端子4a及び負出力端子4b、差動入力／差動出力型のオペアンプ3a、1対のスイッチトキャパシタSCa及びSCb、オペアンプの非反転出力端子と反転入力端子との間に接続したリミッタ回路6Ba及び帰還キャパシタCfaと、オペアンプの反転出力端子と非反転入力端子との間に接続したリミッタ回路6Bb及び帰還キャパシタCfbと、を備えている。第4に、差動入力／单一出力型構成の実施形態において、オペアンプの反転入力端子への入力及び帰還を非反転入力端子への入力及び帰還に変更することが可能である。

#### 【0041】

##### 【発明の効果】

以上に説明した本発明による関数演算回路用の波形整形回路によれば、絶縁伝達を行う電圧伝達部を設けることにより、負荷並びに帰還回路  $Z_f$  との相互干渉が低減する。これによって、負荷及び帰還回路のインピーダンスによる波形整形動作への影響を最小限にすることができる。このことは、関数演算回路のスリューレートの向上、並びに波形整形動作のセトリング時間の短縮をもたらす。また、電圧 - 電流変換部を設けることにより、波形整形動作のセトリング時間を更に短縮することができる。このセトリング時間の短縮により、高速の関数演算回路においては、より誤差の少ない関数演算出力を生成することが可能となる。また更に、演算増幅器の入力側に電圧 - 電流変換部を接続する構成であるため、変換部に必要な回路の能力が小さくて済むようになる。

##### 【図面の簡単な説明】

【図1】本発明による波形整形回路を備えた第1の実施形態の関数演算回路Aを示す回路図であり、波形整形回路は、その基本概念を示している。

【図2】図1の関数演算回路Aのより具体化した第2の実施形態の関数演算回路Bを示す回路図。

【図3】図2の関数演算回路Bについて、リミッタ回路（上側のみ図示）がOFF状態のときの等価回路を示す図。

【図4】図2の関数演算回路Bについて、リミッタ回路（上側のみ図示）がOFF-ON遷移状態のときの等価回路を示す図。

【図5】図2の関数演算回路Bについて、リミット回路（上側のみ図示）がON状態のときの等価回路を示す図。

【図6】図1の関数演算回路Aをより具体化した第3の実施形態の関数演算回路Cを示す回路図。

【図7】図1の関数演算回路Aをより具体化した別の第4の実施形態の関数演算回路Dを示す回路図。

【図8】図2の関数演算回路Bをより具体化したスイッチトキャパシタ型積分回路B'を示す回路図。

【図9】図6の関数演算回路Cをより具体化したスイッチトキャパシタ型積分回路C'を示す回路図。

【図10】図7の関数演算回路Dをより具体化したスイッチトキャパシタ型積分回路D'を示す回路図。

【図11】図8の積分回路B'のリミッタのターンオン特性を示す特性図であり、比較のため、図20の従来回路の特性を実線で示し、本発明回路の特性を点線で示している。

【図12】図9の積分回路C'のリミッタのターンオン特性を示す特性図であり、比較の

10

20

30

40

50

ため、図20の従来回路の特性を実線で示し、本発明回路の特性を点線で示している。

【図13】図10の積分回路D'のリミッタのターンオン特性を示す特性図であり、比較のため、図20の従来回路の特性を実線で示し、本発明回路の特性を点線で示している。

【図14】図2の関数演算回路Bを具体化した1例である反転増幅器B"を示す回路図。

【図15】図8の積分回路B'を差動入力／差動出力型に変更したスイッチトキャパシタ型積分回路B'''を示す回路図。

【図16】従来のリミッタ回路付き関数演算回路を示す回路図。

【図17】図16の従来回路について、リミット回路（上側のみ図示）のOFF状態における等価回路を示す図。

【図18】図16の従来回路について、リミット回路（上側のみ図示）のOFF-ON遷移状態における等価回路を示す図。 10

【図19】図16の従来回路について、リミット回路（上側のみ図示）のON状態における等価回路を示す図。

【図20】図16の従来回路構成のスイッチトキャパシタ型積分回路であって、本発明回路と比較するための回路を示す図。

#### 【符号の説明】

1, 1a, 1b: 入力端子

2: 入力回路

3, 3a: 演算増幅器

4, 4a, 4b: 入力端子

5: 帰還回路

6: 波形整形回路

6B, 6C, 6D, 6Ba, 6Bb: リミッタ回路

64, 64C, 64D: 上側リミット回路

66, 66C, 66D: 下側リミット回路

$V_{in}$ : 入力電圧

$V_{out}$ : 出力電圧

$V_{CCP}$ : 正電源電圧

$V_{CCN}$ : 負電源電圧

$V_{REF}$ : 基準電圧

$V_{LM1}$ : 上側リミットレベル

$V_{LM2}$ : 下側リミットレベル

S C, S Ca, S Cb, S C': スイッチトキャパシタ

20

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 11】

【図 10】

【図 12】

【図 13】

【図 14】

【図 16】

【図 15】

【図 17】

【図18】

(従来技術)

OFF-ON遷移状態

【図20】

(従来回路)

【図19】

(従来技術)

ON状態

---

フロントページの続き

(72)発明者 室田 敏夫

神奈川県厚木市長谷仲町422-1 日本バーブラウン株式会社 厚木テクニカルセンター内

(72)発明者 濱 崎 利彦

神奈川県厚木市長谷仲町422-1 日本バーブラウン株式会社 厚木テクニカルセンター内

審査官 高木 進

(56)参考文献 特開昭46-000460(JP,A)

特開平08-125462(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03F 3/00-3/45

H03G 11/00