(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

9 June 2011 (09.06.2011)

(10) International Publication Number

WO 2011/068106 A1

(51) International Patent Classification:

*G02F 1/1368* (2006.01) *H01L 29/786* (2006.01)

*G02F 1/139* (2006.01)

(21) International Application Number:

PCT/JP2010/071418

(22) International Filing Date:

24 November 2010 (24.11.2010)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

2009-277088 4 December 2009 (04.12.2009) JP

(71) Applicant (for all designated States except US): SEMI-

CONDUCTOR ENERGY LABORATORY CO., LTD.

[JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(72) Inventors; and

(75) Inventors/Applicants (for US only): YAMAZAKI,

Shunpei [JP/JP]; c/o SEMICONDUCTOR ENERGY

LABORATORY CO., LTD., 398, Hase, Atsugi-shi,

Kanagawa, 2430036 (JP). KIMURA, Hajime. NISHI,

Takeshi.

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: DISPLAY DEVICE AND ELECTRONIC DEVICE INCLUDING THE SAME

FIG. 5B

(57) Abstract: A low-power-consuming display device including a liquid crystal material which exhibits a blue phase is provided. A display device includes a first substrate having a pixel portion in which a pixel including a transistor is provided; a second substrate which faces the first substrate; and a liquid crystal layer between the first substrate and the second substrate; in which the liquid crystal layer includes a liquid crystal material which exhibits a blue phase; a gate of the transistor is electrically connected to a scan line, one of a source and a drain of the transistor is electrically connected to a signal line, and the other of the source and the drain of the transistor is electrically connected to an electrode; and the transistor includes an oxide semiconductor layer a hydrogen concentration of which is  $5 \times 10^{19} / \text{cm}^3$  or less.

WO 2011/068106 A1

## DESCRIPTION

**DISPLAY DEVICE AND ELECTRONIC DEVICE INCLUDING THE SAME**5 **TECHNICAL FIELD**

[0001]

The present invention relates to display devices. Further, the present invention relates to electronic devices including the display device.

10 **BACKGROUND ART**

[0002]

As display devices, liquid crystal display devices or electroluminescence display devices (hereinafter, referred to as EL display devices) including electroluminescence elements are known. The mainstream of liquid crystal display devices is a display device utilizing liquid crystal called nematic liquid crystal. Further, a display device utilizing a liquid crystal material which exhibits a blue phase has been attracting attention in recent years (e.g., see Patent Document 1).

[Reference]

[0003]

20 [Patent Document 1] PCT International Publication No. 05/090520

**DISCLOSURE OF INVENTION**

[0004]

A display device including a liquid crystal material which exhibits a blue phase has characteristics in that high-speed response is possible, a viewing angle is wide, and 25 an alignment film is not required. On the other hand, the display device including a liquid crystal material which exhibits a blue phase has a problem in that driving voltage is significantly higher than that of a liquid crystal display device of another type. Therefore, in an active matrix liquid crystal display device including a liquid crystal material which exhibits a blue phase where transistors serve as switching elements, the 30 transistors need to have high drain breakdown voltage. In addition, significantly high driving voltage will lead to high power consumption.

[0005]

An object of one embodiment of the present invention is to provide a highly-reliable display device including a liquid crystal material which exhibits a blue phase. Further, another object is to provide a low-power-consuming display device including a liquid crystal material which exhibits a blue phase. Note that the present invention solves at least one of the above problems.

5 [0006]

In view of the foregoing problems, in one embodiment of the present invention, each pixel in a display device at least includes a transistor including a high-purity oxide semiconductor. Here, a "high-purity oxide semiconductor" is an oxide semiconductor in which hydrogen is reduced as much as possible and which is intrinsic or substantially 10 intrinsic. One example of a high-purity oxide semiconductor is an oxide semiconductor the hydrogen concentration of which is  $5 \times 10^{19} /cm^3$  or less at most, preferably  $5 \times 10^{18} /cm^3$  or less, more preferably  $5 \times 10^{17} /cm^3$  or less, or less than  $1 \times 15 10^{16} /cm^3$ . A transistor is formed using, for a channel formation region, an oxide semiconductor film the carrier concentration of which is less than  $1 \times 10^{14} /cm^3$ , preferably less than  $1 \times 10^{12} /cm^3$ , more preferably less than  $1 \times 10^{11} /cm^3$  or less than  $6.0 \times 10^{10} /cm^3$ . Note that the hydrogen concentration in the oxide semiconductor layer may be measured by secondary ion mass spectrometry (SIMS).

20 [0007]

An embodiment of the present invention is a display device including: a first substrate having a pixel portion in which a pixel including a transistor is provided; a second substrate which faces the first substrate; and a liquid crystal layer between the first substrate and the second substrate; in which the liquid crystal layer includes a liquid crystal material which exhibits a blue phase; a gate of the transistor is electrically connected to a scan line, one of a source and a drain of the transistor is electrically connected to a signal line, and the other of the source and the drain of the transistor is electrically connected to an electrode; and the transistor includes an oxide semiconductor layer a hydrogen concentration of which is  $5 \times 10^{19} /cm^3$  or less.

25 [0008]

Another embodiment of the present invention is a display device including: a first substrate having a pixel portion in which a pixel including a transistor is provided;

a second substrate which faces the first substrate; a liquid crystal layer between the first substrate and the second substrate; and a capacitor digital-to-analog converter which converts a digital video signal into an analog video signal; in which the liquid crystal layer includes a liquid crystal material which exhibits a blue phase; a gate of the transistor is electrically connected to a scan line, one of a source and a drain of the transistor is electrically connected to a signal line, and the other of the source and the drain of the transistor is electrically connected to an electrode; the transistor includes an oxide semiconductor layer a hydrogen concentration of which is  $5 \times 10^{19} /cm^3$  or less; and the analog video signal is input to the electrode via the signal line and the transistor.

10 [0009]

Further, another embodiment of the present invention is a display device in which a period when the display device displays a still image includes a period when output of a signal to all the scan lines in the pixel portion is stopped.

[0010]

15 Another embodiment of the present invention is a display device including: a first substrate having a pixel portion in which a pixel including a transistor is provided; a second substrate which faces the first substrate; and a liquid crystal layer between the first substrate and the second substrate, the liquid crystal layer including a liquid crystal material which exhibits a blue phase; a driver circuit portion driving the pixel portion; a 20 signal generation circuit generating a control signal for driving the driver circuit portion and an image signal supplied to the pixel; a memory circuit storing image signals of respective frame periods; a comparison circuit detecting a difference between image signals of successive frame periods among the image signals of the respective frame periods stored in the memory circuit; a selection circuit selecting and outputting the 25 image signals of the successive frame periods when the comparison circuit detects a difference; and a display control circuit supplying the control signal and the image signal output from the selection circuit to the driver circuit portion when the comparison circuit detects a difference, and stopping supply of the control signal to the driver circuit portion when the comparison circuit does not detect a difference; in which the transistor 30 includes an oxide semiconductor layer a hydrogen concentration of which is  $5 \times 10^{19} /cm^3$  or less.

## [0011]

In another embodiment of the present invention, the control signal is a high power supply potential, a low power supply potential, a clock signal, a start pulse signal, or a reset signal.

## 5 [0012]

In another embodiment of the present invention, a carrier concentration of the oxide semiconductor layer is less than  $1 \times 10^{14} / \text{cm}^3$ .

## [0013]

In another embodiment of the present invention, the oxide semiconductor layer 10 has a band gap of 2 eV or more.

## [0014]

In another embodiment of the present invention, a resistivity of the liquid crystal material which exhibits a blue phase is  $1 \times 10^9 \Omega \cdot \text{cm}$  or more.

## [0015]

15 Another embodiment of the present invention is an electronic device including the above display device.

## [0016]

Note that a "liquid crystal material" refers to a composition containing liquid crystal. A liquid crystal material which exhibits a blue phase contains liquid crystal 20 and a chiral agent. As the liquid crystal, thermotropic liquid crystal, low-molecular liquid crystal, high-molecular liquid crystal, ferroelectric liquid crystal, anti-ferroelectric liquid crystal, or the like is used. The chiral agent is employed to align the liquid crystal in a helical structure and to make the liquid crystal exhibit a blue phase. For example, a liquid crystal material into which a chiral agent is mixed at 5 25 wt% or more is used for a liquid crystal layer.

## [0017]

Note that it is difficult to distinguish a source and a drain of a transistor from each other because of the structure thereof. Further, potential levels may be interchanged depending on an operation of a circuit. Therefore, in this specification, a 30 source and a drain is not particularly specified and are referred to as a first electrode (or a first terminal) and a second electrode (or a second terminal). For example, in the

case where the first electrode is a source, the second electrode refers to a drain, whereas in the case where the first electrode is a drain, the second electrode refers to a source.

[0018]

Note that in this specification, an aperture ratio refers to a ratio of a light-transmitting area to a unit area; the aperture ratio is decreased as an area occupied by components that do not transmit light is widened, whereas the aperture ratio is increased as an area occupied by components that transmit light is widened. In a display device, the aperture ratio is increased by a reduction in area occupied by a wiring and a capacitor line that overlap with a pixel electrode, and by a reduction in size 10 of a transistor.

[0019]

In this specification, the phrase "A and B are connected" refers to the case where A and B are electrically connected (i.e., A and B are connected with another element or circuit interposed therebetween), the case where A and B are functionally connected (i.e., A and B are functionally connected with another circuit interposed therebetween), or the case where A and B are directly connected (i.e., A and B are connected without another element or circuit interposed therebetween). Note that, each of A and B is an object (e.g., a device, an element, a circuit, a wiring, an electrode, a terminal, a conductive film, or a layer).

20 [0020]

Further, in this specification, ordinal numbers such as first, second, third, to  $N$ -th ( $N$  is a natural number) are used in order to avoid confusion among components, and the terms do not limit the components numerically. For example, a transistor which is referred to as a "first transistor" in this specification may alternatively be 25 referred to as a "second transistor" as long as it is not confused with another component.

[0021]

According to one embodiment of the present invention, a transistor including a high-purity oxide semiconductor is used as a switching element in each pixel. A transistor including a high-purity oxide semiconductor has stable electrical 30 characteristics. For example, the drain breakdown voltage can be 100 V or more, preferably 500 V, more preferably 1 kV or more. Therefore, with such a transistor, a

highly-reliable display device can be provided even in the case where the driving voltage is high like the case of a display device including a liquid crystal material which exhibits a blue phase.

[0022]

5 In addition, off-state current of a transistor including a high-purity oxide semiconductor can be reduced to  $1 \times 10^{-16}$  A or less, preferably  $1 \times 10^{-17}$  A or less, more preferably  $1 \times 10^{-18}$  A or less. Thus, voltage can be held in a storage capacitor for a long period of time and thus power consumption for displaying a still image or the like can be suppressed.

10 [0023]

Furthermore, the image to be displayed is determined whether it is a still image or a moving image, and in a period in which a still image is displayed, operation of a driver circuit portion is stopped, whereby power consumption of the display device can be further reduced.

15

#### BRIEF DESCRIPTION OF DRAWINGS

[0024]

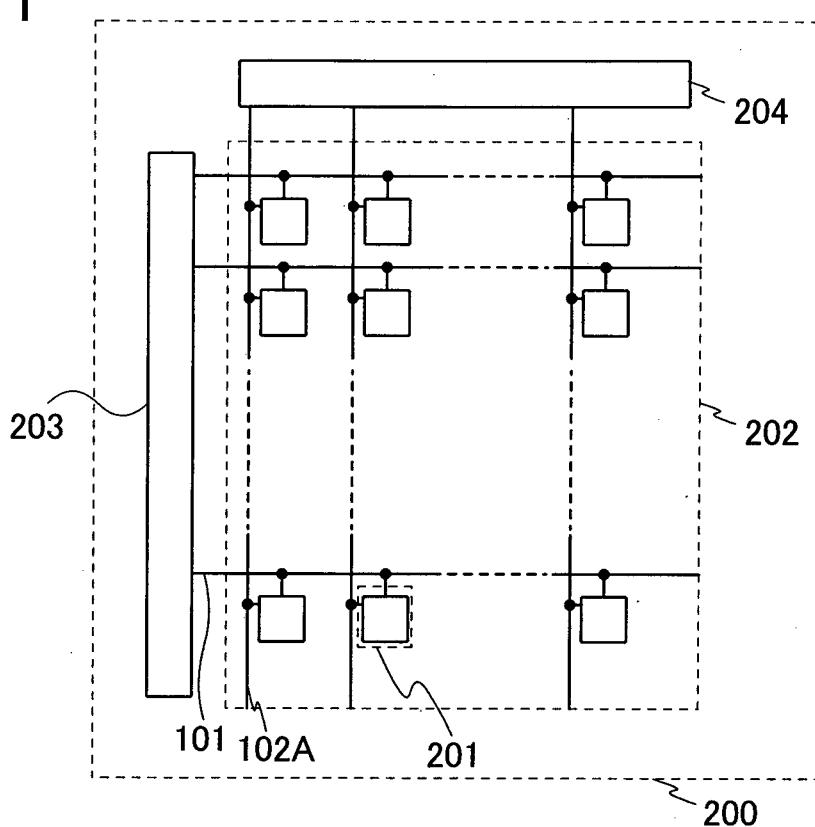

FIG. 1 illustrates a structural example of a display device.

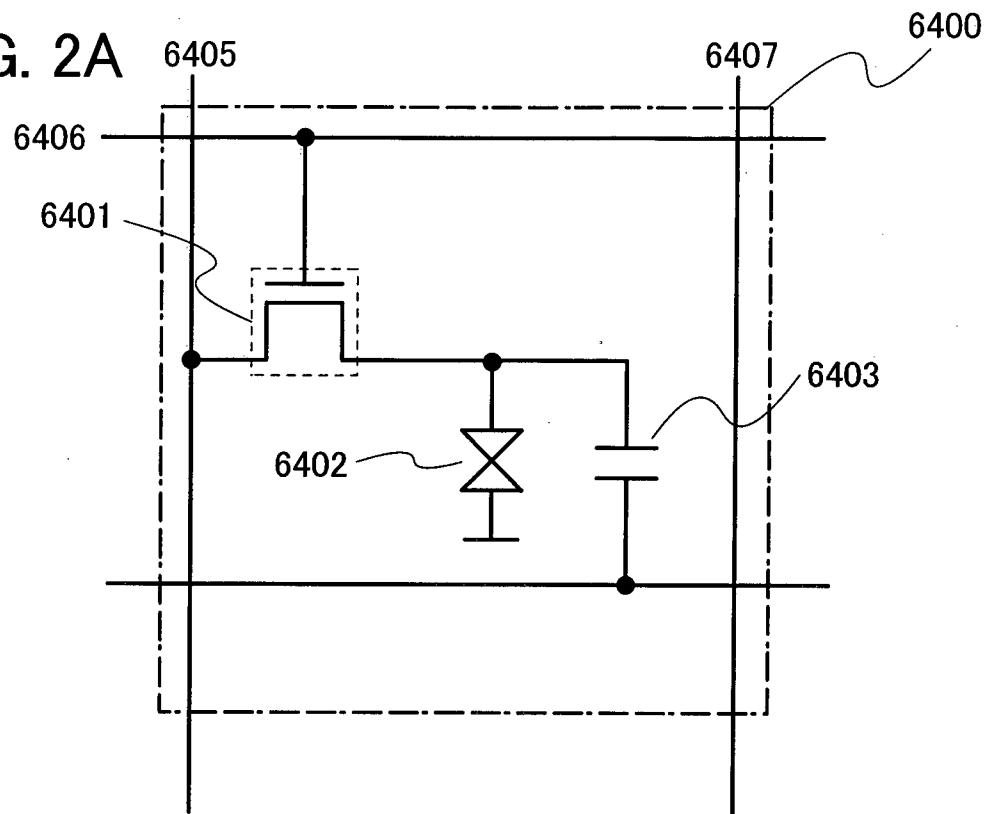

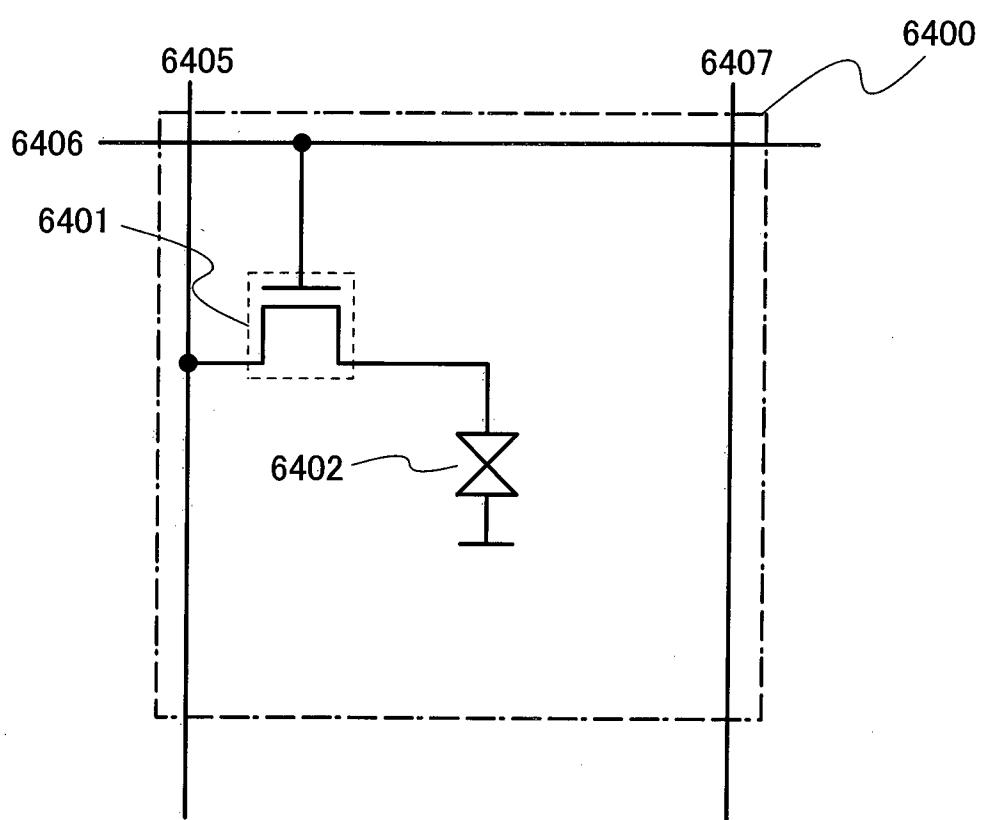

FIGS. 2A and 2B are each an equivalent circuit diagram illustrating a structural example of a pixel.

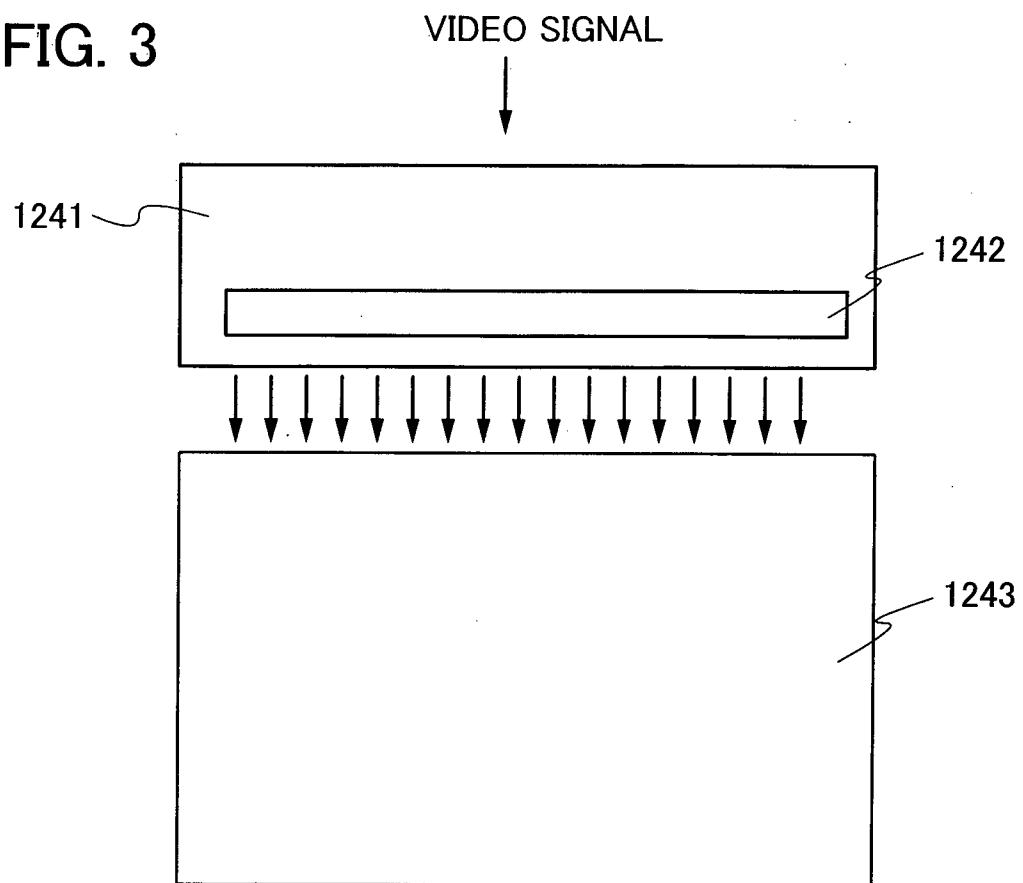

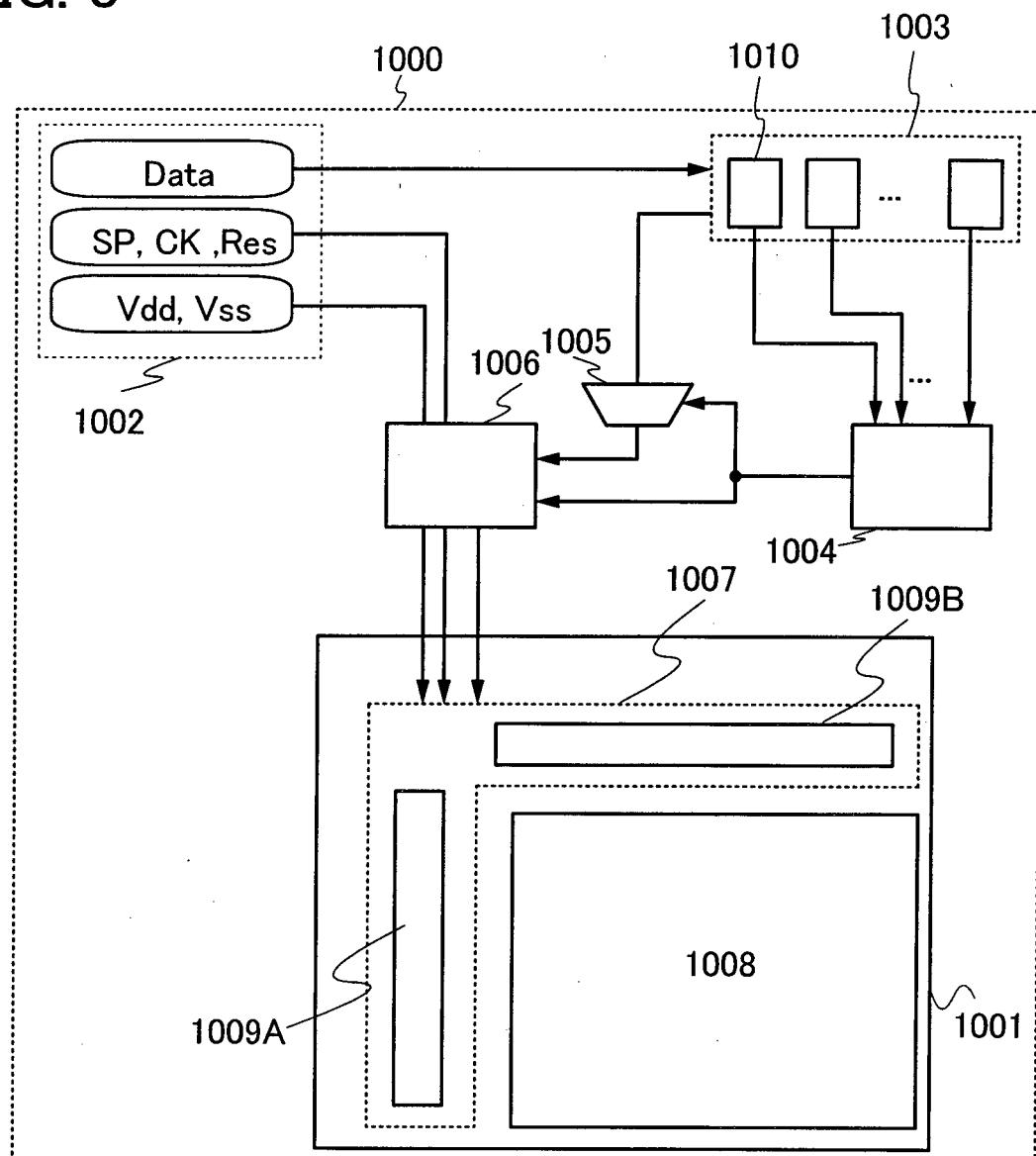

20 FIG. 3 illustrates an example of a block diagram of a display device.

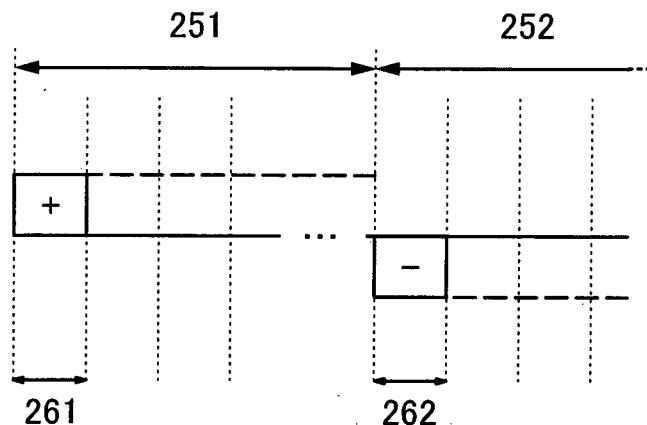

FIGS. 4A and 4B each illustrate a relation between a writing period and a holding period of a pixel.

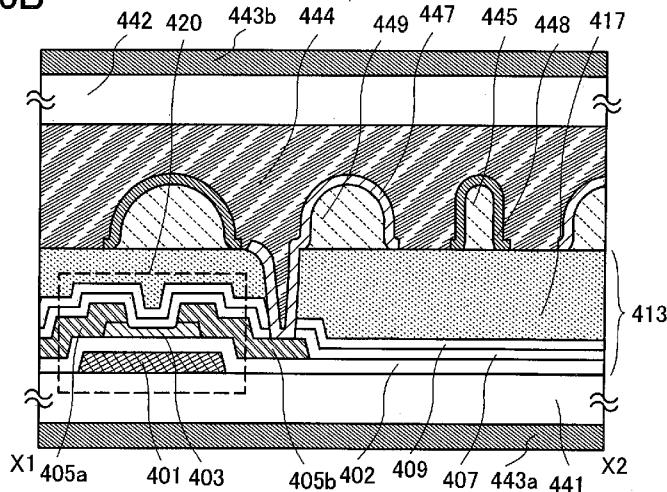

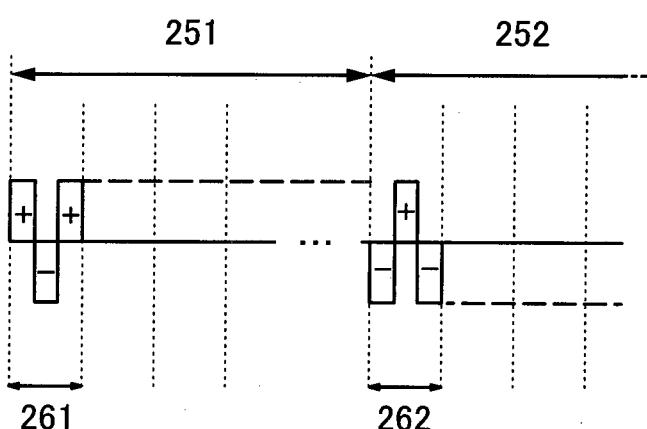

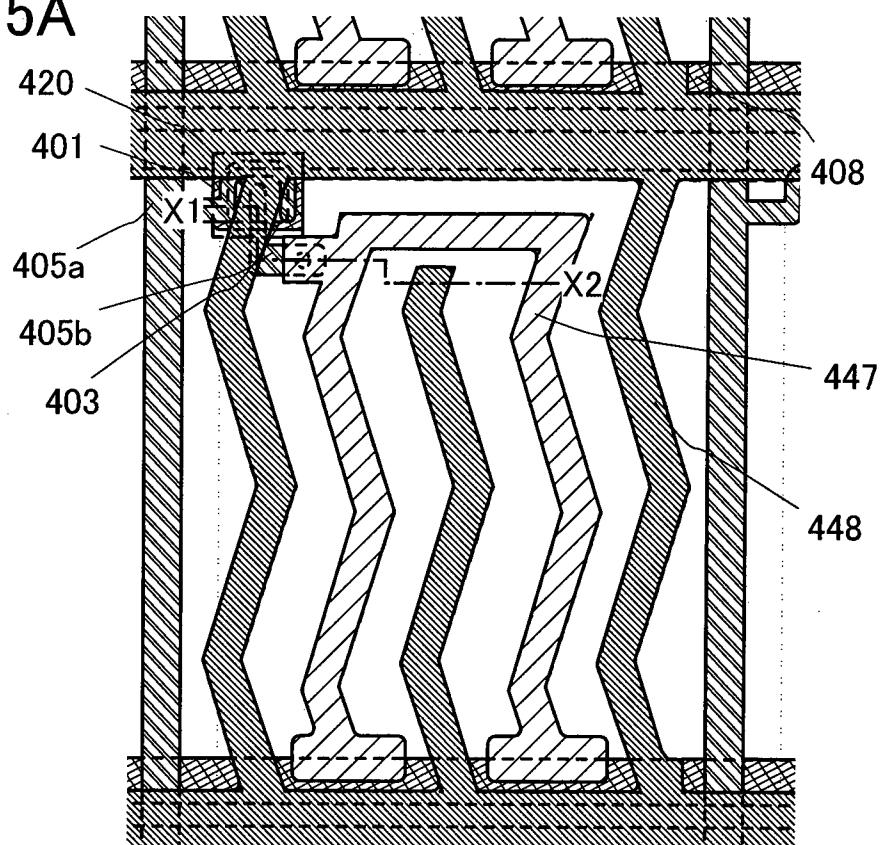

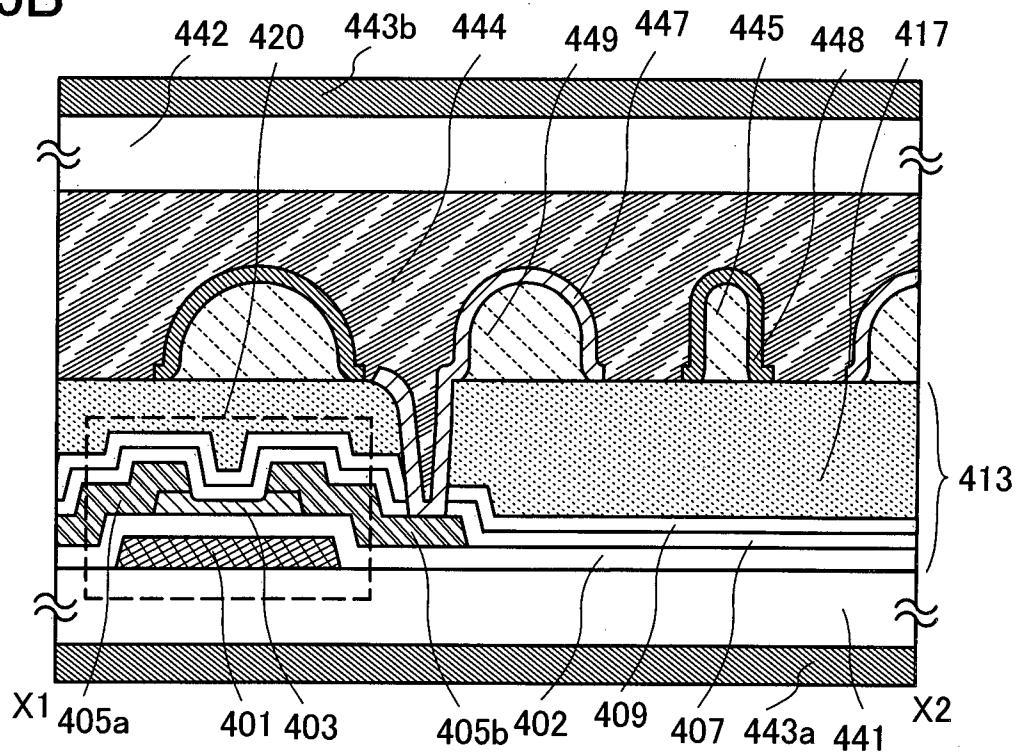

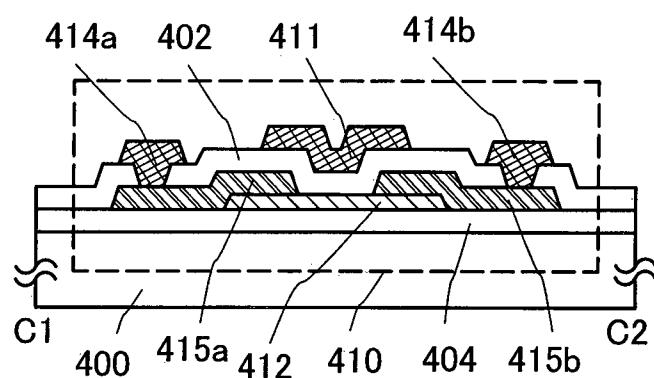

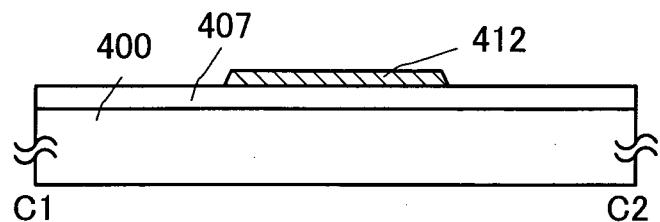

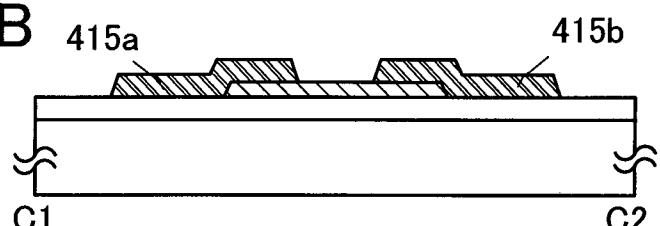

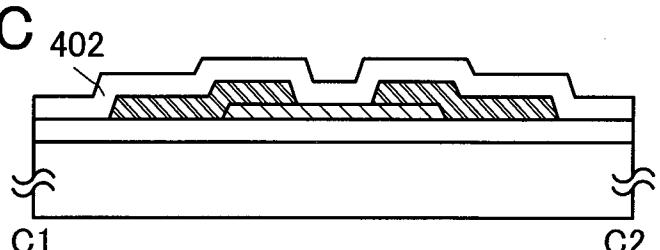

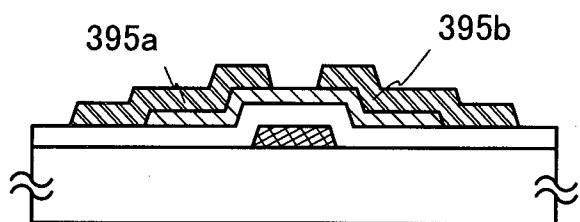

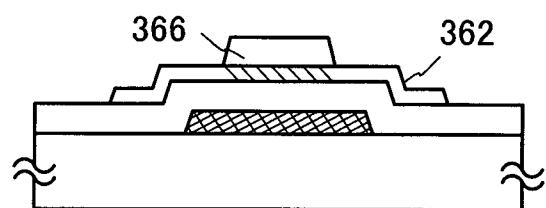

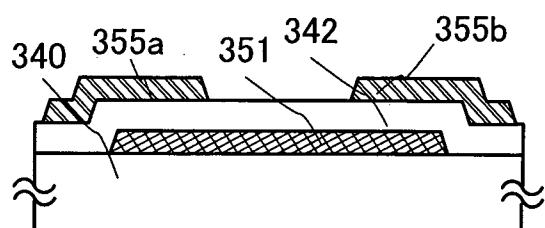

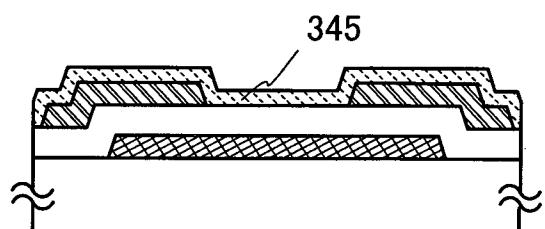

25 FIGS. 5A and 5B are a plan view and a cross-sectional view illustrating a structural example of a pixel.

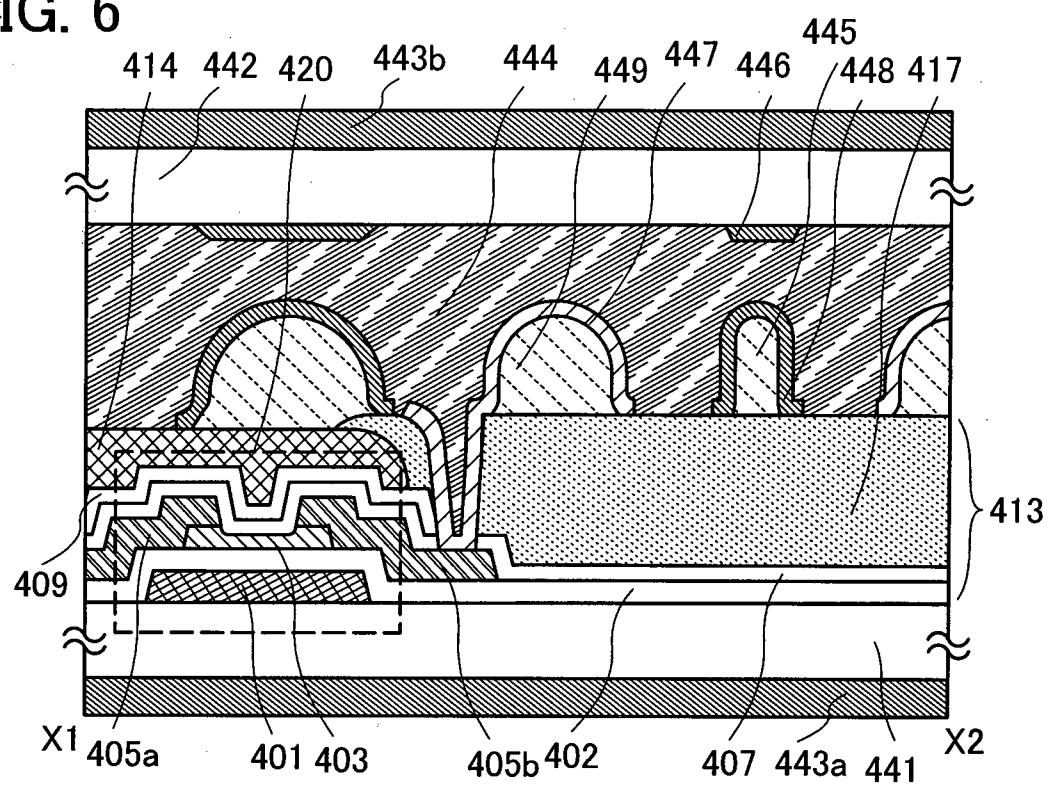

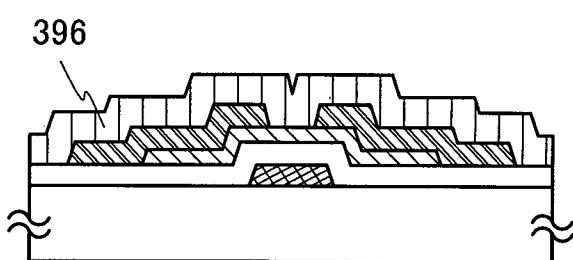

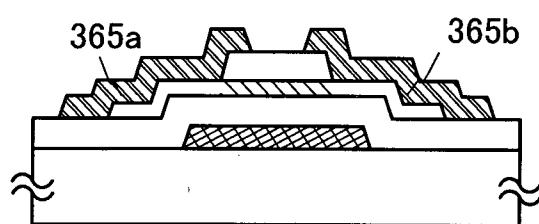

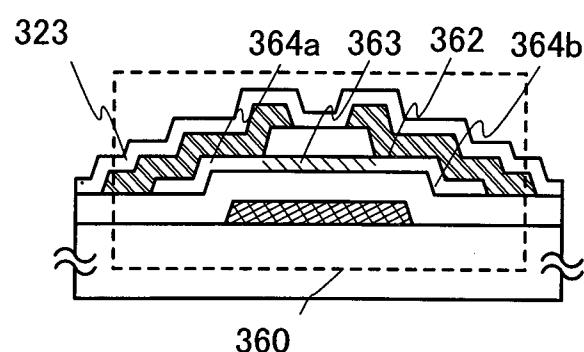

FIG. 6 is a cross-sectional view illustrating a structural example of a pixel.

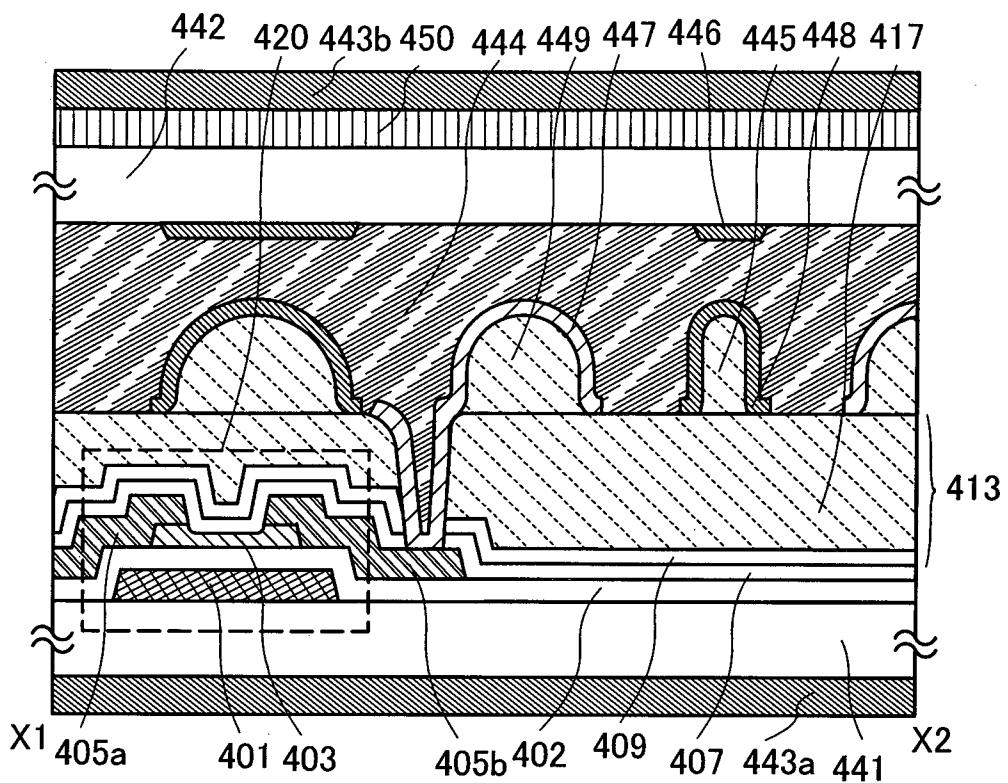

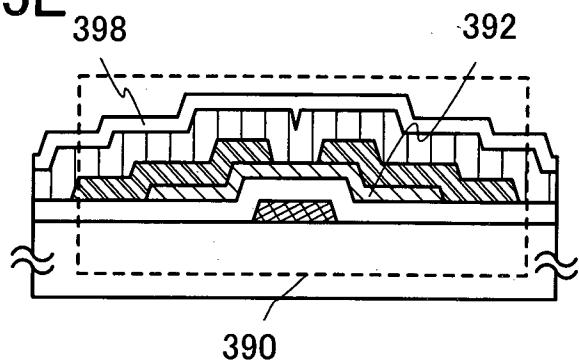

FIG. 7 is a cross-sectional view illustrating a structural example of a pixel.

FIG. 8 is an example of a block diagram of a display device.

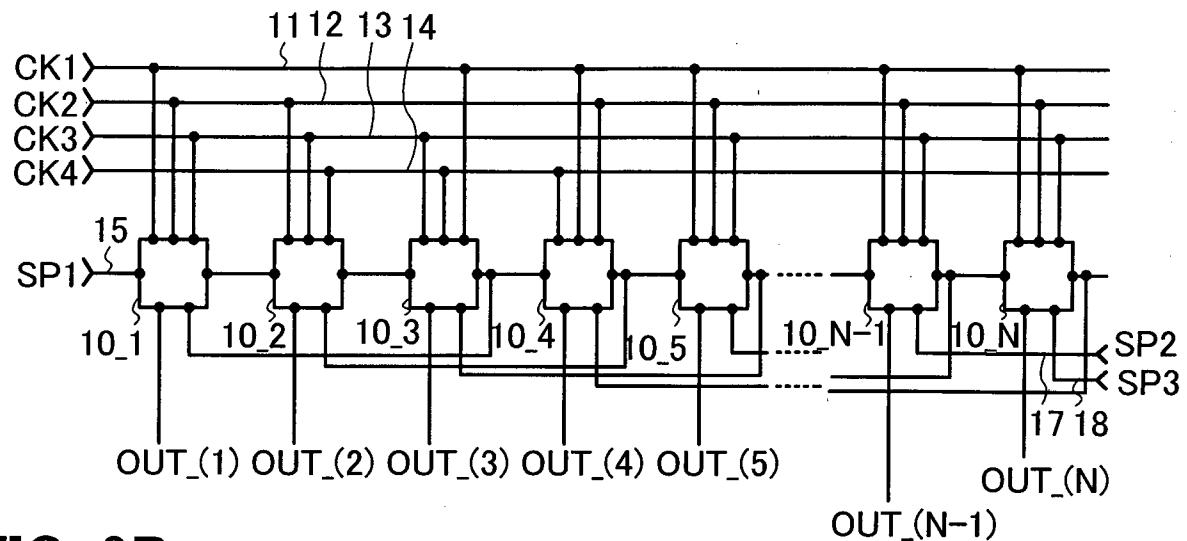

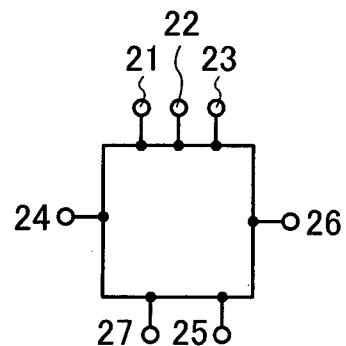

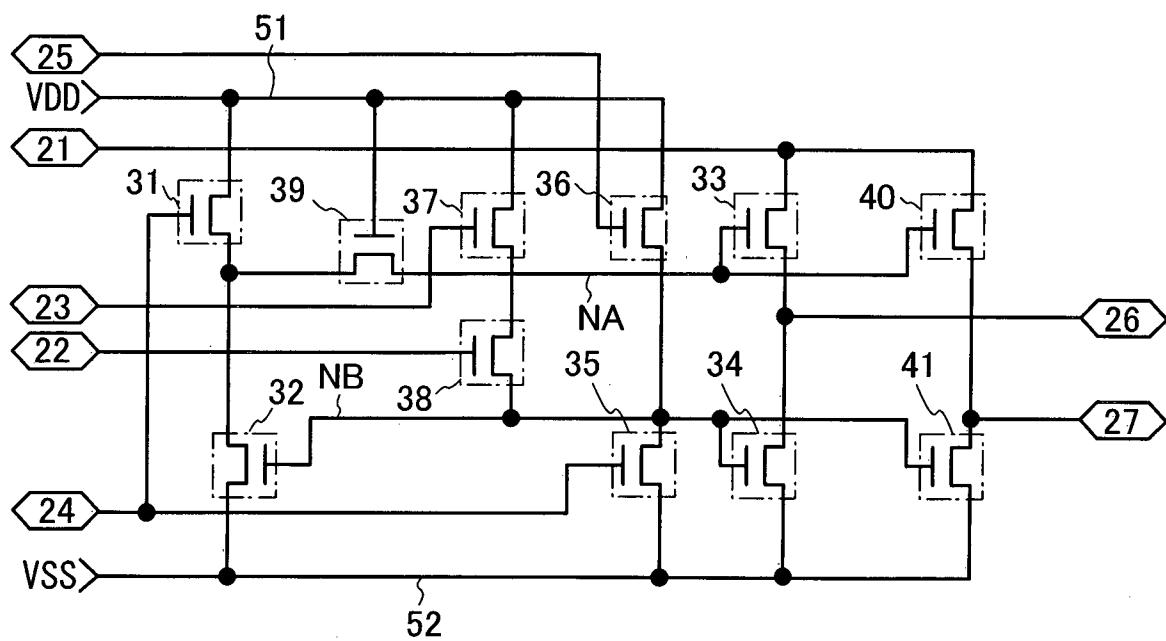

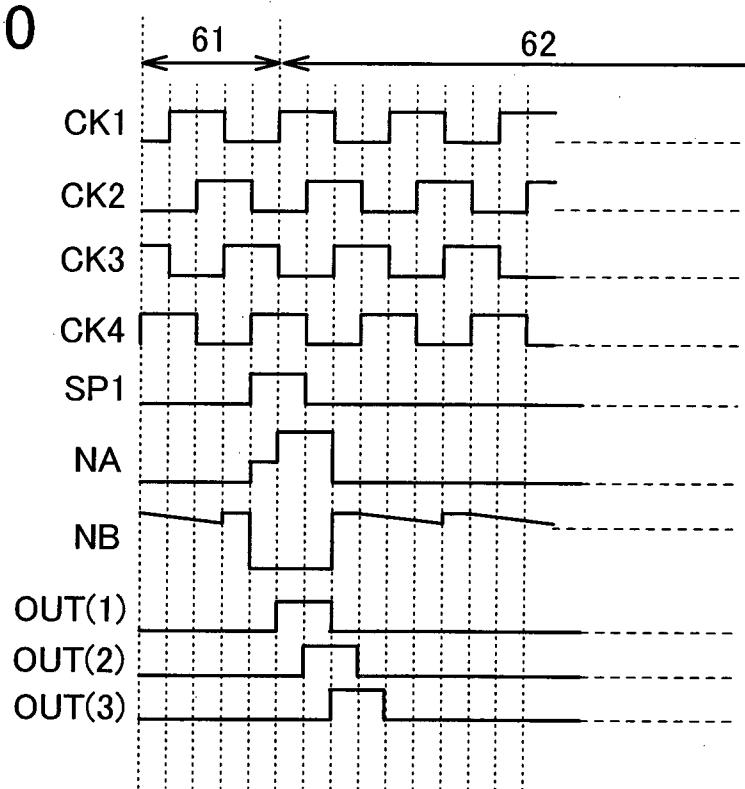

FIGS. 9A to 9C illustrate an example of a driver circuit.

30 FIG. 10 is a timing diagram of a driver circuit.

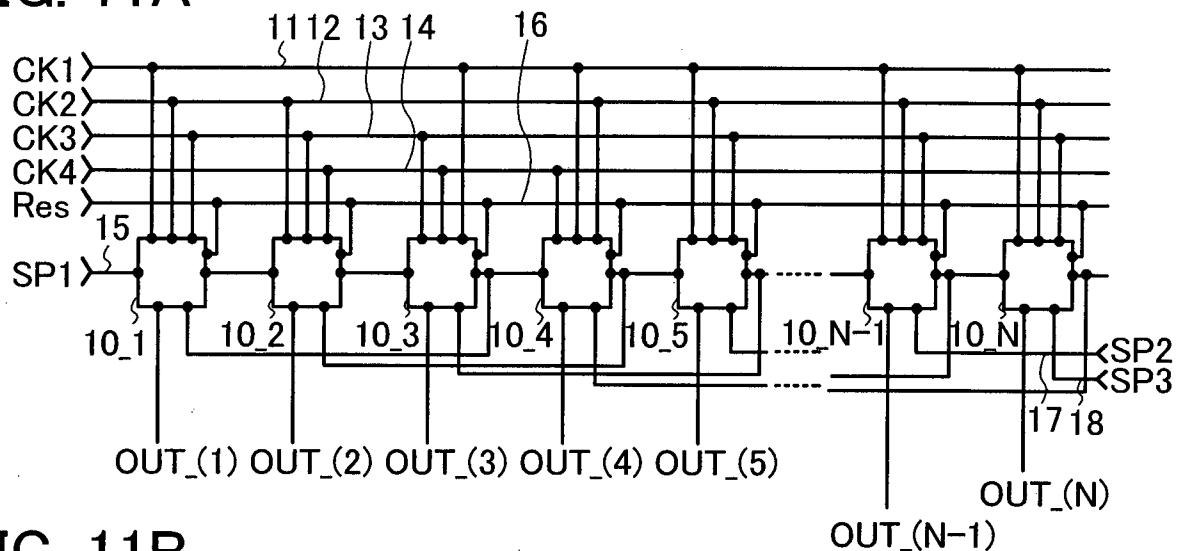

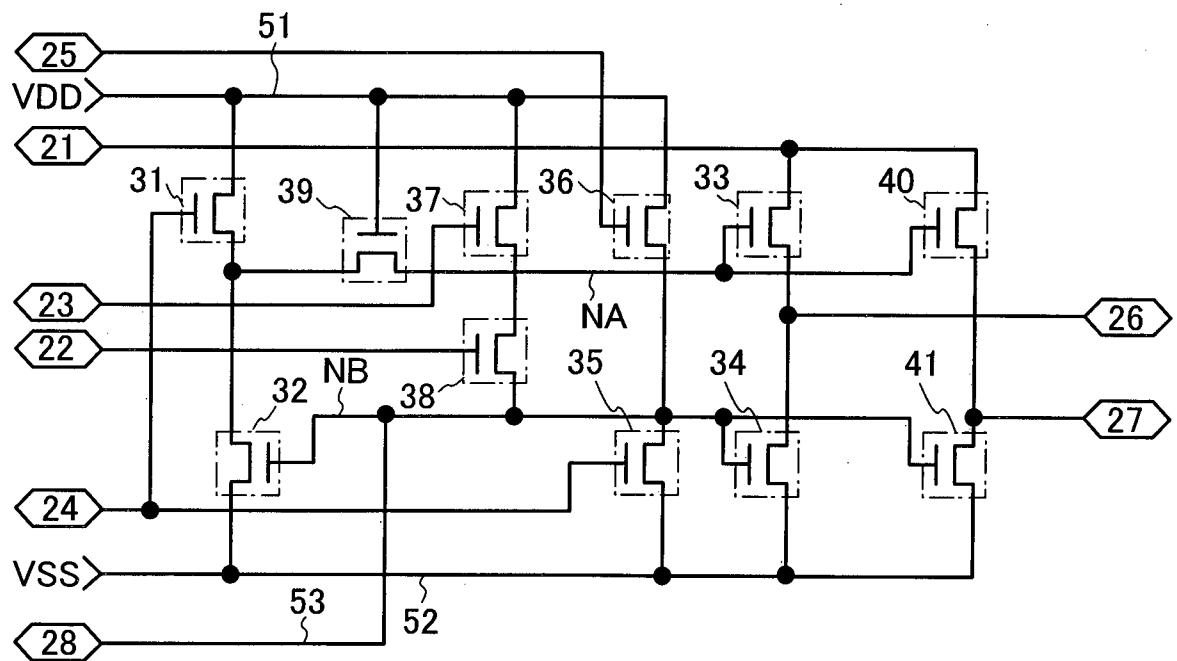

FIGS. 11A to 11C illustrate an example of a driver circuit.

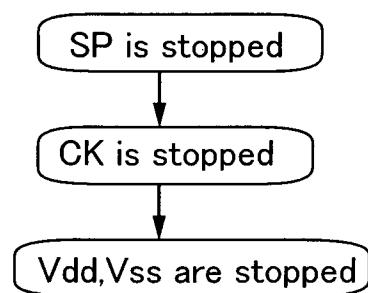

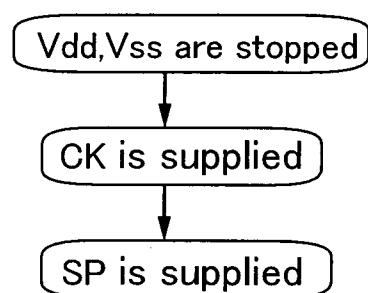

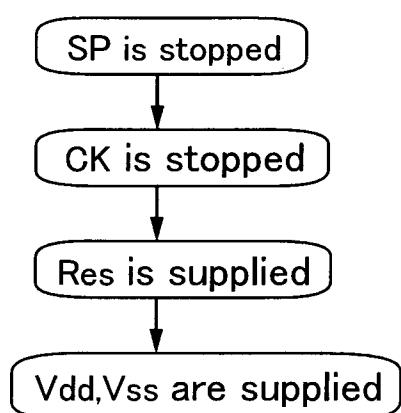

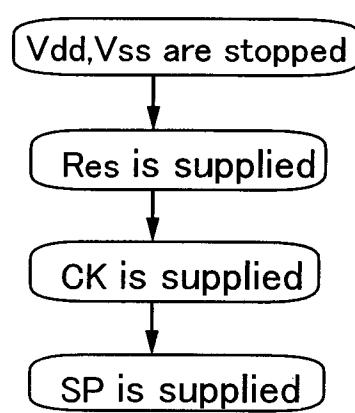

FIGS. 12A to 12D illustrate examples of a process for supplying and stopping signals supplied to a driver circuit.

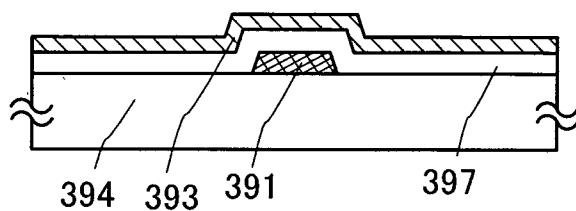

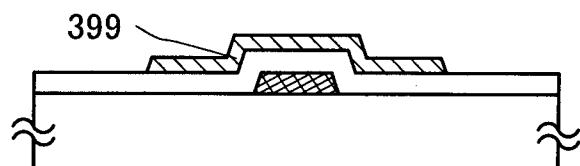

FIGS. 13A and 13B are a plan view and a cross-sectional view illustrating an example of a transistor.

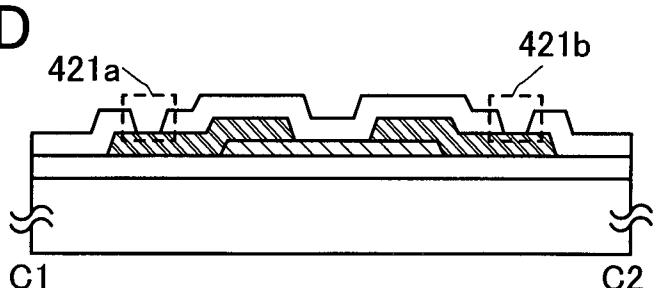

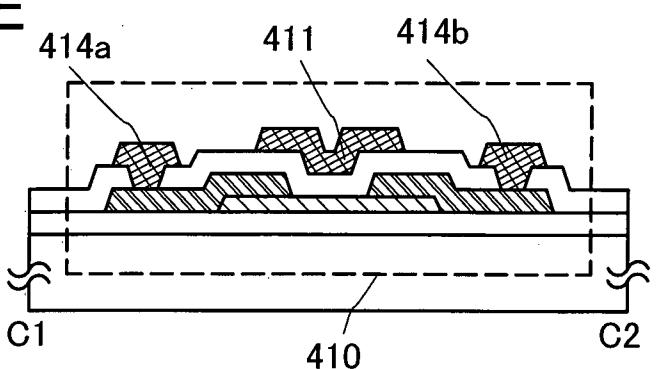

5 FIGS. 14A to 14E are cross-sectional views illustrating an example of a method for manufacturing a transistor.

FIGS. 15A to 15E are cross-sectional views illustrating an example of a method for manufacturing a transistor.

10 FIGS. 16A to 16D are cross-sectional views illustrating an example of a method for manufacturing a transistor.

FIGS. 17A to 17D are cross-sectional views illustrating an example of a method for manufacturing a transistor.

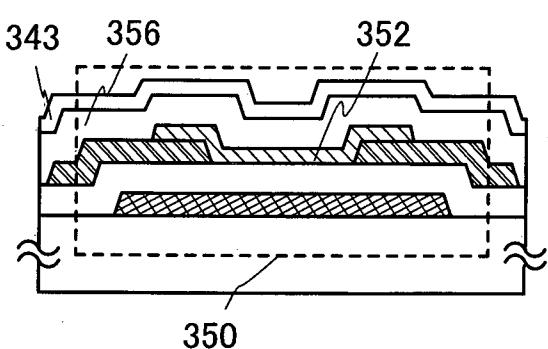

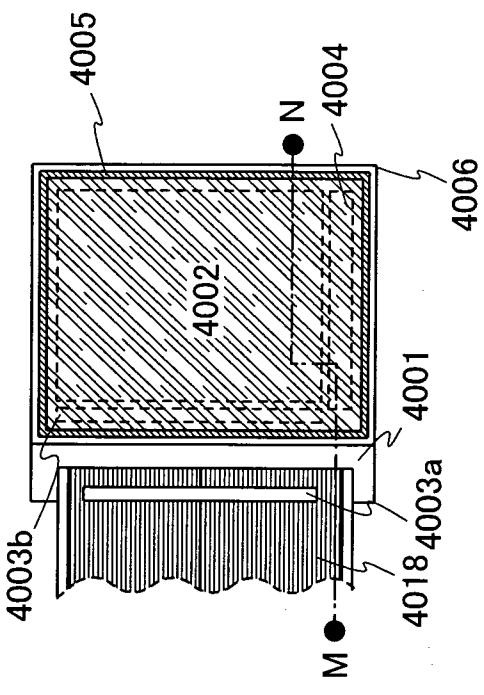

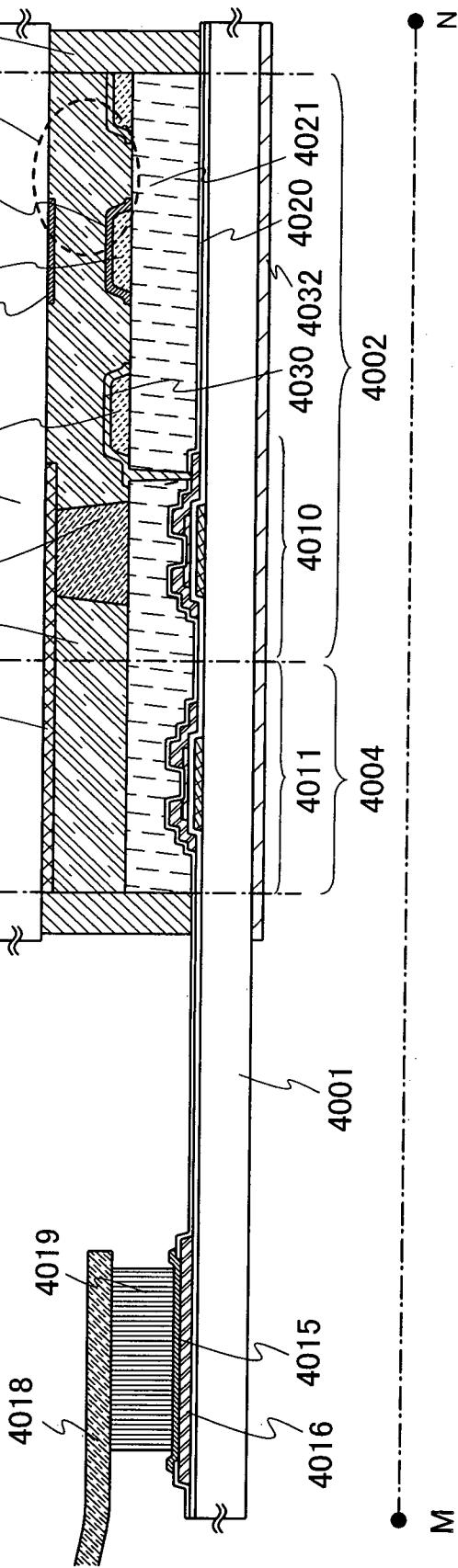

FIGS. 18A1, 18A2, and 18B are plan views and a cross-sectional view illustrating an example of a liquid crystal display panel.

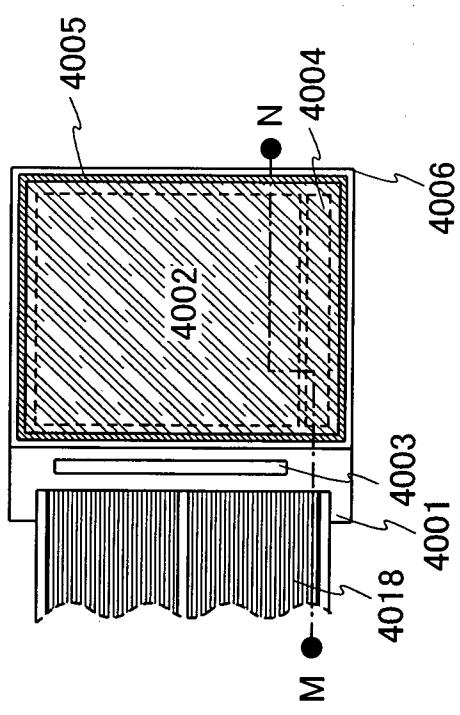

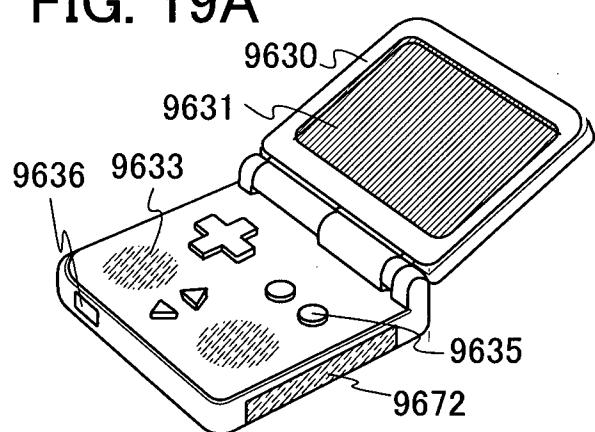

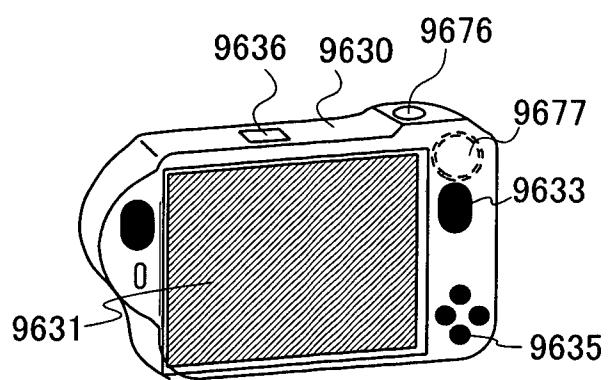

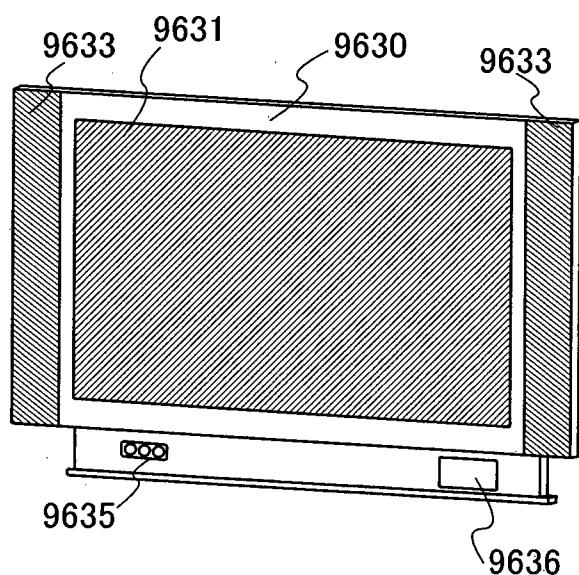

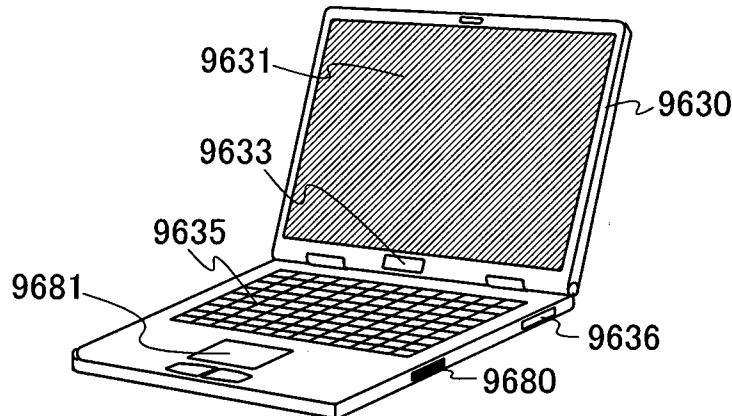

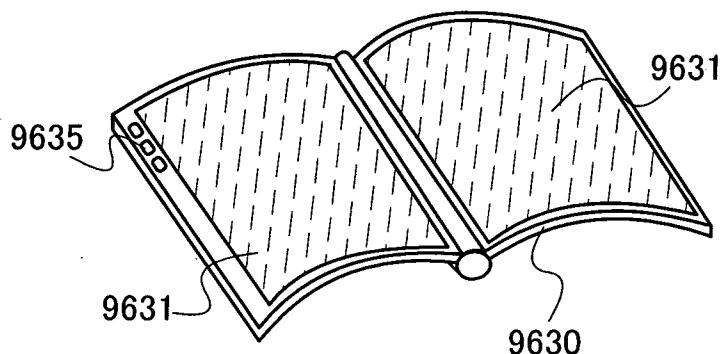

15 FIGS. 19A to 19C each illustrate an electronic device.

FIGS. 20A to 20D each illustrate an electronic device.

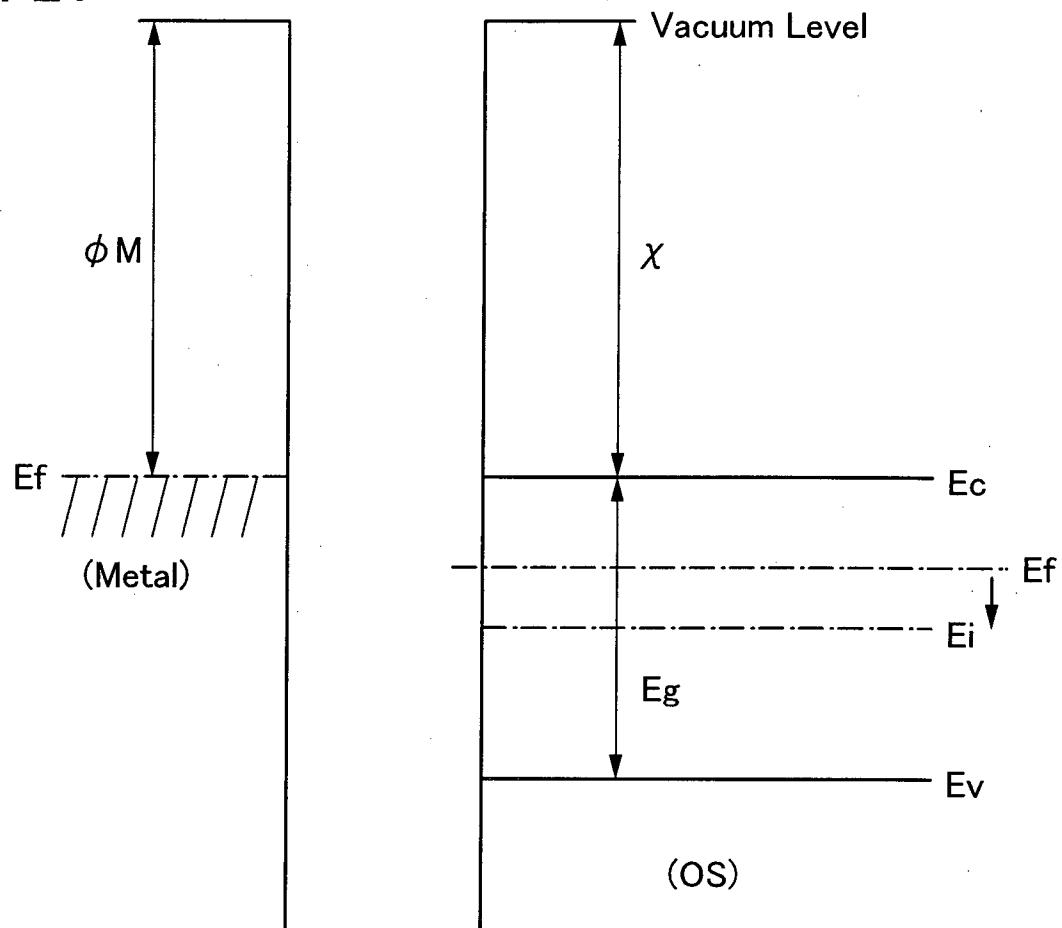

FIG. 21 is an energy band diagram.

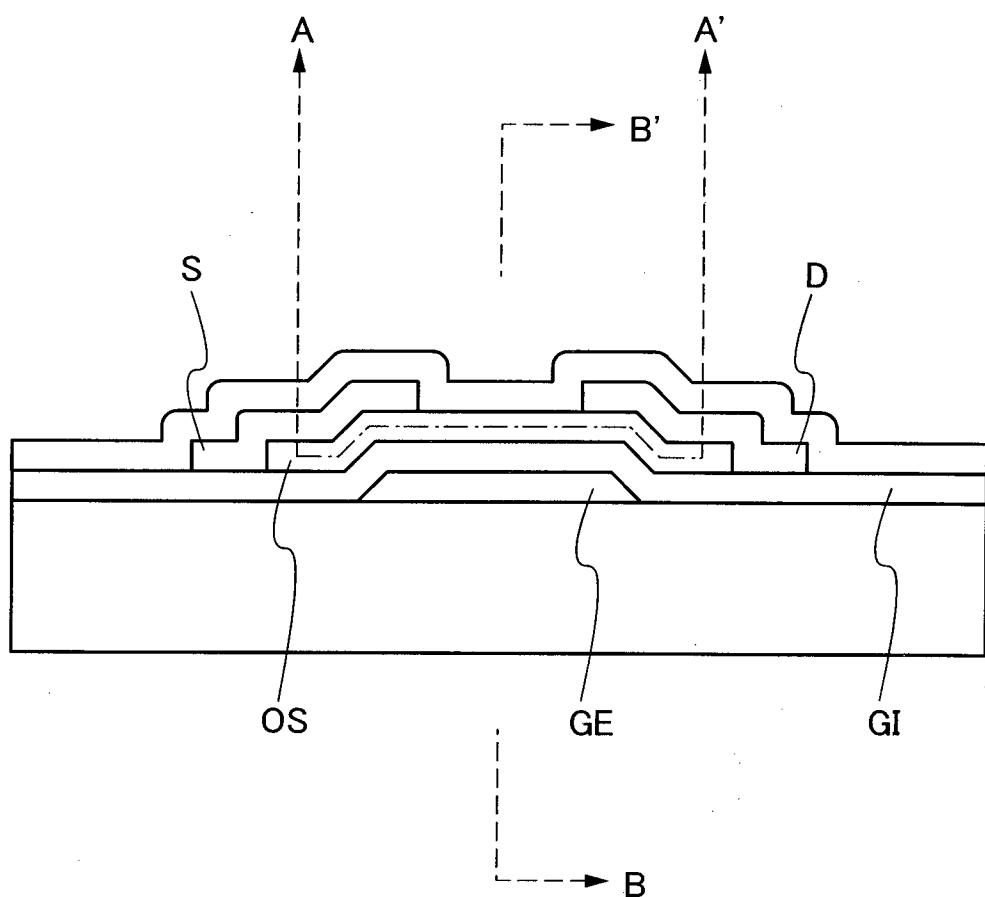

FIG. 22 illustrates a transistor including an oxide semiconductor.

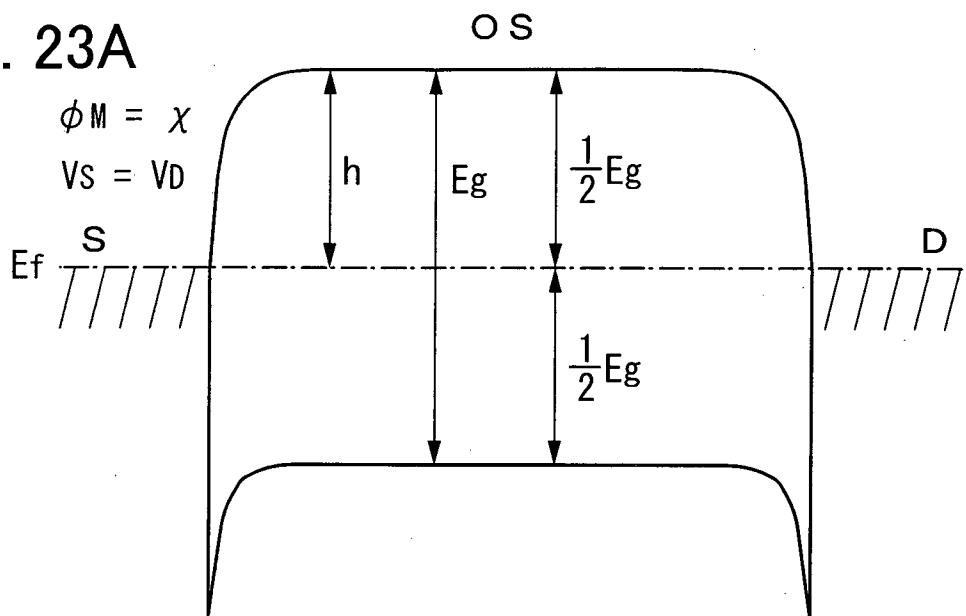

FIGS. 23A and 23B are energy band diagrams.

20 FIGS. 24A and 24B are energy band diagrams.

FIG. 25 is a graph showing electric characteristics of a transistor.

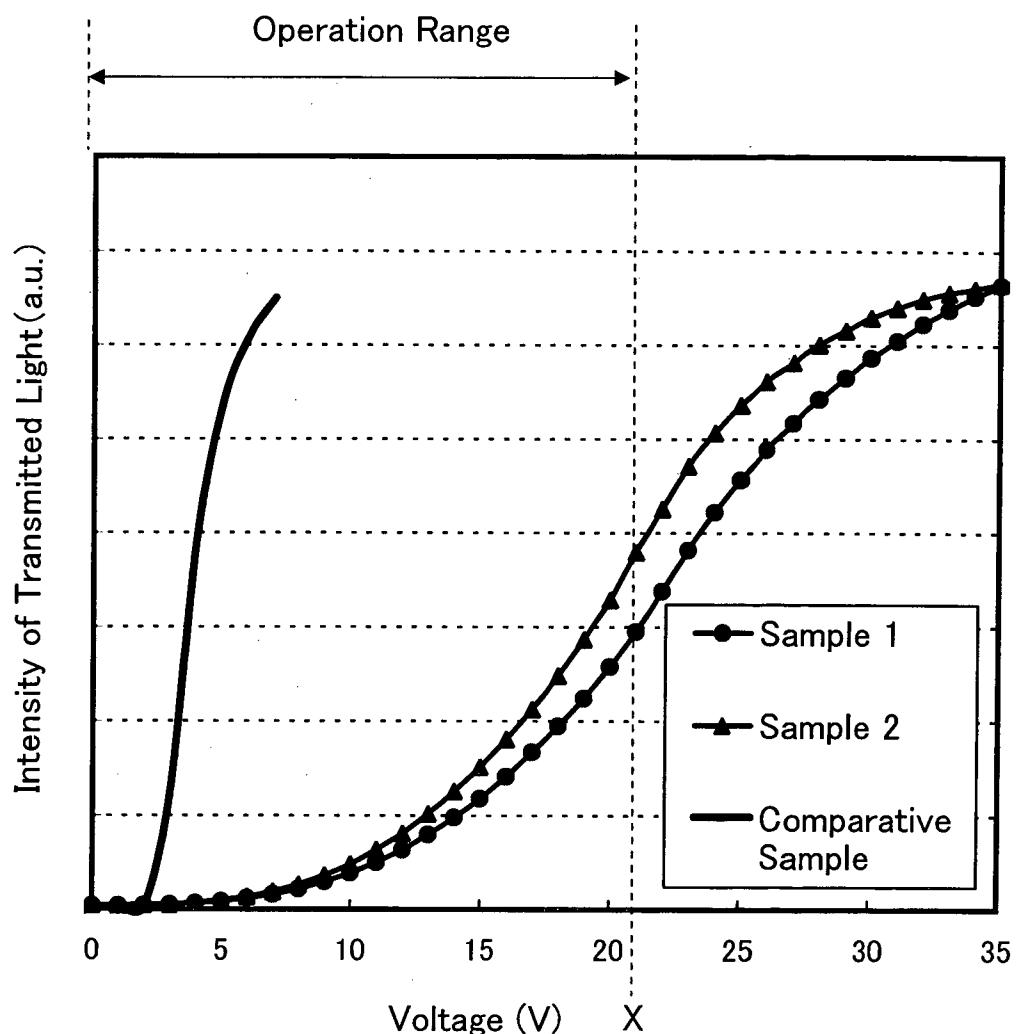

FIG. 26 is a graph showing a light transmittance characteristic of a liquid crystal material which exhibits a blue phase in accordance with voltage.

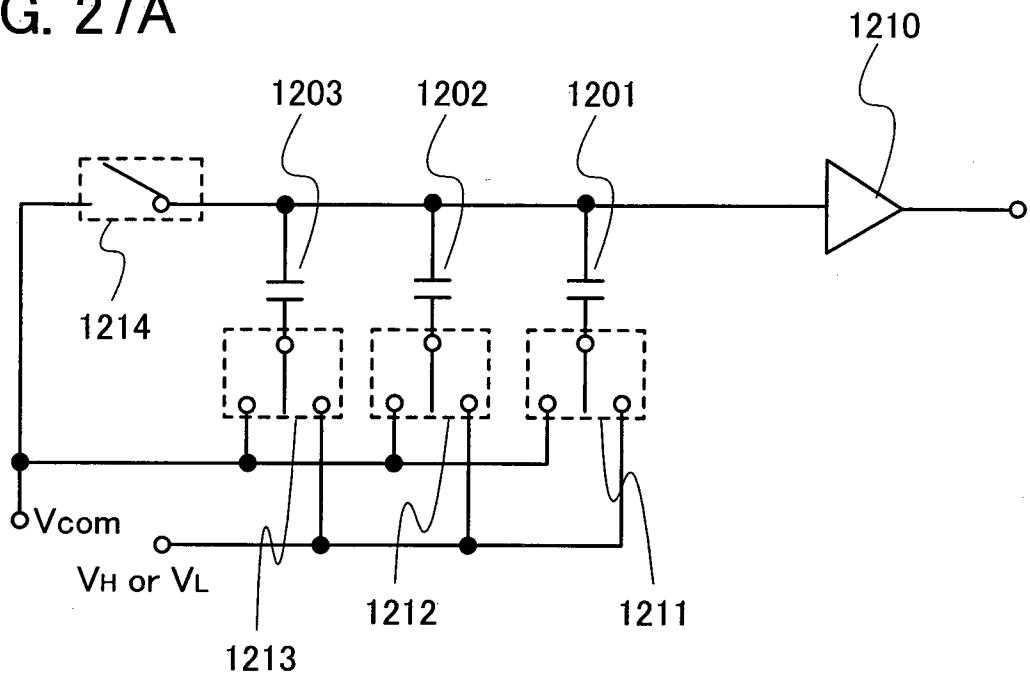

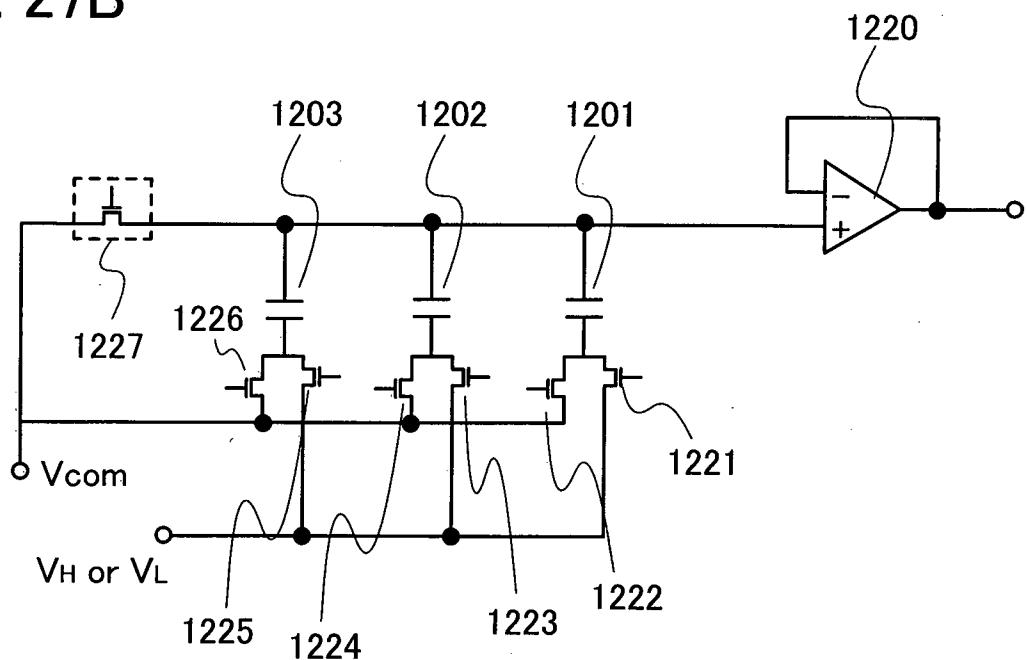

25 FIGS. 27A and 27B illustrate structural examples of a circuit of a capacitor digital-to-analog converter.

## BEST MODE FOR CARRYING OUT THE INVENTION

[0025]

30 Embodiments of the present invention will be described in detail with reference to the drawings. Note that the present invention is not limited to the following description and it will be readily appreciated by those skilled in the art that modes and details can be modified in various ways without departing from the spirit and the scope

of the present invention. Accordingly, the present invention should not be construed as being limited to the description of the embodiments. Note that in the embodiments of present invention to be described below, the same reference numerals are used to denote the same components in different drawings.

5 [0026]

Note that, each of the embodiments described below can be implemented by being combined with any of the other embodiments given in this specification unless otherwise specified.

[0027]

10 (Embodiment 1)

In this embodiment, an example of a display device which is one embodiment of the present invention will be described. Specifically, a structural example of a pixel in a pixel portion of a display device will be described.

[0028]

15 FIG. 1 illustrates a structural example of a display device which is one embodiment of the present invention. As is illustrated in FIG. 1, in a display device, a pixel portion 202 in which a plurality of pixels 201 are arranged in a matrix is provided over a substrate 200. In addition, the display device includes a scan line driver circuit 203 (a first driver circuit) and a signal line driver circuit 204 (a second driver circuit) as 20 circuits for driving the plurality of pixels 201. Whether the pixels 201 are in a selected state or in a non-selected state is determined for each row in accordance with a scan signal supplied through a first wiring 101 (a scan line) electrically connected to the scan line driver circuit 203. The pixel 201 selected by the scan signal is supplied with a video voltage (also referred to as an image signal, a video signal, or video data) through 25 a second wiring 102A (a signal line) electrically connected to the signal line driver circuit 204.

[0029]

Note that although FIG. 1 illustrates a structure where the scan line driver circuit 203 and the signal line driver circuit 204 are provided over the substrate 200, the 30 present invention is not limited to this structure. Only one of the scan line driver circuit 203 and the signal line driver circuit 204 may be provided over the substrate 200 and the other may be separately mounted. Alternatively, only the pixel portion 202

may be provided over the substrate 200 and the scan line driver circuit 203 and the signal line driver circuit 204 may be separately mounted.

[0030]

Further, although FIG. 1 illustrates an example where the plurality of pixels 201 are arranged in a matrix (a stripe arrangement), the present invention is not limited to this structure. As for the arrangement of the pixels 201, a delta arrangement or Bayer arrangement may be employed as an alternative to a stripe arrangement.

[0031]

As a display method in the pixel portion 202, a progressive method, an interlace method or the like can be employed. Color components controlled in the pixel at the time of color display are not limited to three colors of R, G, and B (R, G, and B represent red, green, and blue, respectively); for example, R, G, B, and W (W represents white), or R, G, B, and one or more of yellow, cyan, magenta, and the like can be employed. Further, the sizes of display regions of may be different between color components of dots. Note that the present invention is not limited to the application to a display device for color display; the present invention can also be applied to a display device for monochrome display.

[0032]

Further, although FIG. 1 illustrates a structure where the ratio of the number of first wirings 101 to the number of second wirings 102A, which are respectively extended in the row direction and the column direction of the pixels, is one to one, the present invention is not limited to this structure. For example, adjacent pixels 201 may share the first wiring 101 or the second wiring 102A and be driven.

[0033]

FIG. 2A is an equivalent circuit diagram illustrating a structural example of the pixel 201 in FIG. 1.

[0034]

The pixel 6400 includes a transistor (hereinafter, also referred to as a switching transistor) 6401, a liquid crystal element 6402, and a capacitor 6403. The liquid crystal element 6402 includes a liquid crystal material which exhibits a blue phase, between a pair of electrodes (a pixel electrode and a counter electrode).

## [0035]

5 A gate of the transistor 6401 is electrically connected to a scan line 6406, one of a source and a drain of the transistor 6401 is electrically connected to a signal line 6405, and the other of the source and the drain of the transistor 6401 is electrically connected to the pixel electrode. Here, in this embodiment, a transistor including a high-purity oxide semiconductor layer is used as the transistor 6401. In addition, the transistor 6401 is an n-channel transistor.

## [0036]

10 The capacitor 6403 includes an insulating layer provided as a dielectric between a pair of electrodes. The capacitance of the capacitor 6403 is set considering leakage current of a thin film transistor provided in the pixel portion or the like so that charge may be held for a predetermined period of time. The capacitance of the capacitor 6403 may also be set considering off-state current of the transistor 6401 or the like. In this embodiment, since the transistor 6401 includes a high-purity oxide 15 semiconductor layer, a capacitor is acceptable enough if it has capacitance less than or equal to 1/3, preferably less than or equal to 1/5 of the liquid crystal capacitance in each pixel.

## [0037]

20 Although the other of the source and the drain of the transistor 6401 is electrically connected to the capacitor 6403 in FIG. 2A, the present invention is not limited to the structure. A structure in FIG. 2B where the capacitor 6403 is not provided can be employed. In other words, in the present invention, since the transistor 6401 includes a high-purity oxide semiconductor layer and off-state current of the transistor 6401 is sufficiently low, voltage can be held for a sufficiently long period 25 of time even with a liquid crystal capacitor, which is formed of a pair of electrodes and a liquid crystal material therebetween, or the like. In addition, since the display device of this embodiment is a transmissive type or a transreflective type, omission of the capacitor 6403 leads to an improvement in aperture ratio.

## [0038]

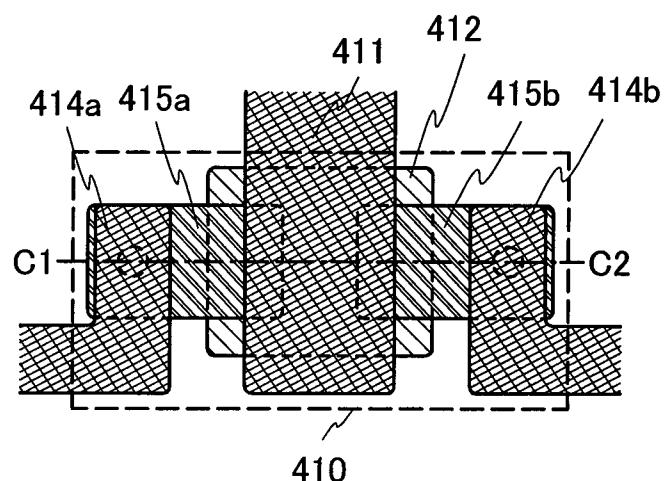

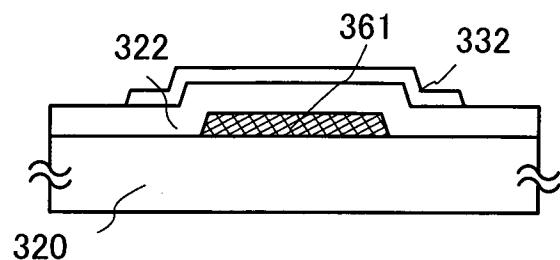

30 FIGS. 5A and 5B are an example of a plan view and a cross-sectional view of the transistor 6401 in the pixel 201. A transistor 420 illustrated in FIGS. 5A and 5B corresponds to the transistor 6401 and has a bottom-gate structure. The transistor 420

is also called an inverted-staggered transistor because a wiring (a gate electrode) 401 is provided under an oxide semiconductor layer 403 serving as a channel region, and a wiring (one of a source electrode and a drain electrode) 405a and a wiring (the other of the source electrode and the drain electrode) 405b are provided on the opposite side of the oxide semiconductor layer 403 from the wiring 401.

5 [0039]

The wiring 401 over a first substrate 441 serves as a gate electrode of the transistor 420. In addition, the wiring 401 may be a scan line itself or may be a wiring which is not a scan line but is electrically connected to a scan line.

10 [0040]

A gate insulating layer 402 is provided to cover the wiring 401. The oxide semiconductor layer 403 is provided over the gate insulating layer 402. The wiring 405a and the wiring 405b are provided over the oxide semiconductor layer 403. The wiring 405a and the wiring 405b are electrically connected to the oxide semiconductor layer 403 and one of them serves as a source electrode and the other of them serves as a drain electrode. Note that the wiring 405a may be a signal line itself or may be an electrode which is not a signal line but is electrically connected to a signal line.

15 [0041]

In addition, an insulating film 413 is provided to cover the transistor 420. An opening is formed in the insulating film 413. Through the opening, a first electrode 447 and the wiring 405b are electrically connected. Note that although the insulating film 413 has a three-layer structure of a first insulating film 407, a second insulating film 409, and a third insulating film 417 in FIG. 5B, the present invention is not limited to the structure. The insulating film 413 may have a single-layer structure, a two-layer structure, or a stack-layer structure of three or more layers.

20 [0042]

Next, the oxide semiconductor layer 403 will be described in detail.

25 [0043]

The oxide semiconductor layer 403 in this embodiment is an oxide semiconductor layer in which impurities, which adversely affect the electric characteristics of the transistor including the oxide semiconductor, are reduced to a very low level, that is, the oxide semiconductor layer 403 is a high-purity oxide

semiconductor. As a typical example of impurities which adversely affect the electric characteristics, hydrogen is given. Hydrogen is an impurity which may be a supplier (a donor) of carriers in an oxide semiconductor. An oxide semiconductor which includes a large amount of hydrogen may become an n-type oxide semiconductor.

5 Thus, a transistor including an oxide semiconductor which includes a large amount of hydrogen may be a normally-on transistor, and the on/off ratio of the transistor cannot be high enough. In this specification, a "high-purity oxide semiconductor" refers to an oxide semiconductor in which hydrogen is reduced as much as possible and which is intrinsic or substantially intrinsic. One example of a high-purity oxide semiconductor 10 is an oxide semiconductor the hydrogen concentration of which is  $5 \times 10^{19} / \text{cm}^3$  or less at most, preferably  $5 \times 10^{18} / \text{cm}^3$  or less, more preferably  $5 \times 10^{17} / \text{cm}^3$  or less, or less than  $1 \times 10^{16} / \text{cm}^3$ . A transistor is formed using, for a channel formation region, an oxide semiconductor film the carrier concentration of which is less than  $1 \times 10^{14} / \text{cm}^3$ , preferably less than  $1 \times 10^{12} / \text{cm}^3$ , more preferably less than  $1 \times 10^{11} / \text{cm}^3$  or less than 15  $6.0 \times 10^{10} / \text{cm}^3$ . Note that the hydrogen concentration of the oxide semiconductor layer may be measured by secondary ion mass spectrometry (SIMS).

[0044]

Further, it is preferable that the energy gap of the oxide semiconductor layer be 2 eV or more, preferably 2.5 eV or more, more preferably 3 eV or more.

20 [0045]

The high-purity oxide semiconductor layer, which is obtained by drastically removing hydrogen included in the oxide semiconductor layer as described above, is used for a channel formation region of a transistor, whereby a transistor with an extremely small off-state current value can be provided.

25 [0046]

Here, off-state current (also referred to as leakage current) refers to current that flows between a source and a drain of a transistor when gate voltage between -5 V to -20 V is applied. In the transistor including an oxide semiconductor which is disclosed in this specification, a current value per channel width (w) of 1  $\mu\text{m}$  is 100 30 aA/ $\mu\text{m}$  or less, preferably 10 aA/ $\mu\text{m}$  or less, more preferably 1 aA/ $\mu\text{m}$  or less.

[0047]

Next, electrical conduction mechanism of a transistor including an oxide semiconductor layer will be described with reference to FIG. 21, FIG. 22, FIGS. 23A and 23B, and FIGS. 24A and 24B. Note that the following description is based on an ideal situation for ease of understanding and does not entirely reflect the actual situation.

5 Note that the following description is just a consideration and is irrelevant to the validity of the present invention.

[0048]

FIG. 21 shows the relationship between the work function ( $\phi_M$ ) of a metal (Metal) and the electron affinity ( $\chi$ ) of an oxide semiconductor (OS). The Fermi level of the metal is denoted by  $E_F$ . The Fermi level of the oxide semiconductor is denoted by  $E_f$ . The energy at the bottom of the conduction band is denoted by  $E_C$ . The energy at the top of the valence band is denoted by  $E_V$ . The intrinsic Fermi level is denoted by  $E_i$ . The energy band gap of the oxide semiconductor is denoted by  $E_g$ . Note that the energy band gap ( $E_g$ ) of the oxide semiconductor is 3.0 eV to 3.5 eV.

15 [0049]

In FIG. 21, in the case of a conventional oxide semiconductor having n-type conductivity, the Fermi level ( $E_f$ ) is apart from the intrinsic Fermi level ( $E_i$ ) positioned in the middle of the band gap ( $E_g$ ) and is positioned near the conduction band ( $E_C$ ).

[0050]

20 Here, when the oxide semiconductor is made closer to an intrinsic semiconductor by decreasing the carrier density, the Fermi level ( $E_f$ ) of the oxide semiconductor becomes closer to the intrinsic Fermi level ( $E_i$ ). In this embodiment, an intrinsic or substantially intrinsic oxide semiconductor is in a state in which carrier density is decreased and the Fermi level ( $E_f$ ) is made close or equal to the intrinsic 25 Fermi level ( $E_i$ ).

[0051]

The intrinsic or substantially intrinsic oxide semiconductor in this embodiment is obtained based on the following technical idea.

[0052]

30 Hydrogen contained in an oxide semiconductor is one of the factors that make the oxide semiconductor have n-type conductivity. In the oxide semiconductor,

hydrogen serves as a donor and forms a shallow level which is 0.1 eV to 0.2 eV below the conduction band and thereby increases the carrier concentration.

[0053]

In addition, deficiency of oxygen (oxygen deficiency) which is a main component of the oxide semiconductor is another factor that makes the oxide semiconductor have n-type conductivity. The oxygen deficiency forms a deep donor level in the oxide semiconductor and thereby increases the carrier concentration.

[0054]

Although many studies on physical properties of a semiconductor, such as density of states (DOS), have been conducted, they do not include an idea of sufficiently reducing defect levels itself. In this embodiment, a highly purified intrinsic oxide semiconductor is obtained by removal of water or hydrogen, which might increase the DOSs, from the oxide semiconductor. This is based on an idea of sufficiently reducing the DOSs itself.

15 [0055]

In other words, in this embodiment, an impurity such as hydrogen, which is one of the factors that make the oxide semiconductor have n-type conductivity, is removed from an oxide semiconductor as much as possible, and oxygen deficiency is also removed, whereby the oxide semiconductor is highly purified. When the oxide semiconductor is highly purified, an intrinsic or substantially intrinsic oxide semiconductor can be obtained. Thus, in FIG. 21, the Fermi level ( $E_f$ ) can be substantially equal to the intrinsic Fermi level ( $E_i$ ).

[0056]

Specifically, the concentration of hydrogen in the oxide semiconductor is decreased to  $5 \times 10^{19} /cm^3$  or lower, preferably  $5 \times 10^{18} /cm^3$  or lower, more preferably  $5 \times 10^{17} /cm^3$  or lower. Further, the carrier concentration of the oxide semiconductor (for example, the carrier concentration is less than  $1 \times 10^{12} /cm^3$ , preferably  $1.45 \times 10^{10} /cm^3$  or less) is preferably much lower than that of a conventional oxide semiconductor.

[0057]

30 FIG. 22 illustrates an example of an inverted-staggered bottom-gate thin film transistor that is formed using an intrinsic or substantially intrinsic oxide semiconductor.

An oxide semiconductor layer (OS) is provided over a gate electrode (GE) with a gate insulating film (GI) provided therebetween. A source electrode (S) and a drain electrode (D) are provided thereover.

[0058]

5 It is preferable that a Schottky barrier be not formed between the oxide semiconductor, and the source and the drain. In this embodiment, the electron affinity ( $\chi$ ) of the oxide semiconductor is substantially equal to the work function ( $\phi_M$ ) of a metal used for the source electrode and the drain electrode. For example, it is said that the electron affinity ( $\chi$ ) is 4.3 eV in the case where the band gap ( $E_g$ ) of the oxide 10 semiconductor is 3.15 eV; thus, the source electrode and the drain electrode may be formed with a structure in which titanium (Ti), which has a work function ( $\phi_M$ ) of about 4.3 eV, is in contact with the oxide semiconductor.

[0059]

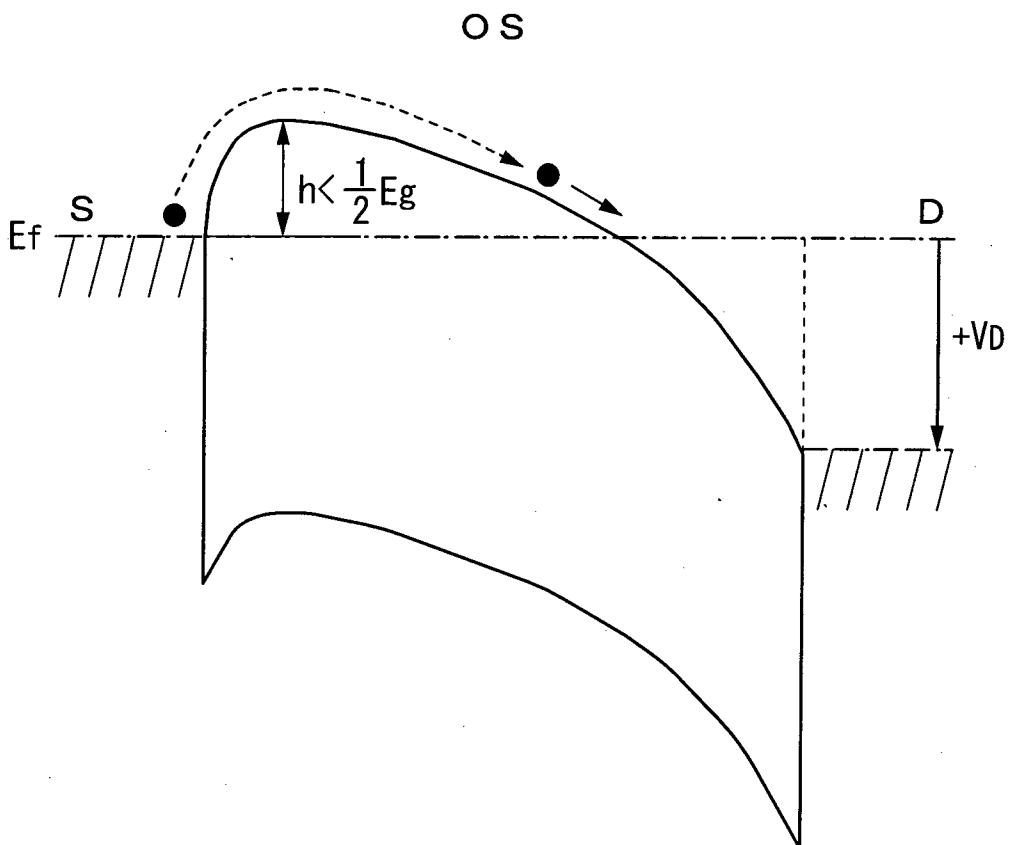

15 FIGS. 23A and 23B are energy band diagrams (schematic diagrams) in an A-A' cross section in FIG. 22. FIG. 23A illustrates the case where a potential difference between the source (S) and the drain (D) is zero (the source and the drain have the same potential,  $V_{DS} = 0$  V). FIG. 23B illustrates the case where the potentials of the drain and the gate are higher than that of the source ( $V_{DS} > 0$  V,  $V_{GS} > 0$ ).

[0060]

20 In FIG. 23B, a black circle (•) indicates an electron. When positive potentials are applied to the gate and the drain (D), the electron is injected into the oxide semiconductor (OS) over a barrier (h) and flows toward the drain (D). The height of the barrier (h) changes depending on the gate voltage and the drain voltage. In the case where positive drain voltage is applied, the height of the barrier is smaller than the 25 height of the barrier in FIG. 23A where no voltage is applied, i.e.,  $1/2E_g$ . Thus, when positive voltage is applied to the gate, the potential barrier is lowered as in FIG. 23B and the transistor is in an on state allowing current to flow. On the other hand, when voltage is not applied to the gate ( $V_g = 0$  V), the transistor is in an off state and current does not flow because of the high potential barrier ( $1/2 E_g$ ).

30 [0061]

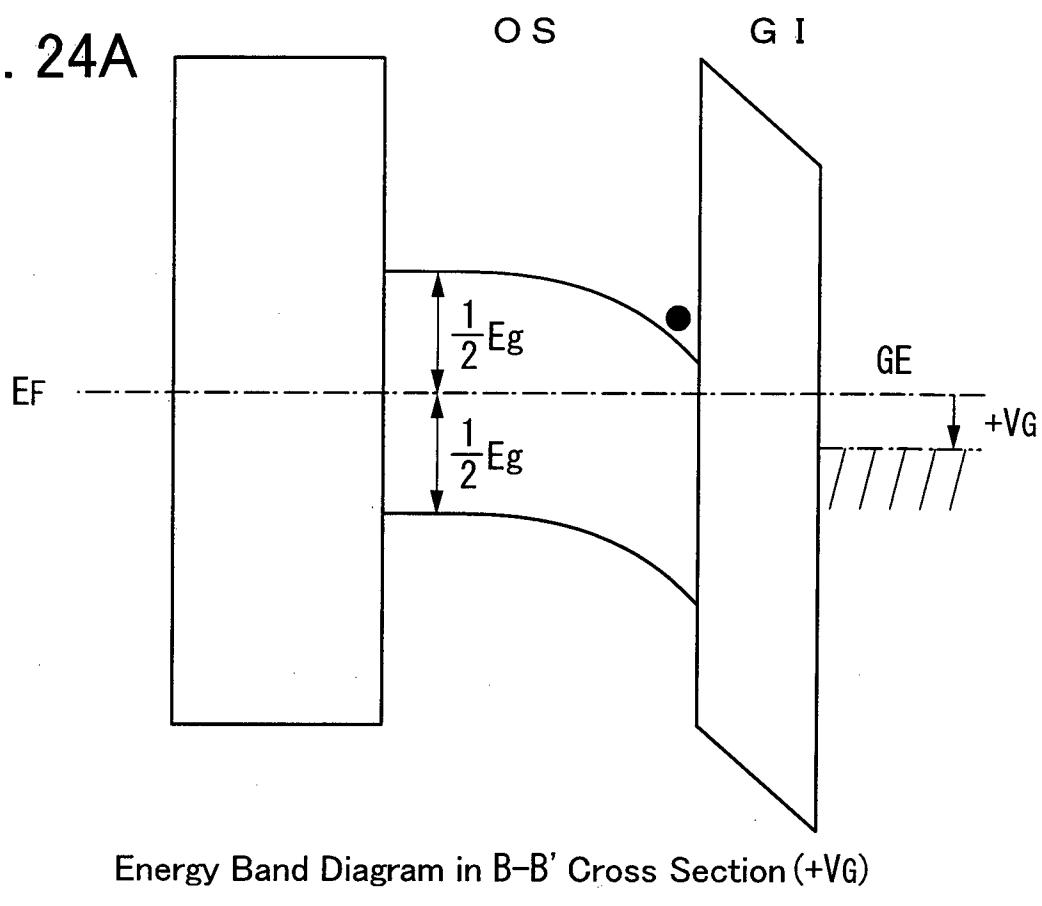

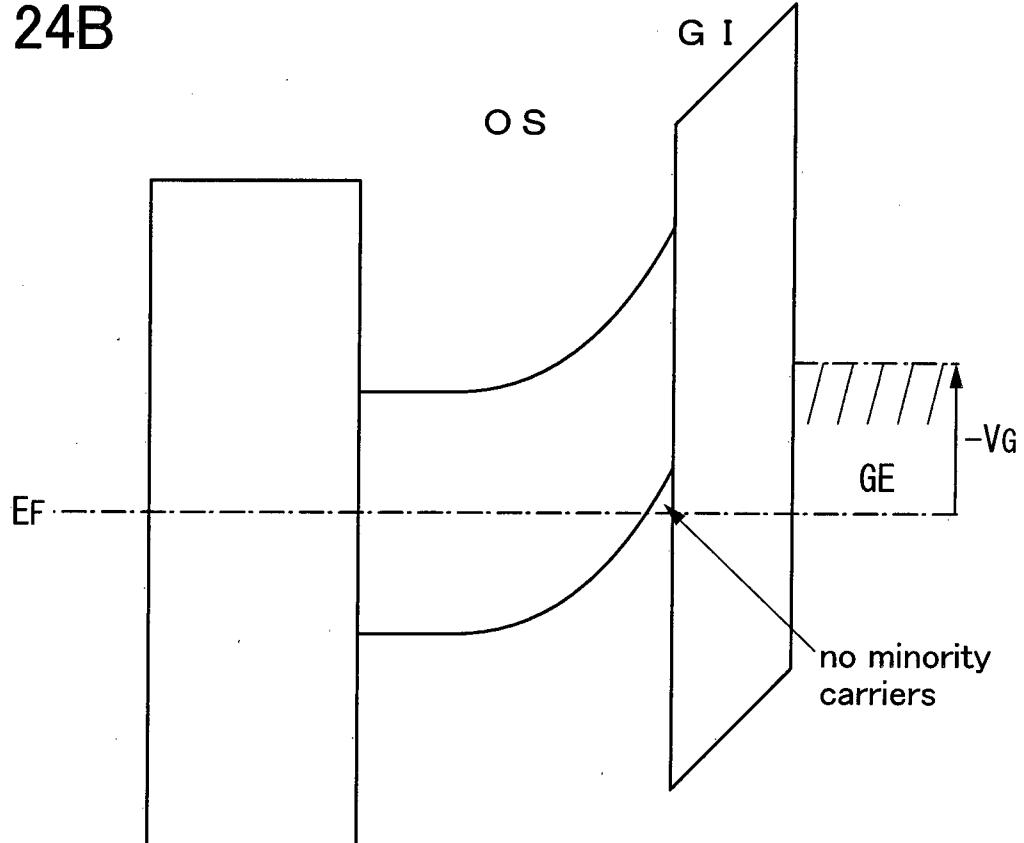

FIGS. 24A and 24B are energy band diagrams (schematic diagrams) along

B-B' cross-section in FIG. 22.

[0062]

As illustrated in FIG. 24A, when a positive potential is applied to the gate, the electron moves in the vicinity of an interface between the gate insulating film (GI) and the oxide semiconductor (OS) (the lowest part of the oxide semiconductor that is energetically stable).

[0063]

On the other hand, when a negative potential (reverse bias) is applied to the gate, as illustrated in FIG. 24B, the current value between the source and drain is extremely close to zero because holes that are minority carriers do not exist substantially.

[0064]

In this manner, when a transistor is formed using an intrinsic or substantially intrinsic oxide semiconductor, current which flows between the source and the drain when a negative potential is applied to the gate (off-state current) can be less than or equal to  $10^{-13}$  A which is the measuring limit. In addition, the temperature characteristics of the transistor formed using an intrinsic or substantially intrinsic oxide semiconductor are favorable. Typically, in the temperature range of from -25 °C to 150 °C, the current-voltage characteristics of the transistor, such as on-state current, off-state current, field-effect mobility, a subthreshold value (an S value), and a threshold voltage, hardly change and deteriorate due to temperature.

[0065]

Note that in the intrinsic or substantially intrinsic oxide semiconductor, interface characteristics with the gate insulating film become noticeable. Therefore, an interface between the gate insulating film and the oxide semiconductor is preferably favorable. Specifically, for example, it is preferable to use an insulating film formed by a CVD method with the use of high-density plasma generated with a power frequency in the range of the VHF band to the microwave band, an insulating film formed by a sputtering method, or the like.

[0066]

Next, hot-carrier degradation of a transistor including an oxide semiconductor

will be described.

[0067]

The hot-carrier degradation refers to a phenomenon in which electrons that are accelerated to high speed become fixed charges by being injected into a gate insulating film from a channel in the vicinity of drain or form a trap level at the interface between the gate insulating film and the oxide semiconductor film, and thereby causing deterioration such as change in threshold voltage or gate leakage current. The factors of the hot-carrier degradation are channel-hot-electron injection (CHE injection) and drain-avalanche-hot-carrier injection (DAHC injection).

10 [0068]

Since the band gap of silicon is as small as 1.12 eV, electrons are likely to be generated like an avalanche owing to an avalanche breakdown, and electrons that are accelerated to be so rapid as to go over a barrier to the gate insulating film are increased in number. On the other hand, the oxide semiconductor described in this embodiment has a wide band gap of 3.15 eV; therefore, the avalanche breakdown is unlikely to occur and resistance to the hot-carrier degradation is higher than that of silicon.

15 [0069]

Note that although the band gap of silicon carbide which is one of materials having high breakdown voltage and that of an oxide semiconductor are substantially equal to each other, electrons are less likely to be accelerated in an oxide semiconductor because the mobility in an oxide semiconductor is smaller than that of silicon carbide by approximately two orders of magnitude. Further, a barrier between an oxide semiconductor and an oxide film that is a gate insulating film is larger than a barrier between any of silicon carbide, gallium nitride, or silicon and an oxide film that is a gate insulating film; therefore, in an oxide semiconductor, the number of electrons injected to the oxide film is extremely small. Accordingly, in a transistor including an intrinsic or substantially intrinsic oxide semiconductor, hot-carrier degradation is less likely to be caused and drain breakdown voltage is high compared with a transistor including silicon carbide, gallium nitride, or silicon. In addition, low-concentration impurity regions do not need to be provided between an oxide semiconductor serving as a channel and source and drain electrodes, whereby the transistor structure can be very simple and the number of manufacturing steps can be reduced.

## [0070]

From the above, a transistor including an intrinsic or substantially intrinsic oxide semiconductor has high drain breakdown voltage of, specifically, 100 V or more, preferably 500 V, more preferably 1 kV or more.

## 5 [0071]

Note that since off-state current is extremely small in the transistor including an intrinsic or substantially intrinsic oxide semiconductor, it is difficult to precisely measure an off-state current value by a measuring method for transistor elements having a general size. Therefore, a test element group (also referred to as TEG) for 10 measurement is formed for measurement. The off-state current which is thus measured will be described below.

## [0072]

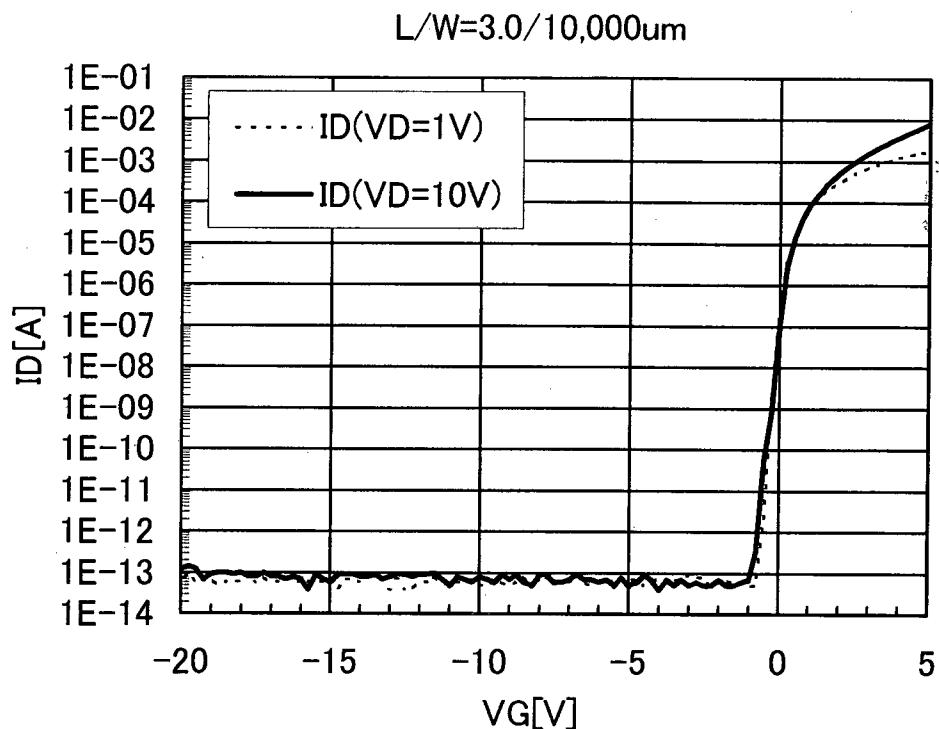

Two hundreds transistors each with  $L/W = 3 \mu\text{m}/50 \mu\text{m}$  were connected in parallel to provide a transistor with  $L/W = 3 \mu\text{m}/10000 \mu\text{m}$  in TEG. FIG. 25 shows the 15 initial characteristics of the transistor. Here,  $V_g$  is in the range of from -20 V to +5 V. In order to measure the initial characteristics of the transistor, change of characteristics of current between a source and a drain (hereinafter referred to as a drain current or  $I_d$ ), i.e.,  $V_g$ - $I_d$  characteristics, were measured under the conditions where the substrate 20 temperature was set to room temperature, the voltage between the source and the drain (hereinafter referred to as a drain voltage or  $V_d$ ) was set to 10 V, and the voltage between the source and the gate (hereinafter referred to as a gate voltage or  $V_g$ ) was changed from -20 V to +20 V.

## [0073]

As shown in FIG. 25, when  $V_d$  is 1 V or 10 V and the gate voltage is in the 25 range of -5V to -20V, the transistor having a channel width  $W$  of 10000  $\mu\text{m}$  has drain current (off-state current) of  $1 \times 10^{-13} [\text{A}]$  or less, which is less than or equal to the resolution (100 fA) of a measuring system (a semiconductor parameter analyzer, Agilent 4156C manufactured by Agilent Technologies Inc.). This off-state current value corresponds to  $1 \times 10^{-17} \text{ A}/\mu\text{m}$  ( $= 10 \text{ aA}/\mu\text{m}$ ) per channel width of 1  $\mu\text{m}$ .

## 30 [0074]

The reason why the off-state current of the transistor can be  $1 \times 10^{-13} [\text{A}]$  or

less as shown in FIG. 25 is that the hydrogen concentration of the oxide semiconductor layer is sufficiently reduced. In other words, the hydrogen concentration of the oxide semiconductor layer is  $5 \times 10^{19}$  atoms/cm<sup>3</sup> or less, preferably  $5 \times 10^{18}$  atoms/cm<sup>3</sup> or less, more preferably  $5 \times 10^{17}$  atoms/cm<sup>3</sup> or less or less than  $1 \times 10^{16}$  atoms/cm<sup>3</sup>. Note that 5 the hydrogen concentration of the oxide semiconductor layer may be measured by secondary ion mass spectrometry (SIMS).

[0075]

The carrier concentration of the oxide semiconductor layer is less than  $1 \times 10^{14}$  /cm<sup>3</sup>, preferably less than  $1 \times 10^{12}$  /cm<sup>3</sup>, more preferably less than  $1 \times 10^{11}$  /cm<sup>3</sup> or less 10 than  $6.0 \times 10^{10}$  /cm<sup>3</sup>. In other words, the carrier concentration of the oxide semiconductor layer is extremely close to zero. Note that for measuring the carrier concentration, for example, a MOS capacitor may be formed and a CV measurement result (CV characteristics) thereof may be evaluated.

[0076]

15 As described above, even in a transistor having a channel width  $W$  of  $1 \times 10^4$   $\mu\text{m}$  and a channel length of  $3 \mu\text{m}$ , excellent electric characteristics, off-state current of  $10^{-13}$  A or less and the subthreshold swing (S value) of 0.1 V/dec. or less (the thickness of the gate insulating film is 100 nm), can be obtained. By highly purifying the oxide semiconductor so that the amount of impurities in the oxide semiconductor may be as 20 small as possible, favorable operation of the transistor can be realized. When a transistor having an extremely small value of off-state current (off-state current value) is used as the transistor 6401 in FIGS. 2A and 2B, an electrical signal such as an image signal can be held for a longer period of time.

[0077]

25 Specifically, in the transistor including the above oxide semiconductor layer, off-state current per channel width of  $1 \mu\text{m}$  can be  $1 \times 10^{-17}$  A or less. On the other hand, in a transistor including low-temperature polysilicon, for example, design or the like is performed while estimating the amount of the off-state current at around  $1 \times 10^{-12}$  A. Thus, the voltage holding period of a transistor including an oxide semiconductor 30 can be approximately  $10^5$  times as long as that of a transistor including low-temperature polysilicon, when the storage capacitance is substantially the same (approximately 0.1

pF). For example, display is generally performed at 60 frames per second (16 msec per frame) in a pixel including a transistor which includes low-temperature polysilicon. The same can be said for the case of still image display because a decrease in rate (an increase in writing interval) will cause a decrease in voltage of a pixel and a defect of display. In contrast, in the case where the transistor including the above oxide semiconductor layer is used, since off-state current is small, the holding period of one signal writing can be approximately 1600 seconds, that is,  $10^5$  times as long as that of the transistor including low-temperature polysilicon. Thus, a still image can be displayed on a display portion even with a small number of writing of image signals. Since the holding period can be extended, the frequency of signal writing can be decreased particularly when a still image is displayed. Therefore, a reduction in power consumption of the display device can be achieved.

[0078]

Further, a transistor including amorphous silicon has off-state current of  $1 \times 10^{-13}$  A or more per channel width of 1  $\mu$ m. Thus, the voltage holding period of a transistor including a high-purity oxide semiconductor can be approximately  $10^4$  times as long as that of a transistor including amorphous silicon, when the storage capacitance is substantially the same (approximately 0.1 pF).

[0079]

FIG. 4A shows a relationship between a writing period and a holding period (also referred to as one frame period). In FIG. 4A, periods 251 and 252 each are a holding period, and periods 261 and 262 each are a writing period. In FIG. 4A, the polarity of voltage (in the diagram, the polarity is indicated by a plus sign or a minus sign) applied to a liquid crystal element, which is a display element, is inverted in every holding period. Accordingly, the electric field applied to the liquid crystal element is not biased, and the degree of deterioration of the liquid crystal element can be decreased. FIG. 4B shows the relationship in the case of writing voltage whose polarity is inverted a plurality of times in each of the writing periods 261 and 262 of FIG. 4A. By writing voltage whose polarity is inverted a plurality of times in each of the writing periods 261 and 262 as illustrated in FIG. 4B, the degree of deterioration of a liquid crystal element can be further decreased. Note that the polarity of the voltage applied at the end of

each of the writing periods 261 and 262 is a polarity to be held in the holding period.

[0080]

When the above transistor including a high-purity oxide semiconductor layer is used, the holding period (the period 251 or the period 252) can be set longer.

5 Therefore, the frequency of writing into a pixel can be drastically decreased particularly when a still image is displayed. Accordingly, in the case of displaying a still image or the like which involves less frequent changes in display, the number of times of signal writing to a pixel can be decreased, and thus power consumption can be reduced.

[0081]

10 In displaying a still image, refresh operation can be performed as appropriate in the holding period, in accordance with the holding rate of the voltage applied to a liquid crystal element. For example, the refresh operation can be performed at the time when the voltage decreases to a predetermined level with respect to a value (initial value) of a voltage just after the signal writing into the pixel electrode of the liquid crystal element.

15 The predetermined level is preferably set, with respect to the initial value, to a voltage at which flickers are not sensed. Specifically, it is preferable to perform the refresh operation (rewriting) every time the voltage reaches a value less than the initial value by 10 %, preferably 3 %.

[0082]

20 During the holding period in still image display, a counter electrode (also referred to as a common electrode) can be put in a floating state. Specifically, a switch may be provided between the counter electrode and a power source for supplying a common potential to the counter electrode. During the writing period, the switch may be turned on and the common potential may be supplied to the counter electrode; after 25 that, during the holding period, the switch may be turned off and the counter electrode may be put in a floating state.

[0083]

Note that the voltage applied to a liquid crystal element in FIGS. 4A and 4B may be input in accordance with dot inversion driving, source line inversion driving, 30 gate line inversion driving, frame inversion driving, or the like.

[0084]

Next, a liquid crystal material which exhibits a blue phase will be described.

## [0085]

A liquid crystal material which exhibits a blue phase contains liquid crystal and a chiral agent. As the liquid crystal, thermotropic liquid crystal, low-molecular liquid crystal, high-molecular liquid crystal, ferroelectric liquid crystal, anti-ferroelectric liquid crystal, or the like is used. These liquid crystal materials exhibit a cholesteric phase, a cholesteric blue phase, a smectic phase, a smectic blue phase, a cubic phase, a chiral nematic phase, an isotropic phase, or the like depending on conditions. The chiral agent is employed to align the liquid crystal in a helical structure and to make the liquid crystal exhibit a blue phase. For example, a liquid crystal material into which a chiral agent is mixed at 5 wt% or more may be used for a liquid crystal layer. For the chiral agent, a material which has a high compatibility with liquid crystal and has a strong twisting power is used. In addition, as a material, either an R-enantiomer or an S-enantiomer is favorable, and the use of a racemic body in which an R-enantiomer and an S-enantiomer are mixed at a ratio of 50:50 is preferably avoided.

## 15 [0086]

A cholesteric blue phase and a smectic blue phase, which are blue phases, are seen in a liquid crystal material having a cholesteric phase or a smectic phase with a relatively short helical pitch of 500 nm or less. The alignment of the liquid crystal material has a double twist structure.

## 20 [0087]

When an electric field is not applied, a liquid crystal material which exhibits a blue phase is optically isotropic. When an electric field is applied, birefringence of the liquid crystal material is induced, whereby light is modulated. In other words, a display device including a liquid crystal material which exhibits a blue phase is of a normally black mode. Note that in application of an electric field to a liquid crystal material which exhibits a blue phase, an electric field is preferably applied horizontally so as to be substantially parallel to a substrate plane. Further, since a display device including a liquid crystal material which exhibits a blue phase does not need the formation of an alignment film, an inexpensive display device can be provided.

## 30 [0088]

Note that the blue phase hardly appears outside a narrow temperature range; therefore, it is preferable that a photocurable resin and a photopolymerization initiator

be added to a liquid crystal material and polymer stabilization treatment may be performed in order to widen the temperature range. The polymer stabilization treatment is performed in such a manner that a liquid crystal material containing a liquid crystal, a chiral agent, a photocurable resin, and a photopolymerization initiator is 5 irradiated with light having a wavelength with which the photocurable resin and the photopolymerization initiator react. Light irradiation in this polymer stabilization treatment may be performed on a liquid crystal material exhibiting an isotropic phase or a blue phase under the control of temperature. For example, the polymer stabilization treatment is performed in such a manner that the temperature of a liquid crystal layer is 10 controlled and the liquid crystal layer exhibiting a blue phase is irradiated with light. However, the polymer stabilization treatment is not limited to this method and may be performed in such a manner that a liquid crystal layer exhibiting an isotropic phase at a temperature within +10 °C, preferably +5 °C of the phase transition temperature between the blue phase and the isotropic phase is irradiated with light. The phase 15 transition temperature between a blue phase and an isotropic phase refers to a temperature at which the phase changes from the blue phase to the isotropic phase when the temperature rises, or a temperature at which the phase changes from the isotropic phase to the blue phase when the temperature decreases.

[0089]

20 As an example of the polymer stabilization treatment, the following method can be given: after heating a liquid crystal layer to the isotropic phase, the temperature of the liquid crystal layer is gradually decreased so that the phase changes to the blue phase, and then, irradiation with light is performed while the temperature at which the blue phase is exhibited is kept. Alternatively, another method can be employed in 25 which after the phase changes to the isotropic phase by gradually heating a liquid crystal layer, the liquid crystal layer can be irradiated with light under a temperature within +10 °C, preferably +5 °C of the phase transition temperature between the blue phase and the isotropic phase (in the state where the liquid crystal layer is exhibiting the isotropic phase). Moreover, in the case where an ultraviolet curable resin (a UV curable resin) 30 is used as the photocurable resin contained in the liquid crystal material, the liquid crystal layer may be irradiated with ultraviolet rays. Even in the case where the blue

phase is not exhibited, if polymer stabilization treatment is performed by irradiation with light at a temperature within +10 °C, preferably +5 °C of the phase transition temperature between the blue phase and the isotropic phase (in the state where the liquid crystal layer is exhibiting the isotropic phase), the response time can be made as short as

5 1 msec or less and high-speed response is possible.

[0090]

In addition, resistivity (or specific resistance) of the liquid crystal material which exhibits a blue phase is preferably made as high as possible. This is because if the resistivity of the liquid crystal material is low, charge will leak to the counter 10 electrode from the pixel electrode through the liquid crystal layer, which may affect the voltage value applied to the liquid crystal layer. Thus, in one embodiment of the present invention, the resistivity of a liquid crystal material which exhibits a blue phase may be  $1 \times 10^9 \Omega\cdot\text{cm}$  or more, preferably  $1 \times 10^{11} \Omega\cdot\text{cm}$  or more, more preferably  $1 \times 10^{12} \Omega\cdot\text{cm}$  or more. Note that the resistivity in this specification is measured at 20 °C.

15 [0091]

In this embodiment, a transistor including a high-purity oxide semiconductor layer is used as a switching element of a pixel in order to utilize advantages of the liquid crystal layer including a liquid crystal material which exhibits a blue phase, e.g., high-speed response of the liquid crystal and viewing angle independence, and also to 20 overcome a disadvantage peculiar to the liquid crystal material which exhibits a blue phase. In other words, since driving voltage of the liquid crystal material which exhibits a blue phase is much higher than that of another liquid crystal driving method, a transistor used as a switching element is required to have a high drain breakdown voltage as well as low power consumption; in this embodiment, a transistor with 25 excellent electric characteristics of high drain breakdown voltage and significantly low off-state current is used as a switching element, whereby a highly-reliable display device with excellent image quality and low power consumption can be provided.

[0092]

(Embodiment 2)

30 In this embodiment, an example of a display device including a liquid crystal material which exhibits a blue phase will be described. Specifically, an example of a

structure of a pixel will be described.

[0093]

In a liquid crystal display device which includes a liquid crystal material which exhibits a blue phase, a method can be employed in which gray scale is controlled by generating an electric field substantially parallel to a substrate surface (i.e., in a lateral direction) to move liquid crystal molecules in a plane parallel to the substrate surface (hereinafter, this method is called a horizontal electric field method). For example, by employing a structure of an electrode illustrated FIGS. 5A and 5B, a horizontal electric field display device can be provided. FIG. 5B is a cross-sectional view taken along line X1-X2 in FIG. 5A.

[0094]

As illustrated in FIG. 5A, a plurality of source wirings (including the wiring 405a) are provided in parallel to each other (extended in the vertical direction in the drawing) and apart from each other. In addition, a plurality of gate wirings (including the wiring 401) are extended in a direction substantially perpendicular to the source wirings (the horizontal direction in the drawing) and provided apart from each other. Capacitor wirings 408 are adjacent to respective gate wirings and are extended in a direction substantially parallel to the gate wirings, that is, a direction substantially perpendicular to the source wirings (the horizontal direction in the drawing). Roughly rectangular space is surrounded by the source wirings, the capacitor wirings 408, and the gate wirings. In this space, the first electrode 447 and a second electrode 448 of the liquid crystal display device are provided with the liquid crystal layer 444 therebetween. The transistor 420 serving as a switch is located in the upper left corner of the drawing. In addition, the first electrodes 447 and the transistors 420 are arranged in a matrix.

[0095]

As illustrated in FIG. 5B, the liquid crystal layer 444 is provided between the first substrate 441 and a second substrate 442. The first substrate 441 and the second substrate 442 are light-transmitting substrates and are respectively provided with a polarizing plate 443a and a polarizing plate 443b on their outer sides (the sides opposite from the liquid crystal layer 444). The average gap between the first substrate 441 and the second substrate 442 (hereinafter, referred to as a cell gap) may be, for example, 1

μm to 10 μm inclusive.

[0096]

The transistor 420 is provided over the first substrate 441 and includes the wiring 401, the gate insulating layer 402, and the oxide semiconductor layer 403. In 5 this embodiment, a high-purity oxide semiconductor layer is used as the oxide semiconductor layer 403. The oxide semiconductor layer 403 is electrically connected to the wirings 405a and 405b serving as a source electrode and a drain electrode. Note that although an inverted-staggered transistor is illustrated as the transistor 420 in FIG. 5B, the present invention is not limited to the structure. That is, a top-gate transistor 10 may alternatively be used.

[0097]

In addition, the first insulating film 407 is provided to cover the transistor 420 and is in contact with the oxide semiconductor layer 403. The second insulating film 409 is provided over the first insulating film 407 and the third insulating film 417 is 15 provided over the second insulating film 409. Although the insulating film which covers the transistor have a three-layer structure in the display device illustrated in FIG. 5B, the present invention is not limited to this structure. In other words, the insulating film which covers the transistor may have a single-layer structure or a two-layer structure.

20 [0098]

In FIG. 5B, a light-transmitting resin having a chromatic color is used as the third insulating film 417 and the third insulating film 417 serves as a coloring layer (a color filter). If the color filter is provided on the second substrate 442 (the counter substrate) side, precise alignment of the pixel region over the first substrate 441 (the element substrate) would be difficult and an image quality may be lowered. In FIG. 25 5B, since the third insulating film 417 is formed on the first substrate 441 side as a color filter, the pixel region and the color filter can be precisely aligned easily.

[0099]

The chromatic-color light-transmitting resin may be formed using a material 30 which transmits only light colored with a chromatic color. Specifically, a photosensitive or non-photosensitive organic resin can be used. When a photosensitive organic resin layer is used, the number of resist masks can be reduced and thus the

process can be simplified.

[0100]

Note that chromatic colors are colors except achromatic colors such as black, gray, and white. Specifically, the chromatic color can be red, green, or blue, for example. Further, cyan, magenta, yellow, or the like may also be used.

[0101]

The thickness of the third insulating film 417 is preferably controlled as appropriate in consideration of a relationship between the concentration of the coloring material to be contained and light transmittance, in order to make the third insulating film 417 serve as a coloring layer (a color filter). Note that in the case where the third interlayer film 417 is formed of a plurality of thin films, at least one of them needs to be a light-transmitting chromatic-color resin layer so that the third insulating film 417 may serve as a color filter.

[0102]

Further, in the case where the thickness of the light-transmitting chromatic-color resin layers differs depending on their chromatic colors or in the case where a light-blocking layer is provided, or in the case where the surface is uneven due to the transistor, an insulating film which transmits light in a visible wavelength range (a so-called colorless and transparent insulating layer) is preferably formed over the third insulating film 417 for planarization of the surface of the third insulating film 417. Improvement in planarization of the third insulating film 417 allows favorable coverage with the first electrode 447 and the second electrode 448 and also a uniform gap (the thickness) of the liquid crystal layer, whereby the visibility of the liquid crystal display device is increased and a higher image quality can be achieved.

[0103]

Further, a light-blocking layer is preferably provided on the second substrate 442 to realize higher contrast and higher definition display. In this case, the light-blocking layer may be formed so as to overlap with the transistor 420 (at least with the semiconductor layer of the transistor) with the liquid crystal layer 444 interposed therebetween.

[0104]

The light-blocking layer is formed using a material that reflects or absorbs light.

For example, a black organic resin can be used. Specifically, a black organic resin which can be formed by mixing a black resin of a pigment material, carbon black, titanium black, or the like into a resin such as photosensitive or non-photosensitive polyimide can be used. Alternatively, a light-blocking metal film can be used. In this 5 case, chromium, molybdenum, nickel, titanium, cobalt, copper, tungsten, aluminum, or the like may be used.

[0105]

A first structure body 449 and a second structure body 445 are provided over the third insulating film 417 and can be referred to as projections (ribs). Note that the 10 first structure body 449 and the second structure body 445 include comb-shaped parts which have opening patterns, bends, and branches.

[0106]

The structure body can be formed using an insulating material (e.g., an organic insulating material and an inorganic insulating material) or a conductive material (e.g., 15 an organic conductive material like a conductive resin, and an inorganic conductive material like metal). For example, a visible light curable resin, an ultraviolet curable resin, or a thermosetting resin can be used. Note that a material which transmits visible light is preferably used for the structure body to avoid a reduction in aperture ratio and in white transmittance. Specifically, an acrylic resin, an epoxy resin, an 20 amine resin, or the like may be used. Further, the structure body may have a stack-layer structure instead of a single-layer structure.

[0107]

The cross-sectional shape of the first structure body 449 and the second structure body 445 along a direction perpendicular to the main surfaces of the first 25 substrate 441 and the second substrate 442 may be a polygon, a triangle, a trapezoid, a semicircle, or a semiellipse. In addition, the first structure body 449 and the second structure body 445 preferably have a smooth curved surface with few steps. For example, as illustrated in FIG. 5B, when the first structure body 449 and the second structure body 445 have a tapered shape with ends having a curvature, the coverage 30 with the first electrode 447 and the second electrode 448 which are formed to cover surfaces (top surfaces and side surfaces) of the first structure body 449 and the second structure body 445 can be improved.

## [0108]

In addition, the height of the first structure body 449 and the second structure body 445 may be at least smaller than the average gap (the cell gap) between the first substrate 441 and the second substrate 442. Specifically, the height may be 0.1  $\mu\text{m}$  or 5 more and less than 10  $\mu\text{m}$ . The structure bodies are preferably high because the higher the first structure body 449 and the second structure body 445 are, the more effectively a horizontal electric field can be applied to the liquid crystal layer 444 and the less driving voltage will be needed. Further, the width of the first structure body 449 and the second structure body 445 may be 0.5  $\mu\text{m}$  to 10  $\mu\text{m}$  inclusive. The first structure body 449 and the second structure body 445 may be arranged with an interval of 1  $\mu\text{m}$  10 to 10  $\mu\text{m}$  inclusive therebetween.

## [0109]

The method for forming the first structure body 449 and the second structure body 445 is not particularly limited, and a dry method such as an evaporation method, a 15 sputtering method, or a CVD method or a wet method such as spin coating, dip coating, spray coating, a droplet discharge method (an ink jetting method), nanoimprinting, or various printing methods (e.g., screen printing or offset printing) may be used depending on the material. An etching step (dry etching or wet etching) may be employed to form a desired pattern, as necessary.

## 20 [0110]

Further, the structure body may be acceptable as long as it projects into the liquid crystal layer from a surface of the substrate which faces the liquid crystal layer. Projections therefore may be provided by etching the third insulating film 417 partly so 25 that the surface facing the liquid crystal layer may be rough. In this case, the third insulating film 417 includes the first projection and the second projection, whereby an additional film formation step for forming the first structure body 449 and the second structure body 445 can be omitted.

## [0111]

The first electrode 447 is formed to cover the first structure body 449 and is 30 electrically connected to the transistor 420. The first electrode 447 serves as the pixel electrode. The second electrode 448 is formed to cover the second structure body 445

and serves as a common electrode. In addition, a capacitor is formed of the first electrode 447, the liquid crystal layer 444, and the capacitor wiring 408.

[0112]

An image signal (an analog video signal) is input to the first electrode 447 through the wiring 405a and the transistor 420. Although the second electrode 448 can be in a floating state (an electrically isolated state), the second electrode 448 may be set to a fixed potential, preferably to a potential around a common potential (an intermediate potential of the image signal which is input to the first electrode 447) so that the potential may be in such a level that does not generate flickers.

10 [0113]

Note that although the first electrode 447 is electrically connected to the transistor 420 through the wiring 405b in FIGS. 5A and 5B, the present invention is not limited to the structure. For example, the first electrode 447 may be directly connected to the oxide semiconductor layer 403 in the transistor 420.

15 [0114]

The height (the thickness) of the first electrode 447 and the second electrode 448 may be at least smaller than the average gap (the cell gap) between the first substrate 441 and the second substrate 442. Specifically, the height may be 0.01  $\mu\text{m}$  to 3  $\mu\text{m}$  inclusive. Here, it is preferable to satisfy  $X = a + b$ , where the average gap (the cell gap) between the first substrate 441 and the second substrate 442 is  $X \mu\text{m}$ , the height of the first structure body 449 and the second structure body 445 is  $a \mu\text{m}$ , and the thickness of the first electrode 447 and the second electrode 448 is  $b \mu\text{m}$ . When the equation  $X = a + b$  is satisfied, the first electrode 447 and the second electrode 448 are in contact with the second substrate 442. In other words, the first structure body 449 and the second structure body 445 serve as spacers in the pixel portion. Accordingly, a columnar spacer or spherical spacer, which is generally provided in the pixel portion to keep the distance between the first substrate 441 and the second substrate 442 uniform, is not additionally needed. Thus, the number of process steps of the display device can be reduced. Note that the first electrode 447 and the second electrode 448 are arranged with an interval of 0.5  $\mu\text{m}$  to 8  $\mu\text{m}$  inclusive therebetween.

30 [0115]

The first electrode 447 and the second electrode 448 are alternately arranged without overlapping with each other. In addition, the first electrode 447 and the second electrode 448 do not have plate-like shapes but have comb-shaped parts which have various opening patterns, bends, and branches.

5 [0116]

The first electrode 447 and the second electrode 448 can be formed using a light-transmitting conductive material such as oxide containing tungsten and indium (indium oxide containing tungsten oxide), oxide containing tungsten, indium, and zinc (indium zinc oxide containing tungsten oxide), oxide containing titanium and indium (indium oxide containing titanium oxide), oxide containing titanium, indium, and tin (indium tin oxide containing titanium oxide), oxide containing indium and tin (indium tin oxide or ITO), oxide containing indium and zinc (indium zinc oxide), and oxide containing silicon, indium, and tin (indium tin oxide to which silicon oxide is added). The second electrode 448 can also be formed using one or plurality of materials selected from metal such as tungsten (W), molybdenum (Mo), zirconium (Zr), hafnium (Hf), vanadium (V), niobium (Nb), tantalum (Ta), chromium (Cr), cobalt (Co), nickel (Ni), titanium (Ti), platinum (Pt), aluminum (Al), copper (Cu), or silver (Ag); an alloy thereof; and nitride thereof. The second electrode 448 can also be formed using a conductive composition containing a conductive high molecule (also referred to as a conductive polymer).

20 [0117]

Note that in FIGS. 5A and 5B, the hatching patterns of the first electrode 447 and the second electrode 448 are different from each other and the materials of them are different for a better understanding of the description, but the present invention is not limited to the structure. That is, the first electrode 447 and the second electrode 448 can be formed using the same material. Specifically, the first electrode 447 and the second electrode 448 are preferably formed using the same light-transmitting conductive material because the number of process steps can be reduced compared with the case where they are formed using different materials. Further, a light-transmitting conductive material is preferably used for forming the first electrode 447 and the second electrode 448 because an aperture ratio will be increased. Further, a light-transmitting conductive material is more preferably used for forming the wiring 405a and the wiring

405b as well as the first electrode 447 and the second electrode 448 so that the aperture ratio may be further increased.

[0118]

Although FIGS. 5A and 5B illustrate a horizontal electric field display device in which the second electrode 448 provided on the first substrate 441 side serves as a common electrode, the present invention is not limited to the structure. For example, as another common electrode, a third electrode (a second common electrode) can be additionally provided on the counter substrate (the second substrate 442) side, in addition to the second electrode 448 (a first common electrode) provided on the first substrate 441 side. In the case where the third electrode is provided, the second electrode 448 on the first substrate side and the third electrode on the second substrate side are arranged to face (overlap with) each other with the liquid crystal layer 444 interposed therebetween. Further, the second electrode 448 and the third electrode are preferably set to the same potential. In addition, the second electrode 448 and the third electrode are preferably formed of the same material.

[0119]

By providing the third electrode on the second substrate side, an electric field can be applied to the liquid crystal layer 444 in an oblique direction (in a direction oblique to the main surface of the first substrate 441) between the first electrode 447 and the third electrode; thus, liquid crystal molecules can be controlled more efficiently. The liquid crystal molecules in the entire liquid crystal layer 444 including the liquid crystal molecules in the thickness direction of the liquid crystal layer 444 can be thereby made to respond and the white transmittance (light transmittance in white display) can be improved. As a result, the contrast ratio, which is a ratio of the white transmittance to the black transmittance (light transmittance in black display), can also be improved.

[0120]

As described above, in this embodiment, the first electrode 447 is provided so as to cover the first structure body 449 and the second electrode 448 is provided so as to cover the second structure body 445, whereby the formation area of the first electrode 447 and the second electrode 448 can be increased in the thickness direction (in a three dimensional direction) of the liquid crystal layer 444. Accordingly, when voltage is applied between the first electrode 447 and the second electrode 448, an electric field

can be widely (effectively) formed between the first electrode 447 and the second electrode 448. Therefore, the driving voltage of the display device can be lowered, which leads to a reduction in power consumption. In addition, since the transistor 420 includes a high-purity oxide semiconductor layer, power consumption for displaying a still image or the like can be reduced as described in Embodiment 1.

5 [0121]

(Embodiment 3)

In this embodiment, another example which is different from the horizontal electric field display device described in Embodiment 2 will be described.

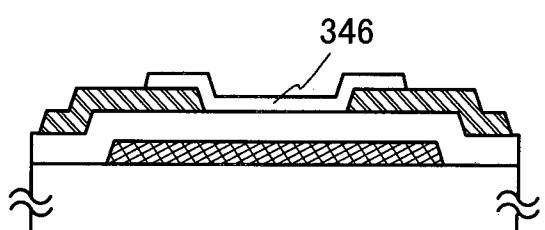

10 [0122]

Although illustrated in FIGS. 5A and 5B and described in Embodiment 2 is the horizontal electric field display device in which the second electrode 448 provided on the first substrate 441 side serves as a common electrode, the present invention is not limited to the structure. For example, as illustrated in FIG. 6, a third electrode 446 (a second common electrode) can be additionally provided on the counter substrate (the second substrate 442) side to be used as a common electrode, in addition to the second electrode 448 (a first common electrode) provided on the first substrate 441 side. In the case where the third electrode is provided, the second electrode 448 on the first substrate side and the third electrode 446 on the second substrate side are arranged to overlap with each other with the liquid crystal layer interposed therebetween. Further, the second electrode 448 and the third electrode 446 are preferably set to the same potential.

20 [0123]

By providing the third electrode 446 on the second substrate side, an electric field can be applied to the liquid crystal layer 444 in an oblique direction (in a direction oblique to the main surface of the first substrate 441) between the first electrode 447 and the third electrode 446; thus, liquid crystal molecules can be controlled more efficiently. The liquid crystal molecules in the entire liquid crystal layer 444 including the liquid crystal molecules in the thickness direction of the liquid crystal layer 444 can be thereby made to respond and the white transmittance can be improved. As a result, the contrast ratio, which is a ratio of the white transmittance to the black transmittance (light transmittance in black display), can also be improved.

## [0124]