(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년06월20일

(11) 등록번호 10-1869323

(24) 등록일자 2018년06월14일

- (51) 국제특허분류(Int. Cl.)

*H01L 29/66* (2006.01) *H01L 21/265* (2006.01)

*H01L 29/06* (2006.01) *H01L 29/40* (2006.01)

*H01L 29/423* (2006.01) *H01L 29/78* (2006.01)

- (52) CPC특허분류

*H01L 29/66734* (2013.01)

*H01L 21/26586* (2013.01)

- (21) 출원번호 10-2016-7025520(분할)

- (22) 출원일자(국제) 2010년10월20일

심사청구일자 2016년09월28일

- (85) 번역문제출일자 2016년09월13일

- (65) 공개번호 10-2016-0111548

- (43) 공개일자 2016년09월26일

- (62) 원출원 특허 10-2012-7009939

원출원일자(국제) 2010년10월20일

심사청구일자 2013년09월23일

- (86) 국제출원번호 PCT/US2010/053454

- (87) 국제공개번호 WO 2011/050116

국제공개일자 2011년04월28일

- (30) 우선권주장

61/253,464 2009년10월20일 미국(US)

12/788,158 2010년05월26일 미국(US)

(56) 선행기술조사문헌

US05233215 A

(뒷면에 계속)

전체 청구항 수 : 총 14 항

심사관 : 김종희

(54) 발명의 명칭 초고밀도 전력 트렌치 MOSFET

**(57) 요 약**

하나의 예로서, 방법은 수직형 MOSFET 의 바디 영역 내에서 다수개의 트렌치들을 형성하는 단계를 포함할 수 있다. 또, 상기 방법은 상기 바디 영역 내로 소스 영역을 경사 주입 단계를 포함할 수 있다. 또한, 유전체 물질은 상기 사수개의 트렌치들 내에서 성장할 수 있다. 게이트 폴리실리콘은 상기 다수개의 트렌치들 내에서 침적될 (뒷면에 계속)

**대 표 도**

수 있다. 게다가, 상기 방법은 상기 게이트 폴리실리콘을 화학기계적 연마하는 과정을 포함할 수 있다. 상기 방법은, 또한, 상기 다수개의 트렌치들 내에서 상기 게이트 폴리실리콘을 백 에칭(etching back)하는 과정을 포함할 수 있다.

## (52) CPC특허분류

*H01L 29/0638* (2013.01)

*H01L 29/407* (2013.01)

*H01L 29/42368* (2013.01)

*H01L 29/7811* (2013.01)

*H01L 29/7813* (2013.01)

## (72) 발명자

**니치텐밸젤, 칼**

미합중국 캘리포니아 94087 서니밸리 567 보보린크

서클

**쉬, 샤론**

미합중국 캘리포니아 95123 산 조스 034 노요 드라

이브

**챈, 큐페이**

미합중국 캘리포니아 95129 산 조스 798 도이레 로

드

**텔린, 키례**

미합중국 캘리포니아 95050 산타 클라라 3385 런던

베리 로드

## (56) 선행기술조사문헌

US06489204 B1

US20010026989 A1

JP2005268679 A\*

JP2009004411 A

JP2009522807 A\*

KR100714198 B1\*

US20070155104 A1

US20060289929 A1\*

\*는 심사관에 의하여 인용된 문헌

## 명세서

### 청구범위

#### 청구항 1

MOSFET(metal-oxide semiconductor field-effect transistor) 제조방법으로서, 기재(substrate)에 에피택셜 영역(an epitaxial region)을 형성하는 단계와, 수직형(vertical) MOSFET용 상기 에피택셜 영역 내에 복수의 트렌치들(trenches)을 형성하는 단계와, 상기 복수의 트렌치들 내에서 제 1 유전체 물질(first dielectric material)을 성장시키는 단계와, 상기 복수의 트렌치들 내에서 게이트 폴리실리콘(gate polysilicon)을 침적(depositing)시키는 단계와, 상기 게이트 폴리실리콘을 화학기계적으로 연마(polishing)하는 단계와, 상기 복수의 트렌치들 내에 상기 게이트 폴리실리콘을 백 에칭(etching back)시키는 단계와, 상기 게이트 폴리실리콘을 백 에칭시키는 단계 이후에, 상기 에피택셜 영역 내로 소스 영역(source regions)을 경사 주입(angle implanting)하는 단계와, 상기 백 에칭된 게이트 폴리실리콘 상에 제 2 유전체 물질(second dielectric material)을 침적시키는 단계와, 상기 제 2 유전체 물질을 화학기계적 연마에 의해 평탄화시키는 단계와, 상기 소스 영역이 형성된 후에, 상기 에피택셜 영역 내로 바디 영역(body region)을 이온 주입하되, 상기 바디 영역을 형성하기 위한 물질이 상기 소스 영역 중 적어도 하나를 통과하도록, 또한, 상기 바디 영역이 상기 에피택셜 영역과 접촉되도록, 상기 바디 영역을 이온 주입하는 단계를 포함하는 MOSFET 제조방법.

#### 청구항 2

제 1 항에 있어서,

상기 제 2 유전체 물질 및 상기 소스 영역 상에 소스 접촉부(source contact)를 자가 정렬(self-aligning)시키는 단계

를 더 포함하는 MOSFET 제조방법.

#### 청구항 3

제 2 항에 있어서,

상기 소스 접촉부는 상기 소스 영역의 적어도 하나와 접촉되는 MOSFET 제조방법.

#### 청구항 4

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 에피택셜 영역은 P-이고, 상기 기재는 P++인

MOSFET 제조방법.

#### 청구항 5

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 에피택셜 영역은 N-이고, 상기 기재는 N++인

MOSFET 제조방법.

#### 청구항 6

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 복수의 트렌치들은 20 제곱 밀리미터당 적어도 1 기가-셀(giga-cells)의 밀도를 가지는

MOSFET 제조방법.

#### 청구항 7

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 복수의 트렌치들 각각은 0.8 마이크로미터 이하의 셀피치(cell pitch) 또는 1 마이크로미터 깊이를 갖는

MOSFET 제조방법.

#### 청구항 8

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 게이트 폴리실리콘을 침적시키는 단계는 상기 성장시키는 단계 후에 이루어지는

MOSFET 제조방법.

#### 청구항 9

제 1 항에 있어서,

상기 백 에칭(etching back)은 상기 게이트 폴리실리콘을 화학기계적으로 연마하는 단계 후에 이루어지는

MOSFET 제조방법.

#### 청구항 10

제 2 항에 있어서,

상기 백 에칭(etching back)은 상기 게이트 폴리실리콘을 화학기계적으로 연마하는 단계 후에 이루어지는

MOSFET 제조방법.

#### 청구항 11

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 에피택셜 영역 내에 에지 터미네이션 트렌치(an edge termination trench)를 형성하는 단계와,

상기 에지 터미네이션 트렌치 내에 상기 제 1 유전체 물질을 침적하는 단계와,

상기 에지 터미네이션 트렌치 내에 에지 터미네이션 폴리실리콘을 침적하는 단계와

상기 에지 터미네이션 폴리 실리콘을 화학기계적으로 연마하는 단계

를 더 포함하는

MOSFET 제조방법.

## 청구항 12

제 11 항에 있어서,

상기 에지 터미네이션 트렌치 내에서 상기 에지 터미네이션 폴리실리콘을 백 에칭(etching back) 하는 단계

를 더 포함하는

MOSFET 제조방법.

## 청구항 13

제 11 항에 있어서,

상기 에지 터미네이션 트렌치는 상기 수직형 MOSFET의 게이트 접촉부보다 넓은

MOSFET 제조방법.

## 청구항 14

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 소스 영역 중 제 1 소스 영역은 제 1 트렌치 표면과 제 2 트렌치 표면에 모두 접촉하고, 상기 제 1 소스

영역은 상기 제 1 트렌치 표면 및 상기 제 2 트렌치 표면 사이에서 연속적인

MOSFET 제조방법.

### 발명의 설명

### 기술 분야

[0001] 본 출원서의 청구항들은 참조로서 미국특허출원(No: 61/253,464) "Super-High Density Power Trench MOSFET with Recessed Gated and Trench Edge Termination"과 합체된다.

### 배경 기술

[0002] 종래의 트렌치 MOSFET의 경우, 원하는 트렌치 패킹 밀도(packing density)를 증가시킬 수 있다. 그러나, 종래의 트렌치 MOSFET의 트렌치 패킹 밀도가 계속적으로 증가함에 따라, 종래의 트렌치 MOSFET 타입을 제작하기에 어려움이 있다. 예를 들어, 포토리소그래피(photolithography)를 이용한 매우 좁은 트렌치를 인쇄하기 위한 시도가 이루어지고 있다. 더욱이, 종래의 트렌치 MOSFET 타입을 제작하는 경우에 상기 매우 좁은 트렌치 내에 재료를 삽입하기가 어려워진다.

### 발명의 내용

### 해결하려는 과제

[0003] 또한, 화학적인 단락을 방지하기 위해, 적절히 정렬되어 확실한 화학적 접촉을 이루도록 하기 위한 요구들이 점

점 늘어나고 있다.

### 과제의 해결 수단

[0004]

하나의 예로서, 본 방법은 수직형 MOSFET(vertical metal-oxide semiconductor field-effect transistor)용 바디 영역 내에 다수 개의 트렌치들을 형성하는 단계를 포함할 수 있다. 또한, 상기 본체 영역에 소스 영역을 경사 주입하는 단계를 포함할 수 있다. 더욱이, 게이트 폴리실리콘을 화학기계적으로 연마하는 단계를 포함할 수 있다. 이러한 방법은 상기 다수개의 트랜치 내에서 상기 게이트 폴리실리콘을 백 에칭(etching back)하는 단계를 더 포함할 수 있다.

[0005]

또 다른 예로서, 장치의 에피택셜 영역에서 엣지 터미널 트랜치(an edge termination trench)를 형성하는 단계를 포함할 수 있다. 유전체 물질(dielectric material)은 상기 엣지 터미널 트랜치(an edge termination trench) 내에 저장될 수 있다. 또한, 폴리실리콘은 상기 엣지 터미널 트랜치(an edge termination trench) 내에 침적될 수 있다. 추가적으로, 상기 방법은 상기 폴리실리콘을 화학기계적으로 연마하는 단계를 포함할 수 있다. 또, 상기 방법은 상기 폴리실리콘을 상기 엣지 터미널 트랜치 내에서 백 에칭하는 단계를 포함할 수 있다.

[0006]

또 다른 실시예에서, 장비는 수직형 MOSFET 의 바디 영역 내에 다수의 트랜치를 포함할 수 있다. 각각의 상기 다수의 트랜치들은 유전체 물질을 포함하는 게이트 폴리실리콘을 포함할 수 있다. 상기 유전체 물질의 상부면은 평면이다. 또한, 상기 장비는 소스 접촉부(source contact) 및 상기 다수의 트랜치들로 정의되는 다수의 메사들(mesas)을 포함할 수 있다. 각각의 상기 다수의 메사들은 상기 소스 접촉부와 접촉되는 소스 영역을 포함할 수 있다.

[0007]

본 발명에서 특정한 실시예에 대한 구체적으로 설명하고 있으나, 본 발명 및 청구항들은 상기 실시예에 한정되지 않는다.

### 도면의 간단한 설명

[0008]

본 발명의 실시예는 실험 방식으로 설명되는 것이며, 본 발명의 도면 및 유사한 요소의 도면부호의 설명 방식에 한정되는 것은 아니다.

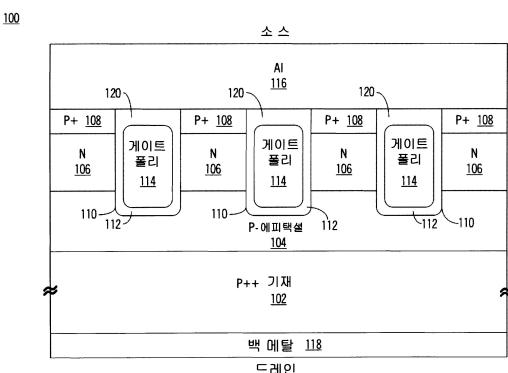

도 1은 본 발명에 따른 다양한 실시예에 따른 초고밀도 P-채널 만입 게이트 전력 트랜치 MOSFET 의 측 단면도이다.

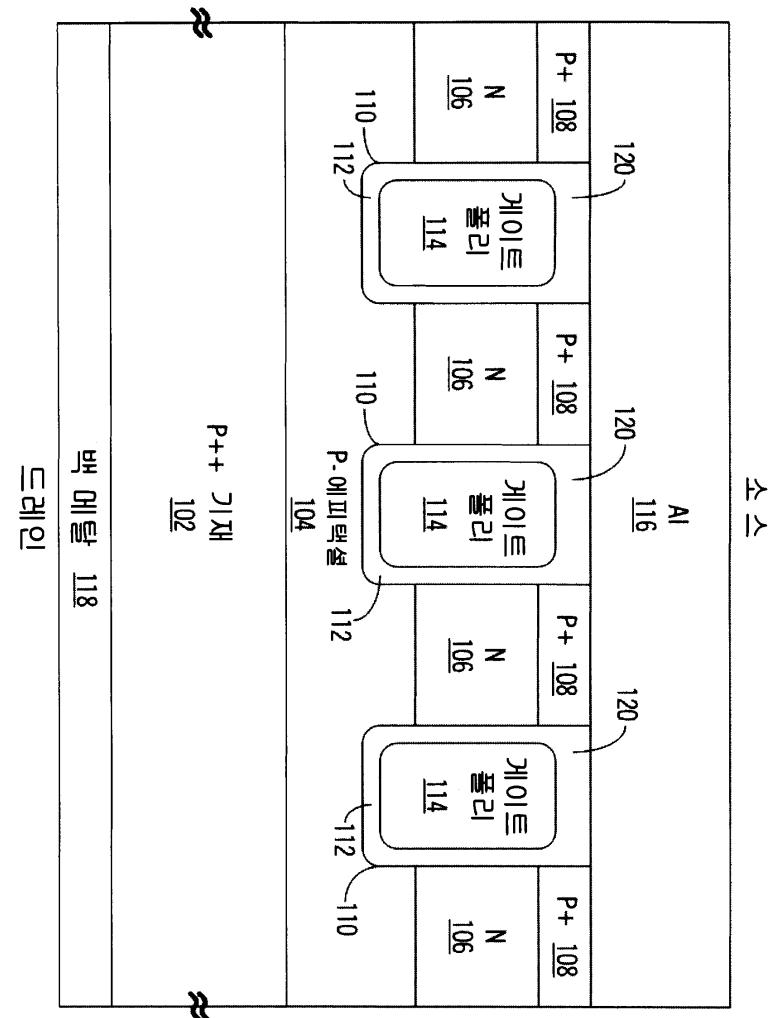

도 2는 본 발명에 따른 다양한 실시예에 따른 초고밀도 N-채널 만입 게이트 전력 트랜치 MOSFET 의 측 단면도이다.

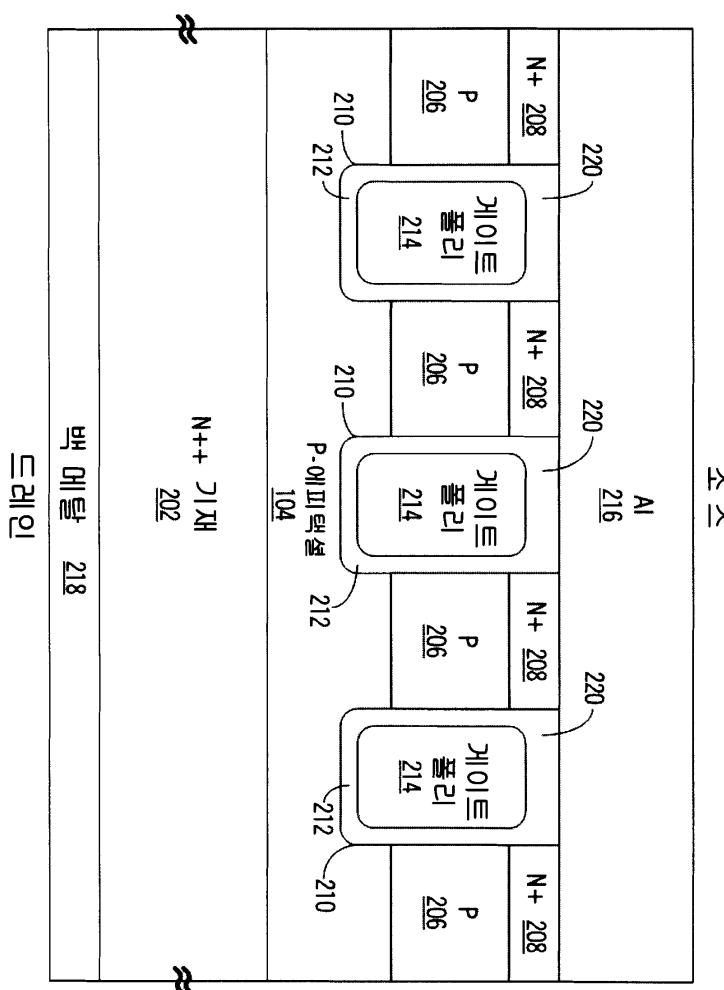

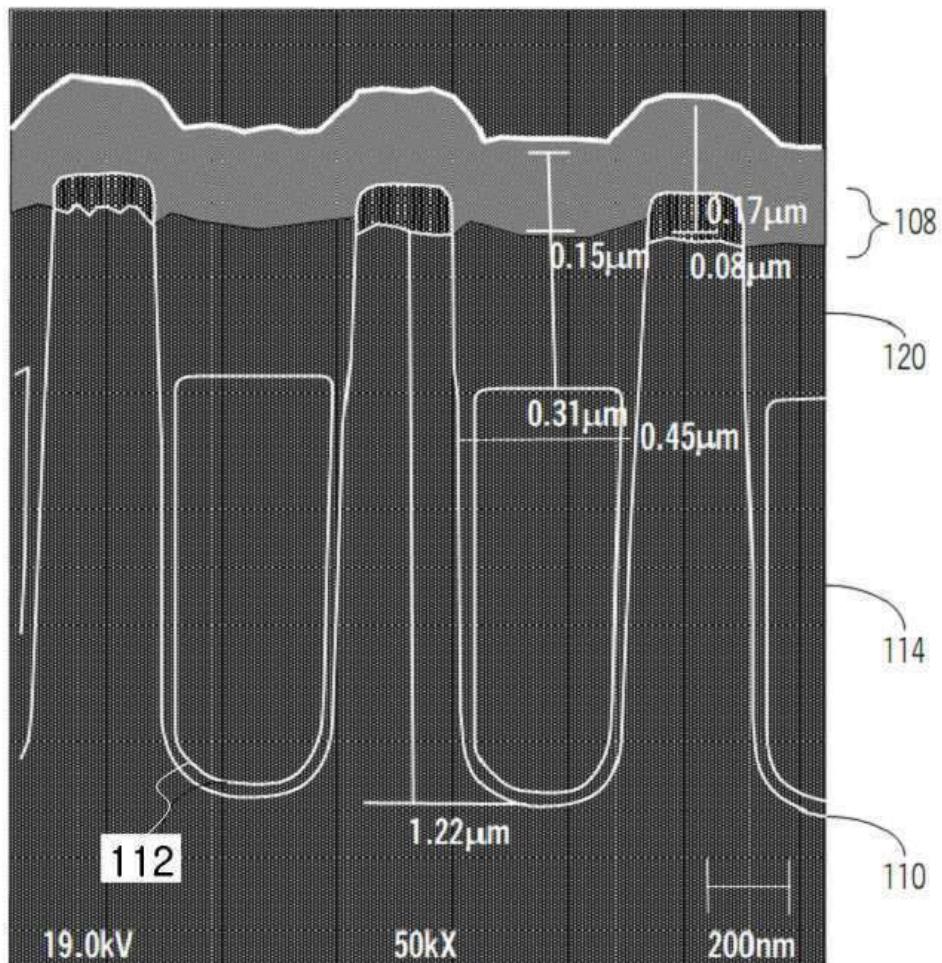

도 3은 본 발명의 실시예에 따른 초고밀도 P-채널 만입 게이트 전력 트랜치 MOSFET이 형성된 부분을 나타내는 측 단면도이다.

도 4는 본 발명의 실시예에 따른 초고밀도 N-채널 만입 게이트 전력 트랜치 MOSFET이 형성된 부분을 나타내는 측 단면도이다.

도 5는 본 발명의 실시예에 따른 다수의 트랜치들 및 종래의 엣지 터미네이션의 측 단면도이다.

도 6은 본 발명의 다양한 실시예에 따른 다수의 트랜치들 및 트랜치 엣지 터미네이션의 측 단면도이다.

도 7은 본 발명의 다양한 실시예에 따른 엑티브 트랜치 센터(active trench center)에 따라 종래의 엣지 터미네이션 및 또 다른 게이트 핵업(gate pickup)의 측 단면도이다.

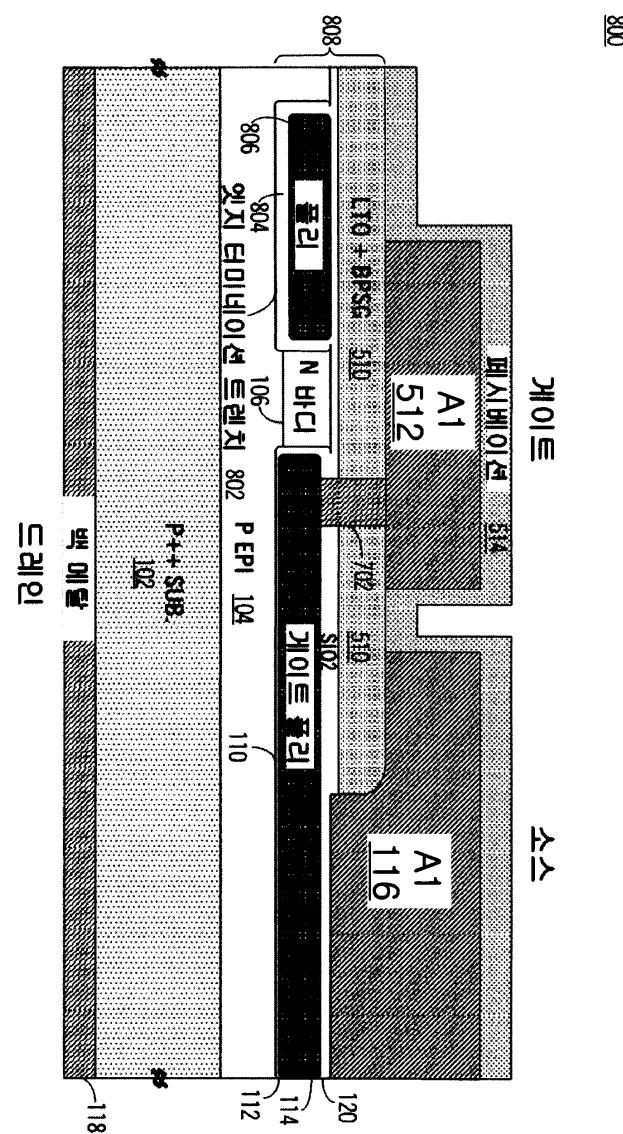

도 8은 본 발명의 다양한 실시예에 따른 엑티브 트랜치 센터(active trench center)에 따라 종래의 엣지 터미네이션 및 또 다른 하나의 게이트 핵업(gate pickup)의 측 단면도이다.

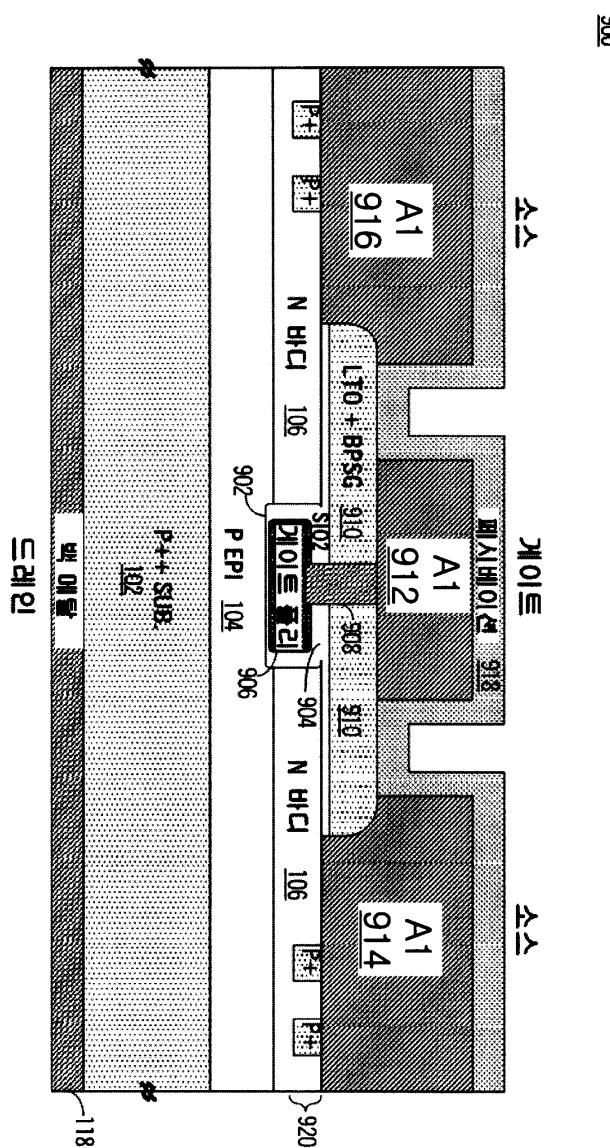

도 9는 본 발명의 다양한 실시예에 따른 메사 센터(mesa center)에 따라 게이트 저항(gate resistance)을 감소시키기 위한 추가적인 게이트 핵업 평거 영역(gate pickup finger region)의 측 단면도이다.

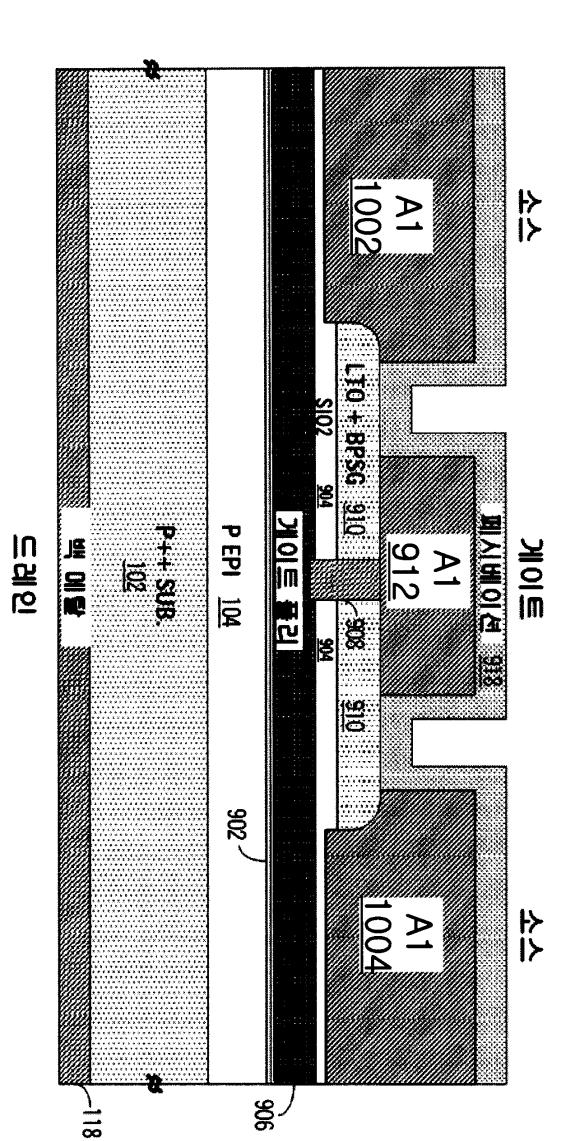

도 10은 본 발명의 다양한 실시예에 따른 상기 트랜치 센터(the trench center)에 따라 도 9의 상기 게이트 핵업 평거 영역(gate pickup finger region)의 다른 측 단면도이다.

도 11은 본 발명의 다양한 실시예에 따른 종래의 엣지 터미네이션을 포함하는 방법의 흐름도이다.

도 12는 본 발명의 다양한 실시예에 따른 종래의 엣지 터미네이션을 포함하는 또 다른 방법의 흐름도이다.

도 13은 본 발명의 다양한 실시예에 따른 종래의 엣지 터미네이션을 포함하는 또 다른 하나의 방법의 흐름도이다.

도 14는 본 발명의 다양한 실시예에 따른 도 11 내지 도 13의 트렌치 엣지 터미네이션을 삽입하는 단계를 포함하는 또 다른 방법의 흐름도이다.

본 상세한 설명에 나타난 도면들은 특별한 언급이 없다면, 확장 해석되어 이해되어서는 안될 것이다.

### 발명을 실시하기 위한 구체적인 내용

[0009]

본 발명에 따른 다양한 실시예들에 대한 설명을 도면을 참조하여 설명된 실험예에 의해 나타낼 것이다. 본 발명의 다양한 실시예를 통하여 설명하지만, 본 발명이 이들의 실시예로 한정되는 것은 아니다. 반면에, 본 발명은 대안, 수정 및 등가물을 포함하며, 이들은 청구항들로부터 이해되는 본 발명의 범주내에 속할 것이다. 또한, 여기에서 본 발명에 따른 다양한 실시예에서, 수많은 특별한 상세한 설명들은 본 발명의 이해를 통해 제공되도록 하기 위함이다. 그러나, 관련분야의 당업자가 이러한 특별한 상세한 설명 없이 수행할 수 있는 자료가 될 것이다. 또 다른 예에서, 공지된 방법, 절차, 요소 및 장비들은 본 발명의 불필요한 잘 알려지지 않은 부분에 대해 설명하지 않는다.

[0010]

도 1은 본 발명의 다양한 실시예에 따른 P-채널 만입 게이트 전력 트렌치 MOSFET(100)의 측 단면도이다. 하나의 예로써, P-채널 만입 게이트 전력 트렌치 MOSFET(100)는 표면 위상최적화(topology) 이슈(issue)를 방지하기 위해 폴리실리콘을 화학기계적으로 연마(CMP), 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질 CMP 평면 기술에 의해 형성될 수 있다. 이러한 기술이 적용됨으로써, P-채널 전력 트렌치 MOSFET (100)의 초고밀도 MOSFET 게이트 채널의 폭은 사진 석판 인쇄의 진보와 함께 달성된다.

[0011]

하나의 실시예에서, 초고밀도 트렌치 MOSFET 은 20 제곱 밀리미터당 적어도 1 기가-셀(giga-cells)의 밀도를 가지나, 이에 한정되는 것은 아니다. 또한, P-채널 전력 트렌치 MOSFET (100)의 만입 게이트 (114)에 의해, 소스 접촉부 (116)는 소스 실리콘 표면 (108) 상부에 자가-정렬될 수 있다. 더욱이, P-채널 전력 트렌치 MOSFET (100)의 높은 팩킹 트랜치 밀도에 의해, 트렌치 (110)들 사이에 위치한 매우 얇은 실리콘 메사의 내부에 바디 도핑(body doping)을 조절하여, 확장-모드(enhanced-mode) MOSFET 장치 및 공핍 방식(depletion-mode) MOSFET 를 만드는 방법을 제공한다.

[0012]

하나의 구체적인 예로서, P-채널 전력 트렌치 MOSFET (100)의 구조는 활성 구역에서 만입 폴리실리콘 게이트 (114)를 가진다. 만입 폴리실리콘 게이트 (114)는 이러한 폴리실리콘을 화학기계적으로 연마한 후에, 폴리실리콘 백 에칭을 수행하여 생성시킬 수 있다. 폴리실리콘 게이트 (114)의 화학기계적 연마 및 폴리실리콘 백 에칭을 이용함으로써, 수직형 폴리실리콘 게이트 (114)의 상부 폴리실리콘 표면은 평평해지고, 더욱 효과적으로 조절될 수 있다. 초고밀도 트렌치 MOSFET (100)의 만입 폴리실리콘 게이트 (114)는 유전체 물질 (120), 실리콘 디옥사이드 (SiO<sub>2</sub>), 저온 옥사이드 (LTO), 대기중 보다 낮은 화학적 압력 침적 (SACVD) 옥사이드 및 이들과 유사한 물질이 주입된 소스 (116)로 부터 격리될 수 있다. 하나의 예에서, 주입된 소스 (120)은 유전체 물질의 화학기계적 연마과정을 이용하여 생성시킬 수 있다. 추가적으로, 주입된 소스 (120)는 상부 실리콘 표면 (108)이 소스가 되도록 할 수 있으므로, 소스 접촉부 (116)는 상부 실리콘 표면 (108)에 자가-정렬될 수 있고, 활성 트랜치 게이트 (114)는 종래의 트렌치 MOSFET 보다 더 조밀하게 포장될 수 있다.

[0013]

하나의 실시예에 따른 도 1에서, 초고밀도 P-채널 전력 트렌치 MOSFET (100)은 P-에피택셜 영역(epitaxial region) 또는 이들에 형성된 층 (104)을 가진 매우 낮은 저항(P++) 기재 (102)를 포함할 수 있다. 또한, N 바디 영역 또는 층 (106)은 P-에피택셜 영역의 상측 부분에 주입될 수 있다. 더욱이, 초고밀도 전력 트렌치 MOSFET (100)은 P++ 소스 영역 또는 N 바디 영역 (106)의 상측 부분에 주입된 층 (106)을 포함할 수 있다. 전력 트렌치 MOSFET (100)은 또한 상기 P++ 소스 층 (108) 내에 위치한 트렌치 (110), N 바디 층 (106)과 P-에피택셜 층 (104)을 포함할 수 있다. 또한, 트렌치 (110)는 유전체 물질 (112)을 포함하는 폴리실리콘 게이트 (114)와 유전체 물질 (120)을 포함할 수 있다. 전력 트렌치 MOSFET (100)은 또한 소스 메탈 영역(source metal region) 또는 침적된 층 (116) 또는 P++ 소스 층 (108)을 포함할 수 있다. 더욱이, 전력 트렌치 MOSFET (100)은 침적된 드레인 메탈(drain metal) 또는 백 메탈(back metal) (118) 또는 P++ 기재 (102)를 포함할 수 있다.

[0014]

상기 초고밀도 P-채널 전력 트렌치 MOSFET (100)은 도 1에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 상기 초고밀도 전력 트렌치 MOSFET (100)은 도 1에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 초고밀도 전력 트렌치 MOSFET (100)은 여기에서 설명되는 유사한 방법으로 이용 또는

수행될 수 있으며, 이들로 한정되는 것은 아니다.

[0015] 도 2는 본 발명의 다양한 실시예에 따른 N-채널 만입 게이트 전력 트렌치 MOSFET (200)의 측 단면도이다. 하나의 실시예에서, N-채널 만입 게이트 전력 트렌치 MOSFET (200)은 표면 위상최적화(topology) 문제(issue)를 방지하기 위해 폴리실리콘 CMP와 유전체 물질 CMP 평탄화 기술을 적용하여 형성시킬 수 있다. 이러한 기술들에 의해, N-채널 전력 트렌치 MOSFET (100)의 초고밀도 MOSFET 게이트 채널의 폭은 사진 석판 인쇄의 진보와 함께 달성된다. 하나의 예에서, 초고밀도 트렌치 MOSFET은 20 제곱 밀리미터당 적어도 1 기가-셀(giga-cells) (또는  $1 \times 10^9$ )의 밀도를 가지나, 이에 한정되는 것은 아니다. 또한, N-채널 전력 트렌치 MOSFET (200)의 만입 게이트 (214)에 의해, 소스 접촉부 (216)는 상부 소스 실리콘 표면 (208)에 자가-정렬될 수 있다. 더욱이, N-채널 전력 트렌치 MOSFET (200)의 매우 높은 패킹 트렌치 밀도에 의해, 트렌치 (210)들 사이에 위치한 매우 얇은 실리콘 메사의 내부에 바디 도핑(body doping)을 조절하여, 확장-모드(enhanced-mode) MOSFET 장치 및 공핍 방식(depletion-mode) MOSFET을 만드는 방법을 제공한다.

[0016] 하나의 구체적인 예로서, N-채널 전력 트렌치 MOSFET (200)의 구조는 활성 구역에서 만입 폴리실리콘 게이트 (214)를 가진다. 만입 폴리실리콘 게이트 (214)는 이러한 폴리실리콘을 화학기계적으로 연마한 후에, 폴리실리콘 백 에칭을 수행하여 생성시킬 수 있다. 폴리실리콘 게이트 (214)의 화학기계적 연마 및 폴리실리콘 백 에칭을 이용함으로써, 수직형 폴리실리콘 게이트 (214)의 상부 폴리실리콘 표면은 평평해지고, 더욱 효과적으로 조절될 수 있다. 초고밀도 트렌치 MOSFET (200)의 만입 폴리실리콘 게이트 (214)는 유전체 물질 (220), 실리콘 디옥사이드 ( $SiO_2$ ), 저온 옥사이드 (LTO), 대기중 보다 낮은 화학적 압력 침적 (SACVD) 옥사이드 및 이들과 유사한 물질이 주입된 소스 (216)으로부터 격리될 수 있다. 하나의 예에서, 주입된 소스 (220)은 유전체 물질의 화학기계적 연마과정을 이용하여 생성시킬 수 있다. 추가적으로, 주입된 소스 (220)는 상부 실리콘 표면 (208)이 소스가 되도록 할 수 있으므로, 소스 접촉부 (216)은 상부 실리콘 표면 (108)에 자가-정렬될 수 있고, 활성 트렌치 게이트 (214)는 종래의 트렌치 MOSFET 보다 더 조밀하게 포장될 수 있다.

[0017] 하나의 실시예에 따른 도 2에서, 초고밀도 N-채널 전력 트렌치 MOSFET (200)은 N-에피택셜 영역(epitaxial region) 또는 이들에 형성된 층 (204)을 가진 매우 낮은 저항(N++) 기재 (202)를 포함할 수 있다. 또한, P 바디 영역 또는 층 (204)은 N-에피택셜 영역의 상측 부분에 주입될 수 있다. 더욱이, 초고밀도 전력 트렌치 MOSFET (200)은 N++ 소스 영역 또는 P 바디 영역 (206)의 상측 부분에 주입된 층 (206)을 포함할 수 있다. 전력 트렌치 MOSFET (200)은 또한 N++ 소스 층 (208) 내에 위치한 트렌치 (210), P 바디 층 (206)과 P-에피택셜 층 (204)를 포함할 수 있다. 또한, 트렌치 (210)는 유전체 물질 (212)를 포함하는 폴리실리콘 게이트 (214)와 유전체 물질 (220)을 포함할 수 있다. 전력 트렌치 MOSFET (200)은 또한 소스 메탈 영역(source metal region) 또는 침적된 층 (216) 또는 N++ 소스 층 (208)을 포함할 수 있다. 더욱이, 전력 트렌치 MOSFET (200)은 침적된 드레인 메탈(drain metal) 또는 백 메탈(back metal) 218 또는 P++ 기재 (202)를 포함할 수 있다.

[0018] 초고밀도 N-채널 전력 트렌치 MOSFET (200)은 도 2에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 초고밀도 전력 트렌치 MOSFET (200)은 도 2에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 초고밀도 전력 트렌치 MOSFET (200)은 여기에서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들로 한정되는 것은 아니다.

[0019] 도 3은 본 발명의 실시예에 따른 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (300)의 하나의 부분에 대한 측 단면도이다. 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (300)는 제작될 수 있고, 도 1의 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100)의 참조 내에서 설명된 어떤 유사한 방법에서의 기능이 될 수 있으나, 이에 한정되는 것은 아니다. 진보된 사진 석판 인쇄 기술과 본 발명의 다양한 실시예에 따른 기술들을 이용함으로써, 도 3의 초고밀도 P-채널 전력 트렌치 MOSFET (300)은, 이에 한정되는 것은 아니며, 20 제곱 밀리미터당 적어도 1 기가-셀(giga-cells)의 밀도보다 같거나 큰, 0.8 마이크로미터(PM) 셀피치(cell pitch) 보다 작은, 또는 대략 1.22 마이크로미터의 깊이를 가진 트렌치 팩킹 밀도를 포함할 수 있다. 더욱이, 트렌치 (110)의 하나는 대략 0.45 마이크로미터의 폭을 가지는 한편, 초고밀도 P-채널 전력 트렌치 MOSFET (300)의 폴리실리콘 게이트 (114)에 위치한 유전체 물질 (120)은 대략 0.31 마이크로미터의 깊이를 가진다. 또, 초고밀도 P-채널 전력 트렌치 MOSFET (300)의 P++ 소스 층 (108)은 대략 0.08 마이크로미터의 깊이를 가진다. 하나의 예로서, 대략 45도 기울기(Tilt)를 가진 경사 소스 주입은 초고밀도 P-채널 전력 트렌치 MOSFET (300)의 폴리실리콘 게이트 (114)의 실리콘 메사(Silicon Mesa)의 측면에 형성된 자가-정렬 소스를 가진다.

[0020] 초고밀도 전력 트렌치 MOSFET (300)은 도 3에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 초고밀도

전력 트렌치 MOSFET (300) 은 도 3에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 초고밀도 전력 트렌치 MOSFET (300) 은 여기에서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들로 한정되는 것은 아니다.

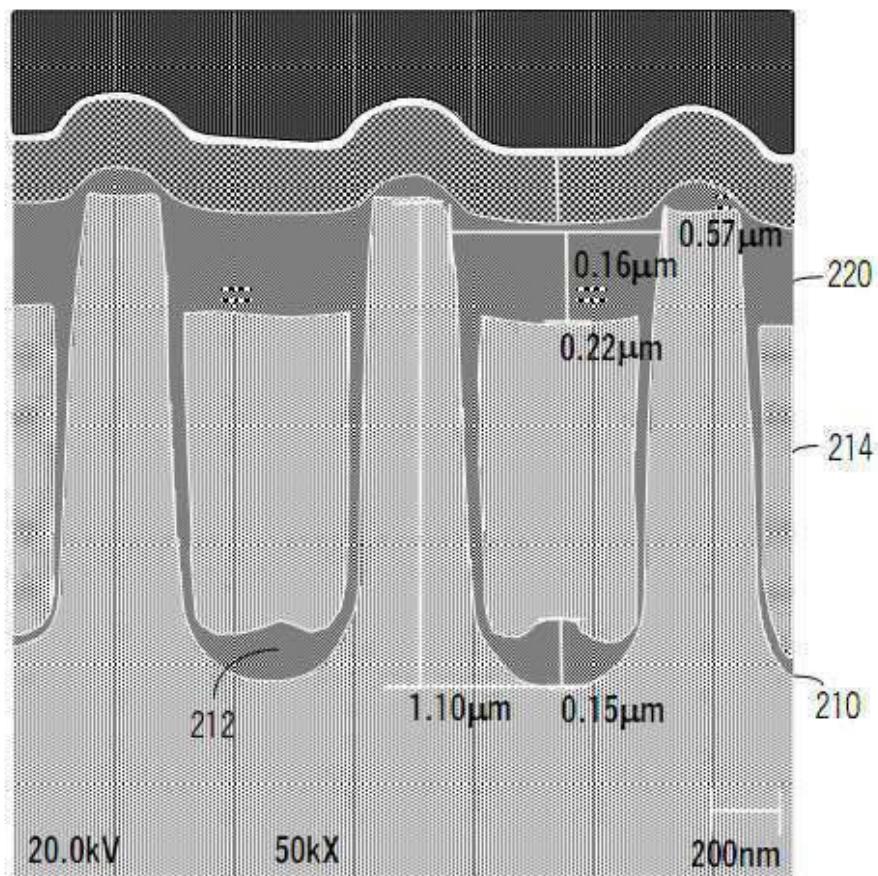

[0021] 도 4는 본 발명에 따른 초고밀도 TBO(Thick Bottom Oxide) N-채널 만입 게이트 전력 트렌치 MOSFET (400) 의 하나의 부분에 대한 측 단면도이다. 초고밀도 N-채널 전력 트렌치 MOSFET (400) 는 제작될 수 있고, 도 2의 초고밀도 N-채널 전력 트렌치 MOSFET (200)의 참조 내에서 설명된 어떤 유사한 방법에서의 기능이 될 수 있으나, 이에 한정되는 것은 아니다. 진보된 사진 석판 인쇄 기술과 본 발명의 다양한 실시예에 따른 기술들을 이용함으로써, 도 4의 초고밀도 N-채널 전력 트렌치 MOSFET (400) 은, 이에 한정되는 것은 아니며, 20 제곱 밀리미터당 적어도 1 기가-셀(giga-cells)의 밀도보다 같거나 큰, 0.8 마이크로미터(PM) 셀피치(cell pitch) 보다 같거나 작은, 또는 대략 1.10 마이크로미터의 깊이를 가진 트렌치 팩킹 밀도를 포함할 수 있다. 더욱이, 트렌치 (220) 의 하나는 대략 0.57 마이크로미터의 폭을 가지는 한편, 초고밀도 N-채널 전력 트렌치 MOSFET (400) 의 폴리실리콘 게이트 (214)에 위치한 유전체 물질 (220) 은 대략 0.22 마이크로미터의 깊이를 가진다. 더욱이, TBO(Thick Bottom Oxide) (또는 유전체 물질) (212) 는 대략 0.15 마이크로미터의 깊이를 가진다.

[0022] 초고밀도 전력 트렌치 MOSFET (400) 은 도 4에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 초고밀도 전력 트렌치 MOSFET (400) 은 도 4에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 초고밀도 전력 트렌치 MOSFET (400) 은 여기에서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들로 한정되는 것은 아니다.

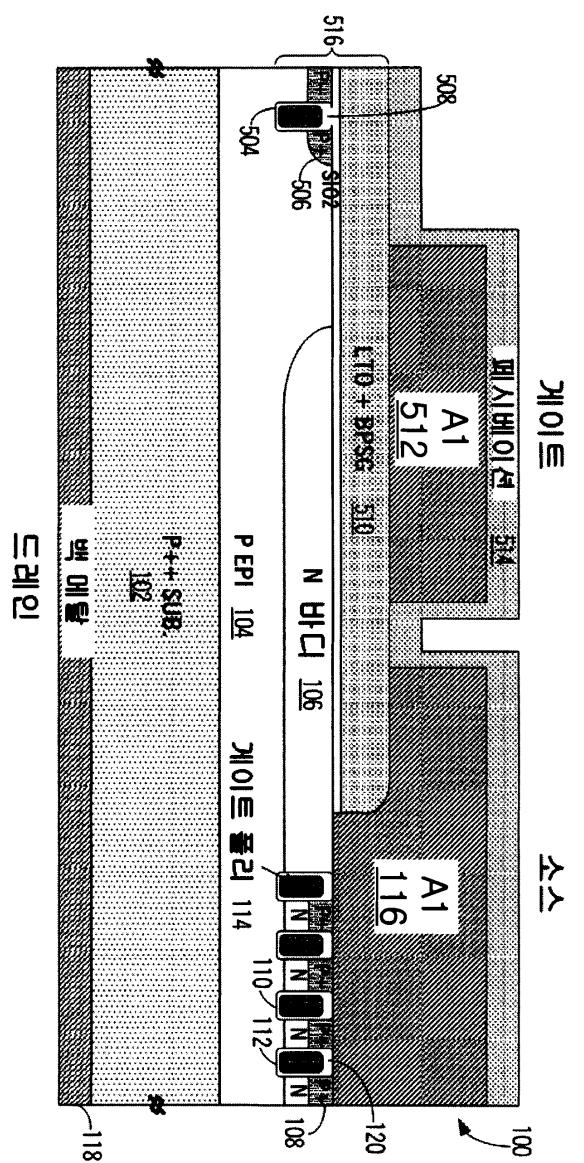

[0023] 도 5는 본 발명의 다양한 실시예에 따른 장치 (500) 의 측 단면도이다. 구체적으로, 장치 (500) 은 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) 과 함께 종래의 엣지 터미네이션 (516) 을 포함한다. 하나의 예로써, 장치 (500) 은 표면 위상최적화(topology) 이슈(issue)를 방지하기 위해 폴리실리콘 CMP, 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질 CMP 평면 기술에 의해 형성될 수 있다. 엣지 터미네이션 (516)의 부분은 P-에피택셜 층 (104) 내에서 형성될 수 있다. 예를 들어, 엣지 터미네이션 (516) 은 P-에피택셜 층 (104) 내에 위치한 트렌치 (504) 를 포함할 수 있다. 또한, 트렌치 (504) 는 실리콘 디옥사이드 ( $\text{SiO}_2$ ), LTO, SACVD 옥사이드 이들과 유사한 물질들과 같은 유전체 물질 (508)에 의해 형성된 다이 엣지 폴리실리콘(die edge Polysilicon) 502 를 포함할 수 있으며, 이에 한정되는 것은 아니다. 더욱이, 엣지 터미네이션 (516) 은 트렌치 (504) 의 양측면의 P-에피택셜 층 (104) 내에 주입될 수 있는 P++ 영역 (506) 을 포함할 수 있다. 유전체 물질 (508) 은 소스 접촉부 (116) 의 아래로 연장될 수 있다. 더욱이, 엣지 터미네이션 (516) 은 저온 옥사이드 (LTO)와 해당 분야에서 전기적 범위(Field)를 감소시키기 위해 유전체 물질 (508) 을 침적시킨 BPSG(borophosphosilicate glass) 층 (510) 을 포함할 수 있다. LTO+ BPSG 층 (510)와 유전체 물질 (508) 는 소스 메탈 (116) 의 아래로 연장될 수 있다. 장치 (500)의 게이트 메탈 베스 (512) 은 LTO+ BPSG 층 (510) 상부에 형성될 수 있다. 추가적으로, 페시베이션(Passivation) 층 (514) 는 LTO+ BPSG 층 (510), 게이트 메탈 베스 (512) 및 소스 메탈 (116) 상부에 침적될 수 있다.

[0024] 하나의 실시예로서 장치 (500) 은 엣지 터미네이션 (516) 과 유사한 엣지 터미네이션과 함께 초고밀도 N-채널 만입 게이트 전력 트렌치 MOSFET (200) 을 포함하여 제작될 수 있다. 이러한 실시예의 하나로 예를 들면, 장치 (500) 내에서 어떠한 P 영역 또는 기재는 N 영역 또는 기재에 대응하여 수행될 수 있다. 더욱이, 장치 (500) 내에서 어떠한 N 영역은 P 영역에 대응하여 수행될 수 있다.

[0025] 장치 (500) 은 도 5에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 장치 (500) 은 도 5에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 장치 (500) 은 여기에서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들로 한정되는 것은 아니다.

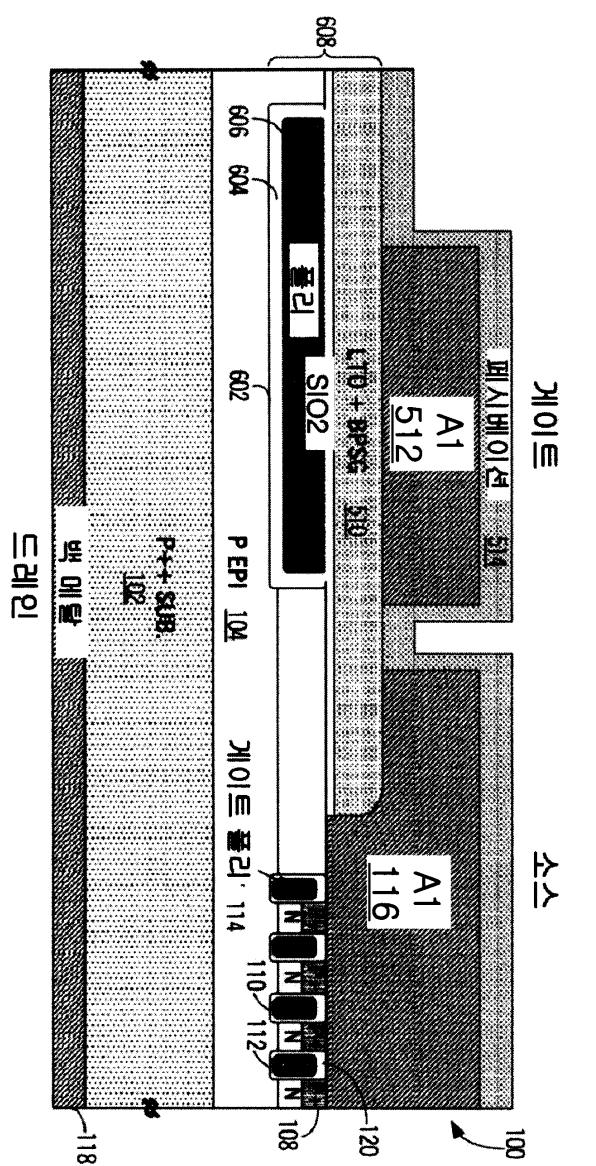

[0026] 도 6은 본 발명의 다양한 실시예에 따른 장치 (600) 의 측 단면도이다. 구체적으로, 장치 (600) 은 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) 과 함께 트렌치 엣지 터미네이션 (608) 을 포함한다. 하나의 예로써, 장치 (600) 은 표면 위상최적화(topology) 이슈(issue)를 방지하기 위해 폴리실리콘 CMP, 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질 CMP 평면 기술에 의해 형성될 수 있다. 트렌치 엣지 터미네이션 (608)의 부분은 P-에피택셜 층 (104) 내에서 제작될 수 있다. 예를 들어, 트렌치 엣지 터미네이션 (608) 은 P-에피택셜 층 (104) 내에 위치한 엣지 터미네이션 트렌치 (602) 를 포함할 수 있다. 또한, 트렌치 (602) 는 실리콘 디옥사이드 ( $\text{SiO}_2$ ), LTO, SACVD 옥사이드 이들과 유사한 물질들과 같은 유전체 물질 (604)에 의해 형성된 엣지 터미네이션 폴리실리콘 (606) 를 포함할 수 있으며, 이에 한정되는 것은 아니다. 유전체 물질 (604) 는 엣지 터미네이션 트렌치 (602) 내에서 다른 두께로 제작될 수 있다. 이러한 실시예의 하나로 예를 들면, 유전체 물질

(604) 의 두께는 장치 (600)의 파괴 전압(BVds) 율로 정의될 수 있다. 유전체 물질 (604) 는 소스 메탈 (116) 의 아래로 연장될 수 있다. 더욱이, 트렌치 엣지 터미네이션 (608) 은 저온 옥사이드 (LTO) 와 해당 분야에서 전기적 범위(Field)를 감소시키기 위해 유전체 물질 (604) 을 침적시킨 BPSG(borophosphosilicate glass) 층 (510) 을 포함할 수 있다. LTO+ BPSG 층 (510) 와 유전체 물질 (604) 는 소스 메탈 (116) 의 아래로 연장될 수 있다. 장치 (600) 의 게이트 메탈 버스 (512) 은 LTO+ BPSG 층 (510) 상부에 형성될 수 있다. 추가적으로, 폐시베이션 (Passivation) 층 (514) 는 LTO+ BPSG 층 (510), 게이트 메탈 버스 (512) 및 소스 메탈 (116) 상부에 침적될 수 있다.

[0027] 하나의 실시예에서, 트렌치 엣지 터미네이션 (608) 은 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) 와 함께 또는 분리되어 제작될 수 있다. 실시예에서, 유전체 물질 (604) 는 엣지 터미네이션 트렌치 (602) 내에서 침적 및/또는 성장될 수 있다. 예를 들어, 엣지 터미네이션 트렌치 (602) 내에서 유전체 물질 (604) 이 바람직한 두께를 가진다면, 유전체 물질 (604) 은 마스크(Mask)를 이용하여 엣지 터미네이션 트렌치 (602) 내에서 침적될 수 있다. 일단 유전체 물질 (604) 가 엣지 터미네이션 트렌치 (602) 내에서 침적 및/또는 성장되었으면, 엣지 터미네이션 폴리실리콘 (606) 은 유전체 물질 (604) 상부에 침적될 수 있다. 이러한 후에, 폴리실리콘 CMP 과정은 엣지 터미네이션 폴리실리콘 (606) 을 평탄화 시키기 위해 이용될 수 있다. 이러한 경우에, 폴리실리콘 CMP 단계는 과정 중에 야기되는 문제점인 위상최적화(topology) 발생 없이 어떠한 절차 흐름 내에 삽입이 가능한 엣지 터미네이션 과정으로 실리콘 표면을 균일적으로 평평하게 회복(Return)시킬 수 있다. 또한, 폴리실리콘 백 에칭 단계는 엣지 터미네이션 폴리실리콘 (606) 에서 이용될 수 있다. 더욱이, 유전체 물질 (604) 의 침적 단계는 엣지 터미네이션 폴리실리콘 (606) 과 N 바디 층 (106) 상에 수행될 수 있다. 하나의 예로서, 유전체 물질 CMP 과정은 유전체 물질 (604) 의 새로운 침적 상에서 수행될 수 있다. 트렌치 엣지 터미네이션 (608) 은 이들 표면에 어떠한 새로운 위상최적화 문제 및 실리콘 영역의 손실 없이 형성될 수 있다.

[0028] 다양한 실시예들에 따른 도 6에서, 엣지 터미네이션 트렌치 (602) 는 트렌치 엣지 터미네이션 (608) 제작 이외에 다른 목적으로 이용될 수 있다. 예를 들어, 폴리실리콘 다이오드, 폴리실리콘 저항기, 폴리실리콘 온도 센서 또는 이들과 유사한 것들과 같은 기능적인 폴리실리콘 구조의 넓은 다양성은 엣지 터미네이션 트렌치 (602) 내에서 제작될 수 있다. 하나 또는 그 이상의 기능적인 폴리실리콘 구조는 엣지 터미네이션 트렌치 (602) 내에서 다양한 방법으로 제작될 수 있다. 예를 들어, 하나 또는 그 이상의 기능적인 폴리실리콘 구조는, 참조로 합체되는 미국특허출원 No. 7/544,545, 명칭 " Trench Polysilicon Diode ", 저자 Chen et al., 출판일 6월 9일, 2009년도 내에 설명되어 있는 어떠한 방법의 엣지 터미네이션 트렌치 (602) 내에서 제작될 수 있다. 하나의 실시예로, 도 6의 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) 와, 엣지 터미네이션 트렌치 (602) 내에서 하나 또는 그 이상의 기능적인 폴리실리콘 구조는 제조비용을 감소시키도록 함께 또는 본질적으로 동시에 제작될 수 있다. 하나의 실시예에서, 도 6의 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) 엣지 터미네이션 트렌치 (602) 내에서 하나 또는 그 이상의 기능적인 폴리실리콘 구조로부터 분리되어 제작될 수 있다

[0029] 장치 (600) 의 하나의 실시예는 트렌치 엣지 터미네이션 (608) 과 유사한 트렌치 엣지 터미네이션과 함께 초고밀도 N-채널 만입 게이트 전력 트렌치 MOSFET (200) 을 포함하여 제작될 수 있다. 이러한 실시예의 예로서, 장치 (600) 내에 나타나는 어떠한 P 영역 또는 기질은 N 영역 또는 기질과 대응하여 수행될 수 있다. 게다가, 장치 (600) 내에 나타나는 어떠한 N 영역은 P 영역에 대응하여 수행될 수 있다.

[0030] 장치 (600) 은 도 6에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 장치 (600) 은 도 6에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 장치 (600) 은 여기에서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들로 한정되는 것은 아니다.

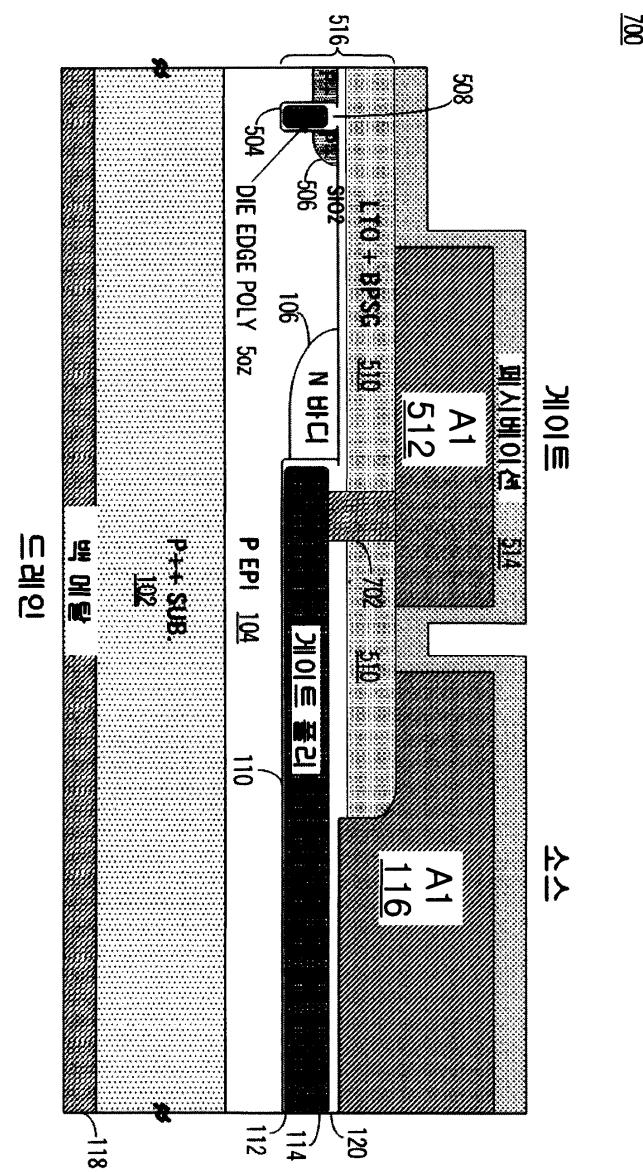

[0031] 도 7은 본 발명의 다양한 실시예에 따른 장치 (700) 의 측 단면도이다. 구체적으로, 장치 (700) 은 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) (도시하지 않음) 와 관계된 게이트 핵업(Gate Pickup)과 함께 종래의 엣지 터미네이션 (516) 을 포함한다. 하나의 예로써, 장치 (700) 는 표면 위상최적화(topology) 이슈(issue) 를 방지하기 위해 폴리실리콘 CMP, 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질 CMP 평면 기술에 의해 형성될 수 있다. 하나의 예로서, 장치 (700) 는 어떻게 게이트 실리콘 (114) 이 게이트 메탈 버스 (512) 와 결합되는지를 보여준다. 예를 들어, 하나 또는 그 이상의 폴리실리콘 (114) 은 소스 메탈 (116) 과 게이트 메탈 버스 (512) 의 아래로 연장되어 형성된다. 홀 또는 바이아(Via) (702) 는 LTO 와, BPSG 층 (510) 와, 유전체 물질 (508), (120) 을 통해 형성될 수 있다. 하나의 예로서, 메탈이 상기 게이트 메탈 버스 (512) 형성에 사용될 때, 상기 게이트 메탈 버스 (512) 의 상기 메탈은 상기 바이아(Via) (702) 를 채울 수 있고, 이들에 게이트 실리콘 (114) 와 접촉될 수 있다.

- [0032] 엣지 터미네이션 (516)의 부분은 P-에피택셜 층 (104) 내에 제작된다. 예를 들어, 엣지 터미네이션 (516)은 P-에피택셜 층 (104) 내에 위치한 트렌치 (504)를 포함할 수 있다. 또한, 트렌치 (504)는 실리콘 디옥사이드 ( $\text{SiO}_2$ ), LTO, SACVD 옥사이드 이들과 유사한 물질들과 같은 유전체 물질 (508)에 의해 형성된 다이 엣지 폴리실리콘 502를 포함할 수 있으며, 이에 한정되는 것은 아니다. 더욱이, 엣지 터미네이션 (516)은 해당 분야에서 전기적 범위(Field)를 감소시키기 위해 유전체 물질 (508) 상에 침적시킨 LTO+BPSG(borophosphosilicate glass) 층 (510)을 포함할 수 있다. LTO+BPSG 층 (510)과 유전체 물질 (508)은 소스 메탈 (116)의 아래로 연장될 수 있다. 장치 (700)의 게이트 메탈 버스 (512)는 LTO+BPSG 층 (510) 상부에 형성될 수 있다. 페시베이션(Passivation) 층 (514)은 LTO+BPSG 층 (510), 게이트 메탈 버스 (512) 및 소스 메탈 (116) 상부에 침적될 수 있다.

- [0033] 도 7의 장치 (700)에 따른 하나의 실시예는 다른 형태로 제작될 수 있음을 보여준다. 이러한 실시예에 따른 예에서, 장치 (700) 내의 어떠한 P 영역 또는 기재는 N 영역 또는 기재에 대응하여 수행될 수 있다. 더욱이, 장치 (700) 내에 나타난 어떠한 N 영역은 P 영역에 대응하여 수행될 수 있다.

- [0034] 장치 (700)은 도 7에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 장치 (700)은 도 7에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 장치 (700)은 여기에서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들로 한정되는 것은 아니다.

- [0035] 도 8은 본 발명의 다양한 실시예에 따른 장치 (800)의 측 단면도이다. 구체적으로, 장치 (800)은 초고밀도 P-채널 만입 게이트 전력 트렌치 MOSFET (100) (도시하지 않음)와 관계된 게이트 픽업(Gate Pickup)과 함께 트렌치 엣지 터미네이션 (808)을 포함한다. 트렌치 엣지 터미네이션 (808)은 제작될 수 있으며, 도 6의 트렌치 엣지 터미네이션 (608)의 참조 내에 설명된 유사한 어떠한 방법의 기능이 될 수 있으나, 이에 한정되는 것은 아니다. 하나의 예에서, 장치 (800)은 표면 위상최적화(topology) 이슈(issue)를 방지하기 위해 폴리실리콘 CMP, 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질 CMP 평면 기술에 의해 형성될 수 있다. 트렌치 엣지 터미네이션 (808)은 수행될 수 있으며, 본원에서 설명되는 트렌치 엣지 터미네이션과 유사한 어떠한 방법의 기능이 될 수 있으며, 이에 한정되는 것은 아니다. 하나의 실시예에서, 장치 (800)는 게이트 폴리실리콘 (114)와 게이트 메탈 버스 (512)가 어떻게 결합되는지를 보여준다. 예를 들어, 예를 들어, 하나 또는 그 이상의 폴리실리콘 (114)는 소스 메탈 (116)과 게이트 메탈 버스 (512)의 아래로 연장되어 형성된다. 훌 또는 바이아(Via) (702)는 LTO와, BPSG 층 (510) 와, 유전체 물질 (508), (120)을 통해 형성될 수 있다. 하나의 예에서, 메탈이 게이트 메탈 버스 (512) 형성에 사용될 때, 게이트 메탈 버스 (512)의 메탈은 바이아(Via) (702)를 채울 수 있고, 게이트 실리콘 (114)과 접촉될 수 있다.

- [0036] 트렌치 엣지 터미네이션 (808)의 부분은 P-에피택셜 층 (104) 내에서 제작될 수 있다. 예를 들어, 트렌치 엣지 터미네이션 (808)은 P-에피택셜 층 (104) 내에서 형성된 트렌치 (802)를 포함할 수 있다. 더욱이, 트렌치 (802)는 실리콘 디옥사이드 ( $\text{SiO}_2$ ), LTO, SACVD 옥사이드 이들과 유사한 물질들과 같은 유전체 물질 (804)에 의해 형성된 엣지 터미네이션 폴리실리콘 (806)을 포함할 수 있으며, 이에 한정되는 것은 아니다. 유전체 물질 (804)은 엣지 터미네이션 트렌치 (802) 내에서 다른 두께로 제작될 수 있다. 이러한 실시예의 하나로 예를 들면, 유전체 물질 (804)의 두께는 장치 (800)의 파괴 전압(BVds)으로 정의될 수 있다. 유전체 물질 (804)은 소스 메탈 (116)의 아래로 연장될 수 있다. 더욱이, 트렌치 엣지 터미네이션 (808)은 해당 분야에서 전기적 범위(Field)를 감소시키기 위해 유전체 물질 (804) 상에 침적시킨 LTO+BPSG(borophosphosilicate glass) 층 (510)을 포함할 수 있다. LTO+BPSG 층 (510)과 유전체 물질 (804)은 소스 메탈 (116)의 아래로 연장될 수 있다. 장치 (800)의 게이트 메탈 버스 (512)는 LTO+BPSG 층 (510) 상부에 형성될 수 있다. 추가적으로, 페시베이션(Passivation) 층 (514)은 LTO+BPSG 층 (510), 게이트 메탈 버스 (512) 및 소스 메탈 (116) 상부에 침적될 수 있다.

- [0037] 도 8의 장치 (800)에 따른 하나의 실시예는 다른 형태로 제작될 수 있음을 보여준다. 이러한 실시예에 따른 예에서, 장치 (800) 내의 어떠한 P 영역 또는 기재는 N 영역 또는 기재에 대응하여 수행될 수 있다. 또한, 장치 (800) 내에 나타난 N 영역은 P 영역에 대응하여 수행될 수 있다.

- [0038] 장치 (800)는 도 8에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 장치 (800)는 도 8에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 장치 (800)는 여기서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0039] 도 9는 본 발명의 다양한 실시예에 따른 장치 (900)의 측 단면도이다. 구체적으로, 장치 (900)은 초고밀도 P-

채널 만입 게이트 전력 트렌치 MOSFET 100 (도시하지 않음)와 관계된 게이트 팽거(Gate Finger)과 함께 종래의 엣지 터미네이션 (516)을 포함한다. 다이가 커질 경우에, 다이 내에서 게이트 충전 지연(Gate Charge Delay) 문제(issue)를 방지하는 범위 내에서 바람직하게 하나 또는 그 이상의 폴리실리콘 게이트 팽거 (906)를 포함할 수 있다. 하나의 예로써, 장치 (900)은 표면 위상최적화(topology) 이슈(issue)를 방지하기 위해 폴리실리콘을 화학기계적 연마(CMP), 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질을 화학기계적 연마 (CMP) 평면 기술에 의해 형성될 수 있다. 하나의 예로서, 장치 (900)은 어떻게 폴리실리콘 게이트 팽거 (906)가 게이트 메탈 (912)와 결합되는지를 보여준다. 예를 들어, 게이트 팽거 트렌치 (902)는 N 바디 (106) 및 P-에피택 층 (104) 내에서 제작될 수 있다. 또한, 게이트 팽거 트렌치 (902)는 실리콘 디옥사이드 ( $\text{SiO}_2$ ), LTO, SACVD 옥사이드 이들과 유사한 물질들과 같은 유전체 물질 (904)에 의해 형성된 폴리실리콘 게이트 팽거 (906)을 포함할 수 있으며, 이에 한정되는 것은 아니다. 유전체 물질 (904)는 게이트 메탈 (912) 및 소스 메탈 (914, 916) 아래로 연장될 수 있다.

[0040] 더욱이, LTO+BPSG 층 (910)은 해당 분야에서 전기적 범위(Field)를 감소시키기 위해 유전체 물질 (904) 상에 침적될 수 있다. LTO+BPSG 층 (910) 및 유전체 물질 (904)는 게이트 메탈 (912) 및 소스 메탈 (914, 916) 아래로 연장될 수 있다. 장치 (900)의 게이트 메탈 (912)은 LTO+BPSG 층 (910) 상에 형성될 수 있다. 추가적으로, 페시베이션(Passivation) 층 (918)은 LTO+ BPSG 층 (910), 게이트 메탈 (912) 및 소스 메탈 (914, 916) 상부에 침적될 수 있다. 홀 또는 바이아(Via) (908)는 LTO+ BPSG 층 (910) 와, 유전체 물질 (904)을 통해 형성될 수 있다. 하나의 예에서, 메탈이 게이트 메탈 (912) 형성에 사용될 때, 상기 게이트 메탈 (912)의 상기 메탈은 상기 바이아(Via) (908)를 채울 수 있고, 이들만으로 상기 실리콘 게이트 팽거 (906)와 접촉될 수 있다. P++ 소스 영역 (920)은 메탈 (914, 916) 아래로 연장된 N 바디 층 (106) 내에 주입되어 있다.

[0041] 도 9의 장치 (900)에 따른 하나의 실시예는 다른 형태로 제작될 수 있음을 보여준다. 이러한 실시예에 따른 예에서, 장치 (900) 내의 어떠한 P 영역 또는 기재는 N 영역 또는 기재에 대응하여 수행될 수 있다. 더욱이, 장치 (900) 내에 나타난 어떠한 N 영역은 P 영역에 대응하여 수행될 수 있다.

[0042] 장치 (900)은 도 9에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 장치 (900)은 도 9에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 장치 (900)는 여기서 설명되는 유사한 방법으로 이용 또는 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0043] 도 10은 본 발명의 다양한 실시예에 따른 도 9의 장치 (900)의 다른 측 단면도이다. 구체적으로, 도 10은 장치 (900)의 폴리실리콘 게이트 팽거 (906)의 길이방향의 측 단면도이다. 하나의 실시예에서, 도 10의 장치 (900)는 표면 위상최적화(topology) 이슈(issue)를 방지하기 위해 폴리실리콘 CMP, 폴리실리콘 백 에칭(polysilicon etch back) 및 유전체 물질 CMP 평면 기술에 의해 형성될 수 있다. 하나의 예로서, 장치 (900)은 폴리실리콘 게이트 팽거 (906)가 게이트 메탈 (912)과 어떻게 결합되는지를 보여준다.

[0044] 예를 들어, 게이트 팽거 트렌치 (902)는 N 바디 (106) (도시하지 않음)와 P-에피택 층 (104) 내에서 제작될 수 있다. 게이트 팽거 트렌치 (902)는 실리콘 디옥사이드 ( $\text{SiO}_2$ ), LTO, SACVD 옥사이드 이들과 유사한 물질들과 같은 유전체 물질 (804)에 의해 형성된 폴리실리콘 게이트 팽거 (906)을 포함할 수 있으며, 이에 한정되는 것은 아니다. 유전체 물질 (904)는 상기 게이트 메탈 (912)와 소스 메탈 (1002, 1004)의 아래로 연장될 수 있다. 더욱이, 상기 LTO+BPSG 층 (910)은 해당 분야에서 전기적 범위(Field)를 감소시키기 위해 상기 유전체 물질 (904) 상에 침적될 수 있다. 상기 LTO+BPSG 층 (910)은 상기 게이트 메탈 (912) 및 상기 소스 메탈 (1002, 1004)의 각각의 부분 아래로 연장될 수 있다. 장치 (900)의 게이트 메탈 (912)은 LTO+BPSG 층 (910) 상에 형성될 수 있다. 추가적으로, 페시베이션(Passivation) 층 (918)은 LTO+ BPSG 층 (910), 게이트 메탈 (912) 및 소스 메탈 (1002, 1004) 상부에 침적될 수 있다. 홀 또는 바이아(Via) (908)는 LTO+ BPSG 층 (910) 와, 유전체 물질 (904)을 통해 형성될 수 있다. 하나의 예에서, 메탈이 상기 게이트 메탈 (912) 형성에 사용될 때, 상기 게이트 메탈 (912)의 상기 메탈은 상기 바이아(Via) (908)를 채울 수 있고, 이들만으로 상기 실리콘 게이트 팽거 (906)와 접촉될 수 있다.

[0045] 도 10의 상기 장치 (900)에 따른 하나의 실시예는 다른 형태로 제작될 수 있음을 보여준다. 이러한 실시예에 따른 예에서, 상기 장치 (900) 내의 어떠한 P 영역 또는 기재는 N 영역 또는 기재에 대응하여 수행될 수 있다. 더욱이, 장치 (900) 내에 나타난 어떠한 N 영역은 P 영역에 대응하여 수행될 수 있다.

[0046] 장치 (900)는 도 10에 도시되어 있는 모든 요소들을 포함하지 않는다. 또한, 장치 (900)는 도 10에 도시되어 있지 않은 하나 또는 그 이상의 요소들을 포함하여 수행될 수 있다. 장치 (900)는 여기서 설명되는 유사한 방

법으로 이용 또는 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0047] 도 11 내지 도 14의 각각은 본 발명의 다양한 실시예에 따른 방법의 흐름도이다. 비록 각 흐름도에는 구체적인 작동이 개시되어 있지 않지만, 그러한 작동은 실시예이다. 각각의 방법은 도면에 도시되어 있는 작동의 모두를 포함하지는 않는다. 또한, 각각의 방법은 다양한 다른 작동 및/또는 개시된 작동의 다양성을 포함한다.

[0048] 마찬가지로, 각각의 흐름도의 작동의 연속은 수정될 수 있다. 각각의 흐름도에서 모든 작동들이 수행되는 것은 아니다. 다양한 실시예에서, 각각의 방법의 하나 또는 그 이상의 작동들은 소프트웨어, 하드웨어 또는 이들의 조합에 의해 조절 또는 운영될 수 있으나, 이들만으로 한정되는 것은 아니다. 각각의 방법은 프로세서(들) 및 기록 및 실행 가능한 지침(또는 코드)이 있는 컴퓨터 또는 컴퓨팅 장치의 조절 하의 전기적 요소들에 의해 조절 또는 운영될 수 있다. 기록 및 실행 가능한 지침(또는 코드)이 있는 컴퓨터 또는 컴퓨팅 장치는 저장될 수 있다. 예를 들어, 휴발성 메모리를 사용할 수 있는 컴퓨팅 장치, 컴퓨터 또는 비휘발성 메모리를 사용할 수 있는 컴퓨팅 장치, 및/또는 컴퓨터 또는 대용량 데이터 저장으로 사용할 수 있는 컴퓨팅 장치와 같은 데이터 저장 요소들일 수 있다. 그러나, 기록 및 실행 가능한 지침(또는 코드)이 있는 컴퓨터 또는 컴퓨팅 장치는 컴퓨터 또는 기록 가능한 중간 또는 메모리 컴퓨팅 장치의 어떠한 타입 내에도 저장될 수 있다.

[0049] 도 11은 초고밀도 트렌치 MOSFET 제조를 위한 본 발명의 다양한 실시예에 따른 방법 1100의 흐름도이다. 예를 들어, 방법 1100은 기재 상의 에피택셜 영역(an epitaxial region)을 형성하는 단계를 포함할 수 있다. 추가적으로, 바디 영역(body region)은 상기 에피택셜 영역에 주입될 수 있다. 트렌치들은 수직형 MOSFET의 하나의 부분으로서 상기 바디 영역 및 상기 에피택셜 영역에 형성될 수 있다. 더욱이, 게이트 옥사이드(gate oxide)는 성장할 수 있고, 게이트 폴리실리콘(gate poly silicon)은 상기 트렌치들 내에 침적될 수 있다. 화학기계적 연마(CMP)는 상기 게이트 폴리실리콘 및 상기 게이트 폴리실리콘을 백 에칭(etching back) 하는 단계에서 수행될 수 있다. 하나 또는 그 이상의 소스 영역은 상기 바디 영역에 주입될 수 있다. 유전체 물질은 성장하거나 상기 게이트 폴리실리콘 및 하나 또는 그 이상의 트렌치들 상에 침적될 수 있다. 상기 유전체 물질을 화학기계적으로 연마를 수행한다. LTO와 BPSG 유전체는 그들의 상측 표면에 침적될 수 있다. 에칭 소스(Etch source) 및 게이트 접촉부들. 전면 메탈 층과 폐시베이션 층은 형성될 수 있다. 웨이퍼 백 그라운딩(Wafer back grounding)과 메탈리제이션(metallization)은 형성될 수 있다. 이러한 방법으로, 초고밀도 트렌치 MOSFET는 본 발명의 다양한 실시예에 따라 제작될 수 있다.

[0050] 도 11의 작동 1102에서, 에피택셜 영역(예: 104 또는 204)은 기재(예: 102 또는 202) 상에 형성될 수 있다. 작동 1102는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1102는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0051] 작동 1104에서, 바디 영역(예: 106 또는 206)은 에피택셜 영역에 주입될 수 있다. 작동 1104는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1104는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0052] 도 11의 작동 1106에서, 트렌치들(예: 110 또는 210)은 상기 바디 영역과 수직형 MOSFET(예: 100 또는 200)의 하나의 부분으로서 상기 에피택셜 영역 내에 형성 또는 에칭될 수 있다.

[0053] 도 11의 작동 1108에서, 게이트 옥사이드(예: 112 또는 212)는 성장할 수 있고, 게이트 실리콘(예: 114 또는 214)은 상기 트렌치들 내에 침적될 수 있다. 작동 1108는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1108는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0054] 도 11의 작동 1110에서, 근본적으로 평탄화시키기 위해 게이트 실리콘을 화학기계적 연마를 행한다. 작동 1110은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1110는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0055] 작동 1112에서, 상기 게이트 폴리실리콘을 백 에칭(etch back)을 수행한다. 작동 1112는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1112는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0056] 작동 1114에서, 하나 또는 그 이상의 소스 영역(예: 108 또는 208)은 상기 바디 영역 내에 주입될 수 있다. 작동 1114는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1114는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0057] 도 11의 작동 1116에서, 유전체 물질(예:120 또는 220)은 성장할 수 있고, 상기 게이트 폴리실리콘 상과 하나 또는 그 이상의 트렌치들 내에 침적될 수 있다. 작동 1116은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1116은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0058] 작동 1118에서, 근본적으로 평탄화시키기 위해 상기 게이트 절연 유전체 물질을 화학기계적 연마를 행한다. 작동 1118은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1118은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0059] 도 11의 작동 1120에서, LTO 및 BPSG 유전체는 이들의 상측 표면에 침적될 수 있다. 작동 1120은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1120은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0060] 작동 1122에서, 소스와 게이트 접촉부를 에칭(또는 형성)한다. 작동 1122은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1122는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0061] 도 11의 작동 1124에서, 전면 메탈 층(예:116, 216, 512 또는 912) 및 페시베이션 층(예:514 또는 (918))은 형성될 수 있다. 작동 1124은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1124는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0062] 도 11의 작동 1126에서, 웨이퍼 백 그라운딩(Wafer back grounding)과 메탈리제이션(metallization)은 형성될 수 있다. 작동 1126은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1126은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다. 작동 1126이 일단 완료되면, 과정 1110은 종료 또는 강제 완료될 수 있다. 이러한 방식으로, 초고밀도 트렌치 MOSFET은 본 발명의 다양한 실시예에 따라 제작될 수 있다.

- [0063] 도 12는 초고밀도 트렌치 MOSFET 제조를 위한 본 발명의 다양한 실시예에 따른 방법 1200의 흐름도이다. 예를 들어, 방법 1200은 기재 상의 에피택셜 영역(an epitaxial region)을 형성하는 단계를 포함할 수 있다. 추가적으로, 트렌치들은 수직형 MOSFET의 하나의 부분으로서 상기 바디 영역 및 상기 에피택셜 영역에 형성 또는 에칭될 수 있다. 게이트 옥사이드(gate oxide)는 성장할 수 있고, 게이트 폴리실리콘(gate poly silicon)은 상기 트렌치들 내에 침적될 수 있다. 더욱이, 화학기계적 연마는 상기 게이트 폴리실리콘 상에서 수행될 수 있다. 바디 영역은 상기 에피택셜 영역 내에 주입될 수 있다. 추가적으로, 방법 1200은 상기 게이트 폴리실리콘을 백 에칭하는 단계를 포함할 수 있다. 하나 또는 그 이상의 소스 영역은 상기 바디 영역에 주입될 수 있다. 유전체 물질은 성장하거나 상기 게이트 폴리실리콘 및 하나 또는 그 이상의 트렌치들 내에 침적될 수 있다. 더욱이, 화학기계적 연마는 유전체 물질 상에서 수행될 수 있다. LTO와 BPSG 유전체는 그들의 상측 표면에 침적될 수 있다. 더욱이, 상기 방법 1200은 에칭 소스(Eching source) 및 게이트 접촉부를 포함할 수 있다. 전면 메탈 층과 페시베이션 층은 형성될 수 있다. 웨이퍼 백 그라운딩(Wafer back grounding)과 메탈리제이션(metallization)은 형성될 수 있다. 이러한 방법으로, 초고밀도 트렌치 MOSFET은 본 발명의 다양한 실시예에 따라 제작될 수 있다.

- [0064] 도 12의 작동 1202에서, 에피택셜 영역(예:104 또는 204)은 기재(예:102 또는 202) 상에 형성될 수 있다. 작동 1202는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1202는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0065] 작동 1(204)에서, 트렌치들(예:110 또는 210)은 수직형의 MOSFET의 부분으로서 상기 에피택셜 내에 형성 또는 에칭될 수 있다. 작동 1(204)는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1(204)는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0066] 도 12의 작동 1(206)에서, 게이트 옥사이드(예:112 또는 212)는 성장할 수 있고, 게이트 실리콘(예:114 또는 214)은 상기 트렌치들 내에 침적될 수 있다. 작동 1(206)은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1(206)은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0067] 도 12의 작동 1(208)에서, 근본적으로 평탄화시키기 위한 상기 CMP 게이트 폴리실리콘. 작동 1(208)은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1(208)은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0068] 작동 1210에서, 바디 영역(예:106 또는 (206))은 상기 에피택셜 영역 내에 주입될 수 있다. 작동 1210은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1210은 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0069] 작동 1212에서, 상기 게이트 폴리실리콘을 백 에칭(etch back)을 수행한다. 작동 1212은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1212는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0070] 작동 1214에서, 하나 또는 그 이상의 소스 영역(예:108 또는 208)은 상기 바디 영역 내에 주입될 수 있다. 작동 1214는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1214는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0071] 도 12의 작동 1216에서, 유전체 물질(예:120 또는 220)은 성장할 수 있고, 상기 게이트 폴리실리콘 상과 하나 또는 그 이상의 트렌치들 내에 침적될 수 있다. 작동 1216는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1216는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0072] 작동 1218에서, 근본적으로 평탄화시키기 위해 상기 게이트 절연 유전체 물질을 화학기계적 연마를 행한다. 작동 1218은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1218는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0073] 도 12의 작동 1220에서, LTO 및 BPSG 유전체는 이들의 상측 표면에 침적될 수 있다. 작동 1220은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1120는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0074] 작동 1222에서, 소스와 게이트 접촉부를 에칭(또는 형성)한다. 작동 1222은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1222는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0075] 도 12의 작동 1224에서, 전면 메탈 층(예:116, 216, 512 또는 912) 및 폐시베이션 층(예:514 또는 918)은 형성될 수 있다. 작동 1224은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1224는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0076] 작동 1226에서, 웨이퍼 백 그라운딩(Wafer back grounding) 과 메탈리제이션(예:118)은 형성될 수 있다. 작동 1226은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1226는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다. 작동 1226이 일단 완료되면, 과정 1200은 종료 및 강제 완료될 수 있다. 이러한 방식으로, 초고밀도 트렌치 MOSFET은 본 발명의 다양한 실시예에 따라 제작될 수 있다.

- [0077] 도 13은 초고밀도 트렌치 MOSFET 제조를 위한 본 발명의 다양한 실시예에 따른 방법 1300의 흐름도이다. 예를 들어, 방법 1300은 기재 상의 에피택셜 영역(an epitaxial region)을 형성하는 단계를 포함할 수 있다. 추가적으로, 트렌치들은 수직형 MOSFET의 하나의 부분으로서 상기 바디 영역 및 상기 에피택셜 영역에 형성 또는 에칭될 수 있다. 상기 게이트 옥사이드(gate oxide)는 성장할 수 있고, 상기 게이트 폴리실리콘(gate polyisilicon)은 상기 트렌치들 내에 침적될 수 있다. 더욱이, 화학기계적 연마는 상기 게이트 폴리실리콘 상에서 수행될 수 있다. 추가적으로, 방법 1300은 상기 게이트 폴리실리콘을 백 에칭하는 단계를 포함할 수 있다. 하나 또는 그 이상의 소스 영역은 상기 장래의 바디 영역에 주입될 수 있다. 유전체 물질은 성장하거나 상기 게이트 폴리실리콘 및 하나 또는 그 이상의 트렌치들 내에 침적될 수 있다. 더욱이, 화학기계적 연마는 유전체 물질 상에서 수행될 수 있다. 바디 영역은 상기 에피택셜 영역 내에 주입될 수 있다. LTO와 BPSG 유전체는 그들의 상측 표면에 침적될 수 있다. 더욱이, 상기 방법 1300은 에칭 소스(Eching source) 및 게이트 접촉부를 포함할 수 있다. 전면 메탈 층과 폐시베이션 층은 형성될 수 있다. 웨이퍼 백 그라운딩(Wafer back grounding) 과 메탈리제이션(metallization)은 형성될 수 있다. 이러한 방법으로, 초고밀도 트렌치 MOSFET는 본 발명의 다양한 실시예에 따라 제작될 수 있다.

- [0078] 도 13의 작동 1302에서, 에피택셜 영역(예:104 또는 (204))는 기재(예:102 또는 202) 상에 형성될 수 있다. 작동 1302는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1302는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0079] 작동 1304에서, 트렌치들(예:110 또는 210)은 수직형 MOSFET(예:100 또는 200)의 하나의 부분으로서 상기 에피택셜 영역 내에 형성 또는 에칭 될 수 있다. 작동 1304는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1304는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0080] 도 13의 작동 1306에서, 게이트 옥사이드(예:112 또는 212)는 성장할 수 있고, 게이트 실리콘(예:114 또는 214)는 상기 트렌치들 내에 침적될 수 있다. 작동 1306는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1306는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0081] 작동 1308에서, 근본적으로 평탄화시키기 위해 상기 게이트 폴리실리콘을 화학기계적 연마를 행한다. 작동 1308은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1308는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0082] 도 13의 작동 1310에서, 상기 게이트 폴리실리콘을 백 에칭(etch back)을 수행한다. 작동 1310은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1310는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0083] 작동 1312에서, 하나 또는 그 이상의 소스 영역(예:108 또는 208)은 상기 장래의 바디 영역 내에 주입될 수 있다. 작동 1114는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1114는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0084] 도 13의 작동 1314에서, 유전체 물질(예:120 또는 220)은 성장할 수 있고, 상기 게이트 폴리실리콘 상과 하나 또는 그 이상의 트렌치들 내에 침적될 수 있다. 작동 1314는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1314는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0085] 작동 1316에서, 근본적으로 평탄화시키기 위해 상기 게이트 절연 유전체 물질을 화학기계적 연마를 행한다. 작동 1316은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1316는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0086] 도 13의 작동 1318에서, 바디 영역(예:106 또는 206)은 상기 에피택셜 영역 내에 주입될 수 있다. 작동 1318은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1318는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0087] 작동 1320에서, LTO 및 BPSG 유전체는 이들의 상측 표면에 침적될 수 있다. 작동 1320은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1320는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0088] 작동 1322에서, 소스와 게이트 접촉부를 에칭(또는 형성)한다. 작동 1322은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1322는 여기에서 설명되는 내용과 유사한 어떠한 방법으로도 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0089] 도 13의 작동 1324에서, 전면 메탈 층(예:116, 216, 512 또는 912) 및 폐시베이션 층(예:514 또는 918)은 형성될 수 있다. 작동 1324은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1324는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

- [0090] 작동 1326에서, 웨이퍼 백 그라운딩(Wafer back grounding)과 메탈리제이션(metallization)(예:118)은 형성될 수 있다. 작동 1326은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1326는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다. 작동 1326이 일단 완료되면, 과정 1300은 종료 및 강제 완료될 수 있다. 이러한 방식으로, 초고밀도 트렌치 MOSFET은 본 발명의 다양한 실시예에 따라 제작될 수 있다.

- [0091] 도 14는 초고밀도 트렌치 MOSFET 제조를 위한 본 발명의 다양한 실시예에 따른 방법 1400의 흐름도이다. 예를 들어, 상기 방법 1400은 기재 상의 에피택셜 영역(an epitaxial region)을 형성하는 단계를 포함할 수 있다. 더 옥이, 옛지 터미네이션 트렌치는 수직형 MOSFET의 하나의 부분으로서 상기 에피택셜 영역 내에 형성 또는 에칭 될 수 있다. 추가적으로, 폴리실리콘은 상기 옛지 터미네이션 트렌치 내에 침적될 수 있다. 더욱이, 화학 기계적 연마는 상기 폴리실리콘 상에, 및 상기 폴리실리콘을 백 에칭하는 단계 중에 실행될 수 있다. 이러한 후에,

과정 1400은 방법 1100 (도 11), 방법 1200(도 12) 또는 방법 1300 (도13)의 조합이 될 수 있다. 다양한 실시 예에 따른 예를 들면, 과정 1400은 도 11의 작동 1104 내지 1126, 도 12의 작동 1(204) 내지 1226 또는 도 13의 작동 1304 내지 1326들이 연속적으로 이루어 질 수 있다. 이러한 방법으로, 본 발명의 다양한 실시예에 따른 트렌치 엣지 터미네이션은 초고밀도 트렌치 MOSFET의 하나의 부분으로 수행될 수 있다.

[0092] 도 14의 작동 1402에서, 에피택셜 영역(예:104 또는 204)는 기재(예:102 또는 202) 상에 형성될 수 있다. 작동 1402는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1402는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0093] 작동 1404에서, 엣지 터미네이션 트렌치(예:802)는 수직형 MOSFET(예:100 또는 200)의 하나의 부분으로서 상기 에피택셜 영역 내에 형성 또는 에칭될 수 있다. 작동 1404는 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1404는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0094] 도 14의 작동 1406에서, 유전체 물질(예:804)는 성장하거나, 상기 엣지 터미네이션 트렌치 내에 침적될 수 있다. 작동 1406은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1406는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0095] 작동 1408에서, 폴리실리콘(예:806)은 상기 엣지 터미네이션 트렌치 내에 침적될 수 있다. 작동 1408은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1408는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0096] 도 14의 작동 1410에서, 상기 폴리실리콘을 화학기계적으로 연마하고 상기 폴리실리콘은 백 에칭을 수행한다. 작동 1410은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1410는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다.

[0097] 과정 1412에서, 과정 1400은 도 11의 작동 1104 내지 1126, 도 12의 작동 1(204) 내지 1226 또는 도 13의 작동 1304 내지 1326들이 연속적으로 이루어 질 수 있다. 작동 1412은 넓은 다양한 방법으로 수행될 수 있다. 예를 들어, 작동 1412는 여기에서 설명되는 내용과 유사한 어떠한 방법으로 수행될 수 있으며, 이들만으로 한정되는 것은 아니다. 이러한 방법으로, 본 발명의 다양한 실시예에 따른 트렌치 엣지 터미네이션은 초고밀도 트렌치 MOSFET을 형성하는 하나의 부분으로서 수행될 수 있다.

[0098] 본 발명에 따른 다양한 구체적인 실시예들에 대한 상기의 설명들은 실시 및 설명의 목적에 비추어 표현되었다. 이들은 완전히 또는 본 발명의 서론 부분에 개시되어 있는 것에 국한되는 것은 아니며, 많은 수정 및 다양성이 상기 개시된 내용으로 비추어 볼 때, 가능하다 할 것이다. 본 발명은 본원의 청구항들과 이와 등등한 내용에 따라 해석된다. 여기서 설명된 모든 구성요소들, 부분들 및 단계들은 바람직하게 포함된다. 이를 어떠한 구성요소들, 부분들 및 단계들은 다른 구성 요소들, 부분들 및 단계들로 대체되거나, 해당분야의 당업자들에게 인지되는 범위내에서 모두가 함께 삭제될 수 있도록 이해된다.

## 구성

[0100] 본 내용은 하기의 구성들을 개시한다.

[0101] 제1구성, 수직형 MOSFET(vertical metal-oxide semiconductor field-effect transistor)용 바디 영역(body region) 내에 다수의 트렌치들(trenches)을 형성하는 과정; 상기 바디 영역 내로 소스 영역을 경사 주입(angle implanting)하는 단계; 상기 다수의 트렌치들 내에서 유전체 물질(dielectric material)을 성장시키는 단계; 상기 다수의 트렌치들 내에서 게이트 폴리실리콘(gate polysilicon)을 침적(depositing)시키는 단계; 상기 게이트 폴리실리콘을 화학기계적으로 연마(polishing)하는 단계; 및 상기 다수의 트렌치들 내에 상기 게이트 폴리실리콘을 백 에칭(back-etching back)시키는 단계;를 포함하는 것을 특징으로 하는 방법.

[0102] 제2 구성. 제 1 구성에 있어서, 상기 백 에칭된 게이트 폴리실리콘 상에 유전체 물질을 침적시키는 단계; 및 상기 유전체 물질을 화학기계적으로 연마하는 단계;를 더 포함하는 것을 특징으로 하는 방법.

[0103] 제3 구성. 제 2 구성에 있어서, 상기 유전체 물질 및 상기 소스 영역 상에 소스 접촉부(source contact)을 자가 정렬(self-aligning)시키는 단계를 더 포함하는 것을 특징으로 하는 방법

[0104] 제4 구성. 제 3 구성에 있어서, 상기 소스 접촉부는 상기 소스 영역의 적어도 하나와 접촉되는 것을 특징으로 하는 방법.

- [0105] 제5 구성. 제 1 구성에 있어서, 기재에 에피택셜 영역(epitaxial region)을 형성하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- [0106] 제6 구성. 제 5 구성에 있어서, 상기 에피택셜 영역은 P-이고, 상기 기재는 P++인 것을 특징으로 하는 방법

- [0107] 제7 구성. 제 5 구성에 있어서, 상기 에피택셜 영역은 N-이고, 상기 기재는 N++인 것을 특징으로 하는 방법.

- [0108] 제8 구성. 장치의 에픽택셜 영역 내의 옆지 터미네이션 트렌치를 형성하는 단계; 상기 옆지 터미네이션 트렌치 내의 유전체 물질(dielectric material)을 침적(depositing)하는 단계; 상기 옆지 터미네이션 트렌치 내의 폴리실리콘을 침적(depositing)하는 단계; 상기 폴리실리콘을 화학기계적으로 연마(polishing)하는 단계; 및 상기 옆지 터미네이션 트렌치 내에서 상기 폴리실리콘을 백 에칭(back-etching back) 하는 단계;를 포함하는 것을 특징으로 하는 방법.

- [0109] 제9 구성. 제 8 구성에 있어서, 상기 백 에칭된 폴리실리콘 상에 유전체 물질을 침적시키는 단계; 및 상기 유전체 물질을 화학기계적으로 연마하는 단계;를 더 포함하는 것을 특징으로 하는 방법

- [0110] 제10구성. 제 9 구성에 있어서, 상기 유전체 물질 상에 LTO 및 BPSG 하는 단계를 더 포함하는 것을 특징으로 하는 방법

- [0111] 제11구성. 제 8 구성에 있어서, 상기 에피택셜 영역 내에 바디 영역을 형성하는 단계를 더 포함하고, 상기 옆지 터미네이션 트렌치는 상기 바디 영역에 둘러싸여 있는 것을 특징으로 하는 방법.

- [0112] 제 12 구성. 제 8 구성에 있어서, 상기 형성 단계에는 수직형 MOSFET의 바디 영역 내에서 다수개의 게이트 트렌치들이 형성되는 단계가 더 포함되는 것을 특징으로 하는 방법.

- [0113] 제13구성. 제 12 구성에 있어서, 상기 폴리실리콘을 침적하는 단계에는 상기 게이트 트렌치(gate trench) 내에 폴리실리콘을 침적하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- [0114] 제14구성. 제 13 구성에 있어서, 상기 화학기계적 연마하는 단계에는 상기 게이트 트렌치(gate trench) 내에서 상기 폴리실리콘을 연마하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- [0115] 제15구성. 제 14 구성에 있어서, 상기 백 에칭(etching back) 단계에는 상기 게이트 트렌치 내에서 상기 폴리실리콘을 백 에칭하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- [0116] 제16구성. 수직형 MOSFET(vertical metal-oxide semiconductor field-effect transistor)용 바디 영역(body region) 내의 다수의 트렌치들(trenches); 상기 다수개의 트렌치들 각각은 유전체 물질로 형성된 게이트 폴리실리콘을 포함하고, 상기 유전체 물질의 상측 표면은 평편화 되며; 소스 접촉부; 및 상기 다수개의 트렌치들로 정의되는 다수개의 메사(Mesa)와, 각각의 상기 다수개의 메사는 상기 소스 접촉부와 접촉된 소스 영역을 포함하는 것을 특징으로 하는 장치.

- [0117] 제17구성. 제 16 구성에 있어서, 상기 다수의 트렌치들은 20 제곱 밀리미터당 적어도 1 기가-셀(giga-cells)의 밀도를 가지는 것을 특징으로 하는 장치.

- [0118] 제18구성. 제 16 구성에 있어서, 상기 다수의 트렌치들의 각각은 0.8 마이크로미터 셀피치(cell pitch) 또는 대략 1 마이크로미터 이하의 깊이를 갖는 것을 특징으로 하는 장치.

- [0119] 제19구성. 제 16 구성에 있어서, 상기 바디 영역 내의 옆지 터미네이션 트렌치, 상기 터미네이션 트렌치는 유전체 물질에 의해 생성된 터미네이션 폴리실리콘을 포함하고, 상기 유전체 물질의 상측 표면은 평편화 되는 것을 특징으로 하는 장치.

- [0120] 제20구성. 제 16 구성에 있어서, 상기 옆지 터미네이션 트렌치(edge termination trench)는 상기 수직형 MOSFET(MOSFET)의 게이트 접촉 보다 넓은 것을 특징으로 하는 장치.

- [0121] 본 발명이 속한 분야에서 통상의 지식을 가진 자라면 상기 내용을 바탕으로 본 발명의 범주 내에서 다양한 응용 및 변형을 수행하는 것이 가능할 것이다.

도면

도면1

100

도면2

200

도면3

300

도면4

400

도면5

도면6

도면7

도면8

도면9

도면10

도면11

기재 상의 에피택셜 영역 형성 1102

에피택셜 영역 내에 바디 영역을 주입 1104

바디 영역 내의 트렌치들 형성 1106

게이트 옥사이드 성장 및

게이트 폴리실리콘 침적 1108

게이트 폴리실리콘 평탄화 CMP 1110

게이트 폴리실리콘 백 에칭 1112

소스 영역 주입 1114

게이트 절연 유전체 성장 또는 침적 1116

게이트 절연 유전체 평탄화 CMP 1118

LTO 및 BPSG 유전체 물질 침적 1120

게이트 절연 유전체 평탄화 CMP 1122

전면 메탈리제이션 및 폐시베이션 1124

후면 그라운딩 및 메탈리제이션 1126

도면12

기재 상의 에피택셜 영역 형성 1202

에피택셜 영역 내에 트렌치들 형성 1204

게이트 옥사이드 성장 및

게이트 폴리실리콘 침적 1206

게이트 폴리실리콘 평탄화 CMT 1208

바디 영역 주입 1210

게이트 폴리실리콘 백 에칭 1212

소스 영역 주입 1214

게이트 절연 유전체 성장 또는 침적 1216

게이트 절연 유전체 평탄화 CMP 1218

LTO 및 BPSG 유전체 물질 침적 1220

소스 접촉부 및 게이트 접촉부 형성 1222

전면 메탈리제이션 및 페시베이션 1224

백 그라운딩 및 메탈리제이션 1226

도면13

기재 상의 에피택셜 영역 형성 1302

에피택셜 영역 내에 트렌치를 형성 1304

게이트 옥사이드 성장 및

게이트 폴리실리콘 침적 1306

게이트 폴리실리콘 평탄화 CMT 1308

게이트 폴리실리콘 백 에칭 1310

소스 영역 주입 1312

게이트 절연 유전체 성장 또는 침적 1314

게이트 절연 유전체 평탄화 CMP 1316

바디 영역 주입 1318

LTO 및 BPSG 유전체 물질 침적 1320

소스 접촉부 및 게이트 접촉부 형성 1322

전면 메탈리제이션 및 페시베이션 1324

후면 그라운딩 및 메탈리제이션 1326

도면14

기재 상의 에피택셜 영역 형성 1402

에지 터미네이션 트렌치 형성 1404

절연 유전체 층 성장 또는 침적 1406

트렌치 내 폴리실리콘

충진을 위한 침적 1408

폴리실리콘 CMT 및 백 에칭 1410

도 11의 1104 내지 1126,

또는 도 12의 1204 내지 1226,

또는 도 13의 1304 내지 1326 과정의 계속

1412