# **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 7:

(11) International Publication Number:

WO 00/62424

H03M 11/24

**A1**

US

(43) International Publication Date:

19 October 2000 (19.10.00)

(21) International Application Number:

PCT/US99/24306

(22) International Filing Date:

18 October 1999 (18.10.99)

(30) Priority Data:

09/290,139

13 April 1999 (13.04.99)

(81) Designated States: JP, KR, European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

### **Published**

With international search report. With amended claims and statement.

(71) Applicant: ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, Mail Stop 68, Sunnyvale, CA 94088–3453 (US).

(72) Inventors: SCHNIZLEIN, Paul, G.; 11410 Antler Bend Road, Austin, TX 78737 (US). TALLO, Kenneth; 3704 Last Oasis Hollow, Austin, TX 79739 (US).

(74) Agent: APPERLEY, Elizabeth, A.; Advanced Micro Devices, Inc., M/S 562, 5204 East Ben White Boulevard, Austin, TX 78741 (US).

## (54) Title: KEYPAD SCANNING WITH FEW PINS

### (57) Abstract

The invention is, in its various aspects, an apparatus and a method for scanning a keypad or a keyboard. The apparatus (20, 80) comprises a keypad (25, 88) and an integrated circuit (30, 84). The keypad includes a plurality of chained resistors (24) and a plurality of key switches (22, 86). Each of the plurality of key switches (22, 86) is tied to a common node (35, 92) at a first terminal (34, 87) thereof and tapping the chained resistors (24, 90) at a second node (44, 89) thereof. Each of the key switches (22, 86) generates a signal indicative of the respective key switch (22, 86) being pressed when the key switch (22, 86) is pressed. The integrated circuit (30, 84) is capable of receiving the generated signal. The integrated circuit (30, 84) furthermore includes an analog to digital converter (45 & 46, 100) capable of generating a reference signal and a circuit capable of determining which key switch (22, 86) has been pressed from the magnitude of the generated voltage signal and the reference signal. The method for scanning a keypad comprises generating a voltage signal whose magnitude indicates which key (22, 86) is being pressed, and determining from the magnitude of the generated voltage signal which key (22, 86) was pressed.

# FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AL | Albania                  | ES | Spain               | LS | Lesotho               | SI | Slovenia                 |

|----|--------------------------|----|---------------------|----|-----------------------|----|--------------------------|

| AM | Armenia                  | FI | Finland             | LT | Lithuania             | SK | Slovakia                 |

| ΑT | Austria                  | FR | France              | LU | Luxembourg            | SN | Senegal                  |

| AU | Australia                | GA | Gabon               | LV | Latvia                | SZ | Swaziland                |

| ΑZ | Azerbaijan               | GB | United Kingdom      | MC | Monaco                | TD | Chad                     |

| BA | Bosnia and Herzegovina   | GE | Georgia             | MD | Republic of Moldova   | TG | Togo                     |

| BB | Barbados                 | GH | Ghana               | MG | Madagascar            | TJ | Tajikistan               |

| BE | Belgium                  | GN | Guinea              | MK |                       |    | Turkmenistan             |

| BF | Burkina Faso             | GR | Greece              |    | Republic of Macedonia | TR | Turkey                   |

| BG | Bulgaria                 | HU | Hungary             | ML | Mali                  | TT | Trinidad and Tobago      |

| BJ | Benin                    | IE | Ireland             | MN | Mongolia              | UA | Ukraine                  |

| BR | Brazil                   | IL | Israel              | MR | Mauritania            | UG | Uganda                   |

| BY | Belarus                  | IS | Iceland             | MW | Malawi                | US | United States of America |

| CA | Canada                   | IT | Italy               | MX | Mexico                | UZ | Uzbekistan               |

| CF | Central African Republic | JP | Japan               | NE | Niger                 | VN | Viet Nam                 |

| CG | Congo                    | KE | Kenya               | NL | Netherlands           | YU | Yugoslavia               |

| CH | Switzerland              | KG | Kyrgyzstan          | NO | Norway                | ZW | Zimbabwe                 |

| CI | Côte d'Ivoire            | KP | Democratic People's | NZ | New Zealand           |    |                          |

| CM | Cameroon                 |    | Republic of Korea   | PL | Poland                |    |                          |

| CN | China                    | KR | Republic of Korea   | PT | Portugal              |    |                          |

| CU | Cuba                     | KZ | Kazakstan           | RO | Romania               |    |                          |

| CZ | Czech Republic           | LC | Saint Lucia         | RU | Russian Federation    |    |                          |

| DE | Germany                  | LI | Liechtenstein       | SD | Sudan                 |    |                          |

| DK | Denmark                  | LK | Sri Lanka           | SE | Sweden                |    |                          |

| EE | Estonia                  | LR | Liberia             | SG | Singapore             |    |                          |

|    |                          |    |                     |    |                       |    |                          |

|    |                          |    |                     |    |                       |    |                          |

#### KEYPAD SCANNING WITH FEW PINS

#### TECHNICAL FIELD

This invention relates to sensing keys on a keypad and, more particularly, a method and apparatus for scanning a keypad or a keyboard using fewer pins than do current techniques.

5

10

15

20

25

30

35

### **BACKGROUND ART**

Keyboards and keypads are commonly associated with computing devices. However, they find application in a large variety of non-computing machines, as well. Exemplary, non-computing machines employing keypads include telephones, microwave ovens, and remote control units for consumer electronics. The array of machines employing keyboards and keypads is extensive and diverse, and ranges well beyond the computing machines with which they are commonly associated.

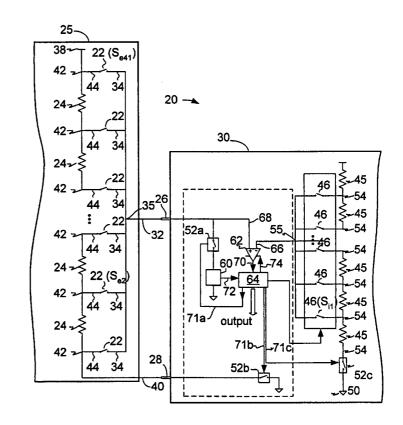

Virtually all these machines, both the computing and the non-computing, employ the same technique for determining when and which keys have been pushed. Figure 1 depicts one implementation of this technique. Typically a switch matrix 10 is constructed, and the key switches 12 are placed at the intersections of rows 14 and columns 16. Each key switch 12 is a key and the switch matrix is the keyboard or keypad. Each key switch 12 is normally open, *i.e.*, the key is not pushed, until it is closed when it is depressed, *i.e.*, the key is pushed or pressed.

The machine associated with the switch matrix 10 determines whether a key has been pushed by "interrogating" the keys. The interrogation is typically conducted by an integrated circuit (not shown) that frequently, though not always, is programmable. The switch matrix 10 communicates with the integrated circuit through the integrated circuit's pins. Pins are the typical interface between the internal circuitry of the integrated circuit and the circuitry with which the integrated circuit must interface. For instance, the integrated circuit's circuitry must be powered, and the power is provided externally from a power supply that transmits a power signal to the integral circuitry through one of the integrated circuit's pins.

Returning to Figure 1, the keys 12 are interrogated by sending words, *i.e.*, groups of digital 1s and 0s, to writable and readable registers (not shown) that control the integrated circuit's pins (not shown). For example, the integrated circuit might write all 0s to the outputs of the rows 14 and read the inputs from the columns 16. If they are all high, *i.e.*, a digital 1, no key is pushed. If any one is low, *i.e.*, a digital 0, then at least one key is pushed. Often, some kind of protection is given in case more than one key is pushed at the same time. That could result in a conflict on a column, if one row is driving low and a different row is driving high, and both rows are connected to a certain column. In the implementation of Figure 1, the drive to high is made resistive, so that excessive current will not flow.

This prior art key sensing scheme is effective at finding which key is pushed. However, it requires the integrated circuit to dedicate a number of pins on the order of  $(2X \text{ (square\_root } N))$ , where N is the number of keys, solely for the purpose of determining whether a key has been pushed and identifying which key it is. The pin count is important because each pin costs money. If the integrated circuit is assembled into a package, usually the package cost goes up with the number of pins. An increased number of pins also increases design difficulty for an integrated circuit, which raises the cost of the integrated circuit when it is produced. Even if the integrated circuit is not packaged, each pin requires drivers and protection devices on the silicon, which take up die area, and also costs money.

Thus, there is a need for a new technique for determining whether a key on a keypad or a keyboard has been pushed and for identifying that key. The present invention is directed to resolving one or all of the problems mentioned above.

## **DISCLOSURE OF INVENTION**

5

10

15

20

25

30

35

40

The invention is, in its various aspects, an apparatus and a method for scanning a keypad or a keyboard. The apparatus comprises a keypad and an integrated circuit. The keypad includes a plurality of chained resistors and a plurality of key switches. Each of the plurality of key switches is tied to a common node at a first terminal thereof and tapping the chained resistors at a second node thereof. Each of the key switches generates a signal indicative of the respective key switch being pressed when the key switch is pressed. The integrated circuit is capable of receiving the generated signal. The integrated circuit furthermore includes an analog to digital converter capable of generating a reference signal and a circuit capable of determining which key switch has been pressed from the magnitude of the generated voltage signal and the reference signal. The method for scanning a keypad generating a voltage signal whose magnitude indicates which key is being pressed, and determining from the magnitude of the generated voltage signal which key was pressed.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

The invention may be understood by reference to the following description taken in conjunction with the accompanying drawings, in which like reference numerals identify like elements, and in which:

Figure 1 illustrates a conventional approach to scanning a keyboard or keypad to determine whether and key has been pushed and, if so, determining which one;

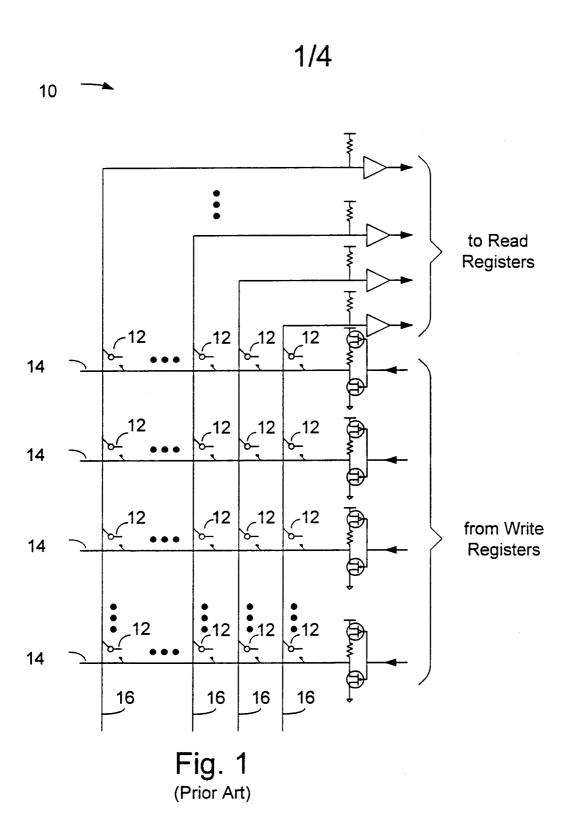

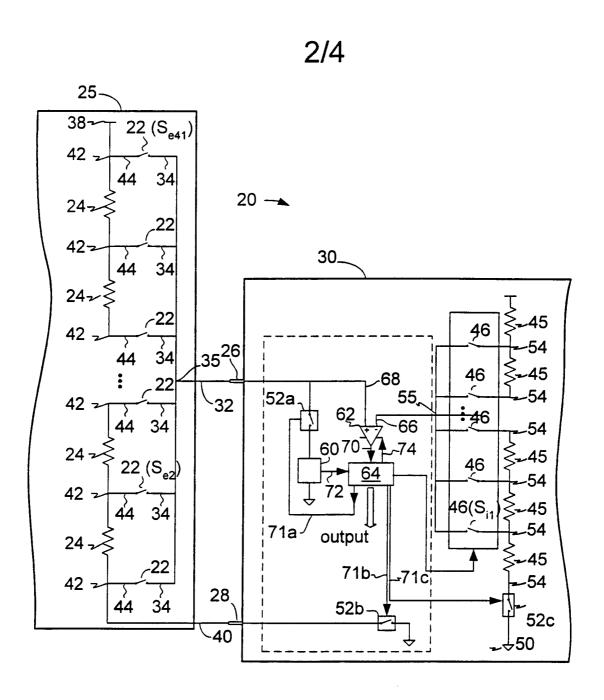

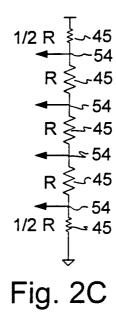

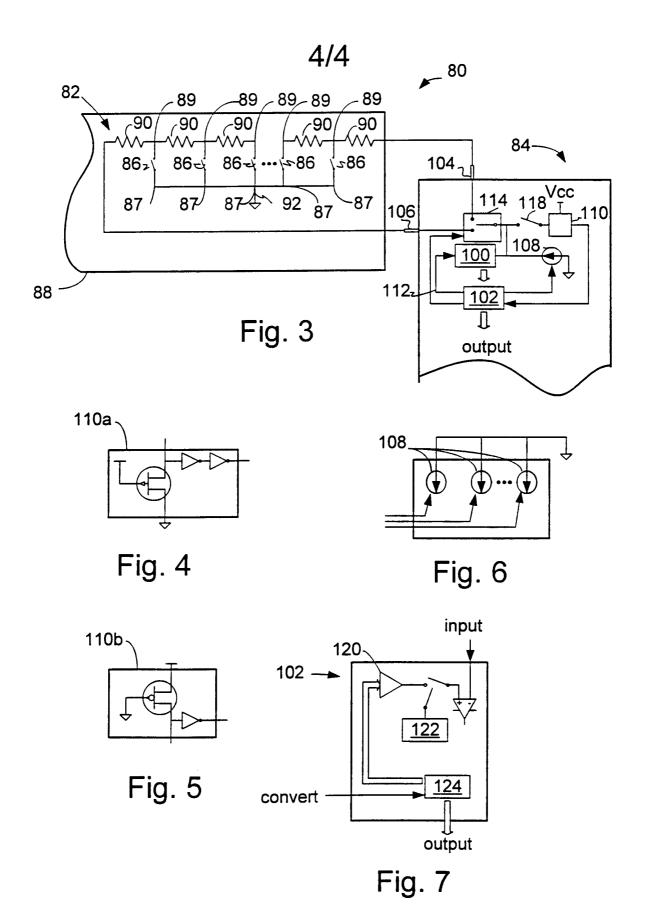

Figures 2A-2C illustrate a first particular implementation of an apparatus constructed and operated in accordance with the present invention;

Figure 3 illustrates a second particular implementation of an apparatus constructed and operated in accordance with the present invention;

Figure 4 illustrates one particular embodiment of a current sensor employed in the embodiment of Figures 2A-2C; and

Figures 5-7 illustrate particular implementations for various elements in the second embodiment of Figure 3.

While the invention is susceptible to various modifications and alternative forms, specific embodiments thereof have been shown by way of example in the drawings and are herein described in detail. It should be understood, however, that the description herein of specific embodiments is not intended to limit the invention to the particular forms disclosed.

## MODE(S) FOR CARRYING OUT THE INVENTION

Illustrative embodiments of the invention are described below. In the interest of clarity, not all features of an actual implementation are described in this specification. It will of course be appreciated that in the development of any such actual embodiment, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with system-related and business-related constraints, which will vary from one implementation to another. Moreover, it will be appreciated that such a development effort, even if complex and time-consuming, would be a routine undertaking for those of ordinary skill in the art having the benefit of this disclosure.

The invention manifests itself in at least two aspects. In a first aspect, the invention is an apparatus, comprising a keypad and an integrated circuit. The keypad includes a plurality of chained, passive components.

typically resistors. However, the invention is not so limited, as other types of passive components, such as capacitors and inductors may be employed. The keypad also includes a plurality of key switches. Each of the plurality of key switches is tied to a common node at a first terminal thereof and taps the chained passive components at a second node thereof, each of the key switches generating a signal indicative of the respective key switch being pressed when the key switch is pressed. The integrated circuit is capable of receiving the signal generated by the keypad and includes an analog to digital ("A/D") converter and a circuit. The A/D converter is capable of generating a reference signal. The circuit is capable of determining which key switch has been pressed from the magnitude of the generated voltage signal and the reference signal. In a second aspect, the invention is a method for scanning a keypad. The method generally comprises generating a voltage signal whose magnitude indicates which key is being pressed and determining from the magnitude of the generated voltage signal which key was pressed.

Both aspects of the invention admit to wide variation. To engender a fuller understanding and appreciation of the invention, two embodiments embodying both these aspects are disclosed. The first embodiment 20 is illustrated in Figures 2A-2C. The second embodiment 80 is illustrated in Figures 3-7. Each shall be discussed in turn.

10

15

20

25

30

35

40

Figure 2A illustrates a particular embodiment 20 of the present invention in which it may be determined how many and which of the key switches 22 of the keyboard or keypad 25 are pressed using only two pins 26 and 28 of the integrated circuit ("IC") 30. Technically, there may be some difference between a keypad and a keyboard. A keypad usually has numeric keys whereas a keyboard usually employs alpha-numeric keys. Keyboards also typically include a keypad. Thus, the principal differences between a keypad and a keyboard are the number and the type of keys. These differences, however, are immaterial to the present invention. Henceforth, the term "keypad" will be used to generically encompass both keyboards and keypads in this disclosure.

The implementation 20 of Figure 2A employs only the two pins 26 and 28 of the IC 30 for a relatively large number N of key switches 22 on the keypad 25. In some variations of this embodiment, only a single pin is necessary as is described below. The number N of key switches 22 is implementation specific. In one particular embodiment of the implementation 20, the number of keys is 41, but the number N of key switches 22 may exceed 100 in alternative embodiments if desired. Hereafter, the number of keys shall be referred to as N. For the sake of clarity. Figure 2A only depicts six key switches 22, but it is to be understood that the invention is not so limited.

Referring more particularly now to Figure 2A, the keypad 25, includes a plurality of N key switches 22 and a plurality of N-1 resistors 24. Each of the N key switches 22 is tied to a first voltage line 32 at a first terminal 34 thereof at a common node 35. The plurality of N-1 resistors 24 are configured in series across a first known electrical potential defined by a first high voltage 38 and a second voltage line 40. In one particular embodiment, each of the resistors 24 is rated for the same resistance. Note that the first voltage line 35 is electrically connected to the pin 26 and the second voltage line 40 is electrically connected to the pin 28 of the IC 30. Although other embodiments might utilize more pins on IC 30, the particular embodiment of the implementation illustrated in Figure 2A employs only two. This is significant improvement over the number that would be required under the conventional approach illustrated in Figure 1 and discussed above.

Returning to Figure 2A, each of the resistors 24 has a tap point 42 on either side thereof. Each tap point 42 is electrically connected to a second terminal 44 of a respective one of the N key switches 22. The N-1 resistors 24 may therefore be said to comprise a "resistor divider chain" divided by the key switches 22 at the tap points 42.

The integrated circuit 30 includes a plurality of N resistors 45. The N resistors 45 are connected in series across a second known electrical potential defined by a second high voltage 48 and a low voltage 50, which in the particular embodiment illustrated is ground. Each pair of the plurality of N resistors defines a tap point 54 therebetween. The IC 30 also includes a second plurality of N switches 46, a first terminal of each one of the N switches 46 is electrically connected to a respective tap point 54 defined by the plurality of N resistors 45.

The IC 30 furthermore comprises a first control switch 52a, a second control switch 52b, a third control switch 52c, a current sensor 60, a comparison circuit 62, and a control circuit 64. The first control switch 52a is electrically connected to the first voltage line 32 at one terminal thereof. The second control switch 52b is electrically connected to the second voltage line 40 at one terminal thereof and to the low voltage 50 at a second terminal thereof. The current sensor 60 is electrically connected to a second terminal of the first control switch 52a and is capable of sensing a current generated when the first control switch 52a is closed and outputting a first data signal indicative thereof. Figure 4 illustrates one particular embodiment 60a for the current sensor 60. In Figure 4, a very high resistance n-channel, field effect transistor ("nFET"), when any current flows through it, will produce a voltage drop big enough to cross the trip point of the inverter. The third control switch 52c connects the chained resistors 45 to ground when closed. Note that the control switches 52a-c are optional and might not be employed in all embodiments.

10

15

20

25

30

35

40

The comparison circuit 62 includes a first input 66 electrically connected to a second terminal of each one of the second plurality of N switches 46 through the common node 55 and a second input 68 electrically connected to the first voltage line 32. The comparison circuit 62 is capable of outputting a second data signal responsive to the comparison of a first input signal and a second input signal. Finally, the control circuit 64 is capable of receiving the first and second data signals and outputting, responsive thereto, a signal indicating which key switch has been pressed. Also responsive to the first and second data signals, the control circuit 64, in the particular embodiment illustrated, is capable of generating: control signals to operate the second plurality of N switches 46 and the control switches 52a-c on the respective lines 71a-c. In embodiments omitting the control switches 52a-c, the control circuit 64 may omit the capability for generating control signals for the control switches 52a-c.

In one particular embodiment, there are N-I equal valued resistors 24 on the keypad 25 in a chain from  $V_{cc}$  (the voltage 38) to  $V_{fg}$  (the voltage on the voltage line 40),  $V_{fg}$  also being a chip pin 28. The key switches 22 are connected to tap points 42 in this divider chain and are connected at the other end to the common node  $V_s$  (node 35),  $V_s$  being the pin 26 to the IC 30. Internal to the IC 30, there is a second resistor divider chain comprised of the equivalent of N equal valued resistors 45. The second resistor chain is tapped differently from the first resistor chain. The N-I internal switches 46 connect the taps 54 to the common node  $V_s$  (the node 55).

The common node  $V_i$  (common node 55) is connected to one input 66 of the voltage comparator 62 and the common node  $V_i$  (node 35) is connected to a second input 68 of the voltage comparator 62. The output 70 of the voltage comparator 62 indicates whether the board voltage  $V_i$  is higher than the internal voltage  $V_i$ . This output 70 is connected to a block of logic 64 that controls all the internal switches 46, as well as the control switches 52a, 52b and 52c. The control switch 52b conditionally connects the node  $V_i$  (node 35) to the current sensor 60. When current flows in the current sensor 60, a logical 1 is transmitted to the logic block 64 on its input line 72, indicating that a key switch 22 has been pushed.

The particular implementation 20 Figure 2A includes optional control switches 52a-c that provide control over power consumption. For instance, the control switch 52a, when closed, connects the resistors 45 to ground and, when open, disconnects the resistors 45 from ground. These control switches 52a-c may be omitted in some

embodiments. Each of the switches 52a-c is controlled, in the particular embodiment illustrated, by the block of logic 64 as described further below. In embodiments omitting the control switch 52b, the resistor chain in the keypad 25 may be directly grounded, thereby eliminating the need for the second pin 28.

Operation begins with the control switch 52b open, so that no current flows in the resistor string. The control switch 52a is set to 1, to connect the current sensor to  $V_0$ . The control switch 52c is set to 0, so that the internal resistor chain is disconnected from ground. Finally, enable line 74 is set to 0 so that the comparator is off and dissipates no power. In this initial condition, no current flows, so no power dissipates until a key switch 22 is pushed.

5

10

15

20

25

30

35

40

When a key switch 22 is pushed, current flows in the current sensor 60, and the "key pushed" input on line 72 changes to 1. Assume the key switch 22, also labeled as  $S_{e2}$ , was pressed, for instance. The logic block 64 then begins following sequence. The control switch 52b closes, so that ground is connected to the bottom of the resistor string on the board and current flows through the resistors 24. The third control switch 52c is then closed, so that current flows in the internal resistor string comprised of the resistors 45. The signal on the line 74 is set to 1, thereby enabling the comparator 62. The control switch 52a is then opened, removing the path through the current sensor 60.

The first switch 46, also labeled  $S_{i1}$ , is closed, thereby connecting the lowest voltage tap of the internal string onto the comparator 62's input 66. If the comparator 62 outputs a 1 on the line 70, the voltage generated by the keypad 25 is higher than that generated by the internal resistor chain on the line 66. This indicates that the pushed key switch 22 has not yet been identified. The process then tests the next switch 46, *i.e.*, opens the first switch 46 and closes the second switch 46, also labeled  $S_{i2}$ , and again examines the state of the comparator 62's output 70. In the case of  $S_{e2}$  assumed above, on closing the second switch 46, the comparator 62's output 70 will go low, because now the voltage on the line 68 is lower than the voltage on the line 66. Because it was second switch 46 that caused this, it can be deduced that  $S_{e2}$  was the key switch 22 pressed on the keypad 25.

If a different key switch 22 was pressed, the process continues closing the switches 46 one at a time while monitoring the comparator 62's output 70. Eventually, the output 70 would go low, and the number of the switch 46 that caused that will be the number of the key switch 22 that is closed. There is an exception in the case of the last, or highest key switch 22, also labeled  $S_{e41}$ , is pushed. In that case, even after closing each switch 46, the output 70 will still be high, whereupon it can be deduced that the remaining switch  $S_{e41}$  was pressed.

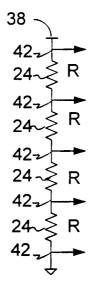

Figures 2B and 2C show how to choose the taps on the internal resistor string of resistors 45. The examples in Figures 2B-2C show an external string of only four resistors 24, 45, respectively, for the sake of clarity. Larger numbers like 40 or 60 are easily feasible, and the limit is determined by how fine of voltages the voltage comparator can discern, and by what tolerance of resistor matching can be achieved on external and internal resistors 24, 45, respectively. In this particular embodiment, each of the resistors 24 has the same value (i.e., R), although the invention is not so limited. The voltages on the internal string are selected to be midway between the voltages possible on the external taps. This is accomplished when the resistors 45 at the top and bottom ends of the internal string are half the value (i.e., R) of those in the middle of the string (i.e., R). This sets the voltages midway between the external voltages, for reliable sensing, and diminishes the requirements on the comparator. The technique can also be scaled down as needed.

The present invention offers numerous advantages over conventional techniques. Besides the previously stated advantage of using only one or two chip pins, this technique has an advantage regarding key resistance. Many keypads use cheap key switches. Cheap key switches used often develop significant resistance of their own

over their lifetime, and the closed key switch can present as much as 1-2 K $\Omega$ s resistance. Because of the high input impedance of the comparator 62, this embodiment is insensitive to this key switch resistance, and can yield the correct answer even if the resistance is over 100 K $\Omega$ s.

This embodiment also performs well relative to power dissipation. No power dissipates until a key switch 22 is pushed, and then the dissipation is dominated by the resistor string. For instance, if an individual resistor 24 is 5 K $\Omega$ s, a string of forty resistors 24 is 200 K $\Omega$ s, and the implementation 20 draws 15  $\mu$ A from a 3V supply. Higher values are possible, limited only by the leakage current on the keypad 25.

Precautions may be taken to correctly identify the pressed key where more than one key switch 22 is accidentally pressed. If the key switches 22 are positioned close together, the implementation 20 may report correctly about only one of them. If the key switches 22 are separated, the implementation 20 may report incorrectly because the resultant voltage might look like a different key switch 22. One approach to this dilemma interrogates after a key switch 22 is detected and does not accept any new information until all of the key switches 22 have been released for some predetermined time. This approach often works because usually the second key switch 22 is pushed later, as the finger rolls a bit off of its intended target. Another approach arranges the resistor string on the keypad 25, so that the key switches 25 that are likely to be pushed together are adjacent on the resistor string 27. When the two resistors 24 associated with the pushed key switches 22 are adjacent to each other, one of the key switches 22 will be detected correctly.

10

15

20

25

30

35

40

Figure 3 illustrates a second embodiment 80 of the present invention. The implementation 80 of Figure 3 is, in some respects, more complicated than the implementation 20 of Figure 2 in that it employs more elements and current sources. However, the additional complexity allows some embodiments to determine which key switch has been pressed with only a single pin. In the embodiment 80 illustrated, however, a redundant determination of which key switch 86 has been pressed is made, thus utilizing a second pin 106. If the redundant check is omitted, the determination can be made with only the single pin 104, as is discussed more fully below.

This approach ties the ends of the resistor string 82 to the IC 84's pins 104 and 106, the common side of the key switches 86 being grounded. The embodiment 80 includes a keypad 88. The keypad 88 comprises a plurality of chained resistors 90 in series across a known electrical potential and a plurality of key switches 86. Each of the key switches 86 is tied to a common node 92 at a first terminal 87 thereof and tap the chained resistors 90 at a second node 89 thereof. Each of the key switches 86 generates a signal indicative of the respective key switch 86 being pressed when the key switch 86 is pressed. In the particular variation of the embodiment 80 illustrated in Figure 3, two signals are actually generated, one each on the lines 98a-b as discussed more fully below. The IC 84 is capable of receiving the signal(s) generated by the key switches 86 of the keypad 88. The IC 84 includes an analog to digital converter 100 capable of generating a reference signal and a circuit 102 capable of determining which key switch 86 has been pressed from the magnitude of the generated voltage signal and the reference signal.

More particularly, the keypad 88 includes a first plurality of N key switches 86, each of the first plurality of N key switches 86 tied to a low voltage at a first terminal thereof. The keypad 88 also includes a plurality of N+1 resistors 90 in series between a first pin 104 and a second pin 106. Each pair of the plurality of N+1 resistors 90 defines a tap point therebetween and each tap point is electrically connected to a second terminal of a respective one of the first plurality of N key switches 86. The IC 84 includes the A/D converter 100, the logic circuit 102, a current source 108, and a current sensor 110.

In operation, the switch 114 is initially closed to the pin 104 and the switch 118 is closed. When a key switch 86 closes, the current sensor 110 detects a current flowing from  $V_{\rm c}$ . This signal is sent to the logic circuit 102, which then disconnects the current sensor 110 from  $V_{\rm cc}$ , and turns on the current source 108. The A/D converter 100 converts the voltage on the pin 104 to a digital word in response to a "convert" command from the logic circuit 102 on the line 112. The digital word corresponds to the measured resistance in the resistor string 82, from the pin 104 to ground ( $R_{PI}$ ). This resistance  $R_{PI}$  indicates which key switch 86 was pressed.

In one particular embodiment, a check is performed on the determination of which key switch 86 was pressed. In this embodiment, the logic circuit 102 closes the switch 114 to the pin 106. The procedure described immediately above is repeated to find the resistance from the pin 106 to ground  $(R_{P2})$ . This resistance also implies which key switch 86 was pressed, and is independent from the  $R_{P1}$  measurement. Both measurements should find the same key switch down. Otherwise, more than one key switch 86 has been pushed. Put another way, the sum of  $R_{P1}$  and  $R_{P2}$  should equal the total resistance of the string 82, or more than one key switch 86 has been pressed. When more than one key switch 86 has been pressed, the logic circuit 102 can inhibit reporting, until it sees only one key switch 86 is pressed. Note, however, that embodiments omitting this check can also omit the pin 106, such that some embodiments can determine which key switch 86 is pressed using only a single pin.

10

15

20

25

30

The A/D converter 100, logic circuit 102, current source 108, and current sensor 110 may be any design known to the art suitable for this application. An exemplary embodiment 110a of the current sensor 110 is illustrated in Figure 5. Figure 5 illustrates one particular embodiment 110a of the current sensor 110. Figure 7 illustrates one implementation of the A/D converter 102, including a digital to analog converter 120, a fixed voltage reference 122, and some successive approximation logic 124. Designs for these elements are well known in the art, and the suitability of various alternatives will become apparent to those skilled in the art having the benefit of this disclosure.

Some alternative embodiments may choose to use multiple current sources 108, and turn them on with control signals as shown in Figure 6. This technique can help with the otherwise large range of voltages some embodiment may need to convert. The more different currents an implementation uses, the fewer the voltages that need to be produced by the A/D converter 100 needs to produce. Typically, most embodiments employ at least two, and probably several, current sources 108.

The particular embodiments disclosed above are illustrative only, as the invention may be modified and practiced in different but equivalent manners apparent to those skilled in the art having the benefit of the teachings herein. Furthermore, no limitations are intended to the details of construction or design herein shown, other than as described in the claims below. It is therefore evident that the particular embodiments disclosed above may be altered or modified to create still other alternative embodiments. Accordingly, the protection sought herein is as set forth in the claims below.

#### **CLAIMS**

1. An apparatus, characterized in that:

a keypad includes:

5

10

15

20

25

30

a plurality of chained, passive components in series across a known electrical potential; and

a plurality of key switches, each of the plurality of key switches tied to a common node at a first terminal thereof and tapping the chained passive components at a second node thereof, each of the key switches generating a signal indicative of the respective key switch being pressed when the key switch is pressed; and

an integrated circuit capable of receiving the generated signal includes:

an analog to digital converter capable of generating a reference signal; and

a circuit capable of determining which key switch has been pressed from the magnitude of the generated signal and the reference signal and capable of outputting a signal indicating which key switch has been pressed.

2. The apparatus of claim 1, wherein:

the first plurality of key switches, includes N key switches and the common node is tied to a first voltage line; and

the plurality of chained, passive components includes N-1 passive components, each of the plurality of N-1 passive components having a tap point on either side thereof, each tap point being electrically connected to a second terminal of a respective one of the N key switches.

3. The apparatus of claim 1, wherein:

the plurality of key switches includes N key switches, each of the N key switches being tied to a first voltage at the first terminal thereof through the common node; and

the plurality of chained, passive components includes N+1 passive components, each pair of the N+1 passive components defining a tap point therebetween, each tap point being electrically connected to a second terminal of a respective one of the of N key switches.

4. The apparatus of claim 1, wherein:

the analog to digital converter includes:

a plurality of N+1 passive components in series across a second known electrical potential, each pair of the N+1 passive components defining a tap point therebetween; and

a second plurality of N key switches, a first terminal of each one of the second plurality of N key switches being electrically connected to a respective tap point defined by the plurality of N+I passive components at a first terminal thereof and being connected to a second common node; and

the circuit capable of determining which key switch has been pressed is further capable of generating a control signal controlling the operation of the second plurality of N key switches.

40

| 6.  | The apparatus of claim 1, wherein:            |

|-----|-----------------------------------------------|

| the | analog to digital converter further includes: |

5

10

15

20

25

30

35

- a current sensor electrically connected to the common node, the current sensor being capable of sensing a current generated when one of the key switches is closed and outputting a first data signal indicative thereof:

- a comparison circuit, including a first input tied to a second terminal of each one of the second plurality of N key switches and a second input electrically connected to the first voltage line, the comparison circuit being capable of outputting a second data signal responsive to the comparison of the first input and the second input; and

the control circuit is further capable of receiving the first and second data signals and capable of, in response thereto, generates the indication of which key switch has been pressed.

- 7. A method for scanning a keypad, the method comprising: generating a voltage signal whose magnitude indicates which key is being pressed; and determining from the magnitude of the generated voltage signal which key was pressed.

- 8. The method of claim 7, wherein determining from the magnitude of the generated voltage signal which key was pressed includes comparing the generated voltage signal to a reference voltage signal of variable magnitude.

- 9. The method of claim 8, further comprising varying the magnitude of the reference voltage signal as the reference voltage signal is compared to the generated voltage signal.

- 10. The method of claim 9, wherein the magnitude is varied by operating a plurality of switches.

- 11. The method of claim 7, wherein determining from the magnitude of the generated voltage signal which key was pressed includes converting the generated voltage signal to a digital representation indicative of the key being pressed.

- 12. The method of claim 11, wherein the method further comprises:

generating a second voltage signal whose magnitude indicates which key is being pressed; and

determining from the magnitude of the second generated voltage signal which key was pressed.

- 13. The method of claim 12, wherein determining from the magnitude of the second generated voltage signal which key was pressed includes converting the second generated voltage signal to a second digital representation indicative of the key being pressed.

### **AMENDED CLAIMS**

[received by the International Bureau on 09 March 2000 (09.03.00); new claim 5 added; remaining claims unchanged (2 pages)]

5. The apparatus of claim 4, wherein:

the analog to digital converter further includes:

a current sensor electrically connected to the common node, the current sensor being capable of sensing a current generated when one of the key switches is closed and outputting a first data signal indicative thereof;

a comparison circuit, including a first input tied to a second terminal of each one of the second plurality of N key switches and a second input electrically connected to the first voltage line, the comparison circuit being capable of outputting a second data signal responsive to the comparison of the first input and the second input; and

the control circuit is further capable of receiving the first and second data signals and capable of, in response thereto, generates the indication of which key switch has been pressed.

15

20

25

30

35

10

5

6. The apparatus of claim 1, wherein:

the analog to digital converter further includes:

- a current sensor electrically connected to the common node, the current sensor being capable of sensing a current generated when one of the key switches is closed and outputting a first data signal indicative thereof;

- a comparison circuit, including a first input tied to a second terminal of each one of the second plurality of N key switches and a second input electrically connected to the first voltage line, the comparison circuit being capable of outputting a second data signal responsive to the comparison of the first input and the second input; and

the control circuit is further capable of receiving the first and second data signals and capable of, in response thereto, generates the indication of which key switch has been pressed.

- 7. A method for scanning a keypad, the method comprising: generating a voltage signal whose magnitude indicates which key is being pressed; and determining from the magnitude of the generated voltage signal which key was pressed.

- 8. The method of claim 7, wherein determining from the magnitude of the generated voltage signal which key was pressed includes comparing the generated voltage signal to a reference voltage signal of variable magnitude.

9. The method of claim 8, further comprising varying the magnitude of the reference voltage signal as the reference voltage signal is compared to the generated voltage signal.

10. The method of claim 9, wherein the magnitude is varied by operating a plurality of switches.

11. The method of claim 7, wherein determining from the magnitude of the generated voltage signal which key was pressed includes converting the generated voltage signal to a digital representation indicative of the key being pressed.

- 5 12. The method of claim 11, wherein the method further comprises: generating a second voltage signal whose magnitude indicates which key is being pressed; and determining from the magnitude of the second generated voltage signal which key was pressed.

- The method of claim 12, wherein determining from the magnitude of the second generated voltage signal which key was pressed includes converting the second generated voltage signal to a second digital representation indicative of the key being pressed.

# **Statement Under Article 19(1)**

The amendment does not add new matter in that the limitations in the new claim 5 are disclosed in Figure 2A and in the accompanying text at page 4, lines 6-25.

Fig. 2A

# 3/4

Fig. 2B

# INTERNATIONAL SEARCH REPORT

Inter. nal Application No PCT/US 99/24306

A. CLASSIFICATION OF SUBJECT MATTER IPC 7 H03M11/24

According to International Patent Classification (IPC) or to both national classification and IPC

### **B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols) IPC 7 H03M

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

| Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |

|------------|------------------------------------------------------------------------------------|-----------------------|

| X          | DE 43 28 663 C (GRUNDIG EMV) 9 June 1994 (1994-06-09) figure 1                     | 1,7,11,<br>12         |

| Y<br>A     | column 3, line 14 - line 47                                                        | 2,3<br>8              |

| Y          | EP 0 123 715 A (GRUNDIG EMV) 7 November 1984 (1984-11-07) page 1                   | 2                     |

| X          | US 5 521 575 A (PACK BOK H)<br>28 May 1996 (1996-05-28)<br>figure 3                | 7,11                  |

| Y          | column 2, line 26 -column 3, line 2<br>-/                                          | 3                     |

|            |                                                                                    |                       |

| Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Patent family members are listed in annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier document but published on or after the international filling date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention carnot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention carnot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.  "&" document member of the same patent family |

| Date of the actual completion of the international search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Date of mailing of the international search report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15 February 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22/02/2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Name and mailing address of the ISA  European Patent Office, P.B. 5818 Patentiaan 2  NL - 2280 HV Rijewijk  Tel. (+31-70) 340-2040, Tx. 31 651 epo ni,  Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer Ogor, M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# INTERNATIONAL SEARCH REPORT

Inte. xnel Application No PCT/US 99/24306

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                         |                       |                       |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| Category * Citation of document, with indication, where appropriate, of                                                                      | the relevant passages | Relevant to claim No. |

| X US 5 057 836 A (INABA HITOSHI<br>15 October 1991 (1991-10-15)<br>figures 1,3<br>column 2, line 17 - line 30<br>column 4, line 16 - line 25 |                       | 7-9,11                |

| A column 4, line 47 -column 5,                                                                                                               | line 19               | 1,10                  |

| X US 4 583 189 A (KOYAMA TSUNE)<br>15 April 1986 (1986-04-15)                                                                                | (UKI)                 | 7–9                   |

| A figures 1,2                                                                                                                                |                       | 1,4,6                 |

| E WO 99 62180 A (QUALCOMM INC)<br>2 December 1999 (1999-12-02)<br>the whole document                                                         |                       | 1,3,7,8,<br>11        |

| E EP 0 917 293 A (KONINKL PHIL) ELECTRONICS NV) 19 May 1999 ( the whole document                                                             | (PS<br>(1999–05–19)   | 7,11-13               |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

|                                                                                                                                              |                       |                       |

# INTERNATIONAL SEARCH REPORT

# information on patent family members

inter. Anal Application No PCT/US 99/24306

| Patent document cited in search report |         | t | Publication Patent family member(s) |                | Publication date |  |

|----------------------------------------|---------|---|-------------------------------------|----------------|------------------|--|

| DE                                     | 4328663 | С | 09-06-1994                          | DE 59408786 D  | 04-11-1999       |  |

|                                        |         |   |                                     | EP 0641086 A   | 01-03-1995       |  |

| EP                                     | 0123715 | Α | 07-11-1984                          | DE 3312153 A   | 04-10-1984       |  |

| US                                     | 5521575 | A | 28-05-1996                          | NONE           |                  |  |

| US                                     | 5057836 | Α | 15-10-1991                          | JP 1187622 A   | 27-07-1989       |  |

|                                        |         |   |                                     | JP 1904723 C   | 08-02-1995       |  |

|                                        |         |   |                                     | JP 6028020 B   | 13-04-1994       |  |

|                                        |         |   |                                     | DE 3901636 A   | 03-08-1989       |  |

|                                        |         |   |                                     | GB 2214339 A,B | 31-08-1989       |  |

|                                        |         |   |                                     | KR 9201960 B   | 07-03-1992       |  |

| US                                     | 4583189 | Α | 15-04-1986                          | JP 1379882 C   | 28-05-1987       |  |

|                                        |         |   |                                     | JP 58213330 A  | 12-12-1983       |  |

|                                        |         |   |                                     | JP 61050329 B  | 04-11-1986       |  |

|                                        |         |   |                                     | DE 3320524 A   | 29-12-1983       |  |

|                                        |         |   |                                     | FR 2528194 A   | 09-12-1983       |  |

|                                        |         |   |                                     | GB 2121577 A,B | 21-12-1983       |  |

| MO                                     | 9962180 | A | 02-12-1999                          | NONE           |                  |  |

| EP                                     | 0917293 | Α | 1 <del>9-</del> 05-1999             | CN 1217501 A   | 26-05-1999       |  |

|                                        |         |   |                                     | JP 11225198 A  | 17-08-1999       |  |