## (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

特表2005-501368 (P2005-501368A)

(43) 公表日 平成17年1月13日(2005.1.13)

(51) Int.C1.<sup>7</sup>

FI

テーマコード (参考)

G 1 1 C 16/02

G 1 1 C 17/00 G 1 1 C 17/00

5B125

612F

G 1 1 C 17/00 612C

#### 審査請求 有 予備審査請求 有 (全 86 頁)

(21) 出願番号 特願2003-522936 (P2003-522936) (86) (22) 出願日 平成14年8月23日 (2002.8.23) (85) 翻訳文提出日 平成16年2月23日 (2004.2.23) (86) 国際出願番号 PCT/US2002/027022 (87) 国際公開番号 W02003/019565 (87) 国際公開日 平成15年3月6日 (2003.3.6)

(31) 優先権主張番号 09/939,394

(32) 優先日 平成13年8月24日 (2001.8.24)

(33) 優先権主張国 米国(US) (71) 出願人 591020009

612B

マイクロン・テクノロジー・インコーポレ

イテッド

MICRON TECHNOLOGY, I

NCORPORATED

アメリカ合衆国アイダホ州、ボーイズ、エ

ス. フェデラル、ウェイ、8000

(74) 代理人 100077665

弁理士 千葉 剛宏

(74) 代理人 100116676

弁理士 宮寺 利幸

(72) 発明者 キース、ブレディー、エル.

アメリカ合衆国、カリフォルニア州 94 019、ハーフ ムーン ベイ、シルバー

アベニュー 688

最終頁に続く

(54) 【発明の名称】ブロック消去機能を有する不揮発性メモリ

## (57)【要約】

#### 【課題】

フラッシュメモリブロックの消去処理を実行する方法及 びその装置を開示する。

## 【解決手段】

一実施の形態においては、この方法は、メモリブロック における所定の割合のロウを消去するステップと、この 所定の割合の消去に使用される消去パルスの数を分析す るステップと、消去されないで残ったロウを消去するた めに、メモリブロックに対して追加して印加されるパル スの許容数を算出するステップとを含む。別の実施の形 態においては、フラッシュメモリデバイスは、メモリア レイと、コントローラと、レジスタとを含む。メモリア レイは、フラッシュメモリセルの複数のブロックを含む 。各ブロックにおけるメモリセルは、複数のロウに配列 される。コントローラは、メモリアレイに対するメモリ 処理の制御に使用され、レジスタは、コントローラに接 続され、メモリセルの各口ウの消去状態をトラックする

### 【特許請求の範囲】

## 【請求項1】

フラッシュメモリにおける処理を実行する方法において、

メモリブロックにおける所定の割合のロウを消去するステップと、

前記所定の割合の口ウの消去に使用される消去パルスの数を分析するステップと、

前記メモリブロックに印加することが可能な追加消去パルスの許容数を算出するステップとを含むことを特徴とするフラッシュメモリにおける処理を実行する方法。

## 【請求項2】

請求項1記載の方法において、さらに、

消去されなかったロウを消去するために、前記メモリプロックに対し、前記許容数の追加消去パルスを印加するステップを含むことを特徴とするフラッシュメモリにおける処理を実行する方法。

#### 【請求項3】

請求項2記載の方法において、さらに、

前記メモリブロックに対して後で行われる他のメモリ処理で使用するために、当該メモリ ブロックにおいて消去されていないロウをラベル付けするステップを含むことを特徴とす るフラッシュメモリにおける処理を実行する方法。

### 【請求項4】

請求項3記載の方法において、

前記他のメモリ処理にプログラミング処理及び読み出し処理が含まれることを特徴とする フラッシュメモリにおける処理を実行する方法。

#### 【請求項5】

フラッシュメモリのブロックを処理する方法において、

前記ブロックが、複数のロウに配列された複数のメモリセルを含み、

前記ブロックに対して少なくとも1つのパルスを印加するステップと、

各消去パルスの後、各口ウに関連付けられたメモリセルが消去されたかどうかを判定する ために各口ウをベリファイするステップと、

前記ブロックにおける所定数のロウが消去されているとベリファイされたときにブロック の消去を終了するステップとを含み、

前記ロウの前記所定数が前記ブロックにおけるロウの合計数よりも少ないことを特徴とするフラッシュメモリのブロックを処理する方法。

## 【請求項6】

請求項5記載の方法において、さらに、

前記ブロックに対して後で行われる他のメモリ処理で使用するために、消去されているとベリファイされなかったロウをラベル付けすることを特徴とするフラッシュメモリのブロックを処理する方法。

#### 【請求項7】

請求項5記載の方法において、

前記所定数のロウをベリファイするのに必要な第1の数のパルスをカウントするステップと、

消去されているとベリファイされていないロウの消去を試行するために前記ブロックに対して印加される第 2 の最大限の数のパルスを算出するステップとを含み、前記第 2 のパルスの数は、前記第 1 のパルスの数よりも少ないことを特徴とするフラッシュメモリのブロックを処理する方法。

#### 【請求項8】

請求項7記載の方法において、

前記第2のパルスの数に応答し、前記ブロックに対し、少なくとも1つの消去パルスを印加するステップと、

各消去パルスの後、各口ウに関連付けられたメモリセルが消去されたかどうかを判定する ために各口ウをベリファイするステップと、 10

20

30

40

前記ブロックにおける所定数のロウが消去されているとベリファイされたときにブロック の消去を終了するステップとを含むことを特徴とするフラッシュメモリのブロックを処理 する方法。

## 【請求項9】

請求項7記載の方法において、前記第2パルスの数は、N2=(A\*N1)+Bによって 算出され、N2は第2のパルスの数であり、N1は、第1のパルスの数であり、Aは、所 定の割合であり、Bは、最小のパルス数であることを特徴とするフラッシュメモリのブロックを処理する方法。

#### 【請求項10】

不揮発性メモリにおける処理を実行する方法において、

複数のロウに配列されたフラッシュメモリセルのブロックに対し、少なくとも 1 つの消去 パルスを印加するステップと、

消去パルスの後、ブロックにおける各口ウが消去されているかどうかをベリファイするステップと、

前記ブロックにおいて所定数のロウが消去されているかどうかをベリファイするために使 用される消去パルスの数をカウントするステップと、

消去されているとベリファイされていないロウの消去を試行するために前記ブロックに対して所定数の消去パルスを印加するステップとを含み、前記消去パルスの所定数は、前記所定数のロウをベリファイするのに使用される消去パルスの数よりも少ないことを特徴とする不揮発性メモリにおける処理を実行する方法。

## 【請求項11】

請求項10記載の方法において、さらに、

前記ブロックに関連付けられたレジスタにおけるメモリセルをプログラムし、消去されているとベリファイされたロウをトラックすることを特徴とする不揮発性メモリにおける処理を実行する方法。

## 【請求項12】

請求項10記載の方法において、さらに、

最初の消去パルスが印加される前に、前記ブロックにおける各メモリセルのプリチャ・ジを行うことを特徴とする不揮発性メモリにおける処理を実行する方法。

## 【請求項13】

請求項10記載の方法において、

前記ベリファイされたロウの前記所定数は、前記ブロックにおけるロウの過半数であることを特徴とする不揮発性メモリにおける処理を実行する方法。

## 【請求項14】

請求項10記載の方法において、前記ブロックに対して所定数の消去パルスが印加された後に消去されているとベリファイされないロウは、ブロックで後に行われるメモリ処理のために、消去されていないとラベル付けされることを特徴とする不揮発性メモリにおける処理を実行する方法。

### 【 請 求 項 1 5 】

不揮発性メモリにおける処理を実行する方法において、

前記 ブロックにおいて 複数 のロウに配列されたフラッシュメモリセルを所定のレベルにプ リチャージするステップと、

前記ブロックに対し、少なくとも1つの第1ステージの消去パルスを印加するステップと

前記ブロックに対して第1ステージの各消去パルスが印加された後、ロウ毎に各メモリセルが消去されたかどうかをベリファイするステップと、

消去されたブロックにおいて半数を超えるロウをベリファイするのに使用され、前記ブロックに対して印加される第1のパルスの数をカウントするステップと、

前記第1のパルスの数の割合として、消去されているとベリファイされていないロウの消去を試行するために前記ブロックに対して印加される第2のパルスの数を算出するステッ

10

20

30

40

プと、

前記ブロックに対し、少なくとも1つの第2ステージの消去パルスを印加するステップと

前記ブロックに対し第 2 ステージの各消去パルスが印加された後、ロウ毎に各メモリセル が消去されたかどうかをベリファイするステップと、

前記ブロックに対し、第2ステージの消去パルスが印加されたか、すべてのロウが消去されているとベリファイされたときに、前記ブロックの消去を終了するステップとを含むことを特徴とする不揮発性メモリにおける処理を実行する方法。

【請求項16】

請求項15記載の方法において、さらに、

ロウが消去されたとベリファイされたときに、当該ロウに関連付けられたレジスタにフラッグを立てることを特徴とする不揮発性メモリにおける処理を実行する方法。

【請求項17】

請求項15記載の方法において、さらに、

前記メモリブロックに対して他の処理を実行するために、消去されたとベリファイされた ロウをラベル付けすることを特徴とする不揮発性メモリにおける処理を実行する方法。

【請求項18】

請求項15記載の方法において、前記第2の数は、N2=(A\*N1)+Bによって算出され、N2は第2の消去パルスの数であり、N1は、第1の消去パルスの数であり、Aは、所定の割合であり、Bは、前記第2ステージにおいて印加される最小のパルス数であることを特徴とする不揮発性メモリにおける処理を実行する方法。

【請求項19】

複数の口ウに配列されたフラッシュメモリセルのブロックを複数含むメモリアレイと、

前記メモリアレイに対するメモリ処理を制御するコントローラと、

メモリセルの各ロウの消去状態をトラックするために前記コントローラに接続されたレジ スタとを含むことを特徴とするフラッシュメモリデバイス。

【請求項20】

請 求 項 1 9 記 載 の フ ラ ッ シ ュ メ モ リ デ バ イ ス に お い て 、 前 記 メ モ リ ア レ イ を 含 む ダ イ の 外 側 に 前 記 レ ジ ス タ が 設 け ら れ て い る こ と を 特 徴 と す る フ ラ ッ シ ュ メ モ リ デ バ イ ス 。

【請求項21】

請求項19記載のフラッシュメモリデバイスにおいて、前記メモリアレイを含むダイの内側に前記レジスタが設けられていることを特徴とするフラッシュメモリデバイス。

【請求項22】

請求項19記載のフラッシュメモリデバイスにおいて、前記レジスタが、

各ブロックに設けられるレジスタサブブロックを含み、

各サブブロックが、前記ブロック内のロウに関連付けられたトラッキング用メモリセルを 複数含み、

前記コントローラは、トラッキング用メモリセルが消去されているとベリファイされた際 に、トラッキングメモリセルをプログラムすることを特徴とするフラッシュメモリデバイ ス。

【請求項23】

請 求 項 2 2 記 載 の フ ラ ッ シ ュ メ モ リ デ バ イ ス に お い て 、 前 記 複 数 の ト ラ ッ キ ン グ メ モ リ セ ル が 揮 発 性 メ モ リ セ ル で あ る こ と を 特 徴 と す る フ ラ ッ シ ュ メ モ リ デ バ イ ス 。

【請求項24】

請 求 項 2 2 記 載 の フ ラ ッ シ ュ メ モ リ デ バ イ ス に お い て 、 前 記 複 数 の ト ラ ッ キ ン グ メ モ リ セ ル が 不 揮 発 性 メ モ リ セ ル で あ る こ と を 特 徴 と す る フ ラ ッ シ ュ メ モ リ デ バ イ ス 。

【請求項25】

請求項22記載のフラッシュメモリデバイスにおいて、前記コントローラは、消去処理の前に、前記トラッキングメモリセルのすべてを消去することを特徴とするフラッシュメモリデバイス。

10

20

30

40

#### 【請求項26】

複数の口ウに配列されたフラッシュメモリセルのブロックを複数含むメモリアレイと、

前記メモリアレイに対するメモリ処理を制御するコントローラと、

レジスタアレイとを含み、前記コントローラは、複数のブロックに配列されたメモリセルのロウが消去されたとベリファイされたことをトラックするために前記レジスタアレイに データを格納することを特徴とする不揮発性メモリデバイス。

#### 【請求項27】

請求項26記載の不揮発性メモリデバイスにおいて、前記レジスタアレイは、複数のレジスタメモリセルを含み、各レジスタメモリセルは、各メモリアレイにおけるメモリセルの各プロックにおけるメモリセルのロウに関連付けられていることを特徴とする不揮発性メモリデバイス。

【請求項28】

請求項26記載の不揮発性メモリデバイスにおいて、前記複数のメモリアレイが大容量記憶デバイスを構成することを特徴とする不揮発性メモリデバイス。

#### 【請求項29】

請求項26記載の不揮発性メモリデバイスにおいて、前記コントローラは、前記ブロックにおける所定数のロウを消去する際に、メモリセルのブロックに対して第1ステージの消去パルスを印加し、当該第1ステージにおいて、前記コントローラは、消去されるロウが所定数に達するのに必要なパルスの数をカウントすることを特徴とする不揮発性メモリデバイス。

【請求項30】

請求項29記載の不揮発性メモリデバイスにおいて、前記ロウの所定数は、消去されるブロックにおけるロウの半数を超えることを特徴とする不揮発性メモリデバイス。

#### 【請求項31】

請求項29記載の不揮発性メモリデバイスにおいて、前記コントローラは、消去しようとする前記プロックに対して第2ステージの消去パルスを印加し、前記第2ステージにおいて前記コントローラが使用する消去パルスの最大数は、前記第1ステージで使用される消去パルスの数よりも少ないことを特徴とする不揮発性メモリデバイス。

## 【請求項32】

請求項31記載の不揮発性メモリデバイスにおいて、前記第2ステージにおいて使用される消去パルスの数は、N2=(A\*N1)+Bによって判定され、N2は、前記第2ステージにおいて使用される消去パルスの最大数であり、N1は、第1ステージにおいて使用される消去パルスの数であり、Aは、所定の割合であり、Bは、第2ステージにおいて使用される消去パルスの最小の数であることを特徴とする不揮発性メモリデバイス。

### 【請求項33】

複数の口ウに配列されたフラッシュメモリセルのブロックを複数含むメモリアレイと、

前記メモリアレイに対するメモリ処理を制御する制御回路とを含み、

前記制御回路は、第1ステージにおいて消去されるブロックに対して第1の数の消去パルスを印加し、第2ステージにおいて前記ブロックに対して第2の数の消去パルスを印加し、前記第2ステージにおいて印加される消去パルスの前記第2の数は、前記プロックにおいて所定数のロウが消去されたことをベリファイするために前記第1ステージにおいて必要とされる消去パルスの数に基づくものであることを特徴とするフラッシュメモリデバイス。

## 【請求項34】

請求項33記載のフラッシュメモリデバイスにおいて、前記第2ステージにおいて印加される第2の消去パルスの数は、前記第1ステージにおいて印加される第1の消去パルスの数よりも少ないことを特徴とするフラッシュメモリデバイス。

## 【請求項35】

請求項33記載のフラッシュメモリデバイスにおいて、さらに、

前記制御回路に接続されたレジスタサブブロックを複数有するレジスタを含み、

20

10

30

40

各レジスタサブブロックは、メモリセルのブロックに関連付けられ、

各レジスタサブブロックは、メモリセルのブロックにおけるロウ毎にレジスタメモリセルを有することによって、制御回路が関連付けされたロウが消去されたことをベリファイされたかどうかを示すデータを格納することを特徴とするフラッシュメモリデバイス。

#### 【請求項36】

請求項35記載のフラッシュメモリデバイスにおいて、各レジスタメモリセルが不揮発性 メモリセルであることを特徴とするフラッシュメモリデバイス。

### 【請求項37】

請求項35記載のフラッシュメモリデバイスにおいて、各レジスタメモリセルが揮発性メ モリセルであることを特徴とするフラッシュメモリデバイス。

#### 【請求項38】

請求項33記載のフラッシュメモリデバイスにおいて、前記制御回路は、前記ブロックに対して後で行われる他のメモリ処理において、消去されたとベリファイされなかったロウを使用しないことを特徴とするフラッシュメモリデバイス。

#### 【請求項39】

請求項38記載のフラッシュメモリデバイスにおいて、他のメモリ処理がプログラミング 処理及び読み出し処理を含むことを特徴とするフラッシュメモリデバイス。

### 【請求項40】

外部消去コマンドを与えるためのプロセッサと、

複数のロウに配列されたフラッシュメモリセルの消去可能なブロックを複数含むメモリアレイと、

前記プロセッサから前記外部消去コマンドを受信し、前記複数のメモリアレイにおけるメ モリセルのブロックに対し、消去処理を実行するコントローラと、

消去されたとベリファイされるメモリセルのロウをトラックするために前記コントローラ に接続された複数のレジスタとを含み、

前記レジスタの各々は、前記メモリアレイの1つに関連付けられ、

前記レジスタの各々は、レジスタサブブロックを複数含み、

前記レジスタサブブロックの各々は、メモリセルのブロックに関連付けられ、

前記 レジス タサブブロック の各々 は、 メモリセルの関連付けられたブロックにおけるロウ 毎に、 レジスタメモリセルを有することを特徴とするフラッシュメモリシステム。

#### 【請求項41】

請求項40記載のフラッシュメモリシステムにおいて、前記コントローラは、関連付けされたロウが消去されているとベリファイされたかどうかを示すデータを前記レジスタメモリセルに格納することを特徴とするフラッシュメモリシステム。

## 【請求項42】

請求項 4 0 記載のフラッシュメモリシステムにおいて、各レジスタは、関連付けされたメ モリセルを含むダイの内側に設けられていることを特徴とするフラッシュメモリシステム

## 【請求項43】

請求項 4 0 記載のフラッシュメモリシステムにおいて、各レジスタは、関連付けされたメ モリセルを含むダイの外側に設けられていることを特徴とするフラッシュメモリシステム

### 【請求項44】

請求項40記載のフラッシュメモリシステムにおいて、前記コントローラは、第1ステージにおいて、前記ブロックにおけるメモリセルの所定数の口ウを消去するためにメモリセルのブロックに対し、第1の数の消去パルスを印加し、第2ステージにおいて、消去されたとベリファイされていない口ウの消去を試行するために、前記ブロックに対して最大限の第2の数の消去パルスを印加し、消去パルスの前記第2の数は、前記第1ステージにおいて印加される消去パルスの第1の数よりも少ないことを特徴とするフラッシュメモリシステム。

10

20

30

### 【請求項45】

請求項44記載のフラッシュメモリシステムにおいて、前記最大限の第2のパルス数が、N2=(A\*N1)+Bによって判定され、N2は、第2ステージにおいて印加される第2のパルスの最大数であり、N1は、第1ステージにおいて印加される消去パルスの第1の数であり、Aは、所定の割合であり、Bは、前記第1ステージにおいて消去されているとベリファイされなかったロウの消去を試行しようとして前記第2ステージにおいて使用される最大数のパルスであることを特徴とするフラッシュメモリシステム。

### 【請求項46】

請求項 4 4 記載のフラッシュメモリデバイスにおいて、メモリセルのロウの前記所定数は、前記ブロックにおけるロウの半数を超えることを特徴とするフラッシュメモリデバイス

10

【発明の詳細な説明】

#### 【技術分野】

[0001]

## 発明の技術分野

本発明は、主に、不揮発性メモリに関する。特に、本発明は、フラッシュメモリデバイスにおける消去処理に関する。

### 【背景技術】

[0002]

## 発明の背景

20

通常、メモリデバイスは、コンピュータの内部記憶領域として使用される。メモリには幾つかの種類がある。例えば、RAM(random-access memory)は、従来、コンピュータのメインメモリとして用いられている。RAMの多くは揮発性であり、コンテンツを記憶した状態を維持するためには、周期的に電気をリフレッシュする必要がある。また、フラッシュメモリは周期的に電気をリフレッシュする必要がある。また、フラッシュメモリには、カーシステムである。例えば、近年のコンピュータには、フラッシュメモリチップに基本的なエノの用途がある。例えば、近年のコンピュータには、フラッシュメモリチップに基本的が容易である。また、デジタルシステムの中には、従来の大容量デバイスの代わりにフラッシュメモリを使用することもある。

30

## [0003]

通常、フラッシュメモリは、メモリアレイを備え、このメモリアレイは、ロウアドレス及びカラムアドレスによって指定されるメモリセルのブロックを複数含む。メモリセルの各々には、フローティングゲートを有して電荷を保持する電界効果トランジスタが設けられる。これらのセルは、ブロック単位のグループに分けられる。各セルは、フローティングゲートに電荷を与えることによって、電気的に、ランダムにプログラムすることができる。電荷は、消去処理によって、フローティングゲートから抜き出される。フローティングゲートにおける電荷の有無によってセルのデータが決定する。

#### [0004]

40

フラッシュメモリの状態の読み出しやベリファイは、リファレンスセル電流を用いて行われる。つまり、リファレンス不揮発性メモリセルは、リファレンスビットラインを介してセンスアンプ回路に接続される。ビットライン間の差動電流を検出することによって、セルのプログラムされた状態を判定することができる。例えば、リファレンスセルを申間状態にプログラムし、このリファレンスセルが完全にプログラムされたメモリセルの約半分の電流を伝達するようにすることが考えられる。読み出されるセルがプログラムされている場合、このセルは、リファレンスメモリセルよりも多くの電流を伝達し、読み出されるセルが消去されている場合、このセルは、リファレンスセルよりも少ない電流を伝達する。

#### [0005]

メモリセルをプログラムするために、例えば、12ボルトの高い正の電圧がセルのコントロールゲートに印加される。さらに、ソース電圧及び基板電圧をグラウンドレベルにした状態で、ドレインに対し、6~9ボルトの中程度の正の電圧が印加される。これにより、メモリセルのドレイン領域近傍のチャンネル領域内への高温電子注入が発生する。これらの高エネルギー電子は、正の電圧を有するコントロールゲートに向かって移動し、フローティングゲート上に集まる。電子は、フローティングゲート上に留まるため、プログラムされていないセルと比較して、セルの実効しきい電圧が高くなっている。

#### 【発明の開示】

#### [0006]

フラッシュメモリにおいては、セルは、ブロック単位で消去される。これは、ブロックにおけるすべてのセルのコントロールゲートに接続された各ワード線に・10~・17ボルトの負の電圧を印加し、ブロックのソース接点を、所定の期間に渡って、例えば、5ボルト以上の電圧(供給電圧Vcc)にすることによって行われ、通常、単一のパルス、または、連続したパルスを印加することによって行われる。各パルスは、メモリ素子のファイングゲートから電子を除去するフィールドを形成する。セルを消去するスピードで、セルの消去に必要なパルスの数は、パルスの電圧レベル、パルス長、温度等、タスに依存する。フラッシュメモリブロック内に存在する個々のセルは、消去速度等が多場場である場合が多い。通常、すべてのセルの消去のレベルは、ブロック内において最も速度である場合が多い。通常のセルには、通常のメモリセルの消去に30パルス必要であるとすれば、通常のセルには、20の余分な消去パルスが印加されることになり、この余分な消去パルスによって過剰消去が発生する可能性がある。

#### [0007]

過剰消去されたセルとは、特定のポイントを超えて消去されたセルを意味する。過剰消去されたセルとは、「枯渇」するものである。つまり、フローティングゲートから電子が過度に除去されるため、フローティングゲートは、セルのしきい値よりも高い電圧を有する状態になる。従って、このセルは、コントロールゲートがグラウンド電位にある場合でも、オフにすることはできない。さらに、過剰消去されたセルが存在する場合、過剰消去セルが存在するカラムに接続されたメモリセルのすべてが消去されたセルとして読み出される可能性がある。メモリセルがプログラムされたものであったとしても、消去されたセルとして読み出されてしまうことがある。

#### [00008]

フラッシュメモリのブロックにおいて過剰消去されたセルの数を抑制するために、一般的に、消去処理は、プリプログラムサイクル、消去サイクル、さらに、ソフトプログラムサイクルにおいては、プロック内のすべてのセルは、所定のレベルを超えるようにプログラムされる。具体的には、プロック内におけるムされるのセルのフローティングゲートが概ね同一の量の電荷を保持するようにプログラムされる。次に、消去サイクルでは、ブロックに対して消去パルスを印加し、ロウ毎におせイクルは、すべてのセルが消去された状態であるかどうかを判別する。消去サイクルは、すべてのセルが消去された状態であるかどうでともある)では、オーターの各コラム(ビット線)をチェックし、過剰消去されたセルがビット線に接続されたセルのコントロールゲートに対し、電流が検出されなくないのように接続されたセルのコントロールゲートに対し、電流が検出されないでシスティマティックにソフトプログラムが実行される(ソフトプログラムパルスが印かされる)。

## [0009]

ソフトプログラムサイクルは、過剰消去されたセルを修復するために使用されるが、過剰 消去されたセルのなかには修復が不可能なものが存在するため、ソフトプログラムサイク 10

20

30

40

20

30

40

50

ルが実行される時点で過剰消去されたセルの数が少ないことが望ましい。また、過剰消去されたセルを修復した場合であっても、過剰消去が繰り返されるにつれて、セルの完全性が失われていく可能性がある。

#### [0010]

上述した理由、または以下に述べる理由により、フラッシュメモリの技術分野において、 ブロック内の他のセルに比べて消去スピードが遅いセルが少数存在するようなフラッシュ メモリのブロック消去方法を改良することが求められている。これらの理由は、当業者で あれば、明細書に記載された内容を理解することによって、明らかとなるであろう。

#### [0011]

#### 発明の要旨

上述した不揮発性メモリデバイスの問題及びその他の問題は、本発明によってその解決が図られ、以下の明細書の記載を検討することによって理解できるであろう。

## [0012]

一実施の形態においては、フラッシュメモリにおける処理を実行する方法が開示される。 この方法は、メモリブロックにおける所定の割合のロウを消去するステップと、前記所定 の割合のロウの消去に使用される消去パルスの数を分析するステップと、前記メモリブロックに印加することが可能な追加消去パルスの許容数を算出するステップとを含む。

#### [0013]

別の実施の形態においては、フラッシュメモリにおける処理を実行する方法が開示される。この方法において、ブロックは、複数の口ウに配列された複数のメモリセルを含み、前記ブロックに対して少なくとも 1 つのパルスを印加するステップと、各消去パルスの後、各口ウに関連付けられたメモリセルが消去されたかどうかを判定するために各口ウをベリファイするステップと、前記ブロックにおける所定数の口ウが消去されているとベリファイされたときにブロックの消去を終了するステップとを含み、前記口ウの前記所定数が前記ブロックにおける口ウの合計数よりも少ない。

#### [0014]

別の実施の形態においては、不揮発性メモリにおける処理を実行する方法が開示される。この方法は、複数の口ウに配列されたフラッシュメモリセルのブロックに対し、少なくとも1つの消去パルスを印加するステップと、消去パルスの後、ブロックにおいて所定数の口ウが消去されているかどうかをベリファイするために使用される消去パルスの数をカウントするステップと、消去されているとベリファイされていないロウの消去を試行するために前記ブロックに対して所定数の消去パルスを印加するステップとを含み、前記消去パルスの所定数は、前記所定数の口ウをベリファイするのに使用される消去パルスの数よりも少ない。

### [0015]

別の実施の形態においては、フラッシュメモリに対する消去処理を実行する方法が開示される。この方法は、前記プロックにおいて複数の口立に配列ったとも11つのの第1ステージの消去パルスを印加するステップと、前記プロックに対して第1ステージの消去パルスを印加するステップと、前記プロックに対して第1ステージのの名消去パルスが印加された後、ロウタにおいて半数を超えるロウをベリファイをするスプロックにおいて半数を超えるロウをベリファイをするプロックにおいて出ている数をカウントするストリカでにおいての別においている数をカウントするストリカでに対している第1のパルスの数を算出すること、前記プロックに対し、少なくとも1つの第2ステージの消去パルスを印加をに対した、前記プロックに対し、少なくとも1つの第3ステージの消去が印加されたかとうかをベリファイでの口ウが消去されたかどうかをベリファイでの口ウが消去されたかどうかをベリファイでの口ウが消去されたかに前記プロックに対し、すべての口ウが消去されているとベリファイを含む。

30

40

50

[0016]

別の実施の形態においては、フラッシュメモリデバイスは、メモリアレイと、コントローラと、レジスタとを含む。メモリアレイは、複数のロウに配列されたフラッシュメモリセルのブロックを複数含む。コントローラは、前記メモリアレイに対するメモリ処理を制御する。レジスタは、メモリセルの各ロウの消去状態をトラックするために前記コントローラに接続されている。

[ 0 0 1 7 ]

別の実施の形態においては、不揮発性メモリデバイスは、複数のメモリアレイと、コントローラと、レジスタアレイとを含む。各メモリアレイは、複数のロウに配列されたフラッシュメモリセルのブロックを複数含む。コントローラは、前記メモリアレイに対するメモリ処理を制御する。レジスタアレイとを含み、コントローラは、複数のブロックに配列されたメモリセルのロウが消去されたとベリファイされたことをトラックするために前記レジスタアレイにデータを格納する。

[0018]

別の実施の形態においては、フラッシュメモリシステムは、メモリアレイと、制御回路とを含む。メモリアレイは、複数のロウに配列されたフラッシュメモリセルのブロックを複数含む。制御回路は、前記メモリアレイに対するメモリ処理を制御する。具体的には、制御回路は、第1ステージにおいて消去されるブロックに対して第1の数の消去パルスを印加し、第2ステージにおいて前記ブロックに対して第2の数の消去パルスを印加し、前記第2ステージにおいて印加される消去パルスの前記第2の数は、前記ブロックにおいて所定数のロウが消去されたことをベリファイするために前記第1ステージにおいて必要とされる消去パルスの数に基づくものである。

[0019]

また、別の実施の形態においては、フラッシュメモリシステムは、プロセッサと、複数のメモリアレイと、コントローラと、複数のレジスタとを含む。プロセッサは、外部消去コマンドを与えるために使用される。各メモリアレイは、消去可能なブロックを複数含む。各ブロックにおけるメモリセルは、複数のロウに配列されたフラッシュメモリセルを含む。コントローラは、前記プロセッサから前記外部消去コマンドを受信する。さらに、コントローラは、前記複数のメモリアレイにおけるメモリセルのブロックに対し、消去処理を実行する。複数のレジスタは、消去されたとベリファイされるメモリセルのロウをトラックするために前記コントローラに接続されている。レジスタの各々は、前記メモリアレイの1つに関連付けられ、レジスタの各々は、レジスタサブブロックを複数含む。レジスタサブブロックの各々は、メモリセルのブロックに関連付けられている。さらに、レジスタサブブロックの各々は、メモリセルの関連付けられたブロックにおけるロウ毎に、レジスタメモリセルを有する。

【発明を実施するための最良の形態】

[0020]

発明の実施の形態

以下、好ましい実施の形態について添付の図面を参照して詳細に説明する。図面は、本願の明細書を構成するものであり、本発明の実施の好ましい実施の形態について具体的に例示している。これらの実施の形態は、当業者が発明を実施できるように充分に詳細に記載されているが、本発明の精神及び範囲を逸脱することなく、論理的、機械的、電気的な変更を施した他の実施の形態を採用することも可能であることが理解できよう。従って、以下の詳細な説明は、限定的なものであると解釈されるべきではない。本発明の範囲は、クレーム及びその均等物によってのみ規定される。

[ 0 0 2 1 ]

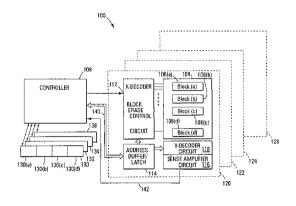

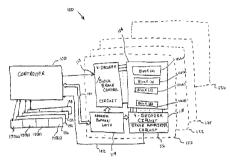

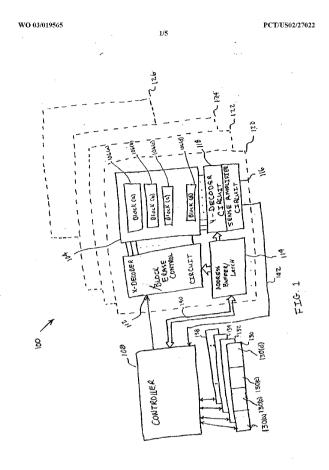

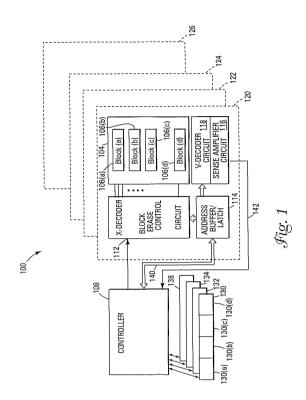

図1は、本発明の一実施の形態に係る大容量フラッシュメモリ100のブロック図である

[0022]

このブロック図は、本発明の理解に必要な要素を簡略化して示したものである。大容量フ

30

50

ラッシュメモリ 1 0 0 は、フラッシュメモリ 1 2 0 を含む。図示したフラッシュメモリ 1 2 0 は、不揮発性メモリセルのアレイ 1 0 4 を含む。アレイ 1 0 4 は、複数のアドレス指 定可能なブロック106(a~d)が配列されたものである。図面上には、アドレス指定 可能なブロック 1 0 6 ( a ~ d ) を 4 個のみ示すが、当業者であれば、本発明のフラッシ ュメモリデバイスがアドレス指定可能なブロックを4個使用したものだけに限定されない ことが理解できるであろう。フラッシュアレイの分割方法を変更し、アドレス指定可能な ブロックの数を増やしてもよいし、減らしてもよい。また、サブブロックを使用すること も可能である。さらに、図示したフラッシュメモリデバイス(120)は、xデコーダ/ ブロック消去制御回路とyデコーダ回路を備える。センスアンプ回路116は、アドレス を指定されたセルの読み出し、ベリファイを行う。アドレスバッファ/ラッチ114は、 アドレス要求を受信するためのものであり、 x デコーダ回路 / ブロック消去制御回路 1 1 2 及び y デコーダ回路 1 1 8 に接続されている。また、本実施の形態において大容量フラ ッシュメモリ 1 2 0 、 1 2 2 、 1 2 4 、及び 1 2 6 として 4 つのフラッシュメモリ 1 0 0 を用いているが、フラッシュメモリの数は、必要な記憶容量に応じて変更することができ 、 本 発 明 の 大 容 量 フ ラ ッ シ ュ メ モ リ が 4 個 の フ ラ ッ シ ュ メ モ リ に 限 定 さ れ な い こ と が 理 解 できよう。

## [ 0 0 2 3 ]

また、図1に示す大容量フラッシュメモリ100は、コントローラ108を有する。コントローラ108は、フラッシュメモリアレイにおいて、フラッシュメモリ120、122、124、及び126で行われるメモリの各処理、即ち、プログラム処理、消去処理、計み出し処理の制御に使用される。例えば、フラッシュメモリ120では、コントローラ108は、データライン142を介してセンスアンプ回路116に接続され、このコントローラに対し、読み出し、またはベリファイを行ったセルの結果が設定され、スのコントローラに対し、またはベリファイを行ったセルの結果が接供される。また、コントローラ108は、メデコーダ/ブロック消去制御回路112に接続され、メモリアレイ104上での消去処理を制御する。図示しないが、フラッシュメモリ120と同様の構成要素は、コントローラ108に接続されている。つまり、フラッシュメモリ120、122、124、126の各々は、コントローラ108に接続されている。つまり、フラッシュメモリ120、122、124、126の各々は、コントローラ108によって制御されている。

## [0024]

図 1 に示されている 4 つのレジスタ 1 3 0 、 1 3 2 、 1 3 4 、及び 1 3 8 の各々は、各フ ラッシュメモリ 1 2 0 、 1 2 2 、 1 2 4 、 及び 1 2 6 のフラッシュメモリアレイに関連付 けられている。例えば、レジスタ130は、フラッシュメモリ120上のフラッシュメモ リアレイ104に関連付けられている。本実施の形態においては、レジスタ130は、フ ラッシュメモリ 1 2 0 を含むダイの外側に設けられている。同様に、レジスタ 1 3 2 、 1 3 4 、 及び 1 3 8 は、 フラッシュメモリ 1 2 2 、 1 2 4 、 及び 1 2 6 の 特定 の 場所 に 設け られている。各レジスタ130、132、134、及び138は、レジスタサブブロック に細分化される。例えば、レジスタ130は、レジスタサブブロック130(a)、13 0 ( b ) 、 1 3 0 ( c ) 、及び 1 3 0 ( d ) を含む。各レジスタサブブロックは、フラッ シュメモリアレイにおけるセルのブロックに関連付けられている。 例えば、レジスタサブ ブロック 1 3 0 ( a ) は、フラッシュメモリアレイ 1 0 4 のブロック 1 0 6 ( a ) に関連 付けられ、レジスタサブブロック130(b)は、フラッシュメモリアレイ104のブロ ック 1 0 6 ( b ) に関連付けられ、レジスタサブブロック 1 3 0 ( c ) は、フラッシュメ モリアレイ 1 0 4 のブロック 1 0 6 ( c ) に関連付けられ、レジスタサブブロック 1 3 0 ( d ) は、フラッシュメモリアレイ 1 0 4 のブロック 1 0 6 ( d ) に関連付けられる。 4 つ の レ ジ ス タ サ ブ ブ ロ ッ ク を 有 す る レ ジ ス タ が 4 個 存 在 す る 場 合 に つ い て 説 明 し た が 、 当 業 者 で あ れ ば 、 レ ジ ス タ の 数 、 レ ジ ス タ サ ブ ブ ロ ッ ク の 数 が 使 用 さ れ る フ ラ ッ シ ュ メ モ リ アレイの数に応じて変更されること、また、フラッシュメモリアレイにおけるブロックの

30

40

50

数を変更可能であることが理解できよう。本発明は、 4 つのレジスタサブブロックを有するレジスタが 4 個存在する場合に限定されるものではない。

#### [0025]

レジスタ130、132、134、及び138は、レジスタアレイとして言及される。レジスタサブブロックの各々は、複数のレジスタメモリセル(トラッキングメモリセルられたブロックの各々は、メモリ内の関連付けられたブロックにおける関連付けられたブロックにおける関連付けられたブロックにおける対し、レジスタサブブロックにおけるできる。できるできる。例えば、メモリのブロックには、ロウが消去されたことをトラックすること、または、ロウが消去されたことをトラックすること、または、ロウが消去されたことをトラックすること、または、ロウが消去されたによった。メモリのブロックに128個のロウが消去されたしがスタサブブロックには、各すのでは、メモリセルが存在すると想定した場合、このブロックに関連付けられたレジスタサブブロックには、存在ウにおけるプログラム状態をトラックするための128個のレジスタメモリセルが存みよいては、レジスタアレイにおけるレジスタメモリセルとして、フラッシュメモリセルなどの不揮発性メモリセルが使用される。

#### [0026]

上述したように、コントローラ108は、各フラッシュメモリアレイの消去処理を制御す る。一実施の形態においては、消去しようとするブロックに対して消去パルスが送信され た場合、コントローラ108がブロックにおける各口ウのベリファイを行う。あるロウが 消去されているとベリファイされた場合、コントローラ108は、関連付けられたレジス タサブブロックにおいて関連付けられたレジスタメモリセルのフラッグを立てる。どのロ ウが消去されたことがベリファイされたかをトラックするだけでなく、コントローラは、 ベリファイされたロウの数をトラックする。消去パルスの後、所定数のロウがベリファイ されていない場合には、さらなる消去パルスがブロックに対して印加される。この処理は 、コントローラ108が所定数のロウが消去されていることをベリファイするまで行われ る。消去されているものとしてベリファイされないロウは、後で行われるメモリ処理にお いて使用されない。本実施の形態においては、各ブロック内において使用しないロウも存 在するが、セルを過剰消去する危険性が減少する。なぜならば、ブロックに対して印加さ れる消去パルスの数は、消去が行われるセルのブロックにおいて、消去される速度が最も 遅いセルやビットに依存しないからである。所定数のロウとは、通常、ロウの半数を超え る数であり、メモリの製造元によって決定される。この数は、平均的なフラッシュメモリ ブロックにおいて、 幾つのロウに遅いビットが含まれているかという点に関する統計的な データを考慮して決められる。例えば、合計のロウの数が128個であり、3個のロウに 遅いビットが含まれていることを想定した場合、このブロックの所定数のロウとは、12 5個になる。

#### [ 0 0 2 7 ]

別の実施の形態においては、コントローラ108は、ベリファイされていないロウにおけるセルの消去を試行する。この実施の形態においては、コントローラは、消去されたロウとして所定数のロウがベリファイされるために使用されるパルスの数をトラックする。次に、コントローラ108は、この数を等式に当てはめ、残りの遅いビットの消去の試行に必要となる追加のパルスの最大の数を算出するとともに、プロック内で他のセルが過剰消去される可能性を最小限にする。

## [0028]

この実施の形態では、追加の消去パルスによって遅いビットの消去を試行する際に半数を超えるセルが過剰消去されるような可能性が考慮される。

#### [0029]

一実施の形態においては、等式 N 2 = ( A \* N 1 )を使用し、遅いビットの消去の試行に使用されるべき消去パルスの最大数を決定する。この際、 N 2 は、消去パルスの最大数であり、 N 1 は、ブロック内のロウの所定数の消去に使用される消去パルスの数であり、 A

20

30

40

50

は、所定の割合であり、Bは、スロウビットの消去を試行する際に使用される最小数のパルスである。A及びBは、通常、製造時に検査終了後決定される。本実施の形態における等式を参照する。この実施の形態の等式を参照すると、N2が増加すれば、N1が増加する。従って、消去されたロウとして所定数のロウがベリファイされるのに多くのパルスを必要とすれば、ブロックにおいて既に消去済みのセルを上書消去する可能性が少ないため、ベリファイされていないロウにおける遅いセルの消去を試行するために、多くのパルスが印加される。また、消去されたロウとして所定数のロウがベリファイされるのに少ないパルスを必要とすれば、各パルスは、既に消去されたセルを過剰消去する可能性が高いため、ベリファイされていないロウにおける遅いセルの消去を試行するために、少ないパルスが印加される。

[0030]

本実施の形態においては、N2個のパルスが印加され、幾つかのロウが、消去されているとベリファイされていない場合、コントローラ108は、メモリアレイに対して後で行われるメモリ処理(即ち、プログラム処理及びメモリ処理)においてベリファイされていない口ウを無視する。一実施の形態においては、コントローラは(108)、関連付けられたレジスタにおけるメモリセルを読み出すことによってこれを行う。コントローラ108が消去されているとフラッグを立てられたりプログラムされたりしていないメモリセルを読み出した場合、消去されたとベリファイされていないロウに関連付けられたメモリセルは、ベリファイされていないロウとして定義される。

[0031]

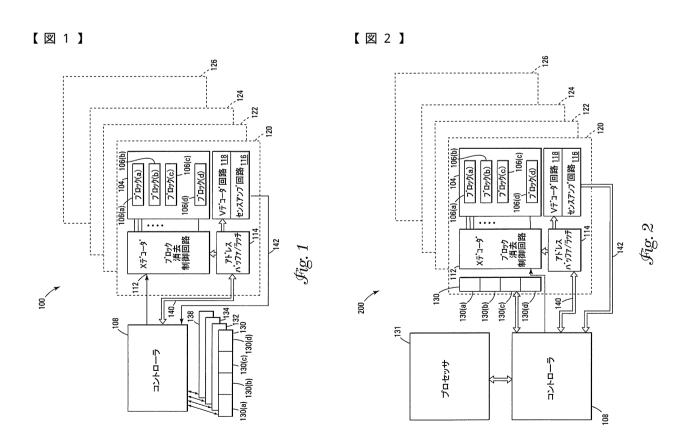

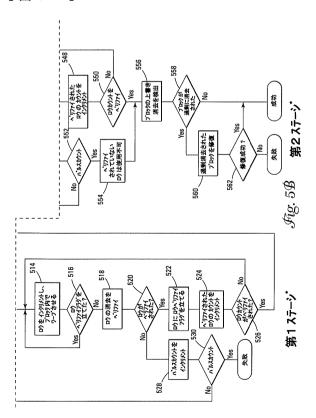

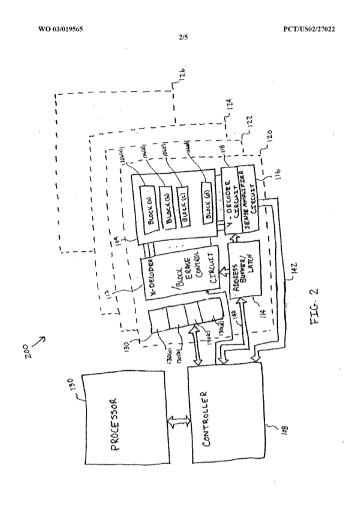

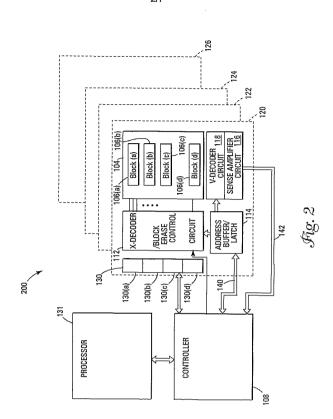

図2は、本発明の別の実施の形態に係る大容量フラッシュメモリ200を示している。本実施の形態においては、各レジスタは、ダイの内部にあり、このダイは、フラッシュメモリアレイのメモリにおいて関連付けられたブロックにおける関連付けられたロウが消去されているとベリファイされたかどうかを示すデータを格納するために関連付けられたフラッシュメモリを含む。図2に示すように、レジスタ130は、フラッシュメモリ120内に存在する。図示しないが、フラッシュメモリ122、124、128の各々には、レジスタが関連付けられている。コントローラ108は、大容量フラッシュメモリ200の各レジスタに接続され、関連付けられたロウの消去された状態に関するデータの格納、取得を行う。また、図2は、コントローラ108に接続されたプロセッサ131を示す。このプロセッサ131は、大容量フラッシュメモリ200における処理及びテストを実行するためのものである。

[0032]

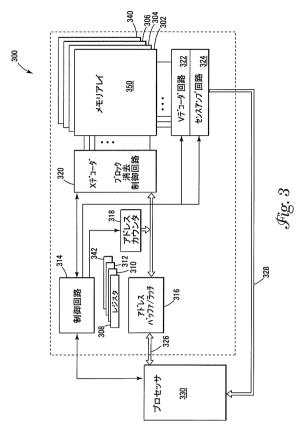

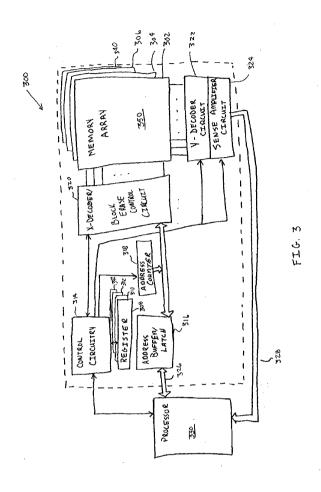

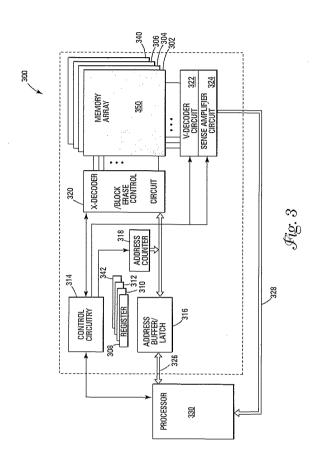

[0033]

図示したフラッシュメモリ 3 0 0 もまた、選択されたロウに対する処理を実行し、ブロック消去処理を制御する x デコーダ / ブロック消去制御回路 3 2 0 を有する。 y デコーダ 3 2 2 は、選択されたコラムに対する処理を実行するために設けられる。センスアンプ回路 3 2 4 は、指定されたセルに対する読み出しやベリファイを行うために設けられる。また、フラッシュメモリ 3 0 0 は、メモリアレイ 3 5 0 に対する各処理、即ち、読み出し処理

30

40

50

、プログラム処理、さらに、消去処理を制御する制御回路 3 1 4 を有する。制御回路 3 1 4 は、コントローラやステートマシンとも呼ばれる。プロセッサ 3 3 0 は、テストや処理の実行のために制御回路 3 1 4 に接続される。また、図示したフラッシュメモリ 3 0 0 は、アドレスバッファ / ラッチ 3 1 6 とアドレスカウンタ 3 1 8 とを有する。

#### [0034]

本実施の形態においては、レジスタ308、310、312、342が制御回路314に接続され、メモリアレイ350上において消去されたロウをトラッキングする。各レジスタは、メモリアレイ350におけるバンクに関連付けられる。例えば、レジスタ308は、バンク302に関連付けられ、レジスタ310は、バンク304に関連付けられる。レジスタ312は、バンク306に関連付けられ、レジスタ342は、バンク340に関連付けられる。図示しないが、各レジスタは、メモリの各ブロックに関連付けられたレジスタサブプロックを有する。メモリの各プロックは、関連付けられたメモリのプロックにおける関連付けられたロウが消去されているかがベリファイされたかどうかを示すデータを格納する複数のメモリセルを有する。レジスタ308、310、312、342は、上述した実施の形態について説明されたように構成される。本発明のスロウビット消去アルゴリズムをより理解するために、まず、従来技術のアルゴリズムについて説明する。

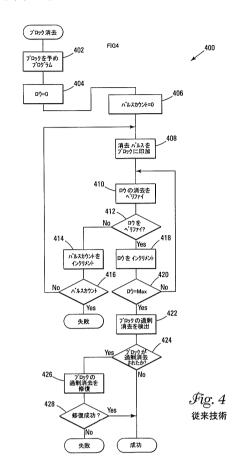

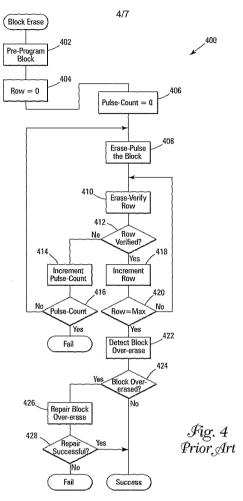

#### [0035]

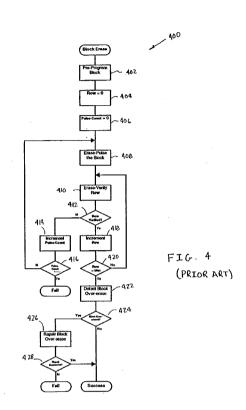

図4は、従来技術に係るブロック消去アルゴリズム400のフローチャートを示す。図示するように、従来技術においては、ブロックにおけるセルを所定のレベルに予めプログラムすることによってブロック消去アルゴリズム400が開始される(402)。次に、ロウアドレス及びパルスカウントの双方がゼロに設定される(404、406)。この後、消去パルスがブロックに印加され(408)、ロウにおける各セルが読み出される(410)。その後、ロウが消去されていることがベリファイされる(412)。

#### [0036]

ロウが消去されているとベリファイされていない場合(410)、パルスカウントがインクレメントされる(414)。次に、パルスカウントがベリファイされ、このカウントが所定の最大の数に達したかどうかがベリファイされる(416)。パルスカウントがパルスの最大の数に達していることがベリファイされた場合には(416)、ブロックの消去が行われない。パルスカウントが最大の数に達していることがベリファイされた場合には(416)、ブロックの消去が行われない。パルスカウントが最大の数に達していないことがベリファイされた場合には(416)、別の消去パルスがブロック(408)に対して印加され、アルゴリズムが進行する。

#### [ 0 0 3 7 ]

ロウが消去されているとベリファイされた場合には(412)、ロウがインクレメントされる(418)。次に、ロウのカウントが最大の数に達しているかどうかがベリファイされる(420)。ロウの各セルが読み込まれ(410)、アルゴリズムが進行する。ロウのカウントが最大の数に達しているとベリファイされた場合には(420)、ブロックの各カラムに対し、過剰消去されたセルが接続されていることを示す電流が発生していないかどうかがチェックされる(422)。次に、過剰消去されたセルが存在しているかどうかを判定するため、ブロックがベリファイされる(424)。

## [ 0 0 3 8 ]

ブロックにおいて、過剰消去されたセルが存在しなければ(424)、ブロック消去が正常に行われたことになる。ブロックに過剰消去したセル(424)が存在する場合には、ソフトプログラムによって過剰消去されたセルの修復が試行される(426)。修復が正常に行われたことがベリファイされない場合には(428)、ブロックに過剰消去されたセルが存在することになる。修復が正常に行われたことがベリファイされた場合には(428)、ブロック消去が正常に行われたことになる。

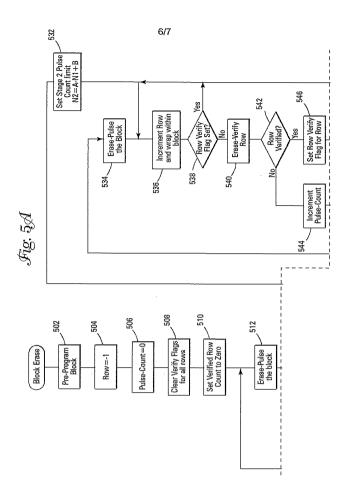

## [0039]

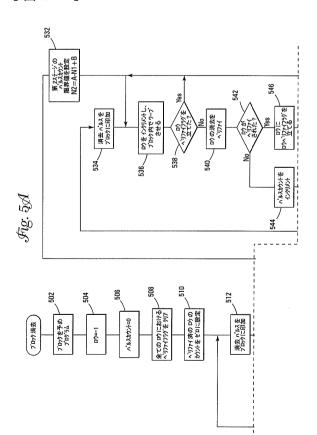

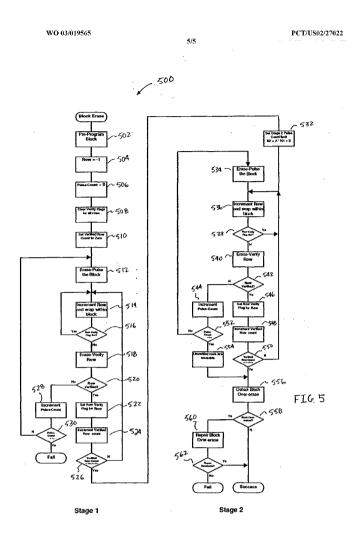

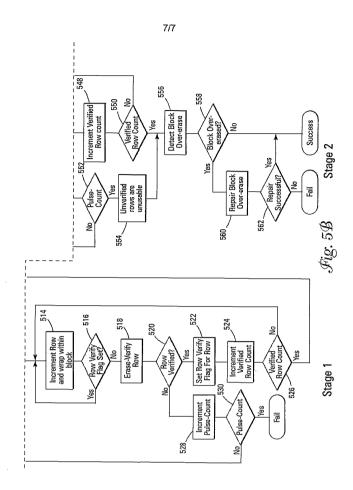

図 5 は、本発明の一実施の形態に係る消去アルゴリズム 5 0 0 のフローチャートを示している。図示するアルゴリズムは、第 1 ステージ及び第 2 ステージを含む。第 1 ステージで

30

40

50

は、所定数の口ウを消去するのに必要なパルスの数をトラックし、レジスタを使用して消去されているとベリファイされた口ウにフラッグを立てる。第2ステージでは、ブロックに対して印加される所定の最大数の消去パルスを算出し、この消去パルスをブロックに対して印加することによって、第1ステージにおいて消去されているとベリファイされなかった口ウの消去を試行する。

[0040]

第1ステージは、ブロック内のセルを所定のレベルに予めプログラムすることによって開始する(502)。ブロックにおけるロウのアドレスカウンタは、・1にセットされる(504)。パルスカウントがゼロ(506)に設定されると、すべてのベリファイフラグがクリアされる(508)。関連付けられたレジスタにおける、ベリファイされたロウのカウントがゼロにセットされる(510)。次に、消去パルスがブロックに印加される(512)。このロウは、インクレメントされる(ロウのカウントが最大値に達すると、ロウのアドレスが第1のロウに戻る)(514)。次に、レジスタがチェックされ、現在アドレスされているロウに対して既に消去されていることを示すフラッグが立てられているかどうかを判定する(516)。

[0041]

ロウが消去されていることを示すフラッグが立てられている場合には(516)、ロウが インクレメントされ(514)、アルゴリズムが進行する。ロウが消去されていることを 示すフラッグが立てられていない場合には、この口ウにおけるセルの各々がベリファイさ れ、すべてのセルが消去されているかどうかが判定される(518)。セルがすべて消去 されているならば、このロウに関連付けられたレジスタにフラッグが立てられ、ロウがイ ン ク レ メ ン ト さ れ ( 5 1 4 ) 、 ア ル ゴ リ ズ ム が 進 行 す る 。 ロ ウ が 消 去 さ れ た と ベ リ フ ァ イ されない場合には、パルスカウントがインクレメントされる(528)。次に、パルスカ ウントがベリファイされ、最大の数に達しているかどうかが判定される(530)。パル ス カ ウ ン ト が 最 大 の 数 に 達 し て い る 場 合 に は 、 現 在 の ロ ウ に 対 し て ブ ロ ッ ク 消 去 処 理 が 実 行されない。しかしながら、パルスカウントが最大の数に達していない場合には、消去パ ルスがブロック(512)に印加され、アルゴリズムが進行する。ロウにおけるすべての セルが消去されているとベリファイされなければ(520)、ロウにおける関連付けられ たレジスタ(522)にフラッグが立てられる。次に、ベリファイされたロウのロウカウ ントがインクレメントされる(524)。次に、ベリファイされたロウ(526)のロウ カウントが所定の値に達しているかがどうかがベリファイされ、ロウがインクレメントさ れ(512)、アルゴリズムが進行する。ロウのロウカウントが所定の最大の値に達して いるとベリファイされた場合には、第2ステージのアルゴリズムが開始する。

[ 0 0 4 2 ]

図示するように、第2ステージは、第1ステージのパルスカウントに所定の等式を当てはめ、第1ステージで消去されているとベリファイされなかった口ウにおけるセルの消去を試行するために必要な、ブロックに対して印加される最大限の消去パルスを求めることによって開始される(532)。次に、ロウがインクレメントされる(ロウが最大値に達しない場合、ロウアドレスは、最初のロウに戻る)(536)。次に、関連付けされたレジスタに対し、ロウが消去されていることを示すフラッグが立てられる(538)。レジスタに対し、フラッグが立てられている場合(538)、ロウがインクレメントされ(536)、アルゴリズムが進行する。レジスタに対し、フラッグが立てられていない場合(538)、関連付けされたロウにおける各セルのプログラム状態が読み出される(540)。次に、すべてのセルが消去されているかどうかを判定するために、ロウがベリファイされる(542)。

[0043]

口ウが消去されているとベリファイされていない場合には(5 4 2 )、パルスカウントがインクレメントされる(5 4 4 )。次に、所定の等式によってパルスの限界値が定まったかどうかを判定するために、パルスカウントがベリファイされる(5 5 2 )。パルスカウントがパルスカウントの限界値でなければ(5 5 2 )、消去パルスがブロックに対して印

加され(534)、アルゴリズムが進行する。パルスカウントがパルスカウントの限界値であれば(552)、ベリファイされていないロウを使用することはできない(554)

[0044]

ロウが消去されているとベリファイされる場合には(542)、関連付けられたレジスタにロウベリファイフラグが立てられる(546)。次に、ベリファイされたロウカウントがインクレメントされる(548)。さらに、ロウカウントがベリファイされ、すべてのロウに対して消去されていることを示すフラッグが立てられているかどうかが判定される(550)。すべてのロウに対して消去されていることを示すフラッグが立てられていない場合には(550)、ロウのアドレスがインクルメントされ、アルゴリズムが進行する。すべてのロウに対して消去されていることを示すフラッグが立てられている場合には(556)、ブロックのカラムが監視され、ブロックに過剰消去されたセルが存在するかどうかが判定される(556)。次に、過剰消去されたセルを処理するためにブロックが処理される(558)。

[0045]

ブロック内に過剰消去されたセルが存在することがベリファイされている場合には(558)、プロックに対する消去処理が成功していることになる。しかしながら、ブロック内に過剰消去されたセルが存在するとベリファイされた場合には(558)、プロックに対し、ソフトプログラムが実行され、過剰消去されたセル(560)の修復が行われる。次に、ブロックがベリファイされ、ソフトプログラムによる過剰消去されたセルの修復が成功したかどうかが判定される(562)。ソフトプログラムによるセルの修復が成功した場合には(562)、プロックが正常に消去されたことになる。しかしながら、ソフトプログラムによるセルの修復が成功しなかった場合には(562)、プロックには過剰消去されたセルが存在することになるため、コントローラ又は制御回路は、ブロックメモリにおける他の処理の際にこのような過剰消去されたセルが存在するロウを使用しないようにする。

[0046]

結 論

フラッシュメモリブロックの消去処理を実行する方法及びその装置を開示する。一実施の形態においては、この方法は、メモリブロックにおける所定の割合の口ウを消去するステップと、この所定の割合の消去に使用される消去パルスの数を分析するステップと、消去されないで残った口ウを消去するために、メモリブロックに対して追加して印加されるパルスの許容数を算出するステップとを含む。別の実施の形態においては、フラッシュメモリデバイスは、メモリアレイと、コントローラと、レジスタとを含む。メモリアレイは、フラッシュメモリセルの複数のブロックを含む。各ブロックにおけるメモリセルは、複数の口ウに配列される。コントローラは、メモリアレイに対するメモリ処理の制御に使用され、レジスタは、コントローラに接続され、メモリセルの各口ウの消去状態をトラックする。

[0047]

本明細書において、本発明の具体的な実施の形態について例示、説明したが、当業者であれば、同一の目的を達成するように計算することによって、図示した具体的な実施の形態の構成を変更することも可能であることが理解できよう。本明細書では、本発明を自由に改変、変形できることが意図されている。つまり、本発明の範囲が、クレーム及びその均等物によってのみ制限されるように意図されていることは明らかである。

【図面の簡単な説明】

[0048]

【図1】本発明の実施の形態に係るメモリデバイスのブロック図である。

【図2】本発明の一実施の形態に係るメモリデバイスのブロック図である。

【図3】本発明の一実施の形態に係るメモリデバイスのブロック図である。

【図4】従来技術に係るブロック消去を示すフローチャートである。

20

30

40

【図 5 A】本発明の一実施の形態に係るブロック消去を示すフローチャートの一部である。 【図 5 B】本発明の一実施の形態に係るブロック消去を示すフローチャート一部である。

# 【図3】

# 【図4】

# 【図5A】

【図5B】

### 【国際公開パンフレット】

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property Organization International Bureau

(43) International Publication Date 6 March 2003 (06.03.2003)

PCT

# (10) International Publication Number WO 03/019565 A2

| (51) | International Patent Classification?: | GHC |

|------|---------------------------------------|-----|

|------|---------------------------------------|-----|

- (21) International Application Number: PCT/US02/27022

- (22) International Filing Date: 23 August 2002 (23.08.2002)

- (25) Filing Language: Engli

- (26) Publication Language:

- (--,

- (30) Priority Data: 09/939,394

- 24 August 2001 (24.08.2001) US

- (71) Applicant: MICRON TECHNOLOGY, INC. [US/US]; 8000 South Federal Way, Boise, ID 83716-9632 (US).

- (72) Inventor: KEAYS, Brady, L.; 688 Silver Avenue, Half Moon Bay, CA 94019 (US).

- (74) Agent: LUNDBERG, Scott, V.; Fogg Slifer Polglaze Lcifert & Jay, P.A., P.O. Box 581009, Minneapolis, MN 55458-1009 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GB, GE, GH, GM, HR, HU, DL, H, N, S, P, KE, KG, PK, RK, ZL, CL, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SL, SK, SL, T, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

- | Einglish | (84) | Designated States | Ingliconal); | ARIPO patent (GII, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), | Eurasian patent (AM, AZ, BY, KG, KZ, MID, RI, TJ, TM), | IUS | European patent (AT, BP, BG, CF, CT, CZ, CD, BD, KE, BE, SF, FR, GB, GR, E, TT, LU, MC, NL, PT, SE, SK, TR, OAP| patent (BF, BJ, CF, GC, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: NON-VOLATILE MEMORY WITH BLOCK ERASE

(57) Abstract: A method and apparatus for crase operations of a flash memory block, analyzing a number of crase pulses used to crase the predetermined percent and calculating an acceptable number of additional crase pulses which could be applied to the memory block to crase the remaining rows. In another embodiment, a flash memory device comprises a memory array has a plurality of blocks of flash memory cells. The memory cells in each block are arranged in rows. The controller is used to controller and rows. The controller is used.

565 A2 ||

10

15

20

PCT/US02/27022

1

#### NON-VOLATILE MEMORY WITH BLOCK ERASE

#### Technical Field of the Invention

The present invention relates generally to non-volatile memories and in particular the present invention relates to erase operations in a flash memory device.

#### Background of the Invention

Memory devices are typically provided as internal storage areas in the computer. There are several different types of memory. One type of memory is random access memory (RAM). RAM has traditionally been used as main memory in a computer environment. Most RAM is volatile, which means that it requires periodic refresh of electricity to maintain its contents. Yet another type memory is a flash memory. A flash memory is a type of memory that is non-volatile. That is, flash memory is a type of memory that retains data even without a periodic refresh of electricity. Flash memory has many applications. For example, many modern computers have their basic I/O system bios stored on a flash memory chip, so that it can be easily updated if necessary. Moreover, some digital systems have replaced conventional mass storage devices with flash memory devices. Specifically, some conventional hard drives in personal computers have been replaced with flash memory.

A typical flash memory comprises a memory array that is separated into blocks of memory cells (cells). Each block of cells is arranged in a row and column fashion. Each cell includes a floating gate field-effect transistor capable of holding a charge. Each cell can be electrically programmed in a random basis by charging the floating gate. The charge can be removed from the floating gate by an erase operation. Thus, the data in a cell is determined by the presence or absence of the charge in the floating gate.

The state of a Flash memory cell is read or verified using a reference cell current. That is, a reference non-volatile memory cell is coupled to a sense amplifier circuit via a reference bit line. The cell to be verified is also coupled to the sense amplifier circuit via a second bit line. A differential current between the bit lines is

PCT/US02/27022

,

detected, and the programmed state of the cell is determined. For example, the reference cell may be programmed to an intermediate state such that it conducts about half the current conducted by a fully programmed memory cell, such that if the cell to be read is programmed, it conducts more current than the reference memory cell, and if the cell to be read is erased, it conducts less current than the reference cell.

To program a memory cell, a high positive voltage such as 12 volts is applied to the control gate of the cell. In addition, a moderate positive voltage such as 6 to 9 volts is applied to the drain while a source voltage and a substrate voltage are at ground level. These conditions result in the inducement of hot electron injection in the channel region near the drain region of the memory cell. These high-energy electrons travel through the thin gate oxide towards the positive voltage present on the control gate and collect on the floating gate. The electrons remain on the floating gate and function to increase the effective threshold voltage of the cell as compared to a cell that has not been programmed.

In flash memories, cells are erased in blocks. This is achieved by putting a negative voltage such as –10 to –17 volts on word lines coupled to the control gates of all the cells in a block of cells and coupling the source connection of the block to a Vcc (power supply) such as 5 volts, or higher for a period of time. This is usually done as a pulse or a series of pulses. Each pulse creates a field that removes electrons from the floating gates of the memory elements. The speed in which a cell is erased, i.e. the number of pulses needed to erase the cell, is dependant on many varying conditions including voltage level of pulses, length of pulses and temperature. It is common to have a flash memory block in which individual memory cells erase at different rates. In this situation, typically the slowest bit in the block dictates the level of erasure of all the cells in the block. This can cause the other cells in the block to become over-erased. If, for example, a typical memory cells require 10 pulses to erase and the slowest memory cell in an erasable block requires 30 pulses to erase, in erasing the slowest cells, the typical cells are subject to an extra 20 erase pulses that could potentially cause them to become over-erased.

An over-erased cell is a cell that has been erased past a certain point. An over-erased cell becomes depleted. That is, too many electrons are removed from

PCT/US02/27022

3

the floating gate, causing a floating gate voltage to become more positive than the threshold of the cell. The cell, therefore, cannot be turned off, even if the control gate is at a ground potential. Moreover, an over-erased cell can cause all memory cells coupled to the same column to be read as erased cells, even though they may be programmed.

To limit the amount of over-erased cells in a block of flash memory, an erase operation comprising a pre-program cycle, an erase cycle, and a soft program cycle, is generally performed. During a pre-program cycle, all the cells in a block are first programmed above a predetermined level. This is done so that the floating gates of all the cells in the block start out with approximately the same amount of charge. The erase cycle then applies an erase pulse to the block and verifies each cell row by row to determine if all the cells are in an erased state. The erase cycle is repeated until all the cells have been verified as being erased. The soft programming cycle, or, as it is sometimes referred to, the voltage (Vt) distribution cycle, then checks each column (bit line) in the block for current levels that would indicate if an over-erased cell is coupled to the bit line. If an over-erased cell is detected in a bit line, a soft program (soft programming pulse) is systematically applied to the control gates of the cells coupled to the bit line until the current can no longer be detected.

Although a soft program cycle can be used to recover over-erased cells, it is however, desired to reduce the number of over-erased cells before a soft program cycle is applied, because some cells that are over-erased cannot be recovered.

Moreover, the integrity of cells that are over-erased and recovered can be diminished with each over-erasure.

For the reasons stated above, and for other reasons stated below which will become apparent to those skilled in the art upon reading and understanding the present specification, there is a need in the art for a flash memory with an improved process for erasing a block of flash memory having a small number of cells that are slow to erase as compared to other cells in the block.

WO 03/019565 PCT/US02/27022

4

#### Summary of the Invention

The above-mentioned problems with non-volatile memory devices and other problems are addressed by the present invention, and will be understood by reading and studying the following specification.

In one embodiment, a method of operating a flash memory is disclosed. The method comprising, erasing a predetermined percent of rows in a memory block, analyzing a number of erase pulses used to erase the predetermined percent and calculating an acceptable number of additional erase pulses which could be applied to the memory block.

In another embodiment, a method of operating a flash memory is disclosed. The method comprising, applying at least one erase pulse to the block, wherein the block has a plurality of memory cells arranged in rows, verifying each row to determine if the memory cells associated with each row are erased after each erase pulse and completing erase of the block when a predetermined number of rows in the block have been verified as being erased, wherein the predetermined number of rows is less than the total number of rows in the block.

In another embodiment, a method of operating a non-volatile memory is disclosed. The method comprising, applying at least one erase pulse to a block of flash memory cells, wherein the block of memory cells is arranged in rows, verifying if each row is erased in the block after each erase pulse is applied, counting the number of erase pulses used to verify a predetermined number of rows have been erased in the block and applying a predetermined number of erase pulses to the block to try to erase the rows that have not been verified as being erased, wherein the predetermined number of erase pulses is a fraction of the number of erase pulses used to verify the predetermined number of rows.

20

In another embodiment, a method of performing an erase operation on a flash memory block is disclosed. The method comprising, pre-charging flash memory cells arranged in rows in the block to a predetermined level, applying at least one first stage erase pulse to the block, verifying if each memory cell is erased by row after each first stage erase pulse is applied to the block, counting a first number of pulses applied to the block, wherein the first number of pulses applied to

10

15

20

PCT/US02/27022

5

the block is the number of pulses used to verify a majority of rows in the block have been erased, calculating a second number based on a fraction of the first number, wherein the second number is a maximum number of additional second stage erase pulses that may be applied to the block to try and erase the memory cells in the rows not yet verified as being erased, applying at least one second stage erase pulse to the block, verifying if each memory cell is erased by row after each second stage erase pulse is applied to the block and completing erase of the block when either the second number of second stage erase pulses have been applied to the block or all the rows have been verified as being erased.

In another embodiment, a flash memory device comprises a memory array, a controller and a register. The memory array has a plurality of blocks of flash memory cells. The memory cells in each block are arranged in rows. The controller is used to control memory operations to the memory array and the register is coupled to the controller to track the erase status of each row of memory cells.

In another embodiment, a non-volatile memory device comprises a plurality of memory arrays, a controller and a register array. Each memory array has a plurality of blocks of flash memory cells. Moreover, the flash memory cells in each block are arranged in rows. The controller is used to control memory operations to the memory arrays. The controller stores data in the register array to track rows of memory cells in blocks verified as being crased.

In another embodiment, a flash memory device comprises, a memory array and a control circuit. The memory array has a plurality of erasable blocks of memory cells. The memory cells in each block are arranged in rows. The control circuit is used to control memory operations to the memory array. Specifically, the control circuit applies a first number of erase pulses to a block being erased in a first stage and a second number of erase pulses to the block in a second stage. The number of erase pulses applied in the second stage is based on the number of erase pulses needed in the first stage to verify a predetermined number of rows in the block have been erased.

In yet another embodiment, a flash memory system comprises, a processor, a plurality of memory arrays, a controller and a plurality of registers. The processor is used to provide external erase commands. Each memory array has a

PCT/US02/27022

,

plurality of erasable blocks of flash memory cells. The memory cells in each block are arranged in rows. The controller is used to receive the external erase commands from the processor. Moreover, the controller performs erase operations on the blocks of memory cells in the plurality of memory arrays. The plurality of registers are coupled to the controller to track rows of memory cells verified as being erased. Each register is associated with one of the memory arrays. In addition, each register has a plurality of register sub-blocks. Each register sub-block is associated with a block of memory cells. Moreover, each sub-block has a register memory cell for each row in its associated block of memory cells.

10

#### Brief Description of the Drawings

Figure 1 is a block diagram of a memory device of an embodiment of the present invention;

Figure 2 is a block diagram of a memory system of one embodiment of the present invention;

Figure 3 is a block diagram of a memory device of one embodiment of the present invention;

Figure 4 is a flow chart illustrating a block erase in the prior art; and

Figure 5 is a flow chart of a block erase of one embodiment of the present invention.

#### Detailed Description of the Invention

In the following detailed description of the preferred embodiments, reference is made to the accompanying drawings, which form a part hereof, and in which is shown by way of illustration specific preferred embodiments in which the inventions may be practiced. These embodiments are described in sufficient detail to enable those skilled in the art to practice the invention, and it is to be understood that other embodiments may be utilized and that logical, mechanical and electrical changes may be made without departing from the spirit and scope of the present invention. The following detailed description is, therefore, not to be taken in a

PCT/US02/27022

7

limiting sense, and the scope of the present invention is defined only by the claims and equivalents thereof.

Referring to Figure 1, a block diagram of one embodiment of a mass storage flash memory 100 of the present invention is illustrated. The diagram is simplified to show those elements relevant to understanding the present invention. The mass storage flash memory 100 includes a flash memory 120. As illustrated, the flash memory 120 has an array 104 of non-volatile memory cells. The array 104 is arranged in a plurality of addressable blocks 106(a-d). Although only four addressable blocks 106(a-d) are shown, it will be appreciated in the art that a flash array may be divided up into more or less addressable blocks or sub-blocks and the present invention is not limited to four addressable blocks per flash memory device. The flash memory device 120 is also illustrated as having an x-decoder/block erase control circuit and a y-decoder circuit. A sense amplifier circuit 116 is provided to read or verify an addressed cell. An address buffer/latch 114 is used to receive address requests and is coupled to the x-decoder circuit/block erase control 112 and the y-decoder circuit 118. Moreover, although in this embodiment the mass storage flash memory 100 is illustrated as having four Flash memories 120, 122, 124 and 126, it will be appreciated in the art that the number of flash memories could very depending on the storage capacity desired and the present invention is not limited to four flash memories per mass storage flash memory.

As Figure 1 also illustrates, the mass storage flash memory 100 has a controller 108. The controller 108 is used to control memory operations (i.e. program, erase and read operations) of the flash memory arrays on the flash memories 120, 122, 124 and 126. For example, regarding flash memory 120, the controller 108 is coupled to the address buffer/latch 114 by address line 140 to provide address requests. The controller 108 is further coupled to the sense amplifier circuit 116 via data line 142 to provide the controller with the results of a cell that is read or verified. The controller 108 is further coupled to the x decoder/block erase control circuit 112 to control erase operations on the memory array 104. Although not shown, each flash memory 122, 124 and 126 has the same elements as flash memory 120. Moreover, the elements of flash memories 122, 124 and 126 are all coupled to the controller 108 in the same manner as the controller

PCT/US02/27022

8

108 is coupled to flash memory 120. Therefore, the controller 108 controls each flash memory 120, 122, 124 and 126.

Referring to Figure 1, four registers 130, 132, 134 and 138 are illustrated. Each register is associated with a respective flash memory array of a flash memory 120, 122, 124 and 126. For example, register 130 is associated with flash memory array 104 on flash memory 120. In this embodiment, register 130 is positioned outside of a die containing flash memory 120. Likewise, registers 132, 134 and 138 are respectfully positioned outside flash memories 122, 124 and 126. Each register 130, 132, 134 and 138 is further separated into register sub-blocks. For example, register 130 contains the register sub-blocks 130(a), 130(b), 130(c) and 130(d). Each register sub-block is associated with a block of cells in a flash memory array. For example, register sub-block 130(a) is associated with block 106(a) of flash memory array 104, register sub-block 130(b) is associated with block 106(b) of flash memory array 104, register sub-block 130(c) is associated with block 106(c) of flash memory array 104 and register sub-block 130(d) is associated with block 106(d) of 15 flash memory array 104. Although four registers having four register sub-blocks are described, it will be understood in the art that the number of registers and register sub-blocks will vary with the number of flash memory arrays used and the number of blocks in each flash memory array and the present invention is not limited to four registers having four register sub-blocks.

The registers 130, 132, 134 and 138 can be referred to as a register array. Each register sub-block contains a plurality of register memory cells, or tracking memory cells, to store data that indicates if an associated row in an associated block of memory has been verified as being erased. That is, each row of cells in a block of cells has an associated register memory cell in a register sub-block to track or flag when the row has been crased. For example, for a block of memory having 128 rows, an associated register sub-block will have 128 register memory cells to track the program state of each row. In one embodiment of the present invention, the register memory cells in the register array are volatile memory cells, such as RAM memory cells. In another embodiment, the register memory cells in the register array are non-volatile memory cells, such as flash memory cells.

20

PCT/US02/27022

9

As stated above, the controller 108 controls erase operations of each flash memory array. In one embodiment, after an erase pulse is applied to a block to be erased, the controller 108 verifies each row in the block. If a row is verified as being erased, the controller 108 flags an associated register memory cell in an associated register sub-block. Besides tracking which rows have been verified as being erased, the controller also tracks the number of rows that have been verified. If a predetermined number of rows have not been verified after an erase pulse, a further crase pulse is applied to the block. This process is repeated until the controller 108 verifies that the predetermined number of rows are erased. Rows not verified as being erased are not used during subsequent memory operations. Although, a number of rows in each block may be unused in this embodiment, the risk of overerasing cells is reduced because the number of erase pulses applied to the block will not be controlled by the slowest cells or bits in the block of cells being erased. The predetermined number of rows is generally a majority of the rows and is selected by the manufacture of the memory and takes into consideration statistical data regarding how many rows could be expected to contain slow bits in an average flash memory block. For example, if the total amount of rows was 128 and it would be expected that three rows might contain slow bits, the predetermined amount of rows for this block would be 125.

In another embodiment, the controller 108 attempts to erase the cells in the rows that have not been verified. In this embodiment, the controller keeps track of the number of pulses used in getting the predetermined amount of rows verified as erased rows. The controller 108 then applies this number to an equation to calculate the maximum number of additional pulses that may be used to try and erase the remaining slow bits while minimizing the risk of over-erasing other cells in the block. This embodiment takes into consideration the likely hood that additional erase pulses would over-erase a majority of the cells in trying to erase slow bits.

In one embodiment, the equation N2 = (A\*N1) + B is used to determine the maximum number of erase pulses that should be used in trying to erase the slow bits. Wherein, N2 is maximum number of erase pulses, N1 is the number of erase pulses used erasing the predetermined number of rows in the block, A is a predetermined fraction and B is a minimum number of pulses to use in trying to

PCT/US02/27022

10

erase the slow bits. A and B are generally set by the manufacture after testing the memory. Referring to the equation in this embodiment, as N2 is increased, N1 is increased. Therefore, if it takes a lot of pulses to reach the predetermined amount of rows verified as being erased rows, more pulse could be applied in trying to erase the slow cells in the unverified rows because the additional pulses are less likely to over-erase the already erased cells in the block. On the other hand, if it takes only a few pulses to reach the predetermined amount of rows verified as erased, a lesser amount of pulses would be applied in trying to erase the slow cells in the unverified rows because each pulse is more likely to over-erase the already erased cells. An erase algorithm incorporating the aforementioned is described in greater detail

In this embodiment, if after N2 pulses have been applied, some of the rows are still not verified as being erased, the controller 108 ignores the unverified rows during subsequent memory operations (i.e. program and read operations) to the memory array. In one embodiment, the controller 108 does this by reading the memory cells in associated registers. If the controller 108 reads a memory cell that has not been flagged or programmed as being erased, the controller 108 skips over the row associated with the memory cell during the subsequent memory operation. In this embodiment, memory cells associated with rows that have not been verified as being erased are labeled as unverified rows.

Referring to Figure 2, another embodiment of a mass storage flash memory 200 of the present invention is illustrated. In this embodiment, each register is internal to a die containing an associated flash memory to store the data that indicates if an associated row in an associated block of memory in a flash memory array has been verified as being erased. As illustrated in Figure 2, register 130 is located in flash memory 120. Although not shown, flash memories 122, 124 and 128 also have an associated register. The controller 108 is coupled to each register of the mass storage memory 200 to store and retrieve data regarding the erased state of an associated row. Figure 2 also illustrates a processor 130 coupled to the controller 130 for operation and testing of the mass storage memory 200.

Although it may be desired to apply the current invention to a mass storage flash memory, as described above, because a mass storage flash memory

PCT/US02/27022

11

may have a significant amount of unused storage space, the present invention could also be applied to a typical flash memory system. Referring to Figure 3, another embodiment of the present invention is illustrated incorporating a typical flash memory 300. The flash memory 300 has a memory array 350. The memory array 350 is shown having four banks 302, 304, 306 and 340. Each bank 302, 304, 306 and 340 contains erasable blocks of memory cells (not shown). Moreover, in one embodiment each block is further arranged in erasable sub-blocks. For example, a 16 Meg memory array can be arranged in four crasable blocks of 4 Meg where each of these blocks contains 16 sub-blocks. Although the memory array is illustrated as only having four banks, it will be appreciated in the art that more or less banks could be used and the present invention is not limited to four banks.

As illustrated, the flash memory 300 also has an x-decoder/block erase control circuit 320 to address selected rows and control block erase operations. A y-decoder 322 is provided to address selected columns. A sense amplifier circuit 324 is also provided to read or verify addressed cells. The flash memory 300 further has control circuitry 314 to control operations, i.e. read, program and erase operations, to the memory array 350. The control circuitry 314 can also be referred to as controller or a state machine. A processor 330 is coupled to the control circuitry 314 for testing and operation. The flash memory 300 is also shown having an address buffer/latch 316 and an address counter 318.

In this embodiment, registers 308, 310, 312, 342 are coupled to the control circuitry 314 to track erased rows in the memory array 350. Each register is associated with a bank in the memory array 350. For example, register 308 is associated with bank 302, register 310 is associated with bank 310, register 312 is associated with bank 340. Although not shown, each register has a register sub-block associated with each block of memory that contains a plurality of memory cells to store data that indicates if an associated row in an associated block of memory has been verified as being erased. Registers 308, 310, 312, 342 are implemented as described in the previous embodiments. To better understand the slow bit erase algorithm of the present invention, an algorithm of the prior art is first discussed.

15

20

25

PCT/US02/27022

12

Referring to Figure 4, a flow chart of a block erase algorithm 400 of the prior art is illustrated. As illustrated, in the prior art, a block erase algorithm 400 is started by pre-programming the cells in the block to a predetermined level (402). The row address and pulse count are then both set to zero (404, 406). An erase pulse is then applied to the block (408). Each cell in a row is read (410). The row is then verified as being erased (412).

If the row is not verified as being erased (410), the pulse count is incremented (414). The pulse count is then verified to see if it has reached a maximum predetermined number (416). If it is verified that the pulse count has reached the maximum number of pulses (416), erase of the block has failed. If it is verified that the pulse count has not reached a maximum number of pulses (416), another erase pulse is applied to the block (408) and the algorithm continues.

If a row is verified as being erased (412), the row is incremented (418). The row count is then verified to see if it is at a maximum (420). If the row count is not at a maximum (420), each cell of the row is read (410) and the algorithm continues. If the row is verified as being at a maximum (420), each column of the block is checked for a current indicating an over-erased cell is coupled thereon (422). The block is then verified for over-erased cells (424).

If the block has no over erased cells (424), the block erase was successful. If there are over-erased cells (424), a repair of the block is attempted with a soft program to recover the over-erased cells (426). An outcome of the repair is then verified (428). If the repair is not verified has being successful (428), the block will have over-erased cells. If the repair is verified as being successful (428), the block erase was a success.

Referring to Figure 5, a flow chart of an erase algorithm 500 of one embodiment of the present invention is illustrated. As illustrated, this algorithm is illustrated as having a first stage and a second stage. The first stage tracks the number of pulses needed to erase the predetermined number of rows and uses the registers to flag the rows that are verified as being erased. The second stage calculates and applies a maximum predetermined number of erase pulses to the block in trying to erase the rows not verified as being erased in the first stage.

25

PCT/US02/27022

13

The first stage begins by pre-programming the cells in the block to a predetermined level (502). An address counter of the rows in the block is set to minus one (504). The pulse count is set to zero (506), all verify flags are cleared (508) in an associated register and a verified row count is set to zero (510). An erase pulse is then applied to the block (512). The row is then incremented (if the row has reached its maximum, the row address starts over at a first row) (514). The register is then checked to determine if the current addressed row has already been flagged as being grased (516).

If the row has been previously flagged as being erased (516), the row is incremented (514) and the algorithm continues. If the row has not been previously flagged as being erased, the cells in the row are then verified to determine if they are all erased (518). If they are all erased, a flag is set in the register associated with the row, the row is then incremented (514) and the algorithm continues. If the row is not verified as being erased, the pulse count is incremented (528). The pulse count is then verified if it has reached a maximum (503). If the pulse count has reached a maximum, block erase of the current row has failed. If however, the pulse count is not at a maximum, an erase pulse is applied to the block (512) and the algorithm continues. If the row is verified that all the cells in the row have been erased (520), the row is flagged in an associated register (522). The row count of verified rows is then incremented (524). The row count of verified rows is then verified if it has reached the predetermined amount of verified rows (526). If the row count of verified rows has not reached the predetermined amount, the row is incremented (512) and the algorithm continues. If the row count of verified rows has reached the predetermined amount, the algorithm starts the second stage.

As illustrated, the second stage is started by applying a predetermined equation to the pulse count of the first stage to determine a maximum erase pulse limit to be applied to the block in trying to erase the cells in rows that were not verified as being erased in the first stage (532). The row is then incremented (if the row has reached its maximum, the row address starts over at the first row) (536). An associated register is then verified if it has been flagged as indicating the row has been erased (538). If the register has been flagged (538), the row is incremented (536) and the algorithm continues. If the register has not been flagged (538), the

10

15

PCT/US02/27022

14

program state of each cell in the associated row is read (540). The row is then verified if all the cells have been erased (542).

If the row is not verified as being erased (542), the pulse count is incremented (544). The pulse count is then verified to see if it is at the pulse limit as set by the predetermined equation (552). If the pulse count is not at the pulse count limit (552), an erase pulse is applied to the block (534) and the algorithm continues. If the pulse count is at the pulse count limit (552), the unverified rows are unusable (554).

If the row is verified as being erased (542), a row verify flag is set in an associated register (546). The verified row count is then incremented (548). The row count is then verified to determine if all the rows have been flagged as being erased (550). If not all the rows have been verified as being erased (550), the row address is incremented (536) and the algorithm continues. If, however, all the rows have been verified as being erased (556), the columns of the block are monitored to determine if the block has any over-erased cells (556). The block is then verified for over-erased cells (558).

If it is verified that there are no over-erased cells in the block (558), the block has successfully been erased. If, however, it is verified that there are over-erased cells in the block (558), a soft-program is applied to the block to recover the over-erased cells (560). The block is then verified if the soft program was successful in recovering the over-erased cells (562). If the soft program was successful (562), the block has been successfully erased. If, however, the soft program was not successful (562), the block will have rows with over-erased cells and the controller or control circuitry will ignore these rows during other operations to the block of memory.

#### Conclusion

A method and apparatus for erase operations of a flash memory block is disclosed. In one embodiment, a method comprises crasing a predetermined percent of rows in a memory block, analyzing a number of erase pulses used to erase the predetermined percent and calculating an acceptable number of additional erase

PCT/US02/27022

15

pulses which could be applied to the memory block to erase the remaining rows. In another embodiment, a flash memory device comprises a memory array, a controller and a register. The memory array has a plurality of blocks of flash memory cells. The memory cells in each block are arranged in rows. The controller is used to control memory operations to the memory array and the register is coupled to the controller to track the erase status of each row of memory cells.

Although specific embodiments have been illustrated and described herein, it will be appreciated by those of ordinary skill in the art that any arrangement, which is calculated to achieve the same purpose, may be substituted for the specific embodiment shown. This application is intended to cover any adaptations or variations of the present invention. Therefore, it is manifestly intended that this invention be limited only by the claims and the equivalents thereof.

WO 03/019565 PCT/US02/27022

What is claimed is:

A method of operating a flash memory comprising:

erasing a predetermined percent of rows in a memory block;

analyzing a number of erase pulses used to erase the predetermined percent;

and

.

16

calculating an acceptable number of additional erase pulses which could be applied to the memory block.  $\,$

- The method of claim 1 further comprising:

applying the number of additional erase pulses to the memory block to erase rows not previously erased.

- The method of claim 2 further comprising:

labeling rows not erased in the memory block for use during subsequent memory operations to the memory block.

- 4. The method of claim 3 wherein the other memory operations include programming and reading operations.

- A method of operating a block of flash memory comprising:

applying at least one erase pulse to the block, wherein the block has a

plurality of memory cells arranged in rows;

verifying each row to determine if the memory cells associated with each row are erased after each erase pulse; and

completing erase of the block when a predetermined number of rows in the block have been verified as being erased, wherein the predetermined number of rows is less than the total number of rows in the block.

6. The method of claim 5 further comprising:

PCT/US02/27022

17

labeling rows not verified as being crased for use during subsequent memory operations on the block.

#### The method of claim 5 further comprising:

counting a first number of pulses needed to verify the predetermined number of rows; and

calculating a maximum number of second pulses to apply to the block to try and erase the rows not verified as being erased, wherein the number of second pulses is a fraction of the first number of pulses.

#### 8. The method of claim 7 further comprising:

applying at least one erase pulse to the block in response to the number of second pulses;

verifying rows to determine if memory cells associated with the rows are erased after each erase pulse; and

completing crase of the block once the number of second pulses have been applied to the block or all the rows have been verified as being crased.

9. The method of claim 7 wherein the number of second pulses is calculated by N2 = (A\*N1) + B, wherein N2 is the number of second pulses, N1 is the first number of pulses, A is a predetermined fraction and B is a minimum number of pulses.

#### 10. A method of operating a non-volatile memory comprising:

applying at least one erase pulse to a block of flash memory cells, wherein the block of memory cells is arranged in rows;

verifying if each row is erased in the block after each erase pulse is applied; counting the number of erase pulses used to verify a predetermined number of rows have been erased in the block; and

applying a predetermined number of erase pulses to the block to try to erase the rows that have not been verified as being erased, wherein the predetermined number of erase pulses is a fraction of the number of erase pulses used to verify the predetermined number of rows.

PCT/US02/27022

18

- 11. The method of claim 10 further comprising: programming memory cells in a register that is associated with the block to track rows that have been verified as being erased.

- The method of claim 10 further comprising; pre-charging each memory cell in the block before initial an erase pulse is applied.

- 13. The method of claim 10 wherein the predetermined number of verified rows is a majority of rows in the block.

- 14. The method of claim 10 further wherein the rows not verified as being erased after the predetermined number of erase pulses are applied to the block are labeled as not erased for subsequent memory operations to the block.

- 15. A method of performing an erase operation on a flash memory block comprising:

pre-charging flash memory cells arranged in rows in the block to a predetermined level;

applying at least one first stage erase pulse to the block;

verifying if each memory cell is erased by row after each first stage erase pulse is applied to the block;

counting a first number of pulses applied to the block, wherein the first number of pulses applied to the block is the number of pulses used to verify a majority of rows in the block have been erased;

calculating a second number based on a fraction of the first number, wherein the second number is a maximum number of additional second stage erase pulses that may be applied to the block to try and erase the memory cells in the rows not yet verified as being erased:

applying at least one second stage erase pulse to the block;

verifying if each memory cell is erased by row after each second stage erase pulse is applied to the block; and

PCT/US02/27022

19

completing erase of the block when either the second number of second stage erase pulses have been applied to the block or all the rows have been verified as being erased.

16. The method of claim 15 further comprising: flagging a register associated with a row when the row is verified as being erased.

- 17. The method of claim 15 further comprising: labeling rows not verified as being erased for other operations to the memory block.

- 18. The method of claim 15 wherein the second number is calculated by N2 = (A\*N1) + B, wherein N2 is the second number, N1 is the first number of erase pulses, A is a predetermined fraction and B is a minimum number of pulses to be applied in the second stage.

- 19. A flash memory device comprising: a memory array having a plurality of blocks of flash memory cells, wherein the memory cells in each block are arranged in rows;

a controller to control memory operations to the memory array; and a register coupled to the controller to track the erase status of each row of memory cells.

- 20. The flash memory device of claim 19 wherein the register is located externally from a die containing the memory array.

- 21. The flash memory device of claim 19 wherein the register is located internally to a die containing the memory array.

- 22. The flash memory device of claim 19 wherein the register comprises: a register sub-block for each block;

PCT/US02/27022

20

each sub-block having a plurality of tracking memory cells, wherein each tracking memory cell is associated with a row in the block; and wherein the controller programs each tracking memory cell when its associated row is verified as being erased.

- 23. The flash memory device of claim 22 wherein the plurality of tracking memory cells are volatile memory cells.

- 24. The flash memory device of claim 22 wherein the plurality of tracking memory cells are non-volatile memory cells.

- 25. The flash memory device of claim 22 wherein the controller erases all the tracking memory cells prior to an erase operation.

- 26. A non-volatile memory device comprising: a plurality of memory arrays, each memory array having a plurality of blocks of flash memory cells, the flash memory cells in each block are arranged in rows; a controller to control memory operations to the memory arrays; and a register array, wherein the controller stores data in the register array to track rows of memory cells in blocks verified as being erased.

- 27. The non-volatile memory device of claim 26 wherein the register array comprises a plurality of register memory cells, wherein each register memory cell is associated with a row of memory cells in each block of memory cells in each memory array.

- 28. The non-volatile memory device of claim 26 wherein the plurality of flash memory arrays make up a mass storage device.

- 29. The non-volatile memory device of claim 26 wherein the controller performs a first stage of erase pulses on a block of memory cells in erasing a predetermined number of rows in the block, wherein in the first stage the controller counts the number of pulses needed to reach the predetermined number of rows erased.

PCT/US02/27022

21

- 30. The non-volatile memory device of claim 29 wherein the predetermined number of rows is a majority of the rows in the block to be erased.

- 31. The non-volatile memory device of claim 29 wherein the controller performs a second stage of erase pulses on the block to be erased, wherein a maximum number of erase pulses used by the controller in the second stage is a fraction of the number of erase pulses used in the first stage.

- 32. The non-volatile memory device of claim 31 wherein the number of erase pulses used in the second stage is determined by N2 = (A\*N1) + B, wherein N2 is the maximum number of erase pulses used in the second stage, N1 is the number of erase pulses used in the first stage, A is a predetermined fraction and B is a minimum number of erase pulses to use in the second stage.

- 33. A flash memory device comprising:

a memory array having a plurality of erasable blocks of memory cells, wherein the memory cells in each block are arranged in rows; and

a control circuit to control memory operations to the memory array, wherein the control circuit applies a first number of erase pulses to a block being erased in a first stage and a second number of erase pulses to the block in a second stage, further wherein the second number of erase pulses applied in the second stage is based on the number of erase pulses needed in the first stage to verify a predetermined number of rows in the block have been erased.

- 34. The flash memory device of claim 33 wherein the second number of erase pulse applied in the second stage is fraction of the first number of erase pulses applied in the first stage.

- 35. The flash memory device of claim 33 further comprising:

a register having a plurality of register sub-blocks coupled to the control circuit, wherein each register sub-block is associated with a block of memory cells, further wherein each register sub-block has a register memory cell for each row in a

PCT/US02/27022

22

block of memory cells for the control circuit to store data indicating if the associated row has been verified as being erased.

- 36. The flash memory device of claim 35 wherein each register memory cell is a non-volatile memory cell.

- 37. The flash memory device of claim 35 wherein each register memory cell is a volatile memory cell.

- 38. The flash memory device of claim 33 further wherein the control circuit does not use rows that have not been verified as being erased in subsequent memory operations to the block.

- 39. The flash memory device of claim 38 wherein the other memory operations include programming and reading.

- A flaşh memory system comprising:

- a processor to provide external erase commands;

- a plurality of memory arrays, wherein each memory array has a plurality of erasable blocks of flash memory cells, further wherein the memory cells in each block are arranged in rows:

- a controller to receive the external erase commands from the processor, wherein the controller performs erase operations on the blocks of memory cells in the plurality of memory arrays; and

- a plurality of registers coupled to the controller to track rows of memory cells verified as being crased, each register is associated with one of the memory arrays, wherein each register has a plurality of register sub-blocks, each register sub-block is associated with a block of memory cells, further wherein each sub-block has a register memory cell for each row in its associated block of memory cells.

- 41. The flash memory system of claim 40 wherein the controller stores data in the register memory cells indicating if an associated row has been verified as being

PCT/US02/27022

23

- 42. The flash memory system of claim 40 wherein each register is internal to a die containing its associated memory cell.

- 43. The flash memory system of claim 40 wherein each register is external to a die containing an associated memory array.

- 44. The flash memory system of claim 40 wherein the controller performs a first stage of applying a first number of erase pulses to a block of memory cells in erasing a predetermined number of rows of memory cells in the block and a second stage of applying a maximum second number of erase pulses to the block to try and erase rows not yet verified as being erased, wherein the second number of erase pulses is a fraction of the first number of erase pulse applied in the first stage.

- 45. The flash memory system of claim 44 wherein the maximum second number of pulses is determined by N2 = (A\*N1) + B, wherein N2 is the maximum number of second number of pulses to be applied in the second stage, N1 is the first number of erase pulses applied in the first stage, A is a predetermined fraction and B is a minimum number of pulses to be used in the second stage in trying to erase the rows that were not verified as being erase in the first stage.

- 46. The flash memory device of claim 44 wherein the predetermined number of rows of memory cells is a majority of rows in the block.

PCT/US02/27022

PCT/US02/27022

# 【国際公開パンフレット(コレクトバージョン)】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

(43) International Publication Date 6 March 2003 (06.03.2003)

PCT

English

WO 2003/019565 A3

(51) International Patent Classification<sup>7</sup>:

(21) International Application Number:

PCT/US2002/027022

(22) International Filing Date: 23 August 2002 (23.08.2002)

(25) Filing Language:

(26) Publication Language:

(30) Priority Data: 24 August 2001 (24.08.2001) US

(71) Applicant: MICRON TECHNOLOGY, INC. [US/US]; 8000 South Federal Way, Boise, ID 83716-9632 (US).

(72) Inventor: KEAYS, Brady, L.; 688 Silver Avenue, Half Moon Bay, CA 94019 (US).

(74) Agent: BOLVIN, Kenneth, W.; Leffert Polglaze & Jay, P.A., P.O. Box 581009, Minneapolis, MN 55458-1009 (US).