# (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 109036279 B (45)授权公告日 2020.04.17

(21)申请号 201811215357.6

(22)申请日 2018.10.18

(65)同一申请的已公布的文献号 申请公布号 CN 109036279 A

(43)申请公布日 2018.12.18

(73)专利权人 京东方科技集团股份有限公司 地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 杨盛际 董学 陈小川 王辉 李胜男 郑增强

(74)专利代理机构 北京同达信恒知识产权代理 有限公司 11291

代理人 郭润湘

(51) Int.CI.

**G09G** 3/3208(2016.01) H01L 27/32(2006.01)

### (56)对比文件

CN 103403787 A, 2013.11.20,

US 2018151125 A1,2018.05.31,

CN 106205493 A, 2016.12.07,

CN 108417178 A, 2018.08.17,

CN 107103878 A, 2017.08.29,

审查员 冯莹

权利要求书2页 说明书11页 附图10页

#### (54)发明名称

阵列基板、驱动方法、有机发光显示面板及 显示装置

#### (57)摘要

本发明公开了一种阵列基板、驱动方法、有 机发光显示面板及显示装置,包括:位于显示区 中的多个发光器件与各发光器件连接的像素电 路,以及位于非显示区中的多个电压控制电路; 其中,一行中至少两个像素电路共用一个电压控 制电路,从而可以简化显示区中各像素电路的结 构,降低显示区中像素电路的占用面积,从而可 以使显示区设置更多的像素电路和发光器件,实 现高PPI的有机发光显示面板。并且,通过电压控 制电路在复位控制信号的控制,将初始化信号输 出至驱动晶体管的第一极,控制对应的发光器件 四 复位,从而可以避免上一帧发光时加载于发光器 62 件上电压对下一帧发光的影响,进而改善残影现象。

1.一种阵列基板,包括:位于显示区中的多个发光器件以及与各所述发光器件一一对应耦接的像素电路;所述像素电路包括驱动晶体管;其特征在于,所述阵列基板还包括:位于所述阵列基板的非显示区中的多个电压控制电路;其中,一行中至少两个像素电路共用一个电压控制电路,且一行像素电路中驱动晶体管的第一极与共用的所述电压控制电路耦接,各所述驱动晶体管的第二极与对应的所述发光器件耦接;

所述电压控制电路被配置为响应于复位控制信号,将初始化信号输出至所述驱动晶体管的第一极,控制对应的发光器件复位;以及响应于发光控制信号,将第一电源信号输出至 所述驱动晶体管的第一极,以驱动发光器件发光;

所述像素电路还包括:第三开关晶体管、存储电容和第四开关晶体管;其中,所述第四 开关晶体管与所述第三开关晶体管的类型不同;

所述第三开关晶体管的栅极用于接收第一栅极扫描信号,所述第三开关晶体管的第一极用于接收数据信号,所述第三开关晶体管的第二极与所述驱动晶体管的栅极耦接;

所述存储电容的第一端与所述驱动晶体管的栅极耦接,所述存储电容的第二端与接地端耦接:

所述第四开关晶体管的栅极用于接收第二栅极扫描信号,所述第四开关晶体管的第一极用于接收所述数据信号,所述第四开关晶体管的第二极与所述驱动晶体管的栅极耦接。

- 2.如权利要求1所述的阵列基板,其特征在于,所述阵列基板还包括:位于显示区中的 多个像素单元,每个像素单元包括多个子像素;各所述子像素包括:一个所述发光器件与一 个所述像素电路。

- 3. 如权利要求2所述的阵列基板,其特征在于,同一行中相邻的至少两个子像素中的像 素电路共用一个所述电压控制电路。

- 4.如权利要求3所述的阵列基板,其特征在于,同一行中的所有像素电路共用一个所述电压控制电路。

- 5.如权利要求1-4任一项所述的阵列基板,其特征在于,所述电压控制电路包括:第一 开关晶体管和第二开关晶体管;

所述第一开关晶体管的栅极用于接收所述复位控制信号,所述第一开关晶体管的第一极用于接收所述初始化信号,所述第一开关晶体管的第二极与对应的驱动晶体管的第一极 耦接:

所述第二开关晶体管的栅极用于接收发光控制信号,所述第二开关晶体管的第一极用于接收所述第一电源信号,所述第二开关晶体管的第二极与对应的驱动晶体管的第一极耦接。

6.如权利要求1-4任一项所述的阵列基板,其特征在于,所述像素电路还包括:第五开 关晶体管;其中,所述驱动晶体管的第二极通过所述第五开关晶体管与对应的发光器件耦 接;

所述第五开关晶体管的栅极与参考信号端耦接,所述第五开关晶体管的第一极与所述 驱动晶体管的第二极耦接,所述第五开关晶体管的第二极与对应的发光器件耦接。

- 7.如权利要求6所述的阵列基板,其特征在于,所述第五开关晶体管为P型晶体管,所述参考信号端为接地端。

- 8. 如权利要求1-4任一项所述的阵列基板,其特征在于,所述阵列基板还包括多条发光

控制信号线,以及与各所述发光控制信号线电连接的发光控制电路;其中,一条所述发光控制信号线与一行所述像素电路电连接的所述电压控制电路电连接,用于向电连接的所述电压控制电路输入所述发光控制信号。

- 9.如权利要求8所述的阵列基板,其特征在于,所述发光控制电路包括多个级联的发光移位寄存器,每一所述发光移位寄存器与一条所述发光控制信号线对应电连接。

- 10.如权利要求8所述的阵列基板,其特征在于,所述阵列基板还包括:一条第一电源信号线;其中,所述第一电源信号线与所有所述电压控制电路电连接,用于向每一个所述电压控制电路输入所述第一电源信号;或者,

所述阵列基板还包括:多条第一电源信号线;其中,一条所述发光控制信号线与一行所述像素电路电连接的所述电压控制电路电连接,用于向电连接的所述电压控制电路输入所述第一电源信号。

- 11.一种有机发光显示面板,其特征在于,包括如权利要求1-10任一项所述的阵列基板。

- 12.一种显示装置,其特征在于,包括如权利要求11所述的有机发光显示面板。

- 13.一种用于如权利要求1-10任一项所述的阵列基板的驱动方法,其特征在于,包括:在一帧显示时间内,控制所述电压控制电路和所述像素电路,以驱动发光器件工作;其中,

驱动一行发光器件工作,包括:

重置阶段,所述电压控制电路响应于复位控制信号,将初始化信号输出至所述驱动晶体管的第一极,控制对应的发光器件复位;

数据写入阶段,将数据信号输出至所述驱动晶体管的栅极;

发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号输出至所述驱动晶体管的第一极,驱动发光器件发光。

14. 如权利要求13所述的驱动方法,其特征在于,在所述发光阶段之后,所述驱动一行发光器件工作还包括:非发光阶段:

在所述非发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号与所述驱动晶体管的第一极断开,控制对应的像素电路驱动连接的发光器件停止发光。

15. 如权利要求14所述的驱动方法,其特征在于,在所述一帧显示时间内,驱动每一行发光器件工作的非发光阶段在相同时间开启;或者,

在所述一帧显示时间内,驱动每一行发光器件工作的非发光阶段逐行依次开启。

16.如权利要求13所述的驱动方法,其特征在于,在所述发光阶段之后,所述驱动一行发光器件工作还包括:调光阶段;所述调光阶段包括:至少一个非发光阶段和至少一个发光阶段;其中,所述非发光阶段和所述发光阶段依次交替排列;

在所述非发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号与所述驱动晶体管的第一极断开,控制对应的像素电路驱动连接的发光器件停止发光;

在所述发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号输出至所述驱动晶体管的第一极,控制对应的像素电路驱动连接的发光器件发光。

17. 如权利要求16所述的驱动方法,其特征在于,在所述一帧显示时间内,驱动每一行发光器件工作的调光阶段在相同时间开启;或者,

在所述一帧显示时间内,驱动每一行发光器件工作的调光阶段逐行依次开启。

# 阵列基板、驱动方法、有机发光显示面板及显示装置

#### 技术领域

[0001] 本发明涉及显示技术领域,特别涉及一种阵列基板、驱动方法、有机发光显示面板及显示装置。

# 背景技术

[0002] 有机发光二极管 (Organic Light Emitting Diode, OLED) 显示面板是当今平板显示器研究领域的热点之一,与液晶显示器 (Liquid Crystal Display, LCD) 相比, OLED显示器具有低能耗、生产成本低、自发光、宽视角及响应速度快等优点。然而,现有的OLED显示面板中包括多个像素单元,每个像素单元包括多个子像素,每个子像素包括:一个OLED以及用于驱动OLED发光的像素电路。像素电路一般包括多个晶体管和电容。由于工艺制备精度的限制,导致像素电路会占用子像素中较大的面积,从而不利于实现高PPI的OLED显示面板。尤其是在OLED设置为Micro-OLED或Mini-OLED时,像素电路占用子像素中较大的面积对高PPI的OLED显示面板的影响尤为明显。

# 发明内容

[0003] 本发明实施例提供一种阵列基板、驱动方法、有机发光显示面板及显示装置,用以降低像素电路占用面积,有利于实现高PPI显示面板。

[0004] 本发明实施例提供了一种阵列基板,包括:位于显示区中的多个发光器件以及与各所述发光器件一一对应耦接的像素电路;所述像素电路包括驱动晶体管;所述阵列基板还包括:位于所述阵列基板的非显示区中的多个电压控制电路;其中,一行中至少两个像素电路共用一个电压控制电路,且一行像素电路中驱动晶体管的第一极与共用的所述电压控制电路耦接,各所述驱动晶体管的第二极与对应的所述发光器件耦接;

[0005] 所述电压控制电路被配置为响应于复位控制信号,将初始化信号输出至所述驱动晶体管的第一极,控制对应的发光器件复位;以及响应于发光控制信号,将第一电源信号输出至所述驱动晶体管的第一极,以驱动发光器件发光。

[0006] 可选地,在本发明实施例中,所述阵列基板还包括:位于显示区中的多个像素单元,每个像素单元包括多个子像素;各所述子像素包括:一个所述发光器件与一个所述像素电路。

[0007] 可选地,在本发明实施例中,同一行中相邻的至少两个子像素中的像素电路共用一个所述电压控制电路。

[0008] 可选地,在本发明实施例中,同一行中的所有像素电路共用一个所述电压控制电路。

[0009] 可选地,在本发明实施例中,所述电压控制电路包括:第一开关晶体管和第二开关晶体管;

[0010] 所述第一开关晶体管的栅极用于接收所述复位控制信号,所述第一开关晶体管的第二极用于接收所述初始化信号,所述第一开关晶体管的第二极与对应的驱动晶体管的第

## 一极耦接:

[0011] 所述第二开关晶体管的栅极用于接收发光控制信号,所述第二开关晶体管的第一极用于接收所述第一电源信号,所述第二开关晶体管的第二极与对应的驱动晶体管的第一极耦接。

[0012] 可选地,在本发明实施例中,所述像素电路还包括:第三开关晶体管和存储电容;

[0013] 所述第三开关晶体管的栅极用于接收第一栅极扫描信号,所述第三开关晶体管的第一极用于接收数据信号,所述第三开关晶体管的第二极与所述驱动晶体管的栅极耦接;

[0014] 所述存储电容的第一端与所述驱动晶体管的栅极耦接,所述存储电容的第二端与接地端耦接。

[0015] 可选地,在本发明实施例中,所述像素电路还包括:第四开关晶体管;其中,所述第四开关晶体管与所述第三开关晶体管的类型不同:

[0016] 所述第四开关晶体管的栅极用于接收第二栅极扫描信号,所述第四开关晶体管的第一极用于接收所述数据信号,所述第四开关晶体管的第二极与所述驱动晶体管的栅极耦接。

[0017] 可选地,在本发明实施例中,所述像素电路还包括:第五开关晶体管;其中,所述驱动晶体管的第二极通过所述第五开关晶体管与对应的发光器件耦接;

[0018] 所述第五开关晶体管的栅极与参考信号端耦接,所述第五开关晶体管的第一极与 所述驱动晶体管的第二极耦接,所述第五开关晶体管的第二极与对应的发光器件耦接。

[0019] 可选地,在本发明实施例中,所述第五开关晶体管为P型晶体管,所述参考信号端为接地端。

[0020] 可选地,在本发明实施例中,所述阵列基板还包括多条发光控制信号线,以及与各所述发光控制信号线电连接的发光控制电路;其中,一条所述发光控制信号线与一行所述像素电路电连接的所述电压控制电路电连接,用于向电连接的所述电压控制电路输入所述发光控制信号。

[0021] 可选地,在本发明实施例中,所述发光控制电路包括多个级联的发光移位寄存器,每一所述发光移位寄存器与一条所述发光控制信号线对应电连接。

[0022] 可选地,在本发明实施例中,所述阵列基板还包括:一条第一电源信号线;其中,所述第一电源信号线与所有所述电压控制电路电连接,用于向每一个所述电压控制电路输入所述第一电源信号;或者,

[0023] 所述阵列基板还包括:多条第一电源信号线;其中,一条所述发光控制信号线与一行所述像素电路电连接的所述电压控制电路电连接,用于向电连接的所述电压控制电路输入所述第一电源信号。

[0024] 相应地,本发明实施例还提供了一种有机发光显示面板,包括本发明实施例提供的阵列基板。

[0025] 相应地,本发明实施例还提供了一种显示装置,包括本发明实施例提供的有机发光显示面板。

[0026] 相应地,本发明实施例还提供了一种用于本发明实施例提供的阵列基板的驱动方法,包括:在一帧显示时间内,控制所述电压控制电路和所述像素电路,以驱动发光器件工作;其中,

[0027] 驱动一行发光器件工作,包括:

[0028] 重置阶段,所述电压控制电路响应于复位控制信号,将初始化信号输出至所述驱动晶体管的第一极,控制对应的发光器件复位;

[0029] 数据写入阶段,将数据信号输出至所述驱动晶体管的栅极;

[0030] 发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号输出至所述驱动晶体管的第一极,驱动发光器件发光。

[0031] 可选地,在本发明实施例中,在所述发光阶段之后,所述驱动一行发光器件工作还包括:非发光阶段;

[0032] 在所述非发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号与所述驱动晶体管的第一极断开,控制对应的像素电路驱动连接的发光器件停止发光。

[0033] 可选地,在本发明实施例中,在所述一帧显示时间内,驱动每一行发光器件工作的 非发光阶段在相同时间开启;或者,

[0034] 在所述一帧显示时间内,驱动每一行发光器件工作的非发光阶段逐行依次开启。

[0035] 可选地,在本发明实施例中,在所述发光阶段之后,所述驱动一行发光器件工作还包括:调光阶段;所述调光阶段包括:至少一个非发光阶段和至少一个发光阶段;其中,所述非发光阶段和所述发光阶段依次交替排列:

[0036] 在所述非发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号与 所述驱动晶体管的第一极断开,控制对应的像素电路驱动连接的发光器件停止发光;

[0037] 在所述发光阶段,所述电压控制电路响应于发光控制信号,将第一电源信号输出至所述驱动晶体管的第一极,控制对应的像素电路驱动连接的发光器件发光。

[0038] 可选地,在本发明实施例中,在所述一帧显示时间内,驱动每一行发光器件工作的调光阶段在相同时间开启;或者,

[0039] 在所述一帧显示时间内,驱动每一行发光器件工作的调光阶段逐行依次开启。

[0040] 本发明有益效果如下:

[0041] 本发明实施例提供的阵列基板、驱动方法、有机发光显示面板及显示装置,包括:位于显示区中的多个发光器件与各发光器件连接的像素电路,以及位于非显示区中的多个电压控制电路;其中,一行中至少两个像素电路共用一个电压控制电路,从而可以简化显示区中各像素电路的结构,降低显示区中像素电路的占用面积,从而可以使显示区设置更多的像素电路和发光器件,实现高PPI 的有机发光显示面板。并且,通过电压控制电路在复位控制信号的控制,将初始化信号输出至驱动晶体管的第一极,控制对应的发光器件复位,从而可以避免上一帧发光时加载于发光器件上电压对下一帧发光的影响,进而改善残影现象。

#### 附图说明

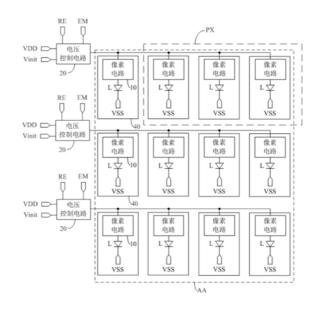

[0042] 图1为本发明实施例提供的阵列基板的结构示意图之一;

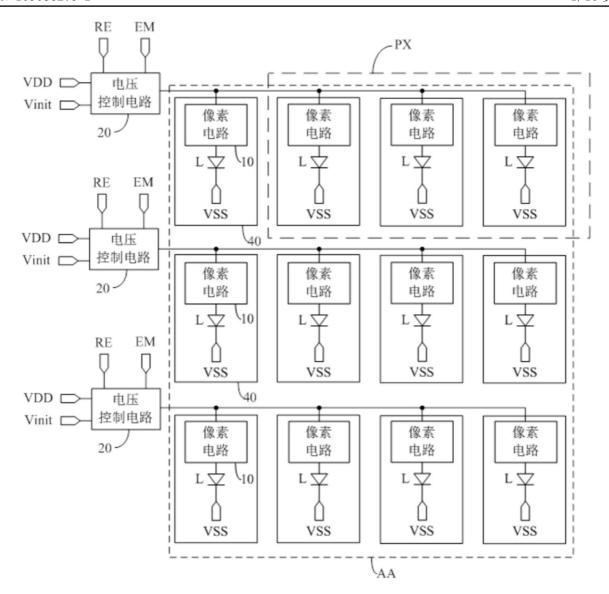

[0043] 图2为本发明实施例提供的阵列基板的结构示意图之二:

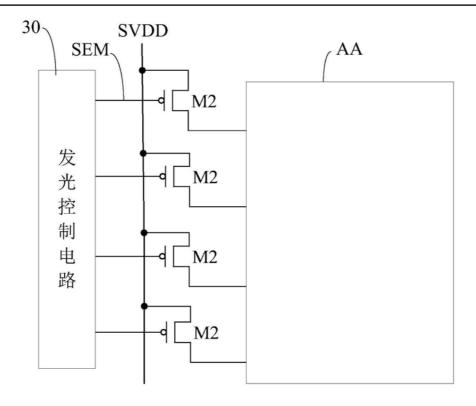

[0044] 图3a为本发明实施例提供的阵列基板的结构示意图之三:

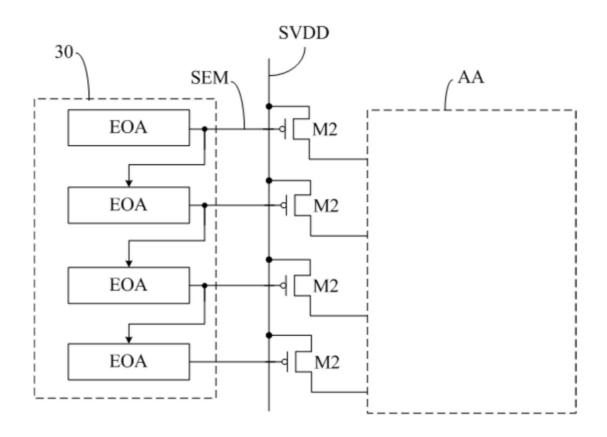

[0045] 图3b为本发明实施例提供的阵列基板的结构示意图之四;

[0046] 图4为本发明实施例提供的阵列基板的具体结构示意图之一;

[0047] 图5为本发明实施例提供的阵列基板的具体结构示意图之二:

[0048] 图6为本发明实施例提供的驱动方法的流程图:

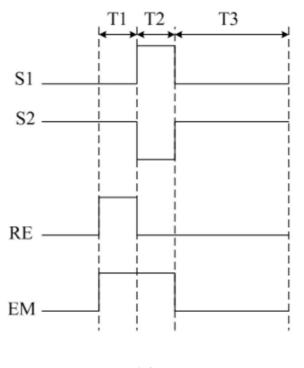

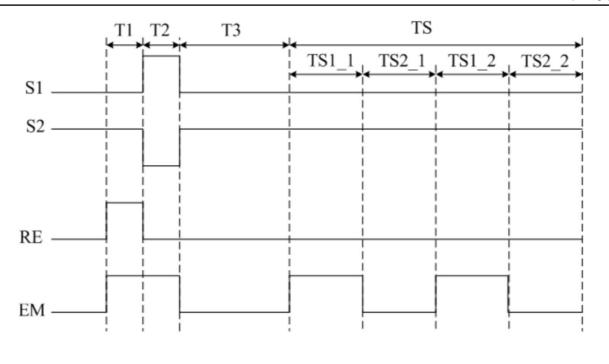

[0049] 图7为本发明实施例提供的电路时序图之一;

[0050] 图8为本发明实施例提供的电路时序图之二;

[0051] 图9为本发明实施例提供的电路时序图之三;

[0052] 图10为本发明实施例提供的电路时序图之四;

[0053] 图11为本发明实施例提供的电路时序图之五;

[0054] 图12为本发明实施例提供的电路时序图之六;

[0055] 图13为本发明实施例提供的电路时序图之七。

# 具体实施方式

[0056] 为了使本发明的目的,技术方案和优点更加清楚,下面结合附图,对本发明实施例提供的阵列基板、驱动方法、有机发光显示面板及显示装置的具体实施方式进行详细地说明。应当理解,下面所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。并且在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。需要注意的是,附图中各层薄膜厚度和形状不反映阵列基板的真实比例,目的只是示意说明本发明内容。并且自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。

[0057] 本发明实施例提供了一种阵列基板,如图1所示,可以包括:位于显示区 AA中的多个发光器件L以及与各发光器件L一一对应耦接的像素电路10;像素电路10包括驱动晶体管。并且,阵列基板还可以包括:位于阵列基板的非显示区(阵列基板中除显示区AA之外的区域)中的多个电压控制电路20;其中,一行中至少两个像素电路10共用一个电压控制电路20,且一行像素电路 10中驱动晶体管的第一极与共用的电压控制电路20耦接,各驱动晶体管的第二极与对应的发光器件L耦接。电压控制电路20被配置为响应于复位控制信号RE,将初始化信号Vinit输出至驱动晶体管的第一极,控制对应的发光器件L复位;以及响应于发光控制信号EM,将第一电源信号VDD输出至驱动晶体管的第一极,以驱动发光器件L发光。

[0058] 本发明实施例提供的上述阵列基板,包括:位于显示区中的多个发光器件与各发光器件连接的像素电路,以及位于非显示区中的多个电压控制电路;其中,一行中至少两个像素电路共用一个电压控制电路,从而可以简化显示区中各像素电路的结构,降低显示区中像素电路的占用面积,从而可以使显示区设置更多的像素电路和发光器件,实现高PPI的有机发光显示面板。并且,通过电压控制电路在复位控制信号的控制,将初始化信号输出至驱动晶体管的第一极,控制对应的发光器件复位,从而可以避免上一帧发光时加载于发光器件上电压对下一帧发光的影响,进而改善残影现象。

[0059] 在具体实施时,在本发明实施例中,如图1所示,阵列基板还可以包括:位于显示区AA中的多个像素单元PX,每个像素单元PX包括多个子像素40;各子像素40分别包括:一个发光器件L与一个像素电路10。进一步地,像素单元PX可以包括3个不同颜色的子像素40。这3个子像素40可以分别为红色子像素、绿色子像素以及蓝色子像素。当然,像素单元也可以包括4个、5个或更多的子像素,这需要根据实际应用环境来设计确定,在此不作限定。

[0060] 在具体实施时,在本发明实施例中,可以使同一行中相邻的至少两个子像素中的

像素电路共用一个电压控制电路。具体地,如图1所示,可以使同一行中的所有像素电路10 共用一个电压控制电路20。或者,也可以使同一行中相邻的两个、三个子像素或更多中的像 素电路共用一个电压控制电路,在此不作限定。这样通过共用电压控制电路可以降低显示 区中像素电路的占用面积。

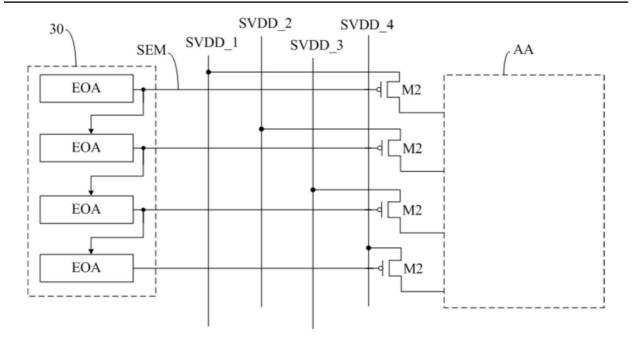

[0061] 在具体实施时,在本发明实施例中,如图2所示,阵列基板还可以包括多条发光控制信号线SEM,以及与各发光控制信号线SEM电连接的发光控制电路30;其中,一条发光控制信号线SEM与一行像素电路电连接的电压控制电路电连接,用于向电连接的电压控制电路输入发光控制信号。具体地,一条发光控制信号线SEM与显示区AA中的一行像素电路电连接的第二开关晶体管 M2的栅极电连接。

[0062] 在具体实施时,在本发明实施例中,如图3a与图3b所示,发光控制电路 30可以包括多个级联的发光移位寄存器E0A,每一发光移位寄存器E0A与一条发光控制信号线SEM对应电连接。具体地,第一级发光移位寄存器E0A的发光输入信号端用于接收帧发光触发信号,其余各级发光移位寄存器E0A的发光输入信号端分别与其相邻的上一级发光移位寄存器E0A的发光输出信号端电连接,以实现对发光控制信号线SEM输入发光控制信号的功能。在实际应用中,发光移位寄存器的结构与现有的结构相同,在此不作赘述。

[0063] 在具体实施时,在本发明实施例中,如图2与图3a所示,阵列基板还可以包括:一条第一电源信号线SVDD;其中,第一电源信号线SVDD与所有电压控制电路电连接,用于向每一个电压控制电路输入第一电源信号。具体地,该第一电源信号线SVDD与所有第二开关晶体管M2的第一极电连接。并且,第一电源信号线SVDD可以设置于非显示区中,进一步降低显示区AA中设置的走线数量,从而可以实现高PPI的有机发光显示面板。

[0064] 在具体实施时,在本发明实施例中,如图3b所示,阵列基板还可以包括:多条第一电源信号线SVDD\_m(1≤m≤M,m和M分别为整数,M代表第一电源信号线的总数,图3b以M=4为例);其中,一条发光控制信号线SVDD\_m 与一行像素电路电连接的电压控制电路电连接,用于向电连接的电压控制电路输入第一电源信号。具体地,一条发光控制信号线SVDD\_m与一行中的所有第二开关晶体管M2的第一极电连接。并且,所有发光控制信号线SVDD\_m 可以设置于非显示区中,进一步降低显示区AA中设置的走线数量,从而可以实现高PPI的有机发光显示面板。

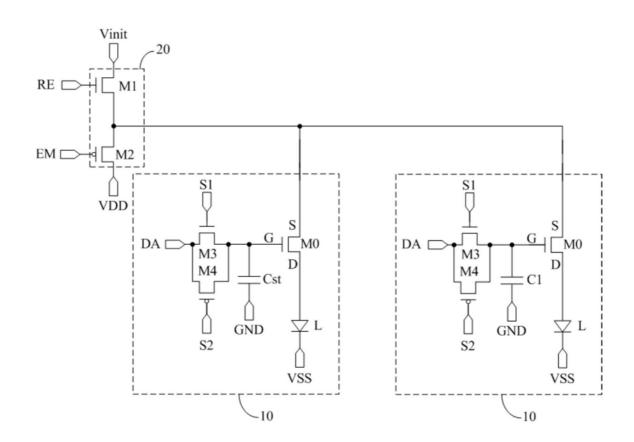

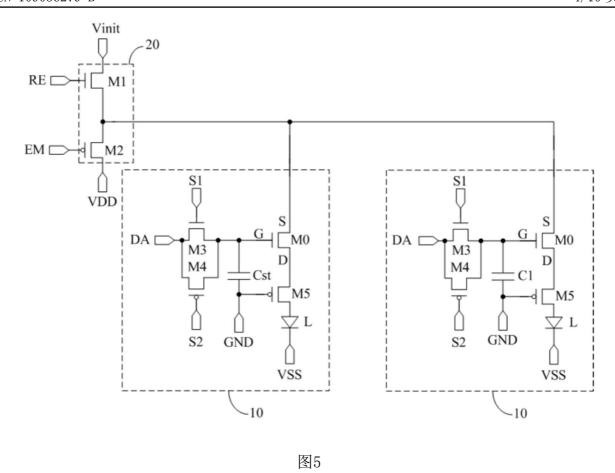

[0065] 在具体实施时,在本发明实施例中,如图4与图5所示,驱动晶体管M0 可以为N型晶体管,在电流由其第一端S流向第二端D时,可以将第一端S 作为其源极,第二端D作为其漏极。在电流由其第二端D流向第一端S时,可以将第二端D作为其源极,第一端S作为其漏极。并且,发光器件L可以包括OLED。这样OLED的正极与驱动晶体管M0的第二端D电连接,OLED的负极与第二电源端VSS电连接。第二电源端VSS的电压一般为负电压或接地电压V<sub>GND</sub>(一般为0V),初始化信号的电压也可以设置为接地电压V<sub>GND</sub>,在此不作限定。其中,可以将OLED设置为Micro-OLED或Mini-OLED,这样进一步有利于实现高PPI的有机发光显示面板。

[0066] 在具体实施时,在本发明实施例中,如图4与图5(以一行中包括的两个像素电路为例)所示,电压控制电路20可以包括:第一开关晶体管M1和第二开关晶体管M2;其中,第一开关晶体管M1的栅极用于接收复位控制信号RE,第一开关晶体管M1的第一极用于接收初始化信号Vinit,第一开关晶体管M1的第二极与对应的驱动晶体管M0的第一极S耦接。第二开关晶体管 M2的栅极用于接收发光控制信号EM,第二开关晶体管M2的第一极用于接收第一电

源信号VDD,第二开关晶体管M2的第二极与对应的驱动晶体管MO 的第一极S耦接。

[0067] 在具体实施时,如图4与图5所示,可以使第一开关晶体管M1与第二开关晶体管M2的类型不同。例如,第一开关晶体管M1为N型晶体管,第二开关晶体管M2为P型晶体管。或者,第一开关晶体管为P型晶体管,第二开关晶体管为N型晶体管。当然,也可以使第一开关晶体管M1与第二开关晶体管 M2的类型相同。在实际应用中,需要根据实际应用环境来设计第一开关晶体管与第二开关晶体管的类型,在此不作限定。

[0068] 在具体实施时,在本发明实施例中,如图4与图5所示,像素电路10还可以包括:第三开关晶体管M3和存储电容Cst;其中,第三开关晶体管M3的栅极用于接收第一栅极扫描信号S1,第三开关晶体管M3的第一极用于接收数据信号DA,第三开关晶体管M3的第二极与驱动晶体管M0的栅极G耦接。存储电容Cst的第一端与驱动晶体管M0的栅极G耦接,存储电容Cst的第二端与接地端GND耦接。

[0069] 进一步地,在具体实施时,在本发明实施例中,如图4与图5所示,像素电路10还可以包括:第四开关晶体管M4;其中,第四开关晶体管M4的栅极用于接收第二栅极扫描信号S2,第四开关晶体管M4的第一极用于接收数据信号DA,第四开关晶体管M4的第二极与驱动晶体管M0的栅极G耦接。并且,第四开关晶体管M4与第三开关晶体管M3的类型不同。例如,第三开关晶体管M3为N型晶体管,第四开关晶体管M4为P型晶体管;或者,第三开关晶体管M3为P型晶体管,第四开关晶体管M4为N型晶体管。

[0070] 在具体实施时,在本发明实施例中,如图5所示,像素电路10还可以包括:第五开关晶体管M5;其中,驱动晶体管M0的第二极D通过第五开关晶体管M5与对应的发光器件L耦接。并且,第五开关晶体管M5的栅极与参考信号端耦接,第五开关晶体管M5的第一极与驱动晶体管M0的第二极D耦接,第五开关晶体管M5的第二极与对应的发光器件L耦接。进一步地,可以将第五开关晶体管M5设置为P型晶体管,参考信号端设置为接地端GND。

[0071] 进一步的,在具体实施时,P型晶体管在高电平的信号作用下截止,在低电平的信号作用下导通;N型晶体管在高电平的信号作用下导通,在低电平的信号作用下截止。

[0072] 需要说明的是,上述开关晶体管可以是薄膜晶体管(TFT,Thin Film Transistor),也可以是金属氧化物半导体场效应管(MOS,Metal Oxide Scmiconductor),在此不作限定。在具体实施中,可以使上述开关晶体管的第一极作为其源极,第二极作为其漏极,或者,第二极作为其源极,第一极作为其漏极,在此不作限定。

[0073] 基于同一发明构思,本发明实施例还提供了一种本发明实施例提供的阵列基板的驱动方法,可以包括:在一帧显示时间内,控制电压控制电路和像素电路,以驱动发光器件工作。

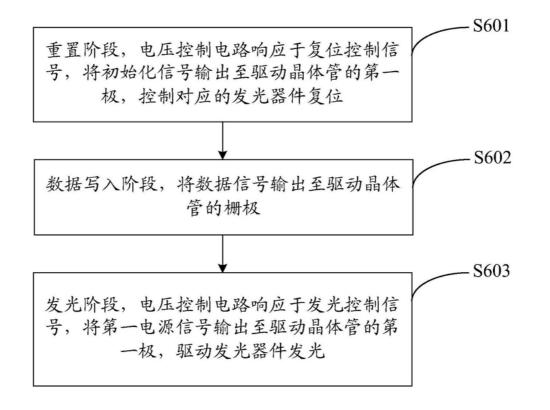

[0074] 在具体实施时,如图6所示,驱动一行发光器件工作,可以包括如下步骤:

[0075] S601、重置阶段,电压控制电路响应于复位控制信号,将初始化信号输出至驱动晶体管的第一极,控制对应的发光器件复位;

[0076] S602、数据写入阶段,将数据信号输出至驱动晶体管的栅极;

[0077] S603、发光阶段,电压控制电路响应于发光控制信号,将第一电源信号输出至驱动晶体管的第一极,驱动发光器件发光。

[0078] 下面以驱动一行发光器件工作,且分别以图4和图5所示的阵列基板的结构为例,结合电路时序图对本发明实施例提供的上述阵列基板的驱动方法作以说明。下述描述中以

1表示高电平的信号,0表示低电平的信号,需要说明的是,1和0是逻辑电平,其仅是为了更好的解释本发明实施例的具体工作过程,而不是在具体实施时施加在各开关晶体管的栅极上的电平。

[0079] 实施例一、

[0080] 以图4所示的阵列基板为例,对应的电路时序图如图7所示。驱动一行发光器件工作,可以包括:重置阶段T1、数据写入阶段T2、发光阶段T3。

[0081] 在重置阶段T1,S1=0,S2=1,RE=1,EM=1。

[0082] 由于EM=1,因此第二开关晶体管M2截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于RE=1,因此第一开关晶体管M1导通,以将初始化信号Vinit提供给驱动晶体管M0的第一极S。需要说明的是,若上一帧显示时,驱动晶体管M0的栅极G通过存储电容Cst存储的是高灰阶的数据信号(即显示高灰阶),则驱动晶体管M0的第一极S、第二极D以及发光器件L的正极的电压可以均被重置到接地电压V<sub>GND</sub>。若上一帧显示时,驱动晶体管M0的栅极G通过存储电容Cst存储的是低灰阶的数据信号(即显示低灰阶),则驱动晶体管M0的栅极G通过存储电容Cst存储的是低灰阶的数据信号(即显示低灰阶),则驱动晶体管M0的第一极S的电压被重置到接地电压V<sub>GND</sub>,并且电流由驱动晶体管M0的第二极D流向其第一极S,使得第二极D和发光器件L的正极的电压可以重置为V<sub>GND</sub>-V<sub>th</sub>。其中,V<sub>th</sub>代表驱动晶体管M0的阈值电压。这样可以避免上一帧发光时加载于发光器件上电压对下一帧发光的影响,进而改善残影现象。

[0083] 在数据写入阶段T1,S1=1,S2=0,RE=0,EM=1。

[0084] 由于EM=1,因此第二开关晶体管M2截止。由于RE=0,因此第一开关晶体管M1截止。由于S1=1,因此第三开关晶体管M3导通。由于S2=0,因此第四开关晶体管M4导通。导通的第三开关晶体管M3和第四开关晶体管M4,可以将数据信号DA提供给驱动晶体管M0的栅极G,从而使驱动晶体管M0的栅极G为数据信号的电压V<sub>DA</sub>,并通过存储电容Cst进行存储。需要说明的是,在数据信号DA的电压为高灰阶对应的电压时,通过P型的第四开关晶体管M4导通以将数据信号DA传输给驱动晶体管M0的栅极G,可以避免数据信号DA的电压受N型的第三开关晶体管M3的阈值电压V<sub>th (M3)</sub>的影响。在数据信号DA的电压为低灰阶对应的电压时,通过N型的第三开关晶体管M3 导通以将数据信号DA传输给驱动晶体管M0的栅极G,可以避免数据信号DA 的电压受P型的第四开关晶体管M4的阈值电压V<sub>th (M4)</sub>的影响。这样可以提高输入到驱动晶体管M0的栅极G上的电压范围。

[0085] 在发光阶段T3,S1=0,S2=1,RE=0,EM=0。

[0086] 由于RE=0,因此第一开关晶体管M1截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于EM=1,因此第二开关晶体管M2导通,以将第一电源信号VDD提供给驱动晶体管M0的第一极S,使其第一极S的电压为第一电源信号VDD的电压Vdd。由于驱动晶体管M0工作处于饱和状态,根据饱和状态电流特性可知,流过驱动晶体管 M0且用于驱动发光器件L发光的工作电流I满足公式: $I=K(V_{GD}-V_{th})^2=K(V_{DA}-V_{D}-V_{th})^2$ ,其中, $V_D$ 代表驱动晶体管M0的第二极D的电压,K为结构参数,相同结构中此数值相对稳定,可以算作常量。这样,工作电流I由第一电源信号VDD通过第二开关晶体管MD的电压,MD的电压,MD的电压,MD的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压,MD0的电压

光器件L的发光。

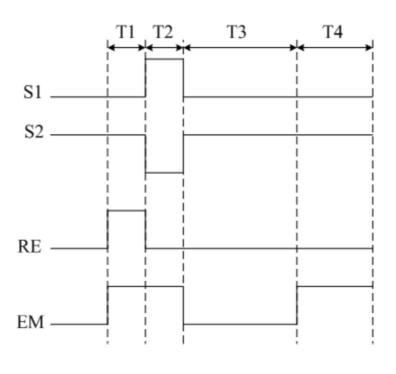

[0087] 实施例二、

[0088] 本实施例对应的阵列基板的结构示意图如图4所示,其针对实施例一中的实施方式进行了变形。下面仅说明本实施例与实施例一的区别之处,其相同之处在此不作赘述。在具体实施时,如图8所示,在发光阶段T3之后,驱动一行发光器件工作还可以包括:非发光阶段T4;其中,在非发光阶段T4,电压控制电路响应于发光控制信号EM,将第一电源信号与驱动晶体管的第一极断开,控制对应的像素电路驱动连接的发光器件停止发光。

[0089] 具体地,对应的电路时序图如图8所示。驱动一行发光器件工作,可以包括:重置阶段T1、数据写入阶段T2、发光阶段T3以及非发光阶段T4。其中,重置阶段T1、数据写入阶段T2、发光阶段T3可以参见实施例一,在此不作赘述。

[0090] 在非发光阶段T4,S1=0,S2=1,RE=0,EM=1。由于RE=0,因此第一开关晶体管M1截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于EM=0,因此第二开关晶体管M2截止。这样,第一电源信号VDD不再通过第二开关晶体管M2与驱动晶体管M0流向发光器件L,从而可以使驱动发光器件L停止发光。这样可以进一步避免上一帧发光时加载于发光器件L的正极上的电压对下一帧发光的影响,进而改善残影现象。

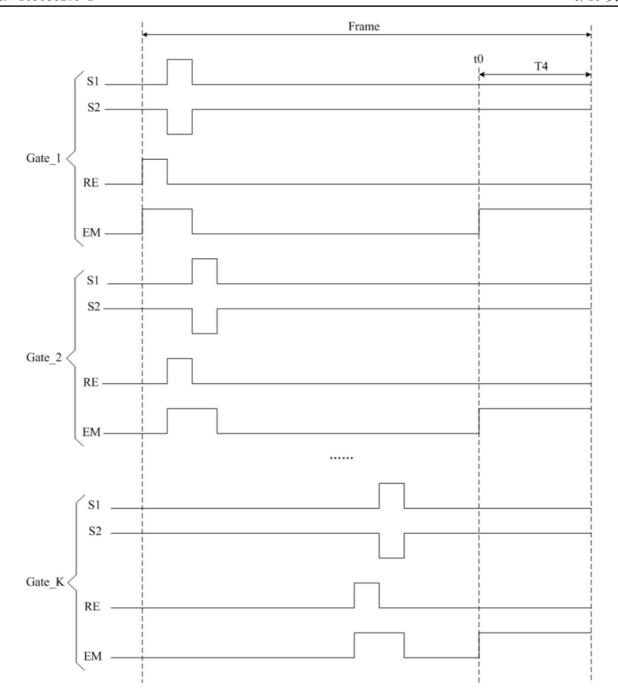

[0091] 实施例三、

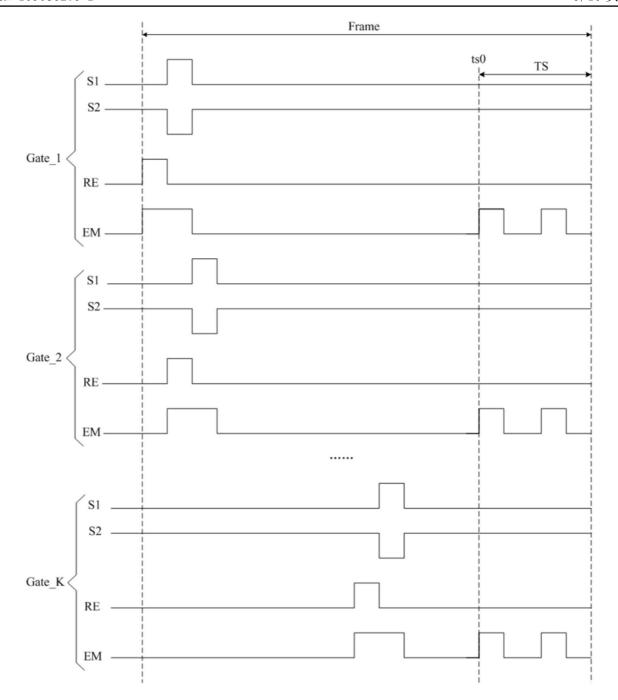

[0092] 在具体实施时,如图9所示,可以在一帧显示时间Frame内,使驱动每一行发光器件工作的非发光阶段T4在相同时间t0开启。

[0093] 具体地,一般阵列基板可以包括K行像素单元,K为正整数。Gate\_k( $1 \le k \le K$ ,且为整数)代表驱动第k行像素单元中像素电路工作的各信号。在一帧显示时间Frame内,可以通过逐行驱动方式,驱动像素电路工作,在驱动第一行像素单元至最后一行像素单元中的发光器件发光以后,再控制每一行像素单元中的发光器件同时停止发光。例如,在一帧显示时间Frame的时长为11.1ms 时,可以使非发光阶段T4占用2ms,其余9.1ms为驱动第一行像素单元至最后一行像素单元中的像素电路发光的时长。

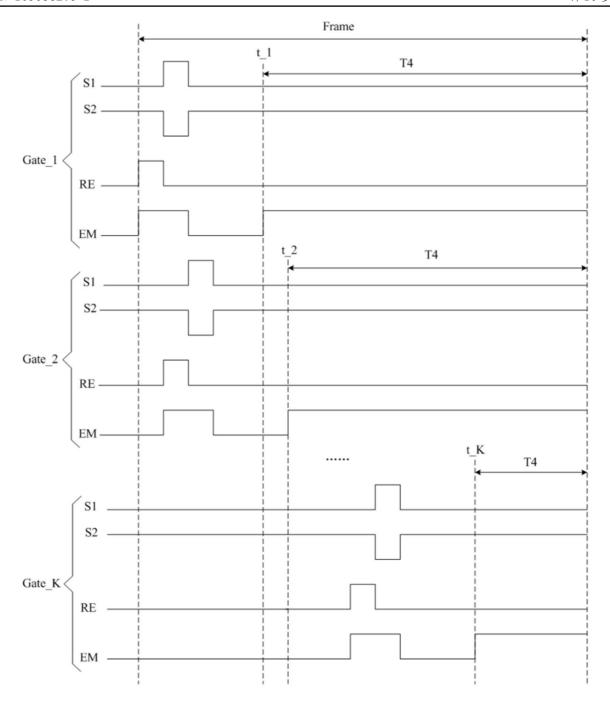

[0094] 实施例四、

[0095] 在具体实施时,如图10所示,在一帧显示时间Frame内,驱动每一行发光器件工作的非发光阶段T4逐行依次开启。在一帧显示时间Frame内,可以通过逐行驱动方式,在驱动第一行像素单元至最后一行像素单元中的像素电路依次工作。

[0096] 具体地,在驱动第一行像素单元中的发光器件发光以后,在时间t\_1时开启进入非发光阶段T4,控制第一行像素电路电连接的第二开关晶体管截止,以控制第一行像素单元中的发光器件停止发光。在驱动第二行像素单元中的发光器件发光以后,在时间t\_2时开启进入非发光阶段T4,控制第二行像素电路电连接的第二开关晶体管截止,以控制第二行像素单元中的发光器件停止发光。在驱动第K行像素单元中的发光器件发光以后,在时间t\_K时开启进入非发光阶段T4,控制第K行像素电路电连接的第二开关晶体管截止,以控制第K行像素单元中的发光器件停止发光。其余依次类推,在此不作赘述。

[0097] 实施例五、

[0098] 本实施例对应的阵列基板的结构示意图如图4所示,其针对实施例一中的实施方式进行了变形。下面仅说明本实施例与实施例一的区别之处,其相同之处在此不作赘述。

[0099] 在具体实施时,如图11所示,在发光阶段T3之后,驱动一行发光器件工作还可以包括:调光阶段TS。调光阶段TS可以包括:至少一个非发光阶段 TS1\_x ( $1 \le x \le X$ ,x和X均为正数,X代表调光阶段具有的非发光阶段的总数,图11以X=2为例)和至少一个发光阶段TS2\_y ( $1 \le y \le Y$ ,y和Y均为正数,Y代表调光阶段具有的发光阶段的总数,图11以Y=2为例);其中,非发光阶段TS1\_x和发光阶段TS2\_y依次交替排列。其中,X可以设置为1、2、3等,Y可以设置为1、2、3等,当然,在实际应用中,不同应用环境对发光器件的亮度的要求不同,因此调光阶段中非发光阶段和发光阶段的数量的具体实施可以根据实际应用环境来设计确定,在此不作限定。

[0100] 具体地,在非发光阶段TS1\_x,电压控制电路响应于发光控制信号,将第一电源信号与驱动晶体管的第一极断开,控制对应的像素电路驱动连接的发光器件停止发光;

[0101] 在发光阶段TS2\_y,电压控制电路响应于发光控制信号,将第一电源信号输出至驱动晶体管的第一极,控制对应的像素电路驱动连接的发光器件发光。这样可以通过设置调光阶段,从而可以有效控制发光器件的亮度。

[0102] 具体地,如图11所示,调光阶段TS可以包括:依次设置的非发光阶段 TS1\_1、发光阶段TS2\_1、非发光阶段TS1\_2、发光阶段TS2\_2。或者,调光阶段也可以包括依次设置的非发光阶段、发光阶段、非发光阶段。在此不作限定。

[0103] 下面以图4为例,结合图11所示的电路时序图对调光阶段TS的工作过程进行说明。在非发光阶段TS1\_1,S1=0,S2=1,RE=0,EM=1。由于RE=0,因此第一开关晶体管M1截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于EM=0,因此第二开关晶体管 M2截止。这样,第一电源信号不再通过第二开关晶体管M2与驱动晶体管M0流向发光器件L,从而使驱动发光器件L停止发光。

[0104] 在发光阶段TS2\_1,S1=0,S2=1,RE=0,EM=0。由于RE=0,因此第一开关晶体管M1截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于EM=1,因此第二开关晶体管M2导通,以将第一电源信号VDD提供给驱动晶体管M0的第一极S。从而使工作电流I 由第一电源信号VDD通过第二开关晶体管M2与驱动晶体管M0流向发光器件L,以驱动发光器件L发光。

[0105] 在非发光阶段TS1\_2,S1=0,S2=1,RE=0,EM=1。由于RE=0,因此第一开关晶体管M1截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于EM=0,因此第二开关晶体管M2截止。这样,第一电源信号不再通过第二开关晶体管M2与驱动晶体管M0流向发光器件L,从而使驱动发光器件L停止发光。

[0106] 在发光阶段TS2\_2,S1=0,S2=1,RE=0,EM=0。由于RE=0,因此第一开关晶体管M1截止。由于S1=0,因此第三开关晶体管M3截止。由于S2=1,因此第四开关晶体管M4截止。由于EM=1,因此第二开关晶体管M2导通,以将第一电源信号VDD提供给驱动晶体管M0的第一极S。从而使工作电流I 由第一电源信号VDD通过第二开关晶体管M2与驱动晶体管M0流向发光器件L,以驱动发光器件L发光。

[0107] 实施例六、

[0108] 在具体实施时,如图12所示,在一帧显示时间Frame内,驱动每一行发光器件工作的调光阶段TS在相同时间ts0开启。

[0109] 具体地,在一帧显示时间Frame内,可以通过逐行驱动方式,驱动像素电路工作,在

驱动第一行像素单元至最后一行像素单元中的发光器件发光以后,再控制每一行像素单元中的发光器件在时间ts0同时进入调光阶段TS。

[0110] 实施例七、

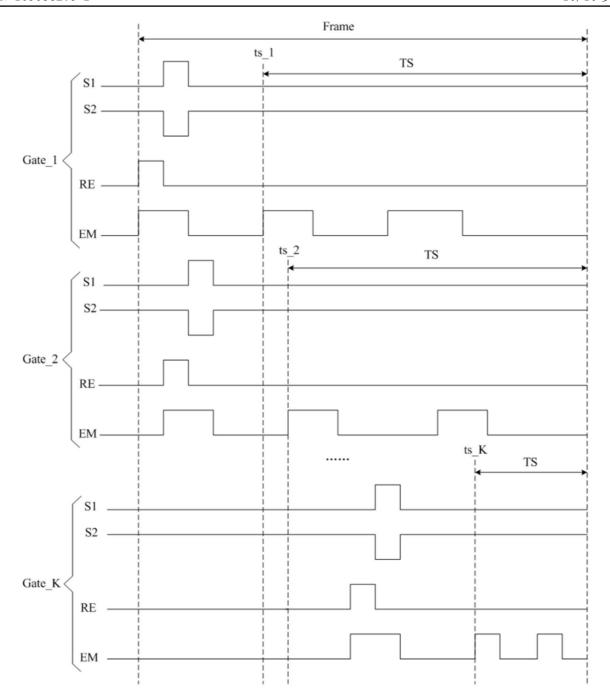

[0111] 在具体实施时,如图13所示,在一帧显示时间Frame内,驱动每一行发光器件工作的调光阶段TS逐行依次开启。

[0112] 具体地,在一帧显示时间Frame内,可以通过逐行驱动方式,在驱动第一行像素单元至最后一行像素单元中的像素电路依次工作。具体地,在驱动第一行像素单元中的发光器件发光以后,在时间ts\_1时开启进入调光阶段TS。在驱动第二行像素单元中的发光器件发光以后,在时间ts\_2时开启进入调光阶段 TS。在驱动第K行像素单元中的发光器件发光以后,在时间t K时开启进入调光阶段TS。其余依次类推,在此不作赘述。

[0113] 实施例八、

[0114] 进一步地,图5所示的阵列基板的结构相比图4,仅是在驱动晶体管M0 的第二极D与发光器件L的正极之间设置有P型的第五开关晶体管M5。该第五开关晶体管M0可以起到对比度钳制器的作用。具体地,在数据信号DA的电压为高灰阶对应的电压(例如高电压)时,即在显示高灰阶画面时,由于第五开关晶体管M5的栅极连接接地端GND,使得第五开关晶体管M5可以在接地端GND的电压和驱动晶体管M0的第二极D的电压的控制下处于开启状态,从而使发光器件L的正极上施加有VDA-Vth,这样使得发光器件L的最大亮度不会受到影响。在数据信号DA的电压为低灰阶(例如低电压)对应的电压时,即在显示低灰阶画面时,由于第五开关晶体管M5的栅极连接接地端GND,使得第五开关晶体管M5不足以在接地端GND的电压和驱动晶体管M0的第二极D的电压的控制下导通,从而可以使流经第五开关晶体管M5的电流非常小,可以相当于驱动晶体管M0的第二极D与发光器件L之间断路,这样使得发光器件L的亮度会达到超级低的水平。这样根据对比度公式可以得出,在这种模式下发光器件L的对比度是最低的。

[0115] 并且,图5所示的阵列基板的结构在其他阶段的工作过程可以分别参见实施例一至实施例七,在此不作赘述。

[0116] 基于同一发明构思,本发明实施例还提供了一种有机发光显示面板,包括本发明实施例提供的阵列基板。该有机发光显示面板解决问题的原理与前述阵列基板相似,因此该有机发光显示面板的实施可以参见前述阵列基板的实施,重复之处在此不再赘述。

[0117] 基于同一发明构思,本发明实施例还提供了一种显示装置,包括本发明实施例提供的上述有机发光显示面板。该显示装置可以为:手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。对于该显示装置的其它必不可少的组成部分均为本领域的普通技术人员应该理解具有的,在此不做赘述,也不应作为对本发明的限制。该显示装置的实施可以参见上述有机发光显示面板的实施例,重复之处不再赘述。

[0118] 本发明实施例提供的阵列基板、驱动方法、有机发光显示面板及显示装置,包括:位于显示区中的多个发光器件与各发光器件连接的像素电路,以及位于非显示区中的多个电压控制电路;其中,一行中至少两个像素电路共用一个电压控制电路,从而可以简化显示区中各像素电路的结构,降低显示区中像素电路的占用面积,从而可以使显示区设置更多的像素电路和发光器件,实现高PPI 的有机发光显示面板。并且,通过电压控制电路在复位

控制信号的控制,将初始化信号输出至驱动晶体管的第一极,控制对应的发光器件复位,从而可以避免上一帧发光时加载于发光器件上电压对下一帧发光的影响,进而改善残影现象。

[0119] 显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

图1

图2

图3a

图3b

图4

图7

图8

图9

图10

图11

图12

图13