(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4851156号

(P4851156)

(45) 発行日 平成24年1月11日(2012.1.11)

(24) 登録日 平成23年10月28日(2011.10.28)

(51) Int.Cl.

F 1

G 11 C 11/406 (2006.01)

G 06 F 12/00 (2006.01)G 11 C 11/34 363 N

G 06 F 12/00 550 B

請求項の数 18 (全 12 頁)

(21) 出願番号 特願2005-307418 (P2005-307418)

(22) 出願日 平成17年10月21日 (2005.10.21)

(65) 公開番号 特開2006-134559 (P2006-134559A)

(43) 公開日 平成18年5月25日 (2006.5.25)

審査請求日 平成20年10月10日 (2008.10.10)

(31) 優先権主張番号 10-2004-0089950

(32) 優先日 平成16年11月5日 (2004.11.5)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeo

ngtong-gu, Suwon-si,

Gyeonggi-do, Republic

of Korea

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100108453

弁理士 村山 靖彦

最終頁に続く

(54) 【発明の名称】リフレッシュ方法、メモリシステム、ダイナミックランダムアクセスメモリ装置、メモリシステムの動作方法及びロジックエンベディッドメモリシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のメモリ装置と第2のメモリ装置を備えた、複数のメモリセルを含む揮発性メモリ装置のリフレッシュ方法であって、

前記第2のメモリ装置から発生されるオートリフレッシュモード活性化命令に応答して前記揮発性メモリ装置の前記第1のメモリ装置のオートリフレッシュモードを活性化させる段階と、

第2のメモリ装置から発生されるオートリフレッシュ命令に応答して前記第1のメモリ装置でオートリフレッシュ動作を実行する段階と、を含み、

前記オートリフレッシュモードが設定されている場合に前記オートリフレッシュ命令の入力時にのみ前記オートリフレッシュ命令に応答して前記オートリフレッシュ動作が実行されることを特徴とするリフレッシュ方法。

## 【請求項 2】

前記第2のメモリ装置からホスト装置へバス占有要請を送る段階と、

前記第2のメモリ装置内で前記オートリフレッシュモード活性化命令と前記オートリフレッシュ命令を生成する段階と、

前記第2のメモリ装置から前記揮発性メモリ装置へ前記バスを通じて前記オートリフレッシュモード活性化命令と前記オートリフレッシュ命令とを伝送する段階と、をさらに含むことを特徴とする請求項1に記載のリフレッシュ方法。

## 【請求項 3】

10

20

前記ホストから前記バス占有要請が承認されるとき、前記オートリフレッシュモード活性化命令は、前記第2のメモリ装置から前記揮発性メモリ装置へ伝送されることを特徴とする請求項2に記載のリフレッシュ方法。

#### 【請求項4】

前記オートリフレッシュ命令は、前記第2のメモリ装置から前記揮発性メモリ装置へ前記オートリフレッシュモード活性化命令が伝送された後、前記第2のメモリ装置から前記揮発性メモリ装置へ伝送されることを特徴とする請求項2に記載のリフレッシュ方法。

#### 【請求項5】

前記オートリフレッシュ動作の終了に応答して前記揮発性メモリ装置の前記オートリフレッシュモードを非活性化させることを特徴とする請求項1に記載のリフレッシュ方法。 10

#### 【請求項6】

メモリセルアレイと前記メモリセルアレイのメモリセルの上でオートリフレッシュ動作を開始する第1の回路を備える第1のメモリ装置と、

前記第1のメモリ装置にオートリフレッシュモード活性化命令を生成して提供するオートリフレッシュ制御回路を備えた第2のメモリ装置と、を含み、

前記第1のメモリ装置は、

前記オートリフレッシュモード活性化命令に応答して前記第1のメモリ装置のオートリフレッシュモードを設定するモード検出部と、

前記オートリフレッシュモードが設定された場合、オートリフレッシュ命令に応答して前記オートリフレッシュ動作を開始する第1の回路内に構成された命令デコーダと、をさらに含み、 20

前記オートリフレッシュ制御回路を含む第2のメモリ装置は、

前記オートリフレッシュ制御回路に提供される前記オートリフレッシュ動作と関連した情報を貯蔵する不揮発性メモリアレイと、

前記オートリフレッシュ制御回路にタイミング信号を提供するタイミング信号発生部と、をさらに含み、

前記オートリフレッシュ制御回路は、前記オートリフレッシュ命令を生成し、

前記第2のメモリ装置から発生されるオートリフレッシュ活性化命令に応答して前記第1のメモリ装置をオートリフレッシュモードに設定した後、前記第2のメモリ装置から発生されるオートリフレッシュ命令に応答して前記第1のメモリ装置でオートリフレッシュを実行することを特徴とするメモリシステム。 30

#### 【請求項7】

前記モード検出部は、前記オートリフレッシュモード活性化命令に応答して第1の制御信号を活性化して前記オートリフレッシュモードを設定することを特徴とする請求項6に記載のメモリシステム。

#### 【請求項8】

前記第1のメモリ装置は、ダイナミックランダムアクセスメモリであり、前記オートリフレッシュ制御回路は、不揮発性メモリセルのアレイから構成される第2のメモリ装置の一部であることを特徴とする請求項6に記載のメモリシステム。

#### 【請求項9】

前記第2のメモリ装置は、前記不揮発性メモリアレイから前記オートリフレッシュ動作と関連した情報が入力される貯蔵ブロックと、発振部から構成された前記タイミング信号発生部と、を含むことを特徴とする請求項6に記載のメモリシステム。 40

#### 【請求項10】

オートリフレッシュモード活性化命令を発生し、第1のメモリ装置であるダイナミックランダムアクセスメモリ装置のオートリフレッシュモードを設定し、オートリフレッシュ命令に応答してオートリフレッシュイネーブル信号を活性化し、オートリフレッシュモードを設定するオートリフレッシュ制御手段を備えた第2のメモリ装置と、

前記オートリフレッシュイネーブル信号に応答してオートリフレッシュ動作を実行するよう構成されたメモリコアを備えた第1のメモリ装置と、を含み、 50

前記オートリフレッシュ制御手段は、

前記オートリフレッシュモード活性化命令に応答して第1の制御信号を活性化させるモード検出部と、

前記第1の制御信号が活性化時前記オートリフレッシュ命令に応答して前記オートリフレッシュイネーブル信号を発生する命令デコーダと、を含むことを特徴とするダイナミックランダムアクセスメモリ装置。

**【請求項11】**

前記命令デコーダは、前記オートリフレッシュ動作が終了されたとき、第2の制御信号を活性化させることを特徴とする請求項10に記載のダイナミックランダムアクセスメモリ装置。10

**【請求項12】**

前記モード検出部は、前記オートリフレッシュモード活性化命令に応答して前記オートリフレッシュモードを示す情報を貯蔵し、前記貯蔵された情報は、前記第2の制御信号の活性化に応答して前記モード検出部によって再初期化されることを特徴とする請求項11に記載のダイナミックランダムアクセスメモリ装置。11

**【請求項13】**

第1のメモリ装置、第2のメモリ装置、そしてホストを含むメモリシステムの動作方法であって、

前記第2のメモリ装置から前記第1のメモリ装置へオートリフレッシュモード活性化命令を伝送する段階と、20

前記オートリフレッシュモード活性化命令に応答して前記第1のメモリ装置のオートリフレッシュモードを設定する段階と、

前記第2のメモリ装置から前記第1のメモリ装置へオートリフレッシュ命令を伝送する段階と、

前記第1のメモリ装置の前記オートリフレッシュモードの設定と前記オートリフレッシュ命令の組合に応答して前記第1のメモリ装置のメモリセル上でオートリフレッシュ動作を実行する段階と、を含むことを特徴とするメモリシステムの動作方法。21

**【請求項14】**

前記第2のメモリ装置から前記ホストへバス占有要請を送る段階をさらに含み、前記オートリフレッシュモード活性化命令は、前記バス占有要請が承認された後、前記第2のメモリ装置から前記第1のメモリ装置へ伝送されることを特徴とする請求項13に記載のメモリシステムの動作方法。30

**【請求項15】**

前記オートリフレッシュモードが設定されない場合、前記第1のメモリ装置は、前記オートリフレッシュ命令に応答しないことを特徴とする請求項14に記載のメモリシステムの動作方法。

**【請求項16】**

第1のメモリ、第2のメモリ、そしてホストを含むメモリシステムの動作方法であって、

前記第1のメモリのオートリフレッシュ動作が必要であるかどうかを前記第2のメモリにおいて決定する段階と、40

前記第2のメモリから前記ホストへバス占有を要請する段階と、

前記バス占有要請が承認された後、前記第2のメモリから前記第1のメモリへモード設定値とモード設定命令とを伝送する段階と、

前記モード設定値と前記モード設定命令に応答して前記第1のメモリのオートリフレッシュモードを設定する段階と、

前記第2のメモリから前記第1のメモリへオートリフレッシュ命令を伝送する段階と、

前記第1のメモリから前記オートリフレッシュ命令を実行する段階と、を含むことを特徴とするメモリシステムの動作方法。

**【請求項17】**

10

20

30

40

50

第1のメモリ装置と、第2のメモリ装置と、を備え、

前記第2のメモリ装置は、

発振部と、

前記第2のメモリ装置上で前記第1のメモリ装置のオートリフレッシュ動作が必要であるか否かを、前記発振部から発生された発振信号に基づいて決定するオートリフレッシュ制御部と、

前記オートリフレッシュ制御部からホストへバス占有要請を伝送し、前記ホストから前記オートリフレッシュ制御部へバス占有要請承認信号を伝送するインターフェース部と、を含み、

前記オートリフレッシュ制御部は、オートリフレッシュモード設定命令とオートリフレッシュ命令を発生し、10

前記第2のメモリ装置から発生されるオートリフレッシュ活性化命令に応答して第1のメモリ装置をオートリフレッシュモードに設定した後、前記第2のメモリ装置から発生されるオートリフレッシュ命令に応答して第1のメモリ装置でオートリフレッシュを実行することを特徴とするロジックエンベディッドメモリシステム。

#### 【請求項18】

前記第2のメモリ装置上で前記オートリフレッシュ動作が実行された場合、前記オートリフレッシュ制御部の決定によって、前記第2のメモリ装置の前記オートリフレッシュ動作に使用されるタイミングと関連された情報を貯蔵する不揮発性メモリをさらに含むことを特徴とする請求項17に記載のロジックエンベディッドメモリシステム。20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、電子システムに関するものであり、より詳しくは、オートリフレッシュ機能が必要なメモリを含むシステムに関するものである。

##### 【背景技術】

##### 【0002】

ダイナミックランダムアクセスメモリ(DRAM)セルのような揮発性メモリセルに貯蔵されたデータは短時間に消失するので、データは周期的にリフレッシュされなければならない。従って、一つ又はそれより多い揮発性メモリセルを含む集積回路は、周期的にリフレッシュサイクルを実行しなければならない。30

##### 【0003】

一般的なリフレッシュサイクル間、感知増幅器は、メモリセルに貯蔵されたデータを読み取り、同一なデータをメモリセルに再び書き込む。より詳しく、メモリセルは、電圧レベルのような信号レベルを貯蔵し、この信号レベルは、貯蔵されたデータの値を示す。例えば、電源電圧の電圧レベルは、ロジック1のデータ値を示し、接地電圧の電圧レベルは、ロジック0のデータ値を示す。不幸にも、メモリセル漏洩(memory-cell leakage)のようなよく知られた現象は、時間の経過によって信号レベルを低下させる。信号レベルが維持されなければ、信号レベルがメモリセルに本来貯蔵されたデータ値から他のデータ値を示すレベルまで信号レベルが低下しうる。例えば、電源電圧(ロジック1)の電圧レベルは、接地電圧に向かって低くなる。信号レベルが維持されなければ、電源電圧の電圧レベルは、ロジック1の代わりにロジック0を示す接地電圧に十分に近接する。貯蔵された信号レベルを維持するために、メモリセルを含む集積回路は、感知増幅器にセルの信号レベルを入力し、感知増幅器によってその入力信号のレベルを最大レベルまで増幅し、最大信号レベルをセルに提供するリフレッシュサイクルを実行する。40

##### 【0004】

揮発性メモリセルを含む集積回路を備えた電子システムは、メモリセルをリフレッシュするようにオートリフレッシュ命令を周期的に発生する。例えば、集積回路は、メモリセルの行とリフレッシュされる行とを指すリフレッシュアドレスカウンタ(又はアドレス発生器)を含む。各オートリフレッシュ命令は、集積回路に各オートリフレッシュサイクル50

を実行させる。各オートリフレッシュサイクルの間に集積回路がアドレスした行のメモリセルをリフレッシュし、カウンタを1だけ増加／減少させる。全ての行がリフレッシュされた後、カウンタは集積回路が続けて行をリフレッシュできるように初期化される。

#### 【0005】

電子システムがメモリセルの貯蔵されたデータを失わない程度にしばしばオートリフレッシュ命令を発生することを保障するために、メモリセルの連続的なリフレッシュの間に経過する最大リフレッシュ周期が決められる。例えば、集積回路が64ms毎に少なくとも一度各メモリセルをリフレッシュしなければならなく、4096(4K)個の行のメモリセルを含み、各リフレッシュサイクル間に全ての行をリフレッシュしなければならないと仮定しよう。メモリセルがデータを維持することを保障するために、電子システムは64ms毎に少なくとも4096回のオートリフレッシュ命令を実行しなければならない。10

#### 【0006】

前述したように、電子システムは、オートリフレッシュ命令を周期的に生成するので、ソフトウェアを基盤としたオートリフレッシュ制御ロジックが電子システムに提供されなければならない。これは、電子システムのソフトウェア負担だけではなく、ハードウェア負担が加重されることを意味する。もしオートリフレッシュ命令を生成する機能がホストから除去されれば、電子システムのハードウェア負担だけではなく、ソフトウェア負担が軽減できる。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

20

#### 【0007】

本発明の技術的課題は、オートリフレッシュ命令に選別的に動作するDRAM及びその動作方法を提供するところにある。

#### 【0008】

本発明の他の技術的課題は、DRAMのオートリフレッシュ動作を制御するロジックエンベディッドメモリ及びその動作方法を提供するところにある。

#### 【0009】

本発明のさらに他の技術的課題は、ホストからのオートリフレッシュ命令なしでDRAMのオートリフレッシュ動作が実行されるメモリシステム及びその動作方法を提供するところにある。30

#### 【課題を解決するための手段】

#### 【0010】

前述した技術的課題を達成するための本発明に従う多数のメモリセルを含む揮発性メモリ装置のリフレッシュ方法は、オートリフレッシュモード活性化命令に応答して揮発性メモリ装置のオートリフレッシュモードを活性化させる段階と、オートリフレッシュ命令に応答して多数のメモリセルのオートリフレッシュ動作を実行する段階と、を含むことを特徴とする。

#### 【0011】

本発明に従うメモリシステムは、メモリセルアレイとメモリセルアレイのメモリセル上でオートリフレッシュ動作を初期化する第1の回路を備える第1のメモリ装置と、第1のメモリ装置にオートリフレッシュモード活性化命令を生成して提供するオートリフレッシュ制御回路と、を含むことを特徴とする。40

#### 【0012】

本発明に従うダイナミックランダムアクセスメモリ装置は、オートリフレッシュモード活性化命令に応答してダイナミックランダムアクセスメモリ装置のオートリフレッシュモードを設定し、オートリフレッシュ命令に応答してオートリフレッシュイネーブル信号を活性化し、オートリフレッシュモードを設定するオートリフレッシュ制御手段と、オートリフレッシュイネーブル信号に応答してオートリフレッシュ動作を実行するように構成されたメモリコアと、を含む。

#### 【0013】

50

本発明に従う第1のメモリ装置、第2のメモリ装置、そしてホストを含むメモリシステムの動作方法は、第2のメモリ装置から第1のメモリ装置へオートリフレッシュモード活性化命令を伝送する段階と、オートリフレッシュモード活性化命令に応答して第1のメモリ装置のオートリフレッシュモードを設定する段階と、第2のメモリ装置から第1のメモリ装置へオートリフレッシュ命令を伝送する段階と、第1のメモリ装置のオートリフレッシュモードの設定とオートリフレッシュ命令の組合に応答して第1のメモリ装置のメモリセル上でオートリフレッシュ動作を実行する段階と、を含むことを特徴とする。

#### 【0014】

本発明に従う第1のメモリ、第2のメモリ、そしてホストを含むメモリシステムの動作方法は、第1のメモリのオートリフレッシュ動作が要求されるとき、第2のメモリを決定する段階と、第2のメモリからホストへバス占有を要請する段階と、バス占有要請が承認された後、第2のメモリから第1のメモリへモード設定値とモード設定命令とを伝送する段階と、モード設定値とモード設定命令に応答して第1のメモリのオートリフレッシュモードを設定する段階と、第2のメモリから第1のメモリへオートリフレッシュ命令を伝送する段階と、第1のメモリでオートリフレッシュ命令を実行する段階と、を含むことを特徴とする。10

#### 【0015】

本発明に従うロジックエンベディッドメモリは、発振部と、第2のメモリ装置上でオートリフレッシュ動作が実行された場合、発振部から発生された発振信号に基づいて決定するオートリフレッシュ制御部と、そしてオートリフレッシュ制御部からホストへバス占有要請を伝送し、ホストからオートリフレッシュ制御部へバス占有要請承認信号を伝送するインターフェース部と、を含み、オートリフレッシュ制御部は、オートリフレッシュモード設定命令とオートリフレッシュ命令とを発生することを特徴とする。20

#### 【発明の効果】

#### 【0016】

前述したように、ホストのオートリフレッシュ機能を除去することによって、ホストのハードウェア負担及びソフトウェア負担を縮めることができる。

#### 【発明を実施するための最良の形態】

#### 【0017】

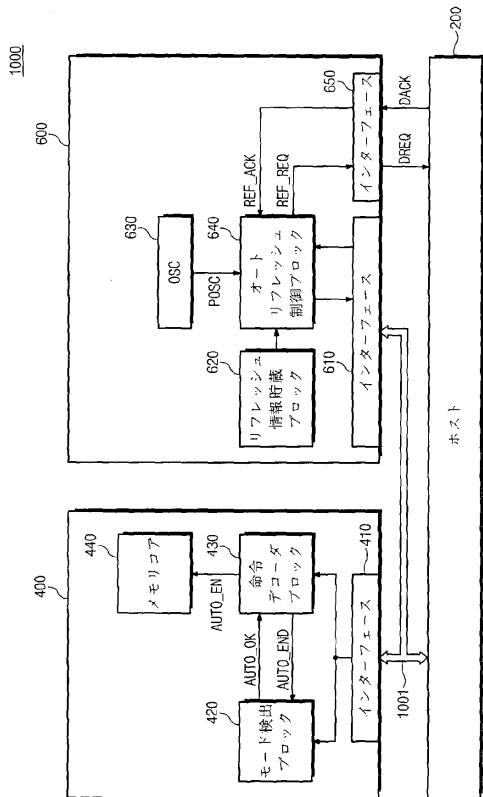

以下、添付した図面を参照して本発明の好適な実施形態を詳細に説明する。図1は、本発明の好適な実施形態のメモリシステムを概略的に示すブロック図である。30

#### 【0018】

図1を参照すると、本発明の好適な実施形態のメモリシステム1000は、ホスト（又はチップセットという）200と、第1のメモリ400と、第2のメモリ600と、を含む。この実施形態において、第1のメモリ400は、オートリフレッシュ機能を有するダイナミックランダムアクセスメモリ（DRAM）であり、第2のメモリ600は、不揮発性メモリとしてNANDフラッシュメモリである。第1及び第2のメモリ400, 600は、マルチチップパッケージ（Multi-Chip Package；MCP）を構成するように具現できる。又は、第1及び第2のメモリ400, 600は、個別的な集積回路としてシステムに適用できる。なお、本発明がこのようなものに限定されないことは当業者に自明である。40

#### 【0019】

第1のメモリ400は、バス1001を通じてホスト200及び第2のメモリ600と連結されている。ここで、バス1001は、制御信号ライン（/CS、/CAS、/RAS、/WE、CKEなど）と、アドレス信号ラインと、データ信号ラインと、を含む。第1のメモリ400は、インターフェースブロック410と、モード検出ブロック420と、命令デコーダブロック430と、メモリコア440と、を含む。インターフェースブロック410は、バス1001を通じて伝達される情報（例えば、命令、アドレス、データなど）が入力され、入力された情報を第1のメモリ400内に提供する。

#### 【0020】

50

モード検出ブロック420は、インターフェースブロック410を通じて提供されるモード設定値（オートリフレッシュモードを設定するための値）を貯蔵するように構成される。例えば、モード検出ブロック420は、オートリフレッシュモードを設定するためのモード設定命令の入力に応答してモード設定値を貯蔵し、制御信号AUTO\_OKを活性化させる。

#### 【0021】

モード設定値は、当業者によく知られたように、アドレスピンを通じて提供されうる。又は、モード設定値はデータピンを通じて提供されうる。よく知られたように、モード設定命令は、/CS、/RAS、/CAS、そして/WEのような制御信号の組合に表現されうる。例えば、/CS、/RAS、/CAS、/WEのような制御信号が全てローに維持されるとき、こうした制御信号の組合がモード設定命令を示す。10

#### 【0022】

命令デコーダブロック430は、制御信号AUTO\_OKに応答して動作し、インターフェースブロック410を通じて入力される命令をデコーディングするように構成される。例えば、制御信号AUTO\_OKが活性化されるとき、命令デコーダブロック430は、インターフェースブロック410を通じて入力されるオートリフレッシュ命令に応答してオートリフレッシュイネーブル信号AUTO\_ENを活性化させる。オートリフレッシュイネーブル信号AUTO\_ENが活性化されるとき、メモリコア440では、一又は複数の行のメモリセルがリフレッシュされる。制御信号AUTO\_OKが非活性化されている場合、インターフェースブロック410を通じてオートリフレッシュ命令が入力されても、命令デコーダブロック430は、オートリフレッシュイネーブル信号AUTO\_ENを活性化させない。20

#### 【0023】

また、命令デコーダブロック430は、オートリフレッシュ動作が完了（又は終了）されるとき、制御信号AUTO\_ENDを活性化させる。制御信号AUTO\_ENの活性化時モード検出ブロック420が初期化される。すなわち、モード検出ブロック420に貯蔵された情報は初期化される。結果的に、命令デコーダブロック430は、制御信号AUTO\_OKが活性化されるときオートリフレッシュ命令に応答してオートリフレッシュイネーブル信号AUTO\_ENを活性化させる。

#### 【0024】

この実施形態において、オートリフレッシュ命令を除外した他の命令（例えば、アクティブ命令、読み取り／書き取り命令、セルフリフレッシュ命令など）がインターフェースブロック410を通じて入力されるとき、命令デコーダブロック430は、制御信号AUTO\_OKの活性化／非活性化に関係なく入力された命令を正常に処理するように構成される。30

#### 【0025】

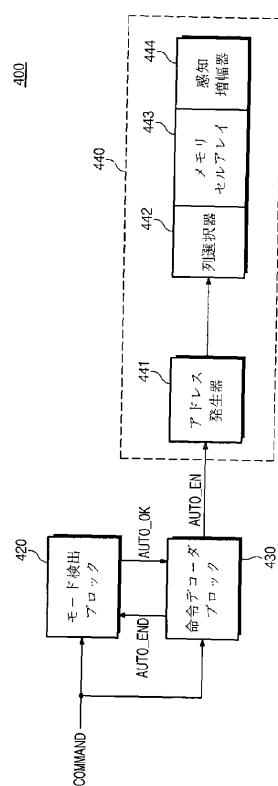

第1のメモリ400のメモリコア440は、図2に示されたように、アドレス発生器441と、行選択器442と、メモリセルアレイ443と、そして感知增幅器444と、を含む。アドレス発生器441は、オートリフレッシュイネーブル信号AUTO\_ENの活性化時毎に行アドレスを1だけ増加／減少させ、行選択器442は、アドレス発生器441によって生成された行アドレス（又はリフレッシュアドレス）に応答してメモリセルアレイ443の行のうち一又は複数の行を選択する。感知增幅器444は、選択された行のメモリセルからデータを読み取り、外部への出力なしで読み取られたデータを選択された行のメモリセルに再び書き込む。すなわち、選択された行のメモリセルがリフレッシュされる。図面には示されないが、メモリコア440には、よく知られた構成要素（例えば、入出力回路、列選択回路など）がさらに提供されること、当業者に自明である。40

#### 【0026】

再び図1を参照すると、第2のメモリ600は、バス1001を通じて第1のメモリ400に連結されている。第2のメモリ600は、第1のインターフェースブロック610と、リフレッシュ情報貯蔵ブロック620と、発振ブロック630と、オートリフレッシ50

ユ制御ブロック 640 と、第2のインターフェースブロック 650 と、を含む。図面には示されないが、第2のメモリ 600 には、不揮発性メモリセルのアレイ、アレイの読み出し／書き込み動作を制御する制御ブロック、ホスト 200 とのインターフェースのためのインターフェースブロックがさらに提供されうる。第2のメモリ 600 には、揮発性メモリセルのアレイ及びアレイの読み出し／書き込み動作を制御する制御ブロックが提供されてもよい。第2のメモリ 600 が不揮発性メモリであれば、リフレッシュ情報貯蔵ブロック 620 に貯蔵された情報は、第2のメモリ 600 に提供される不揮発性メモリのアレイ（図示せず）に貯蔵され、不揮発性メモリセルのアレイに貯蔵されたリフレッシュ情報は、パワーアップ時に自動的にリフレッシュ情報貯蔵ブロック 620 に伝送されうる。又は、リフレッシュ情報貯蔵ブロック 620 に貯蔵された情報は、パワーアップ時にホスト 200 に提供されうる。10

#### 【0027】

リフレッシュ情報貯蔵ブロック 620 は、オートリフレッシュ動作に必要な情報（例えば、オートリフレッシュ時間（ $t_{REF}$ ）、リフレッシュ回数など）を貯蔵するように構成される。発振ブロック 630 は、パワーアップ後にオートリフレッシュ動作のための発振信号 POSC を生成するように構成される。

#### 【0028】

オートリフレッシュ制御ブロック 640 は、リフレッシュ情報貯蔵ブロック 620 からのオートリフレッシュ情報及び発信信号 POSC に応答してモード設定命令及びオートリフレッシュ命令を発生する。例えば、オートリフレッシュ制御ブロック 640 は、発振信号 POSC に応答してオートリフレッシュ動作が実行されるべきであるか否かを判別し、判別結果によってリフレッシュ要求信号 REF\_\_REQ を発生する。すなわち、第1のメモリ 400 についてのオートリフレッシュ動作が実行されるべきである場合、オートリフレッシュ制御ブロック 640 は、リフレッシュ要求信号 REF\_\_REQ を発生する。20

#### 【0029】

リフレッシュ要求信号 REF\_\_REQ についての応答としてリフレッシュ承認信号 REF\_\_ACK が入力されるとき、オートリフレッシュ制御ブロック 640 は、モード設定値と共にモード設定命令を発生し、所定時間（例えば、2 - クロックサイクル）後にオートリフレッシュ命令を連続的に発生する。オートリフレッシュ制御ブロック 640 から生成されたモード設定値及びモード設定命令は、バス 1001 を通じて第1のメモリ 400 へ同時に（又は連続的に）伝送される。第1のメモリ 400 のモード検出ブロック 420 は、モード設定命令に応答してモード設定値を貯蔵する。第2のインターフェースブロック 650 は、リフレッシュ要求信号 REF\_\_REQ をバス要求信号 DREQ でホスト 200 に出力し、ホスト 200 からのバス承認信号 DACK をリフレッシュ承認信号 REF\_\_ACK としてオートリフレッシュ制御ブロック 640 に出力する。30

#### 【0030】

オートリフレッシュ動作を制御するためのロジックを含むので、第2のメモリ 600 は、“ロジックエンベディッドメモリ（logic embedded memory）”という。

#### 【0031】

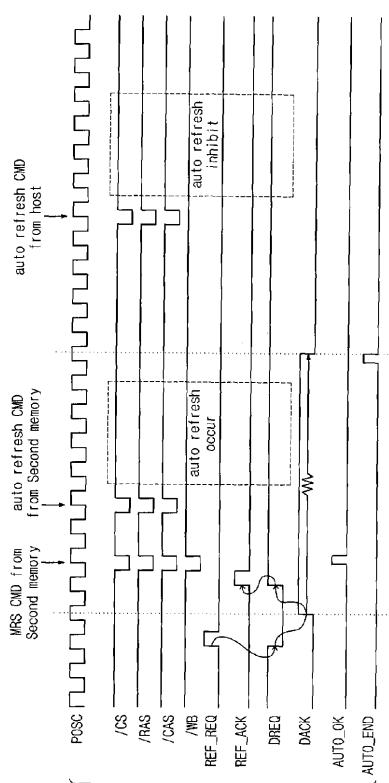

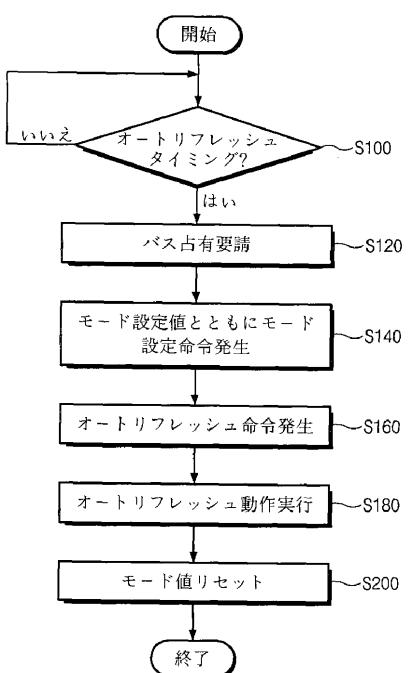

図3は、本発明の好適な実施形態のメモリシステムのオートリフレッシュ動作を説明するためのタイミング図であり、図4は、本発明の好適な実施形態のメモリシステムのオートリフレッシュ動作を説明するための流れ図である。以下、本発明の好適な実施形態のメモリシステムのオートリフレッシュ動作が参照図面に基づいて詳細に説明される。40

#### 【0032】

第2のメモリ 600 のオートリフレッシュ制御ブロック 640 は、発振ブロック 630 からの発振信号 POSC に応答して第1のメモリ 400 のオートリフレッシュ動作が必要であるか否か（又はオートリフレッシュタイミング）を判別する（S100）。この際、オートリフレッシュ制御ブロック 640 は、リフレッシュ情報貯蔵ブロック 620 に貯蔵されたオートリフレッシュ情報に基づいてオートリフレッシュ時間（又はオートリフレ50

シュータイミング)を判断する。例えば、オートリフレッシュ制御ブロック640は、発振信号POS Cをカウントし、カウントされた値がオートリフレッシュ時間に到達したか否かを判断する。第1のメモリ400についてのオートリフレッシュ動作が必要である場合、第2のメモリ600は、ホスト200に対してバス占有を要請する(S120)。具体的には、オートリフレッシュ制御ブロック640は、リフレッシュ要求信号REF\_REQをパルスとして生成し、インターフェースブロック650は、リフレッシュ要求信号REF\_REQに応答してバス要求信号DREQをローに活性化させる。ホスト200は、バス要求信号DREQの活性化に応答してバス承認信号ACKをハイに活性化させる。インターフェースブロック650は、バス承認信号ACKの活性化に応答してリフレッシュ承認信号REF\_ACKをパルスとして生成する。

10

#### 【0033】

オートリフレッシュ制御ブロック640は、リフレッシュ承認信号REF\_ACKの活性化に応答してモード設定値と共にモード設定命令(それがローに維持される/CS、/WE、/RAS、/CASの組合)を発生する(S140)。モード設定値及びモード設定命令は、第1のインターフェースブロック610を通じてバス1001上に載せられ、バス1001に載せられたモード設定値及びモード設定命令は、第1のメモリ400のインターフェースブロック410を通じてモード検出ブロック420に伝達される。モード検出ブロック420は、モード設定命令に応答してモード設定値を貯蔵することと同時に制御信号AUTO\_OKを活性化させる。その後、オートリフレッシュ制御ブロック630は、オートリフレッシュ命令を発生する(S160)。オートリフレッシュ命令は、インターフェースブロック610、バス1001、そしてインターフェースブロック410を通じて命令デコーダブロック430に伝達される。これにより、第1のメモリ400についてのオートリフレッシュ動作が実行される(S180)。

20

#### 【0034】

すなわち、制御信号AUTO\_OKの活性化時、命令デコーダブロック430は、入力されたオートリフレッシュ命令に応答してオートリフレッシュイネーブル信号AUTO\_ENをパルスとして発生する。これにより、メモリコア440で一又は複数の行のメモリセルがリフレッシュされる。

#### 【0035】

リフレッシュ時間が経過した後、命令デコーダ回路430は、制御信号AUTO\_ENを活性化させる(S200)。これにより、モード検出ブロック420が初期化される。すなわち、制御信号AUTO\_OKが非活性化される。以後、オートリフレッシュ動作が要求されるとき毎に、オートリフレッシュ制御ブロック630は、前述したような同一な方式にバス要請動作、モード設定動作、オートリフレッシュ動作を実行する。

30

#### 【0036】

ホスト200がオートリフレッシュ命令を発生すれば、オートリフレッシュ命令は第1のメモリ400のモード検出ブロック420に伝達される。この際、オートリフレッシュ命令の入力以前にモード検出ブロック420が前述したモード設定値に設定されないので、制御信号AUTO\_OKは非活性化状態に維持される。これは、命令デコーダブロック430がホスト200から提供されたオートリフレッシュ命令に応答しないことを意味する。すなわち、ホスト200によって生成されたオートリフレッシュ命令は、第1のメモリ400で認識されなく、その結果ホスト200で要請されたオートリフレッシュ動作は無視される。

40

#### 【0037】

結果的に、本発明の好適な実施形態のメモリシステムの場合、オートリフレッシュ命令を生成する機能をホスト200から除去することができる。これは、ホスト200のハードウェア負担だけではなく、ソフトウェア負担が軽減されることを意味する。ホスト200がオートリフレッシュ機能を有する場合においても、第1のメモリ400のオートリフレッシュ動作は第2のメモリ600から提供されるオートリフレッシュ命令に応じて実行されうる。すなわち、本発明の好適な実施形態のメモリシステムには、オートリフレッシュ

50

ユ機能を有するホストだけではなく、オートリフレッシュ機能を有しないホストにも適用することができる。

【0038】

この実施形態において、モード検出ブロック420から生成される制御信号AUTO\_OKはパルスとして生成される。これに反して、制御信号AUTO\_OKがモード設定命令の入力時活性化され、制御信号AUTO\_ENDの活性化時非活性化されるようにモード検出ブロック420を具現することが可能である。こうした場合、命令デコーダブロック430は、制御信号AUTO\_OKの活性化区間中オートリフレッシュ命令が入力される。

【0039】

以上、添付した図面を参照して本発明の好適な実施形態を説明したが、当業者であれば、本発明の技術的思想や必須的な特徴を変更せずに他の具体的な形態で実施されうることを理解することができる。したがって、上述した好適な実施形態は、例示的なものであり、限定的なものではないと理解されるべきである。

【図面の簡単な説明】

【0040】

【図1】本発明の好適な実施形態のメモリシステムを概略的に示すブロック図である。

【図2】図1に示された第1のメモリを概略的に示すブロック図である。

【図3】本発明の好適な実施形態のメモリシステムの動作を説明するためのタイミング図である。

【図4】本発明の好適な実施形態のメモリシステムの動作を説明するための流れ図である。

【符号の説明】

【0041】

200 ホスト

400 第1のメモリ

410, 610, 650 インターフェース

420 モード検出ブロック

430 命令デコーダブロック

440 メモリコア

620 リフレッシュ情報貯蔵ブロック

630 発振ブロック

640 オートリフレッシュ制御ブロック

10

20

30

【図1】

【図2】

【図3】

【 図 4 】

---

フロントページの続き

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 曹成奎

大韓民国京畿道龍仁市器興邑書川里ヒュンダイアパート イヒュンタウン ヒュンダイホームタウ

ン105-301

審査官 滝谷 亮一

(56)参考文献 特開2004-022123(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/406

G 06 F 12/00