(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4697397号

(P4697397)

(45) 発行日 平成23年6月8日(2011.6.8)

(24) 登録日 平成23年3月11日(2011.3.11)

(51) Int.Cl.

F 1

|             |           |            |     |

|-------------|-----------|------------|-----|

| HO1L 33/32  | (2010.01) | HO1L 33/00 | 186 |

| HO1L 27/04  | (2006.01) | HO1L 27/04 | H   |

| HO1L 21/822 | (2006.01) | HO1L 27/15 | A   |

| HO1L 27/15  | (2006.01) |            |     |

請求項の数 3 (全 28 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-39649 (P2005-39649)    |

| (22) 出願日  | 平成17年2月16日 (2005.2.16)        |

| (65) 公開番号 | 特開2006-228904 (P2006-228904A) |

| (43) 公開日  | 平成18年8月31日 (2006.8.31)        |

| 審査請求日     | 平成20年1月11日 (2008.1.11)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000106276<br>サンケン電気株式会社<br>埼玉県新座市北野3丁目6番3号 |

| (74) 代理人  | 100072154<br>弁理士 高野 則次                     |

| (72) 発明者  | 佐藤 純治<br>埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内       |

| (72) 発明者  | 田嶋 未来雄<br>埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内      |

| (72) 発明者  | 李 哲次<br>埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内        |

最終頁に続く

(54) 【発明の名称】複合半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体発光素子部とこの半導体発光素子部を過電圧から保護するための保護素子部とを含む複合半導体装置であって、

前記半導体発光素子部は、一方の主面と他方の主面とを有し且つ導電性を有し且つ第1導電型を有する半導体基板と、互いに対向する第1及び第2の主面と前記第1の主面から前記第2の主面に至る傾斜側面とを有し且つ前記第2の主面が前記半導体基板の一方の主面に電気的及び機械的に結合されている発光半導体領域と、前記発光半導体領域の前記第1の主面に配置された第1の電極と、前記半導体基板に接続された第2の電極とを備え、前記保護素子部は、前記半導体基板の延長部分と前記発光半導体領域の前記傾斜側面に光透過性を有する絶縁膜を介して配置された光透過性を有する第2導電型半導体膜とから成り、

前記第2導電型半導体膜の一端部分は前記半導体基板の前記延長部分にp-n接合接觸し、前記第2導電型半導体膜の他端部分は前記第1の電極に接続され、

前記第1の電極は光透過性を有し、

前記発光半導体領域は前記半導体基板の一方の主面上に気相成長された半導体又は前記半導体基板に熱圧着で貼り合わせた半導体からなることを特徴とする複合半導体装置。

## 【請求項 2】

前記第2導電型半導体膜は前記第1の電極の上を覆う部分を有し、前記覆う部分は前記第1の電極を保護する機能を有していることを特徴とする請求項1記載の複合半導体装置

。

### 【請求項 3】

前記第1の電極は、パット電極機能を有している部分を備えていることを特徴とする請求項1又は2記載の複合半導体装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は半導体発光素子部とこれを過電圧から保護するための保護素子部とを有する複合半導体装置に関する。

#### 【背景技術】

10

#### 【0002】

近年、半導体発光素子として、365 nm ~ 550 nm程度範囲内の波長の光を放射させることが可能な窒化物半導体材料を使用した発光素子が注目されている。

#### 【0003】

ところで、窒化物半導体材料を使用した発光素子の静電破壊耐量は例えば100 V程度と比較的低い。静電破壊の問題を解決するために、サファイア基板上に発光ダイオードとこれを保護するための保護素子とを設けることが後記特許文献1及び2に開示されている。即ち、特許文献1及び2にはサファイア基板上に発光ダイオードを設けると共に、保護用pn接合ダイオードを設け、これ等を導体によって逆並列接続することが開示されている。この様に保護用pn接合ダイオードを発光ダイオードに逆並列接続すると、発光ダイオードに順方向電圧が印加されている時に、保護用pn接合ダイオードは逆方向バイアス状態となり、電流は発光ダイオードを通って流れ、保護用pn接合ダイオードを通ってほとんど流れない。逆に、発光ダイオードに逆方向電圧が印加されている時には、保護用pn接合ダイオードが順バイアス状態となり、保護用pn接合ダイオードの順方向の立上り電圧（導通開始電圧）よりも高い電圧が印加された時に保護用pn接合ダイオードが導通状態となり、発光ダイオードの電圧が保護用pn接合ダイオードの順方向電圧に制限される。

20

#### 【0004】

しかし、特許文献1及び2に開示されている上記のサファイア基板上に発光ダイオードと保護用pn接合ダイオードとを分離して横方向に並べて配置すると、保護用pn接合ダイオードの分だけ複合半導体装置のチップサイズが大きくなる。また、チップサイズを従来と同一とした場合には発光ダイオードの有効発光面積が低減し、輝度の低下を招く。

30

更に、特許文献1及び2に開示されているように発光ダイオードと保護用pn接合ダイオードとを分離して配置すると、これ等を逆並列接続するための導体を引き回すことが必要になり、その分だけ複合半導体装置のサイズが大きくなる。

更に、特許文献1の保護用pn接合ダイオードは、発光ダイオードのためのエピタキシャル成長層と同時に形成されたエピタキシャル成長層を使用して構成されている。従って、保護用pn接合ダイオードの半導体層の厚さが発光ダイオードのエピタキシャル成長層の厚さに制限され、保護用pn接合ダイオードの順方向電圧を好ましい値に設定することが困難である。なお、保護用pn接合ダイオードの順方向電圧の好ましい値は、正常時に発光ダイオードに印加される逆方向電圧よりも高く、且つ発光ダイオードの許容最大逆方向電圧よりも低い値である。

40

更に、特許文献1の図8に示されている実施形態に従う発光ダイオードは、InGaNから成る活性層とこの一方の側に配置されたp型GaN層（pクラッド層）とこの他方の側に配置されたn型GaN層（nクラッド層）とから成り、保護用pn接合ダイオードはnクラッド層に連続しているn型GaN層と活性層と同一のInGaN層とpクラッド層と同一のp型GaN層とから成る。保護用pn接合ダイオードのn型GaN層に設けられたカソード電極は発光ダイオードのアソード電極に接続され、発光ダイオードのカソード電極はnクラッド層に接続されている。従って、発光ダイオードのカソード電極と保護用pn接合ダイオードのカソード電極とが共にn型GaN層に接続されているので、もしこ

50

れ等の相互間距離が短いと、これ等の相互間に電流が流れ、発光ダイオードに電流が流れない可能性がある。このため、発光ダイオードのカソード電極と保護用 p-n 接合ダイオードのカソード電極との距離を十分に大きくすることが必要になり、複合半導体装置のサイズが必然的に大きくなる。

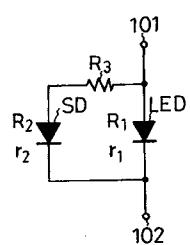

特許文献 1 の図 1 には、発光ダイオードの p 型 GaN 層 (p クラッド層) の延長部分の抵抗を発光ダイオードのアノード電極とカソード電極との間に接続し、この抵抗を保護素子として使用する別の実施形態が開示されている。発光ダイオードのカソード電極を p 型クラッド層の延長部分に接触させると、この接触はショットキー接觸又はこれに近い状態になる。従って、特許文献 1 の保護素子としての抵抗を含む複合半導体装置を図 2-9 の等価回路で示すことができる。即ち、この等価回路において、発光ダイオード LED のアノード電極 101 とカソード電極 102 との間にショットキーバリヤダイオード SD が保護用抵抗 R3 を介して接続されている。保護用抵抗 R3 はアノード電極 101 とのショットキーバリヤダイオード SD との間に介在する p 型 GaN 層 (p クラッド層) の長さに比例した値を有する。ショットキーバリヤダイオード SD は発光ダイオード LED に対して保護用抵抗 R3 を介して順方向並列接続されている。従って、もし保護用抵抗 R3 の値が小さいと、発光ダイオードに順方向電圧が印加された時に、保護用抵抗 R3 を介して電流が流れ、発光ダイオードが発光しない。保護用抵抗 R3 の値を R3、発光ダイオード LED の順方向の抵抗値を R1、逆方向の抵抗値を r1、ショットキーバリヤダイオード SD の順方向の抵抗値を R2、逆方向の抵抗値を r2 とした時、R2 + R3 が R1 よりも十分に大きいことが発光ダイオード LED の発光条件であり、また、r2 + R3 が r1 よりも十分に小さいことが保護用抵抗 R3 に基づいて保護機能を得る条件である。10

上記条件を満足させるように p 型 GaN 層 (p クラッド層) の延長部分を設定することには困難を伴なう。また、抵抗 R3 を得るために p クラッド層の延長部分を設けると、チップサイズが必然的に大きくなる。20

**【特許文献 1】特開平 10 - 65215 号公報**

**【特許文献 2】特開平 10 - 200159 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

本発明が解決しようとする課題は、保護素子部を伴なった半導体発光装置、即ち発光素子と保護素子との複合半導体装置の小型化を図ることが困難なことである。また、発光素子と受光素子と保護素子との一体化が要求されることがあるが、これ等を含む複合半導体装置の小型化を図ることが困難であった。30

**【課題を解決するための手段】**

**【0006】**

上記課題を解決するための本発明は、半導体発光素子部とこの半導体発光素子部を過電圧から保護するための保護素子部とを含む複合半導体装置であつて、

前記半導体発光素子部は、一方の主面と他方の主面とを有し且つ導電性を有し且つ第 1 導電型を有する半導体基板と、互いに対向する第 1 及び第 2 の主面と前記第 1 の主面から前記第 2 の主面に至る傾斜側面とを有し且つ前記第 2 の主面が前記半導体基板の一方の主面に電気的及び機械的に結合されている発光半導体領域と、前記発光半導体領域の前記第 1 の主面に配置された第 1 の電極と、前記半導体基板に接続された第 2 の電極とを備え、前記保護素子部は、前記半導体基板の延長部分と前記発光半導体領域の前記傾斜側面に光透過性を有する絶縁膜を介して配置された光透過性を有する第 2 導電型半導体膜とから成り、40

前記第 2 導電型半導体膜の一端部分は前記半導体基板の前記延長部分に p-n 接合接觸し、前記第 2 導電型半導体膜の他端部分は前記第 1 の電極に接続され、

前記第 1 の電極は光透過性を有し、

前記発光半導体領域は前記半導体基板の一方の主面上に気相成長された半導体又は前記半導体基板に熱圧着で貼り合わせた半導体からなることを特徴とする複合半導体装置に係わ50

るものである。

なお、本願において、光とは半導体発光素子部から放射される光を意味する。また、複合半導体装置とは保護素子部を伴なった半導体発光装置を意味する。また、保護素子部とは、半導体発光素子部を過電圧から保護する機能を有する保護素子を意味する。

#### 【0007】

請求項2に示すように、前記第2導電型半導体膜は前記第1の電極の上を覆う部分を有し、前記覆う部分は前記第1の電極を保護する機能を有していることことが望ましい。前記第2導電型半導体膜の前記覆う部分が耐湿性又は防傷性又はこれらの両方を有する保護膜機能を有することによって、従来の保護膜を省くこと、又は従来の保護膜を保護膜機能の低いものに置き換えることが可能になり、小型化及び低コスト化が可能になる。10

また、請求項3に示すように、第1の電極は、パッド電極機能を有している部分を備えていることが望ましい。

#### 【発明の効果】

#### 【0008】

本発明によれば次の効果を得ることができる。

(1) 発光半導体領域をその逆方向又は順方向又はこれ等の両方の過電圧から保護するための前記保護素子部が、前記発光半導体領域の傾斜側面に設けられているので、保護素子部を伴なった半導体発光装置即ち複合半導体装置の小型化を達成することができる。

(2) 導電性を有している基板が使用されているので、基板によって半導体発光素子部と保護素子部との相互接続が容易に達成される。従って、半導体発光素子部と保護素子部との構成が単純化され、小型化及び低コスト化が達成される。20

(3) 第2導電型半導体膜及び絶縁膜が光透過性を有するので、発光半導体領域の傾斜側面から光を外部に取り出すことができ、光の外部取り出し効率が向上する。

#### 【発明を実施するための最良の形態】

#### 【0009】

次に、図1～図28を参照して本発明の実施形態を説明する。

#### 【実施例1】

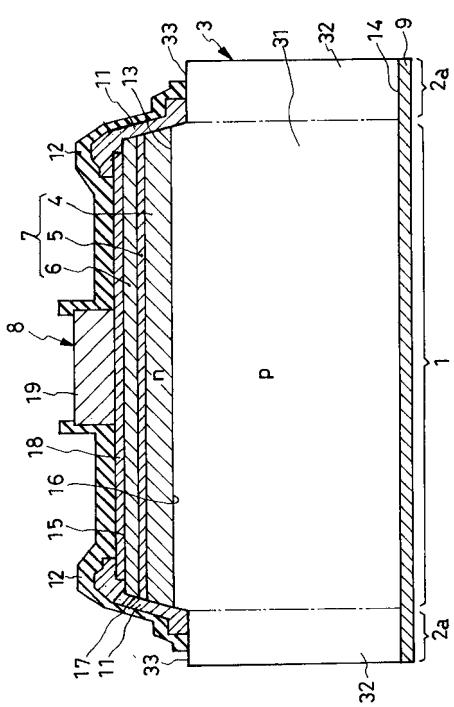

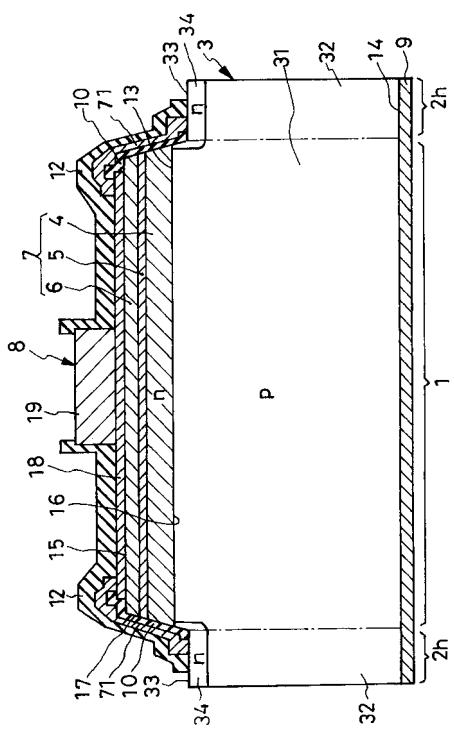

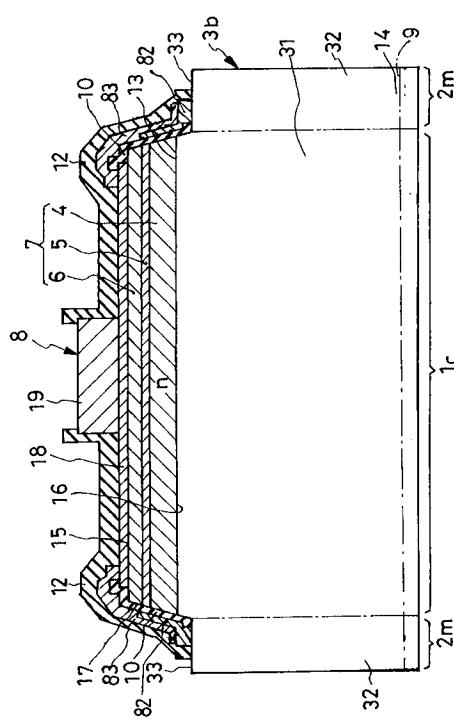

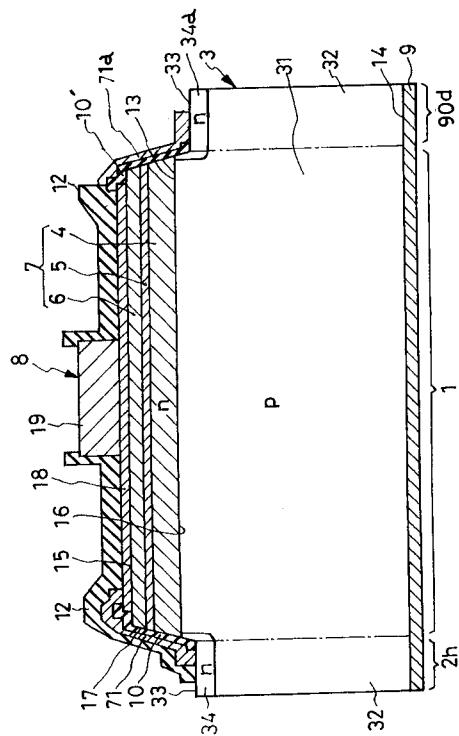

#### 【0010】

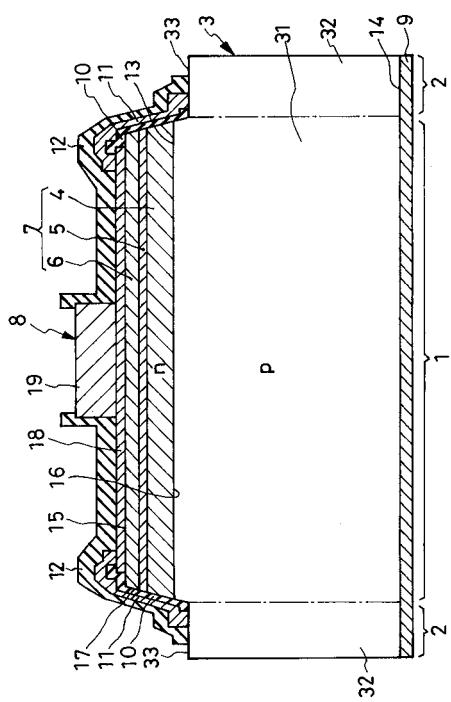

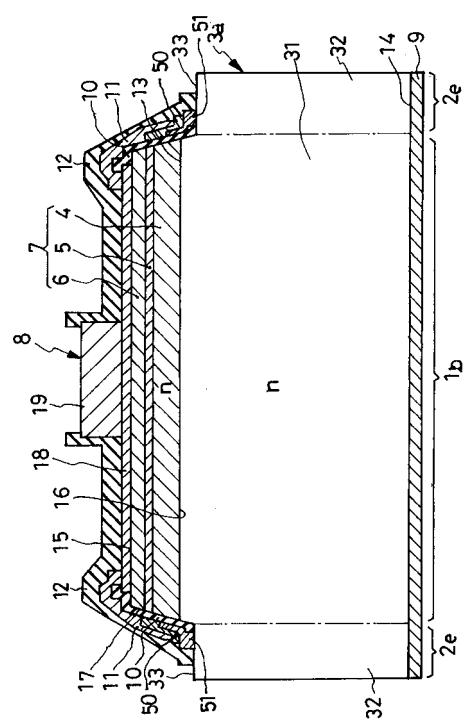

図1に示す本発明の実施例1に従う複合半導体装置は、半導体発光素子部（以下、発光素子部と言う。）1と保護素子部2とから成る。発光素子部1には半導体発光ダイオードが形成され、保護素子部2には発光素子部1を過電圧から保護するための保護ダイオードが形成されている。30

#### 【0011】

発光素子部1と保護素子部2とは共通の導電性基板としてのp型（第1導電型）のシリコン半導体基板3を使用して構成されている。半導体基板3の鎖線で区画して示す中央部分31は主として発光素子の構成に寄与し、中央部分31の延在部分としての外周部分32は主として保護素子の構成に寄与している。この半導体基板3の詳細は後述する。

#### 【0012】

発光素子部1は、半導体基板3の中央部分31と、n型半導体層4、活性層5及びp型半導体層6から成る発光半導体領域（主半導体領域）7と第1の電極8と第2の電極9とから成る。40

保護素子部2は、半導体基板3の中央部分31の延在部分としての外周部分32と絶縁膜10と第2導電型半導体膜としてのn型半導体薄膜11とから成る。

第1の電極8の大部分とn型半導体薄膜11は、耐湿性及び防傷性を有する例えばシリコン酸化膜(SiO<sub>2</sub>)から成る光透過性保護膜12によって覆われている。次に、図1の各部を詳しく説明する。

#### 【0013】

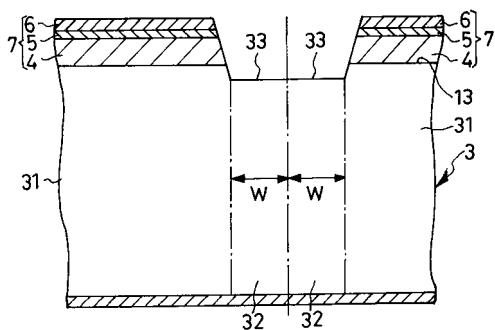

導電性を有する基板としての半導体基板3は導電型決定用不純物としてボロン等の3族元素を含むp型単結晶シリコン基板から成り、一方の正面13と他方の正面14とを有する。この半導体基板3のp型不純物濃度は、例えば $5 \times 10^{18} \sim 5 \times 10^{19} \text{ cm}^{-3}$ 程度で50

あり、抵抗率は  $0.0001 \text{ } \cdot \text{cm} \sim 0.01 \text{ } \cdot \text{cm}$  程度である。従って、半導体基板 3 は導電性基板であり、発光素子部 1 の電流通路として機能する。更に、半導体基板 3 は、発光半導体領域 7 のエピタキシャル成長のための基板としての機能、及び発光半導体領域 7 と第 1 の電極 8 との機械的支持体としての機能を有する。半導体基板 3 の好ましい厚みは比較的厚い  $200 \sim 500 \mu\text{m}$  である。半導体基板 3 の一方の正面 13 は平坦であつても差し支えない。しかし、1枚の半導体ウエハから複数の複合半導体装置を作製する時に、比較的大きな面積を有する発光半導体領域 7 を図 3 に示すようにエッチングによって複数個に分割すると、必然的に半導体基板 3 もエッチングされて凹部即ち段部 33 が生じる。このエッチングにおいて、半導体基板 3 は発光半導体領域 7 をエッチングストップとして機能している。なお、保護素子部 2 の複合化の有無に関係なく、ウエハを個別の半導体発光素子に分割する時に、2つの発光半導体領域の相互間に分割のために必要な幅 ( $w + w$ ) を有する段部 33 又は発光半導体領域 7 で覆われない部分が生じる。10

#### 【0014】

半導体基板 3 上には、一般に n 型クラッド層と呼ばれている n 型半導体層 4 と活性層 5 と一般に p 型クラッド層と呼ばれている p 型半導体層 6 とが順次に周知のエピタキシャル成長法によって形成されている。発光半導体領域 7 の各層 4、5、6 は 3 - 5 族化合物半導体の 1 種である周知の窒化物半導体から成る。従って、発光半導体領域 7 の n 型半導体層 4 とシリコン半導体基板 3 とはヘテロ接合である。図 1 では p 型半導体基板 3 に対して n 型半導体層 4 が接触しているが、これらのヘテロ接合界面の電圧降下は比較的小さい。20

即ち、p 型シリコン半導体基板 3 と窒化物半導体から成る n 型半導体層 4 との間に図示されていない合金化層が生じているために、第 1 及び第 2 の電極 8、9 間に発光半導体領域 7 を順方向バイアスする向きの電圧を印加した時の n 型半導体層 4 と p 型半導体基板 3 との間の界面における電圧降下は小さい。勿論、図 1 の p 型半導体基板 3 の代りに n 型半導体基板を使用し、且つ n 型半導体薄膜 11 の代りに p 型半導体薄膜を形成することもできる。

#### 【0015】

n 型半導体層 4 は、図 1 において 1 つの層で示されているが、バッファ層と n 型半導体層との組み合せで構成することができる。

図 1 において活性層 5 も 1 つの層で示されているが、実際には周知の多重量子井戸構造を有している。もし、ダブルヘテロ接合構造にすることが要求されない場合には、発光半導体領域 7 から活性層 5 を省くこともできる。30

図 1 において、活性層 5 の上に配置された p 型半導体層 6 は 1 つの層で示されているが、この p 型半導体層 6 に周知の電流拡散層、コンタクト層等を含めることができる。

#### 【0016】

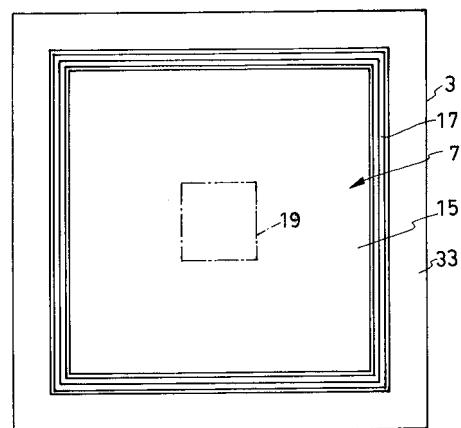

発光半導体領域 7 は、互いに対向している第 1 及び第 2 の正面 15、16 と、傾斜を有する側面 17 とを有している。この実施例 1 では発光半導体領域 7 の第 1 の正面 15 が光取出しに利用され、第 2 の正面 16 が半導体基板 3 の一方の正面 13 に電気的及び機械的に結合されている。

なお、この実施例 1 では図 2 に示すように発光半導体領域 7 及び半導体基板 3 が平面的に見て四角形のパターンを有しているが、それぞれを平面的に見て円形パターン又は別の任意のパターンとすることができます。また、半導体基板 3 を四角形パターンとし、発光半導体領域 7 のみを円形パターン又は任意のパターンとすることもできる。40

#### 【0017】

発光半導体領域 7 の上に配置された第 1 の電極 8 は、第 1 の部分としての光透過性電極 18 と第 2 の部分としてのボンディングパッド電極 19 とから成る。光透過性電極 18 は発光半導体領域 7 の第 1 の正面 15 のほぼ全体に配置され、且つ p 型半導体層 6 に電気的に接続されている。この光透過性電極 18 は、一般に ITO と呼ばれている酸化インジウム ( $\text{In}_2\text{O}_3$ ) と酸化錫 ( $\text{SnO}_2$ ) との混合物から成る  $100 \text{ nm}$  程度の膜とすることが望ましい。しかし、光透過性電極 18 を ITO 以外の  $\text{ZnO}$  (酸化亜鉛)、 $\text{Ag}$  (銀) 等の別の材料で光透過可能な厚みに形成することもできる。ボンディングパッド電極 19 50

は発光半導体領域 7 の第 1 の主面 15 の面積よりも小さい面積を有するように形成され且つ A1 又は Au 等から成る外部接続用ワイヤを結合することができる金属からなり、光透過性電極 18 に接続されている。このボンディングパッド電極 19 は光透過性電極 18 よりも厚く形成され且つ光を実質的に透過させないので、図 2 で鎖線で示すように発光半導体領域 7 の第 1 の主面 15 の中央部分に限定的に配置されている。

#### 【0018】

第 2 の電極 9 は半導体基板 3 の他方の主面 14 に接続されている。なお、半導体基板 3 は導電性を有するので、第 2 の電極 9 を半導体基板 3 の一方の主面 13 の外周部分に接続することもできる。

#### 【0019】

発光半導体領域 7 を静電気等の過電圧から保護するための保護素子部 2 の一部としての n 型半導体薄膜 11 は、 p 型の半導体基板 3 の外周部分 32 に p-n 接触している一端部分と、絶縁膜 10 を介して発光半導体領域 7 の側面 17 上に配置されている部分と、第 1 の電極 8 の一部である光透過性電極 18 に電気的に接続されている他端部分とを有する。この n 型半導体薄膜 11 と p 型の半導体基板 3 との界面の p-n 接合が保護ダイオードとして機能する。発光半導体領域 7 の側面 17 が傾斜しているために、平面的に見て即ち半導体基板 3 の一方の主面 13 に対して垂直な方向から半導体基板 3 を見て、保護素子部 2 の一部としての n 型半導体薄膜 11 が半導体基板 3 の内側に配置されている。

この実施例 1 では、傾斜している側面 17 からの光取出しを可能にするために、絶縁膜 10 は 1 nm ~ 2 nm 程度に形成され、また n 型半導体薄膜 11 も 1 nm ~ 2 nm 程度に形成され、それぞれが光透過性を有する。また、 n 型半導体薄膜 11 と光透過性電極 18 とを覆う保護膜 12 も光透過性を有する材料及び厚さに形成されている。n 型半導体薄膜 11 に光透過性が要求されないか、又は光透過性が低くても差し支えない場合は、 n 型半導体薄膜 11 の厚みを 1 nm ~ 1 μm の範囲で任意に変えること、又は n 型半導体薄膜 11 を 1 μm よりも厚い n 型半導体厚膜に変えることができる。

#### 【0020】

図 1 の n 型半導体薄膜 11 はアモルファス（非晶質）シリコンで形成されているが、この代りに例えば ITO、ZnO、SnO<sub>2</sub>、In<sub>2</sub>O<sub>3</sub>、ZnS、ZnSe、ZnSb<sub>2</sub>O<sub>6</sub>、CdO、CdIn<sub>2</sub>O<sub>4</sub>、MgIn<sub>2</sub>O<sub>4</sub>、ZnGa<sub>2</sub>O<sub>4</sub>、CdGa<sub>2</sub>O<sub>4</sub>、Ga<sub>2</sub>O<sub>3</sub>、GaIn<sub>3</sub>、CdSnO<sub>4</sub>、InGaMgO<sub>4</sub>、InGasZnO<sub>4</sub>、Zn<sub>2</sub>In<sub>2</sub>O<sub>5</sub>、AgSbO<sub>3</sub>、Cd<sub>2</sub>Sb<sub>2</sub>O<sub>7</sub>、Cd<sub>2</sub>GeO<sub>4</sub>、AgInO<sub>2</sub>、CdS、CdSe 等で形成することもできる。また、 n 型半導体薄膜 11 の代わりに n 型半導体厚膜を設けることもできる。

半導体薄膜 11 は、蒸着、又は CVD、又は印刷（塗布）、又はスパッタ等の周知の方法で形成される。

#### 【0021】

この実施例では発光半導体領域 7 の側面 17 の全周を囲むように n 型半導体薄膜 11 が形成されているが、側面 17 の一部のみに半導体薄膜 11 を形成することもできる。しかし、側面 17 の全周又はできるだけ多くの部分に半導体薄膜 11 を形成することが望ましい。これにより、 n 型半導体薄膜 11 を薄く形成しても、所望の電流容量を得ることが可能になる。

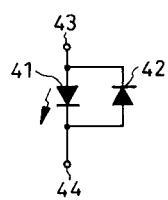

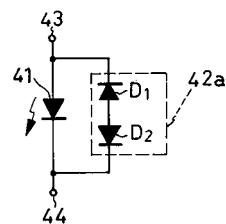

#### 【0022】

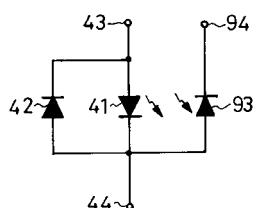

図 1 の複合半導体装置の発光素子部 1 は図 4 の発光素子としての発光ダイオード 41 の機能を有し、保護素子部 2 は図 4 の保護素子としての保護ダイオード 42 の機能を有する。図 1 の第 1 及び第 2 の電極 8、9 は図 4 の第 1 及び第 2 の端子 43、44 として機能する。従って、発光素子部 1 に基づく発光ダイオード 41 に対して保護素子部 2 に基づく保護ダイオード 42 は逆方向並列に接続されている。

#### 【0023】

保護ダイオード 42 の順方向電圧即ち順方向の立上り電圧（導通開始電圧）は、発光ダイオード 41 の許容最大逆方向電圧（逆方向耐電圧）よりも低く設定される。また、保護

10

20

30

40

50

ダイオード42の順方向電圧は、正常時に発光ダイオード41に印加される逆方向電圧よりも高いことが望ましい。発光ダイオード41に異常な逆方向の電圧が印加されると、保護ダイオード42が導通し、発光ダイオード41の電圧が保護ダイオード42の順方向電圧に抑えられ、発光ダイオード41に逆方向のサージ電圧等の過電圧が印加されることを阻止でき、発光ダイオード41を破壊から保護することができる。

なお、保護ダイオード42をツエナーダイオード等の定電圧ダイオードで構成することもできる。この定電圧ダイオードの逆方向の降伏電圧は、発光ダイオード41に対して正常時に順方向に印加される電圧と許容最大順方向電圧（順方向耐電圧）との間であることが望ましい。これにより、定電圧ダイオードの逆方向降伏電圧以上の電圧が発光ダイオード41に印加されることを防ぐことができ、発光ダイオード41をサージ電圧等の順方向の過電圧から保護することができる。定電圧ダイオードの順方向電圧は保護ダイオード42の順方向電圧と同一であることが望ましい。10

定電圧ダイオードを設けると、発光ダイオード41を逆方向と順方向との両方の過電圧から保護することができる。もし、発光ダイオード41を逆方向の過電圧から保護することが要求されない場合は、定電圧ダイオードの順方向電圧を任意に設定し、定電圧ダイオードによって発光ダイオード41を順方向の過電圧から保護する。

#### 【0024】

本実施例の複合半導体装置は次の効果を有する。

(1) 発光半導体領域7の側面17上に保護素子部2の一部を配置し、且つ発光半導体領域7が設けられない半導体基板3の外周部分32を保護素子部2の一部として使用する構成であるので、半導体基板3の一方の主面13に対する発光半導体領域7の占有面積の実質的な低減を伴なわないので過電圧保護機能を得ることができる。要するに、従来と同一の光出力を得る場合には、複合半導体装置の小型化を達成することができる。また、複合半導体装置を従来と同一寸法に形成する場合には、従来よりも光出力を大きくすることができます。20

(2) 発光半導体領域7の側面17が傾斜しているので、平面的に見て保護素子部2の一部としてのn型半導体薄膜11を半導体基板3の内側に配置することができ、複合半導体装置の小型化を良好に達成することができる。

(3) 発光素子部1と保護素子部2とで共通の半導体基板3を使用し、且つn型半導体薄膜11を第1の電極8に直接に接続する構成であるので、図4に示すように発光ダイオード41に保護ダイオード42を並列接続する構成及び工程を簡略化することができ、複合半導体装置の小型化及び低コスト化を達成することができる。30

(4) n型半導体薄膜11を、生産性に優れた蒸着、CVD、スパッタ、スクリーン印刷等で形成できるので、保護素子の製造コストの低減を図ることができる。

(5) 絶縁膜10、n型半導体薄膜11、保護膜12が光透過性を有するので、発光半導体領域7の側面17から光を外部に取り出すことができ、光の外部取り出し効率が向上する。

#### 【実施例2】

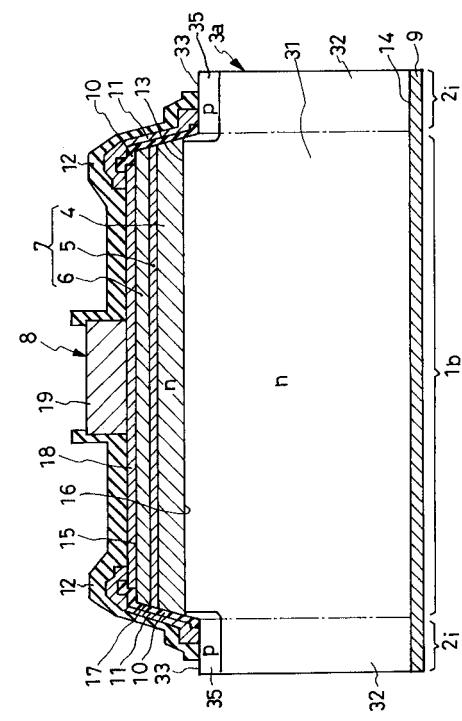

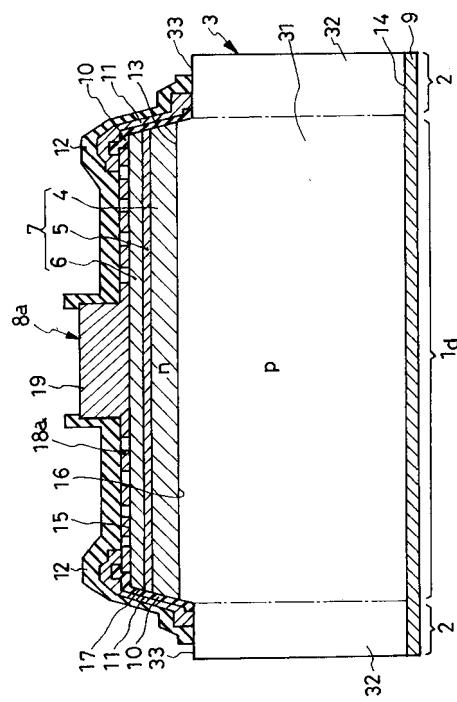

#### 【0025】

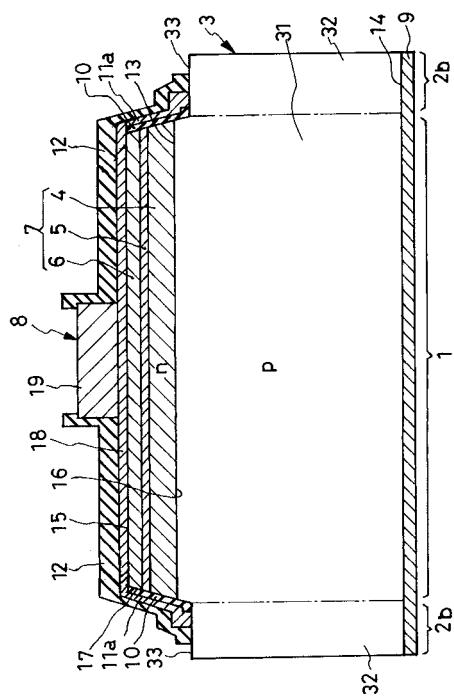

図5に示す実施例2に従う複合半導体装置は、変形した保護素子部2aを設け、この他は図1と同一に構成したものである。従って、図5、及び後述する図6～図28において図1と実質的に同一の部分には同一の符号を付し、また、図5～図28において相互に共通する部分には同一の符号を付し、その説明を省略する。40

#### 【0026】

図5の保護素子部2aは、図1の保護素子部2から絶縁膜10を省き、この他は図1と同一に形成したものに相当する。絶縁膜10が省かれているので、図5ではn型半導体薄膜11が発光半導体領域7の側面17に直接に接触している。しかし、n型半導体薄膜11を活性層5よりも大きなバンドギャップを有する材料、好ましくは発光半導体領域7の各層4、5、6よりも大きなバンドギャップを有する材料で形成することによってn型半導体薄膜11から発光半導体領域7へ又はこの逆のリーク電流は極めて小さくなり、実用50

上問題がない。

従って、図5の実施例によっても図1の実施例と同一の効果を得ることができる。

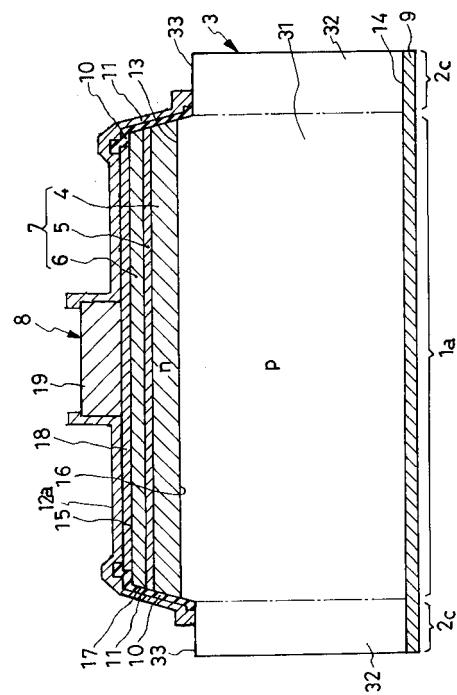

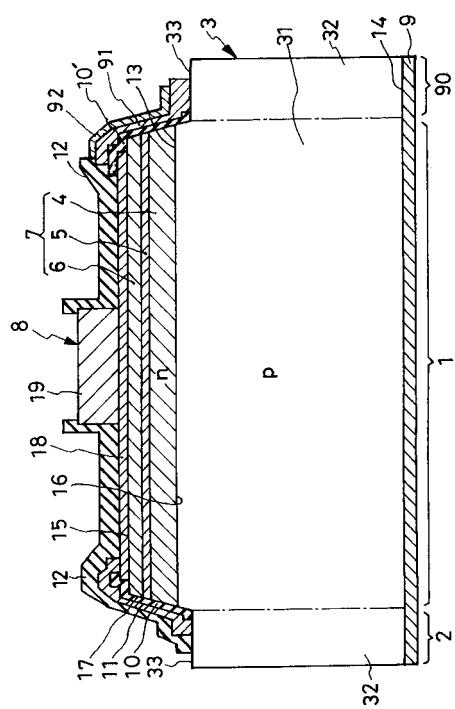

**【実施例3】**

**【0027】**

図6に示す実施例3の複合半導体装置は、変形された保護素子部2bを設けた他は図1と同一に形成したものである。

**【0028】**

図6の保護素子部2bは光透過性電極18と同一材料(例えばITO)から成るn型半導体薄膜11aを設け、この他は図1と同一に構成したものである。図6のn型半導体薄膜11aは光透過性電極18と同一材料であるので、両者を同一工程で形成し、連続させることができる。これにより、複合半導体装置の製造工程の簡略化を図ることができる。なお、光透過性電極18がn型半導体薄膜であっても、p型半導体層6との間の障壁はさほど高くないので実用上問題ない。

本実施例3は上記効果の他に図1の実施例1と同一の効果も有する。

**【0029】**

図6の変形として図6を図5と同様に絶縁膜10を省き、n型半導体薄膜11を発光半導体領域7の側面17に直接に形成することもできる。

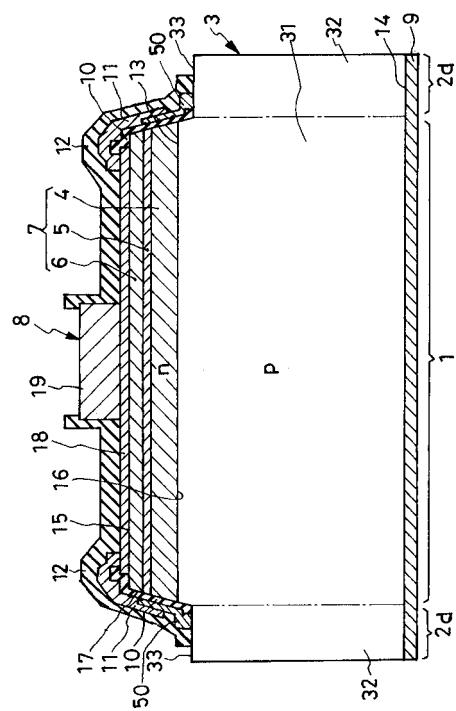

**【実施例4】**

**【0030】**

図7の実施例4の複合半導体装置は、変形された発光素子部1a及び保護素子部2cを設けた他は図1と同一に形成したものである。

変形された発光素子部1aは図1の保護膜12の代りに光透過性を有するn型半導体薄膜11の延在部分12aを光透過性電極15の上に配置し、この他は図1と同一に形成したものに相当する。図7の保護素子部2cは図1の保護素子部2から保護膜17を省き、この他は図1と同一に形成したものに相当する。

**【0031】**

この実施例4では、n型半導体薄膜11の延在部分12aが光透過性電極15の保護膜として機能しているので、保護膜の形成を省くことができ、この分だけコストの低減を図ることができる。

なお、図7の実施例4は図1の実施例1と同一の効果も有する。

**【実施例5】**

**【0032】**

図8の実施例5の複合半導体装置は、変形された保護素子部2dを設け、この他は図1と同一に形成したものである。

**【0033】**

図8の保護素子部2dは図1の保護素子部2にp型半導体薄膜50を追加し、この他は図1と実質的に同一に形成したものである。図8のp型(第1導電型)半導体薄膜50はp型の半導体基板3の外周部分32に低抵抗接觸して電気的に接続されている一端部分と絶縁膜10を介して発光半導体領域7の側面17に対向配置されている部分と有する。n型(第2導電型)半導体薄膜11はp型半導体薄膜50にpn接觸している一端部分と絶縁膜10を介して発光半導体領域7の側面17に対向配置されている部分と光透過性電極15に低抵抗接觸して電気的に接続されている他端部分と有する。保護膜12はp型半導体薄膜50とn型半導体薄膜11との両方を被覆している。

なお、p型半導体薄膜50は、アモルファスシリコン、NiO、Cu<sub>2</sub>O、FeO、CuAlO<sub>2</sub>、CuGaO<sub>2</sub>、SrCu<sub>2</sub>O<sub>2</sub>等で形成することができる。

**【0034】**

図8の実施例5ではp型半導体薄膜50とn型半導体薄膜11との間のpn接合が図4の保護ダイオード42と同様に機能する。

**【0035】**

なお、図8の実施例5においても、図5と同様に絶縁膜10を省くこと、図6と同様に

10

20

30

40

50

n型半導体薄膜11を光透過性電極15と同一材料で形成すること、図7と同様にn型半導体薄膜11を光透過性電極15の上に延在させて保護膜12を省くことができる。

#### 【実施例6】

##### 【0036】

図9の実施例6の複合半導体装置は、変形された発光素子部1bと保護素子部2eを設け、その他は図1と同一に形成したものである。従って、図9において図1と同一の部分には同一の符号を付してその説明を省略する。

##### 【0037】

図9の発光素子部1bはn型シリコン半導体基板3aを有する他は図1と同一に形成されている。図9の保護素子部2eは図8と同様にp型半導体薄膜50を有し、更に金属層51を有する。金属層51は半導体基板3の外周部分32の一方の主面13上に配置された部分と絶縁膜10を介して発光半導体領域7の側面17に対向配置されている部分とを有する。

##### 【0038】

p型半導体薄膜50は絶縁膜10を介して発光半導体領域7の側面17に対向配置されている部分と金属層51に低抵抗接觸して電気的に接続されている部分とを有する。図9のn型半導体薄膜11は図8と同様にp型半導体薄膜50にpn接觸している部分と光透過性電極18に低抵抗接觸して電気的に接続されている部分とを有する。

##### 【0039】

図9の実施例6は図8の実施例5に金属層51を追加した点を除いて図8と実質的に同一に構成したものであるので、実施例5と同一の効果を有する。

なお、図9では金属層51を有するので、n型半導体基板3aが使用されている。しかし、図9では半導体基板3aの導電型がp型半導体薄膜50に拘束されないので、半導体基板3aの導電型をp型に変えることもできる。

##### 【0040】

図9の実施例6においても、図5と同様に絶縁膜10を省くこと、図6と同様にn型半導体薄膜11を光透過性電極18と同一材料で形成すること、図7と同様にn型半導体薄膜11を光透過性電極18の上に延在させて保護膜12を省くことができる。

#### 【実施例7】

##### 【0041】

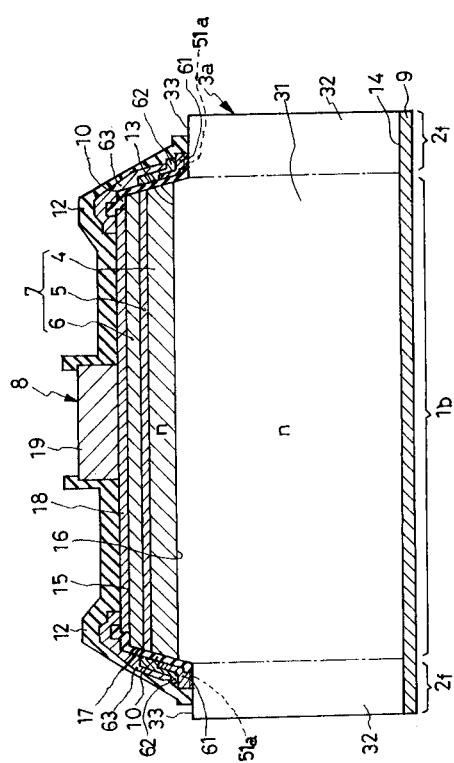

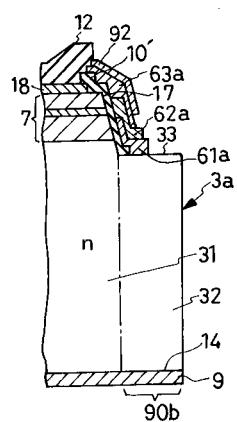

図10の実施例7の複合半導体装置は、変形された発光素子部1bと保護素子部2fを設け、この他は図1と同一に形成したものである。

##### 【0042】

図10の発光素子部1bはn型シリコン半導体基板3aを有する他は図1と同一に形成されている。図10の保護素子部2fは、n型の第1の半導体薄膜61とp型の第2の半導体薄膜62とn型の第3の半導体薄膜63とを有する。n型の第1の半導体薄膜61はn型の半導体基板3aに接觸している部分と発光半導体領域7の側面17上に絶縁膜10を介して配置されている部分とを有する。n型の第1及び第3の半導体薄膜61、63は、図1のn型半導体薄膜11と同一材料によって同一方法で形成されている。p型の第2の半導体薄膜62はn型の第1の半導体薄膜61にpn接觸している部分と絶縁膜10を介して発光半導体領域7の側面17上に配置された部分とを有する。このp型の第2の半導体薄膜62は図8及び図9に示されているp型半導体薄膜50と同一材料によって同一方法で形成されている。n型の第3の半導体薄膜63はp型の第2の半導体薄膜62にpn接觸している部分と光透過性電極18に接続されている部分とを有する。第1、第2及び第3の半導体薄膜61、62、63は発光半導体領域7の側面17に対向配置された部分を有し且つ互いに重ねられた部分を有してn-p-n-3層ダイオードを構成している。

##### 【0043】

図10の複合半導体装置の等価回路を図11で示すことができる。図11の発光素子としての発光ダイオード41は発光素子部1bに対応し、保護素子としてのn-p-n-3層ダイオード42aは保護素子部2fに対応し、第1の端子43は第1の電極8に対応し、第2

10

20

30

40

50

の端子 4 4 は第 2 の電極 9 に対応している。発光ダイオード 4 1 に並列接続された n p n 3 層ダイオード 4 2 a は、一般にダイアック (D I A C) 又は双方向性ダイオードと呼ばれるものであって、逆方向に接続された第 1 のダイオード D1 と順方向に接続された第 2 のダイオード D2 との直列回路で示すことができる。なお n p n 3 層ダイオード 4 2 a を逆方向の第 1 のダイオード D1 と順方向の第 2 のダイオード D2 との並列回路で示すこともある。n p n 3 層ダイオード 4 2 a の順方向及び逆方向の降伏電圧は図 4 に関係して説明した定電圧ダイオードと同様に設定される。即ち、n p n 3 層ダイオード 4 2 a に第 2 の端子 4 4 から第 1 の端子 4 3 に向う逆方向の電圧が印加された時の降伏電圧は、発光ダイオード 4 1 に逆方向に印加される電圧よりも高いことが望ましい。また、n p n 3 層ダイオード 4 2 a に第 1 の端子 4 3 から第 2 の端子 4 4 に向う順方向の電圧が印加された時の降伏電圧は、正常時において発光ダイオード 4 1 に順方向に印加される電圧と許容最大順方向電圧 (順方向耐電圧)との間であることが望ましい。発光ダイオード 4 1 に印加される最大電圧は n p n 3 層ダイオード 4 2 a の電圧に制限されるので、発光ダイオード 4 1 を順方向及び逆方向の過電圧から保護することができる。10

#### 【0044】

図 10 の実施例 7 の保護素子部 2 f の構造は、図 1 の実施例 1 に類似しているので、実施例 7 によっても実施例 1 と同一の効果を得ることができる。

#### 【0045】

図 10 の実施例 7 においても、図 5 と同様に絶縁膜 1 0 を省くこと、図 6 と同様に n 型の第 3 の半導体薄膜 6 3 を光透過性電極 1 8 と同一材料で形成すること、図 7 と同様に n 型の第 3 の半導体薄膜 6 3 を光透過性電極 1 8 の上に延在させて保護膜 1 2 を省くことができる。20

また、図 10 において、第 1 の半導体薄膜 6 1 と半導体基板 3 a との間に点線で示すように金属層 5 1 a を配置することができる。このように金属層 5 1 a を配置した場合には半導体基板 3 a を p 型に変えることもできる。

#### 【実施例 8】

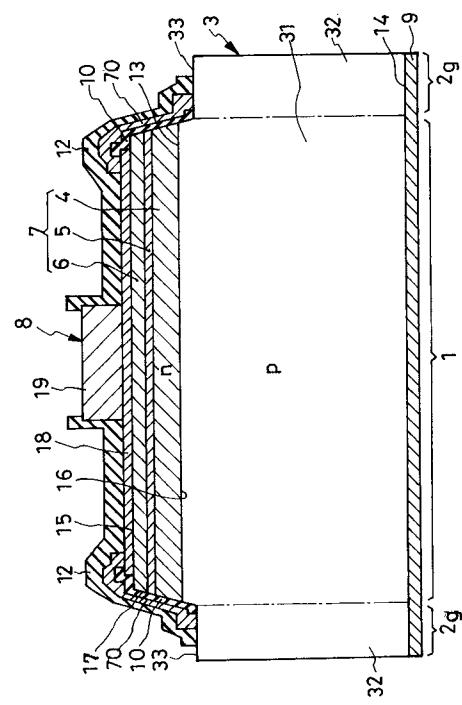

#### 【0046】

図 12 の実施例 8 の複合半導体装置は、変形された保護素子部 2 g を設け、この他は図 1 と一緒に形成したものである。30

#### 【0047】

図 12 の保護素子部 2 g は図 12 の n 型半導体薄膜 1 1 の代りにショットキー電極として機能する金属膜 7 0 を設け、この他は図 1 と一緒に形成したものである。金属膜 7 0 は半導体基板 3 の外周部分 3 2 の一方の主面 1 3 上に配置された一端部分と発光半導体領域 7 の側面 1 7 上に絶縁膜 1 0 を介して配置された部分と光透過性電極 1 8 に接続された他端部分とを有する。

#### 【0048】

金属膜 7 0 は p 型半導体基板 3 に対してショットキー接触し、ショットキーダイオードを構成している。ショットキー接触を得るために金属膜 7 0 を、T i、P t、C r、A l、S m、P t S i、P d<sub>2</sub> S i 等から選択された材料で形成することができる。金属膜 7 0 と半導体基板 3 とに基づくショットキーダイオードは図 4 の p n 接合から成る保護ダイオード 4 2 と同様な機能を有し、発光素子部 1 に基づく発光ダイオード 4 1 に逆方向並列に接続されている。従って、図 12 の実施例 8 によっても実施例 1 と同様な効果を得ることができる。40

#### 【実施例 9】

#### 【0049】

図 13 の実施例 9 の複合半導体装置は、変形された保護素子部 2 h を設け、この他は図 1 と一緒に形成したものである。

#### 【0050】

図 13 の保護素子部 2 h は、p 型半導体基板 3 の外周部分 3 2 の一方の主面に n 型半導

10

20

30

40

50

体領域34を有し、且つこのn型半導体領域34と光透過性電極18とを接続するための金属膜71を有する。図13ではn型半導体領域34が半導体基板3の中央部分31に少しあみ出しているが、外周部分32の中のみに設けることもできる。金属膜71はn型半導体領域34に低抵抗接触して電気的に接続されている一端部分と発光半導体領域7の側面17上に絶縁膜10を介して配置された部分と光透過性電極18に低抵抗接触して電気的に接続されている他端部分とを有する。

#### 【0051】

n型半導体領域34とp型半導体基板3との間のpn接合に基づくダイオードは、図4の保護ダイオード42と同様に発光素子部1の発光ダイオード41に逆方向並列に接続され、保護ダイオード42と同様に発光ダイオード41を過電圧から保護する。

10

#### 【0052】

図13の複合半導体装置においても、保護素子部2hを構成する金属膜71が半導体半導体領域7の側面17上に絶縁膜10を介して配置され、且つ発光ダイオード41の発光機能に無関係な半導体領域3の外周部分32に保護ダイオードのためのn型半導体領域34が形成されているので、発光半導体領域7の第1の正面15の面積を従来と同一とした場合には、複合半導体装置を従来よりも小型にすることができる。即ち、図3によって既に説明したように半導体基板3の外周部分32は発光ダイオードのみを構成する場合においても必然的に生じる部分である。また、n型半導体領域34はエッティングストッパー機能を得るために設けられることが多い。従って、外周部分32に保護素子としてのpn接合ダイオードを形成しても、複合半導体装置の外形寸法の実質的な増大を招かない。このため、図13の実施例9によっても図1の実施例1と同様な効果を得ることができる。

20

#### 【実施例10】

#### 【0053】

図14の実施例10の複合半導体装置は、変形された発光素子部1bと保護素子部2iを設け、この他は図1と同一に形成したものである。

#### 【0054】

図14の発光素子部1bはn型シリコン半導体基板3aを有する他は図1と同一に形成されている。図14の保護素子部2iは半導体基板3aの外周部分32がn型(第1導電型)であり、この外周部分32の一方の正面にp型(第2導電型)半導体領域35が形成されている点で図1と相違し、この他は図1と同一に形成されている。なお、図14ではp型半導体領域35が半導体基板3aの中央部分31に少しあみ出しているが、外周部分32の中のみに形成することもできる。発光半導体領域7の側面17上に絶縁膜10を介して配置されたn型半導体薄膜11の一端部分はp型半導体領域35にpn接觸し、他端部分は光透過性電極18に接続されている。従って、第1の電極8と第2の電極9との間に図11の発光ダイオード41と同様なものが形成され且つ図11のn p n 3層ダイオード42aと同様な保護素子が形成されている。即ち、図14の保護素子部2iにおいて、n型半導体薄膜11とp型半導体領域35との間のpn接合によって図11の第1のダイオードD1に相当するものが形成され、p型半導体領域35とn型半導体領域3aとの間のpn接合で図11の第2のダイオードD2に相当するものが形成されている。図14の保護素子部2iにおけるn p n 3層ダイオードの特性を図11で説明したn p n 3層ダイオード42aと同様な特性にすることによって図10の実施例7と同一の過電圧保護機能を得ることができる。

30

#### 【0055】

図14の実施例10は、保護素子部2iが実施例1~9と同様な技術的思想で構成されているので、実施例1~9と同様な効果を有する。

#### 【0056】

図14の実施例10においても、図5と同様に絶縁膜10を省くこと、図6と同様にn型半導体薄膜11を光透過性電極18と同一材料で形成すること、図7と同様にn型半導体薄膜11を光透過性電極18の上に延在させて保護膜12を省くことができる。

#### 【実施例11】

40

50

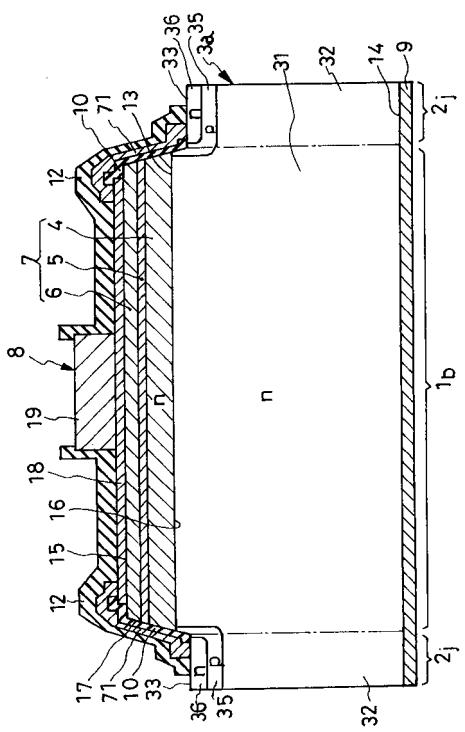

## 【0057】

図15の実施例11の複合半導体装置は、変形された発光素子部1bと保護素子部2jを設け、この他は図1と同じに形成したものである。

## 【0058】

図15の発光素子部1bはn型シリコン半導体基板3aを有する他は図1と同じに形成されている。図15の保護素子部2jは、n型(第1導電型)の半導体基板3aの外周部分32に一方の正面13側に形成されたp型(第2導電型)の第1の半導体領域35とn型の第2の半導体領域36とを有する。p型の第1の半導体領域35とn型半導体基板3aとの間にpn接合が生じている。n型の第2の半導体領域36はp型の第1の半導体領域35の中に形成され、両者間にpn接合が生じている。n型の第2の半導体領域36を光透過性電極18に接続するための金属膜71が設けられている。金属膜71は発光半導体領域7の側面17上に絶縁膜10を介して配置されている部分と第2の半導体領域36に低抵抗接觸して電気的に接続されている一端部分と光透過性電極18に低抵抗接觸して電気的に接続されている他端部分とを有する。10

## 【0059】

図15の保護素子部2jは第1及び第2の電極8,9間に2つのpn接合を有するので、図11のn p n 3層ダイオード42aと同一の機能を有する。また、図15の保護素子部2jのn p n 3層ダイオードは有効発光面積を低減させないように形成されているので、図15の実施例11は実施例1~10と同様な効果を有する。なお、図15ではp型の第1の半導体領域35が半導体基板3aの中央部分31に少しほみ出しているが、外周部分32の中のみに限定的に設けることもできる。また、n型の第2の半導体領域36を半導体基板3aの中央部分31にはみ出るように形成することもできる。20

## 【実施例12】

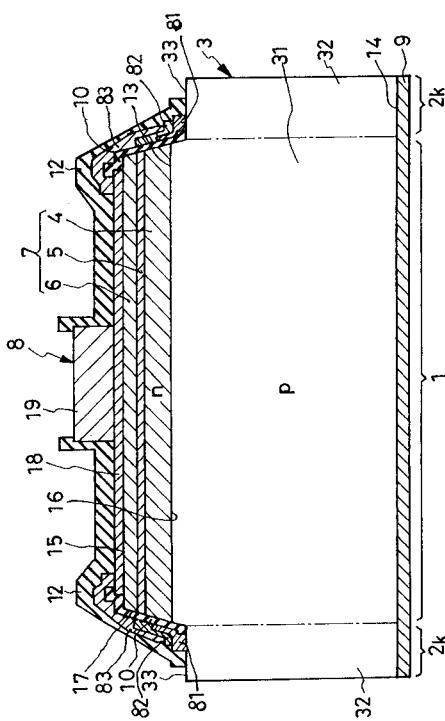

## 【0060】

図16の実施例12の複合半導体装置は、変形された保護素子部2kを設け、この他は図1と同じに形成したものである。

## 【0061】

図16の保護素子部2kは、保護素子とバリスタ特性とコンデンサ特性とを得るために、第1の金属層81とバリスタ特性及びコンデンサ特性を得ることができる半導体磁器から成る誘電体層82と第2の金属層83とを有している。第1の金属層81は半導体基板3の外周部分32の一方の正面13に配置された部分と発光半導体領域7の側面17上に絶縁膜10を介して配置された部分とを有する。誘電体層82は第1の金属層81の上に配置されている。第2の金属層83は誘電体層82の上に配置された部分と光透過性電極18に接続された部分とを有する。30

## 【0062】

図16の複合半導体装置を図17の等価回路で示すことができる。図16の第1及び第2の電極8,9は図17の第1及び第2の端子43,44に対応し、発光素子部1は発光ダイオード41に対応し、保護素子部2kは電圧非直線抵抗体即ちバリスタVRとコンデンサCとを組み合せた保護素子42bに対応している。発光ダイオード41に並列接続されたバリスタVRは図11のn p n 3層ダイオード42aと同様に双方向ダイオードとして機能する。従って、バリスタVRの導電開始電圧即ちバリスタ電圧は図11のn p n 3層ダイオード42aと同一に設定するのが望ましい。誘電体層82と第1及び第2の金属層81,83とによってコンデンサCも形成されている。コンデンサCは発光ダイオード41に並列接続されているので、サージ電圧を吸収して発光ダイオード41を過電圧から保護する。保護素子42bは図17に示すようにバリスタVRとコンデンサCとの両方の機能を有していることが望ましいが、いずれか一方のみの機能を有するように構成することもできる。保護素子42bを構成する誘電体層82の材料の選定によって主としてバリスタ機能を得ること、又は主としてコンデンサ機能を得ることができる。40

## 【0063】

図16の実施例12においても保護素子部2kを発光半導体領域7の側面17に沿って

50

設けているので、図1の実施例1と同一の効果を得ることができる。

【実施例13】

【0064】

図18の実施例13の複合半導体装置は、変形された発光素子部1cと保護素子部2mを設け、この他は図1と同一に形成したものである。

【0065】

図18の発光素子部1cは金属基板3bを有する他は図1と同一に形成されている。図18の保護素子部2mは、図16の保護素子部2kと同様に図17に示すバリスタVRとコンデンサCとから形成するものであって、図16の第1の金属層81を省き、誘電体層82を金属基板3bの一方の主面上に直接に形成し、この他は図16と同一に形成したものである。図18に示すように金属基板3bを使用する場合であっても図16の第1の金属層81に相当するものを設けても差し支えないが、構成を簡略化するために図18では第1の金属層81を省いている。図18において鎖線で示すように金属基板3bの一部が第2の電極9として機能する。勿論、金属基板3bに独立の第2の電極を結合させることもできる。図18の実施例13によっても実施例1及び16と同様な効果を得ることができる。

10

【実施例14】

【0066】

図19の実施例14の複合半導体装置は、変形された発光素子部1dを設け、この他は図1と同一に形成したものである。

20

【0067】

図19の発光素子部1dは変形された第1の電極18aを除いて図1と同一に形成されている。図19の第1の電極18aは、第1の部分としての帯状電極18aと第1の部分としてのボンディングパッド電極19とを有する。帯状電極18aは図1に示されている光透過性電極18の代りに設けられており、発光半導体領域7の第1の主面15上に配置され且つ平面的に見て格子状又は網目状又はストライプ状パターンに形成され、且つボンディングパッド電極19に接続されている。帯状電極18aは光透過性を有する導電体でも良いし、光透過性を有さない導電体でもよい。この帯状電極18aは発光半導体領域7に流す電流をボンディングパッド電極19よりも外周側に分散させる機能を有する。保護素子部2のn型半導体薄膜11は帯状電極18aに接続されている。光は帯状電極18aの開口を介して外部に取り出される。

30

【0068】

図19の実施例14は図1の実施例1と同一構成の保護素子部2を有するので、実施例1と同一の効果を有する。

【0069】

なお、図5～図10、及び図12～図16、及び図18に示す実施例1～13、及び後述する図20、図23～図28実施例15～21の光透過性電極18を図19の帯状電極18aに置き換えることができる。

【実施例15】

【0070】

40

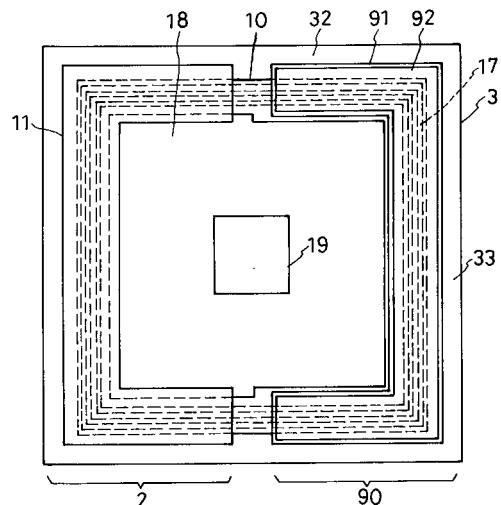

図20～図22に示す実施例15の複合半導体装置は、発光素子と保護素子と受光素子即ち光・電気変換素子又は光センサとが複合化され、発光素子部1と保護素子部2と受光素子部90とを有する。

【0071】

図20及び図21に示す保護素子部2は、その平面形状が図21に示すように変形された他は図1及び図2と同一に構成されている。即ち、図20から保護膜12を省いて複合半導体装置を示す図21から明らかのように保護素子部2における保護素子用n型半導体薄膜11は、発光半導体領域7の側面17のほぼ半周即ち左半分と基板3の外周部分32のほぼ半周即ち左半分に配置されている。

なお、図20の保護素子部2の代りに図8の保護素子部2d、図10の保護素子部2f、

50

図12の保護素子部2g、図13の保護素子部2h、図14の保護素子部2i、又は図15の保護素子部2j等を設けることができる。

#### 【0072】

受光素子部90は受光素子としてのホトダイオードを構成するための部分であって、基板3の延長部分としての外周部分32の右半分と、受光素子用n型半導体薄膜91と、受光素子用電極層92とから成る。

#### 【0073】

受光素子用n型半導体薄膜91は、保護素子用n型半導体薄膜11の下の絶縁膜10の延長部分に相当する光透過性を有する絶縁膜10'の上に配置されている部分とp型半導体基板3の外周部分32にpn接觸している部分とを有する。この受光素子用n型半導体薄膜91は、保護素子用n型半導体薄膜11と同一材料且つ同一方法で形成することができる。受光素子用電極層92は、受光素子用n型半導体薄膜91の上に金属を被着させることによって形成されている。なお、p型半導体基板3及び受光素子用n型半導体薄膜91は発光半導体領域7から放射された光を吸収できる材料（例えばシリコン）で形成される。

10

#### 【0074】

図20及び図21の実施例15の複合半導体装置は、図22の等価回路で示すことができる。図22における発光ダイオード41と保護ダイオード42とは、実施例1と同様に発光素子部1と保護素子部2とで形成されている。ホトダイオード93は、受光素子部90によって形成されている。ホトダイオード93のアノードは図20の第2の電極9に対応する第2の端子44に接続され、カソードは図20の受光素子用電極層92に対応する第3の端子94に接続されている。

20

#### 【0075】

ホトダイオード93は、発光ダイオード41の発光状態の検出のために使用される。即ち、発光半導体領域7から放射された光の一部はp型半導体基板3の外周部分32と受光素子用n型半導体領域91とで形成されているpn接合に至り、ここで吸収されて電気パワーに変換される。更に詳細には、窒化物半導体から成る発光半導体領域7のバンドギャップはシリコン半導体基板3のバンドギャップよりも大きいので、シリコン半導体基板3のバンドギャップよりも大きなエネルギーを持った波長の光が発光半導体領域7から発生し、この光の一部がシリコン半導体基板3の外周部分32と受光素子用n型半導体薄膜91とから成るの受光素子部分90において電気エネルギーに変換される。図22においてホトダイオード93から出力を得るために第2の端子44及び第3の端子94に周知の出力回路（図示せず）が接続される。この出力回路は発光半導体領域7から放射された光量又は光束に所望の関数関係（例えば、比例関係）を有する出力電流又は電圧を出力する。

30

#### 【0076】

この実施例15は、実施例1と同一の効果を有する他に、次の効果を有する。

(1) 受光素子としてのホトダイオード93が発光素子としての発光ダイオード41に一体化されているので、発光ダイオード41の発光状態を正確且つ容易にモニターすることができる。また発光ダイオード41の明るさをホトダイオード93でモニターし、発光ダイオード41の明るさを制御することが可能になる。

40

(2) ホトダイオード93はp型シリコン半導体基板3の外周部分32と発光半導体領域7の側面17に配置された受光素子用n型半導体薄膜91との組み合せで構成されているので、ホトダイオード93を小型且つ安価に形成することができる。なお、既に説明したようにp型シリコン半導体基板3の外周部分32は発光素子を形成する時に必然的に生じる部分であるので、受光素子を設けることによる半導体基板3のサイズの実質的な増大を招かない。

(3) ホトダイオード93は保護ダイオード42と同一の材料及び同一の方法で形成されているので、複合半導体装置の低コスト化を達成できる。

(4) 第2の電極9を発光素子と保護素子と受光素子とで共用しているので、小型化及び低コスト化を達成できる。

50

## 【実施例 16】

## 【0077】

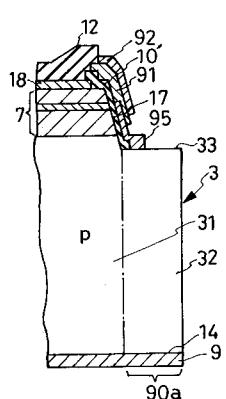

図23に実施例16の複合半導体装置の一部が示されている。この実施例16の複合半導体装置は、図20及び図21に示す実施例15の複合半導体装置の受光素子部90を受光素子部90aに変形し、且つ図20及び図21の保護素子部2の構成を図8の保護素子部2dに変形したものに相当する。

## 【0078】

図23の受光素子部90aは、図20及び図21の実施例15の受光素子部90と同様にシリコン半導体基板3の外周部分32の右半分と発光半導体領域7の側面17の右半分とに形成され、受光素子用のp型半導体薄膜95とn型半導体薄膜91と電極層92とを有する。

10

## 【0079】

受光素子用p型半導体薄膜95は図8の保護素子用p型半導体薄膜50と同一材料且つ同一方法で形成され、p型シリコン半導体基板3の外周部分32に電気的に接続されている部分と光透過性を有する絶縁膜10'を介して発光半導体領域7の側面17上に配置されている部分とを有する。

## 【0080】

図23の受光素子用n型半導体薄膜91は、図8の保護素子用n型半導体薄膜11と同一材料且つ同一方法で形成され、且つp型半導体薄膜95にpn接触している部分と光透過性を有する絶縁膜10'を介して側面17に対向配置されている部分とを有する。受光素子用p型半導体薄膜95及び受光素子用n型半導体薄膜91は、発光半導体領域7から放射された光を吸収できる材料(例えばシリコン)で形成される。従って、受光素子用p型半導体薄膜95及び受光素子用n型半導体薄膜91とで形成されるホトダイオードは図20の実施例15のホトダイオードと同様に機能する。

20

## 【0081】

受光素子用電極層92は、図20と同様にn型半導体薄膜91に電気的に接続されている。受光素子部90aにおけるp型シリコン半導体基板3の外周部分32はp型半導体薄膜95を第2の電極9に電気的に接続する機能を有する。なお、この受光素子部90aにおける外周部分32は発光半導体領域7から放射された光を吸収できる材料から選択されたシリコン半導体から成るので、光導電効果を有し、発光半導体領域7から光が発生した時に導電率が増加する。

30

## 【0082】

図23の実施例16の複合半導体装置は、図20の実施例15と同一の効果を有する。

## 【0083】

図23の複合半導体装置の図示が省略されている保護素子部は、コストの低減のために図8と同様に形成されているが、この代りに図1の保護素子部2、図10の保護素子部2f、図12の保護素子部2g、図13の保護素子部2h、図14の保護素子部2i、又は図15の保護素子部2j等を設けることができる。

## 【実施例 17】

## 【0084】

図24に実施例17の複合半導体装置の一部が示されている。この実施例17の複合半導体装置は、図20及び図21に示す実施例15のp型シリコン半導体基板3をn型シリコン半導体基板3aに変形し、且つ受光素子部90をホトトランジスタ機能を有する受光素子部90bに変形し、且つ図20及び図21の保護素子部2の構成を図10の保護素子部2fに変形したものに相当する。

40

## 【0085】

図24の受光素子部90bは、図20及び図21の実施例15の受光素子部90と同様にシリコン半導体基板3の外周部分32の右半分と発光半導体領域7の側面17の右半分とに形成され、n-p-n型受光素子用のn型半導体薄膜61aとp型半導体薄膜62aとn型半導体薄膜63aと電極層92とを有する。

50

**【0086】**

受光素子用 n 型半導体薄膜 6 1 a は図 1 0 の保護素子用 n 型半導体薄膜 6 1 と同一材料及び同一方法で形成され、且つ n 型半導体基板 3 a の外周部分 3 2 に電気的に接続された部分と光透過性を有する絶縁膜 1 0 ' を介して発光半導体領域 7 の側面 1 7 に対向配置された部分とを有する。なお、受光素子用 n 型半導体薄膜 6 1 a と n 型半導体基板 3 a の外周部分 3 2 との間に金属層を配置することができる。

**【0087】**

受光素子用 p 型半導体薄膜 6 2 a は図 1 0 の保護素子用 p 型半導体薄膜 6 1 と同一材料且つ同一方法で形成され、n 型半導体薄膜 6 1 a に p n 接触している部分と光透過性を有する絶縁膜 1 0 ' を介して発光半導体領域 7 の側面 1 7 上に配置されている部分とを有する。10

**【0088】**

図 2 4 の受光素子用 n 型半導体薄膜 6 3 a は、図 1 0 の保護素子用 n 型半導体薄膜 6 3 と同一材料且つ同一方法で形成され、p 型半導体薄膜 6 2 a に p n 接触している部分と光透過性を有する絶縁膜 1 0 ' を介して側面 1 7 に対向配置されている部分とを有する。なお、受光素子用 n 型半導体薄膜 6 1 a 、受光素子用 p 型半導体薄膜 6 2 a 及び受光素子用 n 型半導体薄膜 6 3 a は、発光半導体領域 7 から放射された光を吸収できる材料（例えばシリコン）で形成される。

**【0089】**

受光素子用電極層 9 2 は、n 型半導体薄膜 6 3 a に電気的に接続されている。受光素子部 9 0 b における n 型シリコン半導体基板 3 a の外周部分 3 2 は n 型半導体薄膜 6 1 a を第 2 の電極 9 に電気的に接続する機能を有する。なお、この受光素子部 9 0 b における外周部分 3 2 はシリコン半導体から成るので、光導電効果を有し、発光半導体領域 7 から光が発生した時に導電率が増加する。20

**【0090】**

図 2 4 の実施例 1 7 の n 型半導体薄膜 6 1 a と p 型半導体薄膜 6 2 a と n 型半導体薄膜 6 3 a とから成る n p n 3 層構成はホトトランジスタとして機能する。ホトトランジスタはホトダイオードと同様に光パワーを電気パワーに変換する機能を有するので、図 2 4 の複合半導体装置は、図 2 0 の実施例 1 5 と同一の効果を有する。

**【0091】**

図 2 4 の複合半導体装置の図示が省略されている保護素子部は、コストの低減のために図 1 0 と同様に形成されているが、この代りに図 1 の保護素子部 2 、図 8 の保護素子部 2 d 、図 1 2 の保護素子部 2 g 、図 1 3 の保護素子部 2 h 、図 1 4 の保護素子部 2 i 、又は図 1 5 の保護素子部 2 j 等を設けることができる。30

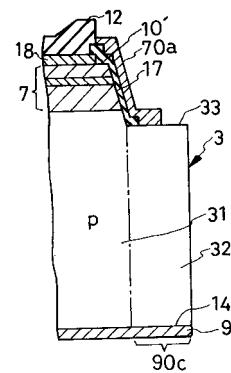

**【実施例 1 8】****【0092】**

図 2 5 に実施例 1 8 の複合半導体装置の一部が示されている。この実施例 1 8 の複合半導体装置は、図 2 0 及び図 2 1 に示す実施例 1 5 の複合半導体装置の受光素子部 9 0 をショットキーダイオードから成る受光素子部 9 0 c に変形し、且つ図 2 0 及び図 2 1 の保護素子部 2 の構成を図 1 2 の保護素子部 2 g に変形したものに相当する。40

**【0093】**

図 2 5 の受光素子部 9 0 c は、図 2 0 及び図 2 1 の実施例 1 5 の受光素子部 9 0 と同様にシリコン半導体基板 3 の外周部分 3 2 の右半分と発光半導体領域 7 の側面 1 7 の右半分とに形成され、ショットキー電極として機能する金属層 7 0 a を有する。

**【0094】**

受光素子部 9 0 c における金属層 7 0 a は、図 1 2 の保護素子部 2 g における金属層 7 0 と同一材料且つ同一方法で形成され、p 型シリコン半導体基板 3 の外周部分 3 2 にショットキー接觸している部分と絶縁膜 1 0 ' を介して発光半導体領域 7 の側面 1 7 上に配置されている部分とを有する。

**【0095】**1020304050

受光素子部 90c の金属層 70a は、図 22 の第 3 の端子 94 と同様に受光出力端子として機能する。受光素子部 90c における p 型シリコン半導体基板 3 の外周部分 32 は金属層 70a を伴ってショットキーダイオードを構成する機能の他に、これを第 2 の電極 9 に電気的に接続する機能を有する。なお、この受光素子部 90c における外周部分 32 はシリコン半導体から成るので、光導電効果を有し、発光半導体領域 7 から光が発生した時に導電率が増加する。なお、金属層 70a がショットキー接触する半導体基板 3 を、シリコン以外の発光半導体領域 7 から放射された光を吸収できる材料で形成することができる。

#### 【 0 0 9 6 】

図 25 の実施例 18 の複合半導体装置は、図 20 の実施例 15 と同一の効果を有する。

10

#### 【 0 0 9 7 】

図 25 の複合半導体装置の図示が省略されている保護素子部は、コストの低減のために図 12 と同様に形成されているが、この代りに図 1 の保護素子部 2 、図 8 の保護素子部 2d 、図 10 の保護素子部 2f 、図 13 の保護素子部 2h 、図 14 の保護素子部 2i 、又は図 15 の保護素子部 2j 等を設けることができる。

#### 【 実施例 19 】

#### 【 0 0 9 8 】

図 26 に実施例 19 の複合半導体装置が示されている。この実施例 19 の複合半導体装置は、図 20 及び図 21 に示す実施例 15 の複合半導体装置の受光素子部 90d をホトダイオードから成る受光素子部 90a に変形し、且つ図 20 及び図 21 の保護素子部 2 の構成を図 13 の保護素子部 2h に変形したものに相当する。

20

#### 【 0 0 9 9 】

図 26 の受光素子部 90d は、図 20 及び図 21 の実施例 15 の受光素子部 90 と同様にシリコン半導体基板 3 の外周部分 32 の右半分と発光半導体領域 7 の側面 17 の右半分とに形成され、受光素子用の n 型半導体領域 34a と金属層 71a とを有する。

#### 【 0 1 0 0 】

受光素子用 n 型半導体領域 34a は図 13 の保護素子用 n 型半導体領域 34 と同一材料且つ同一方法で p 型半導体基板 3 内に形成されている。即ち、ホトダイオードを構成するための受光素子用 n 型半導体領域 34a は、これと p 型半導体基板 3 の外周部分 32 との間に p-n 接合を生じさせるために、p 型シリコン半導体基板 3 の外周部分 32 の一方の正面 33 側に形成されている。半導体基板 3 及び受光素子用 n 型半導体領域 34a を、シリコン以外の発光半導体領域 7 から放射された光を吸収できる材料で形成することができる。

30

#### 【 0 1 0 1 】

受光素子用金属層 71a は、図 13 の保護素子用金属層 71 と同様に絶縁膜 10' の上に形成され、その一端は n 型半導体領域 34a に電気的に接続されている。受光素子部 90d における p 型シリコン半導体基板 3 の外周部分 32 はホトダイオードの p 型領域として機能すると共に、このホトダイオードを第 2 の電極 9 に電気的に接続する機能を有する。なお、この受光素子部 90d における外周部分 32 はシリコン半導体から成るので、光導電効果を有し、発光半導体領域 7 から光が発生した時に導電率が増加する。

40

#### 【 0 1 0 2 】

図 26 の実施例 19 の複合半導体装置は、図 20 の実施例 15 と同一の効果を有する。

#### 【 0 1 0 3 】

図 26 の複合半導体装置の保護素子部 2h の代りに図 1 の保護素子部 2 、図 8 の保護素子部 2d 、図 10 の保護素子部 2f 、図 12 の保護素子部 2g 、図 14 の保護素子部 2i 、又は図 15 の保護素子部 2j 等を設けることもできる。

#### 【 実施例 20 】

#### 【 0 1 0 4 】

図 27 に実施例 20 の複合半導体装置の一部が示されている。この実施例 20 の複合半導体装置は、図 20 及び図 21 に示す実施例 15 の複合半導体装置の p 型シリコン半導体

50

基板 3 を n 型シリコン半導体基板 3 a に変形し、且つ受光素子部 9 0 e を n p n ホトトランジスタから成る受光素子部 9 0 e に変形し、且つ図 2 0 及び図 2 1 の保護素子部 2 の構成を図 1 4 の保護素子部 2 i に変形したものに相当する。

#### 【 0 1 0 5 】

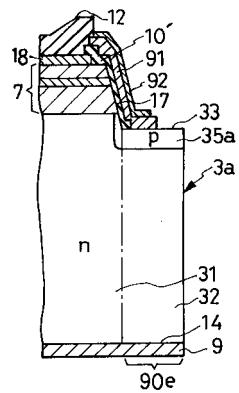

図 2 7 の受光素子部 9 0 e は、図 2 0 及び図 2 1 の実施例 1 5 の受光素子部 9 0 と同様にシリコン半導体基板 3 a の外周部分 3 2 の右半分と発光半導体領域 7 の側面 1 7 の右半分とに形成され、n p n ホトトランジスタを構成するための受光素子用の p 型半導体領域 3 5 a と図 2 0 と同一の n 型半導体薄膜 9 1 と電極層 9 2 とを有する。

#### 【 0 1 0 6 】

受光素子用 p 型半導体領域 3 5 a は図 1 4 の保護素子用 p 型半導体領域 3 5 と同一材料 10 且つ同一方法で形成され、n 型シリコン半導体基板 3 a の外周部分 3 2 の一方の主面 3 3 に露出している。

#### 【 0 1 0 7 】

図 2 7 の受光素子用 n 型半導体薄膜 9 1 は、図 1 4 の保護素子用 n 型半導体薄膜 1 1 と同一材料且つ同一方法で形成され、且つ半導体基板 3 a の p 型半導体領域 3 5 a に p n 接触している部分と光透過性を有する絶縁膜 1 0 ' を介して側面 1 7 に対向配置されている部分とを有する。なお、半導体基板 3 a 、受光素子用 p 型半導体領域 3 5 a 及び受光素子用 n 型半導体薄膜 9 1 は、発光半導体領域 7 から放射された光を吸収できる材料（例えばシリコン）で形成される。

#### 【 0 1 0 8 】

受光素子用電極層 9 2 は、n 型半導体薄膜 9 1 に電気的に接続され、図 2 2 の第 3 の端子 9 4 と同様に受光出力端子として機能する。受光素子部 9 0 e における p 型シリコン半導体基板 3 a の外周部分 3 2 は p 型半導体領域 3 5 a の形成に利用されていると共に、n p n ホトトランジスタを第 2 の電極 9 に電気的に接続する機能を有する。なお、この受光素子部 9 0 e における外周部分 3 2 はシリコン半導体から成るので、光導電効果を有し、発光半導体領域 7 から光が発生した時に導電率が増加する。

#### 【 0 1 0 9 】

図 2 7 の実施例 2 0 の複合半導体装置は、n 型シリコン半導体基板 3 a と p 型半導体領域 3 5 a と n 型半導体薄膜 9 1 とから成る n p n ホトトランジスタを有するので、図 2 0 の実施例 1 5 と同一の効果を得ることができる。

#### 【 0 1 1 0 】

図 2 7 の複合半導体装置の図示が省略されている保護素子部は、コスト低減のために図 1 4 と同様に形成されているが、この代りに図 1 の保護素子部 2 、図 8 の保護素子部 2 d 、図 1 0 の保護素子部 2 f 、図 1 2 の保護素子部 2 g 、図 1 3 の保護素子部 2 h 、又は図 1 5 の保護素子部 2 j 等を設けることができる。

#### 【 実施例 2 1 】

#### 【 0 1 1 1 】

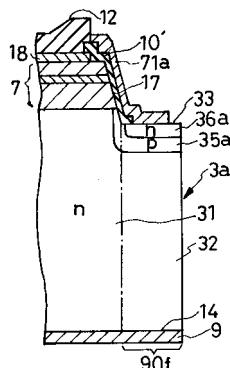

図 2 8 に実施例 2 1 の複合半導体装置の一部が示されている。この実施例 2 1 の複合半導体装置は、図 2 0 及び図 2 1 に示す実施例 1 5 の複合半導体装置の p 型シリコン半導体基板 3 を n 型シリコン半導体基板 3 a に変形し、且つ受光素子部 9 0 をホトトランジスタから成る受光素子部 9 0 f に変形し、且つ図 2 0 及び図 2 1 の保護素子部 2 の構成を図 1 5 の保護素子部 2 j に変形したものに相当する。

#### 【 0 1 1 2 】

図 2 8 の受光素子部 9 0 f は、図 2 0 及び図 2 1 の実施例 1 5 の受光素子部 9 0 と同様にシリコン半導体基板 3 a の外周部分 3 2 の右半分と発光半導体領域 7 の側面 1 7 の右半分とに形成され、受光素子用の p 型半導体領域 3 5 a と n 型半導体領域 3 6 a と金属層 7 1 a とを有する。

#### 【 0 1 1 3 】

受光素子用 p 型半導体領域 3 5 a は図 1 5 の保護素子用 p 型半導体領域 3 5 と同一材料 50 且つ同一方法で形成され、p 型シリコン半導体基板 3 a の外周部分 3 2 に配置されている

。

## 【0114】

図28の受光素子用n型半導体領域36aは、図15の保護素子用n型半導体領域36と同一材料且つ同一方法で形成され、且つp型半導体領域35aにpn接觸している。半導体基板3a、受光素子用p型半導体領域35a及び受光素子用n型半導体領域36aを、シリコン以外の発光半導体領域7から放射された光を吸収できる材料で形成することができる。

## 【0115】

受光素子用金属層71aは図15の保護素子用金属層71と同一材料且つ同一方法で形成され、n型半導体領域36aに電気的に接続され、図22の第3の端子94と同様な機能を有する。受光素子部90fにおけるn型シリコン半導体基板3aの外周部分32はn-p-nホトトランジスタの形成に使用されていると共に、このホトトランジスタを第2の電極9に電気的に接続するためにも使用されている。なお、この受光素子部90fにおける外周部分32はシリコン半導体から成るので、光導電効果を有し、発光半導体領域7から光が発生した時に導電率が増加する。

## 【0116】

図28の実施例21の複合半導体装置のn-p-nホトトランジスタは、ホトダイオードと同様に受光素子として機能するので、図28の実施例21は図20の実施例15と同一の効果を有する。

## 【0117】

図28の複合半導体装置の図示が省略されている保護素子部は、コスト低減のために図15と同様に形成されているが、この代りに図1の保護素子部2、図8の保護素子部2d、図10の保護素子部2f、図12の保護素子部2g、図13の保護素子部2h、又は図14の保護素子部2i等を設けることができる。

## 【0118】

本発明は上述の実施例に限定されるものではなく、例えば次の変形が可能なものである。

(1) 図5～図10、図12～図16、図18、図20、及び図23～図28に示す実施例1～13、及び15～21の光透過性電極18、及び図19の帯状電極18aを省くこともできる。この場合には発光半導体領域7に周知の電流分散層を設けることが望ましい。

(2) 図8、図9、図10及び図16の半導体基板3, 3aを金属基板に置き換えることができる。

(3) 発光半導体領域7から基板3, 3a, 3b側に放射された光を発光半導体領域7の第1の主面15側に反射させる機能を第2の電極9に与えること、又は独立した反射層を基板3, 3a, 3bの一方の主面13側又は他方の主面14側に設けることができる。

(4) 必要に応じて基板3, 3aの他方の主面14から光を取り出すことができる。

(5) 半導体基板3, 3aの外周部分32の不純物濃度を中央部分31と異なる値にすることができる。

(6) 半導体基板3, 3a、発光半導体領域7の各層4～6、保護素子部2～2mの各半導体薄膜11, 50, 61, 62, 63、基板内の半導体領域34, 35, 36、を実施例と反対の導電型にすることができる。

(7) シリコン半導体基板3又は3aを単結晶シリコン以外の多結晶シリコン又はSiC等のシリコン化合物、又は3-5族化合物半導体とすることができる。

(8) 半導体基板3又は3aの上に発光半導体領域7を気相成長させる代わりに、半導体基板3又は3a又は金属基板3bに発光半導体領域2を熱圧着等で貼り合わせることができる。

(9) 保護素子部2～2lの保護素子に、これとは別の機能を有する保護素子、例えば、pn接合ダイオード、n-p-n又はpn-pの3層ダイオード、ショットキーダイオード、バリスタ、及びコンデンサ等から選択されたものを付加することができる。特にpn接

10

20

30

40

50

合ダイオード等にコンデンサを並列に接続することは過電圧保護に有効である。

(10) 図1、図5～図10、図13、図14、図16、図18及び図19の保護素子部における保護素子を、半導体薄膜で形成する代りに半導体厚膜で形成すること、又はダイオード、パリスタ、及びコンデンサ等の個別部品で形成すること、又は半導体薄膜と半導体厚膜と個別部品から選択された複数の組合せで形成することができる。

(11) 受光素子としてホトダイオード又はホトトランジスタを設ける代わりに、光導電型受光素子(光導電型センサ)を設けることができる。光導電型受光素子は図25の金属層70aを光吸収可能な半導体基板3にオーミック接触させることによって得られる。なお、図25の半導体基板3は光導電効果を有するので、図25の受光素子をショットキーバリヤ型の受光素子と光導電型受光素子との組み合わせ素子と呼ぶこともできる。 10

(12) 図20、図23～図28の絶縁膜10の部分に、これに代わって保護膜12の延長部分を設けることができる。

(13) 図20、図23～図28の受光素子部に、光入力が要求されている箇所以外を覆うための遮光層を設けることができる。

#### 【産業上の利用可能性】

#### 【0119】

本発明は、半導体発光素子と保護素子との複合半導体装置に利用可能である。

#### 【図面の簡単な説明】

#### 【0120】

【図1】本発明の実施例1に従う複合半導体装置を概略的に示す中央縦断面図である。 20

【図2】図1の複合半導体装置の発光半導体領域及び半導体基板を縮小して示す平面図である。

【図3】図1の発光半導体領域と半導体基板の一部を切断前のウエハ状態で示す断面図である。

【図4】図1の複合半導体装置の電気回路図である。

【図5】実施例2の複合半導体装置を概略的に示す中央縦断面図である。

【図6】実施例3の複合半導体装置を概略的に示す中央縦断面図である。

【図7】実施例4の複合半導体装置を概略的に示す中央縦断面図である。

【図8】実施例5の複合半導体装置を概略的に示す中央縦断面図である。

【図9】実施例6の複合半導体装置を概略的に示す中央縦断面図である。 30

【図10】実施例7の複合半導体装置を概略的に示す中央縦断面図である。

【図11】図10の複合半導体装置の電気回路図である。

【図12】実施例8の複合半導体装置を概略的に示す中央縦断面図である。

【図13】実施例9の複合半導体装置を概略的に示す中央縦断面図である。

【図14】実施例10の複合半導体装置を概略的に示す中央縦断面図である。

【図15】実施例11の複合半導体装置を概略的に示す中央縦断面図である。

【図16】実施例12の複合半導体装置を概略的に示す中央縦断面図である。

【図17】図16の複合半導体装置の電気回路図である。

【図18】実施例13の複合半導体装置を概略的に示す中央縦断面図である。

【図19】実施例14の複合半導体装置を概略的に示す中央縦断面図である。 40

【図20】実施例15の複合半導体装置を概略的に示す中央縦断面図である。

【図21】図20の複合半導体装置を保護膜を省いて示す平面図である。

【図22】図20の複合半導体装置の電気回路図である。

【図23】実施例16の複合半導体装置の一部を概略的に示す中央縦断面図である。

【図24】実施例17の複合半導体装置の一部を概略的に示す中央縦断面図である。

【図25】実施例18の複合半導体装置の一部を概略的に示す中央縦断面図である。

【図26】実施例19の複合半導体装置を概略的に示す中央縦断面図である。

【図27】実施例20の複合半導体装置の一部を概略的に示す中央縦断面図である。

【図28】実施例21の複合半導体装置の一部を概略的に示す中央縦断面図である。

【図29】従来の保護素子を伴う発光素子を示す電気回路図である。 50

## 【符号の説明】

## 【0121】

- 1 ~ 1 d 発光素子部

- 2 ~ 2 1 保護素子部

- 3 , 3 a 半導体基板

- 7 発光半導体領域

- 8 第1の電極

- 9 第2の電極

- 10 絶縁膜

- 11 n型半導体薄膜

- 12 保護膜

10

【図1】

【図2】

【図3】

【図4】

【 图 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図25】

【図24】

【図26】

【図27】

【図28】

【図29】

---

フロントページの続き

(72)発明者 丹羽 愛玲

埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内

(72)発明者 神井 康宏

埼玉県新座市北野三丁目6番3号 サンケン電気株式会社内

審査官 百瀬 正之

(56)参考文献 特開2001-230448(JP,A)

国際公開第2004/109782(WO,A1)

特開昭62-069693(JP,A)

特開平11-298041(JP,A)

特表平11-507182(JP,A)

特開平10-065215(JP,A)

特開平10-200159(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64