(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

特許第7043201号

(P7043201)

(45)発行日 令和4年3月29日(2022.3.29)

(24)登録日 令和4年3月18日(2022.3.18)

(51)国際特許分類

|        |                  |     |        |        |

|--------|------------------|-----|--------|--------|

| H 04 L | 45/28 (2022.01)  | F I | H 04 L | 45/28  |

| H 04 L | 47/125 (2022.01) |     | H 04 L | 47/125 |

| G 06 F | 13/00 (2006.01)  |     | G 06 F | 13/00  |

請求項の数 20 (全24頁)

|                   |                             |          |                                                                                         |

|-------------------|-----------------------------|----------|-----------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2017-156664(P2017-156664) | (73)特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路12<br>9    |

| (22)出願日           | 平成29年8月14日(2017.8.14)       |          |                                                                                         |

| (65)公開番号          | 特開2018-29337(P2018-29337A)  |          |                                                                                         |

| (43)公開日           | 平成30年2月22日(2018.2.22)       |          |                                                                                         |

| 審査請求日             | 令和2年8月11日(2020.8.11)        |          |                                                                                         |

| (31)優先権主張番号       | 62/377487                   | (74)代理人  | 110000051                                                                               |

| (32)優先日           | 平成28年8月19日(2016.8.19)       | (72)発明者  | 特許業務法人共生国際特許事務所<br>グネスワラ アール・マリブディ<br>アメリカ合衆国 94555 カリフォルニア州 フレモント ミモサ テラス 34<br>最終頁に続く |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |          |                                                                                         |

| (31)優先権主張番号       | 15/344438                   |          |                                                                                         |

| (32)優先日           | 平成28年11月4日(2016.11.4)       |          |                                                                                         |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |          |                                                                                         |

| 早期審査対象出願          |                             |          |                                                                                         |

| 前置審査              |                             |          |                                                                                         |

(54)【発明の名称】 コンピューティング資源への高可用性アクセスを提供するコンピューティングシステム及び予備資源連結ファブリック

**(57)【特許請求の範囲】****【請求項1】**

コンピューティング資源への高可用性アクセスを提供するコンピューティングシステムであって、

複数のインターフェイスと、

複数のコンピューティング資源セットと、

少なくとも3つからなる複数のスイッチと、を備え、

前記コンピューティング資源セットの各々は、複数のコンピューティング資源を含み、

前記複数のスイッチの各々は、ホストリンクを通じて前記インターフェイスの中の対応する1つに連結され、複数の資源連結を通じて前記複数のコンピューティング資源セットの中の対応する複数のコンピューティング資源セットのコンピューティング資源に直接連結され、前記複数のスイッチの中の1つが故障の場合、前記複数のスイッチの間の複数のクロス接続を通じて前記複数のスイッチの中の残りのスイッチにデータトラフィックが分散されるように構成され、

前記コンピューティングシステムは、N個(但し、Nは自然数)のインターフェイスを含み、

前記コンピューティング資源セットのコンピューティング資源の中の1つが全処理量を達成するのに要求されるトラフィック帯域幅の量を帯域幅ユニットB(但し、Bは正数)で表す場合、前記複数の資源連結の各々は、少なくとも $1 \times B$ のトラフィック帯域幅を有し、各コンピューティング資源セットがK(但し、Kは自然数)個のコンピューティング資源

を有する場合、前記複数のインターフェイスの各々の各ホストリンクは、 $K \times B$  のトラフィック帯域幅を支援し、

前記複数のクロス接続の各クロス接続は、少なくとも  $K \times B / (N - 1)$  のトラフィック帯域幅を有することを特徴とするコンピューティングシステム。

#### 【請求項 2】

前記少なくとも 3 つからなる複数のスイッチは、

第 1 スイッチと、

第 2 スイッチと、

第 1 クロス接続を通じて前記第 1 スイッチに直接連結され、第 2 クロス接続を通じて前記第 2 スイッチに直接連結される第 3 スイッチと、を含むことを特徴とする請求項 1 に記載のコンピューティングシステム。 10

#### 【請求項 3】

第 1 ホストリンクを通じて前記第 1 スイッチに連結され、前記複数のインターフェイスの中の第 1 インターフェイスを含む第 1 サーバーノードと、

第 2 ホストリンクを通じて前記第 2 スイッチに連結され、前記複数のインターフェイスの中の第 2 インターフェイスを含む第 2 サーバーノードと、を更に含むことを特徴とする請求項 2 に記載のコンピューティングシステム。 20

#### 【請求項 4】

第 3 ホストリンクを通じて前記第 3 スイッチに連結される第 3 サーバーノードを更に含むことを特徴とする請求項 3 に記載のコンピューティングシステム。 20

#### 【請求項 5】

前記第 1 サーバーノードに直接連結される第 1 補助スイッチと、

前記第 2 サーバーノードに直接連結される第 2 補助スイッチと、

前記第 3 サーバーノードに直接連結される第 3 補助スイッチと、

前記第 1 補助スイッチを前記第 2 補助スイッチに直接連結する第 1 クロス接続と、

前記第 1 補助スイッチを前記第 3 補助スイッチに直接連結する第 2 クロス接続と、

前記第 2 補助スイッチを前記第 3 補助スイッチに直接連結する第 3 クロス接続と、を更に含むことを特徴とする請求項 4 に記載のコンピューティングシステム。 30

#### 【請求項 6】

前記複数のコンピューティング資源セットの中の第 1 コンピューティング資源セットは、前記複数のコンピューティング資源として複数のデータ格納装置を含む第 1 データ格納装置セットを含み、

前記第 1 データ格納装置セットのデータ格納装置の各々は、前記複数の資源連結の中の第 1 資源連結を通じて前記第 1 スイッチに直接連結される第 1 ポートと、前記複数の資源連結の中の第 2 資源連結を通じて前記第 2 スイッチに直接連結される第 2 ポートとを有し、前記複数のコンピューティング資源セットの中の第 2 コンピューティング資源セットは、前記複数のコンピューティング資源として複数のデータ格納装置を含む第 2 データ格納装置セットを含み、

前記第 2 データ格納装置セットのデータ格納装置の各々は、前記複数の資源連結の中の第 3 資源連結を通じて前記第 1 スイッチに直接連結される第 1 ポートと、前記複数の資源連結の中の第 4 資源連結を通じて前記第 2 スイッチに直接連結される第 2 ポートとを有することを特徴とする請求項 3 に記載のコンピューティングシステム。 40

#### 【請求項 7】

第 3 クロス接続を通じて前記第 1 スイッチに直接連結され、第 4 クロス接続を通じて前記第 2 スイッチに直接連結される第 4 スイッチを更に含むことを特徴とする請求項 6 に記載のコンピューティングシステム。

#### 【請求項 8】

前記複数のコンピューティング資源として複数のデータ格納装置を含む第 3 データ格納装置セットを更に含み、

前記第 3 データ格納装置セットのデータ格納装置の各々は、第 5 資源連結を通じて前記第 50

3スイッチに直接連結される第1ポートと、第6資源連結を通じて前記第4スイッチに直接連結される第2ポートとを有することを特徴とする請求項7に記載のコンピューティングシステム。

**【請求項9】**

第4ホストリンクを通じて前記第4スイッチに直接連結される第4サーバーノードを更に含むことを特徴とする請求項8に記載のコンピューティングシステム。

**【請求項10】**

前記複数のコンピューティング資源として複数のデータ格納装置を含む第4データ格納装置セットを更に含み、

前記第4データ格納装置セットのデータ格納装置の各々は、第7資源連結を通じて前記第3スイッチに直接連結される第1ポートと、第8資源連結を通じて前記第4スイッチに直接連結される第2ポートとを有することを特徴とする請求項9に記載のコンピューティングシステム。10

**【請求項11】**

前記複数のスイッチの各々は、他のスイッチの故障を検出し、前記複数のスイッチの各々に対応する各クロス接続及び前記ホストリンクを通じて前記第1データ格納装置セット及び前記第2データ格納装置セットへのアクセスを提供するように構成されることを特徴とする請求項6に記載のコンピューティングシステム。

**【請求項12】**

前記複数のスイッチは、PCIe (Peripheral Component Interconnect Express) スイッチであり、20

前記ホストリンク及び前記複数の資源連結は、PCIeバスリンクであることを特徴とする請求項1に記載のコンピューティングシステム。

**【請求項13】**

少なくとも2つの高可用性ペア (high-availability pairs) を備えるコンピューティングシステムであって、

各高可用性ペアは、

第1スイッチと、

第2スイッチと、

第1ホストリンクを通じて前記第1スイッチに連結される第1インターフェイスと、30

第2ホストリンクを通じて前記第2スイッチに連結される第2インターフェイスと、

第1資源連結を通じて前記第1スイッチに直接連結され、第2資源連結を通じて前記第2スイッチに直接連結される複数のコンピューティング資源を含む第1コンピューティング資源セットと、

第3資源連結を通じて前記第1スイッチに直接連結され、第4資源連結を通じて前記第2スイッチに直接連結される複数のコンピューティング資源を含む第2コンピューティング資源セットと、

複数の第1クロス接続と、

複数の第2クロス接続と、を含み、

前記第1クロス接続の各々は、前記第1スイッチを他の高可用性ペアの各々の各スイッチに直接連結し、40

前記第2クロス接続の各々は、前記第2スイッチを前記他の高可用性ペアの各々の各スイッチに直接連結し、

前記コンピューティングシステムは、N個（但し、Nは自然数）のサーバーノードを含み、前記第1及び第2コンピューティング資源セットのコンピューティング資源の中の1つが全処理量を達成するのに要求されるトラフィック帯域幅の量を帯域幅ユニットB（但し、Bは正数）で表す場合、前記第1～第4資源連結の各々は、少なくとも $1 \times B$ のトラフィック帯域幅を有し、

各コンピューティング資源セットはがK（但し、Kは自然数）個のコンピューティング資源を有する場合、各サーバーノードは、 $K \times B$ のトラフィック帯域幅を支援し、50

前記第1及び第2クロス接続の各々は、少なくともK×B/(N-1)のトラフィック帯域幅を有することを特徴とするコンピューティングシステム。

**【請求項14】**

前記第1コンピューティング資源セットは、前記複数のコンピューティング資源として複数のデータ格納装置を含む第1データ格納装置セットを含み、

前記第1データ格納装置セットのデータ格納装置の各々は、前記第1資源連結を通じて前記第1スイッチに直接連結される第1ポートと、前記第2資源連結を通じて前記第2スイッチに直接連結される第2ポートとを有し、

前記第2コンピューティング資源セットは、前記複数のコンピューティング資源として複数のデータ格納装置を含む第2データ格納装置セットを含み、

前記第2データ格納装置セットのデータ格納装置の各々は、前記第3資源連結を通じて前記第1スイッチに直接連結される第1ポートと、前記第4資源連結を通じて前記第2スイッチに直接連結される第2ポートとを有することを特徴とする請求項13に記載のコンピューティングシステム。

**【請求項15】**

前記第1スイッチは、前記第2スイッチの故障を検出し、前記第1ホストリンク及び前記第1クロス接続を通じて前記第1データ格納装置セット及び前記第2データ格納装置セットへのアクセスを提供するように構成されることを特徴とする請求項14に記載のコンピューティングシステム。

**【請求項16】**

前記第1及び第2スイッチは、PCIe(Peripheral Component Interconnect Express)スイッチであり、

前記第1及び第2ホストリンク及び前記第1～第4資源連結は、PCIeバスリンクであることを特徴とする請求項13に記載のコンピューティングシステム。

**【請求項17】**

前記少なくとも2つの高可用性ペアは、

第1高可用性ペアと、

第2高可用性ペアと、

第3高可用性ペアと、

第4高可用性ペアと、を含むことを特徴とする請求項13に記載のコンピューティングシステム。

**【請求項18】**

予備資源連結ファブリックであって、

第1スイッチと、

第2スイッチと、

第1クロス接続を通じて前記第1スイッチに直接連結され、第2クロス接続を通じて前記第2スイッチに直接連結される第3スイッチと、

複数のコンピューティング資源を含む第1コンピューティング資源セットと、

複数のコンピューティング資源を含む第2コンピューティング資源セットと、を備え、

前記第1コンピューティング資源セットのコンピューティング資源の各々は、第1資源連結を通じて前記第1スイッチに直接連結される第1ポートと、第2資源連結を通じて前記第2スイッチに直接連結される第2ポートとを有し、

前記第2コンピューティング資源セットのコンピューティング資源の各々は、第3資源連結を通じて前記第1スイッチに直接連結される第1ポートと、第4資源連結を通じて前記第2スイッチに直接連結される第2ポートとを有し、

前記予備資源連結ファブリックは、N個(但し、Nは自然数)のインターフェイスを更に含み、前記第1～第3スイッチの各々は、ホストリンクを通じて前記N個のインターフェイスの対応する1つに連結され、

前記第1及び第2コンピューティング資源セットのコンピューティング資源の中の1つが全処理量を達成するのに要求されるトラフィック帯域幅の量を帯域幅ユニットB(但し、

10

20

30

40

50

B は正数)で表す場合、前記第1～第4資源連結の各々は、少なくとも  $1 \times B$  のトラフィック帯域幅を有し、

各コンピューティング資源セットが K (但し、K は自然数) 個のコンピューティング資源を有する場合、前記 N 個のインターフェイスの各々の各ホストリンクは、 $K \times B$  のトラフィック帯域幅を支援し、

前記第1クロス接続及び前記第2クロス接続の各々は、少なくとも  $K \times B / (N - 1)$  のトラフィック帯域幅を有することを特徴とする予備資源連結ファブリック。

#### 【請求項 19】

前記第1スイッチは、前記第2スイッチの故障を検出し、前記第1クロス接続を通じて前記第1コンピューティング資源セット及び前記第2コンピューティング資源セットへのアクセスを提供するように構成されることを特徴とする請求項18に記載の予備資源連結ファブリック。

10

#### 【請求項 20】

第3資源連結を通じて前記第1スイッチに直接連結され、第4資源連結を通じて前記第2スイッチに直接連結される第4スイッチを更に含むことを特徴とする請求項18に記載の予備資源連結ファブリック。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明はコンピューティング資源への高可用性アクセスを提供するコンピュータシステム及び予備資源連結ファブリックに係り、より詳しくは、冗長性 (redundancy) を提供するコンピュータシステム及び予備資源連結ファブリックに関する。

20

##### 【背景技術】

##### 【0002】

コンピュータシステムの分野において、データ及び他のコンピューティング資源への信頼性ある高性能アクセス (reliable and high performance access) はビジネス及び日常生活において重要である。高可用性 (HA; high availability) の用語は1つの要素の故障 (又は1つの障害箇所; single points of failure) を除去するか、又は減少させる (例えば、1つの要素の故障が全体システムの故障とならないようにシステムに冗長性を提供する) システムを説明するために頻繁に使用される。

30

##### 【0003】

高可用性の長所を有する例示的なコンピュータシステムは LAN (local area network) のようなコンピュータネットワーク又はインターネットを通じてデータの検索又は格納のためのデータ資源を提供できる SAN (storage area network) のようなデータ格納システムを含む。

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

本発明の目的は向上した性能を有するコンピューティング資源への高可用性及び負荷均性を提供するコンピューティングシステム及び予備資源連結ファブリックを提供することにある。

40

##### 【課題を解決するための手段】

##### 【0005】

本発明の目的は、適応的多重経路ファブリックの使用を通じてコンピューティング資源への高可用性及び負荷均等性を提供することにある。

##### 【0006】

本発明の一実施形態によれば、コンピューティング資源への高可用性アクセスを提供するコンピューティングシステムは、複数のインターフェイス、複数のコンピューティング資源セット、及び少なくとも3つのスイッチを含み、前記複数のコンピューティング資源セ

50

ットの各々は複数のコンピューティング資源を含み、前記少なくとも3つのスイッチの各々はホストリンクを通じて前記インターフェイスの中の対応する1つと連結され、複数の資源連結を通じて前記複数のコンピューティング資源セットの中の対応する1つと連結され、前記スイッチの中の1つが故障の場合、前記スイッチの間の複数のクロス接続を通じて前記スイッチの中の残されているスイッチにデータトラフィックが分散されるように構成される。

#### 【0007】

前記少なくとも3つのスイッチは第1スイッチ、第2スイッチ、及び第1クロス接続を通じて前記第1スイッチと直接連結され、第2クロス接続を通じて前記第2スイッチと直接連結される第3スイッチを含む。 10

#### 【0008】

前記コンピューティングシステムは第1ホストリンクを通じて前記第1スイッチと連結され、前記複数のインターフェイスの中の第1インターフェイスを含む第1サーバーノード、及び第2ホストリンクを通じて前記第2スイッチと連結され、前記複数のインターフェイスの中の第2インターフェイスを含む第2サーバーノードをさらに含む。

#### 【0009】

前記コンピューティングシステムは第3ホストリンクを通じて前記第3スイッチと連結される第3サーバーノードをさらに含む。

#### 【0010】

前記コンピューティングシステムは前記第1サーバーノードと直接連結される第1補助スイッチ、前記第2サーバーノードと直接連結される第2補助スイッチ、前記第3サーバーノードと直接連結される第3補助スイッチ、前記第1補助スイッチを前記第2補助スイッチと直接連結する第1クロス接続、前記第1補助スイッチを前記第3補助スイッチと直接連結する第2クロス接続、前記第2補助スイッチを前記第3補助スイッチと直接連結する第3クロス接続をさらに含む。 20

#### 【0011】

前記複数のコンピューティング資源セットの中の第1コンピューティング資源セットは第1データ格納装置セットを含み、前記第1データ格納装置セットのデータ格納装置の各々は前記複数の資源連結の中の第1資源連結を通じて前記第1スイッチと直接連結された第1ポート及び前記複数の資源連結の中の第2資源連結を通じて前記第2スイッチと直接連結された第2ポートを含み、前記複数のコンピューティング資源セットの中の第2コンピューティング資源セットは第2データ格納装置セットを含み、前記第2データ格納装置セットのデータ格納装置の各々は前記複数の資源連結の中の第3資源連結を通じて前記第1スイッチと直接連結された第3ポート及び前記複数の資源連結の中の第4資源連結を通じて前記2スイッチと直接連結される第4ポートを含む。 30

#### 【0012】

前記コンピューティングシステムは第3クロス接続を通じて前記第1スイッチと直接連結され、第4クロス接続を通じて前記第2スイッチと直接連結される第4スイッチをさらに含む。

#### 【0013】

前記コンピューティングシステムは第3データ格納装置セットをさらに含み、前記第3データ格納装置セットのデータ格納装置の各々は第5資源連結を通じて前記第3スイッチと直接連結される第5ポート及び第6資源連結を通じて前記第4スイッチと直接連結される第6ポートを含む。 40

#### 【0014】

前記コンピューティングシステムは第4ホストリンクを通じて前記第4スイッチと直接連結された第4サーバーノードをさらに含む。

#### 【0015】

前記コンピューティングシステムは第4データ格納装置セットをさらに含み、前記第4データ格納装置セットのデータ格納装置の各々は第7資源連結を通じて前記第3スイッチと

10

20

30

40

50

直接連結される第7ポート及び第8資源連結を通じて前記第4スイッチと直接連結される第8ポートを含む。

【0016】

前記スイッチの各々は他のスイッチの故障を検出し、前記スイッチに対応する前記クロス接続及び前記ホストリンクを通じて前記第1データ格納装置セットのデータ格納装置及び前記第2データ格納装置セットのデータ格納装置へのアクセスを提供するように構成される。

【0017】

前記コンピューティングシステムはN個（但し、Nは自然数）のインターフェイスを含み、帯域幅ユニットB（但し、Bは正数）は前記コンピューティング資源セットの中の1つが全帯域幅（full bandwidth）にて動作するのに要求されるトラフィック帯域幅の量を示し、前記複数の資源連結の各々は少なくとも $1 \times B$ のトラフィック帯域幅を含み、前記複数のコンピューティング資源セットの各々はK（但し、Kは自然数）個以下のコンピューティング資源を含み、前記複数のインターフェイスの各々のホストリンクの各々は $K \times B$ の正常のトラフィック帯域幅及び $K \times B$ 以上の最大のトラフィック帯域幅を支援し、前記複数のクロス接続の各々は少なくとも $K \times B / (N - 1)$ のトラフィック帯域幅を含む。

10

【0018】

前記スイッチはPCIe（Peripheral Component Interconnect Express）スイッチであり、前記ホストリンク及び前記資源連結はPCIeバスリンクである。

20

【0019】

本発明の一実施形態に係るコンピューティングシステムは少なくとも2つの高可用性ペア（high-availability pairs）を含み、前記高可用性ペアの各々は、第1スイッチ、第2スイッチ、第1ホストリンクを通じて前記第1スイッチと連結される第1インターフェイス、第2ホストリンクを通じて前記第2スイッチと連結される第2インターフェイス、第1資源連結を通じて前記第1スイッチと連結され、第2資源連結を通じて前記第2スイッチと連結される第1コンピューティング資源セット、第3資源連結を通じて前記第1スイッチと連結され、第4資源連結を通じて前記第2スイッチと連結される第2コンピューティング資源セット、複数の第1クロス接続、及び複数の第2クロス接続を含み、前記複数の第1クロス接続の各々は前記第1スイッチを他の高可用性ペアの各スイッチに直接連結し、前記第2クロス接続の各々は前記第2スイッチを前記他の高可用性ペアの各スイッチに直接連結する。

30

【0020】

前記第1コンピューティング資源セットは第1データ格納装置セットを含み、前記第1データ格納装置セットのデータ格納装置の各々は前記第1資源連結を通じて前記第1スイッチと直接連結される第1ポート及び前記第2資源連結を通じて前記第2スイッチと直接連結される第2ポートを含み、前記第2コンピューティング資源セットは第2データ格納装置セットを含み、前記第2データ格納装置セットのデータ格納装置の各々は前記第3資源連結を通じて前記第1スイッチと直接連結される第3ポート及び前記第4資源連結を通じて前記第2スイッチと直接連結される第4ポートを含む。

40

【0021】

前記第1スイッチは前記第2スイッチの故障を検出し、前記第1ホストリンク及び前記第1クロス接続を通じて前記第1データ格納装置セットのデータ格納装置及び前記第2データ格納装置セットのデータ格納装置へのアクセスを提供するように構成される。

【0022】

前記コンピューティングシステムは、N個（但し、Nは自然数）のサーバーノードを含み、帯域幅ユニットB（但し、Bは正数）は前記コンピューティング資源の中の1つが全帯域幅（full bandwidth）にて動作するのに要求されるトラフィック帯域幅の量であり、資源連結の各々は少なくとも $1 \times B$ のトラフィック帯域幅を含み、コンピュ

50

ーティング資源セットの各々はK（但し、Kは自然数）個以下のコンピューティング資源を含み、前記サーバーノードの各々はK×Bの正常(normal)のトラフィック帯域幅を支援し、K×B以上の最大(maximum)のトラフィック帯域幅を支援し、クロス接続の各々は少なくともK×B/(N-1)のトラフィック帯域幅を含む。

#### 【0023】

前記スイッチはPCIe(Peripheral Component Interconnect Express)スイッチであり、前記ホストリンク及び前記資源連結はPCIeバスリンクである。

#### 【0024】

前記少なくとも2つの高可用性ペアは第1高可用性ペア、第2高可用性ペア、第3高可用性ペア、及び第4高可用性ペアを含む。

10

#### 【0025】

本発明の一実施形態に係る予備資源連結ファブリックは第1スイッチ、第2スイッチ、第1クロス接続を通じて前記第1スイッチと直接連結され、第2クロス接続を通じて前記第2スイッチと直接連結される第3スイッチ、第1コンピューティング資源セット、及び第2コンピューティング資源セットを含み、前記第1コンピューティング資源セットの各々は第1資源連結を通じて前記第1スイッチと直接連結された第1ポート及び第2資源連結を通じて前記第2スイッチと直接連結される第2ポートを含み、前記第2コンピューティング資源セットの各々は第3資源連結を通じて前記第1スイッチと直接連結される第3ポート及び第4資源連結を通じて前記第2スイッチと直接連結される第4ポートを含む。

20

#### 【0026】

前記第1スイッチは前記第2スイッチの故障を検出し、前記第1クロス接続を通じて前記第1コンピューティング資源セット及び前記第2コンピューティング資源セットへのアクセスを提供するように構成される。

#### 【0027】

前記予備資源連結ファブリックは第3資源連結を通じて前記第1スイッチと直接連結され、第4資源連結を通じて前記第2スイッチと直接連結される第4スイッチをさらに含む。

#### 【0028】

前記予備資源連結ファブリックは第5資源連結を通じて前記第3スイッチと直接連結され、第6資源連結を通じて前記第4スイッチと直接連結される第3コンピューティング資源セットをさらに含む。

30

#### 【0029】

前記予備資源連結ファブリックは第7資源連結を通じて前記第3スイッチと直接連結され、第8資源連結を通じて前記第4スイッチと直接連結される第4コンピューティング資源セットをさらに含む。

#### 【発明の効果】

#### 【0030】

本発明に係るインターフェイス及びコンピューティング資源の間に位置した適応的ファブリック(adaptive fabric)は、故障状況においてコンピューティング資源へのアクセスを維持し、一部の実施形態において、故障状況において資源への最大限のパフォーマンスアクセス(full performance access)を維持する。したがって、向上した性能を有する高可用性及び負荷均等のためのコンピューティングシステム及び予備資源連結ファブリックが提供される。

40

#### 【図面の簡単な説明】

#### 【0031】

詳細な説明と共に、添付した図面は本発明の例示的な実施形態を示し、説明と共に本発明の原理を説明する。

【図1】本発明の一実施形態に係る適応的多重経路ファブリック(adaptive multipath fabric)を含むデータ格納システムを示すブロック図である。

【図2】本発明の一実施形態に係る適応的多重経路ファブリックを含むデータ格納システ

50

ムを示すブロック図である。

【図3】本発明の一実施形態に係るスイッチの故障及びデータ伝送トラフィックのリバランシング( *rebalancing* )を示すブロック図である。

【図4】本発明の一実施形態に係る、サーバーノードの故障及びデータ伝送のリバランシングを示すブロック図である。

【図5】本発明の一実施形態に係るサーバーノードを連結する補助ファブリックをさらに含むシステムのブロック図である。

【図6】本発明の一実施形態に係る2つのサーバーノード及び1つのデータ格納装置セットを含む小さい高可用性構成( *small high availability configuration* )を示すブロック図である。 10

【図7】本発明の一実施形態に係る追加的なデータ格納装置セットを含む図6に図示された構成からの拡張を示す。

【図8】本発明の一実施形態に係る追加的なサーバーノードを含む図6に図示された構成からの拡張を示す。

【図9】本発明の一実施形態に係る、192 GB / sの全体処理量のために8個のスイッチを通じて48個のデータ格納装置に連結された8個のサーバーノードを含むシステムを示すブロック図である。

#### 【発明を実施するための形態】

##### 【0032】

以下の詳細な説明において、説明を簡易にするために本発明の特定例示的な実施形態のみを説明する。当業者は、本発明が多様な他の形態に具現されるので、例示的な実施形態に限定されると理解されてはならない。詳細な説明の全体において、類似の参照番号は類似の構成要素を示す。 20

##### 【0033】

本発明の実施形態は、インターフェイスのセットを通じてコンピューティング資源への高可用性アクセス( *high availability access* )を提供するシステム及び方法と一般的に連関される。インターフェイス及びコンピューティング資源の間に位置した適応的ファブリック( *adaptive fabric* )は故障状況においてもコンピューティング資源へのアクセスを維持し、実施形態において、故障状況においてコンピューティング資源への最大限のパフォーマンスアクセス( *full performance access* )を維持する。 30

##### 【0034】

例えば、コンピューティング資源への高可用性アクセス( *high - availability access* )を提供するデータ格納コンピューティングシステムは複数のインターフェイスと、複数のコンピューティング資源セットと、少なくとも3つのスイッチと、を含む。コンピューティング資源セットの各々は複数のコンピューティング資源を含む。スイッチの各々はホストリンクを通じてインターフェイスの中の対応する1つと連結され、資源連結( *resource connection* )を通じてコンピューティング資源セットの中の対応する1つと連結される。スイッチの各々はスイッチの中の1つが故障の場合、スイッチ間の複数のクロス接続( *cross - connections* )を通じてデータトラフィックがスイッチの中の残るスイッチに分散されるように構成される。 40

##### 【0035】

さらに具体的に、SAN( *storage area network* )システムのようなデータ格納システムは1つ以上のサーバーノードと連結されたデータ格納装置を含む。例えば、データ格納装置はPCIe( *peripheral component interconnect express* )バスのようなバスを通じてサーバーノードと連結されたSSD( *solid state drive* )又はHDD( *hard disk drive* )である。例えば、各サーバーノードは中央処理ユニット、メモリ、及びデータ格納装置に格納されたデータへの遠隔アクセスを提供するネットワークインターフェイスを含む。この時、データ格納装置はサーバーノードにマッピングされる。しかし、1つの 50

サーバーノード (single server node) が故障の場合（例えば、ネットワークインターフェイス、バス、又はCPUが故障の場合）、データ格納装置に格納されたデータへのアクセスが損失されるので、1つのサーバーノードのみを使用するネットワークストレージシステムは高可用性 (HA) を提供できない。

#### 【0036】

このように、本発明の実施形態は、コンピューティング資源への高可用性アクセスを提供する適応的ファブリック (adaptive fabric) に係る。一実施形態において、コンピューティング資源の各々は複数のスイッチと連結され、スイッチの各々は適応的ファブリックのクロス接続を通じて少なくとも1つの他のスイッチと連結される。スイッチの各々はコンピューティング資源の使用者との通信のためのインターフェイス（例えば、ネットワークインターフェイス）と連結される。インターフェイスの故障又はスイッチの故障が発生した場合、適応的ファブリックは他のインターフェイスのクロス接続を通じてデータへの経路を再設定 (reroute) する。

#### 【0037】

一実施形態において、インターフェイスはホストサーバーノードの構成要素である。この時、サーバーノードはプロセッサ (CPU) 及びメモリを含むコンピュータシステムである。サーバーノードは、サーバーノードのメモリに格納され、サーバーノードのプロセッサによって実行され、駆動されるアプリケーションを通じて使用者にコンピューティング資源と連関されたサービスへのアクセスを提供する。例えば、コンピューティング資源はデータ格納装置セットであり、この場合、アプリケーションはネットワークファイルサーバー、ウェブサーバー、データベースサーバー等である。他の例として、コンピューティング資源はローレイテンシキャッシュ (low latency caches) を提供する動的メモリ (dynamic memory) である。その他の例として、コンピューティング資源はグラフィック処理ユニット (GPU; graphical processor unit) であり、この場合、アプリケーションは、例えば3次元レンダリングエンジン、マシンラーニングトレーニングプラットフォーム（例えば、トレーニングニューラルネットワーク）、暗号通貨マイナー (crypto currency miner)（例えば、ビットコイン）等である。

#### 【0038】

本発明の実施形態は、データ格納装置のようなコンピューティング資源への充分な帯域幅（伝送速度）の提供と関連する。サーバーノードにあまりにも多くのデータ格納装置が連結された場合、データ格納装置に最大限のパフォーマンス (full performance) を可能にする、サーバーノード及びデータ格納装置の間の可用である帯域幅が十分でないこともあり得る。さらに具体的に、1つのサーバーノードシステムにおいて、8個のSSDがPCIeスイッチと連結され、各SSDがPCIeスイッチへの4レーンリンク (X4) を飽和させ、サーバーノードがPCIeスイッチへの32レーンリンク (X32) を含む場合、8個のSSDだけでサーバーノードへの連結を飽和させるのに十分である。追加的なデータ格納装置がシステムに追加される場合、サーバーノード及びPCIeスイッチの間の連結がシステムにおいて隘路現象 (bottleneck) として作用するので、データ格納装置の全体を最大限のパフォーマンスにより動作させるのに帯域幅が十分ではないことがあり得る。一部の状況において、サーバーノード及びネットワークアダプターの間の連結がシステムにおける隘路現象に類似して作用する。

#### 【0039】

一部のデータ格納装置は冗長性 (redundancy) を提供する2つの連結ポート (two connection ports) を含む。例えば、デュアルPCIeポートを含むデータ格納装置は第1サーバーノードと連結された第1ポート及び第2サーバーノードと連結された第2ポートを含む。このような方式により、サーバーノードの中の1つが故障の場合、データ格納装置は他のサーバーノードを通じて相変わらずアクセスされる。

#### 【0040】

しかし、このような方式において、サーバーノードの故障は帯域幅制限 (bandwidth)

10

20

30

40

50

*the limitations*)を悪化させる。上述した例を続いて参照すれば、2つのサーバーノードの全てが連結されたデータ格納装置に対する充分な帯域幅を提供できる反面、サーバーノードの中の1つが故障の場合、データ格納装置への/からのすべてのトラフィックが、生存サーバーノード(*surviving server node*)によって管理される。生存サーバーノードは追加的なトラフィックを管理するのに充分な帯域幅を有しないことがある。特に、データ格納装置の帯域幅要求が既にサーバーノードへの2つのリンクを飽和させた場合、サーバーノードの中の1つの故障は約50%のパフォーマンス減少を発生させる。

#### 【0041】

本発明の一部の実施形態は複数のサーバーノードを通じてデータ格納装置へのアクセスを提供するシステム及び方法に係る。この時、システム及び方法はサーバーノードの故障状況においてパフォーマンス低下無しにデータ格納装置の可能な最大限のパフォーマンス(*full performance potential*)を維持する。さらに詳細には、本発明の実施形態は、複数のスイッチを通じてサーバーノードと(マルチポートデータ格納装置のような)コンピューティング資源を連結する適応的多重経路ファブリック(*adaptive multipath fabric*)と関連する。この時、多重経路ファブリックはシステムの故障状況においてデータトラフィックに対する代替経路(*alternative paths*)を提供する。本発明の実施形態は、要求された特定のシステムパフォーマンスプロフィールを達成するために、多様な複数のサーバーノード及びコンピューティング資源(例えば、データ格納装置)のセットに適用される。本発明の実施形態は、ノード故障状況においても、特定のパフォーマンスプロフィールを維持する一方で、初期構成に対してデータ格納装置又はサーバーノードをさらに追加することによって、コンピューティング資源(例えば、データ格納容量)及び一般コンピューティング能力の双方の増大(*scaling*)を可能にする。

#### 【0042】

説明を簡易にするために、本発明の実施形態は、以下において、PCIeスイッチ及びPCIeファブリックを通じてホストサーバーノードと連結されたNVMe(*non-volatile memory express*)インターフェイスを含むソリッドステートドライブを参照して説明する。しかし、本発明の実施形態はこれに限定されず、ファブリックの基本構造(*underlying architecture*)はイーサーネット(登録商標)(Ethernet(登録商標))、IB(Infiniband(登録商標))、ファイバチャネル(Fibre Channel)、SCSI(small computer system interface)、SAS(serially attached SCSI)等の他のインターフェイスに適用される。追加的に、本発明の実施形態はハードディスクドライブ、テープドライブ、DRAM(*dynamic random access memory*)のような揮発性メモリの他の形態の資源、及びベクトルプロセッサ、グラフィック処理ユニット(GPUs)、デジタル信号プロセッサ(DSPs; digital signal processors)、及びFPGA(*field programmable gate array*)のような演算ユニットに高可用性を提供するのに適用される。

#### 【0043】

<多重経路ファブリック構造(*Multipath fabric structure*)>

本発明の実施形態は、コンピューティング資源がデュアルポートデータ格納装置セットであり、連結及びスイッチがPCIe連結及びスイッチであり、インターフェイスがネットワークインターフェイスであるデータ格納システムの特定事例を参照して以下に説明する。しかし、本発明の実施形態はこれに限定されず、他の形態のコンピューティング資源、連結プロトコル、及びインターフェイスに適用できる。

#### 【0044】

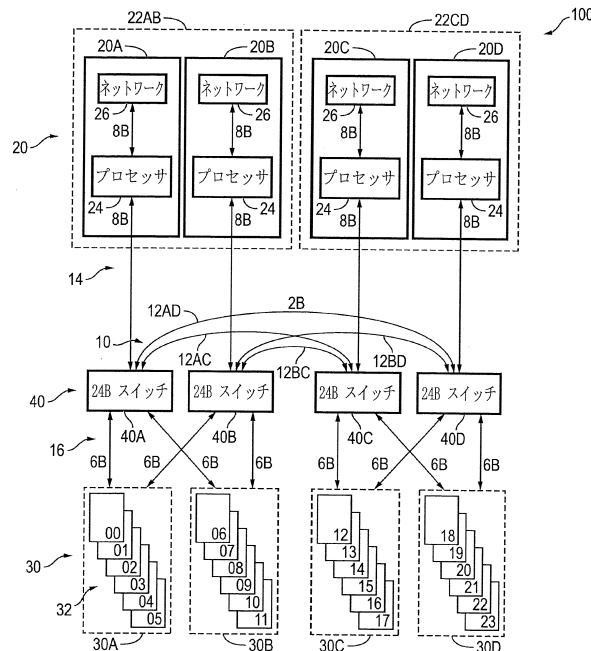

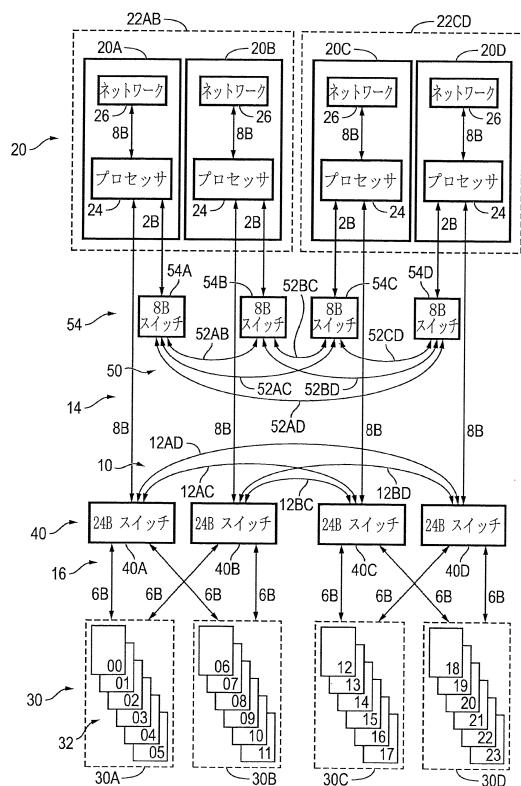

図1は本発明の一実施形態に係る適応的多重経路ファブリックを含むデータ格納システム100を示すブロック図である。図1の実施形態はサーバーノード20をデュアルポート

10

20

30

40

50

データ格納装置セット30と連結するファブリック10を含む。ファブリック10は印刷回路基板上のパターン(trace)、複数の電気配線(例えば、リボンケーブル、mini-SAS HDケーブル、OCU Linkケーブル等)、及びそれらの組合せのような多様な方式により具現される。ファブリック10はスイッチ40の間のクロス接続12AC、12BC、12BD、12ADを含む。ノード故障の場合に帯域幅バランシング(balancing)の提供のために追加的に、クロス接続12AC、12BC、12BD、12ADはエンドポイント再割当及び帯域幅バランシングに使用されて入力/出力(I/O)負荷及び非平衡ノードCPU使用をカウンティングするだけでなく、データ格納装置セット30の間のピアツーピア通信(例えば、サーバーノード20からの干渉無しに、第1データ格納装置セット30A及び第2データ格納装置セット30Bの間の直接メモリアクセス伝送(direct memory access transfers))を提供する。

#### 【0045】

デュアルポートデータ格納装置セット30の各々は1つ以上のデュアルポートデータ格納装置32を含む。各デュアルポートデータ格納装置32は資源リンク16を通じて2つの他のスイッチと連結される。本文に使用する“スイッチ(switch)”の用語は通信のためにスイッチと連結された装置に対して複数の通信経路を提供する電気的な構成要素を示す。スイッチは装置の間のトラフィックの経路を設定し、スイッチと連結された通信装置の間の連結を設定する。

#### 【0046】

図1に図示したように、各サーバーノード20は1つ以上のプロセッサ24(例えば、Intel(登録商標) Xeon(登録商標) プロセッサ)を含む。1つ以上のプロセッサ24はPCIe連結を通じてネットワークインターフェイスカード(NIC)26(例えば、イーサーネット(登録商標) NIC)と連結され、ホストリンク14(例えば、他のPCIe連結又は複数のPCIe連結)を通じて対応するスイッチ40と連結される。各サーバーノード20は高可用性ピア(HA peer; high availability peer)と指称される他の1つのサーバーノード20とペアをなす。例えば、サーバーノード20A、20BはHAピアであり、ペア22ABを形成する。共通HAピアのペア22はファブリック10を通じて2つの予備経路(redundant paths)により1つ以上のデータ格納装置セット30をアクセスする。例えば、HAペア22ABはデータ格納装置セット30A、30Bへアクセスする。HAピアノードの他のペア22は他のデータ格納装置セット30に他の予備経路によりアクセスする。例えば、HAペア22CDはデータ格納装置セット(30C、30D)へアクセスする。

#### 【0047】

ファブリック10は複数のHAピアのペア22を連結して、1つのサーバーノード故障状況において、データ格納装置32及びすべてのノードにわたった均衡ある帯域幅のための連結を提供する。N個のサーバーノード20(又はN個のスイッチ40)を具備するシステムにおいて、1つのスイッチ40から他の(N-2)個のスイッチ40の各々への追加的なクロス接続帯域幅の量は正常、非故障モードの動作において各サーバーノード20によって支援される帯域幅(正常帯域幅“normal bandwidth”)の1/(N-1)倍である。結果的に、1つのノードの故障による帯域幅の損失は残る(N-1)個のノードによって減少される。

#### 【0048】

さらに詳細には、図1は4つのサーバーノード20(N=4)を示す。説明を簡易にするために、図1は帯域幅ユニットBで表した帯域幅を示し、この時、Bはデータ格納装置32の中の1つの帯域幅要求を示す。図1において、データ格納装置セット30の各々は6個のデータ格納装置32を含む。したがって、データ格納装置セット30の各々は6Bの帯域幅(各データ格納装置32当たり1B)を必要とする。図1に図示したように、4つのサーバーノード20はシステムにおいて24個のデータ格納装置32に総24Bの処理量(ノード当たり6B)を提供する。

**【 0 0 4 9 】**

サーバーノード 20 及びそれに対応するスイッチ 40 の間の各連結の実際(a c t u a l)の帯域幅の容量(c a p a c i t y)は 8 B であるので、データ格納装置セット 30 の各々において要求される 6 B の帯域幅の容量を 2 B ぐらい超過する。また、図 1 の実施形態において、ホストプロセッサ 24 及びネットワークインターフェイス 26 の間の連結はホストプロセッサ 24 及びスイッチ 40 の間の帯域幅、例えば 8 B と少なくとも同一の帯域幅を有する。

**【 0 0 5 0 】**

図 1 に図示した実施形態において、各ノードから非 HA ピアノードの各々へのクロス接続帯域幅は  $6 \text{ B} / 3 = 2 \text{ B}$  である。例えば、第 1 サーバーノード 20 A と対応する第 1 スイッチ 40 A 及びその非 HA ピアノード 20 C、20 D のスイッチ 40 C、40 D の間のクロス接続 12 A C、12 A D の各々のクロス接続帯域幅は 2 B である。同様に、第 2 サーバーノード 20 B と対応する第 2 スイッチ 40 B 及びその非 HA ピアノード 20 C、20 D のスイッチ 40 C、40 D の間のクロス接続 12 B C、12 B D の各々のクロス接続帯域幅は 2 B である。図 1 に図示したように、クロス接続 12 はスイッチ 40 の間に形成される。しかし、本発明の実施形態がこれに限定されず、上述したように、クロス接続 12 の各々の最小帯域幅は正常、非故障モードの動作において各サーバーノード 20 によって支援される帯域幅をサーバーの個数 ( $N$ ) から 1 を差し引いた値により割った帯域幅に設定される。その他の実施形態において、システムが複数のサーバーノード 20 の故障を許容するように設計された場合、クロス接続 20 の各々の最小帯域幅は正常、非故障モードの動作において各サーバーノード 20 によって支援される帯域幅をサーバーの個数 ( $N$ ) から許容される故障の個数を差し引いた値により割った帯域幅に設定される。

10

20

20

**【 0 0 5 1 】**

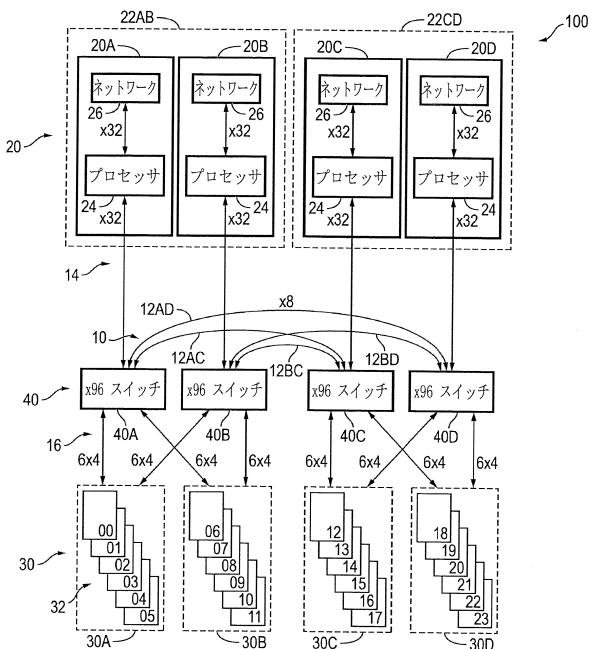

図 2 は本発明の一実施形態に係る適応的多重経路ファブリックを含むデータ格納システムを示すブロック図であり、 $B = X 4$  ( 例えば、4 レーン PCI e リンクの帯域幅 ) である場合の適応的多重経路を含むデータ格納システム 100 を示すブロック図である。PCI e 3.0 の場合、X 4 リンクは約 4 GB / s の最大帯域幅又は処理量を提供する。類似の構成に図 1 と同様の参照番号が付与され、このような構成に対する説明は省略する。

**【 0 0 5 2 】**

図 2 に図示した実施形態において、ノード当たり 64 個の PCI e 3.0 レーンを具備する 4 つのサーバーノード 20 は各々セット当たり 6 個のドライブを含む 4 つのセットに配置された 24 個のデュアルポート NVMe SSD と連結される。24 個のデュアルポート NVMe SSD の各々は 2 つのエンドポイント ( 即ち、2 つの SSD エンドポイント ) を含む。この時、各エンドポイントはサーバーノードの中のいずれか 1 つに割当される。例えば、第 1 データ格納装置セット 30 A において SSD のエンドポイントの各々は第 1 サーバーノード 20 A に割当される。PCI e 3.0 を使用する場合、図 2 に図示したシステムは 96 GB / s 使用者データ処理量 ( PCI e 3.0 帯域幅の 96 レーン ) のエンドツーエンドシステムパフォーマンスプロフィール及び高可用性 ( 1 つのサーバーノード 故障の状況においてすべての SSD への最大限のパフォーマンスアクセスが維持されること ) を保障する。

30

40

**【 0 0 5 3 】**

図 2 の例示的な実施形態において、全負荷により動作中である場合、NVMe SSD 2 の各々は、約 4 GB / s によりデータを伝送し单一 X 4 リンクによって提供される。また、デュアルポート NVMe SSD の 2 つのポートの各々は X 4 リンクを提供する。結果的に、NVMe SSD の 2 つのポートの中の 1 つの故障はデータ格納装置が相変わらず最大限のパフォーマンスにて動作できるようになる。NVMe SSD の各々が 4 つの PCI e レーンの帯域幅を要求するので、データ格納装置の全体セット 30 の最大限のパフォーマンスを維持するために、6 個のデュアルポート NVMe SSD のセットの各々は  $6 \times 4 = X 24$  すなわち 24 レーンの帯域幅を必要とする。

**【 0 0 5 4 】**

50

図2に図示したように、データ格納装置セット30はPCIeスイッチ40と連結される。各スイッチ40はPCIe連結を通じて対応するホストサーバーノード20と連結される。図2の実施形態において、PCIeスイッチとサーバーノード20のホストプロセッサ24との間にX32リンクが存在する。

#### 【0055】

図2に図示した構成において、サーバーノード20A、20Bは12個のSSD00乃至11(第1データ格納装置セット30A、第2データ格納装置セット30Bに該当する2個のSSDセット)にデュアルポートアクセスを提供するHAピアノードである。同様に、サーバーノード20C、20Dは他の12個のSSD12乃至23(2個のデータ格納装置セット30C、30Dに該当する2個のSSDセット)にデュアルポートアクセスを提供するHAピアノードである。10

#### 【0056】

図2に図示したPCIeファブリック10はホストリンク14をさらに含む。ホストリンク14はスイッチ40及び資源(データ格納装置32)の間の資源連結16に追加的に、4つのサーバーノード20からスイッチ40への総128個のPCIe3.0レーン(各ノード当たり32レーン)を連結する。ホストリンク14の各々は複数の連結を含む。例えば、デュアル-プロセッササーバーノードの場合、各サーバーノードからの32個のレーンはサーバーノードの第1CPUソケットと連結された16個のレーン及びサーバーノードの第2CPUソケットと連結された16個のレーンを含む。また、サーバーノード20の各々はサーバーノードを複数のスイッチ40と連結する複数のホストリンク14を含む。図2の実施形態に図示したように、資源連結16は24個のデュアルポートNVMe SSDにわたった総192個のレーンを含む。この時、各SSDはX4レーンの帯域幅(最大4GB/s)の処理容量を有する。各SSDは処理容量(SSD当たりX4レーン)に比べて2倍多いポート連結(SSD当たり2X4レーン)を含む。24個のドライブにわたった総96個のレーンに対するSSD当たりX4レーンの全処理量(full throughput)を達成するために、各サーバーノード20はX32レーンの処理容量の中のX24レーンの帯域幅を提供する。20

#### 【0057】

一部の状況において、デュアルポートNVMe SSDの各ポートはSSDの全処理容量(full throughput capability)より低い帯域幅を有する。例えば、一部デュアルポートNVMe SSDは2つのX2ポートのみを含み、これは各ポートはX2レーンのみを支援することを意味する。結果的に、SSDの最大処理量はX4レーンであると仮定すれば、ポートの中の1つが故障であるか、又はポートの中の1つと連結されたスイッチが故障の場合、SSDはX2レーン(即ち、SSDの処理容量の半分)のみの連結が可能である。30

#### 【0058】

1つのサーバーノードが故障の状況において、96GB/sの持続可能な帯域幅を支援するために、ファブリック10のクロス接続12はノード20A、20C、ノード20A、20D、ノード20B、20C、及びノード20B、20Dの各々の間に24GB/s/(N-1)=8GB/sのクロス接続帯域幅(cross-connection bandwidth)を提供する。40

#### 【0059】

PCIeスイッチ40によって提供されるレーンの最小個数は連結された構成要素、即ち2つのデータ格納装置セット30(例えば、第1PCIeスイッチ40Aは第1データ格納装置セット30Aのデータ格納装置及び第2データ格納装置セット30Bのデータ格納装置と連結される)、ホストプロセッサ24、及びファブリック10のクロス接続12の必要条件に依存する。図2に図示した実施形態において、全体 $24 + 24 + 32 + 8 + 8 = 96$ レーンに対して、データ格納装置セット30の各々は24レーンを必要とし、ホストプロセッサ24は32レーンを必要とし、ファブリック10への2つのクロス接続12の各々は8レーンを必要とする。図2に図示した実施形態において、PCIeスイッチ450

0の各々はX 9 6スイッチすなわち9 6レーンスイッチである。しかし、本発明の実施形態がこれに限定されることはなく、スイッチは連結された構成が必要とする数より多いレーンを含む。このような特定実施形態において、PCIeスイッチは9 6レーン以上を含む。

#### 【0060】

<ノード故障における帯域幅リバランシング(Rebalancing bandwidth under node failure)>

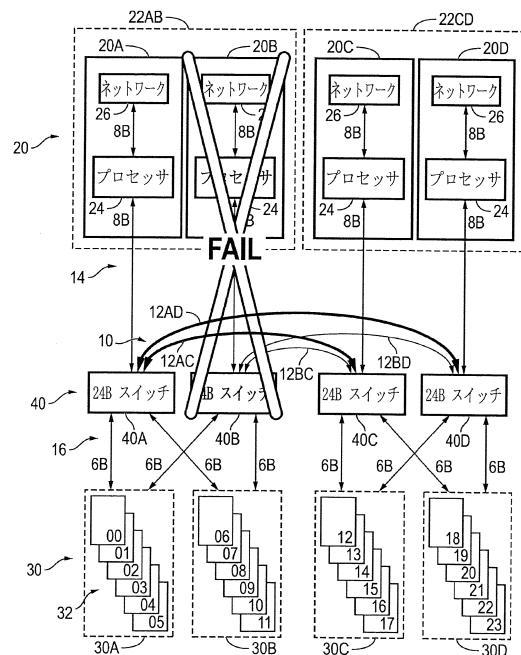

図3は本発明の一実施形態に係るスイッチの故障及びデータ伝送トラフィックのリバランシング(rebalancing)を示すブロック図である。サーバーノード及びスイッチの間の予備連結(redundant connections)がないので、スイッチ40の故障状況において、スイッチ40と連関されたサーバーノード20はシステムの残りの部分との連結が切断される。したがって、本発明の一部の実施形態において、スイッチ40の故障はそれと連関されたサーバーノードの損失を実質的に発生させる。しかし、本発明の実施形態がこれに限定されることはなく、一部の実施形態において、サーバーノードは複数のスイッチと連結される。

10

#### 【0061】

図3の実施形態において、故障のスイッチ40Bと連結されたサーバーノード20Bはデータ格納システム100から連結が切断され、それによって、スイッチ40B及びサーバーノード20Bによって管理される作業負荷又はデータトラフィックが残りの(N-1)個のスイッチ40A、40C、40D及び(N-1)個のサーバーノード20A、20C、20Dに分散される。故障のスイッチ又はノード20Bと連結されたデータ格納装置セット30に/からのデータ伝送は重複して連結されたスイッチ40Aを経由する。このような作業負荷のリバランシングはシステムの24個SSD全体の処理量(SSD当たりX4リンク)を維持する。

20

#### 【0062】

システムに内装された超過容量により、故障のスイッチと連結されたドライブセットに/からのデータ伝送のパフォーマンスが維持される。特に、帯域幅の一部はHAペアの生存メンバーに直接連結されたサーバーノードからもたらされ、帯域幅の残る部分はファブリック10を通じて連結された他のサーバーノード(例えば、20A、20C、20D)によって提供される。また、残りの(N-1)個のサーバーノード(例えば、20A、20C、20D)は追加的な負荷を収容するように、各々のスイッチ(例えば、40A、40C、40Dとの連結により充分な帯域幅を有する。

30

#### 【0063】

本発明の一部の実施形態において、適応的多重経路ファブリック10のスイッチ40はこのようなノード故障を自動的に検出し、続いてSSDエンドポイントをサーバーノード20に自動的に再割当し、生存サーバーノードを通じて帯域幅をリバランシングするようにプログラムされる。言い換えれば、スイッチ40はスイッチの現在の構成に基づいて各SSDにどのように連結されるかに対する情報を維持し、エラー条件に対して物理及びリンク階層により他のスイッチ40、データ格納装置セット30、及びサーバーノード20の間の連結をモニタリングし、このようなエラーを管理システム(例えば、サーバーノード20の中の1つ又は他の専用管理プロセッサ)に報告する。管理システムは報告されたエラーに基づいてリンク又はサーバーノードが故障であるか否かを判別し、SSDのSSDエンドポイントをサーバーノード20の中の到達できるノードに再割当するようにスイッチ40を再構成する。図3に図示した1つのノード故障による帯域幅の低下はないが、ノードの間のクロス接続12はPCIeスイッチの1つの追加的なレベルを経由し、これによって追加的な遅延が発生する。しかし、PCIeスイッチを通じた遅延はSSDに/からのデータアクセスの全体遅延と比較して一般的に小さく、無視できる。

40

#### 【0064】

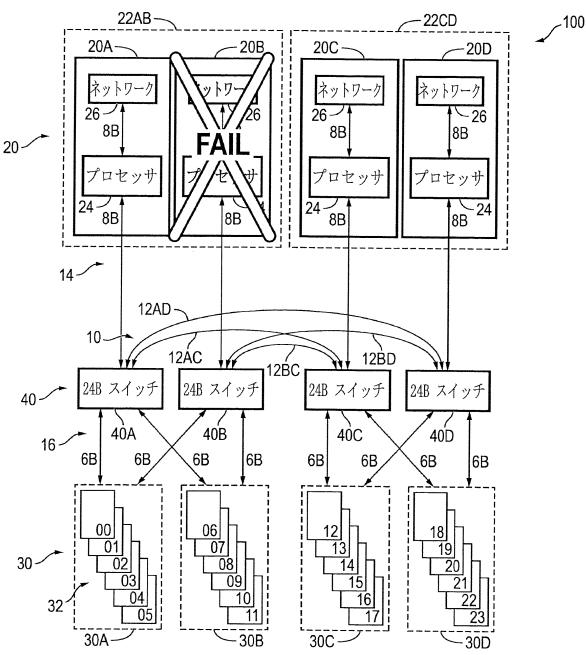

図4は本発明の一実施形態に係るサーバーノードの故障及びデータ伝送のリバランシング(rebalancing)を示すブロック図である。図4を参照すれば、サーバーノー

50

ド 2 0 B が故障であるが、対応するスイッチ 4 0 B は生存した状況であって、データは機能スイッチ 4 0 B を通じて相変わらず、経由できるが、3 つの生存サーバーノード 2 0 A、2 0 C、2 0 D のみを通じてアクセスされる。このような状況において、適応的多重経路ファブリックの管理システム（例えば、サーバーノード 2 0 の中の1つ又は他の専用管理プロセッサ）はサーバーノード 2 0 B の故障を自動的に検出するようにプログラムされ、図3に図示した実施形態のように、SSDエンドポイントを生存エンドポイント（surviving endpoints）に自動的に再割当する。本発明の他の実施形態において、エラーの検出及びスイッチ 4 0 の自動的再構成はスイッチ自体により（例えば、スイッチ 4 0 に集積された処理ユニットによって）具現される。

#### 【0065】

本発明の一部の実施形態において、個別のスイッチは2個のデータ格納装置セット30が最大限のパフォーマンス（full performance）にて動作するのに充分な帯域幅を提供しなくともよい。例えば、スイッチ 4 0 B が故障の場合、データ格納装置セット30 A、30 B への唯一の経路は生存スイッチ 4 0 A を通じる経路である。生存スイッチ 4 0 A が X 9 6 レーンより小さいレーンを含む場合、データ格納装置セット30 A、30 B は最大限のパフォーマンスにて動作するのに充分な帯域幅を有さない。しかし、スイッチ 4 0 B が故障ではなく、連関されたサーバーノード 2 0 B のみが故障の場合、スイッチ 4 0 B が正常サーバーノード 2 0 C、2 0 D にデータを再ルーティングすることに参加できる。このような一部の実施形態において、データ格納装置セット30の全部が最大限のパフォーマンスにて続いている動作できる充分な帯域幅が提供される。

#### 【0066】

<ノード間通信（Inter-node communication）>

本発明の一部の実施形態において、補助ファブリック 50（secondary fabric）がサーバーノード 2 0 の間の通信のために含まれる。図5は本発明の一実施形態に係るサーバーノード 2 0 を連結する補助ファブリック 50 をさらに含むシステムのブロック図である。補助ファブリック 50 は補助スイッチ 54（例えば、54 A、54 B、54 C、及び 54 D）を他の1つに連結する相互連結 52（inter-connections）（例えば、52 AB、52 AC、52 AD、52 BC、及び 52 BD）を含む。この時、補助スイッチ 54 の各々は対応する1つのサーバーノード 2 0 と直接連結される。例えば、補助スイッチ 54 A はサーバーノード 2 0 A と直接連結される。ファブリック 10 と同様に、補助ファブリック 50 は印刷回路基板上のパターン（trace）、複数の電気配線（例えば、リボンケーブル、mini-SASHDケーブル、OCULinkケーブル等）、及びそれらの組合せのような多様な方式により具現される。本発明の一実施形態によれば、補助ファブリック 50 はサーバーノード CPU NTB（non-transparent bridge）ポートと連結される。補助ファブリック 50 はサーバーノード 2 0 の間のメタデータを同期化するのに使用され、サーバーノード 2 0 の間の低遅延内部通信（low-latency internal communication）を提供する。

#### 【0067】

<ファブリックの漸進的な拡張（Incrementally expanding the fabric）>

図1、図2、図3、図4、及び図5は4つのデータ格納装置セットへの高可用性及び高性能アクセスを提供するサーバーノード 2 0 の2つのペア 2 2 を具備するシステムを示しているが、本発明の実施形態がこれに限定されることではない。

#### 【0068】

本発明の実施形態は特定アプリケーションの作業負荷の必要条件によってデータ格納装置、スイッチ、及びサーバーノードの構成を含む。

#### 【0069】

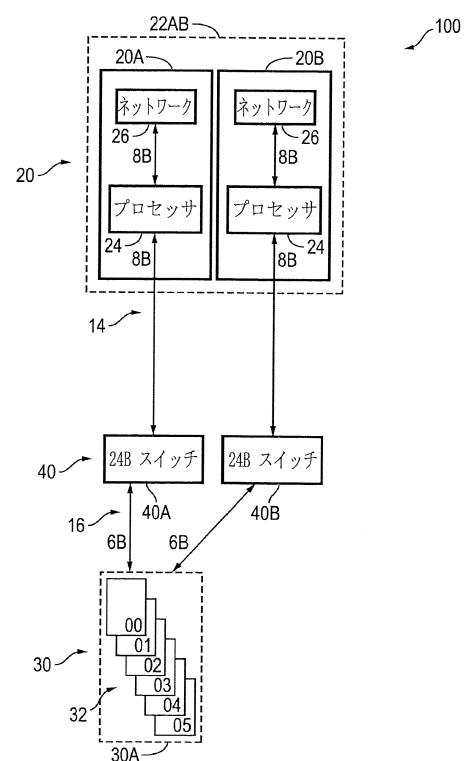

図6は本発明の一実施形態に係る1つのデータ格納装置セット30 A 及び2つのサーバーノード 2 0 A、2 0 B を含む小さい高可用性構成を示すブロック図である。図6の構成は

10

20

30

40

50

1つのデータ格納装置セット30Aのデータ格納容量が現在作業負荷に対して充分な場合、及び予備サーバーノードを通じた高可用性が適切な場合に有用である。

#### 【0070】

図6を参照すれば、1つのデータ格納装置セット30Aは第1スイッチ40A及び第2スイッチ40Bの両方と連結される。図1の実施形態と同様に、第1スイッチ40Aは第1サーバーノード20Aと連結され、第2スイッチ40Bは第2サーバーノード20Bと連結される。第1サーバーノード20A又は第2サーバーノード20Bの中のいずれか1つが故障の場合、データ格納装置セット30Aは生存ノードを通じてアクセスを維持する。

#### 【0071】

データ格納需要が増加する場合、追加的なデータ格納装置セットが図6のシステムに追加できる。例えば、第1スイッチ40A及び第2スイッチ40Bの全てに追加データ格納装置を連結することによって、追加的な1つのデータ格納装置セットが追加されて、他のスイッチへの相互連結無しに、第1サーバーノード20A、第2サーバーノード20B、第1スイッチ40A、第2スイッチ40B、第1データ格納装置セット30A、及び第2データ格納装置セット30Bと実質的に類似に構成される。前述のように、サーバーノード20A、20Bの中の1つ又はスイッチ40A、40Bの中の1つが故障の場合、第1及び第2データ格納装置セット30A、30Bの全てはアクセス可能であるように維持される。

10

#### 【0072】

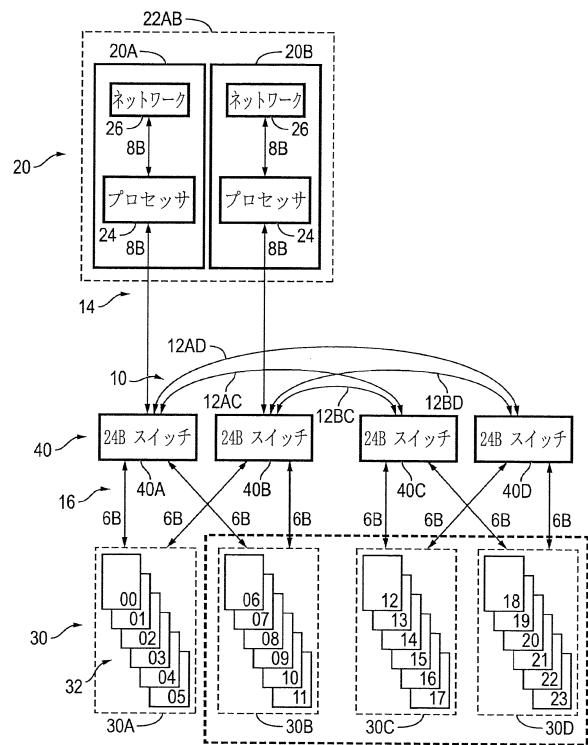

図7は本発明の一実施形態に係る追加的なデータ格納装置セットを含む図6に図示した構成からの拡張を示す。図7に図示したように、第2データ格納装置セット30Bは第1スイッチ40A及び第2スイッチ40Bと連結される。図7の構成は追加的なサーバーノードの代わりに第3スイッチ40C及び第4スイッチ40Dの追加的なクロス接続をさらに含む。第3データ格納装置セット30Cは第3及び第4スイッチ40C、40Dと連結され、第4データ格納装置セット30Dは第3及び第4スイッチ40C、40Dと連結される。クロス接続12AC、12BCは第3スイッチ40Cを第1及び第2スイッチ40A、40Bと連結し、クロス接続12AD、12BDは第4スイッチ40Dを第1及び第2スイッチ40A、40Bと連結する。結果的に、第1及び第2サーバーノード20A、20Bは第3及び第4スイッチ40C、40Dを通じて第3及び第4データ格納装置セット30C、30Dをアクセスする。

20

#### 【0073】

図7に図示した構成において、サーバーノード20A、20Bの中の1つが故障の場合、又は4つのスイッチ40A、40B、40C、40Dの中のいずれかが故障の場合において、データ格納装置の全部がアクセス可能であるように維持される。しかし、第3及び第4データ格納装置セット30C、30Dのデータ処理パフォーマンス(data throughput performance)はクロス接続12の帯域幅によって制限され、サーバーノード20及びその対応するスイッチ40の間のホストリンク14によって制限される。特に、図7の配列において、2つのサーバーノード20は4つのデータ格納装置セット30の全部に総16Bの帯域幅(各サーバーノード20毎に8B)を提供し、これはクロス接続12AC、12AD、12BD、12BDのみを通じて連結されるデータ格納装置セット30C、30Dへの可用である最大帯域幅と対応する、データ格納装置セット当たり4Bを意味する。言い換えれば、クロス接続当たり2Bであり、4つのクロス接続は2つのドライブセットと共有される総8B(ドライブセット当たり4B)を提供する。また、サーバーノードの中の一部又はスイッチの中の一部の故障はシステムのデータ処理量に追加的な影響を及ぼす。このような意味において図7の構成は、例えば充分な帯域幅が総格納容量より重要でない場合にさらに適合する。

30

40

#### 【0074】

追加的な帯域幅が要求される場合、図7の構成はサーバーノードを第3及び第4スイッチ40C、40Dに連結するように拡張され、これにしたがって図2に図示したのと実質的に同一な構造になる。このような意味において、本発明の実施形態は使用者の増加する要

50

求条件を対応するために必要に応じてシステムの漸進的な拡張を許容する。

**【 0 0 7 5 】**

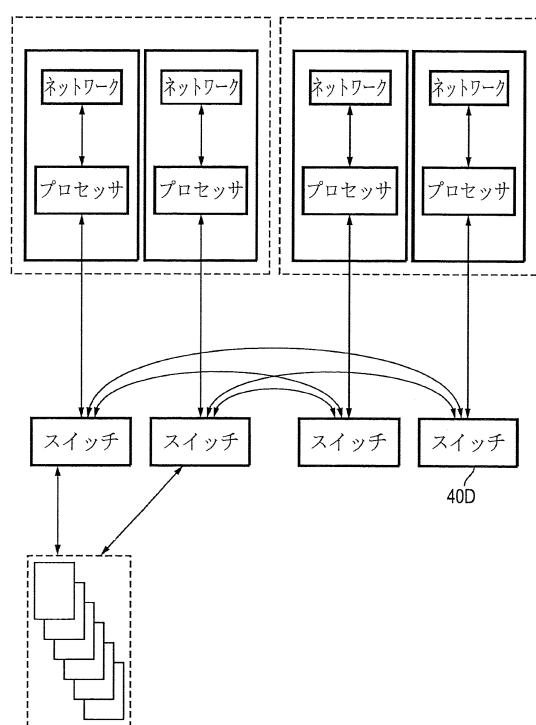

本発明のその他の実施形態において、使用者によって要求される作業負荷はデータ集中 (data-intensive) より演算集中 (compute-intensive) による。図 8 は本発明の一実施形態に係る追加的なサーバーノードを含む図 6 に図示した構成からの拡張を示す。

**【 0 0 7 6 】**

図 6 に図示したように 6 個のデータ格納装置の 1 つのセット 30A 及び 2 つのサーバーノードの基本構成に、第 3 サーバーノード 20C がクロス接続 12AC、12BC を通じて第 1 及び第 2 スイッチ 40A、40B と連結された第 3 スイッチ 40C と共に追加される。又は、第 3 サーバーノード 20C は追加的なスイッチの代わりにパッシブ相互連結ボード (passive interconnect board) (例えば、サーバーノード 20C 及びスイッチ 40A、40B の間の効率的な直接連結) を通じて第 1 及び第 2 スイッチ 40A、40B と連結される。これは同一のデータ格納装置セットへのアクセスを維持しながら、システムの演算能力を向上させる。演算要求がさらに増加する場合、第 4 ノード 20D が第 4 スイッチ 40D 又はパッシブ連結ボードの中の 1 つを通じて第 1 及び第 2 スイッチ 40A、40B と連結される。

10

**【 0 0 7 7 】**

本願の使用事例は、2 つのサーバーノード 20A、20B 上において駆動するソフトウェアスタックがデータ格納装置 32 への最高帯域幅を達成する能力に影響を及ぼす隘路現象である場合であり、この場合、さらに多くのサーバーノードの追加がさらに多くのサーバー演算能力を提供する。追加的なストレージが要求される場合、追加的なデータ格納装置セットが図 7 に図示したのと類似な方式により漸進的に追加されて図 2 に図示したように 24 個のデータ格納装置及び 4 つのサーバーノードの構造が達成される。

20

**【 0 0 7 8 】**

説明を簡易にするために、本発明の実施形態が 4 個以下のスイッチを含む構造により説明した。しかし、本発明の範囲がこれに限定されることではない。例えば、本発明の一部の実施形態は 4 個以上のスイッチを含む。

**【 0 0 7 9 】**

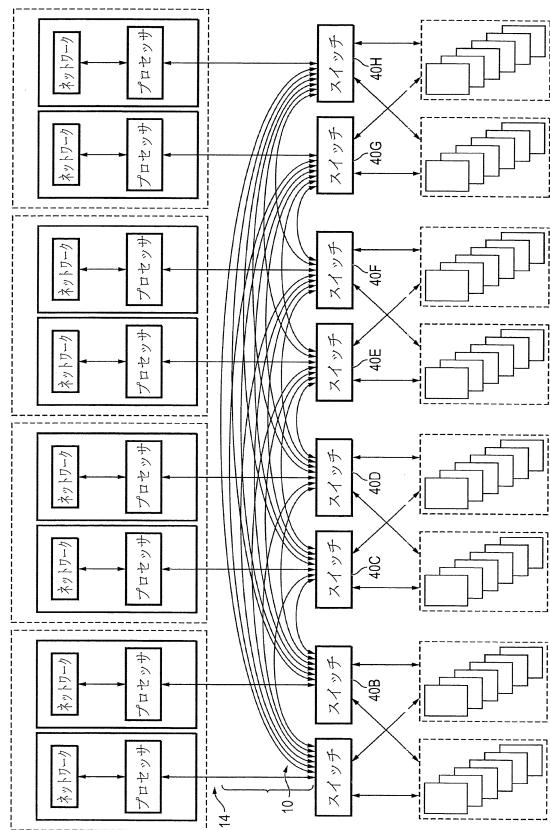

類似の方式を使用する場合、本発明の実施形態に係る適応的多重経路ファブリックを含むデータ格納システム 100 の変形は、例えば、144 GB / s の全体処理量に対して、6 個のスイッチを通じて 36 個のデータ装置と連結された 6 個のノードを含む。他の例として、図 9 は本発明の一実施形態に係る 192 GB / s の全体処理量 (各々約 4 GB / s を有するデータ格納装置に対する上述した仮定に基づく) のために 8 個のスイッチ 40A、40B、40C、40D、40E、40F、40G、40H を通じて 48 個のデータ格納装置と連結された 8 個のサーバーノード 20A、20B、20C、20D、20E、20F、20G、20H を含むシステムを示すブロック図である。

30

**【 0 0 8 0 】**

このように、本発明の実施形態に係る適応的多重経路ファブリック構造はサーバーノードのグループ及び高性能マルチポート NVMe SSD のグループを使用して均衡を成し、構成可能なエンドツーエンドシステムパフォーマンスプロファイル (balanced and configurable end-to-end system performance profile) を提供する。パフォーマンスはサーバーノード及びエンドポイントを通じて均衡を成し、パフォーマンスは 1 つのノードが故障しても維持され、均衡をなす。

40

**【 0 0 8 1 】**

データ格納システムは、例えばイーサーネット (登録商標) 連結を通じて SAN を提供し、多重経路ファブリックはサーバーノードへの基本ドライブの間のパフォーマンスに相応しいイーサーネット (登録商標) を通じてネットワークストレージパフォーマンスを提供する。

50

**【 0 0 8 2 】**

例えば、システムパフォーマンスプロフィールは 100 GB / s 使用者データ処理量と、サーバーノードの間のローレイテンシ内部通信と、エンドポイント上のデータへの高可用性アクセスとの中の 1 つ以上の組合せである。

**【 0 0 8 3 】**

本発明の実施形態は適応的多重経路ファブリック構造を提供する。適応的多重経路ファブリック構造はサーバーノードのグループ (PCIe ルート - コンプレックス ) をマルチポート SSD のグループと連結し、

サーバーノードの個数、SSD の個数、エンドツーエンドパフォーマンス規定 (end-to-end performance specification) に関して柔軟性 (flexibility) を提供し、

10

サーバーノード及び SSD を通じてエンドツーエンド負荷均衡を支援し、SSD のマルチポートを通じて一対のサーバーノード (HA-peers) から SSD のセットへの予備アクセスを提供し、

様々なペアの HA ピアノードの間のクロス接続帯域幅を提供して故障復旧及び負荷均等化シナリオによりすべてのサーバーノードに帯域幅をリバランシングし、すべての生存ノードによって帯域幅をリバランシングすることによってエンドツーエンドシステムパフォーマンスの低下無しに 1 つのノード故障に耐え、自動故障検出及びその後のサーバーノードへの SSD エンドポイントの再割当及び帯域幅のリバランシングに転じる能力を提供する。

**【 0 0 8 4 】**

本発明の実施形態は、柔軟な拡張可能な方式によりサーバーノードのような PCIe ルート - コンプレックスをデュアルポート NVMe SSD のようなマルチポート PCIe エンドポイントと連結する機能と、

20

1 つのルート - コンプレックス故障 (HA) の状況においてパフォーマンス低下を制限しながら、すべての PCIe エンドポイントを継続的にアクセスする機能と、ルート - コンプレックス及びエンドポイントの間の帯域幅の割当を調整する機能と、

故障復旧又は負荷バランシングシナリオにより、PCIe エンドポイントをルートコンプレックスに動的に再割当する機能と、

ホストルート - コンプレックス上のオーバーヘッド無しにエンドポイントの間のピアツーピアデータ伝送を遂行する機能と、HA ピアサーバーノードの間のローレイテンシの高い処理量通信を遂行する機能を可能とする。

30

**【 0 0 8 5 】**

本発明を特定例示的な実施形態と関連して説明したが、本発明が記載した実施形態に限定されず、特許請求範囲の範囲及びその思想内に含まれる同等の配列及び多様な変形及びそれらの均等物を含むと意図する。

**【 0 0 8 6 】**

例えば、本発明の実施形態は PCIe スイッチを通じてサーバーノードに連結される PCIe ポートを含むソリッドステートドライブとしてコンピューティング資源に関して説明したが、本発明の実施形態はこれに限定されない。例えば、本発明の実施形態において、ソリッドステートドライブは 2 以上のポートを含むが、代わりに多様な複数のエンドポイントポート (例えば、2 以上のポート) を含む SSD の使用も含む。また、本発明の一部の実施形態において、サーバーノードは複数のポートを通じてファブリックに連結される。例えば、サーバーノードは多数のホストリンクを通じて 1 つ以上のスイッチと連結され、それによって、ホストリンク又はスイッチが故障の状況において、サーバーノード及びコンピューティング資源の間の予備連結を提供する。ホストリンク及びスイッチの帯域幅に応じて、このような予備連結は、故障状態においても、サーバーノードが最高帯域幅にて動作するようにする。

40

**【 0 0 8 7 】**

一部の実施形態によれば、ソリッドステートドライブはイーサーネット (登録商標) 、IB (Infiniband (登録商標)) 、FC (Fibre Channel) 、SA

10

20

30

40

50

S ( s e r i a l l y a t t a c h e d S C S I ) 等の他のインターフェイスを使用する。例えば、イーサーネット（登録商標）インターフェイスの場合に、P C I e スイッチはネットワーク（イーサーネット（登録商標））スイッチに交替される。

#### 【 0 0 8 8 】

一部の実施形態によれば、適応的多重経路ファブリックを使用して連結された資源はハードディスクドライブ、テープドライブ、D R A Mのような揮発性メモリの他の形態のコンピューティング資源、及びベクトルプロセッサ、G P U、D S P、F P G Aのようなコンピューティングユニットである。

#### 【 0 0 8 9 】

本発明のその他の実施形態において、個別的なコンピューティング資源の各々は複数のポートを含むことを必要としない。例えば、各コンピューティング資源セットは個別的なコンピューティング資源の各々へのリンク及び2つの連結されたスイッチ40にリンクを提供するアダプター又はスイッチを含む。さらに詳細な例として、データ格納装置32の各々は各データ格納装置32がデータ格納ストレージ装置のセットと連関されたアダプターと連結される単一ポートデータ格納装置である。アダプターは2つのスイッチ40と連結される。このような方式により、個別的なデータ格納装置の各々が単一ポート装置であっても、データ格納装置セット30は複数のスイッチ40に相変わらず連結される。このような技法は上述したように他の形態のコンピューティング資源に適用できる。

10

#### 【 0 0 9 0 】

説明を簡易にするために、インターフェイスの相対的な帯域幅は図示した実施形態において同一であるが（例えば、データ格納装置の各セットに対して6B、各サーバーノード及び対応するスイッチの間の連結に対して8B、及びスイッチの間の各クロス接続に対して2B）、本発明の実施形態がこれに限定されることではなく、本発明の実施形態は他の帯域幅（例えば、インターフェイスと連関されたコンピューティング資源の処理量と対応する帯域幅）を提供するインターフェイスを含む実施形態をさらに含む。1つのサーバーノードの故障状況において、適応的多重経路ファブリックと連結された資源の最大限のパフォーマンスを維持するように設計された本発明の一部の実施形態において、クロス接続の全体帯域幅（又はクロス接続帯域幅）は1つのノードによって一般的に提供される帯域幅と少なくとも同一であって十分である。本発明の一部の実施形態が本文において、クロス接続の全部が同一の帯域幅を有し、H Aペアが外部のすべてのスイッチに連結されると説明したが、本発明の実施形態がこれに限定されることではない。例えば、一部の実施形態において、クロス接続は他の帯域幅を有し、一部の実施形態において、クロス接続は他のスイッチの全部より少ない数にて形成される。

20

#### 【 0 0 9 1 】

説明を簡易にするために、8個以下のホストを含む実施形態を説明したが、本発明の実施形態がこれに限定されることなく、類似な概念が多様な数のホストにより具現される。

30

#### 【 0 0 9 2 】

同様に、本発明の実施形態が正確に6個のデータ格納装置のセットに限定されることではなく、各セットにおいて多数のS S D（例えば、各セットにおいて同一の数又は各セットにおいて多様な数）を含む実施形態をさらに含む。

40

#### 【 0 0 9 3 】

本発明の実施形態は、ファブリック故障検出及び再構成機能を使用してストレージ管理ツールと通信してストレージ基盤施設管理を向上させる。

#### 【 符号の説明 】

#### 【 0 0 9 4 】

1 0 ファブリック

1 2 クロス接続

1 4 ホストリンク

1 6 資源リンク

2 0 サーバーノード

50

- 2 2 ペア

2 4 ホストプロセッサ

2 6 ネットワークインターフェイス

3 0 データ格納装置セット

3 2 データ格納装置

4 0 スイッチ

5 0 補助ファブリック

5 2 相互連結

5 4 補助スイッチ

1 0 0 データ格納システム

10

【図面】

【図1】

【図2】

20

30

40

50

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

【図 7】

【図 8】

10

20

【図 9】

30

40

50

---

フロントページの続き

3 1 4

(72)発明者 ステファン ジー . フィッシャー

アメリカ合衆国 9 4 0 4 1 カリフォルニア州 マウンテン ビュー 2 6 3 ビラ エステー アバ

ート 1 6 0 0

(72)発明者 ジャン ピン

アメリカ合衆国 9 5 0 3 5 カリフォルニア州 ミルピタス ガルシア コート 3 1 6

(72)発明者 インディラ ジョシ

アメリカ合衆国 9 5 0 7 0 カリフォルニア州 サラトガ ボニー リッジ ウェイ 1 9 9 5 0

(72)発明者 ハリー ロジャース

アメリカ合衆国 9 5 1 2 5 カリフォルニア州 クレストフィールド ドライブ 1 3 3 5

審査官 大石 博見

(56)参考文献 米国特許出願公開第2 0 0 9 / 0 2 0 4 7 4 3 ( U S , A 1 )

(58)調査した分野 (Int.Cl. , D B 名)

H 0 4 L 4 5 / 2 8

H 0 4 L 4 7 / 1 2 5

G 0 6 F 1 3 / 0 0