(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-278407

(P2006-278407A)

(43) 公開日 平成18年10月12日(2006.10.12)

(51) Int.CI.

H01L 21/60

(2006.01)

F 1

H01L 21/60

301D

テーマコード(参考)

5FO44

審査請求 未請求 請求項の数 9 O L (全 14 頁)

|           |                            |           |                                                 |

|-----------|----------------------------|-----------|-------------------------------------------------|

| (21) 出願番号 | 特願2005-91023 (P2005-91023) | (71) 出願人  | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |

| (22) 出願日  | 平成17年3月28日 (2005.3.28)     | (74) 代理人  | 100082175<br>弁理士 高田 守                           |

|           |                            | (74) 代理人  | 100106150<br>弁理士 高橋 英樹                          |

|           |                            | (72) 発明者  | 新川 秀之<br>東京都千代田区丸の内二丁目4番1号 株<br>式会社ルネサステクノロジ内   |

|           |                            | F ターム(参考) | 5F044 AA07 AA12 CC01 CC05 CC07<br>HH00          |

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】 高集積化された半導体装置を安定して製造することができる半導体装置の製造方法を得る。

【解決手段】 複数のパッドについてバンプ電極を形成し、そのバンプ電極上にワイヤをステッチボンディングする場合に、まず、第1工程として、複数のパッドの1つにバンプ電極を形成する。次に、第2工程として、第1工程の直後に、バンプ電極上にワイヤをステッチボンディングする。そして、第3工程として、複数のパッドの他の各パッドについて同様に第1工程と第2工程を繰り返し行う。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

第1の複数のパッドを有する第1のチップと、第2の複数のパッドを有する第2のチップを準備する工程と、

キャピラリから排出したワイヤによって、前記第1の複数のパッドの何れかに、第1のバンプ電極を形成する工程と、

前記第1のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第1のバンプ電極と、前記第2の複数のパッドの何れかとを電気的に接続する第1のワイヤを形成する工程と、

前記第1のワイヤを形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第1の複数のパッドの別の何れかに、第2のバンプ電極を形成する工程とを有する半導体装置の製造方法。 10

**【請求項 2】**

前記第1のワイヤを形成する工程は、前記キャピラリから排出したワイヤの先端に、金属ボールを形成する工程と、前記金属ボールを前記第2の複数のパッドの何れかにボンディングする工程と、前記金属ボールから伸びるワイヤを前記キャピラリから排出して、前記金属ボールから伸びるワイヤの一部を前記第1のバンプ電極上にステッチボンディングする工程とを有する半導体装置の製造方法。

**【請求項 3】**

前記第1のバンプ電極を形成する工程は、前記キャピラリから排出したワイヤの先端に、金属ボールを形成する工程と、前記金属ボールを前記第1の複数のパッドの何れかにボンディングする工程と、前記金属ボールから伸びるワイヤを前記金属ボール上でカットする工程とを有する半導体装置の製造方法。 20

**【請求項 4】**

前記第2のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第2のバンプ電極と、前記第2の複数の電極パッドの別の何れかとを電気的に接続する第2のワイヤを形成する工程とを有する半導体装置の製造方法。

**【請求項 5】**

第1の複数のパッドと、前記第1の複数のパッドよりも間隔が狭い第2の複数のパッドとを有する第1のチップと、第3の複数のパッドを有する第2のチップを準備する工程と、 30

キャピラリから排出したワイヤによって、前記第1の複数のパッド上に、第1の複数のバンプ電極を形成し、前記第2の複数のパッド上に、第2の複数のバンプ電極を形成する工程と、

前記第1及び第2の複数のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第1の複数のバンプ電極と、前記第3の複数のパッドの何れかとを電気的に接続する第1の複数のワイヤを形成する工程と、

前記第1の複数のワイヤを形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第2の複数のバンプ電極と、前記第3の複数のパッドの別の何れかとを電気的に接続する第2の複数のワイヤを形成する工程とを有する半導体装置の製造方法。 40

**【請求項 6】**

キャピラリに通したワイヤによりパッド上にバンプ電極を形成する工程と、

前記バンプ電極を形成する工程の後に、少なくとも前記ワイヤと前記キャピラリの内壁との隙間以上の振幅で前記キャピラリを横方向に動作させる工程と、

前記キャピラリを横方向に動作させる工程の後に、クランバで前記ワイヤを挟んで上方に引っ張ることで前記ワイヤをカットする工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 7】**

前記キャピラリを横方向に動作させる前に、前記キャピラリを前記バンプ電極よりも上方に退避させる工程を更に有することを特徴とする請求項3に記載の半導体装置の製造方法 50

。

### 【請求項 8】

キャピラリを用いてバンプ電極上にワイヤをステッチボンディングする工程と、前記ステッチボンディングする工程の後に、少なくとも前記ワイヤと前記キャピラリの内壁との隙間以上の振幅で前記キャピラリを横方向に動作させる工程と、

前記キャピラリを横方向に動作させる工程の後に、クランパで前記ワイヤを挟んで上方に引っ張ることで前記ワイヤをカットする工程とを有することを特徴とする半導体装置の製造方法。

### 【請求項 9】

前記キャピラリを横方向に動作させる前に、前記キャピラリを、前記ステッチボンディングした位置から、前記ワイヤのループ進入方向に前記キャピラリの横方向動作の振幅の半分以上退避させる工程を更に有することを特徴とする請求項 5 に記載の半導体装置の製造方法。 10

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、キャピラリに通した金属ワイヤによりバンプ電極を形成し、そのバンプ電極上に金属ワイヤをステッチボンディングする半導体装置の製造方法に関するものである。 20

#### 【背景技術】

#### 【0002】

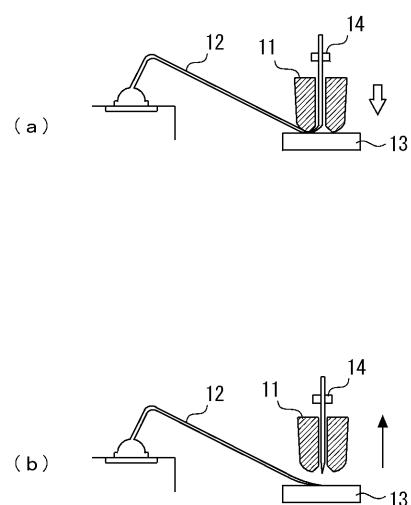

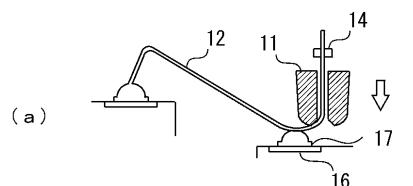

図 9 ( a ) 及び ( b ) は、リード上にステッチボンディングする様子を示す断面図である。図 9 ( a ) に示すように、キャピラリ 11 により金の合金からなるワイヤである金ワイヤ 12 をリード 13 に押圧し、超音波振動をかけて金ワイヤ 12 をリード 13 にステッチボンディングする。この際、リード 13 は堅いため、キャピラリ 11 とリード 13 に挟まれた金ワイヤ 12 は肉薄化される。これにより金ワイヤ 12 の強度が低くなるため、図 9 ( b ) に示すように、クランパ 14 で金ワイヤ 12 を挟んで上方に引っ張ることで金ワイヤ 12 を容易にカット ( テールカット ) することができる。金属ワイヤとしては、金ワイヤ以外の金属製のワイヤを用いる事もある。 20

#### 【0003】

チップ上の A 1 パッドに直接に金ワイヤをボンディングする場合、キャピラリの荷重が集中して A 1 パッド下の SiO<sub>2</sub> 層間絶縁膜にクラックが入る。このため、チップツーチップ ( chip-to-chip ) のワイヤボンディングにはバンプ電極が用いられる ( 例えば、特許文献 1 参照 )。また、薄型パッケージでは、金ワイヤの高さを低くするためにバンプ電極を用いた逆ボンディングが行われる。 30

#### 【0004】

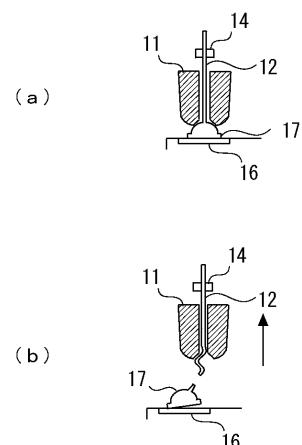

図 10 ( a ) 及び ( b ) は、従来のバンプ電極形成の様子を示す断面図である。まず、図 10 ( a ) に示すように、チップの A 1 パッド 16 上に、キャピラリ 11 から排出した金ワイヤ 12 によりバンプ電極 17 を形成する。その後、図 10 ( b ) に示すように、クランパ 14 で金ワイヤ 12 を挟んで上方に引っ張ることで金ワイヤ 12 をカットする。 40

#### 【0005】

また、図 11 ( a ) 及び ( b ) は、従来のバンプ電極上への金ワイヤのステッチボンディングの様子を示す断面図である。まず、図 11 ( a ) に示すように、キャピラリ 11 により金ワイヤ 12 をバンプ電極 17 に押圧し、超音波振動をかけて金ワイヤ 12 を潰してバンプ電極 17 に接合する。その後、図 11 ( b ) に示すように、クランパ 14 で金ワイヤ 12 を挟んで上方に引っ張ることで金ワイヤ 12 をカットする。 40

#### 【0006】

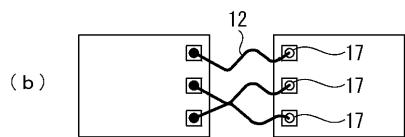

また、図 12 ( a ) 及び ( b ) は、従来のチップ間ワイヤの方法を示す上面図である。図 12 ( a ) に示すように複数のバンプ電極 17 を全部作った後に、図 12 ( b ) に示すように各バンプ電極 17 上に金ワイヤ 12 をステッチボンディングする。

#### 【0007】

50

20

30

40

50

【特許文献 1】特開 2001 - 15541 号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかし、従来のバンプ電極上への金ワイヤのステッチボンディングにおいて、バンプ電極 17 は柔らかいため、キャピラリ 11 とバンプ電極 17 で挟まれた金ワイヤ 12 の押し潰しが不十分となり、金ワイヤ 12 を十分に肉薄化することができない。これにより、金ワイヤ 12 の強度が高くなるため、金ワイヤ 12 をカットした際の反動による金ワイヤ 12 のヨレや、バンプ電極 17 の A1 パッド 16 からの引き剥がしが発生する。また、従来のバンプ電極形成でも同様の現象が発生する。その結果、ヨレに起因する金ワイヤ 12 の S 字曲がりにより金ワイヤ同士が電気的にショートし、またバンプ電極 17 の引き剥がしがにより電気的にオープンするため、高集積化された半導体装置を安定して製造することができないという問題があった。

【0009】

特に、従来のチップ間ワイヤの方法（図 12 (a) 及び (b)）を用いると、バンプ電極 17 の形成において消費される金ワイヤ 12 の長さは短いため、バンプ電極 17 を連続して形成する工程において、キャピラリ内に特定のワイヤが消費されずに残り続ける。従って、バンプ電極 17 の連続形成によりキャピラリ内の特定の金ワイヤ 12 にヨレが繰り返し蓄積され、キャピラリの長さとほぼ同じ 10 mm 程度までよれが大きくなる。これにより、金ワイヤ 12 の S 字曲がりが大きくなり、金ワイヤ 12 同士のショートが発生し易くなる。

【0010】

本発明は、上述のような課題を解決するためになされたもので、その目的は、高集積化された半導体装置を安定して製造することができる半導体装置の製造方法を得るものである。

【課題を解決するための手段】

【0011】

第 1 の発明は、第 1 の複数のパッドを有する第 1 のチップと、第 2 の複数のパッドを有する第 2 のチップを準備する工程と、

キャピラリから排出したワイヤによって、前記第 1 の複数のパッドの何れかに、第 1 のバンプ電極を形成する工程と、

前記第 1 のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第 1 のバンプ電極と、前記第 2 の複数のパッドの何れかとを電気的に接続する第 1 のワイヤを形成する工程と、

前記第 1 のワイヤを形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第 1 の複数のパッドの別の何れかに、第 2 のバンプ電極を形成する工程とを有する半導体装置の製造方法である。

【0012】

第 2 の発明は、第 1 の複数のパッドと、前記第 1 の複数のパッドよりも間隔が狭い第 2 の複数のパッドとを有する第 1 のチップと、第 3 の複数のパッドを有する第 2 のチップを準備する工程と、

キャピラリから排出したワイヤによって、前記第 1 の複数のパッド上に、第 1 の複数のバンプ電極を形成し、前記第 2 の複数のパッド上に、第 2 の複数のバンプ電極を形成する工程と、

前記第 1 及び第 2 の複数のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第 1 の複数のバンプ電極と、前記第 3 の複数のパッドの何れかとを電気的に接続する第 1 の複数のワイヤを形成する工程と、

前記第 1 の複数のワイヤを形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第 2 の複数のバンプ電極と、前記第 3 の複数のパッドの別の何れかとを電気的に接続する第 2 の複数のワイヤを形成する工程とを有する半導体装置の製造方法である。

10

20

30

40

50

## 【0013】

第3の発明は、キャピラリに通したワイヤによりパッド上にバンプ電極を形成する工程と、前記バンプ電極を形成する工程の後に、少なくともワイヤとキャピラリの内壁との隙間以上の振幅でキャピラリを横方向に動作させる工程と、前記キャピラリを横方向に動作させる工程の後に、クランバでワイヤを挟んで上方向に引っ張ることでワイヤをカットする工程とを有する半導体装置の製造方法である。

## 【0014】

第4の発明は、キャピラリを用いてバンプ電極上にワイヤをステッチボンディングする工程と、前記ステッチボンディングする工程の後に、少なくともワイヤとキャピラリの内壁との隙間以上の振幅でキャピラリを横方向に動作させる工程と、前記キャピラリを横方向に動作させる工程の後に、クランバでワイヤを挟んで上方向に引っ張ることでワイヤをカットする工程とを有する半導体装置の製造方法である。

10

## 【発明の効果】

## 【0015】

第1の発明により、1回のテールカットの反動によるワイヤのヨレを分散することができるため、ワイヤのS字曲がりを防ぐことができる。第2の発明により、ワイヤのS字曲がりによるワイヤ同士の電気的ショートを防ぐことができる。第3の発明又は第4の発明により、金ワイヤのS字曲がり及びバンプ電極の剥がれを抑制することができる。よって、本発明によれば、高集積化された半導体装置を安定して製造することができる。

20

## 【発明を実施するための最良の形態】

## 【0016】

## 実施の形態1.

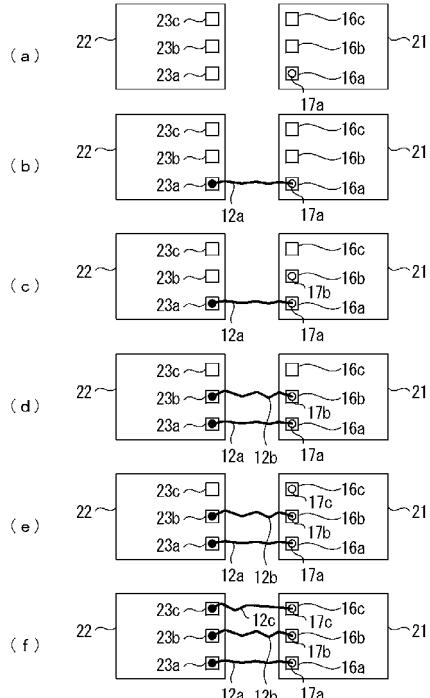

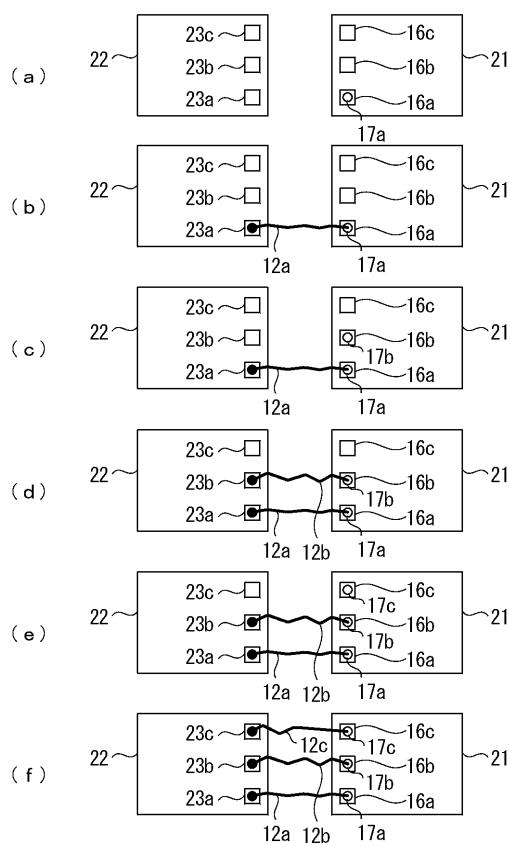

図1(a)～(f)は、本発明の実施の形態1に係る半導体装置の製造方法を示す上面図であり、図2(a)～(d)はその断面図である。

## 【0017】

まず、図1(a)に示すように、A1パッド16a～16c(第1の複数のパッド)を有するチップ21(第1のチップ)と、A1パッド23a～23c(第2の複数のパッド)を有するチップ22(第2のチップ)を準備する。次に、図2(a)に示すように、キャピラリ11から排出した金ワイヤ12の先端をトーチ31からの放電により溶融することによって、金ワイヤ12よりも直径が大きい金ボール32を形成する。その後、図2(b)に示すように、キャピラリ11によって、金ボール32をステージ33上に配置されたチップ21のA1パッド16a上に押圧し、加重、熱、超音波などを印可する事によって、金ボール32とA1パッド16aの界面を接合する。その後、図1(a)及び図2(c)に示すように、キャピラリ11より上の金ワイヤ12をクランバ14で挟んで引っ張り、金ボール32の上で金ワイヤ12を切断する。このようにして、キャピラリ11から排出した金ワイヤ12によって、A1パッド16aにバンプ電極17a(第1のバンプ電極)を形成する。

30

## 【0018】

その後に、図2(a)と同様にキャピラリ11から排出した金ワイヤ12の先端に金ボール32を形成し、図1(b)及び図2(d)に示すように、キャピラリ11を用いて金ワイヤ12の先端の金ボール32をチップ22のA1パッド23aにボールボンディング(ファーストボンディング)する。その後、金ボール32から延びる金ワイヤ12をキャピラリ11から排出して、バンプ電極17a上まで伸ばし、キャピラリ11により金ワイヤ12をバンプ電極17aに10ms間押圧し、超音波振動をかけて、金ボール32から延びる金ワイヤ12の一部をバンプ電極17a上にステッチボンディング(セカンドボンディング)する。そして、クランバ14で金ワイヤ12を挟んで上方向に引っ張ることで金ワイヤ12をカット(テールカット)する。このようにして、キャピラリ11から排出した金ワイヤ12によって、バンプ電極17aとA1パッド23aを電気的に接続する金ワイヤ12a(第1のワイヤ)を形成する。

40

## 【0019】

50

その後に、図1(c)に示すように、図1(a)及び図2(c)と同様に、チップ21のA1パッド16bにバンプ電極17b(第2のバンプ電極)を形成する。その後に、図1(d)に示すように、チップ22のA1パッド23bに金ワイヤ12の先端の金ボールをボールボンディングした後、金ワイヤ12をバンプ電極17b上にステッチボンディングする。このようにして、キャピラリ11から排出した金ワイヤ12によって、バンプ電極17bとA1パッド23bを電気的に接続する金ワイヤ12b(第2のワイヤ)を形成する。

#### 【0020】

その後に、図1(e)に示すように、チップ21のA1パッド16cにバンプ電極17cを形成する。その後に、図1(f)に示すように、チップ22のA1パッド23cに金ワイヤ12の先端の金ボールをボールボンディングした後、金ワイヤ12をバンプ電極17c上にステッチボンディングすることで、バンプ電極17cとA1パッド23cを電気的に接続する金ワイヤ12cを形成する。

#### 【0021】

このように、実施の形態1では、まず、複数のA1パッドの1つにバンプ電極を形成し、その直後にバンプ電極上に金ワイヤをステッチボンディングする。そして、他のA1パッドについても同様の工程を繰り返し行う。これにより、連続的に複数のバンプ電極をまとめて形成した後に、複数の金ワイヤをボンディングする従来の方法(図12(a)及び(b))に比べて、1回のテールカットの反動による金ワイヤのヨレを分散することができるため、バンプ電極形成のたびに発生する金ワイヤのS字曲がりの大幅な蓄積を抑制することができる。本発明においては、バンプ電極の形成1回ごとに、チップ間を接続するワイヤを形成する事で、金ワイヤのS字曲がりの蓄積を最小限に抑える事ができる。しかし、これに限る物ではなく、複数のバンプ電極をまとめて形成した後に、チップ間を接続するワイヤを形成するようにしても良い。しかしこの場合でも、大量のバンプ電極をまとめて形成すると、キャピラリ内の特定のワイヤに対するS字曲がりの蓄積が大きくなるため、まとめて形成するバンプ電極の個数はなるべく少ない方が好ましい。例えば、複数のバンプをまとめて形成する場合でも、バンプ形成工程と、ワイヤ形成工程を複数回繰り返すようにする事により、全てのバンプをまとめて形成した後に、ワイヤを形成する場合に比較して、キャピラリ内の特定のワイヤに対するS字曲がりの蓄積を多少なりとも抑制する事ができ好ましい。

#### 【0022】

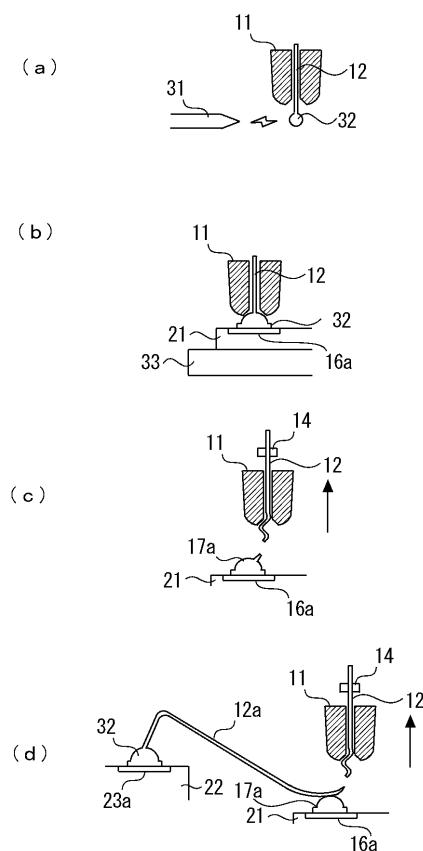

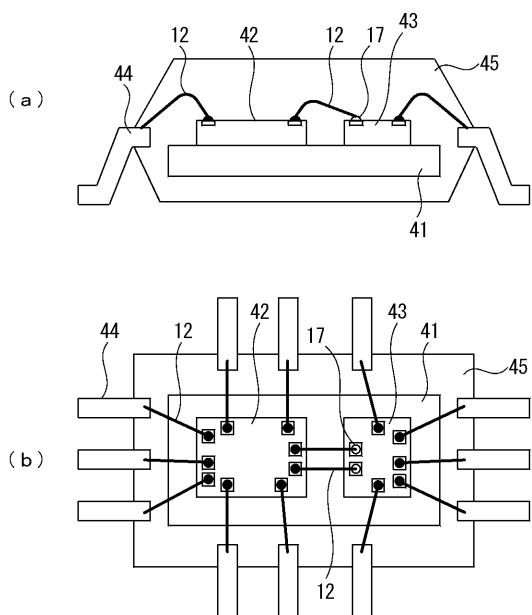

図3(a)は、本発明を適用することができる半導体装置の一例を示す断面図であり、図3(b)はその上面図である。ガラスエポキシ配線基板31上に、チップ32、スペーサチップ33、チップ34、チップ35が積載されている。また、チップ34, 35上にはバンプ電極17が形成されている。そして、金ワイヤ12が、リード36にボールボンディングされ、バンプ電極17上にステッチボンディングされている。このように、チップ上に複数のバンプ電極を形成し、前記チップ上のバンプ電極にステッチボンディングによって接続する複数のワイヤを形成する半導体装置の製造方法に本発明を適用することができる。このような場合でも、やはり、何れかのチップ上に形成する全てのバンプ電極をまとめて形成した後で、そのチップに接続するワイヤを形成するのは好ましくなく、例えば、バンプ電極を1個形成するごとに、接続するワイヤを形成するか、もしくは、複数のバンプを形成する工程と、複数のワイヤを形成する工程を繰り返すようにするのが好ましい。図3の半導体装置においては、さらに、全体が樹脂37により封止され、ガラスエポキシ配線基板31の底面に半田ボール38が形成されている。

#### 【0023】

図4(a)は、本発明を適用することができる半導体装置の他の例を示す断面図であり、図4(b)はその上面図である。ダイパッド41上にチップ42とチップ43が並べて搭載されている。このチップ42, 43とリード44は金ワイヤ12により接続されている。また、チップ43のA1パッド上にはバンプ電極17が形成されている。そして、金ワイヤ12が、チップ42のA1パッドにボールボンディングされ、バンプ電極17上に

10

20

30

40

50

ステッチボンディングされている。このチップ間ボンディングに本発明を適用することができる。さらに、全体が樹脂45により封止されている。

#### 【0024】

##### 実施の形態2.

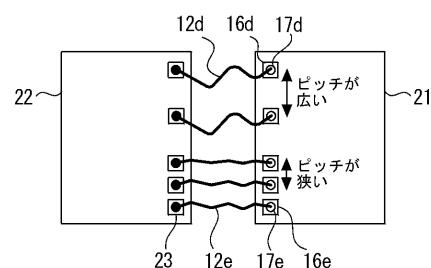

図5は、本発明の実施の形態2に係る半導体装置の製造方法を示す上面図である。まず、図5に示すように、複数のA1パッド16d(第1の複数のパッド)と、この複数のA1パッド16dよりも間隔が広い複数のA1パッド16e(第2の複数のパッド)とを有するチップ21(第1のチップ)と、複数のA1パッド23(第3の複数のパッド)を有するチップ22(第2のチップ)を準備する。

#### 【0025】

次に、キャピラリ11から排出した金ワイヤによって、チップ21の複数のA1パッド16dにそれぞれバンプ電極17d(第1の複数のバンプ電極)を形成し、複数のA1パッド16eにそれぞれバンプ電極17e(第2の複数のバンプ電極)を形成する。

#### 【0026】

その後、キャピラリから排出したワイヤによって、複数のバンプ電極17dと、複数のA1パッド23の何れかとを電気的に接続する金ワイヤ12d(第1の複数のワイヤ)を形成する。具体的には、キャピラリを用いてチップ22の複数のA1パッド23の一つに金ワイヤ12dの先端の金ボールをボールボンディングした後、対応するA1パッド16dのバンプ電極17d上に金ワイヤ12をステッチボンディングする。

#### 【0027】

その後、同様に、キャピラリから排出したワイヤによって、複数のバンプ電極17eと、複数のA1パッド23の別の何れかとを電気的に接続する金ワイヤ12e(第2の複数のワイヤ)を形成する。

#### 【0028】

このように、チップ21の複数のA1パッド16d, 16eのうち、隣接するパッド間のピッチが広いパッド16dに接続するワイヤ12dの形成を、ピッチが狭いパッド16eへ接続するワイヤ12eの形成よりも先に行う。

#### 【0029】

ここで、チップ21の複数のA1パッド16d, 16eに、ステッチボンディングによりワイヤを接続する場合には、ステッチボンディング工程におけるチップへの局所的な応力集中を軽減するために、あらかじめ柔軟な金ボールからなるバンプ電極17d, 17eをA1パッド16d, 16e上に形成しておく。このとき、複数のバンプ電極17d, 17eをA1パッド16d, 16e上に形成しておく。このとき、複数のバンプ電極17d, 17eを連続して形成すると、金ワイヤの消費量が少ないために、バンプ電極形成によって発生する金ワイヤのS字曲がりが、キャピラリ11内の特定のワイヤに繰り返し蓄積され、大きなS字曲がりが生じたワイヤdがキャピラリ11内に形成される。このように、大きなS字曲がりが生じたワイヤ12dを、ピッチが狭いパッド16eに接続するワイヤとして使用すると、ワイヤ同士の短絡の可能性が高まる。

#### 【0030】

そこで、本発明においては、連続するバンプ電極17d, 17eの形成によって、大きなS字曲がりが蓄積されたワイヤ12dを、ピッチが広いパッド16dに接続するワイヤとして消費することで、ピッチが狭いパッド16eを接続するワイヤ12e同士の短絡の発生を防ぐことができる。

#### 【0031】

具体的には、ヨレが蓄積された金ワイヤを接続する対象である、ピッチが広いA1パッド16eについて、金ワイヤのループ長さに応じて最小ピッチを以下のようにするのが好ましい。

10

20

30

40

| 金ワイヤのループ長さ | A1パッドの最小ピッチ |

|------------|-------------|

| 0.4~5.0 mm | 150 μm以上    |

| 0.4~2.5 mm | 100 μm以上    |

| 0.4~1.8 mm | 70 μm以上     |

**【0032】**

なお、本実施の形態2を実施の形態1と組み合わせることで、金ワイヤのS字曲がりを抑制することができ、金ワイヤ同士が電気的にショートするのを更に確実に防ぐことができる。

10

**【0033】****実施の形態3.**

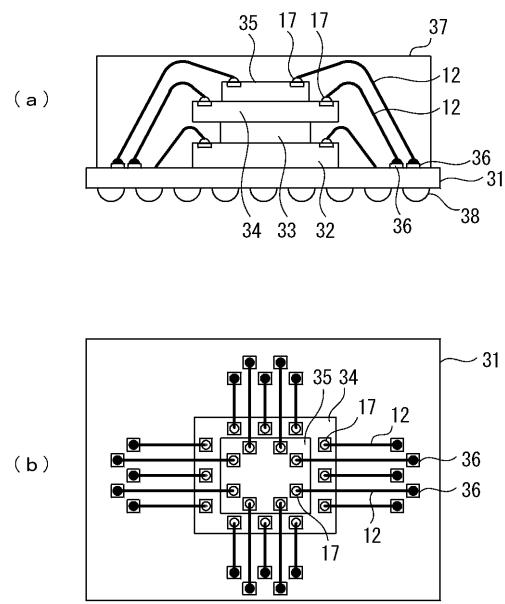

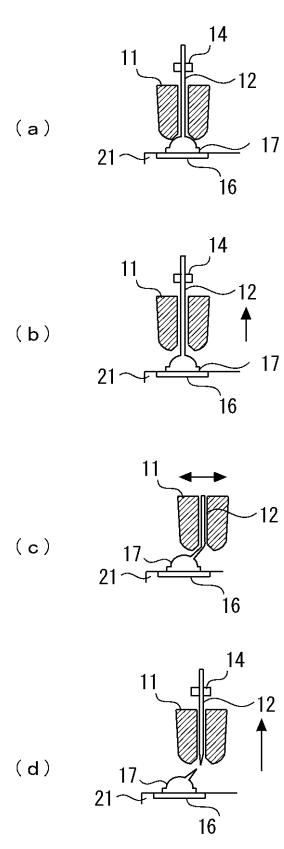

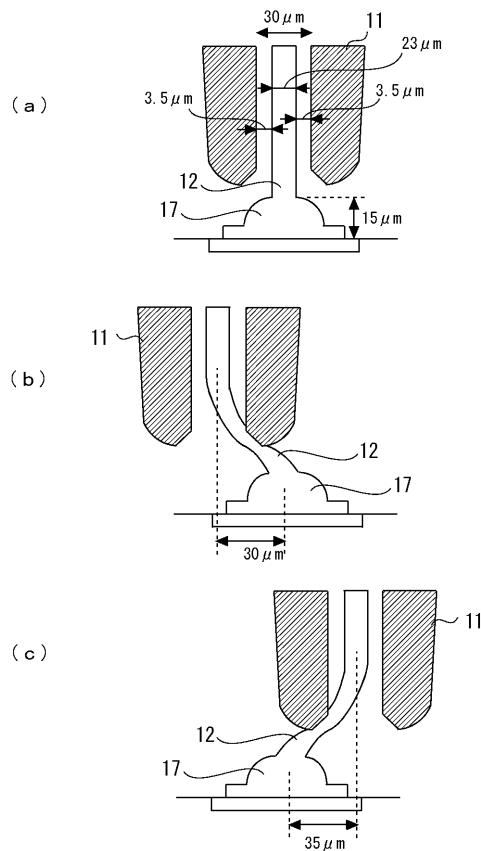

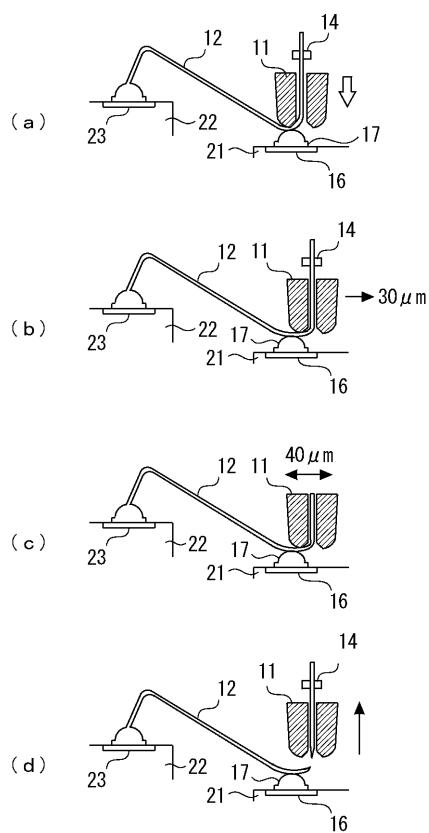

図6(a)~(d)は、本発明の実施の形態3に係る半導体装置の製造方法を示す断面図である。また、図7(a)~(c)は、キャピラリの先端部を示す拡大断面図である。

**【0034】**

まず、図6(a)に示すように、キャピラリ11から排出した金ワイヤ12の先端の金ボールをチップ21のA1パッド16上に接合させてバンプ電極17を形成する。そして、図6(b)に示すように、キャピラリ11を15 μm上昇させる。ここで、バンプ電極17の高さは15 μmであるため、キャピラリ11はバンプ電極17よりも上に退避される。本実施の形態において使用するキャピラリ11及び金ワイヤ12の寸法は、図7(a)に示すように、キャピラリ11の内径が30 μm、金ワイヤ12の直径が23 μmである。

20

**【0035】**

その後に、図6(c)に示すように、キャピラリ11を横方向に往復運動させる。ただし、キャピラリ11の動作振幅を少なくとも金ワイヤ12とキャピラリ11の内壁との隙間以上とする。具体的には、金ワイヤ12の直径が23 μm、キャピラリ11の内径が30 μmであるため、両者の隙間は平均すると片側で3.5 μm、両側合わせると7 μmである。動作振幅としては、最低限、キャピラリ11内壁と金ワイヤ12の片側の隙間である3.5 μm以上である必要がある。金ワイヤ12のテールカット部分に十分なストレスを付与し、カット強度を低下させるためには、動作振幅としては、キャピラリ11内壁と金ワイヤ12の両側の隙間の和である7 μm以上にするのがより好ましい。そこで、例えば図7(b)に示すように、キャピラリ11を一方向へ30 μm水平移動させた後、図7(c)に示すように、反対方向に65 μm水平移動させる。これにより、金ワイヤ12のテールカット部分にストレスを付与し、カット強度を低減させることができる。また、水平移動の大きさによっては、水平移動によって、金ワイヤ12をバンプ電極17から切断する事も可能である。

30

**【0036】**

その後に、図6(d)に示すように、クランバ14で金ワイヤ12を挟んで上方向に引っ張ることで金ワイヤ12をカットする。この際、キャピラリ11の往復運動により金ワイヤ12の強度を低減しているため、金ワイヤ12のカットの反動を低減することができ、金ワイヤ12のS字曲がり及びバンプ電極17の剥がれを抑制することができる。

40

**【0037】**

また、キャピラリ11の往復運動の前にキャピラリ11をバンプ電極17よりも上に退避することで、往復運動の際にキャピラリ11とバンプ電極17が接触してバンプ電極17がダメージを受けるのを防ぐことができる。

**【0038】**

なお、キャピラリ11を横方向へ往復運動させる代わりに横方向へ円運動させてもよく、その他、ベクトルで分解した場合に横方向への移動を含む動作であればよい。また、振動の周波数や動作手段については、特に限定する物ではないが、超音波振動の振幅は一般的に1 μm以下であるため、金ワイヤ12の強度を低減させるためのキャピラリ11の動

50

作として十分な振幅を得るのは難しい。本実施の形態においては、モーターを動力源として、機械的に位置制御しながら動作させることによって、上記キャピラリ11の水平移動動作を発生させた。また、本実施の形態3も図2又は図3の半導体装置に適用することができる。

#### 【0039】

##### 実施の形態4.

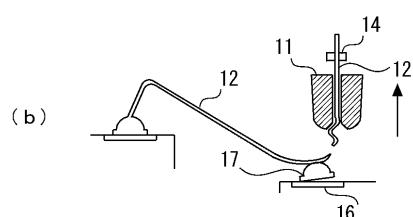

図8(a)～(d)は、本発明の実施の形態4に係る半導体装置の製造方法を示す断面図である。

#### 【0040】

まず、図8(a)に示すように、キャピラリ11を用いて、チップ22のA1パッド23に金ワイヤ12先端の金ボールをボールボンディングした後、チップ21のA1パッド16上に形成されたバンプ電極17上に金ワイヤ12をステッチボンディングする。具体的には、キャピラリ11により金ワイヤ12をバンプ電極17に10ms間押圧し、超音波振動をかけて金ワイヤ12を潰してバンプ電極17に接合する。10

#### 【0041】

その後に、図8(b)に示すように、キャピラリ11を金ワイヤ12のループ進入方向に、後工程のキャピラリ11の横方向動作の振幅の半分以上退避させる。例えば、キャピラリ11を30μm水平移動させる。

#### 【0042】

その後に、図8(c)に示すように、実施の形態3と同様に、キャピラリ11を横方向に往復運動させる。ただし、キャピラリ11の動作振幅を少なくとも金ワイヤ12とキャピラリ11の内壁との隙間以上とする。すなわち、動作振幅としては、最低限、キャピラリ11内壁と金ワイヤ12の片側の隙間である3.5μm以上である必要がある。また、金ワイヤ12のテールカット部分に十分なストレスを付与し、カット強度を低下させるためには、動作振幅としては、キャピラリ11内壁と金ワイヤ12の両側の隙間の和である7μm以上にするのがより好ましい。本実施の形態における動作振幅は40μmである。20

#### 【0043】

その後に、図8(d)に示すように、クランバ14で金ワイヤ12を挟んで上方向に引っ張ることで金ワイヤ12をカットする。この際、キャピラリ11の往復運動により金ワイヤ12のカット強度を低減しているため、金ワイヤ12のカットの反動を低減することができ、金ワイヤ12のS字曲がり及びバンプ電極17の剥がれを抑制することができる。往復運動の動作振幅によっては、往復運動によって金ワイヤ12を切断する事も可能である。この場合には、金ワイヤ12のカットの反動によるワイヤのS字曲がりは最小限に抑える事ができる。30

#### 【0044】

また、キャピラリ11の往復運動の前に、ステッチボンディングを開始した位置、すなわち、金ワイヤ12がバンプ電極17に接触した位置からキャピラリ11を往復動作の振幅の半分以上離しているため、キャピラリ11の往復運動において、金ワイヤ12とバンプ電極17との接合部分や、金ワイヤ12の根本の部分へのストレスの付与を軽減する事ができ、ワイヤの大幅な強度の低下や、断線を防ぐことができる。40

#### 【図面の簡単な説明】

#### 【0045】

【図1】本発明の実施の形態1に係る半導体装置の製造方法を示す上面図である。

【図2】本発明の実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図3】本発明を適用することができる半導体装置の一例を示す断面図(a)及び上面図(b)である。

【図4】本発明を適用することができる半導体装置の他の例を示す断面図(a)及び上面図(b)である。

【図5】本発明の実施の形態2に係る半導体装置の製造方法を示す上面図である。

【図6】本発明の実施の形態3に係る半導体装置の製造方法を示す断面図である。50

【図7】キャピラリの先端部を示す拡大断面図である。

【図8】本発明の実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図9】リード上にステッチボンディングする様子を示す断面図である。

【図10】従来のバンプ電極形成の様子を示す断面図である。

【図11】従来のバンプ電極上へのワイヤのステッチボンディングの様子を示す断面図である。

【図12】従来のチップ間ワイヤの方法を示す上面図である。

#### 【符号の説明】

##### 【0046】

11 キャピラリ

12、12a～12e 金ワイヤ(ワイヤ)

16、16a～16e、23、23a～23c Alパッド(パッド)

17、17a～17e バンプ電極

21、22 チップ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

## 【手続補正書】

【提出日】平成18年1月5日(2006.1.5)

## 【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

## 【請求項1】

第1の複数のパッドを有する第1のチップと、第2の複数のパッドを有する第2のチップを準備する工程と、

キャピラリから排出したワイヤによって、前記第1の複数のパッドの何れかに、第1のバンプ電極を形成する工程と、

前記第1のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第1のバンプ電極と、前記第2の複数のパッドの何れかとを電気的に接続する第1のワイヤを形成する工程と、

前記第1のワイヤを形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第1の複数のパッドの別の何れかに、第2のバンプ電極を形成する工程とを有する半導体装置の製造方法。

## 【請求項2】

前記第1のワイヤを形成する工程は、前記キャピラリから排出したワイヤの先端に、金属ボールを形成する工程と、前記金属ボールを前記第2の複数のパッドの何れかにボンディングする工程と、前記金属ボールから伸びるワイヤを前記キャピラリから排出して、前記金属ボールから伸びるワイヤの一部を前記第1のバンプ電極上にステッチボンディングする工程とを有する請求項1に記載の半導体装置の製造方法。

**【請求項3】**

前記第1のバンプ電極を形成する工程は、前記キャピラリから排出したワイヤの先端に、金属ボールを形成する工程と、前記金属ボールを前記第1の複数のパッドの何れかにボンディングする工程と、前記金属ボールから伸びるワイヤを前記金属ボール上でカットする工程とを有する請求項1に記載の半導体装置の製造方法。

**【請求項4】**

前記第2のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第2のバンプ電極と、前記第2の複数の電極パッドの別の何れかとを電気的に接続する第2のワイヤを形成する工程を有する請求項1に記載の半導体装置の製造方法。

**【請求項5】**

第1の複数のパッドと、前記第1の複数のパッドよりも間隔が狭い第2の複数のパッドとを有する第1のチップと、第3の複数のパッドを有する第2のチップを準備する工程と、

キャピラリから排出したワイヤによって、前記第1の複数のパッド上に、第1の複数のバンプ電極を形成し、前記第2の複数のパッド上に、第2の複数のバンプ電極を形成する工程と、

前記第1及び第2の複数のバンプ電極を形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第1の複数のバンプ電極と、前記第3の複数のパッドの何れかとを電気的に接続する第1の複数のワイヤを形成する工程と、

前記第1の複数のワイヤを形成する工程の後に、前記キャピラリから排出したワイヤによって、前記第2の複数のバンプ電極と、前記第3の複数のパッドの別の何れかとを電気的に接続する第2の複数のワイヤを形成する工程とを有する半導体装置の製造方法。

**【請求項6】**

キャピラリに通したワイヤによりパッド上にバンプ電極を形成する工程と、

前記バンプ電極を形成する工程の後に、少なくとも前記ワイヤと前記キャピラリの内壁との隙間以上の振幅で前記キャピラリを横方向に動作させる工程と、

前記キャピラリを横方向に動作させる工程の後に、クランバで前記ワイヤを挟んで上方に引っ張ることで前記ワイヤをカットする工程とを有することを特徴とする半導体装置の製造方法。

**【請求項7】**

前記キャピラリを横方向に動作させる前に、前記キャピラリを前記バンプ電極よりも上方に退避させる工程を更に有することを特徴とする請求項6に記載の半導体装置の製造方法。

**【請求項8】**

キャピラリを用いてバンプ電極上にワイヤをステッチボンディングする工程と、

前記ステッチボンディングする工程の後に、少なくとも前記ワイヤと前記キャピラリの内壁との隙間以上の振幅で前記キャピラリを横方向に動作させる工程と、

前記キャピラリを横方向に動作させる工程の後に、クランバで前記ワイヤを挟んで上方に引っ張ることで前記ワイヤをカットする工程とを有することを特徴とする半導体装置の製造方法。

**【請求項9】**

前記キャピラリを横方向に動作させる前に、前記キャピラリを、前記ステッチボンディングした位置から、前記ワイヤのループ進入方向に前記キャピラリの横方向動作の振幅の半分以上退避させる工程を更に有することを特徴とする請求項8に記載の半導体装置の製造方法。