(19) 日本国特許庁 (JP)

(12) 公 開 特 許 公 報(A)

(11) 特許出願公開番号

特開2006-99500

(P2006-99500A)

(43) 公開日 平成18年4月13日(2006.4.13)

(51) Int. Cl.

G05F 1/56 (2006.01)

F |

G05F 1/56 310C

G05F 1/56 310F

### テーマコード（参考）

5H430

| 審査請求 未請求 請求項の数 5 O L (全 11 頁) |                                                       |

|-------------------------------|-------------------------------------------------------|

| (21) 出願番号                     | 特願2004-285807 (P2004-285807)                          |

| (22) 出願日                      | 平成16年9月30日 (2004. 9. 30)                              |

| (71) 出願人                      | 000006220<br>ミツミ電機株式会社<br>東京都多摩市鶴牧2丁目11番地2            |

| (74) 代理人                      | 100077838<br>弁理士 池田 肇保                                |

| (72) 発明者                      | 山口 公一<br>神奈川県厚木市酒井1601 ミツミ電機<br>株式会社厚木事業所内            |

| F ターム (参考)                    | 5H430 BB01 BB05 BB09 EE03 FF02<br>FF13 GG01 HH03 LA00 |

(54) 【発明の名称】 レギュレータ回路

(57) 【要約】

【課題】 出力コンデンサ  $C_o$  の低容量化、低 ESR 化に対応できるレギュレータ回路を安価に提供する。

【解決手段】 電源端子 ( $V_{DD}$ ) と出力端子 ( $V_{OU}$ ) との間に接続された出力トランジスタ ( $Q10$ ) と、出力端子と接地端子との間の出力電圧を分圧して中間ノード ( $N1$ ) から分圧電圧を生成する分圧回路 ( $R1, R2$ ) と、基準電圧と分圧電圧との差に応じた誤差信号を発生するエラーアンプ ( $Q1 \sim Q8, 11$ ) と、誤差信号に応じて出力トランジスタを制御する制御トランジスタ ( $Q9$ ) とを備えるレギュレータ回路において、出力端子と分圧回路の中間ノード ( $N1$ ) との間に第1の位相補正用コンデンサ ( $C1$ ) を接続し、出力端子とエラーアンプの所定のノード ( $N2$ ) との間に第2の位相補正用コンデンサ ( $C2$ ) を接続する。

【選択図】 図4

## 【特許請求の範囲】

## 【請求項 1】

電源端子と出力端子と接地端子とを持つレギュレータ回路であって、前記電源端子と前記出力端子との間に接続された出力トランジスタと、該出力端子と前記接地端子との間の出力電圧を分圧して中間ノードから分圧電圧を生成する分圧回路と、基準電圧と前記分圧電圧との差に応じた誤差信号を発生するエラーアンプと、前記誤差信号に応じて前記出力トランジスタを制御する制御トランジスタとを備え、前記出力トランジスタを制御することにより前記出力電圧を安定化させる、前記レギュレータ回路において、

前記出力端子と前記分圧回路の前記中間ノードとの間に接続された第1の位相補正用コンデンサと、

前記出力端子と前記エラーアンプの所定のノードとの間に接続された第2の位相補正用コンデンサと

を有することを特徴とするレギュレータ回路。

## 【請求項 2】

請求項1に記載のレギュレータ回路において、

前記エラーアンプは、前記基準電圧が供給される制御端子を持つ第1のトランジスタと、前記分圧電圧が供給される制御端子を持つ第2のトランジスタと、前記第1のトランジスタおよび前記第2のトランジスタの一方の主要電極端子と前記接地端子との間に接続された定電流源と、前記第1のトランジスタの他方の主要電極端子と前記電源端子との間に接続された第1のカレントミラー回路と、前記第2のトランジスタの他方の主要電極端子と前記電源端子との間に接続された第2のカレントミラー回路と、前記第1のカレントミラー回路および前記第2のカレントミラー回路と前記接地端子との間に接続された第3のカレントミラー回路とから構成され、

前記第1のカレントミラー回路と前記第3のカレントミラー回路との接続点が前記誤差信号を出力する出力ノードであり、前記第3のカレントミラー回路は、前記出力ノードに一方の主要電極端子が接続されたトランジスタを含み、当該トランジスタの制御端子が前記所定のノードであることを特徴とするレギュレータ回路。

## 【請求項 3】

請求項2に記載のレギュレータ回路において、

前記エラーアンプを構成するトランジスタがバイポーラトランジスタで構成されており、前記第3のカレントミラー回路は、前記第2のカレントミラー回路と前記接地端子との間に接続された別のトランジスタを含み、当該別のトランジスタの制御端子と前記所定のノードとの間には同じ抵抗値を持つ2つの抵抗器が直列に接続され、該2つの抵抗器の接続点と前記別のトランジスタの一方の主要電極端子とが直接接続されていることを特徴とするレギュレータ回路。

## 【請求項 4】

請求項3に記載のレギュレータ回路において、

前記第2の位相補正用コンデンサは、0.5 pF～20 pFの範囲の容量値を持ち、前記2つの抵抗器の各々は、200～60kの範囲の抵抗値を持つことを特徴とするレギュレータ回路。

## 【請求項 5】

請求項4に記載のレギュレータ回路において、

前記2つの抵抗器の抵抗値と前記第2の位相補正用コンデンサの容量値とで規定される時定数が、進み位相補償を施したい周波数によって決められることを特徴とするレギュレータ回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、レギュレータ回路に関し、特に、大電流出力を必要とするシリーズレギュレ

10

20

30

40

50

ータ I C に関する。

【背景技術】

【0 0 0 2】

レギュレータ回路は、外部から供給される電源電圧を安定化し、安定化された出力電圧を出力端子へ供給する回路である。レギュレータ回路の出力端子には、出力コンデンサ（出力容量）が接続された上で、負荷が接続される。これにより、負荷には、レギュレータ回路で安定化され、かつ出力コンデンサで平滑化された出力電圧が供給される。

【0 0 0 3】

レギュレータ回路の出力側に接続される出力コンデンサ C。としては、電解コンデンサやタンタルコンデンサが一般的であるが、小型化の要請などに応えるため、より小容量のセラミックコンデンサも用いられるようになってきている。 10

【0 0 0 4】

ところで、コンデンサは、その種類によって異なる E S R 値 (Equivalent Series Resistance: 等価直列抵抗) を持つことが知られている。例えば、電解コンデンサは、周波数や温度により変化するが、およそ 0.1 ~ 100 [ ] の E S R 値を有し、タンタルコンデンサは、0.01 ~ 1 [ ] の E S R 値を有する。また、セラミックコンデンサは、0.001 ~ 0.1 [ ] の E S R 値を有している。そして、レギュレータ回路の出力端子に接続される出力コンデンサの E S R 値が、レギュレータ回路の位相補償レンジとの関係において適切でない場合、発振が生じることがある。

【0 0 0 5】

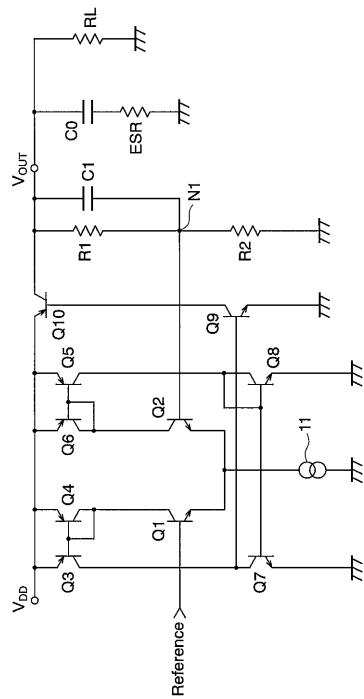

従来のレギュレータ回路は、例えば、図 1 に示されるように構成されている。 20

【0 0 0 6】

図示のレギュレータ回路は、電源端子 V<sub>DD</sub> と、接地端子 GND と、出力端子 V<sub>OUT</sub> とを有する 3 端子レギュレータ回路（シリーズレギュレータ I C）である。図示のレギュレータ回路は、出力電流が例えば 150 mA 以上の大電流出力用であるので、それを構成するトランジスタはバイポーラトランジスタである。周知のように、バイポーラトランジスタは、制御端子としてベースを持ち、一対の主要電極端子としてコレクタおよびエミッタを持つ。

【0 0 0 7】

このレギュレータ回路は、定電流源 1 1 と、第 1 乃至第 10 のトランジスタ Q 1 ~ Q 10 と、第 1 及び第 2 の抵抗器 R 1、R 2 と、位相補正用コンデンサ C 1 とを有している。 30

【0 0 0 8】

定電流源 1 1 と第 1 乃至第 8 のトランジスタ Q 1 ~ Q 8 とは、第 1 及び第 2 の抵抗器 R 1、R 2 で分圧された分圧電圧と、図示しない参照電圧生成回路で生成された参照電圧との差に応じた誤差信号を発生するエラーアンプを構成する。

【0 0 0 9】

第 9 のトランジスタ Q 9 は、エラーアンプが出力する誤差信号を増幅して第 10 のトランジスタ Q 10 のベースに供給する制御トランジスタとして働く。

【0 0 1 0】

第 10 のトランジスタ Q 10 は、電源端子 V<sub>DD</sub> と出力端子 V<sub>OUT</sub> との間に接続される出力トランジスタ（パワートランジスタ）であって、電源端子 V<sub>DD</sub> に与えられる入力電圧をレギュレートして出力電圧を出力端子 V<sub>OUT</sub> へ供給する。 40

【0 0 1 1】

第 1 及び第 2 の抵抗器 R 1 及び R 2 は、互いに直列接続され、出力端子 V<sub>OUT</sub> と接地端子 GND との間に接続される。これら抵抗器 R 1 及び R 2 は、前述の通り、出力電圧を分圧して分圧電圧を生成する分圧回路として働く。

【0 0 1 2】

位相補正用コンデンサ C 1 は、出力端子 V<sub>OUT</sub> と上記分圧回路の分圧電圧を生成する中間ノード N 1 との間に接続されている。

【0 0 1 3】

10

20

30

40

50

第1及び第2の抵抗器R1及びR2と位相補正用コンデンサC1との組み合わせは、進相補償回路として動作する（例えば、非特許文献1参照）。また、上述したレギュレタ回路は、例えば非特許文献2に記載されている。

【0014】

次に、エラーアンプの構成について説明する。第1のトランジスタQ1は、n p n形バイポーラトランジスタから成り、そのベースには基準電圧が供給される。第2のトランジスタQ2も、n p n形バイポーラトランジスタから成り、そのベースには分圧電圧が供給される。第1のトランジスタQ1と第2のトランジスタQ2のエミッタ同士は接続され、定電流源11を介して接地される。

【0015】

第1のトランジスタQ1のコレクタと電源端子V<sub>DD</sub>との間には、第3および第4のトランジスタQ3、Q4から構成される第1のカレントミラー回路が接続されている。第3および第4のトランジスタQ3、Q4は、p n p形バイポーラトランジスタから成る。第3および第4のトランジスタQ3、Q4のエミッタは電源端子V<sub>DD</sub>に接続されている。第3のトランジスタQ3のベースは第4のトランジスタQ4のベースに接続されている。第4のトランジスタQ4のベースは、第4のトランジスタQ4のコレクタに接続されている。第4のトランジスタQ4のコレクタは第1のトランジスタQ1のコレクタに接続されている。

【0016】

第2のトランジスタQ2のコレクタと電源端子V<sub>DD</sub>との間には、第5および第6のトランジスタQ5、Q6から構成される第2のカレントミラー回路が接続されている。第5および第6のトランジスタQ5、Q6は、p n p形バイポーラトランジスタから成る。第5および第6のトランジスタQ5、Q6のエミッタは電源端子V<sub>DD</sub>に接続されている。第5のトランジスタQ5のベースは第6のトランジスタQ6のベースに接続されている。第6のトランジスタQ6のベースは、第6のトランジスタQ6のコレクタに接続されている。第6のトランジスタQ6のコレクタは第2のトランジスタQ2のコレクタに接続されている。

【0017】

第1のカレントミラー回路および第2のカレントミラー回路と接地端子との間には、第7および第8のトランジスタQ7、Q8から構成される第3のカレントミラー回路が接続されている。第7および第8のトランジスタQ7、Q8は、n p n形バイポーラトランジスタから成る。第7および第8のトランジスタQ7、Q8のエミッタは接地端子に接続されている。第7のトランジスタQ7のベースは第8のトランジスタQ8のベースに接続されている。第7のトランジスタQ7のコレクタは第3のトランジスタQ3のコレクタに接続されている。第8のトランジスタQ8のベースは第8のトランジスタQ8のコレクタに接続されている。第8のトランジスタQ8のコレクタは第5のトランジスタQ5のコレクタに接続されている。

【0018】

第1のカレントミラー回路と第3のカレントミラー回路との接続点（換言すれば、第3のトランジスタQ3および第7のトランジスタQ7のコレクタ）が、上記誤差信号を出力する出力ノードである。

【0019】

制御トランジスタとして動作する第9のトランジスタQ9は、n p n形バイポーラトランジスタから成り、そのベースが上記出力ノードに接続され、エミッタが接地端子に接続されている。

【0020】

出力トランジスタとして動作する第10のトランジスタQ10は、p n p形バイポーラトランジスタから成り、そのベースが第9のトランジスタQ9のコレクタに接続され、エミッタが電源端子V<sub>DD</sub>に接続され、コレクタが出力端子V<sub>OUT</sub>に接続されている。

【0021】

10

20

30

40

50

図1のレギュレータ回路において、電源端子 $V_{DD}$ に電源電圧（例えば、3~7[V]）が与えられると、第1及び第2のトランジスタQ1, Q2には、これらのベースに与えられる電圧差に応じた電流が流れる。第1のトランジスタQ1のベースに供給される参照電圧は、例えば、0.6~1.2[V]である。

#### 【0022】

第1及び第2のカレントミラー回路は、第1及び第2のトランジスタQ1, Q2に流れる電流と同じ大きさの電流を第7及び第8のトランジスタQ7, Q8にそれぞれ流す。第7及び第8のトランジスタQ7, Q8に供給される電流の差が、第9のトランジスタQ9のベースに電圧（誤差信号）を与えることによって第9のトランジスタQ9に流れる電流が変化する。その結果、第10のトランジスタQ10のベース電流が変化し、出力端子 $V_{OUT}$ に供給される出力電圧（例えば、0.8~5[V]）がレギュレート（安定化）される。

10

#### 【0023】

位相補正用コンデンサC1は、例えば、20pFの容量値を持ち、このレギュレータ回路の位相補償レンジを拡大（位相進み補償）する。

#### 【0024】

一般に、レギュレータ回路が発振しないためには、ゲインが0dBになる周波数での位相余裕（マージン）が例えば45°以上に保たれている必要がある。

#### 【0025】

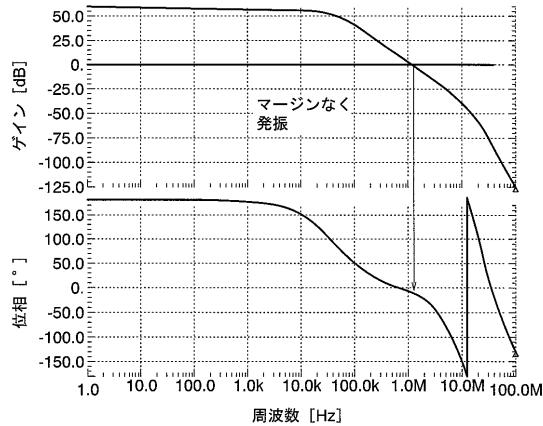

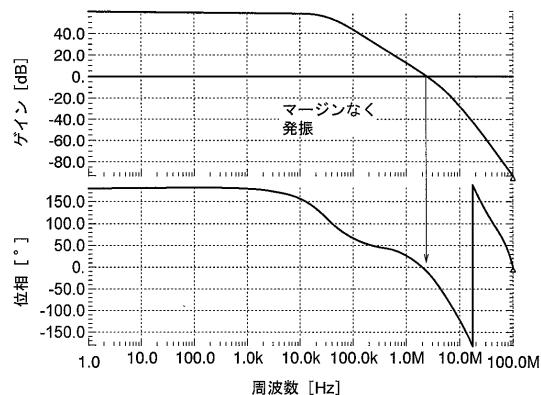

図2に、図1のレギュレータ回路から位相補正用コンデンサC1を削除したレギュレータ回路において、出力コンデンサC<sub>o</sub>のESRが0.01、出力電流が500mAのときの、レギュレータ回路のオープンループ特性を示す。この図2から、位相補正用コンデンサC1がないレギュレータ回路では、ゲインが0dBになる周波数での位相余裕（マージン）がないことが分かる。そのため、位相補正用コンデンサC1がないレギュレータ回路は発振する。

20

#### 【0026】

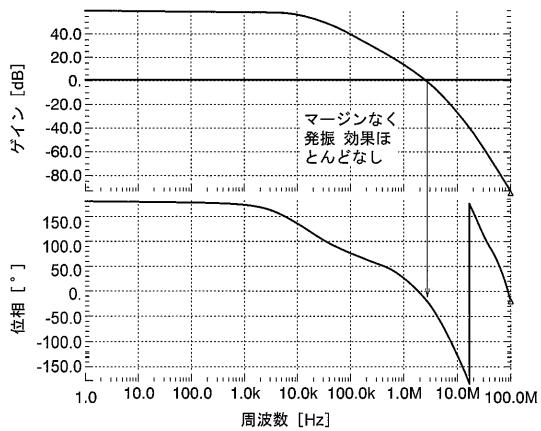

図3に、図1のレギュレータ回路において、出力コンデンサC<sub>o</sub>のESRが0.01、出力電流が500mAのときの、レギュレータ回路のオープンループ特性を示す。この図3から、位相補正用コンデンサC1があるレギュレータ回路でも、ゲインが0dBになる周波数での位相余裕（マージン）がないことが分かる。そのため、位相補正用コンデンサC1があるレギュレータ回路でも発振する。

30

#### 【0027】

このように、出力コンデンサC<sub>o</sub>のESRが低い場合には、たとえ位相補正用コンデンサC1を設けたとしても、レギュレータ回路が発振することが分かる。

#### 【0028】

【非特許文献1】トランジスタ技術 98.08号 p409

【非特許文献2】「実用アナログ電子回路設計法」、渡辺一雄著、総合電子出版社発行、1996.6.22、第1版4章 低電圧設計法と設計留意点 p110

#### 【発明の開示】

#### 【発明が解決しようとする課題】

40

#### 【0029】

上述したように、従来のレギュレータ回路は、出力コンデンサC<sub>o</sub>の低容量化、低ESR化に対応することが困難であるという問題点を有している。

#### 【0030】

そこで、本発明は、出力コンデンサC<sub>o</sub>の低容量化、低ESR化に対応できるレギュレータ回路を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0031】

本発明によれば、電源端子（ $V_{DD}$ ）と出力端子（ $V_{OUT}$ ）と接地端子とを持つレギュレータ回路であって、前記電源端子と前記出力端子との間に接続された出力トランジス

50

タ ( Q 1 0 ) と、該出力端子と前記接地端子との間の出力電圧を分圧して中間ノード ( N 1 ) から分圧電圧を生成する分圧回路 ( R 1 , R 2 ) と、基準電圧と前記分圧電圧との差に応じた誤差信号を発生するエラーアンプ ( Q 1 ~ Q 8 , 1 1 ) と、前記誤差信号に応じて前記出力トランジスタを制御する制御トランジスタ ( Q 9 ) とを備え、前記出力トランジスタを制御することにより前記出力電圧を安定化させる、前記レギュレータ回路において、前記出力端子と前記分圧回路の前記中間ノードとの間に接続された第 1 の位相補正用コンデンサ ( C 1 ) と、前記出力端子と前記エラーアンプの所定のノード ( N 2 ) との間に接続された第 2 の位相補正用コンデンサ ( C 2 ) とを有することを特徴とするレギュレータ回路が得られる。

## 【 0 0 3 2 】

上記レギュレータ回路において、前記エラーアンプは、前記基準電圧が供給される制御端子を持つ第 1 のトランジスタ ( Q 1 ) と、前記分圧電圧が供給される制御端子を持つ第 2 のトランジスタ ( Q 2 ) と、前記第 1 のトランジスタおよび前記第 2 のトランジスタの一方の主要電極端子と前記接地端子との間に接続された定電流源 ( 1 1 ) と、前記第 1 のトランジスタの他方の主要電極端子と前記電源端子との間に接続された第 1 のカレントミラー回路 ( Q 3 , Q 4 ) と、前記第 2 のトランジスタの他方の主要電極端子と前記電源端子との間に接続された第 2 のカレントミラー回路 ( Q 5 , Q 6 ) と、前記第 1 のカレントミラー回路および前記第 2 のカレントミラー回路と前記接地端子との間に接続された第 3 のカレントミラー回路 ( Q 7 , Q 8 ) とから構成される。前記第 1 のカレントミラー回路と前記第 3 のカレントミラー回路との接続点が前記誤差信号を出力する出力ノード ( N 3 ) である。前記第 3 のカレントミラー回路は、前記出力ノードに一方の主要電極端子が接続されたトランジスタ ( Q 7 ) を含み、当該トランジスタの制御端子が前記所定のノード ( N 2 ) である。

## 【 0 0 3 3 】

また、上記レギュレータ回路において、前記エラーアンプを構成するトランジスタは、バイポーラトランジスタで構成されて良い。その場合、前記第 3 のカレントミラー回路は、前記第 2 のカレントミラー回路と前記接地端子との間に接続された別のトランジスタ ( Q 8 ) を含み、当該別のトランジスタの制御端子と前記所定のノードとの間には同じ抵抗値を持つ 2 つの抵抗器 ( R 3 , R 4 ) が直列に接続され、該 2 つの抵抗器の接続点と前記別のトランジスタの一方の主要電極端子とが直接接続されていることが望ましい。

## 【 0 0 3 4 】

更に、上記レギュレータ回路において、前記第 2 の位相補正用コンデンサ ( C 2 ) は、0.5 pF ~ 20 pF の範囲の容量値を持ち、前記 2 つの抵抗器 ( R 3 , R 4 ) の各々は、200 ~ 600 k の範囲の抵抗値を持つことが好ましい。そして、前記 2 つの抵抗器の抵抗値と前記第 2 の位相補正用コンデンサの容量値とで規定される時定数は、進み位相補償を施したい周波数によって決められる。

## 【 0 0 3 5 】

なお、上記括弧内の符号は、本願発明の理解を容易にするために付したものであって、何ら本発明を限定するものではない。

## 【 発明の効果 】

## 【 0 0 3 6 】

レギュレータ回路の発振を防止するために、第 1 の位相補正用コンデンサばかりでなく第 2 の位相補正用コンデンサをも備えているので、低容量、低 ESR に対応できるレギュレータ回路を提供することができる。

## 【 発明を実施するための最良の形態 】

## 【 0 0 3 7 】

以下、本発明の実施の形態について図面を参照して詳細に説明する。

## 【 0 0 3 8 】

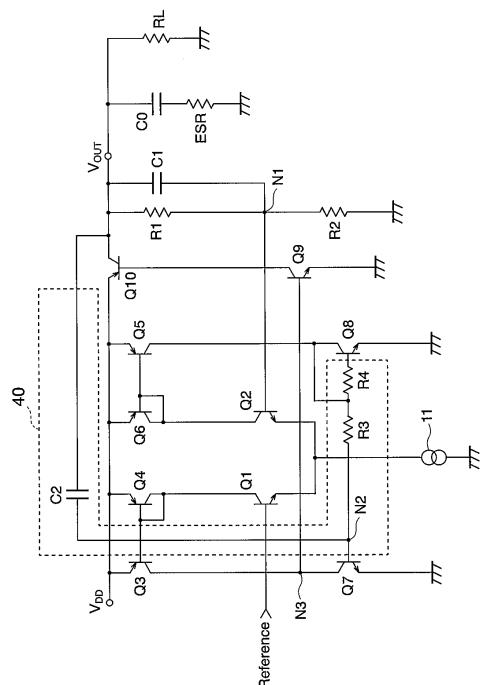

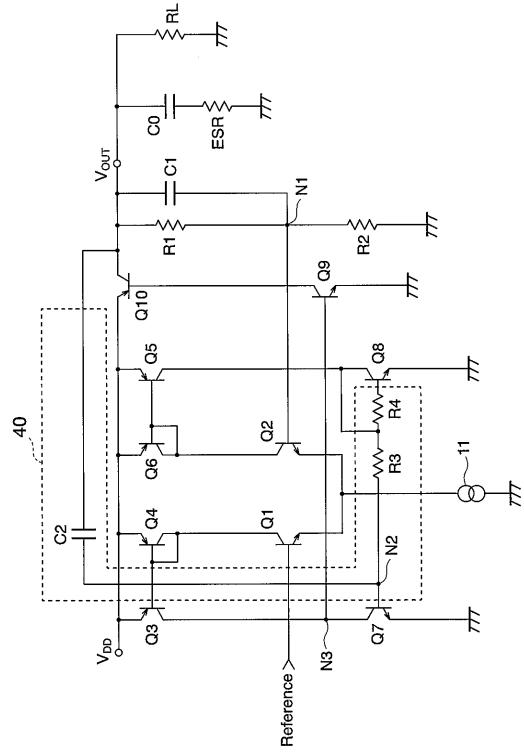

図 4 に本発明の一実施の形態に係るレギュレータ回路 ( シリーズレギュレータ I C ) の回路図を示す。このレギュレータ回路は、従来のレギュレータ回路とほぼ同じ構成を有し

10

20

30

40

50

ており、第2の位相補正用コンデンサC2を含む位相補正回路部40を有している点で異なっている。

【0039】

詳述すると、このレギュレータ回路は、定電流源11と、第1乃至第10のトランジスタQ1～Q10と、第1及び第2の抵抗器R1、R2と、第1の位相補正用コンデンサC1と、位相補正回路部40とを有している。ここで、位相補正回路部40は、第3及び第4の抵抗器R3及びR4（例えば、5[k]及び5[k]）と、第2の位相補正用コンデンサC2（例えば、3[pF]）とから構成されている。

【0040】

換言すると、図示のレギュレータ回路は、電源端子V<sub>DD</sub>と出力端子V<sub>OUT</sub>との間に接続された出力トランジスタQ10と、この出力端子V<sub>OUT</sub>と接地端子との間の出力電圧を分圧して中間ノードN1から分圧電圧を生成する分圧回路（R1, R2）と、基準電圧と分圧電圧との差に応じた誤差信号を発生するエラーアンプ（Q1～Q8、11）と、誤差信号に応じて出力トランジスタQ10を制御する制御トランジスタQ9とを備える。レギュレータ回路は、出力トランジスタQ10を制御することにより出力電圧を安定化させるものである。そして、図示のレギュレータ回路は、出力端子V<sub>OUT</sub>と分圧回路（R1, R2）の中間ノードN1との間に接続された第1の位相補正用コンデンサC1と、出力端子V<sub>OUT</sub>とエラーアンプの所定のノードN2（後述する）との間に接続された第2の位相補正用コンデンサC2を含む位相補正回路部40とを更に備えている。

【0041】

図示のレギュレータ回路は、大電流出力を必要とするレギュレータ回路であるので、それを構成するトランジスタはすべてバイポーラトランジスタで構成されている。周知のように、バイポーラトランジスタは、制御端子としてベースを持ち、一対の主要電極端子としてコレクタ及びエミッタを持っている。

【0042】

定電流源11と第1乃至第8のトランジスタQ1～Q8は、2つの入力信号（後述する分圧電圧及び参照電圧）の差に基づく誤差信号を生成するエラーアンプを構成する。

【0043】

第1及び第2のトランジスタQ1及びQ2は、ともにn-p-n形バイポーラトランジスタから成る。これらトランジスタQ1及びQ2のエミッタは定電流源11に共通に接続され、コレクタは後述する第1及び第2のカレントミラー回路に夫々接続されている。また、第1のトランジスタQ1のベースには、図示しない参照電圧生成回路で生成された参照電圧が供給される。第2のトランジスタQ2のベースには、分圧回路（R1, R2）の中間ノードN1から出力される分圧電圧が供給される。そして、第1及び第2のトランジスタQ1及びQ2は、これらのベースに供給される電圧の差に応じて、定電流源11が生成した定電流を分割する。

【0044】

第3及び第4のトランジスタQ3及びQ4は、ともにp-n-p形バイポーラトランジスタから成る。これらトランジスタQ3及びQ4のエミッタはともに電源端子V<sub>DD</sub>に接続され、ベースは互いに接続されるとともに第4のトランジスタQ4のコレクタにも接続されている。また、第3のトランジスタQ3のコレクタは、後述する第7のトランジスタQ7のコレクタに接続されている。これらトランジスタQ3及びQ4は、第1のカレントミラー回路を構成し、第1のトランジスタQ1に流れる電流と同一の電流を第7のトランジスタQ7に供給する。

【0045】

第5及び第6のトランジスタQ5及びQ6は、ともにp-n-p形バイポーラトランジスタから成る。これらトランジスタQ5及びQ6のエミッタはともに電源端子V<sub>DD</sub>に接続され、ベースは互いに接続されるとともに第6のトランジスタQ6のコレクタにも接続されている。また、第5のトランジスタQ5のコレクタは、後述する第8のトランジスタQ8のコレクタに接続されている。これらトランジスタQ5及びQ6は、第2のカレントミラ

10

20

30

40

50

一回路を構成し、第2のトランジスタQ2に流れる電流と同一の電流を第8のトランジスタQ8に供給する。

【0046】

第7及び第8のトランジスタQ7及びQ8は、ともにn p n形バイポーラトランジスタから成る。第7のトランジスタ(誤差信号生成用トランジスタ)Q7のエミッタは接地端子に接続され、ベースは位相補正回路部40の第3の抵抗器R3の一方の端子に接続されている。第8のトランジスタQ8のエミッタは接地端子に接続され、ベースは位相補正回路部40の第4の抵抗器R4の一方の端子に接続されている。第8のトランジスタQ8のコレクタは、第3及び第4の抵抗器R3, R4の接続点に接続されている。また、第7及び第8のトランジスタQ7及びQ8は、第3のカレントミラー回路を構成し、第7のトランジスタQ7のコレクタである出力ノードN3に、第7のトランジスタQ7と第8のトランジスタQ8とに夫々供給される電流の差に応じた電圧(誤差信号)を発生させる。

【0047】

第9のトランジスタQ9は、n p n形バイポーラトランジスタから成る。第9のトランジスタQ9のエミッタは接地端子に、コレクタは第10のトランジスタQ10のベースに、ベースは第7のトランジスタQ7のコレクタ(第3のトランジスタQ3のコレクタ)N3に、夫々接続されている。第9のトランジスタQ9は、誤差信号に応じて第10のトランジスタQ10のベースに流れる電流を制御する制御トランジスタとして動作する。

【0048】

第10のトランジスタQ10は、p n p形バイポーラトランジスタから成る。第10のトランジスタQ10のエミッタは電源端子V<sub>DD</sub>に接続され、コレクタは出力端子V<sub>OUT</sub>に接続されている。第10のトランジスタQ10は、そのベース電流に応じて、電源端子V<sub>DD</sub>に与えられる電源電圧をレギュレートし、出力電圧として出力端子V<sub>OUT</sub>へ供給する。

【0049】

第1及び第2の抵抗器R1及びR2は、互いに直列接続され、出力端子V<sub>OUT</sub>と接地端子との間に接続される。また、これら抵抗器R1及びR2の接続点(中間ノード)N1が、前述の通り第2のトランジスタQ2のベースに接続される。第1及び第2の抵抗器R1及びR2は、出力端子V<sub>OUT</sub>に供給される出力電圧を分圧し、分圧電圧を第2のトランジスタQ1のベースに供給する分圧回路として働く。

【0050】

第1の位相補正用コンデンサC1は、出力端子V<sub>OUT</sub>と分圧回路の中間ノードN1との間に接続されている。

【0051】

位相補正回路部40の第2の位相補正用コンデンサC2の一方の端子は、出力端子V<sub>OUT</sub>に接続され、他方の端子は、第7のトランジスタQ7のベースに夫々接続されている。すなわち、第7のトランジスタQ7のベースがエラーアンプの所定のノードN2である。第2の位相補正用コンデンサC2は、出力電圧に応じて第7のトランジスタQ7のベース電位を変化させ、エラーアンプから出力される誤差信号を補正する。

【0052】

以上の構成により、図4のレギュレータ回路は、従来と同様に、電源端子V<sub>DD</sub>に与えられた電源電圧をレギュレートし、レギュレートされた電源電圧を出力電圧として、出力端子V<sub>OUT</sub>に供給する。

【0053】

本実施の形態に係るレギュレータ回路は、第1の位相補正用コンデンサC1ばかりでなく、第2の位相補正用コンデンサC2を含む位相補正回路部40をも備えているので、従来のレギュレータ回路よりもより一層進み位相補償を行うことができる。

【0054】

図5に、図4のレギュレータ回路から第3及び第4の抵抗器R3, R4を削除したレギュレータ回路において、出力コンデンサC<sub>0</sub>のESRが0.01、出力電流が500m

10

20

30

40

50

A のときの、レギュレータ回路のオープンループ特性を示す。この図 5 から、第 3 及び第 4 の抵抗器 R 3, R 4 がないレギュレータ回路では、ゲインが 0 dB になる周波数での位相余裕（マージン）がないことが分かる。そのため、第 3 及び第 4 の抵抗器 R 3, R 4 がないレギュレータ回路は発振する。

#### 【0055】

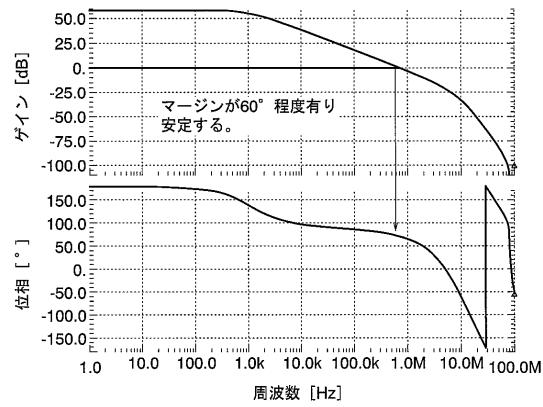

図 6 に、図 4 のレギュレータ回路において、出力コンデンサ C<sub>0</sub> の ESR が 0.01 、出力電流が 500 mA のときの、レギュレータ回路のオープンループ特性を示す。この図 6 から、図 4 のレギュレータ回路では、ゲインが 0 dB になる周波数での位相余裕（マージン）が 60° 程度あることが分かる。また、位相が 0° となる周波数以上の周波数帯では、ゲインが負となっているので、このレギュレータ回路は発振することはない。

10

#### 【0056】

以上説明したように、本実施の形態に係るレギュレート回路は、第 1 の位相補正用コンデンサ C<sub>1</sub> ばかりでなく、第 2 の位相補正用コンデンサ C<sub>2</sub> を含む位相補正回路部 40 をも備えているので、低容量、低 ESR の出力コンデンサ C<sub>0</sub> に対応することができる。

#### 【0057】

尚、位相補正回路部 40 を構成する第 3 及び第 4 の抵抗器 R<sub>3</sub>, R<sub>4</sub> は、第 3 のカレントミラー回路を構成する第 7 及び第 8 のトランジスタ Q<sub>7</sub> 及び Q<sub>8</sub> のベース - エミッタ間電位を同一にする必要があるので、同じ抵抗値を持っている。また、第 3 及び第 4 の抵抗器 R<sub>3</sub>, R<sub>4</sub> の抵抗値としては、200 ~ 60 k の範囲であることが望ましい。下限の抵抗値を 200 と設定したのは、第 3 及び第 4 の抵抗器 R<sub>3</sub>, R<sub>4</sub> を流れる電流が 1 μA 程度で、第 7 及び第 8 のトランジスタ Q<sub>7</sub> 及び Q<sub>8</sub> のエミッタ抵抗が 26 程度あるので、その影響を受けないようにするためである。また、上限の抵抗値を 60 k と設定したのは、それ以上高い抵抗値を製造することは製造プロセス上バラツキが大きくなり、同じ抵抗値を持つ抵抗器を製造することが困難になるからである。

20

#### 【0058】

一方、第 2 の位相補正用コンデンサ C<sub>2</sub> の容量値としては、0.5 pF ~ 20 pF の範囲にあることが好ましい。上記コンデンサ C<sub>2</sub> の容量値を 0.5 pF ~ 20 pF の範囲としたのは、上記の容量値を持つコンデンサを半導体上に製造するまでの問題より、適度な値としたものである。

30

#### 【0059】

また、第 3 及び第 4 の抵抗器 R<sub>3</sub>, R<sub>4</sub> の抵抗値と第 2 の位相補正用コンデンサ C<sub>2</sub> の容量値とで規定される時定数は、進み位相補償を施したい周波数によって決められる。

#### 【0060】

本発明者は、図 4 に示すレギュレータ回路において、第 7 のトランジスタ Q<sub>7</sub> のベース - コレクタ間にコンデンサを接続することにより、さらに進み位相補償の効果が上がることを確認している。そのコンデンサの容量値としては、5 pF ~ 50 pF の範囲が適当であった。

40

#### 【0061】

尚、本発明は、上述した実施の形態に限定されず、本発明の趣旨を逸脱しない範囲で種々の変更が可能なのはいうまでもない。例えば、上述した実施の形態では、バイポーラトランジスタで構成されたレギュレータ回路について説明しているが、本発明は、出力電流が 50 mA ~ 100 mA の範囲の小出力電流用の場合には、MOSFET で構成されたレギュレータ回路にも同様に適用可能である。各 MOSFET は、制御端子としてゲートを持ち、一対の主要電極端子としてドレインおよびソースを持つ。その場合には、第 1 の位相補正用コンデンサに加えて、少なくとも第 2 の位相補正用コンデンサを備えたもので構成することができる。

#### 【図面の簡単な説明】

#### 【0062】

【図 1】従来のレギュレータ回路の一例の回路図である。

【図 2】図 1 のレギュレータ回路から位相補正用のコンデンサを削除したレギュレータ回

50

路の、 $ESR = 0.01$  で出力電流が 500 mA の場合のオープンループ特性を示すグラフである。

【図 3】図 1 のレギュレータ回路の、 $ESR = 0.01$  で出力電流が 500 mA の場合のオープンループ特性を示すグラフである。

【図 4】本発明の一実施の形態に係るレギュレータ回路の回路図である。

【図 5】図 4 のレギュレータ回路から位相補正回路部の 2 つの抵抗器を削除したレギュレータ回路の、 $ESR = 0.01$  で出力電流が 500 mA の場合のオープンループ特性を示すグラフである。

【図 6】図 4 のレギュレータ回路の、 $ESR = 0.01$  で出力電流が 500 mA の場合のオープンループ特性を示すグラフである。

10

20

【符号の説明】

【0063】

|                  |                 |

|------------------|-----------------|

| 1 1              | 定電流回路           |

| 4 0              | 位相補正回路部         |

| Q 1 ~ Q 1 0      | トランジスタ          |

| R 1 ~ R 4        | 抵抗器             |

| C 1              | 第 1 の位相補正用コンデンサ |

| C 2              | 第 2 の位相補正用コンデンサ |

| C <sub>o</sub>   | 出力コンデンサ         |

| ESR              | 等価直列抵抗          |

| V <sub>DD</sub>  | 電源端子            |

| V <sub>OUT</sub> | 出力端子            |

| R <sub>L</sub>   | 負荷抵抗            |

【図 1】

【図 2】

【図3】

【 図 4 】

【図5】

【 义 6 】