(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-157971

(P2008-157971A)

(43) 公開日 平成20年7月10日(2008.7.10)

(51) Int.Cl.

G01R 31/3183 (2006.01)

G01R 13/34 (2006.01)

F 1

G01R 31/28

G01R 13/34

テーマコード(参考)

2G132

審査請求 有 請求項の数 1 O L (全 35 頁)

(21) 出願番号 特願2008-75855 (P2008-75855)

(22) 出願日 平成20年3月24日 (2008.3.24)

(62) 分割の表示 特願2006-56374 (P2006-56374)

の分割

原出願日 平成18年3月2日 (2006.3.2)

(31) 優先権主張番号 特願2005-59282 (P2005-59282)

(32) 優先日 平成17年3月3日 (2005.3.3)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 396023993

株式会社半導体理工学研究センター

神奈川県横浜市港北区新横浜3丁目17番

地2 友泉新横浜ビル6階

(74) 代理人 100101454

弁理士 山田 卓二

(74) 代理人 100081422

弁理士 田中 光雄

(74) 代理人 100125874

弁理士 川端 純市

(72) 発明者 永田 真

兵庫県神戸市灘区篠原南町5-4-14-

201

F ターム(参考) 2G132 AA11 AB02 AD10 AG08 AK07

AL00

(54) 【発明の名称】サンプリングタイミング信号発生器

## (57) 【要約】

【課題】動作雑音が従来技術に比較して小さくオンチップ信号波形測定装置に適したサンプリングタイミング信号発生器を提供する。

【解決手段】システムクロック信号に同期して所定の基準バイアス電圧を発生して出力するレプリカDLL回路21と、マスタクロック信号と基準バイアス電圧とに基づいて、基準バイアス電圧に対応する基準電流をn分の1に分流してなる電流を発生し、発生された電流に基づいて出力負荷容量を充電する時間をn倍することにより所定の遅延時間を生成し、マスタクロック信号を当該遅延時間だけ遅延させて複数のイネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生する遅延信号発生回路22とを備える。レプリカDLL回路21は、遅延時間がシステムクロック信号の周期に等しくなるように基準バイアス電圧を発生して、遅延信号発生回路22はイネーブルタイミング信号を発生する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

所定のシステムクロック信号及び所定のマスタクロック信号に基づいて、複数のイネーブルタイミング信号を発生するサンプリングタイミング信号発生器であって、

上記サンプリングタイミング信号発生器は、

上記システムクロック信号に基づいて、上記システムクロック信号に同期して所定の基準バイアス電圧を発生して出力するレプリカ D L L (Delayed Locked Loop) 回路と、

上記マスタクロック信号と上記基準バイアス電圧とにに基づいて、上記基準バイアス電圧に対応する基準電流を  $n$  分の 1 (ここで、 $n$  は 1 以上の数である。) に分流してなる電流を発生し、発生された電流に基づいて出力負荷容量を充電する時間を  $n$  倍することにより所定の遅延時間を生成し、上記マスタクロック信号を当該遅延時間だけ遅延させることにより、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生する遅延信号発生回路とを備え、

上記レプリカ D L L 回路は、上記遅延時間が上記システムクロック信号の周期に等しくなるように上記基準バイアス電圧を発生することにより、上記遅延信号発生回路は、上記イネーブルタイミング信号を発生することを特徴とするサンプリングタイミング信号発生器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、例えば、半導体大規模集積回路 (LSI) の内部信号や電源電圧、接地電圧、ウェル電圧、基板電圧などの固定電圧配線上の信号波形をオンチップでかつ多チャンネルで取得するための信号波形測定装置及び信号波形測定システム、並びに、信号波形測定システムのためのサンプリングタイミング信号発生器に関する。

**【背景技術】****【0002】**

半導体製造プロセスの微細化とともにチップに搭載する回路規模は増大し、近年はアナログとデジタル、あるいは高周波無線通信処理とベースバンドデータ処理といった異なる種類の信号処理機能を单一チップ上に統合するミックスストラグナル・システム LSI が一般的になっている。しかしながら、このような LSI はいくつもの機能回路がチップ内部で結合した構成をとるために、各機能回路の動作状態をチップ外部から観測できず、動作不良時の故障解析を困難にしていた。一方で、高速・低消費電力化 LSI では電源ノード / ウェル / 基板に発生する雑音の考慮がますます重要になり、チップ内の雑音をオンチップで測定評価する必要性が増している。また、これらの背景技術が特許文献 1～3 において開示されている。

**【0003】**

**【特許文献 1】**特開平 10 - 123215 号公報。

**【特許文献 2】**特開 2001 - 077160 号公報。

**【特許文献 3】**特開 2003 - 028898 号公報。

**【非特許文献 1】**Makoto Nagata et al., "Effects of Power-Supply Parasitic Components on Substrate Noise Generation in Large-Scale Digital Circuits", 2001 Symposium on VLSI Circuits Digest of Technical Papers, #15-1, Kyoto in Japan, pp.159-162, June 2001.

**【非特許文献 2】**野口宏一朗ほか，“オンチップ電源ノード測定技術”、第 7 回システム LSI ワークショップ予稿集、電子情報通信学会第 2 種研究会集積回路研究専門委員会主催、pp. 287 - 290, 2003 年 11 月。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

これらの要求には、LSI チップに内部信号を測定する機能を搭載することが有効であ

10

20

30

40

50

る。従来、ソースフォロア( S F )回路とラッチコンパレータ( L C )で構成した検出フロントエンド( F E )回路をアレイ化することにより、チップ内の雑音分布が測定できることが示されている( 非特許文献 1 参照 )。しかしながら、検出フロントエンド回路のみのオンチップ化では、測定に必要なピン数が多く、外部測定器の要求性能も高いため、高コストであるという問題点があった。その解決策として、検出フロントエンド回路に加えて、タイミング信号発生回路や参照電圧発生機構をオンチップ化する構成も提案されている( 非特許文献 2 参照 )。

#### 【 0 0 0 5 】

しかしながら、測定時間の短縮、チップ面積の削減、及び多チャンネル化における測定精度の確保が課題として残されており、大規模集積回路の内部信号や電源電圧、接地電圧、ウェル電圧、基板電圧の雑音など多様な波形をオンチップかつ多チャンネルに測定する手段としては不十分であった。

10

#### 【 0 0 0 6 】

本発明の第 1 の目的は、システム L S I を構成する機能回路の内部信号や各種電圧の雑音など、チップ内部の多観測点における波形を高速かつ高精度に取得することができる信号波形測定装置及び信号波形測定システムを提供することにある。

#### 【 0 0 0 7 】

また、本発明の第 2 の目的は、上記信号波形測定システムのためのサンプリングタイミング信号発生器であって、動作雑音が従来技術に比較して小さくオンチップ信号波形測定装置に適したサンプリングタイミング信号発生器を提供することにある。

20

#### 【 課題を解決するための手段 】

#### 【 0 0 0 8 】

第 1 の発明に係る信号波形測定装置は、I C チップ上に設けられ、上記 I C チップ上の複数の検出点の信号波形を測定するマルチチャンネルの信号波形測定装置であって、

所定のタイミング信号に基づいて、互いに異なる複数の参照電圧を逐次発生して出力する参照電圧発生器と、

上記複数の検出点に対応して設けられ、所定のイネーブルタイミング信号に基づいて上記各検出点の電圧を緩衝増幅した後、上記緩衝増幅した電圧を上記各参照電圧と比較してその比較結果を 2 値デジタル出力信号にデジタル化して出力する複数の信号検出フロントエンド回路と、

30

上記各信号検出フロントエンド回路からの 2 値デジタル出力信号を時分割多重化して多重化したデジタル出力信号を出力するマルチプレクサと、

上記マルチプレクサから出力される多重化した 2 値デジタル出力信号の所定値の数を計数することにより、上記各信号検出フロントエンド回路によって検出された各検出点の検出電圧についての判定出力確率を算出して出力するデータ処理ユニットとを備えたことを特徴とする。

#### 【 0 0 0 9 】

上記信号波形測定装置は、

所定のシステムクロック信号及び所定のマスタクロック信号に基づいて、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生するサンプリングタイミング信号発生器と、

40

上記イネーブルタイミング制御信号を多重分離することにより、上記各信号検出フロントエンド回路を順次動作させるためのイネーブルタイミング信号を発生して出力するデマルチプレクサとを備え、

上記サンプリングタイミング信号発生器は、

上記システムクロック信号に基づいて、上記システムクロック信号に同期して所定の基準バイアス電圧を発生して出力するレプリカ D L L ( Delayed Locked Loop ) 回路と、

上記マスタクロック信号と上記基準バイアス電圧とにに基づいて、上記基準バイアス電圧に対応する基準電流を n 分の 1 ( ここで、n は 1 以上の数である。 ) に分流してなる電流を発生し、発生された電流に基づいて出力負荷容量を充電することにより

50

所定の遅延時間を生成し、上記マスタクロック信号を当該遅延時間だけ遅延させることにより、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生する遅延信号発生回路とを備え、

上記レプリカ D L L 回路が、上記遅延時間が上記システムクロック信号の周期に等しくなるように上記基準バイアス電圧を発生することにより、上記遅延信号発生回路は、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生することを特徴とする。

#### 【 0 0 1 0 】

また、上記信号波形測定装置において、上記各信号検出フロントエンド回路は、

上記イネーブルタイミング信号に基づいて上記各検出点の電圧を緩衝増幅するソースフォロワ回路と、

10

上記緩衝増幅した電圧を上記各参照電圧と比較してその比較結果を 2 値デジタル出力信号にデジタル化して出力するコンパレータとを備えたことを特徴とする。

#### 【 0 0 1 1 】

とて代わって、上記各信号検出フロントエンド回路において、

上記イネーブルタイミング信号に基づいて上記各検出点の電圧を緩衝増幅するソースフォロワ回路と、

20

上記緩衝増幅した電圧を電流に変換する電圧 - 電流変換器と、

上記変換された電流をサンプルホールドするサンプルホールド回路と、

上記サンプルホールドされた電流を、上記各参照電圧から変換された参照電流と比較してその比較結果を 2 値デジタル出力信号にデジタル化して出力するコンパレータとを備えたことを特徴とする。

20

#### 【 0 0 1 2 】

さらに、上記信号波形測定装置において、上記各信号検出フロントエンド回路のソースフォロワ回路は、互いに異なる入力電圧範囲を有する複数のソースフォロワを含み、

上記各信号検出フロントエンド回路は、上記複数のソースフォロワを順次選択する選択回路を含み、

上記各信号検出フロントエンド回路のソースフォロワ回路は、上記各ソースフォロワの入力電圧範囲よりも広い入力電圧範囲を有することを特徴とする。

#### 【 0 0 1 3 】

またさらに、上記信号波形測定装置において、上記データ処理ユニットは、上記マルチプレクサから出力される多重化した 2 値デジタル出力信号の所定値の数を計数するカウンタ回路と、

30

上記カウンタ回路により計数された 2 値デジタル出力信号の所定値の数に基づいて、上記各信号検出フロントエンド回路によって検出された各検出点の検出電圧についての判定出力確率を算出して、当該判定出力確率のシリアルデータを出力するシフトレジスタ回路とを備えたことを特徴とする。

ここで、上記データ処理ユニットは、上記検出電圧と上記参照電圧とがともに一定であるとき、一定の判定出力確率のシリアルデータを出力することを特徴とする。

#### 【 0 0 1 4 】

第 2 の発明に係る信号波形測定システムは、

上記信号波形測定装置と、

上記 I C チップとは別の外部装置において設けられ、上記データ処理ユニットからの各検出点の検出電圧についての判定出力確率に基づいて、参照電圧に対する比較結果の判定出力確率の特性においてその特性の傾きが実質的に最大になるときの参照電圧が検出電圧であるという特徴を用いて、上記各検出点の検出電圧を決定する別のデータ処理ユニットとをさらに備えたことを特徴とする。

40

#### 【 0 0 1 5 】

上記信号波形測定システムにおいて、上記別のデータ処理ユニットは、上記データ処理ユニットからの判定出力確率のデータを順次記憶装置に記憶し、上記データ処理ユニット

50

からの判定出力確率のデータを、上記記憶装置に直近に記憶した判定出力確率の最新データと比較し、異なるときのみ上記データ処理ユニットからの判定出力確率のデータを上記記憶装置に記憶することにより、参照電圧に対する比較結果の判定出力確率の特性においてその特性の傾きが実質的に最大になる領域近傍の遷移領域のみの判定出力確率のデータのみを上記記憶装置に記憶することを特徴とする。

#### 【0016】

第3の発明に係るサンプリングタイミング信号発生器は、所定のシステムクロック信号及び所定のマスタクロック信号に基づいて、複数のイネーブルタイミング信号を発生するサンプリングタイミング信号発生器であって、

上記サンプリングタイミング信号発生器は、

10

上記システムクロック信号に基づいて、上記システムクロック信号に同期して所定の基準バイアス電圧を発生して出力するレプリカD L L (Delayed Locked Loop)回路と、

上記マスタクロック信号と上記基準バイアス電圧とに基づいて、上記基準バイアス電圧に対応する基準電流をn分の1(ここで、nは1以上の数である。)に分流してなる電流を発生し、発生された電流に基づいて出力負荷容量を充電する時間をn倍することにより所定の遅延時間を生成し、上記マスタクロック信号を当該遅延時間だけ遅延させることにより、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生する遅延信号発生回路とを備え、

上記レプリカD L L回路は、上記遅延時間が上記システムクロック信号の周期に等しくなるように上記基準バイアス電圧を発生することにより、上記遅延信号発生回路は、上記イネーブルタイミング信号を発生することを特徴とする。

20

#### 【発明の効果】

#### 【0017】

従って、本発明に係る信号波形測定装置及び信号波形測定システムによれば、各信号検出フロントエンド回路を検出点に対応して設け、上記各信号検出フロントエンド回路からの2値デジタル出力信号に基づいて、各検出点の検出電圧についての判定出力確率を算出して出力し、当該判定出力確率に基づいて検出電圧を決定するように構成した。それ故、例えばシステムLSIを構成する機能回路の内部信号や電源電圧、接地電圧、ウェル電圧、基板電圧の雑音など、チップ内部の多観測点における波形を高速かつ高精度に取得することができる。また、多チャンネルのオンチップ波形取得によるシステムLSIのテストコストを削減できるとともに、設計の信頼性を向上させることができる。

30

#### 【0018】

また、本発明に係るサンプリングタイミング信号発生器によれば、システムクロック信号に基づいて、上記システムクロック信号に同期して所定の基準バイアス電圧を発生して出力し、上記マスタクロック信号と上記基準バイアス電圧とに基づいて、上記基準バイアス電圧に対応する基準電流をn分の1(ここで、nは1以上の数である。)に分流してなる電流を発生し、発生された電流に基づいて出力負荷容量を充電する時間をn倍することにより所定の遅延時間を生成し、上記マスタクロック信号を当該遅延時間だけ遅延させることにより、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生し、上記遅延時間が上記システムクロック信号の周期に等しくなるように上記基準バイアス電圧を発生することにより、上記イネーブルタイミング信号を発生する。それ故、信号波形測定システムのためのサンプリングタイミング信号発生器であって、動作雑音が従来技術に比較して小さくオンチップ信号波形測定装置に適したサンプリングタイミング信号発生器を提供できる。

40

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、本発明に係る実施形態について図面を参照して説明する。なお、以下の各実施形態において、同様の構成要素については同一の符号を付している。

#### 【0020】

第1の実施形態。

50

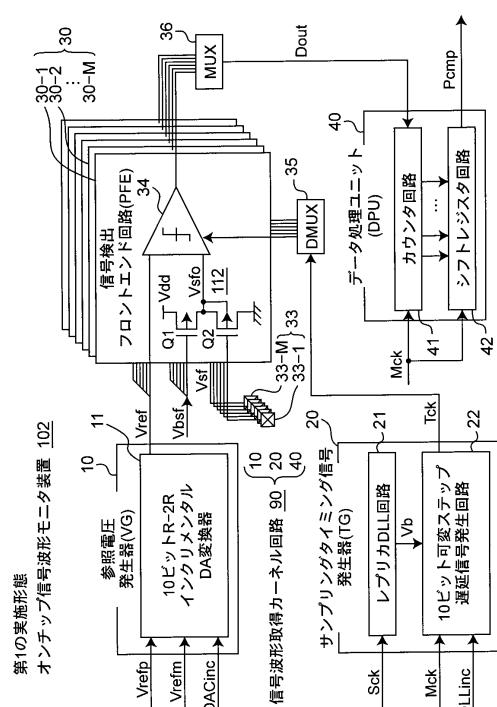

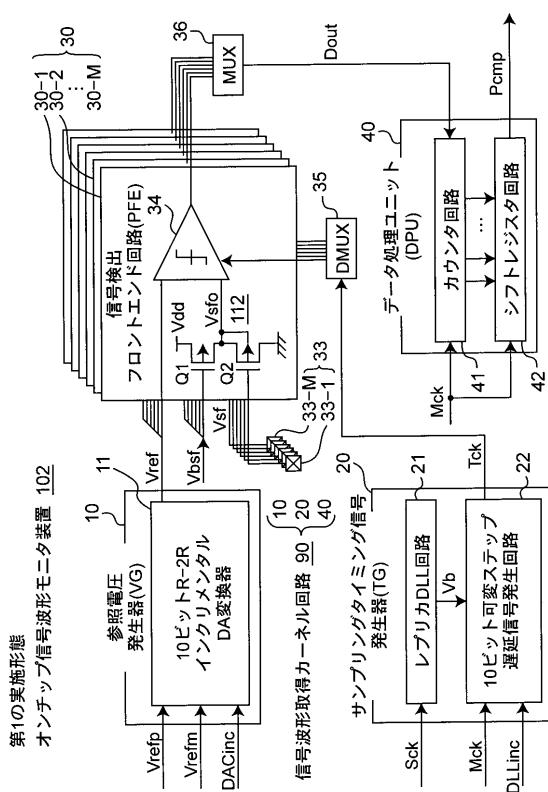

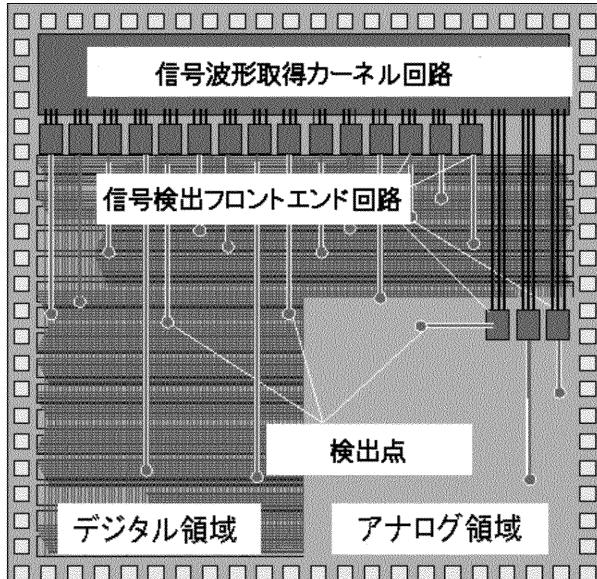

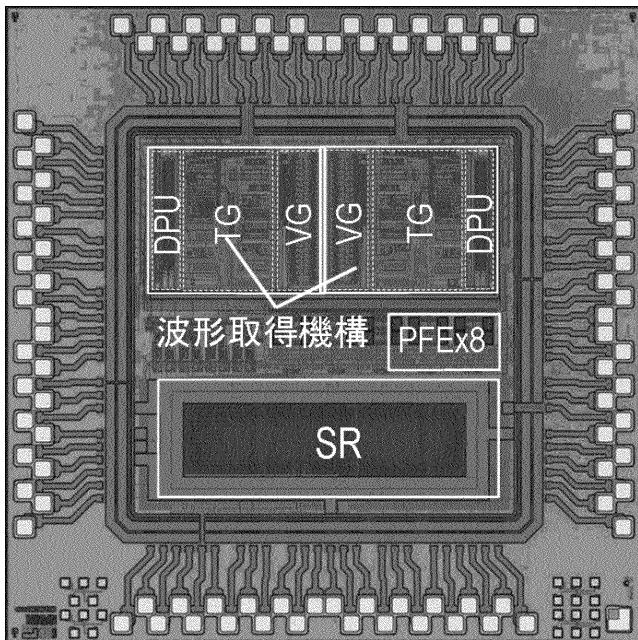

図1は、本発明の第1の実施形態に係るオンチップ信号波形モニタ装置102の構成を示すブロック図であり、図2は、図1のオンチップ信号波形モニタ装置を搭載したシステムLSIのフロアプランを示す平面図である。

#### 【0021】

オンチップ信号波形モニタ装置102は、図1に示すように、複数M個の信号検出フロントエンド30-1乃至30-Mを含む信号検出フロントエンド回路(PFE)(総称して符号30を付す。)と、参照電圧発生器(VG)10と、サンプリングタイミング信号発生器(TG)20と、データ処理ユニット(DPU)40とを備えて構成され、1個のLSIチップ(図2参照)上に搭載されて実装される。ここで、後者の3個の回路10, 20, 40をまとめて総称して、信号波形取得カーネル回路90という。

10

#### 【0022】

ここで、信号検出フロントエンド回路30は、LSIチップ上の複数M個の検出点33-1乃至33-M(総称して、符号33を付す。)における対象信号の検出機能に加えてその対象信号に対するサンプリング機能及び参照電圧との比較機能を備える。この結果、信号波形取得カーネル回路90に対する多重化を、サンプリングクロックやコンパレータ出力などのデジタル信号系と、参照電圧やバイアス電圧などのDC信号系に限定でき、検出信号そのものの多重化を回避することにより、多チャンネル化による測定精度の劣化を抑えられる(図1参照)。すなわち、サンプリングタイミング信号発生器20からの複数のイネーブルブルタイミング信号からなる多重化されたイネーブルタイミング制御信号Tckをデマルチプレクサ35により多重分離して、各信号検出フロントエンド回路30を順次選択的に動作させるための複数のイネーブルタイミング信号を、順次選択的に各信号検出フロントエンド回路30に出力することにより、各信号検出フロントエンド回路30を順次選択的に動作させる一方、動作された各信号検出フロントエンド回路30からのデジタル出力信号Doutをマルチプレクサ36により時分割多重化してデータ処理ユニット40に出力する。また、図2に示すように、複数M個の信号検出フロントエンド回路30を測定対象の検出点33近傍に配置し、信号波形取得カーネル回路90をチップ縁端部の空きエリアに配備することで、LSIチップの面積増を抑える一方で、同様に、信号検出フロントエンド回路30のデジタル化機能(A/D変換機能)により、長距離配線間クロストーク等による多チャンネル化の精度劣化要因を回避している。

20

#### 【0023】

信号波形取得カーネル回路90は、信号検出フロントエンド回路30のデジタル化動作に対して、参照電圧及びサンプリングタイミングを離散化ステップ単位で単調増加するよう制御する。一方、各ステップにおいて、信号検出フロントエンド回路30のコンパレータ34からの比較結果の2値デジタル出力信号の“1”的数を一定回数毎に計数し、その計数値のデータを、判定出力確率Pcmpを示す信号として連続的にシリアル出力する回路も搭載している。例えば、2<sup>10</sup>回の比較動作に対して、たかだか10クロックサイクル程度で、信号検出フロントエンド回路30の判定出力確率Pcmpの信号の読み出しが可能であるから、オンチップ信号波形モニタ装置102の外側に設けられた外部装置のオフチップメモリに格納するために十分なバッファ時間が確保できるため、オンチップのメモリを必要としない。さらに、デジタル化値の決定にはメモリ内のデータをテスタやパソコン用コンピュータで並行処理すればよく、参照電圧発生に対するフィードバック機能を必要としない。このような制御方式の結果、データ処理ユニット40の面積は極めて小さく、またたかだか数個程度のI/Oピンで外部装置と接続できる。さらに、オンチップ信号測定に要する時間も従来例の方法(全ての信号を外部測定器で発生)に比べて大幅に(例えば、1/20以下に)低減できる。

40

#### 【0024】

本発明の第1の実施形態に係るオンチップ信号波形モニタ装置102は、多観測点化に対して検出性能の劣化やチップ面積あるいはピン数の増大を回避できる特徴を有し、さらに波形取得を高速化できる。この結果、本発明の第1の実施形態によれば、ミックストシグナルLSIにおけるオンチップのアナログ機能評価や動作不良解析、アナログ信号の波

50

形劣化と周辺雑音の相関解析に基づく感度モデルの定量化及びオンチップパラメタ抽出、等の応用領域への展開が期待できる。さらに、これらの測定において外部のアナログ信号発生器が不要となるため、ミックストシグナル・システムLSIの評価がデジタルLSIテストで実施可能となり、測定コストを大きく削減できる。

#### 【0025】

本発明に係る第1の実施形態の構成の特徴点とその効果は、次の通りである。

(1) 各信号検出フロントエンド回路30をそれに対応する複数の測定対象の検出点33近傍に配置し、複数の検出フロントエンド回路30に対して、信号波形取得カーネル回路90を共有する構成とすることで、LSIチップの実効面積を削減することができる。

10

(2) 各信号検出フロントエンド回路30にデジタル化機構(A/D変換機能)を搭載する構成により、多チャンネル化による精度劣化を抑制することができる。

(3) アナログ信号発生のオンチップ化により、デジタルLSIテストでミックストシグナル・システムLSIの動作診断を実現することができる。

(4) 信号検出フロントエンド回路30のコンパレータ34からの判定出力確率Pcmppを一定クロック数毎に繰り返し出力するためのデータ処理ユニット40(カウンタ回路41とシフトレジスタ回路42とから構成される)の搭載により、信号取得時間を著しく低減することができる。

(5) 従来例に係る、ソースフォロワ回路及びラッチコンパレータからなる回路で実証されている高線形かつ広帯域なオンチップ雑音検出方法に、本発明の第1の実施形態に係るオンチップ信号波形モニタ装置102によるオンチップ波形取得機構を組み合わせることにより、測定時間を従来例に比べて1/20以下に低減することができる。この結果、アナログ機能モジュール内の信号波形と周辺基板雑音波形の相関測定や、ミックストシグナルLSIにおける複数事象を原因とした複雑かつダイナミックな動作不良解析など、これまででは測定時間がかかりすぎて不可能だった多観測点測定を実現することができる。

20

(6) 多チャンネル化したオンチップ信号検出回路である信号検出フロントエンド回路30を搭載することで設計改善の確度の向上を実現することができる。具体的には、アナログ信号の波形劣化と周辺雑音の相関解析に基づく感度モデルの定量化とパラメタ抽出を行う方法、システムLSIにおけるダイナミック動作不良解析の方法を示すことができる。

#### 【0026】

以下、本発明に係る第1の実施形態とその実施例について以下詳述する。

#### 【0027】

本発明に係る第1の実施形態の目的及びねらいは以下の通りである。すなわち、LSIの高機能化や高性能化が進み、今ではほとんどのLSIがミックストシグナルLSIとなっている。しかし、多くのミックストシグナルLSIでは、回路機能間の相互作用による性能劣化や動作不良が問題となっている。オンチップでの波形取得は、回路の動作診断、電源雑音解析、機能回路の性能検証、故障解析など多くの目的に有効な手段であり、本発明に係る研究では高波形精度、低成本のマルチチャンネルオンチップ信号モニタ方法を提案する。

#### 【0028】

次いで、本発明に係る第1の実施形態の実施例の概要について以下に説明する。

##### (1) 利用分野

本発明に係る第1の実施形態は、オンチップ波形取得、アナログ/ミックストシグナルLSIの動作検証、性能検証、ビルトイン・セルフ・テスト機能(BIST(Built-In Self-test))などに利用できる。

##### (2) 構成の特徴

本発明の第1の実施形態に係るオンチップ信号波形モニタ装置102は、信号検出フロントエンド回路30に加え、波形取得に必要な信号を生成する波形取得機構である信号波形取得カーネル回路90をオンチップして実装する。複数M個の信号検出フロントエンド回路30が1つの波形取得機構である信号波形取得カーネル回路90を共有する構成を有する。

10

20

30

40

40

50

(3) 性能

本発明の第1の実施形態に係るオンチップ信号波形モニタ装置102は、オンチップするための面積コストを最小限に抑えつつ、測定コストを削減し、波形取得時間を高速化する。検出精度を低下させることなくマルチチャンネル化できる。

(4) 試作

本発明の第1の実施形態の実施例では、8チャンネルオンチップ信号波形モニタ装置を1個のLSIチップ上に、 $0.18\mu\text{m CMOS}$ プロセスで試作した。

(5) 実測性能

本発明の第1の実施形態の実施例によれば、時間分解能40 psec、電圧分解能 $200\mu\text{V}$ での波形取得を実現した。また、検出回路のみオンチップした場合と比較し、精度を維持したまま95%の測定時間削減を達成した。10

【0029】

さらに、本発明の第1の実施形態による訴求点及び効果は以下の通りである。複数M個の信号検出フロントエンド回路30と、信号波形取得カーネル回路90とからなる、マルチチャンネルのオンチップ信号波形モニタ装置102(図1)を提案する。サンプリングタイミング信号発生器20と、参照電圧発生器10と、データ処理ユニット40からなる信号波形取得カーネル回路90は、LSIチップ縁端部の空きスペースに配備可能であり、面積コストを最小限に抑えられる。信号検出フロントエンド回路30のデジタル化機能により、配線間クロストークなどによる検出精度を低下させることなく、マルチチャンネル化できる。また、本実施形態によれば、外部アナログ信号発生器や複雑な測定制御を不要とし、測定コストを削減できる。試作した実施例に係るオンチップ信号波形モニタ装置102は、従来例の方法と同等の波形精度(図18及び図19)を達成しつつ、95%の測定時間短縮(図20)を実現した。本実施形態によりアピールしたい指標は、適用性、実現性、完成度、将来性、流通性などである。20

【0030】

以下、本発明の実施形態とその実施例についてさらに詳しく説明する。

【0031】

SOC (Systems On a chip) 市場の拡大につれてLSIの高機能化や高性能化が進み、今ではほとんどのLSIがミックストシグナルLSIとなっている。多くのミックストシグナルLSIは、回路自身が動作することにより機能回路が相互干渉し、デジタルアナログ変換の精度劣化、PLL (Phase-Locked Loops) のクロック分配や回路のクリティカルパスにおけるジッターやスキューの増加などの性能劣化が引き起こされ、それにともなう動作不良の問題に直面している。また、このようなLSIはいくつもの機能がチップ内部で結合した構成をとるため、各機能回路の動作状況をチップ外部から観測できない。一方、高速低消費電力化LSIでは、電源電圧、接地電圧、ウェル電圧及び基板電圧に発生する雑音の考慮がますます重要になり、LSIチップ内の雑音をオンチップで測定評価する必要が増している。30

【0032】

これらを解決する最も一般的な方法は、LSIチップに内部信号を測定する機能を搭載し、オンチップで信号測定を行うことである。オンチップ信号測定はBISTの動作テスト機能としてだけでなく、電源雑音解析、機能回路の性能検証、故障解析などに有効な手段であり、EDA (Electric Design Automation) ツールの導入や検証、デザインフロー改善には不可欠な技術である。本実施形態では、測定コストの低減と、高波形精度を実現するオンチップマルチチャンネル信号モニタ回路の構成方法を提案する。関連研究として、アナログ及びミックストシグナルLSIテストのためのオンチップアナログテスト信号生成と信号波形検出方法、高速デジタル信号のためのオンチップオシロスコープマクロが発表されている。この他にも、オンチップでの電源電圧及び接地電圧の雑音測定、デジタル信号測定、クロックジッター測定の報告例がある。40

【0033】

次いで、オンチップ信号波形モニタ装置102の構成について以下に詳述する。

## 【0034】

マルチチャンネルのオンチップ信号波形モニタ装置102の回路をLSIチップ上にオンチップで実装した、デバイス全体のシステム構成図を図1に示す。また、実際に製作した本実施形態の実施例に係る半導体LSIチップの平面図を図2に示す。信号検出のために、比較的小さい面積を有する信号検出フロントエンド(Probing Front-End)回路30を、機能回路ブロック近傍であって対象信号を測定する検出点33近傍に複数個配置し、検出点33で被検出信号をプローブし、検出信号を各信号検出フロントエンド回路30から出力させる。波形検出のために必要な信号を生成する信号波形取得カーネル(Waveform Acquisition Kernel)回路90はLSIチップ内に1つだけ配置され、すべての信号検出フロントエンド回路30が1つの信号波形取得カーネル回路90を共有している。

10

## 【0035】

図1のオンチップ信号波形モニタ装置102は、

(a) 参照電圧発生器(Reference Voltage Generator: VG)10と、サンプリングタイミング信号発生器(Sampling Timing Generator: TG)20と、データ処理ユニット(Data Processing Unit: DPU)40とからなる信号波形取得カーネル回路90と、

(b) 複数M個の信号検出フロントエンド(Probing Front-End: PFE)回路30とを備えて構成される。

## 【0036】

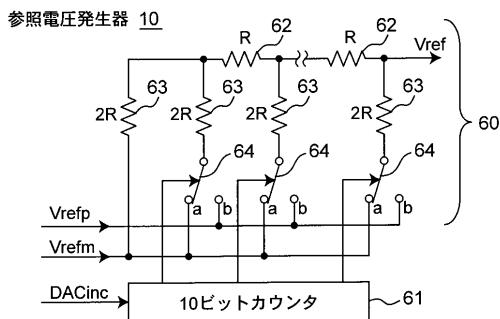

ここで、参照電圧発生器10は10ビットR2-Rラダー型インクリメンタルDA変換器11を備えて構成され、DA変換器11は入力される3つの信号(参照プラス電圧Vrefpと、参照マイナス電圧Vrefmと、DA変換器用インクリメント信号DACinc(参照電圧インクリメント信号である。)とを含む)に基づいて、参照電圧Vrefを発生して各信号検出フロントエンド回路30に出力する。また、サンプリングタイミング信号発生器20は、(a)システムクロック信号Sckに基づいてバイアス電圧Vbを発生して遅延信号発生回路22に出力するするレプリカDLL(Delayed Locked Loop)回路21(この回路21は、実際により近い環境で正確なバイアス電圧を発生するために提供される、DLLと同様の構成を有するレプリカ回路である。)と、(b)マスタクロック信号Mckと、DLL用インクリメント信号DLLinc(タイミングインクリメント信号である。)とにに基づいて、イネーブルタイミング制御信号Tckを発生してデマルチプレクサ35を介して各信号検出フロントエンド回路30に出力する10ビット可変ステップ遅延信号発生回路22とを備えて構成される。ここで、マスタクロック信号Mckは、システムクロック信号Sckを例えば1/4分周して生成される。

20

30

## 【0037】

デマルチプレクサ35は、遅延信号発生回路22からの複数のイネーブルタイミング信号からなる多重化されたイネーブルタイミング制御信号Tckを多重分離して各イネーブルタイミング信号をそれぞれ各信号検出フロントエンド回路30に出力することにより、各信号検出フロントエンド回路30を時分割的に選択して動作させる。そして、各信号検出フロントエンド回路30からのデジタル出力信号はマルチプレクサ36により多重化された後、多重化デジタル出力信号Doutがデータ処理ユニット40のカウンタ回路41に出力される。

40

## 【0038】

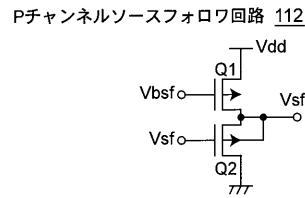

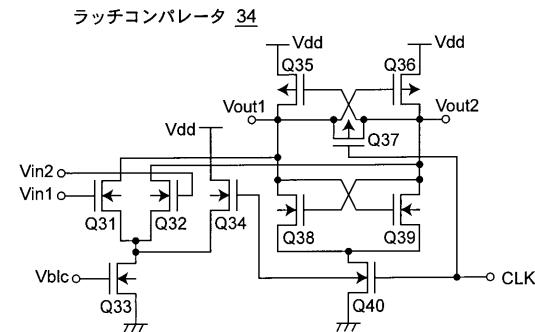

各信号検出フロントエンド回路30は、バイアス電圧Vbsfで動作する2個のPチャンネルMOS電界効果トランジスタ(以下、MOS電界効果トランジスタをMOSFETという。)Q1, Q2から構成され、各検出点33からの検出電圧Vssfを緩衝増幅して検出電圧Vsf0として出力するソースフォロワ回路112(図1では、一例として、Pチャンネルソースフォロワ回路112を図示している。当該回路について詳細後述する。)と、検出された電圧Vssfを参照電圧発生器10からの参照電圧Vrefと、サンプリングクロックのイネーブルタイミング制御信号Tck内のイネーブルタイミング信号のタイミングで比較し、比較結果のデジタル出力信号をマルチプレクサ36を介して、多重化デジタル出力信号としてデータ処理ユニット40に出力するラッチコンパレータ34とを

50

備えて構成される。データ処理ユニット40は、10ビットカウンタ回路41と、10ビットシフトレジスタ回路42とを備えて構成される。ここで、カウンタ回路41は、各検出点33についての各参照電圧Vrefの比較動作毎に、多重化デジタル出力信号の“1”の数を計数することにより、判定出力確率Pcmpを算出し、シフトレジスタ回路42は、算出した判定出力確率Pcmpを10ビットのシリアルデジタルデータPcmpに変換して出力する。すなわち、図5を参照して詳細後述するように、多重化デジタル出力信号の“1”の数は各検出点33での各参照電圧Vref毎の判定出力確率Pcmpに対応する。なお、データ処理ユニット40は、検出電圧VsFと参照電圧Vrefとがともに一定であるとき、一定の判定出力確率のシリアルデータを出力することを特徴としている。

10

#### 【0039】

図3は従来例に係るマルチチャンネル逐次比較型AD変換装置の構成を示すブロック図である。当該マルチチャンネル逐次比較型AD変換装置は、各検出点33での検出電圧をサンプルホールドする複数M個のサンプルホールド回路38-1乃至38-M(総称して符号38を付す。)と、SAR(Successive Approximation Register)型コンパレータ51を含むAD変換器50と、サンプリングタイミング信号発生器20と、マルチプレクサ39と、デマルチプレクサ35とを備えて構成される一般的なAD変換装置である。ここで、各サンプルホールド回路38は、サンプリングタイミング信号発生器20からのイネーブルタイミング制御信号Tckからデマルチプレクサ35による多重分離されたイネーブルタイミング信号によりオンとなるスイッチSW11と、電圧電荷を蓄積するキャパシタ37とを備えて構成される。また、AD変換器50は、コンパレータ51と、逐次変換レジスタ(SAR)52と、参照電圧発生器53とを備えて構成される。以上のように構成された図3の従来例では、サンプルホールド回路38からA/D変換器50へのアナログ信号経路がマルチプレクサ39により多重化されているためマルチチャンネル化するほど波形精度が低下してしまう。

20

#### 【0040】

一方、図1の実施形態では、バイアス電圧VbsF及び参照電圧Vrefなどの直流信号経路を共通化し、イネーブルタイミング制御信号Tck及びデジタル出力信号Doutなどのデジタル信号経路のみの多重化を行うことで、アナログ信号経路の多重化を無くしている。また、同時にステートレジスタ(図1において図示せず。)を用いて排他的に1つの信号検出フロントエンド回路30だけを動作させる一方、他のすべての信号検出フロントエンド回路30を波形検出動作に影響しないようにカットオフするように制御することで、検出精度劣化要因を回避している。なお、遅延信号発生回路22からのイネーブルタイミング制御信号Tckは、上記ステートレジスタにより選択された信号検出フロントエンド回路30にのみデマルチプレクサ35を介して供給される。

30

#### 【0041】

すなわち、本実施形態に係るオンチップ信号波形モニタ装置102は、1つの信号波形取得カーネル回路90に対して複数の信号検出フロントエンド回路30を接続するように構成することを特徴としている。検出点33を増やしたい場合は、小さな面積の信号検出フロントエンド回路30のみを増やせば良く、信号波形取得カーネル回路90は、SOCレイアウト後の空きスペースに1つだけ配備すればよいので、オンチップコストを最小限に抑えることができる。

40

#### 【0042】

本実施形態に係るオンチップ信号波形モニタ装置102によれば、参照電圧発生器10においてインクリメンタルDA変換器11を用いることで、逐次比較型AD変換器の逐次変換レジスタ(SAR: Successive Approximation Register)52に相応する探索制御を不要にしている。また、本実施形態に係るオンチップ信号波形モニタ装置102の信号検出フロントエンド回路30は、サンプリング原理に基づき、ラッチコンパレータ34により検出電圧VsFと参照電圧Vrefを繰り返し比較し統計処理を行うことで、サンプリング容量を代用している。その詳細動作については以下に詳述する。

50

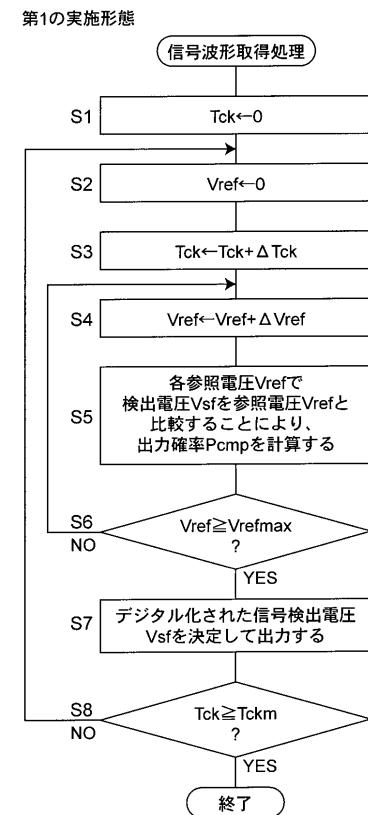

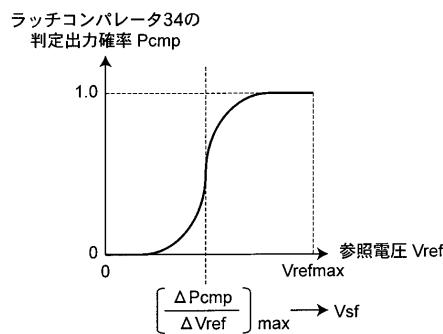

## 【0043】

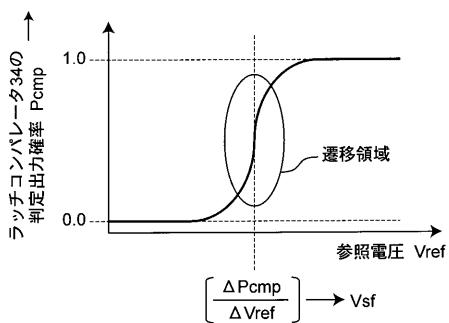

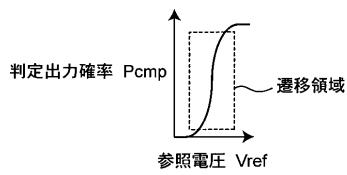

次いで、本実施形態に係る信号波形取得処理と、当該装置に係る測定コストについて以下に説明する。図4は、第1の実施形態に係るオンチップ信号波形モニタ装置102によって実行される信号波形取得処理を示すフローチャートであり、図5は図4の信号波形取得処理における参照電圧 $V_{ref}$ に対する判定出力確率 $P_{cmp}$ を示すグラフである。図4から明らかなように、信号波形取得処理は、イネーブルタイミング制御信号 $T_{ck}$ を変化させるサンプリングタイミングループと、参照電圧 $V_{ref}$ を変化させる参照電圧ループの2重ループからなり、各ループ内でそれぞれ参照電圧発生器10とサンプリングタイミング信号発生器20とが繰り返しインクリメントされて動作される。また、図5から明らかなように、参照電圧 $V_{ref}$ を上昇させるにつれて、ラッチコンパレータ34の判定出力確率 $P_{cmp}$ (コンパレータ34が2値出力値1を出力する回数の確率)である。本実施形態では、2値出力値1を計数しているが、本発明はこれに限らず、もしラッチコンパレータ34の比較結果が逆であるときは、2値出力値0を計数してもよい。)は上昇するが、遷移領域のある点で傾きが最大になり、その点が検出電圧 $V_{sf}$ であると推定される。すなわち、図5から明らかなように、コンパレータ34からの2値デジタル出力信号の“1”的数は各検出点33での各参照電圧 $V_{ref}$ 毎の判定出力確率 $P_{cmp}$ に対応する。

10

## 【0044】

図4の信号波形取得処理では、ステップS1においてイネーブルタイミング制御信号 $T_{ck}$ を0にリセットした後、ステップS2において、参照電圧 $V_{ref}$ を0にリセットし、ステップS3においてイネーブルタイミング制御信号 $T_{ck}$ を所定の遅延時間 $T_{ck}$ だけ遅延させる。次いで、ステップS4において、参照電圧 $V_{ref}$ を所定の増分電圧 $V_{ref}$ だけ増大させた後、ステップS5において各参照電圧 $V_{ref}$ で検出電圧 $V_{sf}$ を参照電圧 $V_{ref}$ と比較することにより、ラッチコンパレータ34の判定出力確率 $P_{cmp}$ を計算し、ステップS6において $V_{ref} < V_{ref max}$ (ここで、 $V_{ref max}$ は、図5に示すように、参照電圧 $V_{ref}$ の最大値であり、実施形態においては、参照プラス電圧 $V_{ref p}$ に等しい。)であるか否かが判断される。ステップS6において、YESのときはステップS7に進む一方、NOのときはステップS4に戻る。ステップS7では、上記計算された判定出力確率 $P_{cmp}$ の特性に基づいて、デジタル化された信号検出電圧 $V_{sf}$ を決定して出力し、ステップS8に進む。ステップS8では、 $T_{ck} = T_{ckm}$ (ここで、 $T_{ckm}$ はタイミングクロック信号の最大時間である。)であるか否かが判断され、NOのときはステップS2に戻る一方、YESのときは当該信号波形取得処理を終了する。なお、ステップS5では、合計 $2^{10}$ 回の比較操作からラッチコンパレータ34の判定出力確率 $P_{cmp}$ を計算することになる。

20

30

## 【0045】

上述の図4の信号波形取得処理では、参照電圧 $V_{ref}$ を所定の増分電圧 $V_{ref}$ だけ増大させているが、本発明はこれに限らず、参照電圧 $V_{ref}$ の最大値から減少させて信号波形を取得させてもよい。

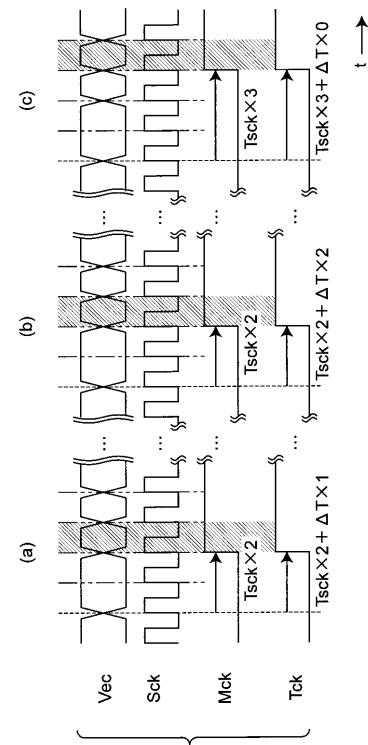

## 【0046】

図6(a)、図6(b)及び図6(c)は図1のサンプリングタイミング信号発生器20によって発生されるイネーブルタイミング制御信号 $T_{ck}$ の発生を示すタイミングチャートである。サンプリングタイミング信号発生器20は、図6(a)に示すように、マスタクロック信号 $M_{ck}$ の立ち下がり信号の遷移毎に、マスタクロック信号 $M_{ck}$ の信号遷移タイミング(タイミング信号 $T_{sc}$ により示される。)に任意の遅延時間 $T$ を付加したイネーブルタイミング制御信号 $T_{ck}$ を発生する。サンプリングタイミング信号発生器20での遅延時間 $T$ は、レプリカDLL回路21を用いてシステムクロック信号 $S_{ck}$ で規格化されている。各信号検出フロントエンド回路30は、サンプリングタイミング信号発生器20により発生されるイネーブルタイミング制御信号 $T_{ck}$ 内のイネーブルタイミング信号の各タイミングで、検出電圧 $V_{sf}$ (図1の回路では、ソースフォロワ回路112の出力電圧 $V_{sf o}$ )を、参照電圧発生器10により発生された参照電圧 $V_{ref}$

40

50

と繰り返し比較する。各参照電圧  $V_{ref}$  でのステップ S 5 の処理において、比較処理は  $2^{10}$  回繰り返され、その結果をデータ処理ユニット 40 により処理しラッチコンパレータ 34 の判定出力確率  $P_{cmp}$  を計算する。各参照電圧  $V_{ref}$  でのステップ S 5 の処理において判定出力確率  $P_{cmp}$  を計算する毎に、参照電圧  $V_{ref}$  は 1 ステップずつインクリメントされる。検出電圧  $V_{sf}$  は、ラッチコンパレータ 34 の遷移領域中の最も急勾配の点  $P_{cmp} / V_{ref}$  (図 5 参照) と定義され、参照電圧発生器 10 が 10 ビットステップでインクリメントされる毎に、検出電圧  $V_{sf}$  に相当する 10 ビットの参照電圧  $V_{ref}$  の値を求める。イネーブルタイミング制御信号  $T_{ck}$  内の各イネーブルタイミング信号での検出電圧  $V_{sf}$  が求まると、サンプリングタイミング信号発生器 20 は、イネーブルタイミング制御信号  $T_{ck}$  を図 6 (b) に示すように、タイミングステップをインクリメントし、再び参照電圧  $V_{ref}$  ループの処理が繰り返される。サンプリングタイミング信号発生器 20 からのイネーブルタイミング制御信号  $T_{ck}$  が 10 ビットステップでインクリメントされると、サンプリングタイミング信号発生器 20 はリセットされ、図 6 (c) に示すように、マスタクロック信号  $M_{ck}$  を 1 システムクロックだけシフトし、再び参照電圧  $V_{ref}$  ループの処理を実行する。この操作を任意の領域で繰り返し行うことで、検出電圧  $V_{sf}$  をオンチップでデジタル化し、検出電圧  $V_{sf}$  の連続時間データをデジタル値で取得する。

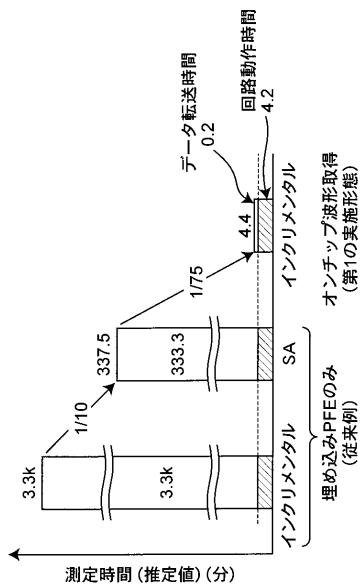

#### 【0047】

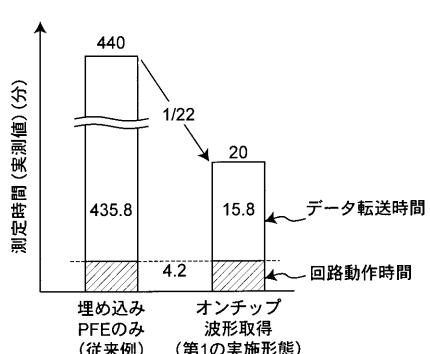

図 7 は、従来例の信号波形モニタ装置（埋め込み PFE のみ）と、第 1 の実施形態に係るオンチップ信号波形モニタ装置 102 における信号波形取得のための測定時間（推定値）を示すグラフである。非特許文献 1 及び 2 において開示された従来例の方法では、これまで、本発明者は、信号検出フロントエンド回路 30 のみをオンチップし、信号波形検出に必要な信号は外部測定器をパーソナルコンピュータにより制御することで、信号波形取得を実現してきた。しかしながら、提案する信号波形取得処理での測定全体のループの繰り返し回数は  $10^9$  のオーダーに達し、膨大な回数の外部測定器アクセスと、測定器制御が必要となり、波形検出には長い測定時間が必要であった。1024 ポイント測定した場合の信号波形検出に掛かる大まかな測定時間（推定値）を図 7 に示している。従来例の通り信号検出フロントエンド回路 30 のみをオンチップして実装した場合、参照電圧  $V_{ref}$  ループ処理に単にインクリメントするだけの単純なアルゴリズムを用いると、波形検出に膨大な測定時間が必要である。参照電圧ループに 2 分探索アルゴリズムを適用すれば（図 3 の逐次比較型（Successive Approximation: SA）A/D 変換装置に適用する。）、測定時間を  $1/10$  程度まで短縮できるが、それでも 5 時間以上必要である。一方、図 1 に示した提案する本実施形態に係るオンチップ信号波形モニタ装置 102 を LSI チップ上にオンチップして実装した場合、オンチップ信号波形モニタ装置 102 を 4 MHz で動作させれば、約 4 分での信号波形取得を達成できる。高時間効率の波形測定はテスト機構として重要な要素であり、本発明に至る目的の 1 つである。

#### 【0048】

提案するオンチップ信号波形モニタ装置 102 を LSI チップ上にオンチップで実装するためには、LSI チップ上でチップエリアが必要となるが、外部装置に高精度のアナログ信号を生成する測定器が不要となるため、ミックスドシグナル LSI の評価をデジタル LSI テスターのようなデジタル測定機器での実施が可能であり、測定コストを大きく削減できる。

#### 【0049】

さらに、オンチップ信号波形モニタ装置 102 の回路構成の詳細について以下に説明する。

#### 【0050】

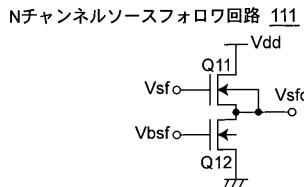

図 8 は図 1 の信号検出フロントエンド回路 30 において用いる N チャンネルソースフォロア回路 111 の構成を示す回路図であり、図 9 は図 1 の信号検出フロントエンド回路 30 において用いる P チャンネルソースフォロア回路 112 の構成を示す回路図であり、図 10 は図 1 の信号検出フロントエンド回路 30 において用いるラッチコンパレータ 34 の構

10

20

30

40

50

成を示す回路図である。図 8 及び図 9において、 $V_{b s f}$  はバイアス電圧であり、 $V_{s f}$  は検出点 33 での検出電圧である。信号検出フロントエンド回路 30 は、2 個の N チャンネル MOSFET Q11, Q12 からなる N チャンネルソースフォロワ回路 111、もししくは 2 個の P チャンネル MOSFET Q1, Q2 からなる P チャンネルソースフォロワ回路 112 と、ラッチコンパレータ 34 とを接続して構成される。これら 2 種類の信号検出フロントエンド回路 30（すなわち、P チャンネル信号検出フロントエンド回路と、N チャンネル信号検出フロントエンド回路とを含む。）は検出したい電圧信号の直流レベルにより使い分け、検出したい信号の直流レベルが、0 V から  $V_{dd}$ （電源電圧）-  $V_{thp}$ （P チャンネル MOSFET のしきい電圧）の場合は P チャンネル信号検出フロントエンド回路を用いる一方、 $V_{thn}$ （N チャンネル MOSFET のしきい電圧）から電源電圧  $V_{dd}$  までの場合は N チャンネル信号検出フロントエンド回路を用いる。アナログ回路における電圧  $V_{dd}/2$  程度の直流レベルを有するアナログ信号においては、P チャンネル信号検出フロントエンド回路と、N チャンネル信号検出フロントエンド回路のどちらのタイプでも検出可能である。信号検出フロントエンド回路 30 に、入出力インターフェース用の 3.3 V の電源電圧を用いれば、電源電圧 1.2 V の低電圧電源の回路に対しては、P チャンネル信号検出フロントエンド回路のみで入力電圧のフルレンジを検出できる。ラッチコンパレータ 34 は小面積にするため、10 個の MOSFET Q31 乃至 Q40 からなる図 10 に示す単純なトポロジを有する公知の差動型ラッチコンパレータを用いた。実施例に係る信号検出フロントエンド回路 30 全体での利得 0 dB で、周波数帯域は 1 GHz である。

10

20

30

40

50

#### 【0051】

オンチップ信号波形取得処理において、信号検出フロントエンド回路 30 は、測定対象回路であるテスト対象デバイス（DUT）への影響を最小限になるように設計する必要がある。そのため、信号検出フロントエンド回路 30 のソースフォロワ回路 111, 112 は検出電圧信号のバッファとしてだけでなく、オンチップ信号波形モニタ装置 102 と、測定対象電圧信号とを電気的に隔離し相互干渉を抑えている。以上より、提案する信号検出フロントエンド回路 30 はミックストシグナル LSIs 内における様々な属性のオンチップ信号波形を測定可能なオンチップ信号波形モニタ装置 102 を実現する。

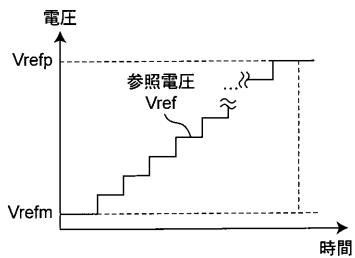

#### 【0052】

図 11 は図 1 の参照電圧発生器 10 の構成を示すブロック図であり、図 12 は図 11 の参照電圧発生器 10 によって発生される参照電圧  $V_{ref}$  を示すタイミングチャートである。図 11 において、参照電圧発生器 10 は、

(a) それぞれ抵抗値  $R$  を有する複数の抵抗 62 と、それぞれ抵抗値  $2R$  を有する複数の抵抗 63 と、複数のスイッチ 64 とを備え、外部装置からの参照プラス電圧  $V_{refp}$  と、参照マイナス電圧  $V_{refm}$  との間の微小な電圧ステップを生成する 10 ビット  $R_2 - R$  型ラダー回路 60 と、

(b) DA 変換器用インクリメント信号  $DAC_{inc}$  を計数してその計数値に基づいて上記複数のスイッチ 64 のオン・オフを制御する 10 ビットカウンタ 61 とを備えて構成される。

ここで、参照電圧発生器 10 は、図 12 に示すように、10 ビットインクリメンタル DA 変換器 11 として動作する。

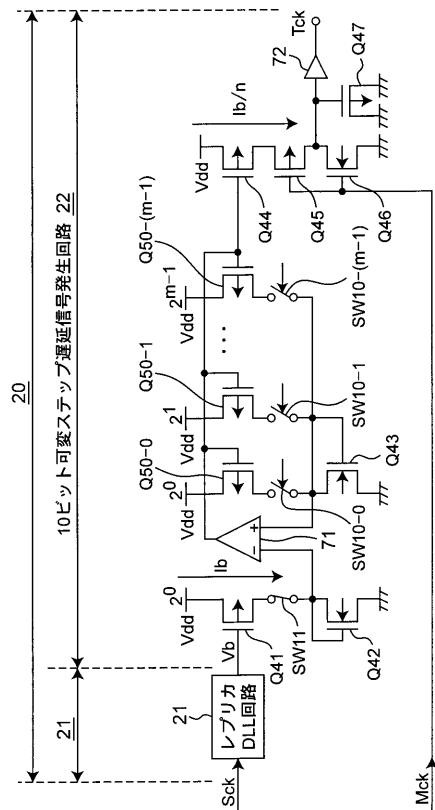

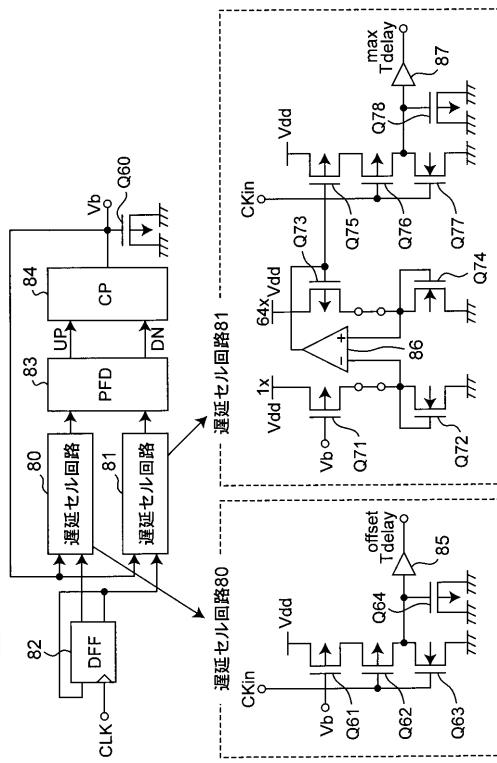

#### 【0053】

イネーブルタイミング制御信号  $T_{ck}$  の生成のために、VCDL（Voltage-Controlled Delay Line）を用いる従来の方法は、遅延ステップ（遅延時間）のビット数の増加により回路規模が指数的に増加するだけでなく、すべての遅延セルが常に入力信号のエッジに反応して動作するため、多くのノイズを発生してしまう。また、バーニアトポロジを用いたタイミングインタボレータにも同様の問題があり、オンチップ信号モニタのためのタイミング発生回路には適さない。そこで、図 13 に示すサンプリングタイミング信号発生器 20 を開発した。図 13 は、図 1 のレプリカ DLL 回路 21 及び 10 ビット可変ステップ遅延信号発生回路 22 を備えたサンプリングタイミング信号発生器 20 の構成を示す回路

図である。可変ステップ遅延信号発生回路22においては、基準バイアス電流Ibを1/n倍（ここで、本実施形態のデジタル処理のごとく実行するときは、好ましくは、nは1以上の自然数であるが、1以上の数（例えば、1.5や2.6など）であってもよい。）することで、出力負荷容量を充電する時間をn倍し、任意の遅延時間T<sub>delay</sub>を生成している。

#### 【0054】

[数1]

$$T_{\text{delay}}(n) = n \times T_{\text{delay}}(0) \quad (1)$$

#### 【0055】

ここで、T<sub>delay</sub>(n)は入力クロック信号であるマスタクロック信号Mckの立ち下がり遷移から、出力クロックであるイネーブルタイミング制御信号Tckの立ち上り遷移までの時間であり、T<sub>delay</sub>(0)は最小遅延時間である。基準バイアス電流Ibは最長遅延時間T<sub>delay</sub>(2<sup>m</sup>)がシステムクロック信号Sckのクロックサイクルと等しくなるように、レプリカDLL回路21からのバイアス電圧Vbにより調整される。

#### 【0056】

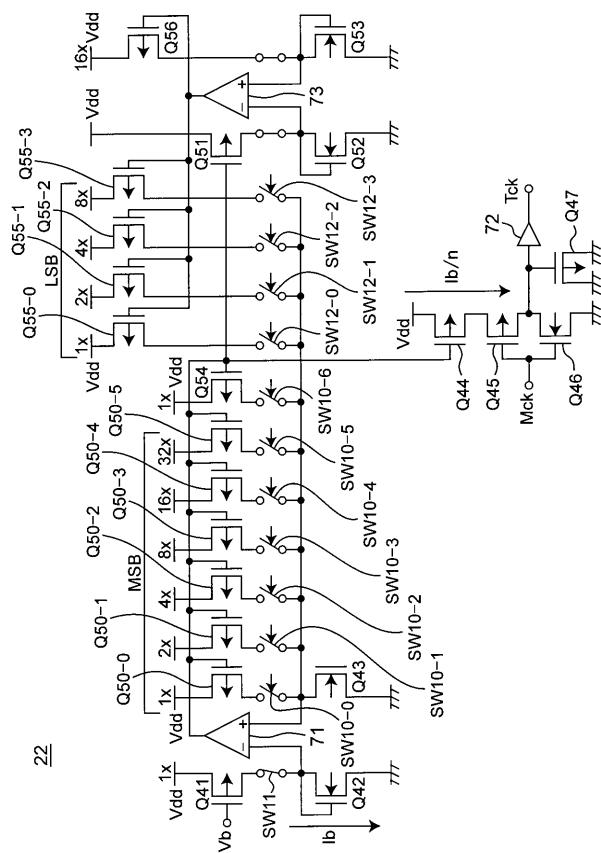

図14は図13の10ビット可変ステップ遅延信号発生回路22の構成の詳細を示す回路図であり、図15は図1のレプリカDLL回路21を示すブロック図及び回路図である。

#### 【0057】

図15のレプリカDLL回路21は、

- (a) クロック信号CLKに基づいて動作する遅延型フリップフロップ82と、

- (b) オフセット遅延時間T<sub>delay</sub><sup>offset</sup>に対応する信号を発生する遅延セル回路80と、

- (c) 最大遅延時間T<sub>delay</sub><sup>max</sup>に対応する信号を発生する遅延セル回路81と、

- (d) 遅延セル回路80, 81からの信号に基づいて位相及び周波数を検出して、位相制御のアップ信号とダウン信号を発生して出力する位相及び周波数検出器83と、

- (e) 位相及び周波数検出器83からの位相制御のアップ信号とダウン信号に基づいてバイアス電圧Vbを発生するチャージポンプ回路84とを備えて構成される。

#### 【0058】

図13及び図14の可変ステップ遅延信号発生回路22において、2個のMOSFET Q41, Q42からなるCMOS回路は、レプリカDLL回路21からのバイアス電圧Vbに基づいて所定のバイアス電流Ibを生成し、当該バイアス電流による電圧を差動増幅器71の反転入力端子に印加する。複数のPチャンネルMOSFET Q50-0乃至Q50-5及び複数のスイッチSW10-0乃至SW10-5から構成されるMSB6ビット用電流分流回路によりバイアス電流Ibを分流し、かつ複数のPチャンネルMOSFET Q55-0乃至Q55-3及び複数のスイッチSW12-0乃至SW12-3から構成されるLSB4ビット用電流分流回路によりバイアス電流Ibをさらに分流する。なお、これら電流分流回路の両側に2個の差動増幅器71, 73を設けており、2個の差動増幅器71, 73はそれぞれ2個の入力端子（非反転入力端子及び反転入力端子）間の電圧値が等くなるように負帰還のかかった回路としている。この回路22では、基準電流Ibに対して10ビット分解能の自然数n分の1の電流Ib/n（ここで、本実施形態のデジタル処理のごとく実行するときは、好ましくは、nは1以上の自然数であるが、1以上の数（例えば、1.5や2.6など）であってもよい。）を発生するにあたり、差動増幅器71によりMSB側6ビットに相当するバイアス電圧を発生し、さらに差動増幅器73によりLSB側4ビットに相当するバイアス電圧の調整を行う。遅延信号発生回路22は、上述のように分流されたバイアス電流Ib/nを生成し、これに基づいて、他の回路を用いてイネーブルタイミング制御信号Tckを発生して出力する。

#### 【0059】

すなわち、可変ステップ遅延信号発生回路22は電流モードの回路であって、MSB6

10

20

30

40

50

ビットの遅延ステップ（遅延時間に対応する）をさらに LSB 4 ビットで分解している。実際の最大遅延時間  $T_{\text{delay}}^{\text{deel}} (= 2^{10})$  は、図 14 に示す MSB 6 ビットの最大遅延時間  $T_{\text{delay}}^{\text{max}}$  から、オフセットの遅延時間 ( $T_{\text{delay}}^{\text{offset}}$ ) を引いた時間で定義され、この遅延時間が、レプリカ DLL 回路 21 により発生されたバイアス電圧 Vb によりシステムクロック信号 Sck のクロック周期に等しくなるように調整される。従って、レプリカ DLL 回路 21 からのバイアス電圧 Vb はシステムクロック信号 Sck で規格化され、サンプリングタイミング信号発生器 20 は、測定対象デバイス (DUT) のシステムクロック信号 Sck を基準とし、かつ同期したサンプリングタイミングを示すイネーブルタイミング信号を含むイネーブルタイミング制御信号 Tck を生成できる。

10

## 【0060】

以上のように構成された可変ステップ遅延信号発生回路 22 を備えたサンプリングタイミング信号発生器 20 は、マスタクロック信号 Mck から、サンプリングタイミングを示すイネーブルタイミング信号を含むイネーブルタイミング制御信号 Tck を生成するために必要な信号遷移はわずか 1 回で、レプリカ DLL 回路 21 においても、フェーズ調整毎に信号遷移は 2 回しか起こらないため、動作雑音が小さく、オンチップ信号波形モニタ装置 102 に適している。

## 【0061】

次いで、評価するための試作システムの実施例について以下に説明する。図 16 は、第 1 の実施形態に係るオンチップ信号波形モニタ装置 102 の実施例に係る試作チップの平面の写真である。本実施例に係る試作 LSI チップを  $0.18 \mu\text{m CMOS}$  プロセスにより試作した。試作 LSI チップ上に、図 16 に示すように、テスト対象デバイス (DUT) である 24 ビットシフトレジスタ (Shift Register: SR) と、信号波形取得カーネル回路 90 (図 16 の写真において、波形取得機構と示す。) と、8 個の信号検出フロントエンド回路 30 と、評価用の信号波形取得カーネル回路 90 とをオンチップで実装した。信号波形取得カーネル回路 90 は  $700 \mu\text{m} \times 600 \mu\text{m}$  のエリアを有し、1 個の信号検出フロントエンド回路 30 は  $60 \mu\text{m} \times 200 \mu\text{m}$  のエリアを有し、LSI チップのサイズは  $2.8 \text{ mm} \times 2.8 \text{ mm}$  である。信号波形取得カーネル回路 90 と信号検出フロントエンド回路 30 の電源電圧  $2.5 \text{ V}$  の入出力用 MOSFET を用いて設計し、ディープ N ウェルの半導体基板を用いることで、基板クロストークを低減している。なお、テスト対象デバイス (DUT) であるシフトレジスタは一般的な電源電圧  $1.8 \text{ V}$  の CMOS デバイスで設計した。

20

## 【0062】

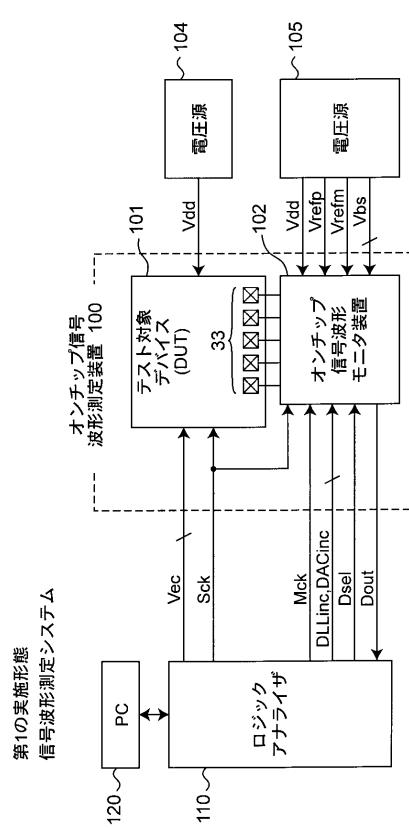

次いで、本実施例の測定結果について以下に説明する。図 17 は、図 1 のオンチップ信号波形モニタ装置 102 を備えた第 1 の実施形態の実施例に係る信号波形測定システムの構成を示すブロック図である。当該信号波形測定システムは、TPC / IP インターフェースにより PC120 制御が可能なロジックアナライザ 110 (Logic Analyzer: LA)、電源電圧供給用電圧源 104 と、バイアス電圧供給用電圧源 105 と、試作チップを搭載した DUT ボードであるオンチップ信号波形モニタ装置 100 とを備えて構成される。ここで、オンチップ信号波形モニタ装置 100 は、テスト対象デバイス (DUT) 101 と、オンチップ信号波形モニタ装置 102 とを備えて構成される。ロジックアナライザ 110 は、例えばシフトレジスタであるテスト対象デバイス (DUT) 101 に対して試験用ベクトルデータ  $V_{ec}$  を発生して出力するとともに、システムクロック信号 Sck を発生してテスト対象デバイス (DUT) 101 及びオンチップ信号波形モニタ装置 102 に入力される。また、ロジックアナライザ 110 はマスタクロック信号 Mck を発生してオンチップ信号波形モニタ装置 102 に出力するとともに、DLL 用インクリメント信号をオンチップ信号波形モニタ装置 102 内のサンプリングタイミング信号発生器 20 に出力し、DA 変換器用インクリメント信号をオンチップ信号波形モニタ装置 102 内の参照電圧発生器 10 に出力する。これに応答してオンチップ信号波形モニタ装置 102 から出力される出力信号についての処理を、ロジックアナライザ 110 が実行する。

30

40

50

## 【0063】

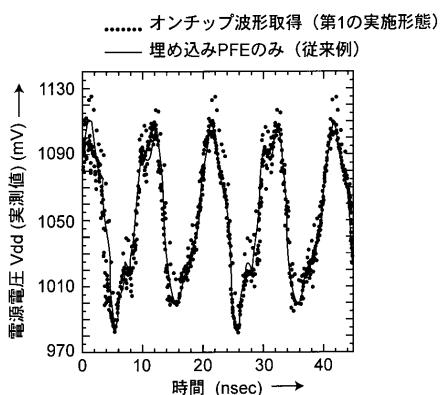

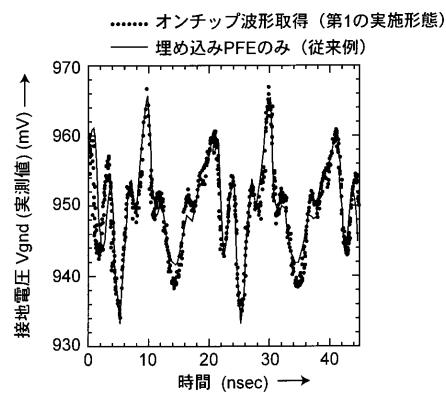

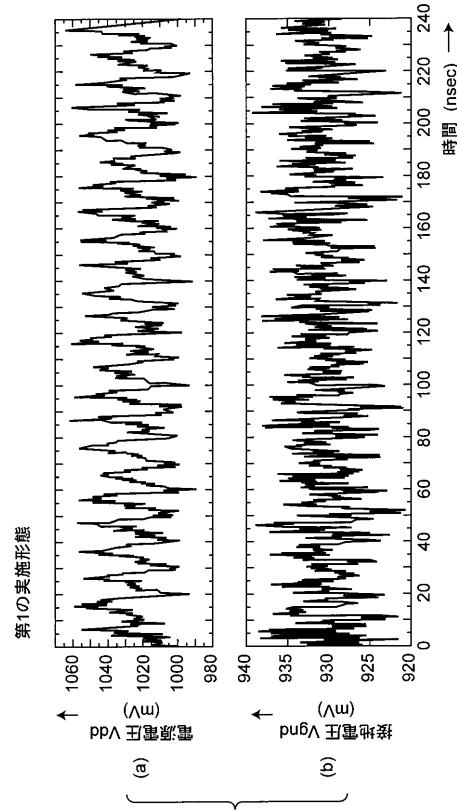

図18は、従来例の信号波形モニタ装置（埋め込みPFEのみ）と、第1の実施形態に係るオンチップ信号波形モニタ装置102とにおける電源電圧Vdd（実測値）を示すグラフであり、図19は、従来例の信号波形モニタ装置（埋め込みPFEのみ）と、第1の実施形態に係るオンチップ信号波形モニタ装置102とにおける接地電圧Vgnd（実測値）を示すグラフである。すなわち、図18及び図19は、100MHzのシステムクロック信号Sckを用いてテスト対象デバイス（DUT）101であるシフトレジスタを作動させたときの、電源電圧Vddと接地電圧Vgndの電位変動を示している。各図においてそれぞれ、2つ波形が図示され、一方の波形はオンチップ信号波形モニタ装置102により、測定に必要な信号をオンチップで生成して得た波形である。このとき、10ビット可変ステップ遅延信号発生回路22は、システムクロック信号Sckを4分周した25MHzクロック信号に同期するように制御用バイアス電圧Vbを発生するレプリカDLL回路21を動作させ、これにより、約40psの遅延時間（遅延ステップ）を生成する。10ビットR2-R型ラダー回路60（図11）は、参照プラス電圧Vrefpと参照マイナス電圧Vrefmに基づいて、ソースフォロワ回路の直流シフト出力電圧を中心する±100mVの参照電圧Vrefを、約200μVの電圧ステップを生成する。もう一方の波形は、同一の分解能のタイミング信号及び参照電圧信号を、外部測定器を用いて生成する従来例に係るオフチップ測定によるものである。どちらも同じ信号検出フロントエンド回路30を用いて測定対象信号を検出している。図18及び図19では、オンチップとオフチップのどちらの信号生成においても実測波形はほぼ一致し、提案するオンチップ信号波形モニタ装置102により高精度な信号波形取得処理が実現できることが示された。

10

20

25

30

## 【0064】

図20は、従来例の信号波形モニタ装置（埋め込みPFEのみ）と、第1の実施形態に係るオンチップ信号波形モニタ装置102とにおける信号波形取得のための測定時間（実測値）を示すグラフである。図20においては、1024ポイントのサンプルの信号波形を、本実施形態に係るオンチップ信号波形モニタ装置102を用いた場合の測定時間と、オフチップで外部測定器を2分探索のアルゴリズムで制御した場合（従来例）の測定時間を図示している。ロジックアナライザ110を用いた測定システムは、図7に示す測定時間に加え、ロジックアナライザ110からパーソナルコンピュータ120へのデータ転送に時間が必要となり測定時間が増加した。しかしながら、提案する本実施形態に係るオンチップ信号波形モニタ装置102は、従来例に比べて95%の測定時間短縮を実現できた。

30

## 【0065】

図21（a）は第1の実施形態に係るオンチップ信号波形モニタ装置102とにおける電源電圧（実測値）を示すグラフであり、図21（b）第1の実施形態に係るオンチップ信号波形モニタ装置102とにおける接地電圧（実測値）を示すグラフである。すなわち、図21（a）及び図21（b）は、電源電圧及び接地電圧の長時間の信号波形取得処理を実行した結果を示す。当該測定においては、システムクロック信号Sckの24周期の期間にわたって、マスタクロック信号Mckを、10ビットの遅延ステップ生成毎に40nsecの時間だけシフトし、全体で6144データポイントの信号波形検出を行った。このデータポイント数でのオンチップ信号波形取得処理は、測定に必要な信号をオンチップ生成した場合のみ、現実的な測定時間内で実行できる。このとき、テスト対象デバイス（DUT）101であるシフトレジスタには、“0011”の4ビットのデータパターンを繰り返し流しているため、実測された信号波形に4クロックサイクルの周期パターンを確認できる。

40

45

50

## 【0066】

以上説明したように、提案する本実施形態に係るマルチチャンネルのオンチップ信号波形モニタ装置102によれば、ミックストシグナルLSIにおける様々な属性のオンチップ信号モニタを実現する。0.18μmCMOSプロセスで設計試作した実施例に係る測

定システムでは、100MHzで動作する被測定デジタル回路に同期して動作し、40ps及び200μVの分解能のマルチチャンネルの信号波形実測を達成し、外部測定器を用いたオフチップ測定技術とほぼ同じ波形精度の実測波形を得られることを確認した。さらに、オフチップ測定と比べて、95%の測定時間削減を達成した。本発明の第1の実施形態に係る技術は、デジタル／アナログミックストシグナルLSIの診断に必要な構成要素に関する技術であり、波形精度、面積効率、測定コストの点で有効であり、デジタルテスト環境でミックストシグナルLSIの評価を実施できる。

#### 【0067】

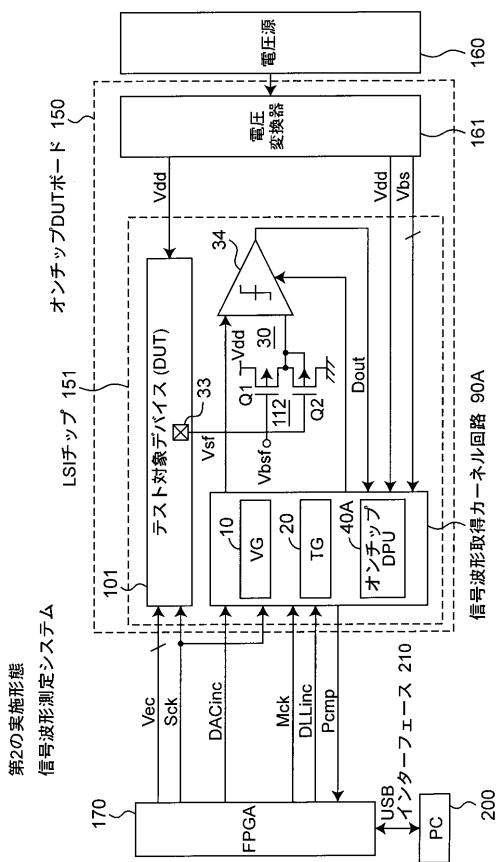

第2の実施形態。

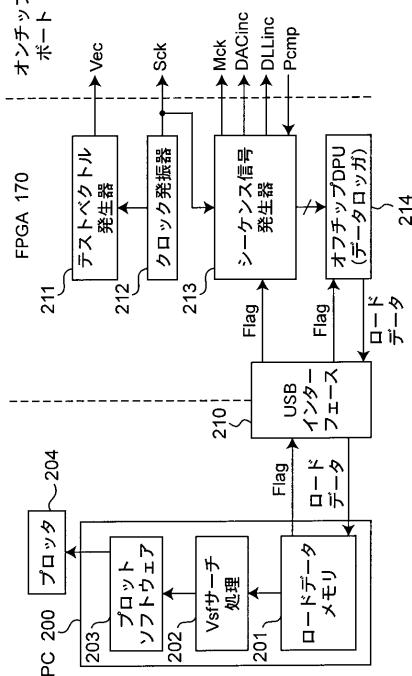

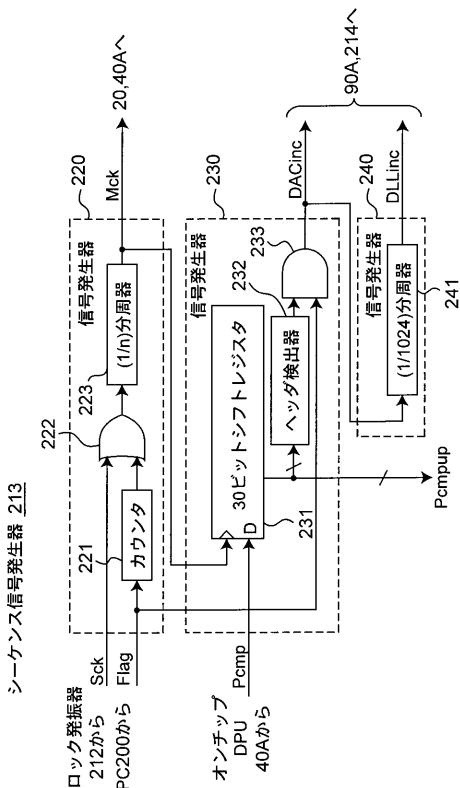

図22は第2の実施形態に係る信号波形測定システムにおいて用いる、参照電圧Vrefに対するラッチコンパレータ34の判定出力確率Pcmpを示すグラフであり、図23は本発明の第2の実施形態に係る信号波形測定システムの構成を示すブロック図である。また、図24は図23のパーソナルコンピュータ200及びFPGA170の詳細を示すブロック図である。

#### 【0068】

第2の実施形態に係る信号波形測定システムは、第1の実施形態に係る図1のデータ処理ユニット40の機能を、LSIチップ上のオンチップDPU40Aと、LSIチップとは別のFPGA170内のオフチップDPU214とに分担させたことを特徴としている。すなわち、第2の実施形態では、図1の信号検出フロントエンド回路30において、検出電圧Vs fを、ラッチコンパレータ34の判定出力確率Pcmp対参照電圧Vref特性(図5)の曲線から決定する回路の実装において、この検出電圧Vs f決定処理をコンパクトに実現するための、オンチップDPU40Aと、オフチップDPU214とに機能分担したことを特徴している。

#### 【0069】

図23において、オンチップDUTボード150は、LSIチップ151と、電圧源160からの電源電圧を所定の電源電圧Vdd及びバイアス電圧Vbsに変換してLSIチップ151に供給する電圧変換器161とを備えて構成される。LSIチップ151は、テスト対象デバイス(DUT)101と、複数の信号検出フロントエンド回路30と、信号波形取得カーネル回路90Aとを備えて構成され、信号波形取得カーネル回路90Aは、参照電圧発生器10と、サンプリングタイミング信号発生器20と、詳細後述するオンチップDPU40Aとを備えて構成される。図24において、FPGA170は、(a)システムクロック信号Sckを発生するクロック発振器212と、

(b)クロック発振器212からのシステムクロック信号Sckに基づいてテストベクトルデータVecを発生してオンチップDUTボード150に出力するテストベクトル発生器211と、

(c)クロック発振器212からのシステムクロック信号Sckと、パーソナルコンピュータ200からのフラグFlagと、判定出力確率Pcmpとに基づいて、種々の信号Mck, DACinc, DLLincとを発生し、処理後の判定出力確率PcmpをオフチップDPU(データロッガ)214に出力するシーケンス信号発生器213と、

(d)パーソナルコンピュータ200からのフラグFlagに基づいて、シーケンス信号発生器213からの判定出力確率Pcmpについて所定の処理を実行した後、パーソナルコンピュータ200に出力するオフチップDPU(データロッガ)214とを備えて構成される。

#### 【0070】

ここで、FPGA170とパーソナルコンピュータ200との間は、USBインターフェース210を用いて各種信号を送受信する。オフチップDPU214からの処理後の判定出力確率Pcmpであるロードデータは、USBインターフェース210を介してパーソナルコンピュータ200のロードデータメモリ201に出力して格納する。パーソナルコンピュータ200は、ロードメモリ201に格納されたロードデータに基づいて所定の検出電圧Vs fサーチ処理202を実行し、その結果をプロットソフトウェア203を用

10

20

30

40

50

いてプロッタ 204 を用いて出力する。

#### 【0071】

ところで、第 1 の実施形態では、図 4 の信号波形取得処理に従って、その参照電圧  $V_{ref}$  ループ処理において、図 5 の特性曲線に示すように、( $P_{cmp} / V_{ref}$ ) $max$  を満たす参照電圧  $V_{ref}$  を検出電圧  $V_{sf}$  の近似値(読み取り値)として得ている。ところで、図 22 は、ラッチコンパレータ 34 の入力電圧(検出電圧)  $V_{sf}$  を一定としたときの、参照電圧  $V_{ref}$  に対する(コンパレータ 34 が 1 を出力するときの)判定出力確率  $P_{cmp}$  の特性曲線を示している。この特性曲線は一般的なコンパレータ回路において普遍な特性を示し、本発明に係る実施形態では、次の 2 つの特徴を利用している。

(特徴 A) 検出電圧  $V_{sf}$  と参照電圧  $V_{ref}$  が一定のとき、判定出力確率  $P_{cmp}$  は変わらない。

(特徴 B) 検出電圧  $V_{sf}$  が一定で、参照電圧  $V_{ref}$  を最小電圧から最大電圧に向けて単一方向にインクリメントしたとき、判定出力確率  $P_{cmp}$  は 0 から「遷移領域」を経て 1 に移動するが、遷移領域以外では参照電圧  $V_{ref}$  の変化に対して判定出力確率  $P_{cmp}$  の値は変化しない。

#### 【0072】

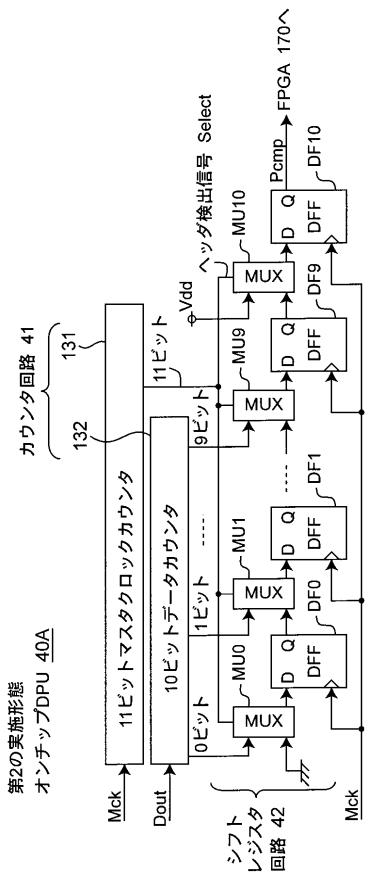

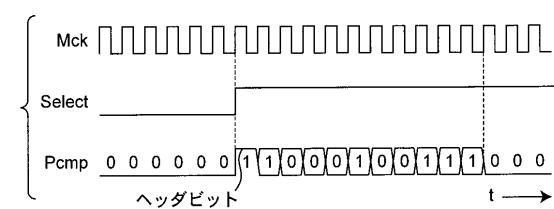

上記特徴 A より、検出電圧  $V_{sf}$  と参照電圧  $V_{ref}$  が一定のとき、ラッチコンパレータ 34 がクロック周期毎の比較動作を連続するとき、任意のクロック数区間における出力値の加算結果から判定出力確率  $P_{cmp}$  を算出してよいということが分かる。図 25 は図 23 のオンチップ DPU40A の構成を示すブロック図であり、図 26 は図 25 のオンチップ DPU40A の動作を示すタイミングチャートである。図 25 のオンチップ DPU40A は、この考え方に基づいて、次の動作ステップを連続して実行する。

(ステップ SS1) マスタクロック信号  $M_{ck}$  に同期した 1024 回のコンパレータ 34 の比較処理毎に、信号検出フロントエンド回路 30 からの“1”的数を計数することにより判定出力確率  $P_{cmp}$  を算出する。

(ステップ SS2) 図 26 に示すように、ヘッダビットとして 1 ビットの“1”をシリアルデータの先頭に付加し、合計 11 ビットシリアルデータとして判定出力確率  $P_{cmp}$  の信号を出力する。

(ステップ SS3) 次いで、図 26 に示すように、ステップ SS2 の後、続けて“0”を出力し続けるとともに、当該オンチップ DPU40A を初期化する。すなわち、検出電圧  $V_{sf}$  と参照電圧  $V_{ref}$  が一定であるとき、オンチップ DPU40A は一定の判定出力確率  $P_{cmp}$  を出力し続ける。

#### 【0073】

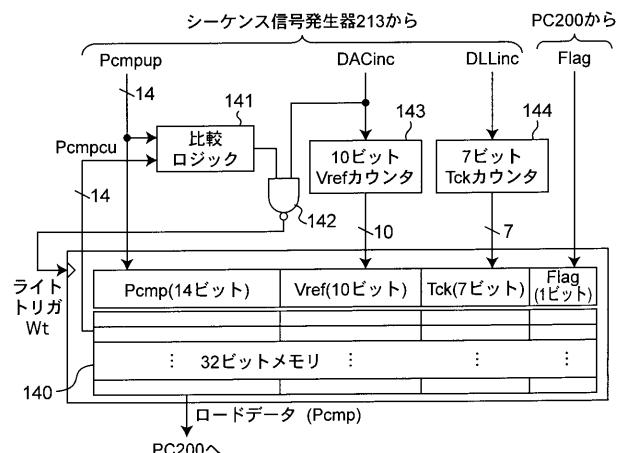

図 27において、オフチップ DPU214 は、 $P_{cmp}$  データメモリである 32 ビットメモリ 140 と、比較ロジック 141 と、 NAND ゲート 142 と、 10 ビット  $V_{rf}$  カウンタ 143 と、 7 ビット  $T_{ck}$  カウンタ 144 とを備えて構成される。上述の特徴 B より、オフチップ DPU214 は、参照電圧  $V_{ref}$  をインクリメント後の判定出力確率  $P_{cmp}$  を、その前の判定出力確率  $P_{cmp}$  と比べて変化があるときのみ  $P_{cmp}$  データメモリである 32 ビットメモリ 140 に格納することにすれば、図 22 の遷移領域のみの判定出力確率  $P_{cmp}$  のデータを保持できる。図 27 のオフチップ DPU214 はこの考え方に基づいて、オンチップ DPU40A からの判定出力確率  $P_{cmp}$  の最新データ  $P_{cmp\_up}$ (具体的には、オンチップ DPU40A からシーケンス信号発生器 213 の信号発生器 230 の 30 ビットシフトレジスタ 231(図 29 参照)を介して入力される)を、NAND ゲート 142 により、32 ビットメモリ 140 内の最新データ  $P_{cmp\_cu}$  と比較して、両者が異なるときのみ 32 ビットメモリ 140 に最新データ  $P_{cmp}$  として格納する。単一方向にインクリメントする参照電圧  $V_{ref}$  の全ステップについてこの処理を行うことで、図 28 のコンパレータ 34 の遷移領域内の判定出力確率  $P_{cm}$  のデータのみを 32 ビットメモリ 140 に蓄える。

#### 【0074】

図 25 のオンチップ DPU40A は、

10

20

30

40

40

50

(a) 11ビットマスタクロックカウンタ131と、10ビットデータカウンタ132とを含むカウンタ回路41と、

(b) 11個のマルチプレクサM U 0乃至M U 1 0と、11個の遅延型フリップフロップD F 0乃至D F 1 0とを含むシフトレジスタ回路42とを備えて構成される。

ここで、11ビットマスタクロックカウンタ131はマスタクロック信号M c kを計数し、図26に示すように、最初の“1”的立ち上がりであるヘッダビットを検出してヘッダ検出信号S e l e c tを発生して出力する。また、10ビットデータカウンタ132はデジタル出力信号D o u tを計数し、上記ヘッダビット後の0ビット目から9ビット目の10ビットの判定出力確率P c m pのシリアルデータをF P G A 1 7 0のシーケンス信号発生器213に出力する。すなわち、オンチップD P U 4 0 Aは、上記特徴Aからコンパレータ34の1024回の比較動作による判定出力確率P c m pを出力し続けるが、その出力データ列の先頭にはヘッダビット“1”が付加されており、また10ビットの出力データ列の後には連続した“0”が並ぶ。すなわち、オンチップD P U 4 0 Aには、判定出力確率P c m pのデータ列からヘッダビットを検出し、有効な10ビットデータを取得する機構を含んでいる。10

#### 【0075】

以上説明したように、上記特徴Aに基づく図25のオフチップD P U 4 0 Aは、図25に示すように、2個のカウンタ131, 132と、10個のマルチプレクサM U 0乃至M U 1 0と、10個の遅延型フリップフロップD F 0乃至D F 1 0程度で構成でき、特に、L S Iチップ内にデータメモリ140を搭載しなくてすむため、回路規模を小さくできる。20

#### 【0076】

図29は図24のシーケンス信号発生器213の構成を示すブロック図である。図29において、シーケンス信号発生器213は3個の信号発生器220, 230, 240を備えて構成される。信号発生器220は、カウンタ221と、オアゲート222と、(1/n)分周器223とを備えて構成され、システムクロック信号S c kと、フラグF l a gとに基づいてマスタクロック信号M c kを発生して、信号発生器230、サンプリングタイミング信号発生器20及びオンチップD P U 4 0 Aに出力する。また、信号発生器230は、30ビットシフトレジスタ231と、ヘッダ検出器232と、アンドゲート233とを備えて構成され、マスタクロック信号M c kと、フラグF l a gと、判定出力確率P c m pとに基づいて、判定出力確率P c m pの最新データP c m p u pをオフチップD P U 2 1 4に出力するとともに、参照電圧インクリメント信号D A C i n cを発生して信号波形取得カーネル回路90A及びオフチップD P U 2 1 4に出力する。さらに、信号発生器240は(1/1024)分周器241を備えて構成され、参照電圧インクリメント信号D A C i n cを1/1024分周することによりタイミングインクリメント信号D L L i n cを発生して信号波形取得カーネル回路90A及びオフチップD P U 2 1 4に出力する。30

#### 【0077】

上述の特徴Bを有するオフチップD P U 2 1 4(図27)は論理回路及びメモリで構成でき、波形測定の制御に必要な各種デジタル信号を発生するシーケンス信号発生器213等とあわせて市販のF P G A(再構成可能なゲートアレイ)170に実装できる。本実施形態に係る信号波形測定システムは、オンチップD U Tボード150と、F P G A 1 7 0と、電圧源160と、パーソナルコンピュータ200とで構成され、ロジックアナライザを用いて同等の機能を実現した図17に比べて、安価かつコンパクトである。40

#### 【0078】

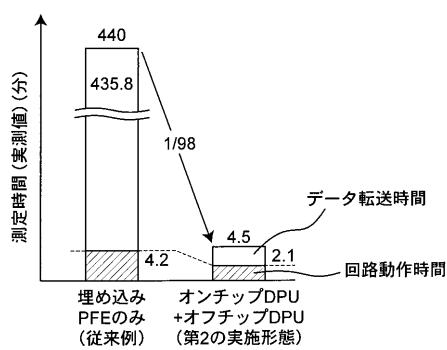

図30は、従来例の信号波形モニタ装置(埋め込みP F Eのみ)と、第2の実施形態に係る図27の信号波形測定システムとにおける信号波形取得のための測定時間(実測値)を示すグラフである。特に、図30は、第2の実施形態の構成による測定時間短縮効果を示しており、信号検出フロントエンド回路30のみを搭載する場合に比べ、測定時間をおよそ1/100以下に短縮できる。ロジックアナライザを用いた第1の実施形態の構成の50

結果(図20)に比べてもさらに1/4以下である。

#### 【0079】

第2の実施形態の測定時間をさらに短縮し、かつ測定確度を向上する方法として、上記特徴Bの特性より、オンチップDPU40Aによるコンパレータ34の比較出力の計数回数Ncmpを可変とする(すなわち、非線形とする)ことが考えられる。例えば、判定出力確率Pcmpが0.0もしくは1.0に近い領域では計数回数Ncmp=256とし、遷移領域では計数回数Ncmp=2048としてもよい。これにより、測定時間をさらに短縮しつつ高精度で測定できる。

#### 【0080】

またさらに、測定時間を短縮しつつ測定確度を向上する方法として、オンチップDPU40Aのカウンタ回路41と、シフトレジスタ回路42とをパイプライン動作するよう構成してもよい。10

#### 【0081】

第3の実施形態。

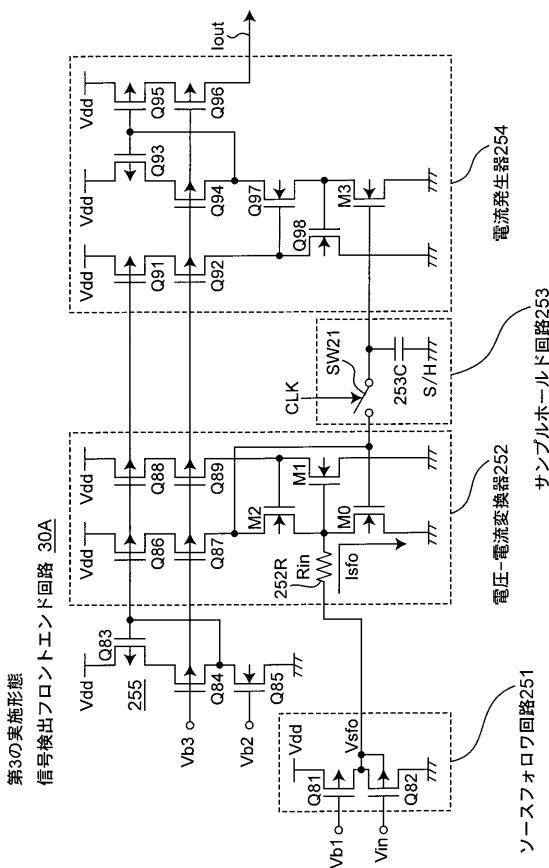

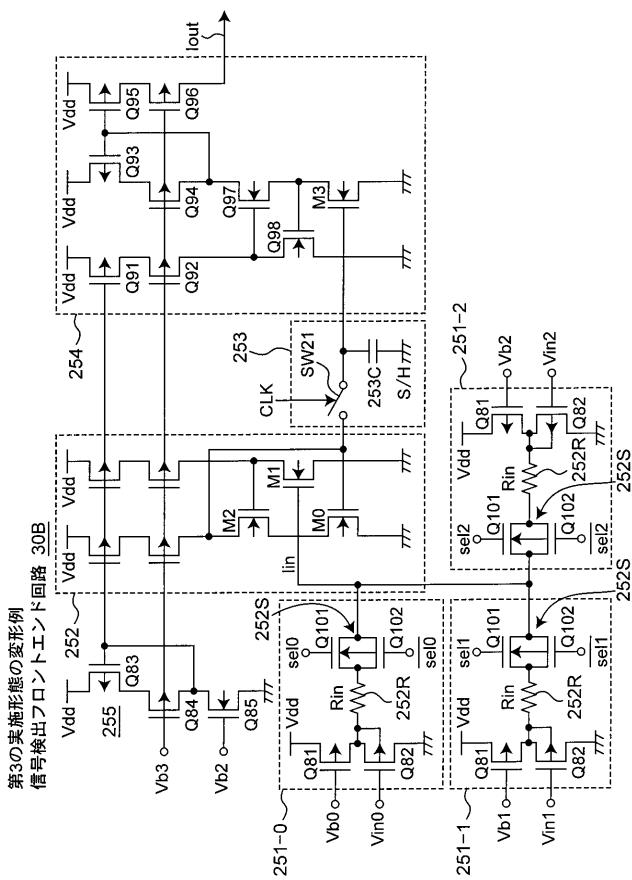

図31は、本発明の第3の実施形態に係る信号検出フロントエンド回路30Aの構成を示す回路図である。すなわち、図31は、電流モードのサンプルホールド回路253を用いた信号検出フロントエンド回路30Aの構成を示す。信号検出フロントエンド回路30Aは、被測定信号電圧Vinを検出するソースフォロワ回路251と、検出された検出電圧を電流に変換する電圧-電流変換器252と、変換された電流をスイッチSW21を介して保持キャパシタ253Cに保持して出力する電流モードのサンプルホールド回路253と、サンプルホールド回路253から出力される電流に基づいて当該電流に比例する対応した所定の大きさの出力電流Ioutを発生して出力する電流発生器254とを備えて構成される。ここで、電圧-電流変換器252と、サンプルホールド回路253と、電流発生器254とをまとめて、電流モードサンプルホールド回路という。図31において、ソースフォロワ回路251の出力電圧Vsf0は抵抗Rinにより $I_{sf0} = V_{sf0} / R_{in}$ の関係式に基づいて電流Isf0に変換される。サンプル動作時は電流Isf0がMOSFETM0に流れ、ホールド動作時は、MOSFETM0のゲート電圧を保持キャパシタ253C上に保持する。このゲート電圧はMOSFETM3で再び電流値に変換され、電流発生器254内のカレントミラー回路を経て出力電流Ioutとして出力される。ここで、MOSFETM0及びM3のチャンネル寸法比R(=ゲート幅W/ゲート長さL)が等しければ、出力電流Iout = Isf0である。20

#### 【0082】

なお、図31の信号検出フロントエンド回路30Aにおいて電流型コンパレータ(図33の電流型コンパレータ34Aと同様である。)を図示していないが、電圧型コンパレータ34と同様に、電流発生器254により発生された電流を、各参照電圧Vrefから変換された参照電流Irefと比較してその比較結果を2値デジタル出力信号にデジタル化して出力する。30

#### 【0083】

図32は、本発明の第3の実施形態の変形例に係る信号検出フロントエンド回路30Bの構成を示す回路図である。第3の実施形態の変形例は、第3の実施形態に比較して、図32に示すように、例えば3個のソースフォロワ回路251-0乃至251-2を、1個の電流モードサンプルホールド回路(回路252, 253, 254を含む。)に接続した多重入力構成を実現したことを特徴としている。40

#### 【0084】

図32において、各ソースフォロワ回路251-0乃至251-2において、2個のMOSFETQ81, Q82からなるソースフォロワの出力端子には、抵抗値Rinの抵抗252Rの一端が接続され、抵抗252Rの他端は、1対のMESFETQ101, Q102からなるセレクタスイッチ252S(3個のソースフォロワ回路251-0乃至251-2のうちの1つのセレクタスイッチ252Sがオンとなるように制御信号sel0とその反転制御信号により制御される。)に接続されている。さらに、セレクタスイッチ2

10

20

30

40

50

52Sは、電流モードサンプルホールド回路の電圧 - 電流変換器252の入力端子Inにまとめて接続されている。このとき、本変形例の回路30Bは、以下の特徴を有する。

(特徴a)電圧 - 電流変換器252の入力端子In、すなわちMOSFETM0のドレイン端子の電圧が、MOSFETM1, M2からなるフィードバック回路によりほぼ一定値に保たれるため、セレクタスイッチ252Sの後段側の電位が一定となる。

(特徴b)各ソースフォロワの出力側において、セレクタスイッチ252Sと、抵抗252Rとが直列接続されており、セレクタスイッチ252Sのオン時の寄生抵抗値はMOSFETQ101, Q102のゲートサイズを適切に選ぶことにより、抵抗252Rのサイズに比べて1桁以上小さく設計できる。

## 【0085】

10

これら2つの特徴a, bにより、本変形例に係る信号検出フロントエンド回路30Bでは、図32に示すように、入力回路を多重化しても、セレクタスイッチ252Sによる信号劣化は十分に小さく、無視できる。さらに、各ソースフォロワ回路251-0乃至251-2である入力回路は、2個のMOSFETQ81, Q82からなるソースフォロワと、抵抗252Rと、セレクタスイッチ252Sのみからなるため、図31の回路30Aそのものを複数個搭載するよりも小面積になる。従って、当該変形例に係る回路構成は、詳細後述する、許容入力電圧範囲の中心電圧の異なる複数個のソースフォロワ回路270-1乃至270-3(図34乃至図36)を用いて同一の被観測信号配線を評価する構成に適用することにより、その回路を小型に実現できる。

## 【0086】

20

なお、図32の信号検出フロントエンド回路30Bにおいて電流型コンパレータ(図33の電流型コンパレータ34Aと同様である。)を図示していないが、電圧型コンパレータ34と同様に、電流発生器254により発生された電流を、各参照電圧Vrefから変換された参照電流Irefと比較してその比較結果を2値デジタル出力信号にデジタル化して出力する。

## 【0087】

30

第4の実施形態。

図1の信号検出フロントエンド回路30が十分に小面積であれば、被観測信号に対して複数個の信号検出フロントエンド回路30を割り付けることが可能である。ここで、通常の信号検出フロントエンド回路30は線形な入出力特性を得ることのできるアナログ入力電圧範囲が被測定信号の振幅よりも小さいことが多い。そこで、上述の複数個の信号検出フロントエンド回路30において、各信号検出フロントエンド回路30の許容入力電圧範囲の合計が被測定信号振幅電圧を十分含むように、信号検出フロントエンド回路30の中心電圧を変更した設計を施すことが可能である。このように、許容入力電圧範囲の中心電圧の異なる複数の信号検出フロントエンド回路30を用いて、同一の被観測信号配線を評価することで、広い入力電圧範囲を得ることを特徴とする、オンチップ信号波形モニタ装置を構成できる。

## 【0088】

40

信号検出フロントエンド回路30の許容入力電圧範囲とその中心電圧を設定する方法として、以下の方法がある。

(1)信号検出フロントエンド回路30のアナログ動作電圧点をMOSFETのゲートサイズで調整する第1の方法。

(2)利用するMOSFETの製造技術に与えられるトランジスタ種類、すなわち、Nチャンネル型MOSFETと、Pチャンネル型MOSFETと、入出力用高耐圧NチャンネルMOSFETと、入出力用高耐圧PチャンネルMOSFETとの組み合わせにより調整する第2の方法。

(3)第1の方法と第2の方法とを併用する方法も有効である。

以下、具体例について説明する。

## 【0089】

50

図33は、本発明の第4の実施形態に係る信号検出フロントエンド回路30Cの構成を

示す回路図である。

### 【0090】

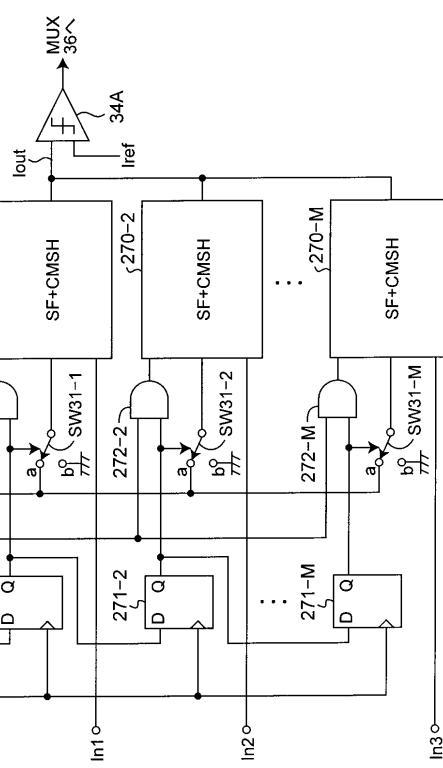

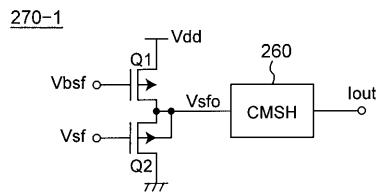

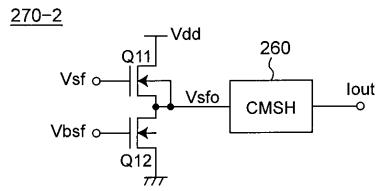

図33において、信号検出フロントエンド回路30Cは、入力電圧範囲が互いに異なる複数M個のソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mと、それらM個のソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mのいずれか1つを動作させるための選択回路と、電流型コンパレータ34Aとを備えて構成される。ここで、選択回路は、

(a) それぞれ検出器選択信号D<sub>se1</sub>を選択クロックCK<sub>se1</sub>に基づいて一時的に記憶して出力するM個の遅延型フリップフロップ271-1乃至271-Mと、

(b) 各遅延型フリップフロップ271-1乃至271-Mからの出力信号をクロック信号CLKがハイレベルのときのみ出力するM個のアンドゲート272-1乃至272-Mと、

(c) 各遅延型フリップフロップ271-1乃至271-Mからの出力信号がハイレベルのときのみ接点a側に切り換えられ、バイアス電圧V<sub>bs</sub>を各ソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mに供給するスイッチSW31-1乃至SW31-Mとを含む。

各ソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mからの出力信号は電流出力I<sub>out</sub>であり、当該電流出力I<sub>out</sub>は電流型コンパレータ34Aに出力される。電流型コンパレータ34Aは入力される検出電流I<sub>out</sub>を、各参照電圧V<sub>ref</sub>から変換された参照電流I<sub>ref</sub>と比較してその比較結果を2値デジタル出力信号にデジタル化してマルチプレクサ36に出力する。

### 【0091】

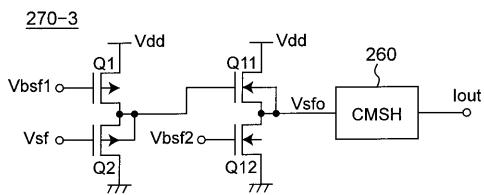

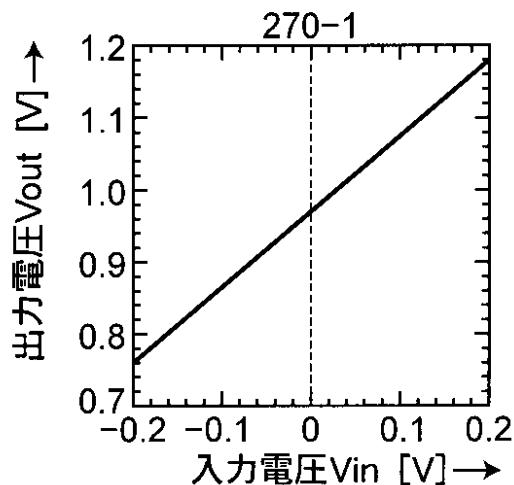

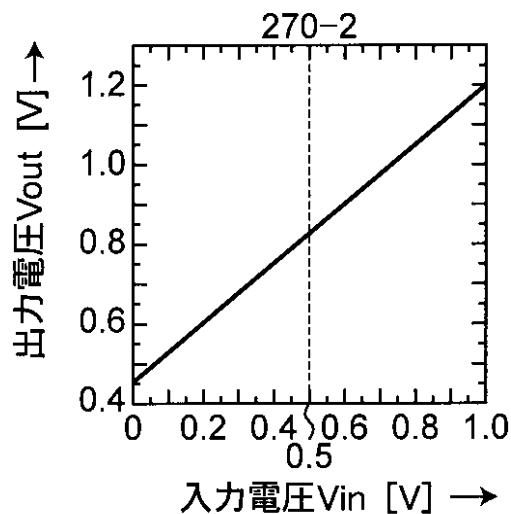

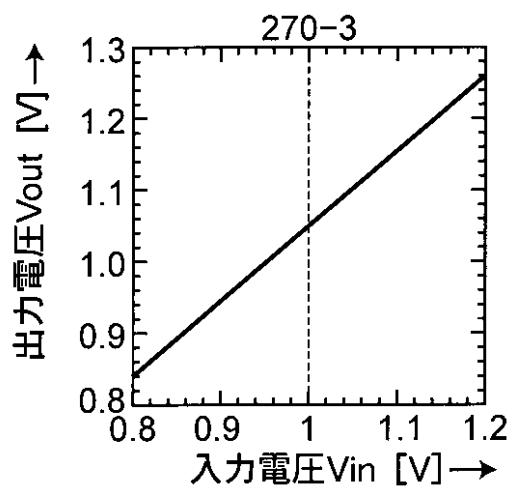

次いで、M=3のときのソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-3の実施例について図34乃至図39を参照して以下に説明する。ここで、図34乃至図36はそれぞれ図33のソースフォロワ及び電流モードサンプルホールド回路270-1, 270-2, 270-3の構成を示すブロック図である。さらに、図37乃至図39はそれぞれ、図34乃至図36のソースフォロワ及び電流モードサンプルホールド回路270-1, 270-2, 270-3の入出力電圧特性を示すグラフである。

### 【0092】

図34のソースフォロワ及び電流モードサンプルホールド回路270-1は、2個のPチャンネルMOSFETQ1, Q2からなるソースフォロワ回路と、電流モードサンプルホールド回路260とを備えて構成される。また、図35のソースフォロワ及び電流モードサンプルホールド回路270-2は、2個のNチャンネルMOSFETQ11, Q12からなるソースフォロワ回路と、電流モードサンプルホールド回路260とを備えて構成される。さらに、図36のソースフォロワ及び電流モードサンプルホールド回路270-3は、2個のPチャンネルMOSFETQ1, Q2からなるソースフォロワ回路及び2個のNチャンネルMOSFETQ11, Q12からなるソースフォロワ回路の従属接続回路と、電流モードサンプルホールド回路260とを備えて構成される。これらのソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-3は、入力段に設けたソースフォロワ回路の入力電圧範囲の中心を、図37乃至図39に示すように、例えば0.0V、0.5V、1.0Vとシフトして設計することが可能である。ここで、図37乃至図39は各ソースフォロワ回路の入出力電圧特性を示し、ソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-3の電流出力I<sub>out</sub>は50Ωの終端抵抗より電圧変換して読みとっている。

### 【0093】

上述したソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mは電流出力I<sub>out</sub>型であるため、図33のように複数M個のソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mをアレイ化して搭載するには、その電流出力を单一の電流読み出し端子に接続するだけでよい。ただし、同時に動作するソースフォロワ及び電流モードサンプルホールド回路270-1乃至270-Mは図33の

10

20

30

40

50

上記選択回路により 1 個のみとし、このために、複数 M 個のソースフォロワ及び電流モードサンプルホールド回路 270 - 1 乃至 270 - M から選択的に 1 個の回路をオンにする選択回路を設けている。

#### 【0094】

上述したソースフォロワ及び電流モードサンプルホールド回路 270 - 1 乃至 270 - M はトランジスタ数が少ないため小型に実現でき、1 つの回路当たり、例えば 0.25  $\mu$ m CMOS 技術で設計した場合に  $30 \mu\text{m} \times 120 \mu\text{m}$  程度のエリアを占有する。

#### 【0095】

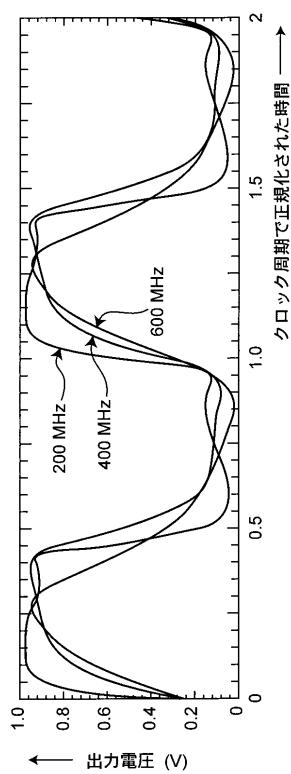

以上説明したように、これらの特徴から、入力電圧範囲の中心の異なるソースフォロワ及び電流モードサンプルホールド回路 270 - 1 乃至 270 - M を複数個用いて同一の被測定信号を観測する構成により、例えば -0.2V から 1.2V の合計入力電圧範囲を実現し、図 40 に示すように、CMOS デジタル回路内部のオンチップ信号のフルスイング波形観測を実現できる。すなわち、図 40 は本発明の第 4 の実施形態に係る信号検出フロントエンド回路 30C において観測したオンチップ信号波形を示す波形図であり、被測定信号は電源電圧 1V の CMOS デジタル回路が動作周波数 200MHz, 400MHz, 600MHz で動作しているときの内部のクロック信号であり、横軸はクロック周期で規格化している。また、このときの信号検出フロントエンド回路 30C 全体の面積は  $120 \mu\text{m} \times 100 \mu\text{m}$  と十分に小面積である。

10

#### 【産業上の利用可能性】

#### 【0096】

以上詳述したように、本発明に係る信号波形測定装置及び信号波形測定システムによれば、各信号検出フロントエンド回路を検出点に対応して設け、上記各信号検出フロントエンド回路からの 2 値デジタル出力信号に基づいて、各検出点の検出電圧についての判定出力確率を算出して出力し、当該判定出力確率に基づいて検出電圧を決定するように構成した。それ故、例えばシステム LSI を構成する機能回路の内部信号や電源電圧、接地電圧、ウェル電圧、基板電圧の雑音など、チップ内部の多観測点における波形を高速かつ高精度に取得することができる。また、多チャンネルのオンチップ波形取得によるシステム LSI のテストコストを削減できるとともに、設計の信頼性を向上させることができる。

20

#### 【0097】

また、本発明に係るサンプリングタイミング信号発生器によれば、システムクロック信号に基づいて、上記システムクロック信号に同期して所定の基準バイアス電圧を発生して出力し、上記マスタクロック信号と上記基準バイアス電圧とに基づいて、上記基準バイアス電圧に対応する基準電流を n 分の 1 (ここで、n は 1 以上の数である。) に分流してなる電流を発生し、発生された電流に基づいて出力負荷容量を充電する時間を n 倍することにより所定の遅延時間を生成し、上記マスタクロック信号を当該遅延時間だけ遅延させることにより、複数の上記イネーブルタイミング信号を多重化されたイネーブルタイミング制御信号を発生し、上記遅延時間が上記システムクロック信号の周期に等しくなるように上記基準バイアス電圧を発生することにより、上記イネーブルタイミング信号を発生する。それ故、信号波形測定システムのためのサンプリングタイミング信号発生器であって、動作雑音が従来技術に比較して小さくオンチップ信号波形測定装置に適したサンプリングタイミング信号発生器を提供できる。

30

#### 【図面の簡単な説明】

#### 【0098】

【図 1】本発明の第 1 の実施形態に係るオンチップ信号波形モニタ装置 102 の構成を示すプロック図である。

40

【図 2】図 1 のオンチップ信号波形モニタ装置を搭載したシステム LSI のフロアプランを示す平面図である。

【図 3】従来例に係るマルチチャンネル逐次比較型 A/D 変換装置の構成を示すプロック図である。

【図 4】第 1 の実施形態に係るオンチップ信号波形モニタ装置 102 によって実行される

50

信号波形取得処理を示すフローチャートである。

【図5】図4の信号波形取得処理における参照電圧V<sub>ref</sub>に対する判定出力確率P<sub>cm<sub>p</sub></sub>を示すグラフである。

【図6】(a)は図1のサンプリングタイミング信号発生器20によって発生されるイネーブルタイミング制御信号T<sub>ck</sub>の発生を示す第1の部分のタイミングチャートであり、(b)は図1のサンプリングタイミング信号発生器20によって発生されるイネーブルタイミング制御信号の発生を示す第2の部分のタイミングチャートであり、(c)は図1のサンプリングタイミング信号発生器20によって発生されるイネーブルタイミング制御信号T<sub>ck</sub>の発生を示す第3の部分のタイミングチャートである。

【図7】従来例の信号波形モニタ装置(埋め込みPFEのみ)と、第1の実施形態に係るオンチップ信号波形モニタ装置102における信号波形取得のための測定時間(推定値)を示すグラフである。10

【図8】図1の信号検出フロントエンド回路30において用いるNチャンネルソースフォロア回路111の構成を示す回路図である。

【図9】図1の信号検出フロントエンド回路30において用いるPチャンネルソースフォロア回路112の構成を示す回路図である。

【図10】図1の信号検出フロントエンド回路30において用いるラッチコパレータ34の構成を示す回路図である。

【図11】図1の参照電圧発生器10の構成を示すブロック図である。

【図12】図11の参照電圧発生器10によって発生される参照電圧V<sub>ref</sub>を示すタイミングチャートである。20

【図13】図1のレプリカDLL回路21及び10ビット可変ステップ遅延信号発生回路22を備えたサンプリングタイミング信号発生器20の構成を示す回路図である。

【図14】図13の10ビット可変ステップ遅延信号発生回路22の構成の詳細を示す回路図である。

【図15】図1のレプリカDLL回路21を示すブロック図及び回路図である。

【図16】第1の実施形態に係るオンチップ信号波形モニタ装置102の実施例に係る試作チップの平面の写真である。

【図17】図1のオンチップ信号波形モニタ装置102を備えた第1の実施形態に係る信号波形測定システムの構成を示すブロック図である。30

【図18】従来例の信号波形モニタ装置(埋め込みPFEのみ)と、第1の実施形態に係るオンチップ信号波形モニタ装置102における電源電圧(実測値)を示すグラフである。

【図19】従来例の信号波形モニタ装置(埋め込みPFEのみ)と、第1の実施形態に係るオンチップ信号波形モニタ装置102における接地電圧(実測値)を示すグラフである。

【図20】従来例の信号波形モニタ装置(埋め込みPFEのみ)と、第1の実施形態に係るオンチップ信号波形モニタ装置102における信号波形取得のための測定時間(実測値)を示すグラフである。

【図21】(a)は第1の実施形態に係るオンチップ信号波形モニタ装置102における電源電圧(実測値)を示すグラフであり、(b)は第1の実施形態に係るオンチップ信号波形モニタ装置102における接地電圧(実測値)を示すグラフである。40

【図22】第2の実施形態に係る信号波形測定システムにおいて用いる、参照電圧V<sub>ref</sub>に対するラッチコンパレータ34の判定出力確率P<sub>cm<sub>p</sub></sub>を示すグラフである。

【図23】本発明の第2の実施形態に係る信号波形測定システムの構成を示すブロック図である。

【図24】図23のパーソナルコンピュータ200及びFPGA170の詳細を示すブロック図である。

【図25】図23のオンチップDPU40Aの構成を示すブロック図である。

【図26】図25のオンチップDPU40Aの動作を示すタイミングチャートである。50

【図27】図24のオフチップDPU302の構成を示すブロック図である。

【図28】図27の32ビットメモリに格納される、参照電圧Vrefに対するデジタル出力信号Pcmpの特性を示すグラフである。

【図29】図24のシーケンス信号発生器213の構成を示すブロック図である。

【図30】従来例の信号波形モニタ装置（埋め込みPFEのみ）と、第2の実施形態に係る図27の信号波形測定システムとにおける信号波形取得のための測定時間（実測値）を示すグラフである。

【図31】本発明の第3の実施形態に係る信号検出フロントエンド回路30Aの構成を示す回路図である。

【図32】本発明の第3の実施形態の変形例に係る信号検出フロントエンド回路30Bの構成を示す回路図である。 10

【図33】本発明の第4の実施形態に係る信号検出フロントエンド回路30Cの構成を示す回路図である。

【図34】図33のソースフォロワ及び電流モードサンプルホールド回路270-1の構成を示すブロック図である。

【図35】図33のソースフォロワ及び電流モードサンプルホールド回路270-2の構成を示すブロック図である。

【図36】図33のソースフォロワ及び電流モードサンプルホールド回路270-3の構成を示すブロック図である。

【図37】図34のソースフォロワ及び電流モードサンプルホールド回路270-1の入出力電圧特性を示すグラフである。 20

【図38】図35のソースフォロワ及び電流モードサンプルホールド回路270-2の入出力電圧特性を示すグラフである。

【図39】図36のソースフォロワ及び電流モードサンプルホールド回路270-3の入出力電圧特性を示すグラフである。

【図40】本発明の第4の実施形態に係る信号検出フロントエンド回路30Cにおいて観測したオンチップ信号波形を示す波形図である。

#### 【符号の説明】

##### 【0099】

10 ... 参照電圧発生器、

11 ... インクリメンタルDA変換器、

20 ... サンプリングタイミング信号発生器、

21 ... レプリカDLL回路、

22 ... 可変ステップ遅延信号発生回路、

30 , 30-1乃至30-M , 30A , 30B , 30C ... 信号検出フロントエンド回路、

33 , 33-1乃至33-M ... 検出点、

34 ... ラッチコンパレータ、

34A ... 電流型コンパレータ、

35 ... デマルチプレクサ、

36 ... マルチプレクサ、

40 ... データ処理ユニット、

40A ... オンチップDPU、

41 ... カウンタ回路、

42 ... シフトレジスタ回路、

60 ... ラダー回路、

61 ... 10ビットカウンタ、

62 , 63 ... 抵抗、

64 ... スイッチ、

71 , 73 ... 差動増幅器、

72 ... インバータ、

30

40

50

|                                                      |    |

|------------------------------------------------------|----|

| 8 0 , 8 1 ... 遅延セル回路、                                |    |

| 8 2 ... 遅延型フリップフロップ、                                 |    |

| 8 3 ... 位相及び周波数検出器、                                  |    |

| 8 4 ... チャージポンプ回路、                                   |    |

| 8 5 , 8 7 ... インバータ、                                 |    |

| 8 6 ... コンパレータ、                                      |    |

| 9 0 , 9 0 A ... 信号波形取得カーネル回路、                        |    |

| 1 0 0 ... オンチップ信号波形測定装置                              |    |

| 1 0 1 ... テスト対象デバイス( D U T )、                        | 10 |

| 1 0 2 ... オンチップ信号波形モニタ装置、                            |    |

| 1 0 4 ... 電圧源、                                       |    |

| 1 0 5 ... 電圧源、                                       |    |

| 1 1 0 ... ロジックアナライザ、                                 |    |

| 1 2 0 ... パーソナルコンピュータ、                               |    |

| 1 1 1 ... Nチャンネルソースフォロワ回路、                           |    |

| 1 1 2 ... Pチャンネルソースフォロワ回路、                           |    |

| 1 2 0 ... パーソナルコンピュータ、                               |    |

| 1 3 1 ... 11ビットマスタクロックカウンタ、                          |    |

| 1 3 2 ... 10ビットデータカウンタ、                              |    |

| 1 4 0 ... 32ビットメモリ、                                  | 20 |

| 1 4 1 ... 比較ロジック、                                    |    |

| 1 4 2 ... ナンドゲート、                                    |    |

| 1 4 3 ... 10ビットVrefカウンタ、                             |    |

| 1 4 4 ... 7ビットTckカウンタ、                               |    |

| 1 5 0 ... オンチップDUTボード、                               |    |

| 1 5 1 ... LSIチップ、                                    |    |

| 1 6 0 ... 電圧源、                                       |    |

| 1 6 1 ... 電圧変換器、                                     |    |

| 1 7 0 ... FPGAs、                                     |    |

| 2 0 0 ... パーソナルコンピュータ、                               | 30 |

| 2 1 0 ... USBインターフェース、                               |    |

| 2 1 1 ... テストベクトル発生器、                                |    |

| 2 1 2 ... クロック発振器、                                   |    |

| 2 1 3 ... シーケンス信号発生器、                                |    |

| 2 1 4 ... オフチップDPU(データロッガ)、                          |    |

| 2 2 0 , 2 3 0 , 2 4 0 ... 信号発生器、                     |    |

| 2 5 1 , 2 5 1 - 0 乃至 2 5 1 - 2 ... ソースフォロワ回路、        |    |

| 2 5 2 ... 電圧・電流変換器、                                  |    |

| 2 5 2 R ... 抵抗、                                      |    |

| 2 5 2 S ... セレクタスイッチ、                                | 40 |

| 2 5 3 ... サンプルホールド回路、                                |    |

| 2 5 4 ... 電流発生器、                                     |    |

| 2 5 5 ... バイアス発生回路、                                  |    |

| 2 6 0 ... 電流モードサンプルホールド回路、                           |    |

| 2 7 0 - 1 乃至 2 7 0 - M ... ソースフォロワ及び電流モードサンプルホールド回路、 |    |

| 2 7 1 - 1 乃至 2 7 1 - M ... 遅延型フリップフロップ、              |    |

| 2 7 2 - 1 乃至 2 7 2 - M ... アンドゲート、                   |    |

| MU0 乃至 MU10 ... マルチプレクサ、                             |    |

| DF1 乃至 DF10 ... 遅延型フリップフロップ、                         |    |

| Q1 乃至 Q112 ... 電界効果トランジスタ、                           | 50 |

SW10-0 乃至 SW10-(m-1), SW11, SW12-0 乃至 SW12-3, SW21, SW31-1 乃至 SW31-M...スイッチ。

【図1】

【図2】

【 図 3 】

【 図 4 】

〔 図 5 〕

【 四 6 】

【図 7】

【図 9】

【図 10】

【図 8】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図 17】

( 18 )

【図19】

【 図 2 1 】

【 义 20 】

【 図 2 2 】

## 第2の実施形態

【図23】

【図24】

【図25】

【図26】

【図27】

第2の実施形態

オフチップDPU 214

【図 28】

【図 29】

【図 30】

【図 31】

【図 3 2】

【図 3 3】

【図 3 4】

【図 3 5】

【図 3 6】

【図 3 7】

【図 3 8】

【図 3 9】

【図 4 0】