(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5848936号

(P5848936)

(45) 発行日 平成28年1月27日(2016.1.27)

(24) 登録日 平成27年12月4日(2015.12.4)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/786 (2006.01)

H01L 29/78 H01L 29/78 H01L 29/78 H01L 29/78

627C 612D 618C 618B

請求項の数 15 (全 26 頁)

(21) 出願番号 特願2011-217269 (P2011-217269)

(22) 出願日 平成23年9月30日 (2011.9.30)

(65) 公開番号 特開2012-104811 (P2012-104811A)

(43) 公開日 平成24年5月31日 (2012.5.31)

審査請求日 平成26年9月26日 (2014.9.26)

(31) 優先権主張番号 特願2010-231372 (P2010-231372)

(32) 優先日 平成22年10月14日 (2010.10.14)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 溝口 隆文

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 白石 康次郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及びマスク膜をこの順に積層して形成し、

前記マスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記マスク膜をドライエッチング又はウェットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層及び前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、前記第1の導電膜の一部にサイドエッチングを伴うウェットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第1のマスク層上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第1のマスク層をドライエッチング又はウェットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

10

20

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

【請求項2】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウエットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜 10 に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層をドライエッチングして除去し、

前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチング又はウエットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

【請求項3】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウエットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜 30 に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層と前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成しつつ第1のマスク層を除去し、

前記サイドウォール絶縁層を形成後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチング又はウエットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

【請求項4】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及びマスク膜をこの順に積層して形成し、

10

20

30

40

50

前記マスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記マスク膜をドライエッチング又はウェットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層及び前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、前記第1のマスク層上に第2のレジストマスクを形成し、

前記第2のレジストマスクを形成後、前記第1の導電膜の一部にサイドエッチングを伴うウェットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第2のレジストマスクを用いて前記第1のマスク層をドライエッチング又はウェットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項5】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウェットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層をドライエッチングして除去し、

前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを形成後、前記第1の導電膜の一部にサイドエッチングを伴うウェットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチング又はウェットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項6】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウェットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

10

20

30

40

50

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層及び前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成しつつ第1のマスク層を除去し、

前記サイドウォール絶縁層を形成後、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを形成後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチング又はウエットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項7】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及びマスク膜をこの順に積層して形成し、

前記マスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記マスク膜をドライエッチング又はウエットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層及び前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、前記第1のマスク層上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第1のマスク層をドライエッチングまたはウエットエッチングして第2のマスク層を形成し、

前記第2のマスク層を形成後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項8】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウエットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層をドライエッチングにより除去し、

前記薄膜積層体を覆って第2の絶縁膜を形成し、

10

20

30

40

50

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッティング又はウエットエッティングして第2のマスク層を形成し、

前記第2のマスク層を形成後、前記第1の導電膜の一部にサイドエッティングを伴うウエットエッティング又はドライエッティングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッティングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項9】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッティング又はウエットエッティングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜及び前記第2の導電膜に対してドライエッティングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層と前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成しつつ第1のマスク層を除去し、

前記サイドウォール絶縁層を形成後、少なくとも前記第2の導電膜上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッティング又はウエットエッティングして第2のマスク層を形成し、

前記第2のマスク層を形成後、前記第1の導電膜の一部にサイドエッティングを伴うウエットエッティング又はドライエッティングを行って第1の電極層を形成し、

前記第1の電極層を形成後、前記第2のレジストマスクを除去し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッティングして、第2の電極層と半導体層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項10】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及びマスク膜をこの順に積層して形成し、

前記マスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記マスク膜をドライエッティング又はウエットエッティングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッティングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層及び前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

前記サイドウォール絶縁層を形成後、前記第1のマスク層上に第2のレジストマスクを形成し、

10

20

30

40

50

前記第2のレジストマスクを用いて前記第1のマスク層をドライエッチング又はウエットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のレジストマスクを除去後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層とを形成することを特徴とする半導体装置の作製方法。

#### 【請求項11】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

10

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウエットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

前記第1のマスク層をドライエッチングして除去し、

前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成し、

20

前記サイドウォール絶縁層を形成後、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチング又はウエットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

前記第2のレジストマスクを除去後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層とを形成することを特徴とする半導体装置の作製方法。

30

#### 【請求項12】

第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜、及び第1のマスク膜をこの順に積層して形成し、

前記第1のマスク膜上に第1のレジストマスクを形成し、

前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチング又はウエットエッチングして第1のマスク層を形成し、

前記第1のレジストマスクを除去し、

前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜、及び前記第2の導電膜に対してドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、

40

前記第1のマスク層及び前記薄膜積層体を覆って第2の絶縁膜を形成し、

前記第2の絶縁膜をエッチバック処理して、少なくとも前記薄膜積層体が有する半導体領域の側面を覆うサイドウォール絶縁層を形成しつつ第1のマスク層を除去し、

前記サイドウォール絶縁層を形成後、少なくとも前記第2の導電膜上に第2のマスク膜を形成し、

前記第2のマスク膜上に第2のレジストマスクを形成し、

前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチング又はウエットエッチングして第2のマスク層を形成し、

前記第2のレジストマスクを除去し、

50

前記第2のレジストマスクを除去後、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチング又はドライエッチングを行って第1の電極層を形成し、

前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングして、第2の電極層と半導体層とを形成することを特徴とする半導体装置の作製方法。

#### 【請求項13】

請求項1乃至請求項12のいずれか一に記載の作製方法により作製した半導体装置の第2の電極層に電気的に接続される画素電極層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項14】

請求項1乃至請求項12のいずれか一に記載の作製方法により作製した半導体装置の第2の電極層に接する領域を有する保護絶縁膜を形成し、

10

前記第2の電極層の一部を露出させるように前記保護絶縁膜に開口部を形成し、

前記開口部上及び前記保護絶縁膜上に画素電極層を形成することを特徴とする半導体装置の作製方法。

#### 【請求項15】

請求項1乃至請求項14のいずれか一において、

前記半導体膜はIn、Ga、及びZnを含む酸化物半導体膜であり、

前記第2の導電膜はチタン膜であり、

前記マスク膜又は前記第1のマスク膜は酸化アルミニウム膜であることを特徴とする半導体装置の作製方法。

20

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置とその作製方法に関する。なお、本明細書において、半導体装置とは、半導体素子自体または半導体素子を含むものをいい、このような半導体素子として、例えばトランジスタ（薄膜トランジスタなど）が挙げられる。また、液晶表示装置などの表示装置も半導体装置に含まれる。

##### 【背景技術】

##### 【0002】

近年、半導体装置は人間の生活に欠かせないものとなっている。このような半導体装置に含まれる薄膜トランジスタなどの半導体素子は、基板上に半導体膜などの薄膜を形成し、該薄膜をフォトリソグラフィ法などにより所望の形状に加工することで作製される。このような作製方法は、例えば、アクティブマトリクス型液晶表示装置（例えば、液晶テレビ）に適用されている。

30

##### 【0003】

アクティブマトリクス型液晶表示装置に代表される半導体装置の作製には、フォトリソグラフィ法を用いることが一般的である。フォトリソグラフィ法では、生産性の観点から、フォトマスクの枚数を少なくすることが求められる。例えば、特許文献1乃至特許文献4には、フォトマスクの枚数を少なくすることができる技術が開示されている。

##### 【0004】

40

ところで、薄膜トランジスタに設けられる半導体層の材料としては、シリコンが広く用いられている。しかし、近年では、半導体層の材料として酸化物半導体を用いた薄膜トランジスタについても、研究が盛んに進められている。しかし、酸化物半導体を用いた薄膜トランジスタでは、半導体層に水分が混入すると、キャリア濃度が大きく変化することが知られている（例えば、特許文献5及び特許文献6）。また、酸化物半導体以外を用いた薄膜トランジスタにおいても、半導体層に水分が混入することで特性が変化することが知られている（例えば、特許文献7）。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

50

【特許文献 1】特開 2009 - 158941 号公報

【特許文献 2】特開 2009 - 239272 号公報

【特許文献 3】特開 2009 - 239276 号公報

【特許文献 4】特開 2010 - 199570 号公報

【特許文献 5】特開 2010 - 182818 号公報

【特許文献 6】特開 2010 - 182819 号公報

【特許文献 7】特開 2005 - 55660 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

10

前記特許文献 1 乃至特許文献 4 に開示された技術によれば、フォトマスクの枚数を少なくすることができる。しかし、例えば、ソース電極及びドレイン電極の形成時にレジストマスクを用いているため、ソース電極及びドレイン電極の形成後にレジストマスクを除去する必要がある。レジストマスクの除去は、一般には、レジスト剥離液を用いて行うが、加工により露出した層がレジスト剥離液に曝されることになる。一方で、レジストマスクの除去は、例えば、酸素プラズマを用いたドライ工程（水分を用いない工程。例えばアッシング工程）により行うことも可能であるが、レジスト残りが生じうる。

【0007】

20

半導体層に水分がひとたび混入すると、これを除去することは容易ではない。混入する水分を除去する手段の一例として、水分が混入した半導体層に対する加熱処理が挙げられる。しかし、例えば、ガラス基板上に半導体層を設けた場合、加熱可能な温度に制約があり、加熱処理には長い時間を要するので、スループットを低下させる一因となる。

【0008】

本発明の一態様は、半導体層となる部分の全面が水分などに曝されず、フォトリソグラフィ法に用いるフォトマスクの枚数を少なくすることが可能な半導体装置の作製方法を提供することを課題とする。特に、半導体層となる部分の全面がレジストマスクを剥離する際のレジスト剥離液に曝されず、フォトリソグラフィ法に用いるフォトマスクの枚数を少なくすることが可能な半導体装置の作製方法を提供することを課題とする。

【課題を解決するための手段】

【0009】

30

本発明の一態様は、半導体層となる部分を密閉して、半導体層となる部分が薬液（例えば、レジスト剥離液）に触れることなく作製することができ、マスク枚数を削減できる半導体装置の作製方法を提供する。

【0010】

本発明の一態様は、第 1 の導電膜、第 1 の絶縁膜、半導体膜、第 2 の導電膜及びマスク膜をこの順に形成し、前記マスク膜上に第 1 のレジストマスクを形成し、前記第 1 のレジストマスクを用いて前記マスク膜を加工して第 1 のマスク層を形成し、前記第 1 のレジストマスクを薬液（例えば、レジスト剥離液）により除去し、前記第 1 のマスク層を用いて前記第 1 の絶縁膜、前記半導体膜及び前記第 2 の導電膜にドライエッチングを行って薄膜積層体を形成しつつ、前記第 1 の導電膜の少なくとも表面を露出させ、前記薄膜積層体の側面を覆うサイドウォール絶縁層を形成し、前記第 1 の導電膜をサイドエッチングして第 1 の電極層を形成し、前記薄膜積層体上の前記第 1 のマスク層（または該第 1 のマスク層を除去して形成した前記薄膜積層体上の更なるマスク膜）上に第 2 のレジストマスクを形成し、前記第 2 のレジストマスクを用いて、前記第 1 のマスク層または前記更なるマスク膜を加工して第 2 のマスク層を形成し、前記第 2 のレジストマスクを薬液（例えば、レジスト剥離液）により除去し、前記第 2 のマスク層を用いて、前記薄膜積層体の上部を加工して第 2 の電極層を形成し、前記半導体膜が露出される工程は、前記第 1 のレジストマスクまたは前記第 2 のレジストマスクが除去された後に行われることを特徴とする半導体装置の作製方法である。

【0011】

40

50

なお、本明細書において、第1の電極層は、少なくともゲート電極を構成し、ゲート配線を構成していてもよい。そして、第2の電極層は、ソース電極及びドレイン電極を構成し、ソース配線を構成していてもよい。

#### 【0012】

なお、本明細書において、「膜」とは、後に加工されることが前提のものであって、被形成面上に概略一様に形成されたものをいう。「層」とは、前記膜を加工したもの、または、前記膜であるが、後に加工しなくてもよいものをいう。

#### 【0013】

なお、本明細書において、エッチバック処理とは、ある面の上において全面に形成された膜に対して異方性の高いエッティング(例えば、ドライエッティング)を行うことで、該全面に形成された膜の被形成面の一部を露出させるまで行うエッティング工程をいう。

10

#### 【0014】

なお、前記構成の本発明の一態様において、第1のレジストマスクと第2のレジストマスクはドライ工程により除去してもよく、ドライ工程により除去する場合には、洗浄工程を経ることが好ましい。

#### 【0015】

また、前記構成の本発明の一態様において、第1のレジストマスクと第2のレジストマスクのいずれか一方が薬液により除去され、他方がドライ工程により除去されてもよい。

#### 【発明の効果】

#### 【0016】

20

本発明の一態様によれば、半導体層となる部分の全面が水分などに曝されず、フォトリソグラフィ法に用いるフォトマスクの枚数を少なくして半導体装置を作製することができる。特に、半導体層となる部分の全面がレジストマスクを剥離する際のレジスト剥離液に曝されず、フォトリソグラフィ法に用いるフォトマスクの枚数を少なくして半導体装置を作製することができる。

#### 【0017】

本発明の一態様によれば、レジスト残りを生じさせることなく、半導体層となる部分の全面を水分に曝さずに、フォトリソグラフィ法に用いるフォトマスクの枚数を少なくして半導体装置を作製することができる。

#### 【図面の簡単な説明】

30

#### 【0018】

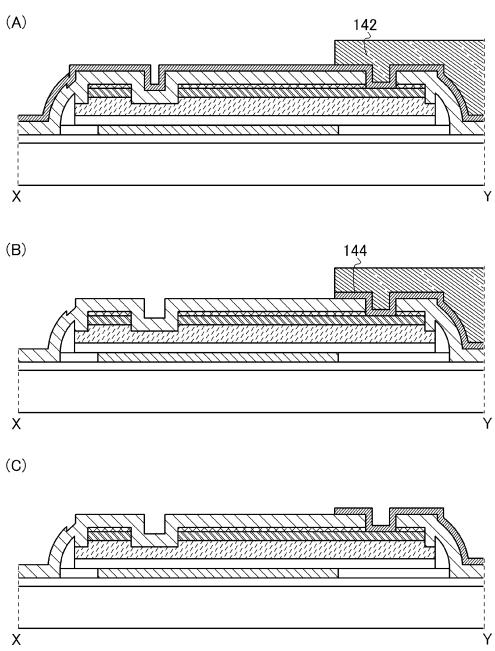

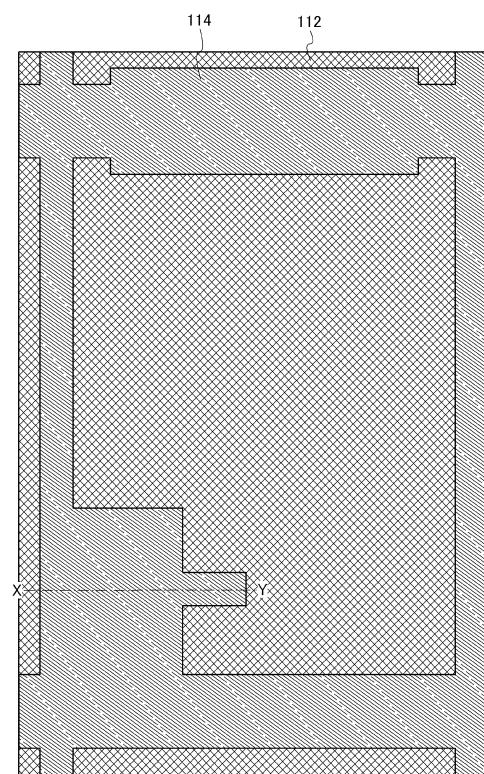

【図1】本発明の一態様である半導体装置の作製方法を説明する断面図。

【図2】本発明の一態様である半導体装置の作製方法を説明する断面図。

【図3】本発明の一態様である半導体装置の作製方法を説明する断面図。

【図4】本発明の一態様である半導体装置の作製方法を説明する断面図。

【図5】本発明の一態様である半導体装置の作製方法を説明する断面図。

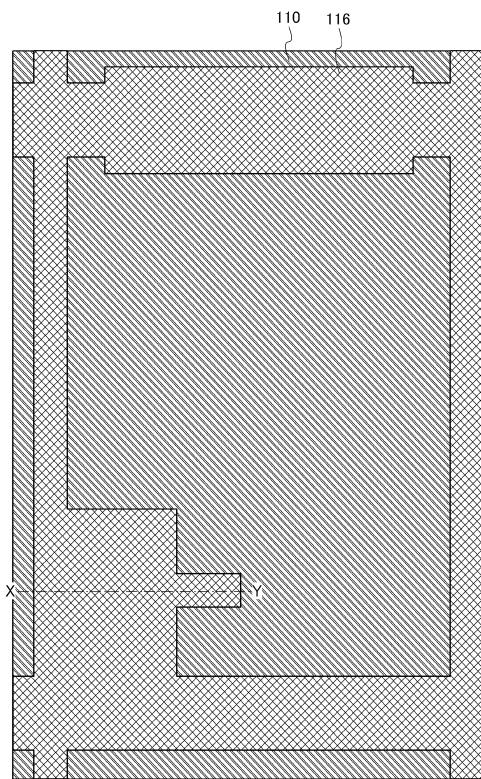

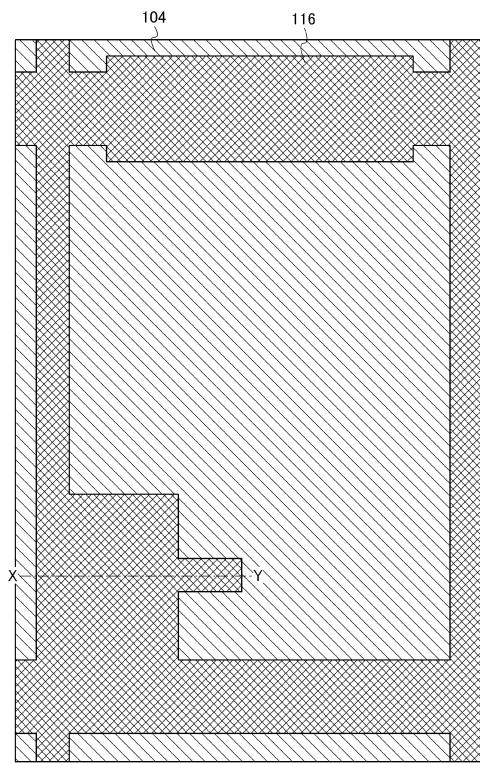

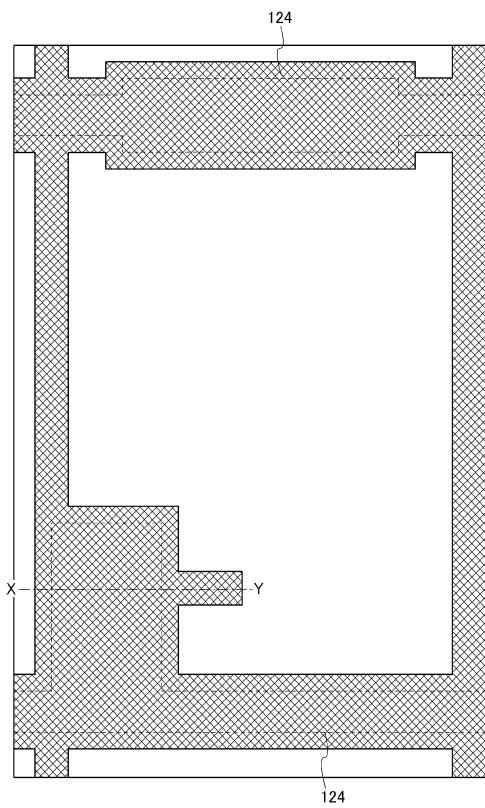

【図6】本発明の一態様である半導体装置の作製方法を説明する上面図。

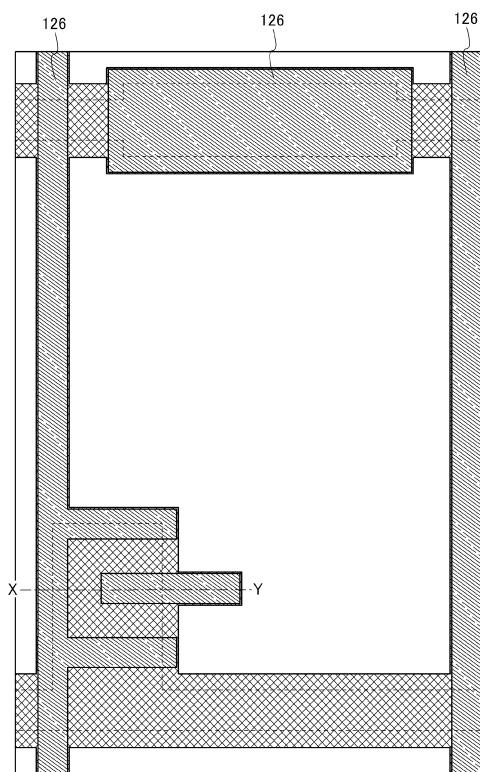

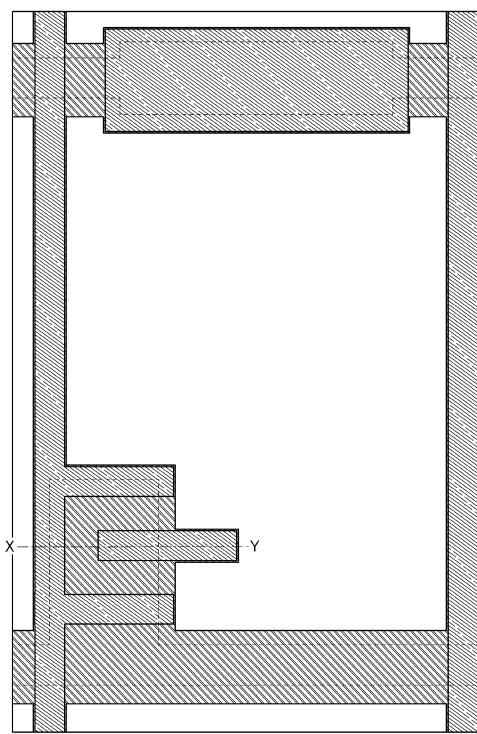

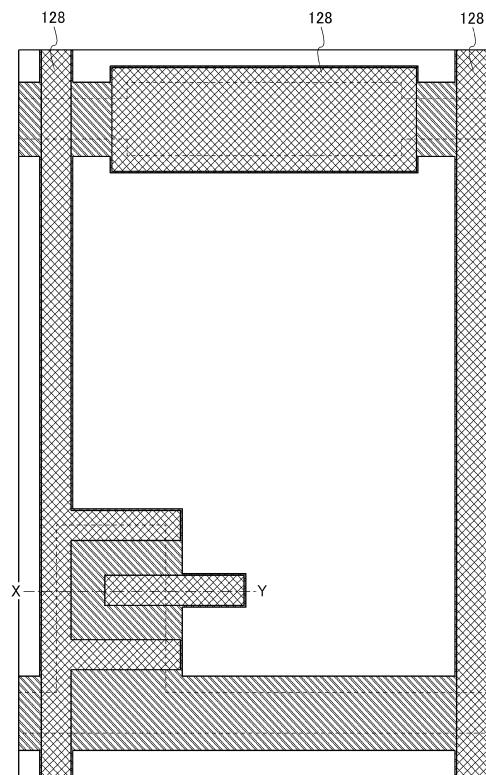

【図7】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図8】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図9】本発明の一態様である半導体装置の作製方法を説明する上面図。

40

【図10】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図11】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図12】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図13】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図14】本発明の一態様である半導体装置の作製方法を説明する上面図。

【図15】本発明の一態様である半導体装置を説明する図。

【図16】本発明の一態様である半導体装置を説明する図。

【図17】本発明の一態様である半導体装置を説明する図。

#### 【発明を実施するための形態】

#### 【0019】

50

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、上面図において、絶縁膜及び絶縁層は図示しないことがある。

#### 【0020】

##### (実施の形態1)

本実施の形態では、本発明の一態様である半導体装置の作製方法について、図面を参照して説明する。

#### 【0021】

本実施の形態にて説明する本発明の一態様である半導体装置の作製方法の一は、第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜及びマスク膜をこの順に積層して形成し、前記マスク膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて前記マスク膜をドライエッチングまたはウエットエッチングすることで第1のマスク層を形成し、前記第1のレジストマスクを除去し、前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜及び前記第2の導電膜にドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、前記第1のマスク層と前記薄膜積層体を覆って第2の絶縁膜を形成し、前記第2の絶縁膜をエッチバック処理することで、少なくとも前記薄膜積層体が有する半導体領域の側面のすべてを覆ってサイドウォール絶縁層を形成し、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチングまたはドライエッチングを行って第1の電極層を形成し、前記第1のマスク層上に第2のレジストマスクを形成し、前記第2のレジストマスクを用いて前記第1のマスク層をドライエッチングまたはウエットエッチングすることで第2のマスク層を形成し、前記第2のレジストマスクを除去し、前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングすることで第2の電極層と半導体層を形成することを特徴とする。

#### 【0022】

または、本発明の一態様である半導体装置の作製方法では、前記第2のマスク層は前記第1のマスク層を加工して形成されたものでなくてもよい。このとき、前記第1のマスク層は前記薄膜積層体の形成後に除去され、前記サイドウォール絶縁層の形成後に第2のマスク膜が形成され、前記第2のマスク膜を加工して第2のマスク層が形成されてもよい。従って、本実施の形態にて説明する本発明の一態様である半導体装置の作製方法の一は、第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜及び第1のマスク膜をこの順に積層して形成し、前記第1のマスク膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチングまたはウエットエッチングすることで第1のマスク層を形成し、前記第1のレジストマスクを除去し、前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜及び前記第2の導電膜にドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、前記第1のマスク層をドライエッチングにより除去し、前記薄膜積層体を覆って第2の絶縁膜を形成し、前記第2の絶縁膜をエッチバック処理することで、少なくとも前記薄膜積層体が有する半導体領域の側面のすべてを覆ってサイドウォール絶縁層を形成し、前記第1の導電膜の一部にサイドエッチングを伴うウエットエッチングまたはドライエッチングを行って第1の電極層を形成し、少なくとも前記薄膜積層体上に第2のマスク膜を形成し、前記第2のマスク膜上に第2のレジストマスクを形成し、前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチングまたはウエットエッチングすることで第2のマスク層を形成し、前記第2のレジストマスクを除去し、前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングすることで第2の電極層と半導体層を形成することを特徴とする。

#### 【0023】

または、本発明の一態様である半導体装置の作製方法では、前記サイドウォール絶縁層の形成時に、前記第1のマスク層が除去されてもよい。従って、本実施の形態にて説明す

10

20

30

40

50

る本発明の一態様である半導体装置の作製方法の一は、第1の導電膜、第1の絶縁膜、半導体膜、第2の導電膜及び第1のマスク膜をこの順に積層して形成し、前記第1のマスク膜上に第1のレジストマスクを形成し、前記第1のレジストマスクを用いて前記第1のマスク膜をドライエッチングまたはウェットエッチングすることで第1のマスク層を形成し、前記第1のレジストマスクを除去し、前記第1のマスク層を用いて前記第1の絶縁膜、前記半導体膜及び前記第2の導電膜にドライエッチングを行って薄膜積層体を形成しつつ、前記第1の導電膜の少なくとも表面を露出させ、前記第1のマスク層と前記薄膜積層体を覆って第2の絶縁膜を形成し、前記第2の絶縁膜をエッチバック処理することで、少なくとも前記薄膜積層体が有する半導体領域の側面のすべてを覆ってサイドウォール絶縁層を形成しつつ第1のマスク層を除去し、前記第1の導電膜の一部にサイドエッチングを伴うウェットエッチングまたはドライエッチングを行って第1の電極層を形成し、少なくとも前記第2の導電層上に第2のマスク膜を形成し、前記第2のマスク膜上に第2のレジストマスクを形成し、前記第2のレジストマスクを用いて前記第2のマスク膜をドライエッチングまたはウェットエッチングすることで第2のマスク層を形成し、前記第2のレジストマスクを除去し、前記第2のマスク層を用いて前記薄膜積層体の上部をドライエッチングすることで第2の電極層と半導体層を形成することを特徴とする。

10

#### 【0024】

なお、前記構成の半導体装置の作製方法において、第1の電極層の形成は、第2のレジストマスクを形成した後、第2のマスク層を形成する前に行ってもよい。または、第2のマスク層を形成した後、第2のレジストマスク除去する前に行ってもよい。または、第2のレジストマスクを除去した後に行ってもよい。

20

#### 【0025】

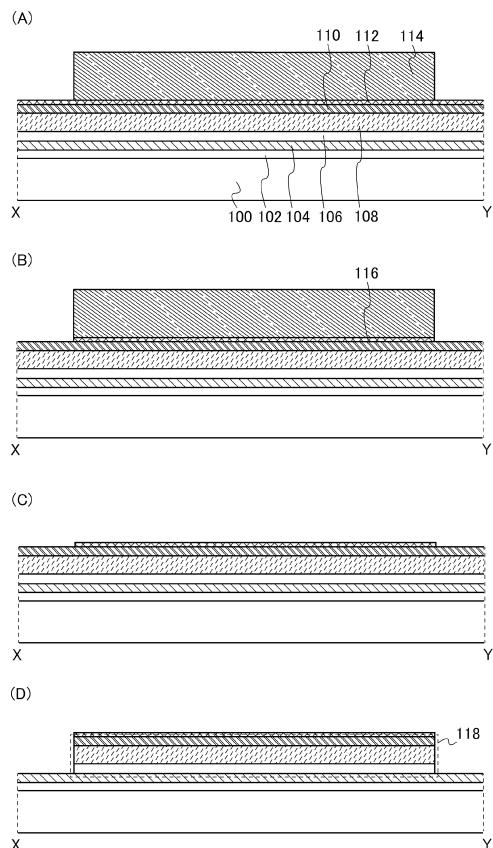

まず、基板100上に下地絶縁層102、第1の導電膜104、第1の絶縁膜106、半導体膜108、第2の導電膜110、マスク膜112を形成する。これらの膜は、単層で形成してもよいし、複数の膜を積層した積層膜であってもよい。そして、マスク膜112上には第1のレジストマスク114を形成する(図1(A)、図6)。

#### 【0026】

基板100は、絶縁性基板である。基板100として、例えば、ガラス基板、石英基板、セラミック基板、または本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板などを用いることができる。基板100がガラス基板である場合には、第1世代(例えば、320mm×400mm)～第10世代(例えば、2950mm×3400mm)のものを用いればよいが、これに限定されるものではない。

30

#### 【0027】

下地絶縁層102は、基板100がエッチングされること、及び基板100にアルカリ金属などが含まれる場合に、これが半導体膜に侵入することを防止するために設けられるものであり、例えば、窒化シリコンにより形成すればよい。なお、下地絶縁層102は、必要のない場合には設けなくてもよい。

#### 【0028】

第1の導電膜104は、例えば、スパッタリング法またはCVD法(プラズマCVD法または熱CVD法などを含む。)などを用いて形成すればよい。第1の導電膜104の材料としては、例えば金属膜、または一導電型の不純物元素が添加された半導体膜などを例示することができる。または、インクジェット法などを用いて形成してもよい。なお、第1の導電膜104は、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、Ti層またはMo層によりAl層を挟持した3層の積層構造とすればよい。

40

#### 【0029】

第1の絶縁膜106は、例えば、スパッタリング法またはCVD法(プラズマCVD法または熱CVD法などを含む。)などを用いて絶縁性材料(例えば、窒化シリコン、窒化酸化シリコン、酸化窒化シリコンまたは酸化シリコンなど)により形成すればよい。なお、第1の絶縁膜106は、単層で形成してもよいし、複数の層を積層して形成してもよい。

50

## 【0030】

なお、「窒化酸化シリコン」とは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、酸素の組成が 5 ~ 30 原子%、窒素の組成が 20 ~ 55 原子%、シリコンの組成が 25 ~ 35 原子%、水素の組成が 10 ~ 30 原子% の範囲で見積もられるものをいう。

## 【0031】

なお、「酸化窒化シリコン」とは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、RBS 及び HFS を用いて測定した場合に、酸素の組成が 50 ~ 70 原子%、窒素の組成が 0.5 ~ 1.5 原子%、シリコンの組成が 25 ~ 35 原子%、水素の組成が 0.1 ~ 1.0 原子% の範囲で見積もられるものをいう。10

## 【0032】

ただし、酸化窒化シリコンまたは窒化酸化シリコンの原子組成の合計を 100 原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

## 【0033】

半導体膜 108 は、半導体膜であればよく、単層であってもよいし、複数の層が積層された積層構造であってもよい。半導体膜 108 として、例えば、酸化物半導体膜またはシリコン膜が挙げられる。20

## 【0034】

半導体膜 108 が酸化物半導体膜である場合には、四元系金属酸化物である In - Sn - Ga - Zn - O 系酸化物半導体や、三元系金属酸化物である In - Ga - Zn - O 系酸化物半導体、In - Sn - Zn - O 系酸化物半導体、In - Al - Zn - O 系酸化物半導体、Sn - Ga - Zn - O 系酸化物半導体、Al - Ga - Zn - O 系酸化物半導体、Sn - Al - Zn - O 系酸化物半導体や、二元系金属酸化物である In - Zn - O 系酸化物半導体、Sn - Zn - O 系酸化物半導体、Al - Zn - O 系酸化物半導体、Zn - Mg - O 系酸化物半導体、Sn - Mg - O 系酸化物半導体、In - Mg - O 系酸化物半導体や、In - O 系酸化物半導体、Sn - O 系酸化物半導体、Zn - O 系酸化物半導体などを用いることができる。また、酸化物半導体膜が SiO<sub>2</sub> を含んでいてもよい。ここで、例えば、In - Ga - Zn - O 系酸化物半導体膜とは、In、Ga または Zn を有する酸化物半導体膜をいい、その化学量論比はとくに問わない。また、In と Ga と Zn 以外の元素を含んでいてもよい。30

## 【0035】

半導体膜 108 が酸化物半導体膜である場合には、例えば、化学式 InM<sub>m</sub>O<sub>3</sub> (ZnO)<sub>m</sub> (m > 0) で表記されるものを用いるということもできる。ここで、M は、Ga、Al、Mn 及び Co から選ばれた一または複数の金属元素を示す。例えば M として、Ga、Ga 及び Al、Ga 及び Mn、または Ga 及び Co などが挙げられる。または、酸化物半導体膜は酸化シリコンを含んでいてもよい。

## 【0036】

また、酸化物半導体膜をスパッタリング法で形成するためのターゲットとしては、例えば、組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol 数比] の酸化物ターゲットを用いる。ただし、このターゲットの材料及び組成に限定されず、例えば、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 2 [mol 数比] の酸化物ターゲットを用いてもよい。

## 【0037】

ここでは、半導体膜 108 が酸化物半導体膜であり、スパッタリング法で形成される場合には、希ガス (例えば Ar) 雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下においてスパッタリング法により形成することができる。

## 【0038】

5020304050

また、酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。このように、充填率の高い酸化物ターゲットを用いることにより、成膜される酸化物半導体膜を緻密な膜とすることができます。

#### 【0039】

半導体膜108が酸化物半導体膜である場合には、半導体膜108に接する第1の絶縁膜106を酸化シリコンにより形成し、後に形成するサイドウォール絶縁層122も酸化シリコンにより形成し、酸化物半導体膜の脱水化または脱水素化を行うことが可能な条件で加熱処理を行うとよい。このように加熱処理を行う場合であっても、酸化物半導体膜が水分に曝されていないため、加熱処理時間は従来よりも短時間でよい。

#### 【0040】

または、半導体膜108として、シリコン膜を用いてもよい。シリコン膜としては、アモルファスシリコン膜を用いればよい。または、キャリア移動度が高いシリコン膜上にキャリア移動度が低いシリコン膜が設けられた積層シリコン膜であってもよい。

#### 【0041】

キャリア移動度が高いシリコン膜としては、結晶性シリコン膜が挙げられる。結晶性シリコンとしては、例えば、微結晶シリコンが挙げられる。ここで、微結晶シリコンとは、非晶質と結晶構造（単結晶、多結晶を含む。）の中間的な構造のものをいう。微結晶シリコンは、熱力学的に安定な第3の状態を有し、短距離秩序を持ち格子歪みを有する結晶質なシリコンであり、結晶粒径が2nm以上200nm以下、好ましくは10nm以上80nm以下、より好ましくは20nm以上50nm以下の柱状または針状の結晶粒が基板表面に対して法線方向に成長しているシリコンである。このため、柱状または針状の結晶粒の界面には、粒界が形成されることもある。なお、ここでの結晶粒径は、基板表面に対して平行な面における結晶粒の最大直径である。また、結晶粒は、非晶質シリコン領域と、単結晶とみなせる微小結晶の結晶子を有する。なお、結晶粒は双晶を有する場合もある。

#### 【0042】

微結晶シリコンでは、そのラマンスペクトルのピークが単結晶シリコンを示す520cm<sup>-1</sup>よりも低波数側にシフトしている。すなわち、単結晶シリコンを示す520cm<sup>-1</sup>と非晶質シリコンを示す480cm<sup>-1</sup>の間に微結晶シリコンのラマンスペクトルのピークがある。さらに、He、Ar、Kr、またはNeなどの希ガス元素を含ませて格子歪みをさらに助長させることで、安定性の高い微結晶シリコンが得られる。

#### 【0043】

キャリア移動度が低いシリコン膜としては、アモルファスシリコン膜を用いればよいが、好ましくは、非晶質シリコンと微小シリコン結晶粒を有し、従来の非晶質シリコン膜と比較して、一定光電流法（CPM：Constant Photocurrent Method）やフォトルミネッセンス分光測定で測定されるUrbach端のエネルギーが小さく、欠陥吸収スペクトル量が少ないシリコン膜であるとよい。このようなシリコン膜は、従来の非晶質シリコン膜と比較して欠陥が少なく、価電子帯のバンド端（移動度端）における準位のテイル（裾）の傾きが急峻である秩序性が高い。

#### 【0044】

キャリア移動度が低いシリコン膜には、ハロゲンまたは窒素を含んでいてもよい。窒素が含まれる場合には、NH<sub>2</sub>基として含んでいてもよい。

#### 【0045】

なお、ここで、キャリア移動度が高いシリコン膜とキャリア移動度が低いシリコン膜の界面領域は、微結晶半導体領域、及び当該微結晶半導体領域の間に充填される非晶質半導体領域を有する。具体的には、キャリア移動度が高いシリコン膜から錐形状に伸びた微結晶半導体領域と、キャリア移動度が低いシリコン膜と同様の「非晶質半導体を含む領域」と、で構成される。

#### 【0046】

キャリア移動度が低いシリコン膜が、ソース電極及びドレイン電極とキャリア移動度が高いシリコン膜の間に設けられると、トランジスタのオフ電流を小さくすることができる

10

20

30

40

50

。また、上記の界面領域において、錐形状に伸びた微結晶シリコン領域を有するため、縦方向（膜の成長方向）の抵抗を低くすることができ、トランジスタのオン電流を高めることができる。すなわち、従来の非晶質シリコンを適用した場合と比較すると、オフ電流を十分に低減させつつ、オン電流の低下を抑制することもでき、トランジスタのスイッチング特性を高くすることができる。

#### 【0047】

なお、微結晶シリコン領域は、キャリア移動度が高いシリコン膜の表面から厚さ方向に成長するが、原料ガスにおいて堆積性ガス（例えば、シラン）に対する水素の流量が小さい場合（すなわち、希釈率が低い場合）、または窒素を含む原料ガスの濃度が高い場合には、微結晶シリコン領域における結晶成長が抑制され、結晶粒が錐形状になり、堆積されて形成されるシリコンは、大部分が非晶質シリコンとなる。

10

#### 【0048】

第2の導電膜110は、例えば、スパッタリング法またはCVD法（プラズマCVD法または熱CVD法などを含む。）などを用いて形成すればよい。または、インクジェット法などを用いて形成してもよい。なお、第2の導電膜110は、単層で形成してもよいし、複数の層を積層して形成してもよい。例えば、T1層上にA1層が設けられた2層の積層構造とすればよい。

#### 【0049】

マスク膜112は、後の第1のエッティング工程及び第3のエッティング工程でエッティングされない（されにくい）材料により形成すればよい。マスク膜112として、例えば、酸化シリコン膜または窒化シリコン膜などの絶縁膜を用いることができる。または、マスク膜112として、例えば、金属膜を用いることができる。金属膜を用いた場合には、電極層の一部として用いることができる。

20

#### 【0050】

第1のレジストマスク114は、レジスト材料をマスク膜112上に塗布するなどして形成した後に、フォトリソグラフィ法により加工して形成する。

#### 【0051】

次に、第1のレジストマスク114を用いてマスク膜112をドライエッティングまたはウエットエッティングすることで第1のマスク層116を形成する（図1（B））。本実施の形態において、この工程を第1のエッティング工程と呼ぶ。

30

#### 【0052】

ここで、第1のエッティング工程は、第2の導電膜110のエッティングレートが小さく、マスク膜112のエッティングレートが大きい条件により行えばよい。すなわち、第1のエッティング工程は、第2の導電膜110に対するマスク膜112のエッティング選択比が高い条件により行えばよい。

#### 【0053】

次に、第1のレジストマスク114を除去する（図1（C）、図7）。

#### 【0054】

次に、第1のマスク層116を用いて、第2の導電膜110、半導体膜108及び第1の絶縁膜106をドライエッティングすることで、薄膜積層体118を形成する（図1（D）、図8）。本実施の形態において、この工程を第2のエッティング工程と呼ぶ。

40

#### 【0055】

ここで、第2のエッティング工程は、第1のマスク層116のエッティングレートが小さく、第2の導電膜110、半導体膜108及び第1の絶縁膜106のエッティングレートが大きい条件により行えばよい。すなわち、第2のエッティング工程は、第1のマスク層116に対する第2の導電膜110、半導体膜108及び第1の絶縁膜106のエッティング選択比が高い条件により行えばよい。なお、第2のエッティング工程は、複数の種類の膜をエッティングするため、複数回の工程（例えば、2段階または3段階）で行うことが好ましい。

#### 【0056】

例えば、第2のエッティング工程は、まず、Cl<sub>2</sub>ガスとCF<sub>4</sub>ガスとO<sub>2</sub>ガスの混合ガ

50

スでエッティングを行う第1の工程と、C<sub>1</sub><sub>2</sub>ガスによりエッティングを行う第2の工程と、C<sub>H</sub>F<sub>3</sub>ガスによりエッティングを行う第3の工程と、により行えばよい。

#### 【0057】

ここで、第1のマスク層116を除去してもよい。第1のマスク層116を除去するには、薄膜積層体118が有する半導体領域に水分が触れない手段（例えば、ドライエッティング処理）を適用する。

#### 【0058】

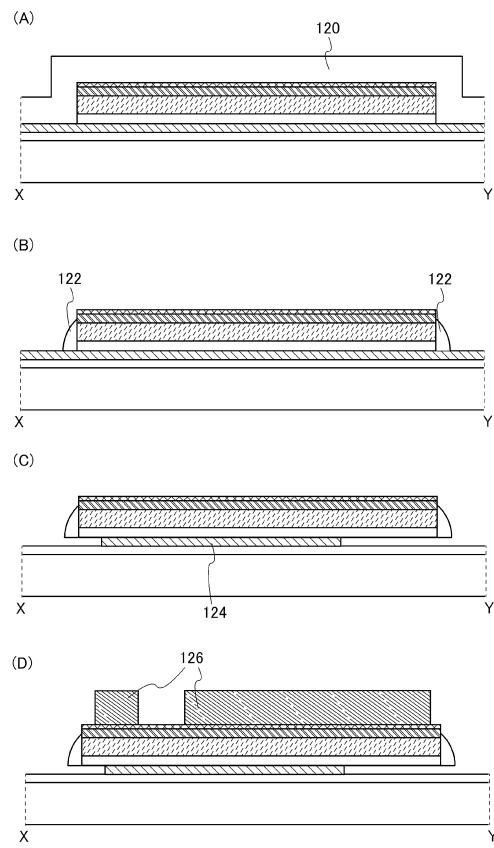

次に、薄膜積層体118を覆ってサイドウォール絶縁膜120をスパッタリング法またはCVD法（プラズマCVD法または熱CVD法などを含む。）などにより形成する（図2（A））。

10

#### 【0059】

なお、サイドウォール絶縁膜120は、第1の絶縁膜106と同じ材料で形成することが好ましい。薄膜積層体118と、後に形成されるサイドウォール絶縁層122の密着性を高めるためである。

#### 【0060】

または、サイドウォール絶縁膜120を形成した後に加熱処理を行ってもよい。薄膜積層体118と、後に形成されるサイドウォール絶縁層122の密着性を高めるためである。

#### 【0061】

次に、サイドウォール絶縁膜120をエッチバック処理することで、少なくとも薄膜積層体118が有する半導体領域の側面のすべてを覆ってサイドウォール絶縁層122を形成する（図2（B））。ここで、エッチバック処理は、第1のマスク層116または薄膜積層体118が有する導電領域が露出されるまで行う。

20

#### 【0062】

次に、第1の導電膜104の一部にサイドエッティングを伴うウエットエッティングまたはドライエッティングを行って第1の電極層124を形成する（図2（C）、図9）。

#### 【0063】

第1の電極層124を形成するエッティング工程では、下地絶縁層102及びサイドウォール絶縁層122がエッティングされず、薄膜積層体118の導電領域（第2の導電膜110により形成される領域）が露出している場合には該領域がエッティングされず、第1の導電膜104がサイドエッティングされる必要がある。従って、例えば、第1の導電膜104としてAl膜またはMo膜を形成し、第2の導電膜110としてTi膜またはW膜を形成し、エッチャントとしては硝酸、酢酸及びリン酸を含む薬液を用いればよい。または、第1の導電膜104としてMo膜を形成し、第2の導電膜110としてTi膜、Al膜またはW膜を形成し、エッチャントとしては過酸化水素水を含む薬液を用いればよい。

30

#### 【0064】

次に、第1のマスク層116上に第2のレジストマスク126を形成する（図2（D）、図10）。

#### 【0065】

第2のレジストマスク126は、レジスト材料を第1のマスク層116上に塗布するなどして形成した後に、フォトリソグラフィ法により加工して形成する。

40

#### 【0066】

または、ここまででの工程で第1のマスク層116が除去されている場合には、少なくとも薄膜積層体118上に第2のマスク膜（図示しない。）を形成し、該第2のマスク膜上に第2のレジストマスク126を形成する。

#### 【0067】

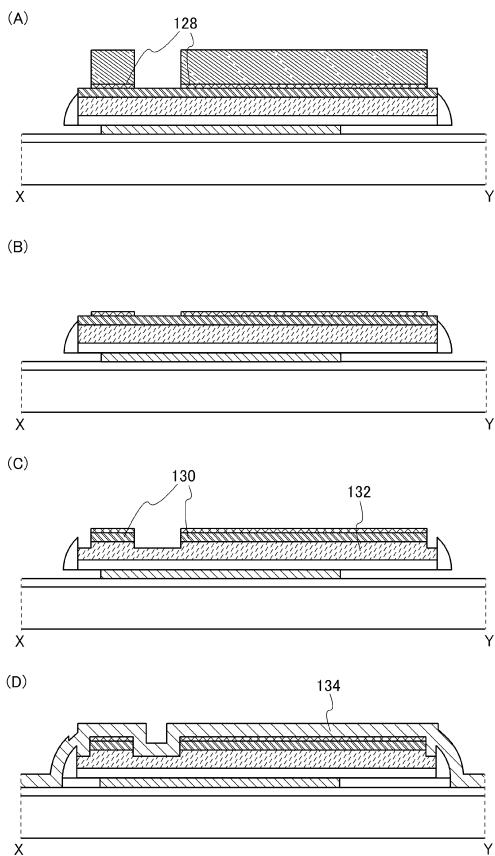

次に、第2のレジストマスク126を用いて第1のマスク層116または第2のマスク膜（図示しない。）をドライエッティングまたはウエットエッティングすることで、第2のマスク層128を形成する。本実施の形態において、この工程を第3のエッティング工程と呼ぶ（図3（A）、図11）。

50

**【0068】**

ここで、第3のエッティング工程は、少なくとも第2の導電膜110、サイドウォール絶縁層122及び第1の絶縁膜106のエッティングレートが小さく、マスク膜112のエッティングレートが大きい条件により行えばよい。すなわち、第3のエッティング工程は、第2の導電膜110、サイドウォール絶縁層122及び第1の絶縁膜106に対するマスク膜112のエッティング選択比が高い条件により行えばよい。

**【0069】**

次に、第2のレジストマスク126を除去する(図3(B)、図12)。

**【0070】**

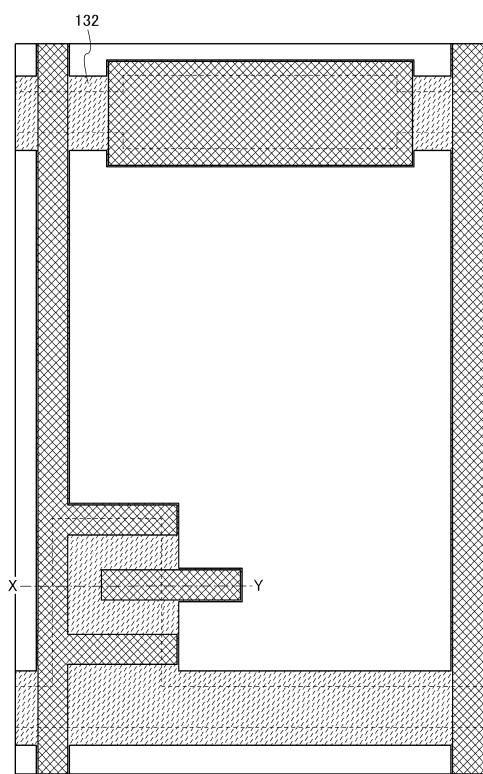

次に、第2のマスク層128を用いて薄膜積層体118が有する導電領域をドライエッティングすることで、第2の電極層130を形成する。本実施の形態において、この工程を第4のエッティング工程と呼ぶ(図3(C)、図13)。なお、この工程により、薄膜積層体118の第2の電極層130と重畠していない部分の半導体領域の上部がエッティングされ、半導体層132が形成される。

10

**【0071】**

ここで、第4のエッティング工程は、半導体膜108のエッティングレートが小さく、第2の導電膜110のエッティングレートが大きい条件により行えばよい。すなわち、第4のエッティング工程は、半導体膜108に対する第2の導電膜110のエッティング選択比が高い条件により行えばよい。

**【0072】**

20

なお、図示していないが、この後に第2のマスク層128を除去してもよい。第2のマスク層128を除去するには、薄膜積層体118が有する半導体領域に水分が触れない手段(例えば、ドライエッティング処理)を適用する。

**【0073】**

以上説明した半導体装置の作製方法では、各種薄膜の材料とエッティング工程に用いるガスまたはエッチャントの組み合わせに注意を要する。

**【0074】**

例えば、半導体膜108がIn-Ga-Zn-O系酸化物半導体膜であり、第2の導電膜110がTi膜であり、マスク膜112が酸化アルミニウム膜である場合には、第1のエッティング工程及び第3のエッティング工程には、エッチャントとして、リン酸、酢酸、硝酸、純水を(一例として、85:5:5:5の体積比)混合させた薬液を用いればよく、第2のエッティング工程には、C1系ガスを用いればよく、第4のエッティング工程には、F系ガスを用いればよい。または、第4のエッティング工程は、C1系ガスによるエッティングとF系ガスによるエッティングの2段階の工程で行ってもよい。

30

**【0075】**

または、半導体膜108がIn-Ga-Zn-O系酸化物半導体膜であり、第2の導電膜110がTi膜であり、マスク膜112が酸化シリコン膜である場合には、第1のエッティング工程及び第3のエッティング工程には、エッチャントとして、フッ酸を用いればよい。このとき、第2のエッティング工程には、C1系ガスを用いればよく、第4のエッティング工程には、F系ガスを用いればよい。または、第4のエッティング工程は、C1系ガスによるエッティングとF系ガスによるエッティングの2段階の工程で行ってもよい。

40

**【0076】**

なお、C1系ガスとしては、CCl<sub>4</sub>ガス、SiCl<sub>4</sub>ガス、BCl<sub>3</sub>ガス及びCl<sub>2</sub>ガスが挙げられる。特に好ましくはBCl<sub>3</sub>ガスとCl<sub>2</sub>ガスの混合ガスを用いる。

**【0077】**

なお、F系ガスとしては、CF<sub>4</sub>ガス、SF<sub>6</sub>ガス、NF<sub>3</sub>ガス、CBrF<sub>3</sub>ガス、CF<sub>3</sub>SO<sub>3</sub>Hガス、及びC<sub>3</sub>F<sub>8</sub>ガスが挙げられる。特に好ましくはSF<sub>6</sub>ガスを用いる。

**【0078】**

なお、サイドウォール絶縁層122は積層構造であってもよい。このとき、薄膜積層体

50

118 の側面に接する内側のサイドウォール絶縁層として、例えば酸化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層または窒化シリコン層をスパッタリング法またはCVD法（プラズマCVD法または熱CVD法などを含む。）により形成し、外側のサイドウォール絶縁層として、例えば酸化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層または窒化シリコン層をスパッタリング法またはCVD法（プラズマCVD法または熱CVD法などを含む。）により形成すればよい。好ましくは、内側のサイドウォール絶縁層として、酸化シリコン層をスパッタリング法により形成し、外側のサイドウォール絶縁層として、例えば窒化シリコン層をプラズマCVD法により形成すると、薄膜積層体118の半導体領域への水素の含有量を少なくすることができ、薄膜積層体118の半導体領域に水素及び水分が侵入しにくくバリア性の高いサイドウォール絶縁層を形成することができる。更には、半導体膜108を酸化物半導体膜とした場合に、酸化物半導体層に接する部分を酸化シリコン層とすることで、酸化物半導体層に酸素を供給することができる。

10

#### 【0079】

次に、上記のとおり作製した半導体装置を覆って保護絶縁膜134を形成する（図3（D））。

#### 【0080】

保護絶縁膜134は、第1の絶縁膜106と同様に、絶縁性材料により形成すればよい。なお、単層で形成してもよいし、複数の層を積層して形成してもよい。ここでは、例えば窒化シリコンまたは酸化アルミニウムにより形成すればよい。

#### 【0081】

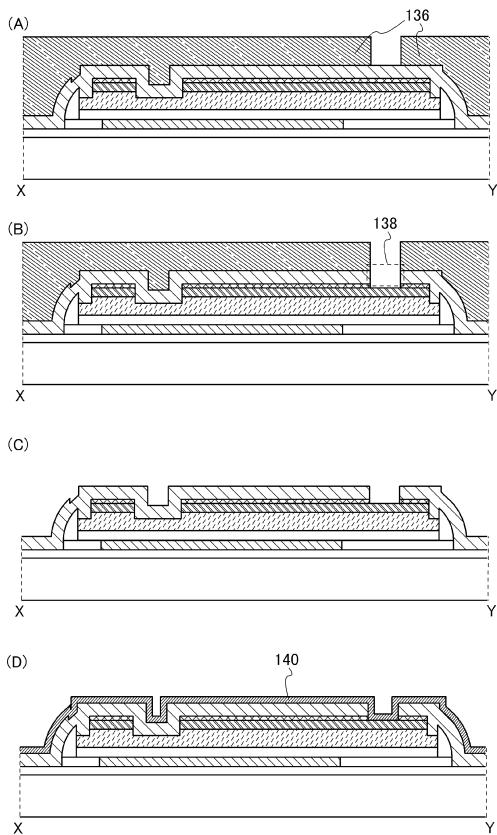

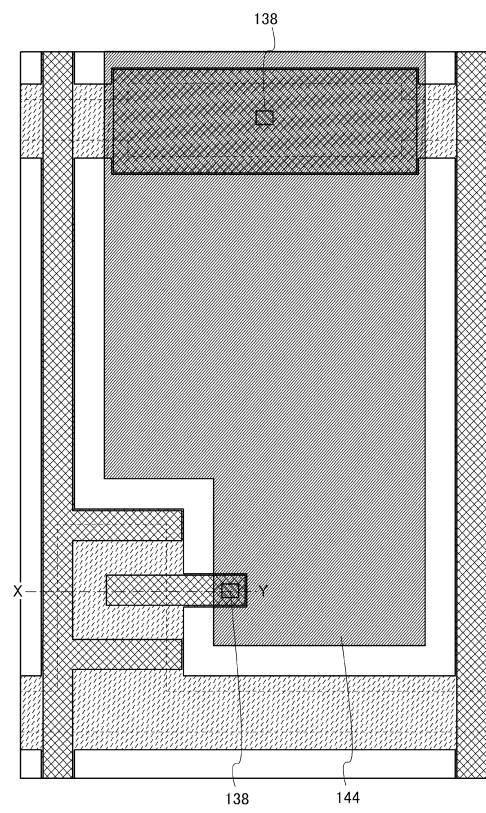

次に、保護絶縁膜134上に第3のレジストマスク136を形成し（図4（A））、保護絶縁膜134の第2の電極層130と重畠する部分に開口部138を形成する（図4（B））。その後、第3のレジストマスク136を除去する（図4（C））。なお、図示していないが、第2のマスク層128が導電性材料により形成されている場合には、開口部138の形成の際に第2のマスク層128を除去しなくてよい。

20

#### 【0082】

なお、保護絶縁膜134を形成する前に第2のマスク層128が除去されている場合には、開口部138を形成する際のエッチング量を少なくすることができる。

#### 【0083】

次に、開口部138を介して第2の電極層130と接続されるように、保護絶縁膜134上に画素電極層144を位置選択的に形成する（図5（C））。本実施の形態では、一例として、保護絶縁膜134上に第3の導電膜140を形成し（図4（D））、第3の導電膜140上に第4のレジストマスク142を形成する（図5（A））。そして、第3の導電膜140をエッチングすることで、画素電極層144が形成される（図5（B））。その後、第4のレジストマスク142を除去する（図5（C）、図14）。

#### 【0084】

ただし、これに限定されず、開口部138を介して第2の電極層130と接続されるように、保護絶縁膜134上にインクジェット法により画素電極層144を位置選択的に形成してもよい。

#### 【0085】

第3の導電膜140は、透明導電膜とすることができる。透明導電膜は、透光性を有する導電性高分子（導電性ポリマーともいう。）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した透明導電膜は、シート抵抗が10000 /以下であり、且つ波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

#### 【0086】

なお、導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、またはアニリン、ピロール及びチオフェンの2種以上の共重合

40

10

20

30

40

50

体またはその誘導体などが挙げられる。

【0087】

透明導電膜は、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITOと示す。）、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物などを用いて形成することもできる。

【0088】

以上説明したように、本実施の形態にて説明した半導体装置は、例えば、液晶表示装置の画素トランジスタに適用することができる。ただし、これに限定されず、本実施の形態の作製方法をEL表示装置に適用してもよい。

10

【0089】

(実施の形態2)

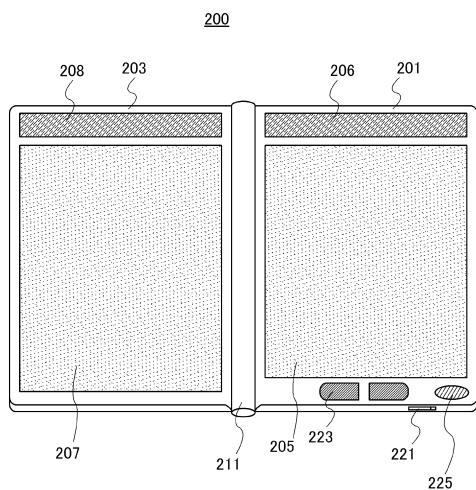

本発明の一態様である半導体装置としては、電子ペーパーが挙げられる。電子ペーパーは、情報を表示するものであればあらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍（電子ブック）、ポスター、デジタルサイネージ、P I D（P u b l i c I n f o r m a t i o n D i s p l a y）、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示等に適用することができる。電子機器の一例を図15に示す。

【0090】

図15は、電子書籍の一例を示している。例えば、電子書籍200は、筐体201および筐体203の2つの筐体で構成されている。筐体201および筐体203は、軸部211により一体とされており、該軸部211を軸として開閉動作を行うことができる。このような構成により、紙の書籍と同様に取り扱うことが可能となる。

20

【0091】

筐体201には表示部205及び光電変換装置206が組み込まれ、筐体203には表示部207及び光電変換装置208が組み込まれている。表示部205及び表示部207は、継ぎ画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部（図15では表示部205）に文章を表示し、左側の表示部（図15では表示部207）に画像を表示することができる。

30

【0092】

また、図15では、筐体201に操作部などを備えた例を示している。例えば、筐体201において、電源221、操作キー223、スピーカ225などを備えている。操作キー223により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやボイントティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、U S B端子、またはA CアダプタおよびU S Bケーブルなどの各種ケーブルと接続可能な端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍200は、電子辞書としての機能を持たせた構成としてもよい。

【0093】

また、電子書籍200は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

40

【0094】

実施の形態1で説明した半導体装置の作製方法を適用することで、半導体装置に設けられる半導体層となる部分の全面が水分などに曝されず、簡略な工程で本実施の形態の半導体装置を作製することができる。

【0095】

(実施の形態3)

本発明の一態様である半導体装置としては、電子ペーパー以外にもさまざまな電子機器（遊技機も含む）が挙げられる。電子機器としては、例えば、テレビジョン装置（テレビ

50

、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

#### 【0096】

図16(A)は、テレビジョン装置の一例を示している。テレビジョン装置300は、筐体301に表示部303が組み込まれている。表示部303により、映像を表示することが可能である。また、ここでは、スタンド305により筐体301を支持した構成を示している。

#### 【0097】

テレビジョン装置300の操作は、筐体301が備える操作スイッチや、別体のリモコン操作機310により行うことができる。リモコン操作機310が備える操作キー309により、チャンネルや音量の操作を行うことができ、表示部303に表示される映像を操作することができる。また、リモコン操作機310に、当該リモコン操作機310から出力する情報を表示する表示部307を設ける構成としてもよい。

#### 【0098】

なお、テレビジョン装置300は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

#### 【0099】

図16(B)は、デジタルフォトフレームの一例を示している。例えば、デジタルフォトフレーム320は、筐体321に表示部323が組み込まれている。表示部323は、各種画像を表示することができ、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

#### 【0100】

なお、デジタルフォトフレーム320は、操作部、外部接続用端子(USB端子、USBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体插入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体插入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部323に表示させることができる。

#### 【0101】

また、デジタルフォトフレーム320は、無線で情報を送受信できる構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

#### 【0102】

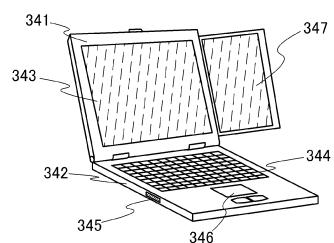

図17は携帯型のコンピュータの一例を示す斜視図である。

#### 【0103】

図17の携帯型のコンピュータは、上部筐体341と下部筐体342とを接続するヒンジユニットを閉状態として表示部343を有する上部筐体341と、キーボード344を有する下部筐体342とを重ねた状態とすることができます、持ち運ぶことが便利であるとともに、使用者がキーボード入力する場合には、ヒンジユニットを開状態として、表示部343を見て入力操作を行うことができる。

#### 【0104】

また、下部筐体342はキーボード344の他に入力操作を行うポインティングデバイス346を有する。また、表示部343をタッチ入力パネルとすれば、表示部の一部に触れることで入力操作を行うこともできる。また、下部筐体342はCPUやハードディスク等の演算機能部を有している。また、下部筐体342は他の機器、例えばUSBの通信規格に準拠した通信ケーブルが差し込まれる外部接続ポート345を有している。

#### 【0105】

10

20

30

40

50

上部筐体341には更に上部筐体341内部にスライドさせて収納可能な表示部347を有しており、広い表示画面を実現することができる。また、収納可能な表示部347の画面の向きを使用者は調節できる。また、収納可能な表示部347をタッチ入力パネルとすれば、収納可能な表示部の一部に触れることで入力操作を行うこともできる。

#### 【0106】

表示部343または収納可能な表示部347は、液晶表示パネル、有機発光素子または無機発光素子などの発光表示パネルなどの映像表示装置を用いる。

#### 【0107】

また、図17の携帯型のコンピュータは、受信機などを備えた構成として、テレビ放送を受信して映像を表示部に表示することができる。また、上部筐体341と下部筐体342とを接続するヒンジユニットを閉状態としたまま、表示部347をスライドさせて画面全面を露出させ、画面角度を調節して使用者がテレビ放送を見ることもできる。この場合には、ヒンジユニットを閉状態として表示部343を表示せず、さらにテレビ放送を表示するだけの回路の起動のみを行うため、最小限の消費電力とすることことができ、バッテリー容量の限られている携帯型のコンピュータにおいて有用である。10

#### 【0108】

実施の形態1で説明した半導体装置の作製方法を適用することで、半導体装置に設けられる半導体層となる部分の全面が水分などに曝されず、簡略な工程で本実施の形態の半導体装置を作製することができる。

#### 【符号の説明】

#### 【0109】

|     |            |    |

|-----|------------|----|

| 100 | 基板         | 20 |

| 102 | 下地絶縁層      |    |

| 104 | 第1の導電膜     |    |

| 106 | 第1の絶縁膜     |    |

| 108 | 半導体膜       |    |

| 110 | 第2の導電膜     |    |

| 112 | マスク膜       |    |

| 114 | 第1のレジストマスク |    |

| 116 | 第1のマスク層    |    |

| 118 | 薄膜積層体      |    |

| 120 | サイドウォール絶縁膜 |    |

| 122 | サイドウォール絶縁層 |    |

| 124 | 第1の電極層     |    |

| 126 | 第2のレジストマスク |    |

| 128 | 第2のマスク層    |    |

| 130 | 第2の電極層     |    |

| 132 | 半導体層       |    |

| 134 | 保護絶縁膜      |    |

| 136 | 第3のレジストマスク | 30 |

| 138 | 開口部        |    |

| 140 | 第3の導電膜     |    |

| 142 | 第4のレジストマスク |    |

| 144 | 画素電極層      |    |

| 200 | 電子書籍       |    |

| 201 | 筐体         |    |

| 203 | 筐体         |    |

| 205 | 表示部        |    |

| 206 | 光電変換装置     |    |

| 207 | 表示部        |    |

40

50

|       |             |    |

|-------|-------------|----|

| 2 0 8 | 光電変換装置      |    |

| 2 1 1 | 軸部          |    |

| 2 2 1 | 電源          |    |

| 2 2 3 | 操作キー        |    |

| 2 2 5 | スピーカ        |    |

| 3 0 0 | テレビジョン装置    |    |

| 3 0 1 | 筐体          |    |

| 3 0 3 | 表示部         |    |

| 3 0 5 | スタンド        | 10 |

| 3 0 7 | 表示部         |    |

| 3 0 9 | 操作キー        |    |

| 3 1 0 | リモコン操作機     |    |

| 3 2 0 | デジタルフォトフレーム |    |

| 3 2 1 | 筐体          |    |

| 3 2 3 | 表示部         |    |

| 3 4 1 | 上部筐体        |    |

| 3 4 2 | 下部筐体        |    |

| 3 4 3 | 表示部         |    |

| 3 4 4 | キーボード       |    |

| 3 4 5 | 外部接続ポート     | 20 |

| 3 4 6 | ポインティングデバイス |    |

| 3 4 7 | 表示部         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特開平03-011744(JP,A)

特開2009-231828(JP,A)

特開2010-199570(JP,A)

国際公開第2010/098101(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786