(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-293813

(P2005-293813A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

**G 11 C 16/06**

G 11 C 17/00

6 3 3 B

5 B 1 2 5

**G 11 C 16/04**

H 01 L 27/10

4 8 1

5

F 0 8 3

**H 01 L 21/8247**

H 01 L 27/10

4 3 4

5 F 1 0 1

**H 01 L 27/10**

H 01 L 29/78

3 7 1

**H 01 L 27/115**

G 11 C 17/00

6 2 2 E

審査請求 未請求 請求項の数 12 O L (全 14 頁) 最終頁に続く

(21) 出願番号

特願2004-192821 (P2004-192821)

(22) 出願日

平成16年6月30日 (2004.6.30)

(31) 優先権主張番号

2004-22677

(32) 優先日

平成16年4月1日 (2004.4.1)

(33) 優先権主張国

韓国 (KR)

(71) 出願人

591024111

株式会社ハイニックスセミコンダクター

大韓民国京畿道利川市夫鉢邑牙美里山13

6-1

(74) 代理人

100066784

弁理士 中川 周吉

(74) 代理人

100095315

弁理士 中川 裕幸

(72) 発明者

季熙烈

大韓民国 京畿道 利川市 夫鉢邑 牙美

里 現代3次アパートメント 302-8

12

F ターム(参考) 5B125 BA02 CA15 DA09 EA05 EC06

FA05 FA06

最終頁に続く

(54) 【発明の名称】 N A N D フラッシュメモリ素子及びその読み取り方法

## (57) 【要約】

【課題】 N A N D フラッシュメモリ素子及びその読み取り方法を提供すること。【解決手段】 本発明は、ローカルストリング選択信号によって複数のビットライン信号を伝送するストリング選択部と、ローカルソース選択信号によって共通ソースライン信号を伝送するソース選択部と、複数のビットライン信号、共通ソースライン信号及び複数のローカルワードライン信号によって所定のデータを格納するセルストリング部とを含むセルブロックと、動作信号によってグローバルストリング選択信号、グローバルソース選択信号及び複数のグローバルワードライン信号をそれぞれ前記ローカルストリング選択信号、前記ローカルソース選択信号及び前記複数のローカルワードライン信号に伝送する X デコーダ部と、所定の制御信号によって前記ローカルストリング選択信号及び前記ローカルソース選択信号に接地電源信号を印加するスイッチ部とを備える。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

ローカルストリング選択信号によって複数のビットライン信号を伝送するストリング選択部と、ローカルソース選択信号によって共通ソースライン信号を伝送するソース選択部と、複数のビットライン信号、共通ソースライン信号及び複数のローカルワードライン信号によって所定のデータを格納するセルストリング部とを含むセルブロックと、

動作信号によってグローバルストリング選択信号、グローバルソース選択信号及び複数のグローバルワードライン信号をそれぞれ前記ローカルストリング選択信号、前記ローカルソース選択信号及び前記複数のローカルワードライン信号に伝送するXデコーダ部と、

所定の制御信号によって前記ローカルストリング選択信号及び前記ローカルソース選択信号に接地電源信号を印加するスイッチ部と

を備えることを特徴とするNANDフラッシュメモリ素子。

**【請求項 2】**

前記スイッチ部は、

前記制御信号によってそれぞれ前記ローカルストリング選択信号に接地電源を伝送するストリング放電トランジスタと、

前記ローカルソース選択信号に接地電源を伝送するソース放電トランジスタと

を備えることを特徴とする請求項1に記載のNANDフラッシュメモリ素子。

**【請求項 3】**

選択された前記セルブロックと接続した前記スイッチ部に印加する前記制御信号はロジックローであり、選択されない前記セルブロックと接続した前記スイッチ部に印加する前記制御信号はロジックハイであることを特徴とする請求項2に記載のNANDフラッシュメモリ素子。

**【請求項 4】**

読み出し動作信号によって前記ビットラインに検出電圧を印加し、前記検出電圧の状態によってセルのプログラム及び消去状態をセンシングするページバッファ部をさらに備えることを特徴とする請求項1に記載のNANDフラッシュメモリ素子。

**【請求項 5】**

前記セルブロックは、

複数のビットラインにそれぞれ接続され前記ローカルストリング選択信号によって前記ビットライン信号を伝送する複数のストリング選択トランジスタと、

共通ソースラインに接続され前記ローカルソース選択信号によって前記共通ソースライン信号を伝送する複数のソース選択トランジスタと、

直列接続された複数のセルが前記複数のストリング選択トランジスタと前記複数のソース選択トランジスタとの間にそれぞれ接続された複数のセルストリングを含み、複数のセルストリング内の同一位置にある前記セルのゲート各々にローカルワードラインが接続され前記複数のビットライン信号、前記共通ソースライン信号及び前記複数のローカルワードライン信号によって所定のデータを格納したり消去することを特徴とする請求項1に記載のNANDフラッシュメモリ素子。

**【請求項 6】**

前記Xデコーダ部は、

前記動作信号によってそれぞれ前記グローバルストリング選択信号を前記ローカルストリング選択信号に伝送するストリング传送トランジスタと、

前記グローバルソース選択信号を前記ローカルソース選択信号に伝送するソース传送トランジスタと、

前記複数のグローバルワードライン信号を前記複数のローカルワードライン信号に伝送する複数のワードライン传送トランジスタと

を備えることを特徴とする請求項1に記載のNANDフラッシュメモリ素子。

**【請求項 7】**

少なくとも2個以上の前記セルブロックの前記ソース選択部に同じ前記ローカルソース

10

20

30

40

50

選択信号が印加されるように、前記セルブロック間の前記ソース選択部を電気的に接続することを特徴とする請求項1に記載のNANDフラッシュメモリ素子。

**【請求項8】**

前記セルブロックの前記ソース選択部にそれぞれ独立された前記ローカルソース選択信号が印加されるように、前記セルブロックの前記ソース選択部を電気的に分離することを特徴とする請求項1に記載のNANDフラッシュメモリ素子。

**【請求項9】**

複数のビットラインに接続された複数のストリング選択トランジスタと共に通ソースラインに接続された複数のソース選択トランジスタとの間に直列接続された複数のセルストリングと、前記複数のストリング選択トランジスタのゲート端子に接続されたローカルストリング選択ラインと、前記複数のソース選択トランジスタのゲート端子に接続されたローカルソース選択ライン及び前記セルストリング内のセル各々のゲート端子に接続された複数のローカルワードラインとを含む複数のセルブロックと、10

それぞれ動作電圧によって駆動しグローバルストリング選択ラインと前記ローカルストリング選択ラインとに接続されたストリング伝送トランジスタと、グローバルソース選択ラインと前記ローカルソース選択ラインとに接続されたソース伝送トランジスタ、複数のグローバルワードラインと前記複数のローカルワードラインとに接続された複数のワードライン伝送トランジスタとを含むXデコーダ部と、10

それぞれ制御電圧によって駆動し接地電源と前記ローカルストリング選択ラインとに接続されたストリング放電トランジスタと、接地電源と前記ローカルソース選択ラインとに接続されたソース放電トランジスタとを含むスイッチ部と、20

読み出し動作信号によって前記ビットラインに検出電圧を印加し、前記検出電圧の状態によってセルのプログラム及び消去状態を判断するページバッファ部と

を備えるNANDフラッシュメモリ素子の読み取り方法において、20

前記Xデコーダ部にグローバルストリング選択電圧、グローバルソース選択電圧及び選択されない複数のワードラインにはバス電圧を印加し、選択されたワードラインには読み出し電圧を印加し、選択された前記セルブロックと接続された前記Xデコーダ部にロジックハイの動作電圧を印加し、選択されない前記セルブロックと接続された前記Xデコーダ部にロジックローの動作電圧を印加するステップと、30

選択された前記セルブロックと接続された前記スイッチ部にロジックローの制御電圧を印加し、選択されない前記セルブロックと接続された前記スイッチ部にロジックハイの制御電圧を印加するステップと、30

前記共通ソースラインとバルクとに接地電圧を印加し、前記ページバッファを介して選択された前記ビットラインに検出電圧を印加した後、前記検出電圧の変化をセンシングするステップと

を備えることを特徴とするNANDフラッシュメモリ素子の読み取り方法。

**【請求項10】**

前記グローバルストリング選択電圧、前記グローバルソース選択電圧及び前記バス電圧として4.0ないし5.0Vの電圧を使用し、前記読み出し電圧として接地電圧を使用することを特徴とする請求項9に記載のNANDフラッシュメモリ素子の読み取り方法。40

**【請求項11】**

選択された前記セルブロックと接続された前記Xデコーダ部に印加されるロジックハイの動作電圧として4.0V+2Vtないし5.0V+2Vt電圧を使用し、選択されない前記セルブロックと接続された前記Xデコーダ部に印加されるロジックローの動作電圧として接地電圧を使用することを特徴とする請求項9に記載のNANDフラッシュメモリ素子の読み取り方法。

**【請求項12】**

前記選択されたセルブロックと接続した前記スイッチ部に印加する前記制御電圧はロジックローであり、前記選択されないセルブロックと接続した前記スイッチ部に印加する前記制御電圧はロジックハイであることを特徴とする請求項9に記載のNANDフラッシュ50

メモリ素子の読み取り方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、NANDフラッシュメモリ素子及びその読み取り方法に関し、特に、素子の漏れ電流を減少させることのできるNANDフラッシュメモリ素子に関する。

【背景技術】

【0002】

NAND型フラッシュ素子は、ドレイン選択トランジスタとソース選択トランジスタとの間に16個または32個単位でセルがストリング(STRING)形態で直列接続している。同一ワードラインを共有しているセルストリングをグループ化して一つのブロックと定義する。10

【0003】

ブロックに印加される電圧の状態によって、読み出し動作のために選択されたブロックと選択されないブロックとに分けられる。

【0004】

まず、読み出し動作時選択されたブロックに印加される電圧状態を述べると、Xデコーダを介して選択されたワードラインには0Vを印加し、パスワードライン、ドレイン選択トランジスタ及びソース選択トランジスタには4.5Vの電圧を印加する。共通ソースラインとバルクとには0Vを印加し、ビットラインには1Vの電圧を印加する。20

【0005】

次に、選択されないブロックを述べると、Xデコーダを介して全体ワードライン、ドレイン選択トランジスタ及びソース選択トランジスタをフローティングさせる。ソース選択トランジスタは、選択されたブロックと選択されないブロックとが電気的に接続されている。選択されないブロックのソース選択トランジスタには4.5Vの電圧が印加されることができる。共通ソースライン、バルク及びビットラインに印加される電圧状態は選択されたブロックと同じである。

【0006】

このような電圧印加時、選択されないブロックのドレイン選択トランジスタ及びソース選択トランジスタにより発生した漏れ電流により素子の動作に悪影響を及ぼしている。一般にストリング単位のNANDアレイは根本的なオン電流(On-Current)が200ないし400nA程度で非常に小さい。短いセンシングタイム(Sensing Time)を持っていくためには、選択されないブロックの漏れ電流が漏れないように制御しなければならない。30

【0007】

また、NANDフラッシュセルは接合漏れ(Junction Leakage)によるプログラムディスター(Programming Disturb)発生を防止するため、8V電圧において数pAの漏れ電流だけを許容する。したがって、ゲート長さが0.1μmのセルと0.18μmの選択トランジスタにもディップ接合(Deep Junction)構造を形成しなければならない。これにより接合部と接合部(Junction To Junction)との間の漏れ、すなわち、パンチスルー(Punch-Through)に弱い問題が発生する。40

【発明の開示】

【発明が解決しようとする課題】

【0008】

したがって、本発明は上述した問題点に鑑みてなされたものであって、その目的とするところは、読み出し動作時選択トランジスタのソースサイド抵抗を大きくして漏れ電流を減少させることのできるNANDフラッシュメモリ素子及びその読み出し方法を提供する。

【課題を解決するための手段】

10

20

30

40

50

**【 0 0 0 9 】**

本発明に係るローカルストリング選択信号によって複数のビットライン信号を伝送するストリング選択部と、ローカルソース選択信号によって共通ソースライン信号を伝送するソース選択部と、複数のビットライン信号、共通ソースライン信号及び複数のローカルワードライン信号によって所定のデータを格納するセルストリング部とを含むセルロックと、動作信号によってグローバルストリング選択信号、グローバルソース選択信号及び複数のグローバルワードライン信号をそれぞれ前記ローカルストリング選択信号、前記ローカルソース選択信号及び前記複数のローカルワードライン信号に伝送するXデコーダ部と、所定の制御信号によって前記ローカルストリング選択信号及び前記ローカルソース選択信号に接地電源信号を印加するスイッチ部とを備えるNANDフラッシュメモリ素子を提供する。

10

**【 0 0 1 0 】**

また、複数のビットラインに接続された複数のストリング選択トランジスタと共にソースラインに接続された複数のソース選択トランジスタとの間に直列接続された複数のセルストリングと、前記複数のストリング選択トランジスタのゲート端子に接続されたローカルストリング選択ラインと、前記複数のソース選択トランジスタのゲート端子に接続されたローカルソース選択ライン及び前記セルストリング内のセル各々のゲート端子に接続された複数のローカルワードラインとを含む複数のセルロックと、それぞれ動作電圧によって駆動しグローバルストリング選択ラインと前記ローカルストリング選択ラインとに接続されたストリング传送トランジスタと、グローバルソース選択ラインと前記ローカルソース選択ラインとに接続されたソース传送トランジスタ、複数のグローバルワードラインと前記複数のローカルワードラインとに接続された複数のワードライン传送トランジスタとを含むXデコーダ部と、それぞれ制御電圧によって駆動し接地電源と前記ローカルストリング選択ラインとに接続されたストリング放電トランジスタと、接地電源と前記ローカルソース選択ラインとに接続されたソース放電トランジスタとを含むスイッチ部と、読み出し動作信号によって前記ビットラインに検出電圧を印加し、前記検出電圧の状態によってセルのプログラム及び消去状態を判断するページバッファ部とを備えるNANDフラッシュメモリ素子において、前記Xデコーダ部にグローバルストリング選択電圧、グローバルソース選択電圧及び選択されない複数のワードラインにはバス電圧を印加し、選択されたワードラインには読み出し電圧を印加し、選択された前記セルロックと接続された前記Xデコーダ部にロジックハイの動作電圧を印加し、選択されない前記セルロックと接続された前記Xデコーダ部にロジックローの動作電圧を印加するステップと、選択された前記セルロックと接続された前記スイッチ部にロジックローの制御電圧を印加し、選択されない前記セルロックと接続された前記スイッチ部にロジックハイの制御電圧を印加するステップと、前記共通ソースラインとバルクとに接地電圧を印加し、前記ページバッファを介して選択された前記ビットラインに検出電圧を印加した後、前記検出電圧の変化をセンシングするステップとを備えることを特徴とするNANDフラッシュメモリ素子の読み取り方法を提供する。

20

30

**【 発明の効果 】****【 0 0 1 1 】**

上述したように、本発明は読み出し動作時、選択されないセルロックのストリング選択のためのトランジスタとソース選択のためのトランジスタとに接地電源を印加することによって、ドレイン選択ラインの抵抗を増加させてバックバイアス効果による漏れ電流を防止できる。

40

**【 0 0 1 2 】**

また、ビットライン漏れ電流が減少してプログラムされたセルと消去されたセルとの間のオン/オフ電流比が増加することになって、素子のセンシングタイムが減少し、リードトリップレンジが増加してデータ保損力及び読み出しディスターブによるしきい電圧変化を防止できる。

**【 0 0 1 3 】**

また、しきい電圧変化に対するマージンを増加させることができ、ページバッファ変化(Page Buffer Variation)に対するマージンを増加させることができる。

#### 【0014】

また、セルブロック間のソース選択トランジスタ各々を分離してソース選択ラインに独立的な電圧を印加することもでき、隣接したセルブロック間のソース選択トランジスタを電気的に接続してソース放電トランジスタの数字を低減できる。

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、添付した図面を参照して本発明の実施の形態をさらに詳細に説明する。

10

#### 【0016】

複数のフラッシュセルがストリング形態で構成されたセルストリングのようなワードラインを共有しているストリングをグループ化して一つのブロックで構成した。このようなブロックを構成している各々のストリングは、グローバルビットラインに1024、2048のような2の倍数単位で並列接続している。また、ブロック配列は、選択トランジスタを基準としてミラー(Mirror)構造で形成されているため、選択トランジスタのストリングアウトサイド接合部(Out-Side Junction)を隣接したブロックの選択トランジスタと共有している。

#### 【0017】

高度な集積化のため、データ入出力バスであるビットラインと接続したストリング選択トランジスタには、その構成上ブロックと別にストリング選択トランジスタゲートバイアスを印加することが効果的である。また、共通ソースラインと接続したソース選択トランジスタは隣接したソース選択トランジスタとゲートバイアス(Gate Bias)とを共有したり、別のゲートバイアスを印加されることが好ましい。

20

#### 【0018】

NANDフラッシュ素子の読み取り動作時、あらゆるブロックはソースラインには0Vを印加し、ビットラインには最大1.3V程度の電圧を印加する。この場合、ビットラインによる漏れ電流をほぼ無視できるが、ストリング選択トランジスタあるいはソース選択トランジスタのソース/ドレイン間漏れ電流は無視できない程度となる。また、ビットラインには1024個のストリングが並列接続しているため、漏れ電流は1024倍に増幅されて流れるようになる。

30

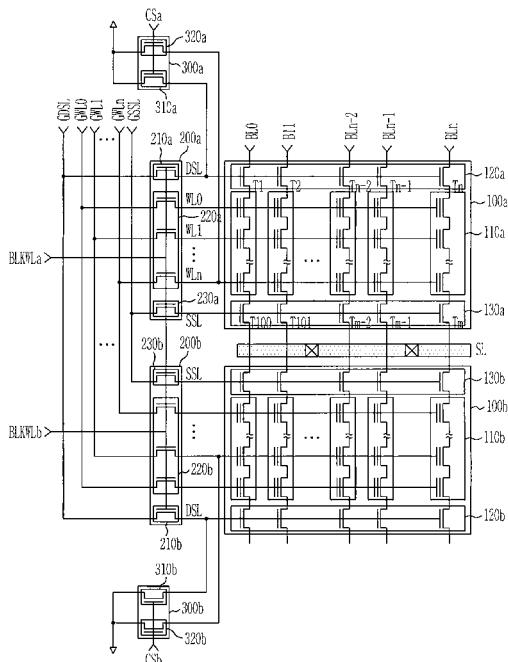

#### 【0019】

図1は、選択されないブロックのストリング選択トランジスタには0Vのゲート電圧を印加し、ソース選択トランジスタはフローティングさせた状態の概念図である。

#### 【0020】

図1を参照すれば、セルの読み取り動作時選択されないブロックのストリング選択トランジスタT1にだけ0Vのゲート電圧を印加し、ソース選択トランジスタT10とセルストリングのゲートをフローティングさせる場合は次の通りである。セルストリング内のセルが消去された状態であれば、大部分のセルが-7ないし-9V程度のしきい電圧(Vt=-9)を有する。この場合、フローティングゲートはポジティブチャージングされている。したがって、容量性カップリング(Capacitive Coupling)を考慮すれば、フローティングゲートの電位(Potential)が4.0ないし5.0V程度となって、セルのワードラインがフローティングされても事実上セルが完全にターンオンされた状態となる。

40

#### 【0021】

また、ソース選択トランジスタT10も隣接したセル、ソースライン及び半導体基板間の容量性カップリングにより約0.4ないし0.5V程度の電位を持つようになる。これによりソース選択トランジスタはほぼターンオンされた状態となる。

#### 【0022】

上述したことにより、ストリング選択トランジスタT1のソースサイドであるソース選

50

択トランジスタ T<sub>10</sub> からセルストリング全体までの直列抵抗が大きく減少するので漏れ電流が流れるようになる。したがって、セルのターンオン状態を防止できなくとも、ソース選択トランジスタのほぼターンオンされた状態のみを予防できれば、ストリング選択トランジスタのソースサイド抵抗を増加させてストリング単位の漏れ電流を減少させることができる。

#### 【 0 0 2 3 】

これに関し素子の構成とそれにともなう素子の読み取り動作に関し図面を参照して詳細に説明する。

#### 【 0 0 2 4 】

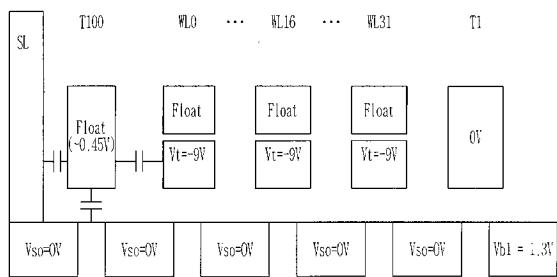

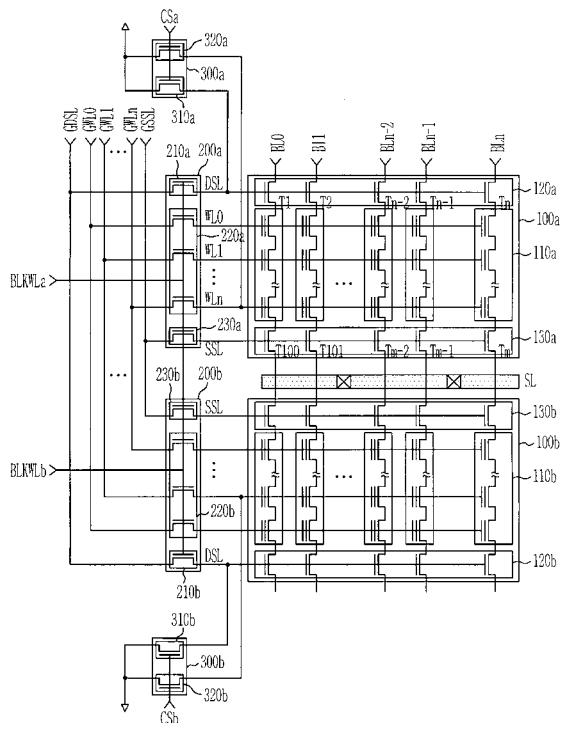

図 2 は、本発明に係る N A N D フラッシュメモリ素子の回路図である。

10

#### 【 0 0 2 5 】

図 2 を参照すれば、本発明の N A N D フラッシュメモリ素子はローカルストリング選択信号 D S L によって複数のビットライン信号 B L を伝送するストリング選択部 120 と、ローカルソース選択信号 S S L によって共通ソースライン信号 S L を伝送するソース選択部 130 と、複数のビットライン信号 B L 、共通ソースライン信号 S L 及び複数のローカルワードライン信号 W L 0 ないし W L n によって所定のデータを格納するセルストリング部 110 を含むセルブロック 100 と、動作信号 B L K W L によってグローバルストリング選択信号 G D S L 、グローバルソース選択信号 G S S L 及び複数のグローバルワードライン信号 G W L 0 ないし G W L n をそれぞれローカルストリング選択信号 D S L 、ローカルソース選択信号 S S L 及び複数のローカルワードライン信号 W L 0 ないし W L n に伝送する X デコーダ部 200 と、所定の制御信号 C S によってローカルストリング選択信号 D S L 及びローカルソース選択信号 S S L に接地電源信号を印加するスイッチ部 300 とを備える。

20

#### 【 0 0 2 6 】

読み出し動作信号(図示せず)によって前記ビットライン B L に検出電圧を印加し、前記検出電圧の状態によってセルのプログラム及び消去状態をセンシングするページバッファ部(図示せず)をさらに備えることができる。

30

#### 【 0 0 2 7 】

セルブロック 100 のストリング選択部 120 は、複数のビットライン B L にそれぞれ接続されローカルストリング選択信号 S S L によってビットライン B L 信号を伝送する複数のストリング選択トランジスタ T<sub>1</sub> ないし T<sub>n</sub> を備える。ソース選択部 130 は、共通ソースライン S L に接続されローカルソース選択信号 S S L によって共通ソースライン S L 信号を伝送する複数のソース選択トランジスタ T<sub>100</sub> ないし T<sub>m</sub> を備える。

40

#### 【 0 0 2 8 】

セルストリング部は直列接続された複数のセルが複数のストリング選択トランジスタ T<sub>1</sub> ないし T<sub>n</sub> と複数のソース選択トランジスタ T<sub>100</sub> ないし T<sub>m</sub>との間にそれぞれ接続された複数のセルストリングを含み、複数のセルストリング内の同一位置にあるセルのゲート各々にローカルワードライン W L が接続され複数のビットライン信号 B L 、共通ソースライン信号 S S L 及び複数のローカルワードライン信号 W L 0 ないし W L n によって所定のデータを格納したり消去する。

40

#### 【 0 0 2 9 】

X デコーダ部 200 は、動作信号 B L K W L によってそれぞれグローバルストリング選択信号 G D S L をローカルストリング選択信号 G S L に伝送するストリング伝送トランジスタ 210 と、グローバルソース選択信号 G S S L をローカルソース選択信号 S S L に伝送するソース伝送トランジスタ 230 と、複数のグローバルワードライン信号 G W L 0 ないし G W L m を複数のローカルワードライン信号 W L 0 ないし W L n に伝送する複数のワードライン伝送トランジスタ 220 とを備える。

#### 【 0 0 3 0 】

スイッチ部 300 は、制御信号 C S によってそれぞれローカルストリング選択信号 D S L に接地電源を伝送するストリング放電トランジスタ 310 と、ローカルソース選択信号

50

S S L に接地電源を伝送するソース放電トランジスタ 3 2 0 とを備える。

#### 【 0 0 3 1 】

この場合、隣接した前記セルブロック 1 0 0 a と 1 0 0 b の前記ソース選択部 1 3 0 a と 1 3 0 b に同じ前記ローカルソース選択信号 S S L が印加されるように、隣接した前記セルブロック間 1 0 0 a と 1 0 0 b の前記ソース選択部 1 3 0 a と 1 3 0 b を電気的に接続したり、隣接した前記セルブロック 1 0 0 a と 1 0 0 b の前記ソース選択部 1 3 0 a と 1 3 0 b にそれぞれ独立された前記ローカルソース選択信号 S S L が印加されるように、隣接した前記セルブロック間 1 0 0 a と 1 0 0 b の前記ソース選択部 1 3 0 a と 1 3 0 b を電気的に分離することができる。また、2 個以上のソース選択部 1 3 0 に同じローカルソース選択信号 S S L が印加されるように、ソース選択部 1 3 0 を電気的に接続できる。

10

#### 【 0 0 3 2 】

複数のストリング選択トランジスタ T 1 ないし T n と複数のソース選択トランジスタ T 1 0 0 ないし T m とは、N M O S トランジスタを使用することが好ましい。複数のストリング選択トランジスタ T 1 ないし T n と複数のソース選択トランジスタ T 1 0 0 ないし T m のうち、最初のトランジスタ T 1 及び T 1 0 0 らの間に複数のセルストリングのうち最初のセルストリングが接続される。複数のセルストリングのうち、最初のセルらは最初のワードライン信号 W L 0 によって動作する。セルストリング 1 1 0 に 1 6 の 2 の倍数個数ぐらいのセルが直列接続されることが好ましい。

#### 【 0 0 3 3 】

ストリング伝送トランジスタ 2 1 0 、ソース伝送トランジスタ 2 3 0 と複数のワードライン伝送トランジスタ 2 2 0 として、1 ないし 2 5 V の電圧でも動作が可能な高電圧 N M O S トランジスタを使用することが好ましい。すなわち、2 0 V 以上の接合ブレークダウン電圧を有するトランジスタを使用することが効果的である。また、上述したトランジスタとしてイオンが注入されない半導体基板上に形成されるネガティブ高電圧トランジスタを使用することが好ましい。

20

#### 【 0 0 3 4 】

ストリング放電トランジスタ 3 1 0 とソース放電トランジスタ 3 2 0 として、高電圧 N M O S トランジスタまたは一般 N M O S トランジスタを使用することが好ましい。

#### 【 0 0 3 5 】

本発明の N A N D フラッシュ素子においては、1 0 2 4 の 2 の倍数個数ぐらいのセルブロック 1 0 0 が位置していることが好ましい。また、上述したように少なくとも 2 個以上のソース選択トランジスタ間のゲート端子を一つのラインで接続することもでき、それぞれ分離されたラインで接続することもできる。ゲート端子を一つのラインで接続する場合、ソース放電トランジスタの数字を減らすことができ、それぞれ分離されたラインで接続する場合、独立的な電圧を印加できる。

30

#### 【 0 0 3 6 】

上述した構成を有する本発明において、選択されたセルブロック内の所定のセル内のデータを読み出すための過程を説明すれば次の通りである。この場合、選択されたセルブロックを図 2 の 1 0 0 a とし、選択されないセルブロックを図 1 の 1 0 0 b として説明する。

40

#### 【 0 0 3 7 】

複数のビットライン B L 0 ないし B L n に接続された複数のストリング選択トランジスタ T 1 ないし T n と共にソースライン S L に接続された複数のソース選択トランジスタ T 1 0 0 ないし T m との間に直列接続された複数のセルストリング 1 1 0 、前記複数のストリング選択トランジスタ T 1 ないし T n のゲート端子に接続されたローカルストリング選択ライン D S L 、前記複数のソース選択トランジスタ T 1 0 0 ないし T m のゲート端子に接続されたローカルソース選択ライン S S L 及び前記セルストリング 1 1 0 内のセル各々のゲート端子に接続された複数のワードライン W L 0 ないし W L n を含む複数のセルブロック 1 0 0 と、それぞれ動作電圧 B L K W L によって駆動しグローバルストリング選択ライン G D S L とローカルストリング選択ライン D S L とに接続されたストリング伝送トランジスタ 2 1 0 、グローバルソース選択ライン G S S L とローカルソース選択ライン S S

50

L とに接続されたソース伝送トランジスタ 230 及び複数のグローバルワードライン GWL 0 ないし GWLn と複数のローカルワードライン WL 0 ないし WLn とに接続された複数のワードライン伝送トランジスタ 220 を含む X デコーダ部 200 と、それぞれ制御電圧 CS によって駆動し接地電源とローカルストリング選択ライン DSL とに接続されたストリング放電トランジスタ 310 と、接地電源とローカルソース選択ライン SSL とに接続されたソース放電トランジスタ SSL を含むスイッチ部 300 と、読み出し動作信号(図示せず)によって前記ビットライン BL に検出電圧を印加し、前記検出電圧の状態によってセルのプログラム及び消去状態をセンシングするページバッファ部(図示せず)を含む NAND フラッシュメモリ素子において、X デコーダ部 200 にグローバルストリング選択電圧、グローバルソース選択電圧、選択されない複数のワードラインにはバス電圧を印加し、選択されたワードラインには読み出し電圧を印加し、選択されたセルブロック 100a と接続された X デコーダ部 200a とにロジックハイの動作電圧 BLKWL a を印加し、選択されないセルブロック 100b と接続された X デコーダ部 200b とにロジックローの動作電圧 BLKWL b を印加する。

10

#### 【0038】

選択されたセルブロック 100a と接続されたスイッチ部 300a とにロジックローの制御電圧 CSA を印加し、選択されないセルブロック 100b と接続されたスイッチ部 300b にロジックハイの制御電圧 CSb を印加する。

20

#### 【0039】

共通ソースライン SL とバルク(図示せず)に接地電圧を印加する。ページバッファを介して選択されたビットラインに検出電圧を印加した後、検出電圧の変化をセンシングする。

#### 【0040】

本実施の形態では上述した電圧の印加順序は素子の読み取り方法によって多様に変更できる。すなわち、スイッチ部 300 に制御電圧を先に印加した後、X デコーダ 200 に所定の電圧を印加することもできる。

30

#### 【0041】

グローバルストリング選択電圧、グローバルソース選択電圧及びバス電圧として 4.0 ないし 5.0 V の電圧を使用することが好ましい。読み出し電圧として接地電圧を使用することが好ましい。

#### 【0042】

選択されたセルブロック 100a と接続された X デコーダ部 200a とにロジックハイの動作電圧 BLKWL a として 4.0 V + 2 Vt ないし 5.0 V + 2 Vt だけの電圧を使用することが好ましく、選択されないセルブロック 100b と接続された X デコーダ部 200b にロジックローの動作電圧 BLKWL b として接地電圧を使用することが好ましい。上記の Vt は X デコーダ部 200 内のトランジスタ等のしきい電圧を意味する。

#### 【0043】

検出電圧としては 0.8 ないし 1.5 V の電圧を使用することが好ましい。

#### 【0044】

以下、上述した説明に基づき NAND フラッシュ素子の読み出し動作時に印加される電圧を表に整理すれば次の通りである。

40

#### 【0045】

表 1 は、本発明に係る NAND フラッシュメモリ素子に印加される電圧を示した表である。

#### 【0046】

【表1】

| Read         | Select Block | Unselect Block |

|--------------|--------------|----------------|

| 選択されたワードライン  | 0V           | Floating       |

| 選択されないワードライン | 4.5V         | Floating       |

| D S L        | 4.5V         | 0V             |

| S S L        | 4.5V         | 0V             |

| S L          | 0V           | 0V             |

| B L          | 1V           | 1V             |

| B u l k      | 0V           | 0V             |

| B L K W L    | 4.5 + 2Vt    | 0V             |

| C S          | 0V           | Vcc            |

10

20

30

## 【0047】

表1を参照し本発明の読み出し動作を具体的に説明すれば次の通りである。

## 【0048】

外部のアドレス入力を介して読み出すためのセルを選択(ワードラインとビットライン選択)し、これに伴い選択されたセルが位置しているセルブロックを選択されたセルブロック100aと定義する。

## 【0049】

Xデコーダ部200のグローバルストリング選択ラインG D S L、グローバルソース選択ラインG S S L及び選択されないグローバルワードラインG W Lに各々4.5Vのグローバルストリング選択電圧、グローバルソース選択電圧及びバス電圧を印加し、選択されたグローバルワードラインG W Lには0Vの電圧を印加する。

## 【0050】

選択されたセルブロック100aと接続されたXデコーダ部200aには4.5 + 2Vtの動作電圧B L K W L aを印加し、選択されないセルブロック100bと接続されたXデコーダ部200bには0Vの動作電圧B L K W L bを印加する。選択されたセルブロック100aと接続されたスイッチ部300aに0Vの電圧を印加し、選択されないセルブロック100bと接続されたスイッチ部300bに電源電圧Vccを印加する。

## 【0051】

これにより、選択されたセルブロック100aのローカルストリング選択ラインD S L

40

50

, ローカルソース選択ライン S S L 及び選択されないローカルワードライン W L には各々 4.5 V のローカルストリング選択電圧、ローカルソース選択電圧及びバス電圧が印加され、選択されたローカルワードライン W L には 0 V の電圧が印加される。一方、選択されないセルブロック 100 b のあらゆるローカルワードライン W L はフローティングされ、ローカルストリング選択ライン D S L とローカルソース選択ライン S S L とには 0 V の電圧が印加される。

#### 【0052】

共通ソースライン S L とバルクに 0 V の電圧を印加し、ビットライン B L に接続されているページバッファを介して選択されたビットラインに 1 V の検出電圧を印加する。所定時間後にビットライン B L に印加された 1 V の検出電圧の変化をページバッファが判断してセルのデータを検出する。これはセルのプログラムまたは消去されている状態のしきい電圧差によってビットラインに充電されている検出電圧が放電されたり、その状態を維持するようになる。10

#### 【0053】

これによりプログラムセルを読み出す場合、ビットラインの漏れ電流が減少するようになって、プログラムされたセルと消去されたセルとの間のオン/オフ電流比が増加するようになる。したがって、素子のセンシングタイム(Sensing Time)が減少するようになり、リードトリップレンジ(Read Trip Range)が増加してデータ保存力(Data Retention)及び読み出しディスクエーブ(Read Disturb)によるしきい電圧変化を防止できる。すなわち、しきい電圧変化に対するマージンを増加させることができる。また、2 K バイトであるページバッファ変化(Page Buffer Variation)に対するマージンを増加させることができる。20

#### 【0054】

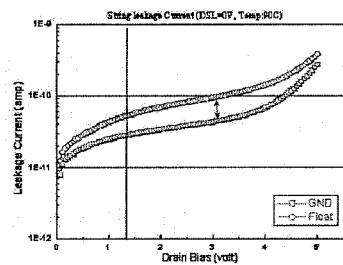

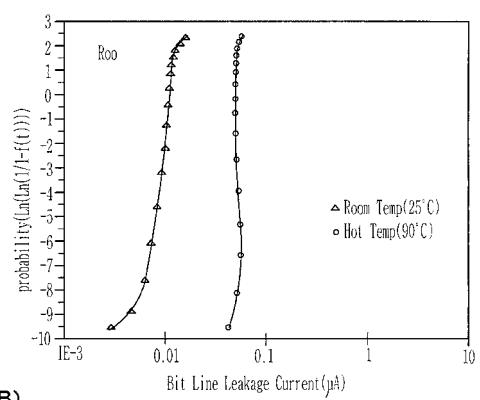

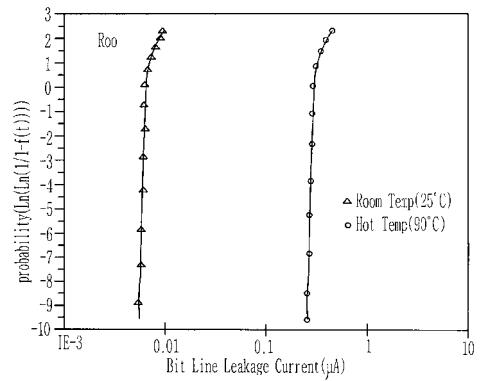

図 3 及び図 4 は、本発明に係る NAND フラッシュメモリ素子の漏れ電流を測定したグラフである。

#### 【0055】

図 3 は、テストパターンにおいてセルのしきい電圧が約 -5 V の場合、ソース選択ラインをフローティングノードで維持した場合と、0 V に維持した場合の漏れ電流をモニタした結果である。ソース選択ラインとこれと隣接したワードラインの容量性カップリング比(Capacitive Coupling Ratio)が小さくて誘起されたポテンシャルが 0.2 ないし 0.3 V 程度にも関わらず、2 ないし 3 倍程度の漏れ電流差を示している。すなわち、ソース選択ラインをフローティングさせた場合より強制的に 0 V を印加した場合が漏れ電流が減少することが分かる。30

#### 【0056】

図 4 A は、ソース選択ラインを 0 V にした場合の漏れ電流をモニタした結果であり、図 4 B は、従来 1024 ブロックの 512 M 製品においてソース選択ラインをフローティングで維持した場合の漏れ電流をモニタした結果である。図 4 A ないし図 4 B に比べて漏れ電流が減少することはもちろん、漏れ電流が均一であることがわかる。すなわち、図 4 A が図 4 B に比べて約 1/4 水準に漏れ電流が減少した。

#### 【0057】

尚、本発明は、上記した本実施の形態に限られるものではなく、本発明の技術的思想から逸脱しない範囲内で多様に変更して実施することが可能である。40

#### 【図面の簡単な説明】

#### 【0058】

【図 1】選択されないブロックのストリング選択トランジスタには 0 V のゲート電圧を印加し、ソース選択トランジスタはフローティングさせた状態の概念図である。

#### 【図 2】本発明に係る NAND フラッシュメモリ素子の回路図である。

【図 3】本発明に係る NAND フラッシュメモリ素子の漏れ電流を測定したグラフである。

#### 【図 4】本発明に係る NAND フラッシュメモリ素子の漏れ電流を測定したグラフである

10

20

30

40

50

## 【符号の説明】

## 【0 0 5 9】

- 1 0 0 セルブロック

- 1 1 0 セルストリング部

- 1 2 0 ストリング選択部

- 1 3 0 ソース選択部

- 2 0 0 Xデコーダ部

- 2 1 0 ストリング伝送トランジスタ

- 2 2 0 ワードライン伝送トランジスタ

- 2 3 0 ソース伝送トランジスタ

- 3 0 0 スイッチ部

- 3 1 0 ストリング放電トランジスタ

- 3 2 0 ソース放電トランジスタ

10

【図 1】

【図 2】

【図3】

【図4】

(A)

(B)

---

フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 01 L 29/788

H 01 L 29/792

F ターム(参考) 5F083 EP02 EP23 EP33 EP34 EP76 ER22 GA06 LA10

5F101 BA01 BB05 BD22 BD34 BE02 BE07