### CORRECTED VERSION

### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 23 August 2007 (23.08.2007)

te PC'

# (10) International Publication Number $WO\ 2007/095080\ A3$

- (51) International Patent Classification: *G06F 12/00* (2006.01)

- (21) International Application Number:

PCT/US2007/003460

- (22) International Filing Date: 8 February 2007 (08.02.2007)

- (25) Filing Language: English

- (26) **Publication Language:** English

- (30) Priority Data:

60/772,414

9 February 2006 (09.02.2006)

US

11/461,437

31 July 2006 (31.07.2006)

US

60/865,624

13 November 2006 (13.11.2006)

US

Not furnished

5 February 2007 (05.02.2007)

US

Not furnished

5 February 2007 (05.02.2007)

US

- (71) Applicants and

- (72) Inventors: RAJAN, Suresh, Natarajan [US/US]; 3284

Isadora Drive, San Jose, CA 95132 (US). SMITH, Michael, John, Sebastian [US/US]; 825 Ilima Court, Palo Alto, CA 94306 (US). SCHAKEL, Keith, R. [US/US]; 6238 Running Springs Rd., San Jose, CA 95135 (US). WANG, David, T. [US/US]; 1039 Coleman Rd. Apt. 6302, San Jose, CA 95123 (US). WEBER, Frederick, Daniel [US/US]; 1137 Settle Ave., San Jose, CA 95125 (US).

- (74) Agents: KOTAB, Dominic, M. et al; Zilka-Kotab, PC, P.O. Box 721 120, San Jose, California 95172-1 120 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY,

[Continued on next page]

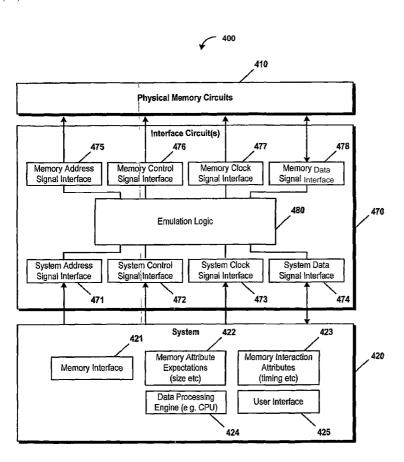

(54) Title: MEMORY CIRCUIT SYSTEM AND METHOD

(57) Abstract: A memory circuit system and method are provided. In one embodiment, an interface circuit is capable of communication with a plurality of memory circuits and a system. In use, the interface circuit is operable to interface the memory circuits and the system for reducing command scheduling constraints of the memory circuits. In another embodiment, an interface circuit is capable communication with a plurality of memory circuits and a system. In use, the interface circuit is operable to translate an address associated with a command communicated between the system and the memory circuits. In yet another embodiment, at least one memory stack comprises a plurality of DRAM integrated circuits. Further, a buffer circuit, coupled to a host system, is utilized for interfacing the memory stack to the host system for transforming one or more physical parameters between the DRAM integrated circuits and the host system. In still yet another embodiment, at least one memory stack comprises a plurality of DRAM integrated circuits. Further, an interface circuit, coupled to a host system, is utilized for interfacing the memory stack to the host system so to operate the memory stack as a single DRAM integrated circuit.

## WO 2007/095080 A3

- MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- (88) Date of publication of the international search report: 10 April 2008

- (48) Date of publication of this corrected version:  $$22\,\mathrm{May}\ 2008$

- (15) Information about Correction: see Notice of 22 May 2008