(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년09월03일

(11) 등록번호 10-1437194

(24) 등록일자 2014년08월27일

(51) 국제특허분류(Int. Cl.)

H01L 27/146 (2006.01)

(21) 출원번호 10-2009-7011278

(22) 출원일자(국제) 2007년11월30일

심사청구일자 2012년08월02일

(85) 번역문제출일자 2009년06월01일

(65) 공개번호 10-2009-0087896

(43) 공개일자 2009년08월18일

(86) 국제출원번호 PCT/US2007/024684

(87) 국제공개번호 WO 2008/069994

국제공개일자 2008년06월12일

(30) 우선권주장

11/565,801 2006년12월01일 미국(US)

(56) 선행기술조사문헌

JP2006049921 A

US20040262651 A1

US20060118835 A1

US20060124976 A1

전체 청구항 수 : 총 36 항

심사관 : 방기인

(54) 발명의 명칭 APS 셀 구조물 및 그 형성 방법, CMOS 이미지 센서 어레이 및 카메라 디바이스

**(57) 요약**

본 발명은 이중 일함수 전송 게이트 디바이스(125)를 갖는 CMOS 액티브 픽셀 센서(APS) 셀 구조물(100) 및 그 제조 방법에 관한 것이다. 전송 게이트 디바이스(125)는 기판(15) 상에 형성된 유전체층(60) 및 유전체층(60) 상에 형성되어 제 1 도전형 도핑 영역(175a) 및 인접하는 제 2 도전형 도핑 영역(175b)을 포함하는 이중 일함수 게이트 도전층(175a, 175b)을 포함한다. 전송 게이트 디바이스(125)는 광감 디바이스(200)에 의해 축적된 전하가 확산 영역(138)으로 이동하는 채널 영역을 규정한다. 제 1 도전형 도핑 영역(175a) 및 제 2 도전형 도핑 영역(175b)을 전기적으로 결합하는 실리사이드 구조물(190)이 이중 일함수 게이트 도전층(175a, 175b) 상에 형성된다. 일실시예에서, 실리사이드 접촉부(190)는 이중 일함수 게이트 도전층(175a, 175b)의 면적보다 작은 면적을 갖는다. 실리사이드 스트랩(190)은 게이트의 한 쪽 또는 다른 쪽이 미결정 전압으로 플로팅하지 않도록 다이오드 동작을 억제한다.

**대표도**

(72) 발명자

가이다쉬 로버트 마이클

미국 뉴욕주 14618 로체스터 앤틀러스 드라이브

460

자페 마크 디

미국 버몬트주 05482 셀버른 고버노스 레인 447

넬슨 에드워드 티

미국 뉴욕주 14534 피츠포드 브룩 로드 59

---

라셀 리차드 제이

미국 버몬트주 05446 콜체스터 그라니트 크릭 로드

225

스탠캠퍼아노 찰스 브이

미국 뉴욕주 14618 로체스터 오아크데일 드라이브

175

## 특허청구의 범위

### 청구항 1

액티브 픽셀 센서(APS; active pixel sensor) 셀 구조물에 있어서,

제 1 도전형 재료의 기판과,

상기 기판 상에 형성된 게이트 유전체층 및 상기 게이트 유전체층 상에 형성된 이중 일함수 게이트 도전층(dual workfunction gate conductor layer)을 포함하는 전송 게이트 디바이스 - 상기 이중 일함수 게이트 도전층은 제 1 도전형 재료의 제 1 도핑 영역과 제 2 도전형 재료의 제 2 도핑 영역을 포함함 - 와,

상기 전송 게이트 디바이스의 상기 제 1 도핑 영역에 인접한 기판 표면 또는 그 아래에 형성되어, 입사광에 응답하여 전하 캐리어를 수집하는 광감 디바이스와,

상기 전송 게이트 디바이스의 상기 제 2 도핑 영역에 인접한 상기 기판 표면에 형성된 제 2 도전형 재료의 확산 영역 - 상기 전송 게이트 디바이스는 상기 광감 디바이스와 상기 확산 영역 사이에서 전하 전송을 가능하게 하는 채널 영역을 형성함 - 과,

상기 이중 일함수 게이트 도전층 위에 형성되며, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 상기 전송 게이트 디바이스의 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 실리사이드 구조물

을 포함하고,

상기 이중 일함수 게이트 도전층 위에 형성되며 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 상기 실리사이드 구조물의 면적은 상기 이중 일함수 게이트 도전층의 면적보다 작은

APS 셀 구조물.

### 청구항 2

제 1 항에 있어서,

상기 광감 디바이스는 포토다이오드를 포함하고,

상기 포토다이오드는

상기 기판 표면 아래에 형성된 제 2 도전형 재료의 수집 웨일(collection well)과,

상기 기판 표면의 상기 수집 웨일 위에 형성된 상기 제 1 도전형 재료의 피닝층(pinning layer)을 포함하는

APS 셀 구조물.

### 청구항 3

제 2 항에 있어서,

상기 피닝층 및 상기 수집 웨일에 인접하게 형성된 격리 영역(isolation region)을 더 포함하는

APS 셀 구조물.

### 청구항 4

제 2 항에 있어서,

상기 기판, 상기 제 1 도전형 재료의 상기 피닝층, 및 상기 전송 게이트 디바이스의 상기 이중 일함수 게이트 도전층의 상기 제 1 도핑 영역은 p형 도핀트 재료를 포함하는

APS 셀 구조물.

### 청구항 5

제 4 항에 있어서,

상기 p형 도편트 재료는 붕소 또는 인듐을 포함하는

APS 셀 구조물.

#### 청구항 6

제 2 항에 있어서,

상기 제 2 도전형 재료의 상기 수집 웨л, 제 2 도전형 재료의 상기 확산 영역, 및 상기 전송 게이트 디바이스의

상기 이중 일함수 게이트 도전층의 상기 제 2 도핑 영역은 n형 도편트 재료를 포함하는

APS 셀 구조물.

#### 청구항 7

제 6 항에 있어서,

상기 n형 도편트 재료는 인, 비소 또는 안티몬 중 하나를 포함하는

APS 셀 구조물.

#### 청구항 8

제 6 항에 있어서,

상기 전송 게이트 디바이스의 상기 이중 일함수 게이트 도전층은 다이오드를 포함하는

APS 셀 구조물.

#### 청구항 9

제 1 항에 있어서,

상기 실리사이드 구조물은 Ti, Ta, W, Co, Ni, Pt, Pd 또는 이들의 합금의 실리사이드를 포함하는

APS 셀 구조물.

#### 청구항 10

삭제

#### 청구항 11

제 1 항에 있어서,

상기 이중 일함수 게이트 도전층 위에 형성되며, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1

도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 상기 실리사이드 구조물의 길이는

상기 이중 일함수 게이트 도전층의 길이보다 짧은

APS 셀 구조물.

#### 청구항 12

제 2 항에 있어서,

상기 전송 게이트 디바이스 아래에 상기 수집 웨л과 상기 확산 영역 사이에서 전하 전송이 가능하게 되는 도전

채널 영역이 배치되고,

상기 실리사이드 구조물은 상기 이중 일함수 게이트 도전층 위에 형성되며, 상기 도전 채널 영역을 규정하는 영

역의 외부에서 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상

기 제 2 도핑 영역을 전기적으로 결합하는

APS 셀 구조물.

### 청구항 13

액티브 픽셀 센서(APS) 셀 구조물을 형성하는 방법에 있어서,

제 1 도전형 재료의 기판을 제공하는 단계와,

상기 기판 상에 형성된 게이트 유전체층 및 상기 게이트 유전체층 상에 형성된 이중 일함수 게이트 도전층을 포함하는 전송 게이트 디바이스를 형성하는 단계 - 상기 이중 일함수 게이트 도전층은 제 1 도전형 재료의 제 1 도핑 영역 및 제 2 도전형 재료의 제 2 도핑 영역을 포함함 - 와,

입사광에 응답하여 전하 캐리어를 수집하기 위해 상기 전송 게이트 디바이스의 상기 제 1 도핑 영역에 인접한 기판 표면 또는 그 아래에 광감 디바이스를 형성하는 단계와,

상기 전송 게이트 디바이스의 상기 제 2 도핑 영역에 인접한 상기 기판 표면에 제 2 도전형 재료의 확산 영역을 형성하는 단계 - 상기 전송 게이트 디바이스는 상기 광감 디바이스와 상기 확산 영역 사이에서 전하 전송을 가능하게 하는 도전 채널 영역을 형성함 - 와,

상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 상기 전송 게이트 디바이스의 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하기 위해 상기 이중 일함수 게이트 도전층 위에 실리사이드 구조물을 형성하는 단계

를 포함하고,

상기 형성된 실리사이드 구조물의 면적은 상기 이중 일함수 게이트 도전층의 면적보다 작은

APS 셀 구조물 형성 방법.

### 청구항 14

제 13 항에 있어서,

상기 광감 디바이스는 포토다이오드를 포함하고,

상기 광감 디바이스를 형성하는 단계는

상기 기판 표면 아래에 형성된 제 2 도전형 재료를 주입하여 상기 제 2 도전형 재료를 포함하는 수집 웨л을 형성하는 단계와,

상기 기판 표면의 상기 수집 웨л 위에 상기 제 1 도전형 재료의 포토다이오드 피닝층을 형성하는 단계를 포함하는

APS 셀 구조물 형성 방법.

### 청구항 15

제 14 항에 있어서,

상기 포토다이오드 피닝층 및 상기 수집 웨л에 인접하게 격리 영역을 형성하는 단계를 더 포함하는

APS 셀 구조물 형성 방법.

### 청구항 16

제 14 항에 있어서,

상기 기판, 상기 제 1 도전형 재료의 상기 피닝층, 및 상기 전송 게이트 디바이스의 상기 이중 일함수 게이트 도전층의 상기 제 1 도핑 영역은 p형 도편트 재료를 포함하는

APS 셀 구조물 형성 방법.

### 청구항 17

제 16 항에 있어서,

상기 p형 도편트 재료는 붕소 또는 인듐을 포함하는

APS 셀 구조물 형성 방법.

### 청구항 18

제 14 항에 있어서,

상기 제 2 도전형 재료의 상기 수집 웨, 제 2 도전형 재료의 상기 확산 영역 및 상기 전송 게이트 디바이스의

상기 이중 일함수 게이트 도전층의 상기 제 2 도핑 영역은 n형 도편트 재료를 포함하는

APS 셀 구조물 형성 방법.

### 청구항 19

제 18 항에 있어서,

상기 n형 도편트 재료는 인, 비소 또는 안티몬 중 하나를 포함하는

APS 셀 구조물 형성 방법.

### 청구항 20

삭제

### 청구항 21

제 13 항에 있어서,

상기 이중 일함수 게이트 도전층 위에 형성되고, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1

도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 상기 실리사이드 구조물의 길이는

상기 이중 일함수 게이트 도전층의 길이보다 짧은

APS 셀 구조물 형성 방법.

### 청구항 22

제 13 항에 있어서,

상기 이중 일함수 게이트 도전층 위에 형성된 상기 실리사이드 구조물은, 상기 전송 게이트 디바이스에 대한 채

널 영역을 규정하는 게이트의 부분으로부터 오프셋되고 상기 도전 채널 영역의 바로 위가 아닌 영역에 걸쳐 연

장되는

APS 셀 구조물 형성 방법.

### 청구항 23

제 13 항에 있어서,

상기 이중 일함수 게이트 도전층 위에 실리사이드 구조물을 형성하는 단계는

상기 이중 일함수 게이트 도전층 상에 절연 캡핑층(insulative capping layer)을 형성하는 단계와,

상기 절연 캡핑층 내의 영역을 개방하여 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상기

제 2 도핑 영역을 모두 포함하는 상기 이중 일함수 게이트 도전층의 표면을 노출시키는 단계와,

상기 이중 일함수 게이트 도전층의 노출된 표면 부분 상에 실리사이드를 형성할 수 있는 금속을 증착하는 단계

와,

상기 실리사이드의 구조물을 형성하기 위해 상기 금속의 재료를 어닐링하는 단계를 포함하는

APS 셀 구조물 형성 방법.

#### 청구항 24

제 23 항에 있어서,

상기 금속은 Ti, Ta, W, Co, Ni, Pt, Pd 또는 이들의 합금을 포함하는

APS 셀 구조물 형성 방법.

#### 청구항 25

제 23 항에 있어서,

상기 어닐링은 500°C 내지 800°C의 온도에서 수행되는

APS 셀 구조물 형성 방법.

#### 청구항 26

액티브 픽셀 센서(APS) 셀 구조물을 각각 포함하는 픽셀들로 이루어진 CMOS 이미지 센서 어레이에 있어서,

상기 APS 셀 구조물은

제 1 도전형 재료의 기판과,

상기 기판 상에 형성된 게이트 유전체층 및 상기 게이트 유전체층 상에 형성된 이중 일함수 게이트 도전층을 포함하는 전송 게이트 디바이스 - 상기 이중 일함수 게이트 도전층은 제 1 도전형 재료의 제 1 도핑 영역 및 제 2 도전형 재료의 제 2 도핑 영역을 포함함 - 와,

상기 전송 게이트 디바이스의 상기 제 1 도핑 영역에 인접한 기판 표면 또는 그 아래에 형성되고, 입사광에 응답하여 전하 캐리어를 수집하는 광감 디바이스와,

상기 전송 게이트 디바이스의 상기 제 2 도핑 영역에 인접한 기판 표면에 형성된 제 2 도전형 재료의 확산 영역 - 상기 전송 게이트 디바이스는 상기 광감 디바이스와 상기 확산 영역 사이에서 전하 전송을 가능하게 하는 채널 영역을 형성함 - 과,

상기 이중 일함수 게이트 도전층 위에 형성되고, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 상기 전송 게이트 디바이스의 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 실리사이드 구조물

을 포함하고,

상기 이중 일함수 게이트 도전층 위에 형성되고, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 상기 실리사이드 구조물의 면적은 상기 이중 일함수 게이트 도전층의 면적보다 작은

CMOS 이미지 센서 어레이.

#### 청구항 27

카메라 디바이스에 있어서,

액티브 픽셀 센서(APS) 셀 구조물을 각각 포함하는 픽셀들로 이루어진 이미지 센서 어레이를 포함하되,

상기 각 APS 셀 구조물은

제 1 도전형 재료의 기판과,

상기 기판 상에 형성된 게이트 유전체층과 상기 게이트 유전체층 상에 형성된 이중 일함수 게이트 도전층을 포함하는 전송 게이트 디바이스 - 상기 이중 일함수 게이트 도전층은 제 1 도전형 재료의 제 1 도핑 영역 및 제 2 도전형 재료의 제 2 도핑 영역을 포함함 - 와,

상기 전송 게이트 디바이스의 상기 제 1 도핑 영역에 인접한 기판 표면 또는 그 아래에 형성되고, 입사광에 응답하여 전하 캐리어를 수집하는 광감 디바이스와,

상기 전송 게이트 디바이스의 상기 제 2 도핑 영역에 인접한 상기 기판 표면에 형성된 제 2 도전형 재료의 확산 영역 - 상기 전송 게이트 디바이스는 상기 광감 디바이스와 상기 확산 영역 사이에서 전하 전송을 가능하게 하는 채널 영역을 형성함 - 과,

상기 이중 일함수 게이트 도전층 위에 형성되고, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 상기 전송 게이트 디바이스의 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 실리사이드 구조물

을 포함하고,

상기 이중 일함수 게이트 도전층 위에 형성되고, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 상기 실리사이드 구조물의 면적은 상기 이중 일함수 게이트 도전층의 면적보다 작은

카메라 디바이스.

## 청구항 28

제 27 항에 있어서,

상기 광감 디바이스는 포토다이오드를 포함하고,

상기 포토다이오드는

상기 기판 표면 아래에 형성된 제 2 도전형 재료의 수집 웨ல과,

상기 기판 표면의 상기 수집 웨爾 위에 형성된 상기 제 1 도전형 재료의 피닝층을 포함하는

카메라 디바이스.

## 청구항 29

제 28 항에 있어서,

상기 피닝층 및 상기 수집 웨爾에 인접하게 형성된 격리 영역을 더 포함하는

카메라 디바이스.

## 청구항 30

제 28 항에 있어서,

상기 기판, 상기 제 1 도전형 재료의 상기 피닝층, 및 상기 전송 게이트 디바이스의 상기 이중 일함수 게이트 도전층의 상기 제 1 도핑 영역은 p형 도핀트 재료를 포함하는

카메라 디바이스.

## 청구항 31

제 30 항에 있어서,

상기 p형 도핀트 재료는 봉소 또는 인듐을 포함하는

카메라 디바이스.

## 청구항 32

제 28 항에 있어서,

상기 제 2 도전형 재료의 상기 수집 웨爾, 제 2 도전형 재료의 상기 확산 영역, 및 상기 전송 게이트 디바이스의

상기 이중 일함수 게이트 도전층의 상기 제 2 도핑 영역은 n형 도편트 재료를 포함하는 카메라 디바이스.

### 청구항 33

제 32 항에 있어서,

상기 n형 도편트 재료는 인, 비소 또는 안티몬 중 하나를 포함하는 카메라 디바이스.

### 청구항 34

제 32 항에 있어서,

상기 전송 게이트 디바이스의 상기 이중 일함수 게이트 도전층은 다이오드를 포함하는 카메라 디바이스.

### 청구항 35

제 27 항에 있어서,

상기 실리사이드 구조물은 Ti, Ta, W, Co, Ni, Pt, Pd 또는 이들의 합금의 실리사이드를 포함하는 카메라 디바이스.

### 청구항 36

제 26 항에 있어서,

상기 APS 셀 구조물의 상기 이중 일함수 게이트 도전층 위에 형성된 상기 실리사이드 구조물의 길이는 상기 이중 일함수 게이트 도전층의 길이보다 짧은

CMOS 이미지 센서 어레이.

### 청구항 37

제 27 항에 있어서,

상기 이중 일함수 게이트 도전층 위에 형성되고, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는 상기 실리사이드 구조물의 길이는 상기 이중 일함수 게이트 도전층의 길이보다 짧은

카메라 디바이스.

### 청구항 38

제 28 항에 있어서,

상기 전송 게이트 디바이스 아래에 상기 수집 웨л과 상기 확산 영역 사이에서 전하 전송이 가능하게 되는 도전 채널 영역이 배치되고,

상기 실리사이드 구조물은 상기 이중 일함수 게이트 도전층 위에 형성되며, 상기 도전 채널 영역을 규정하는 영역의 외부에서 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 상기 제 2 도핑 영역을 전기적으로 결합하는

카메라 디바이스.

## 명세서

## 기술 분야

[0001]

본 발명은 반도체 광학 이미지 센서에 관한 것으로, 특히 랙(lag)이 감소되고, 보다 높은 용량을 가지며 암전류가 보다 낮은 신규한 CMOS(complementary metal oxide semiconductor)이미지 센서 셀 구조에 관한 것이다.

## 배경 기술

[0002]

CMOS 이미지 센서는 디지털 카메라, 이동 전화, 셀룰러 전화, PDA(personal digital assistant)와 같은 보급형 디지털 장치, 개인용 컴퓨터, 의료기기 등과 같이 이미지 핵심을 요구하는 응용기기용의 종래의 CCD 센서를 대체하기 시작하고 있다. 바람직하게는, CMOS 이미지 센서는 포토다이오드 등과 같은 반도체 디바이스에 대해 현재의 CMOS 제조 공정을 적용하여 저비용으로 제조된다. 또한, CMOS 이미지 센서는 단일 전원에 의해 동작할 수 있어, 그 전력 소비가 CCD 센서의 전력 소비보다 낮게 억제될 수 있으며, 또한 CMOS로 회로 및 유사한 논리 처리 장치를 센서 칩에 쉽게 통합하여 CMOS 이미지 센서를 소형화할 수 있다.

[0003]

현재의 CMOS 이미지 센서는 광 에너지를 수집하여 이것을 판독가능한 전기 신호로 변환하는데 사용되는 CMOS 액티브 픽셀 센서(APS; Active Pixel Sensor) 셀의 어레이를 포함한다. 각각의 APS 셀은 하부에 있는 광 생성 전하(photo-generated charge)를 축적하기 위한 기판의 도핑 영역 상에 포토다이오드, 포토케이트 또는 포토컨덕터와 같은 광감 소자를 포함한다. 판독 회로는 각각의 픽셀 셀에 접속되고, 흔히 판독시에 광감 소자로부터 전하를 수집하는 확산 영역을 포함한다. 통상적으로, 이것은 플로팅 확산 영역에 전기적으로 접속된 게이트를 갖는 트랜지스터 디바이스에 의해 수행된다. 이미저는 또한 광감 소자로부터 채널을 가로질러 플로팅 확산 영역으로 전하를 전송하는 전송 게이트와, 플로팅 확산 영역을 전하 전송 전에 사전결정된 전하 레벨로 리셋하는 트랜지스터를 포함할 수도 있다.

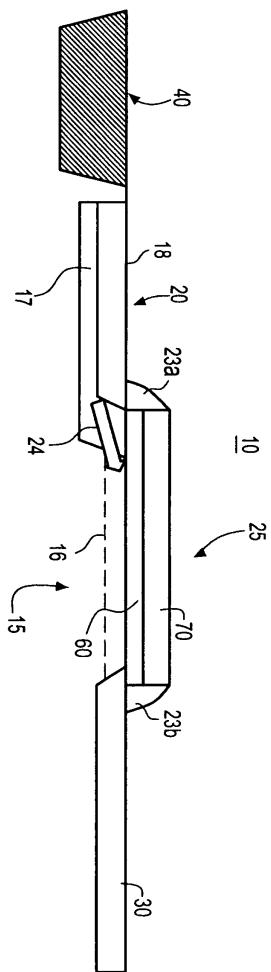

[0004]

도 1에 도시된 바와 같이, 통상적인 CMOS APS 셀(10)은 p형으로 도핑된 피닝층(pinning layer)(18) 및 그 아래의 약하게 도핑된 n형 영역(17)을 갖는 핀드(pinned) 포토다이오드(20)를 포함한다. 통상적으로, 핀드 다이오드(20)는 다이오드 피닝층(18)보다 낮은 p형 농도를 갖는 p 웨일 표면층 또는 p형 기판(15) 또는 p형 에피택셜층 상에 형성된다. 공지되어 있는 바와 같이, 표면 도핑된 p형 피닝층(18)은 기판(15)(또는 p형 에피택셜층 또는 p 웨일 표면층)과 전기 접촉한다. 따라서, 포토다이오드(20)는 동일 전위를 갖는 2개의 p형 영역(18, 15)을 가지며, 따라서 n형 도핑 영역(17)은 피닝 전압(V<sub>p</sub>)에서 완전히 공핍된다. 즉, 표면 피닝층(18)은 기판에 전기접촉 한다. 핀드 포토다이오드는 포토다이오드 내의 전위가 완전히 공핍될 때 상수값 V<sub>p</sub>에 고정되므로 "핀드(pinned)"라고 지칭된다. 이 핀드 포토다이오드 구성은 암 전류(암 환경에서 픽셀에 의해 출력된 전류)를 감소 시킴으로써 디바이스 성능을 향상시킨다. 그러나, 핀드 포토다이오드 구성은 포토다이오드로부터 플로팅 노드로의 전하의 불완전한 전송으로 인한 이미지 랙(image lag)을 일으킬 수도 있다.

[0005]

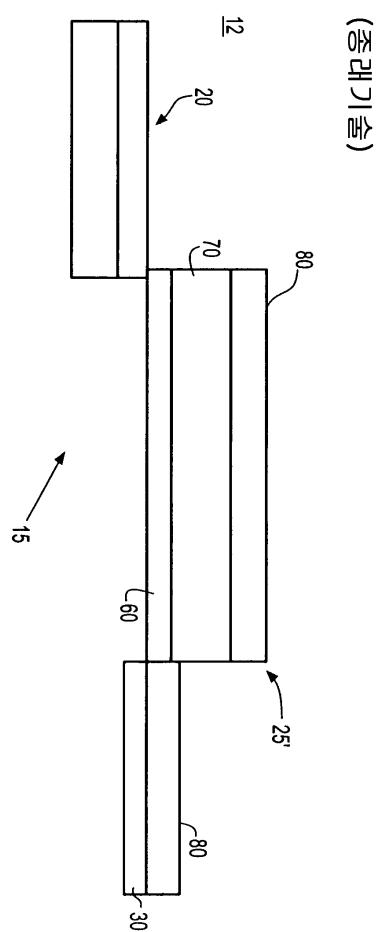

도 1에 도시된 바와 같이, n형 도핑 영역(17) 및 포토다이오드(20)의 p형 영역(18)은 얇은 트렌치 격리(STI; shallow trench isolation) 영역(40)과 같은 격리 영역과 얇은 스페이서 구조물(23a,b)에 의해 둘러싸인 전하 전송 트랜지스터 게이트(25) 사이에서 이격된다. 얇은 트렌치 격리(STI) 영역(40)은 인접 픽셀 셀로부터 셀을 격리시키는 픽셀 이미지 셀 가까이에 위치한다. 동작시에, 픽셀로부터의 광은 n형 영역(17)에서 전자를 수집하는 다이오드를 통해 포토다이오드 상으로 아래로 포커싱된다. 전송 게이트(25)가 동작할 때, 즉 예를 들어 얇은 유전체층(60) 위에 n형 도핑된 폴리실리콘층(70)을 포함하는 전송 게이트(70)에 전압을 인가함으로써 턴온될 때, 광 생성 전하(24)가 도핑된 n형 도핑 영역(17)을 축적하는 전하로부터 전송 디바이스 채널(16)을 통해 플로팅 확산 영역(30), 예를 들어 n<sup>+</sup>형으로 도핑된 플로팅 "노드"로 전송된다.

[0006]

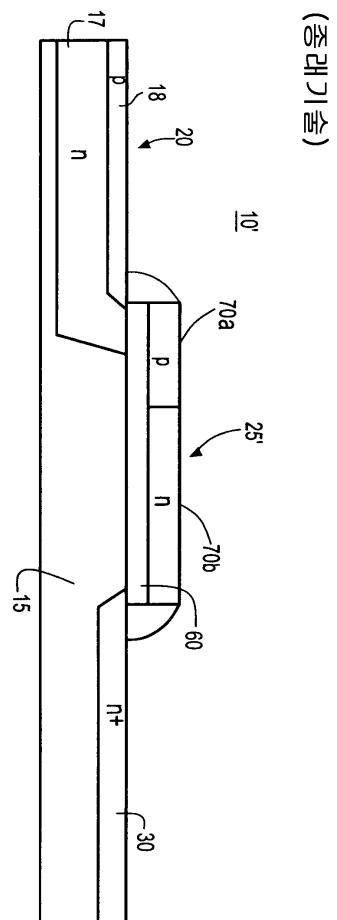

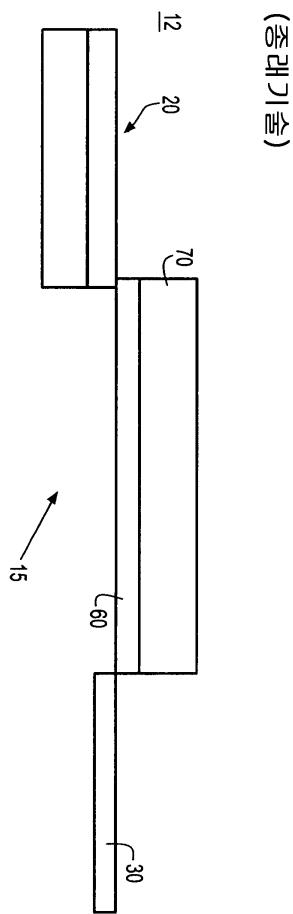

도 2는 p형 재료(70a)인 부분 및 n형(70b)인 부분을 갖는 게이트(25')를 포함하는 종래기술의 CMOS APS 셀(10')을 도시한 것이다. 게이트의 n형 부분(70b)은 보다 낮은 V<sub>t</sub>를 가지며, 게이트의 p-형 부분(70a)은 보다 높은 V<sub>t</sub>를 갖는다. 이들 두 부분이 게이트 내에 동시에 존재하기 때문에, 전송 게이트는 포토다이오드로부터 플로팅 확산부로 전자를 전송하는 내부 전계를 갖는다. 또한, CMOS APS 셀(10')의 설계에서, 어레이 내의 플로팅 노드 확산부 위에 형성된 실리사이드 접촉 영역(도시되어 있지 않음)의 존재가 밝은 점결함 누설(bright point defect leakage) 문제를 일으키는 것으로 알려져 있다. 즉, 이들 확산부 위에서 형성된 실리사이드 접촉부의 부가적인 존재로 인해, 예비 픽셀들이 픽셀을 사용할 수 없게 만들 정도의 높은 레벨의 전류를 누설하는 실리사이드 "스파이크"를 경험하는 것으로 파악되었다. 그 결과, 밝은 점 수율(bright point yield)을 위해 실리사이드가 CMOS 이미저의 어레이로부터 제거되었다.

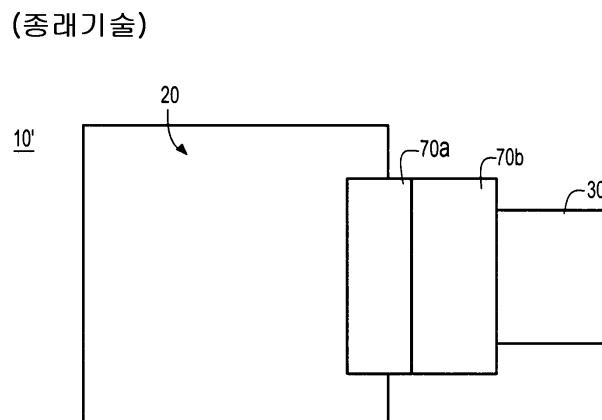

[0007] 도 3a는 전송 게이트 폴리실리콘 및 플로팅 확산부 위에 형성된 실리사이드층(80)이 유지되는 동안 실리사이드가 광을 차단하므로 포토다이오드 표면으로부터 차단된 실리사이드층을 갖는 CMOS 이미저(12)를 도시한 것이다. 도 3b는 훨씬 더 낮은 누설 동작을 위해 게이트 폴리 및 플로팅 확산부로부터 실리사이드층(80)을 제거한 도 3a의 CMOS 이미저(12)를 도시한 것이다.

[0008] 도 3c는 포토다이오드(20), 게이트 폴리 영역(70a, 70b) 및 플로팅 확산 노드(30)로부터 실리사이드 표면층을 제거한 도 2의 CMOS 이미저(10')의 평면도이다.

[0009] 그러나, 불행히도 n 및 p 영역을 갖는 전송 게이트를 갖는 이미저에서 실리사이드가 없으면, 게이트 내의 내장 다이오드로 형성된 각각의 CMOS APS 셀 게이트 폴리실리콘이 전체 게이트가 접촉되지 못하게 한다. 즉, 폴리실리콘 게이트의 n형 또는 p형 측 어느 한 쪽에만 접속되는 접촉부는 게이트 폴리층의 다른 극성에 적절히 접속되지 않을 것이다. 이 때문에, 게이트의 접촉되지 않은 부분 상에 시간 의존 전압이 발생한다. 즉, 게이트의 n형 부분에 접촉이 이루어지면, p형 부분이 부동하고, 마찬가지로 게이트의 p형 측에 접촉이 이루어지면, n형 부분이 부동한다. 경계부 바로 위에 접촉부가 형성되면, 접촉 중첩으로 인해 통계적으로 한쪽에만 접촉이 이루어질 수 있다.

[0010] 따라서 감소된(낮은) 랙 및 암전류를 나타내며, 밝은 스파이크 누설 현상을 제거하는 신규한 APS 셀 구조를 포함하는 CMOS 이미지 센서 어레이를 제공하는 것이 매우 바람직하다.

### 발명의 상세한 설명

[0011] 본 발명은 일반적으로 개선된 반도체 이미징 디바이스에 관한 것으로, 특히 표준 CMOS 공정을 이용하여 제조될 수 있는 이미징 디바이스에 관한 것이다.

[0012] 본 발명은 CMOS 이미지 센서에 관한 것으로, 여기서 상기 센서는 광검출 영역(예를 들면, 포토다이오드)과, 플로팅 확산부와, 상기 광검출 영역과 플로팅 확산부 사이에 위치하며 다이오드를 형성하는 n형 및 p형 도핑 영역을 포함하는 전송 게이트와, 전송 게이트의 n형 및 p형 도핑 영역을 전기적으로 결합하는 상호접속층(예를 들면, 실리사이드 구조물)을 포함한다.

[0013] 본 발명의 일실시예에서, 상호접속층은 실리사이드를 포함하고, 적어도 폴리실리콘 전송 게이트의 p형 영역의 일부분 및 n형 영역의 일부분이 물리적으로 접촉하여 형성된다. 실리사이드층은 폴리 게이트 폭의 전부 또는 단지 일부분 위에 있을 수 있고 실리사이드는 확산부(즉, 포토다이오드 및 플로팅 확산부) 상에 형성되지 않는다.

[0014] 바람직하게는, 2개의 일함수(n형 및 p형 게이트 폴리)를 갖는 전송 게이트 디바이스 및 실리사이드 스트랩을 포함하는 본 발명의 CMOS 이미저는 암전류를 위한 포토다이오드에서 높은 장벽을 나타내는 반면에 낮은 랙 성능을 위해 플로팅 확산부에서는 낮은 장벽이 제공된다. 실리사이드 스트랩은 다이오드 동작이 게이트의 한 쪽 또는 다른 쪽이 미정 전압으로 부동할 수 없게 한다.

[0015] 따라서, 본 발명의 일측면에 따르면, 액티브 픽셀 센서(APS) 셀 구조물 및 그 제조 방법이 제공된다. 액티브 픽셀 센서(APS)는 제 1 도전형 재료의 기판과, 기판 상에 형성된 게이트 유전체층과 게이트 유전체층 상에 형성된 이중 일함수 게이트 도전층을 포함하는 전송 게이트 디바이스 -상기 이중 일함수 게이트 도전층은 제 1 도전형 재료의 제 1 도핑 영역과 제 2 도전형 재료의 제 2 도핑 영역을 포함함- 와, 전송 게이트 디바이스의 제 1 도핑 영역에 인접한 기판 표면 또는 그 아래에 형성되어, 입사광에 응답하여 전하 캐리어를 수집하는 광감 디바이스와, 전송 게이트 디바이스의 상기 제 2 도핑 영역에 인접한 상기 기판 표면에 형성된 제 2 도전형 재료의 확산 영역 -상기 전송 게이트 디바이스는 광감 디바이스와 확산 영역 사이에서 전하 전송을 가능하게 하는 채널 영역을 형성함- 과, 전송 게이트 디바이스의 제 1 도전형 재료의 제 1 도핑 영역과 전송 게이트 디바이스의 제 2 도전형 재료의 제 2 도핑 영역을 전기적으로 결합하는, 상기 이중 일함수 게이트 도전층 상에 형성된 실리사이드 구조물을 포함한다.

[0016] 일실시예에서, 광감 디바이스는 포토다이오드를 포함하고, 포토다이오드는 기판 표면 아래에 형성된 제 2 도전형 재료의 수집 웰(collection well)과, 수집 웰 상의 기판 표면에 형성된 제 1 도전형 재료의 피닝층을 포함한다.

[0017] 일실시예에서, 기판, 상기 제 1 도전형 재료의 피닝층 및 전송 게이트의 이중 일함수 게이트 도전층의 제 1 도

평 영역은 봉소 또는 인듐과 같은 p형 도편트 재료를 포함한다. 제 2 도전형 재료의 수집 웨爾, 제 2 도전형 재료의 확산 영역 및 전송 게이트의 이중 일함수 게이트 도전층의 제 2 도핑 영역은 인, 비소 또는 안티몬과 같은 n형 도편트 재료를 포함한다.

[0018] 또한, 실리사이드 구조물은 Ti, Ta, W, Co, Ni, Pt, Pd 또는 이들의 합금의 실리사이드를 포함한다.

[0019] 일실시예에서, 상기 전송 게이트 디바이스의 제 1 도전형 재료의 상기 제 1 도핑 영역과 제 2 도전형 재료의 제 2 도핑 영역을 전기적으로 결합하는 이중 일함수 게이트 도전층 위에 형성된 실리사이드 구조물의 면적은 이중 일함수 게이트 도전층의 면적보다 작다.

[0020] 이와 달리, 전송 게이트 디바이스의 제 1 도전형 재료의 제 1 도핑 영역과 제 2 도전형 재료의 제 2 도핑 영역을 전기적으로 결합하는 이중 일함수 게이트 도전층 위에 형성된 실리사이드 구조물의 길이는 이중 일함수 게이트 도전층의 길이보다 작다.

[0021] 전송 게이트 디바이스가 상기 전송 게이트 디바이스 아래의 수집 웨爾 및 확산 영역 사이에서 전하 전송이 가능한 도전 채널 영역을 규정한다고 가정하면, 다른 실시예에서는, 실리사이드 구조물이 제 1 도전형 재료의 제 1 도핑 영역과 도전 채널 영역을 규정하는 영역의 외부의 전송 게이트 디바이스의 제 2 도전형 재료의 제 2 도핑 영역을 전기적으로 결합하는 이중 일함수 게이트 도전층 상에 형성된다.

[0022] 바람직하게는, 본 발명의 사상은 양 극성의 디바이스, 즉 n형 포토다이오드, p형 피닝충 및 nFET와, p형 포토다이오드, pFET를 갖는 n형 피닝충에 적용될 수 있다.

## 실시예

[0033] 본 발명의 목적, 특징 및 이점은, 첨부 도면을 참조한 이하의 상세한 설명을 고려하면, 당업자에게 명확해질 것이다.

[0034] 본 발명을 상세히 설명하기 전에, 본 발명은 제한적이지는 않지만 바람직하게는 CMOS 액티브 픽셀 센서에 사용 된다는 점을 안다면 유익할 것이다. 액티브 픽셀 센서(APS)는 스위치로서 기능하는 트랜지스터 이외의, 픽셀 내의 능동 소자를 지칭한다. 예를 들면, 플로팅 확산부 또는 증폭기가 능동 소자이다. CMOS는 픽셀과 관련되지만 통상적으로는 픽셀 내에 존재하지 않고, 트랜지스터의 소스/드레인이나 하나의 도편트 유형이고 그 짹을 이루는 트랜지스터가 반대의 도편트 유형인 경우에 형성되는 트랜지스터들과 같은 상보형 금속 산화물 실리콘 타입 전기 소자를 지칭한다. CMOS 디바이스는 몇몇 이점을 포함하는데, 그 중 하나는 적은 전력을 소비한다는 것이다.

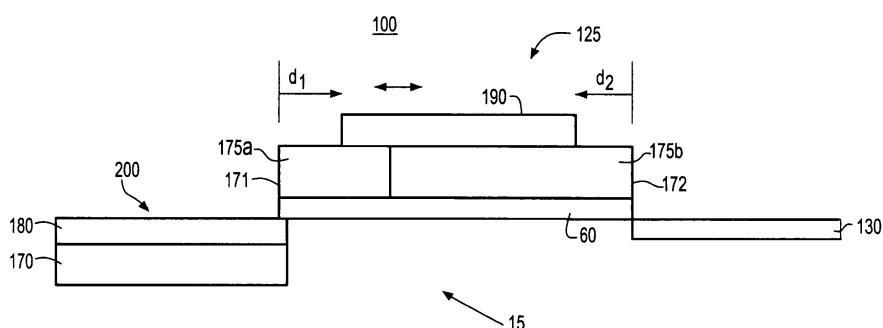

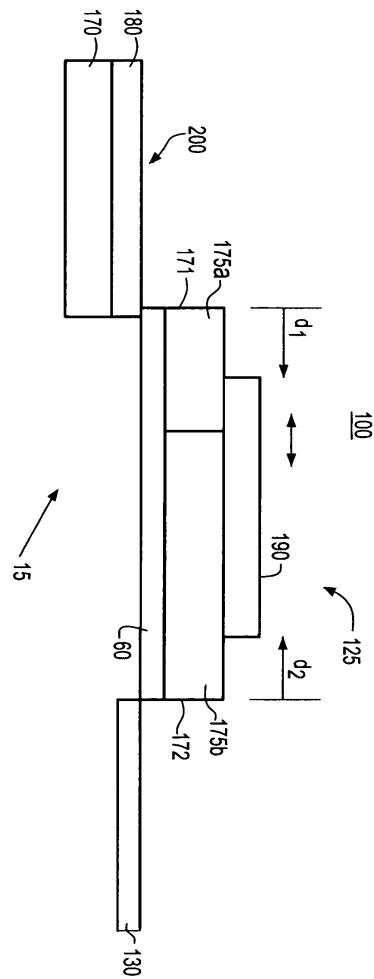

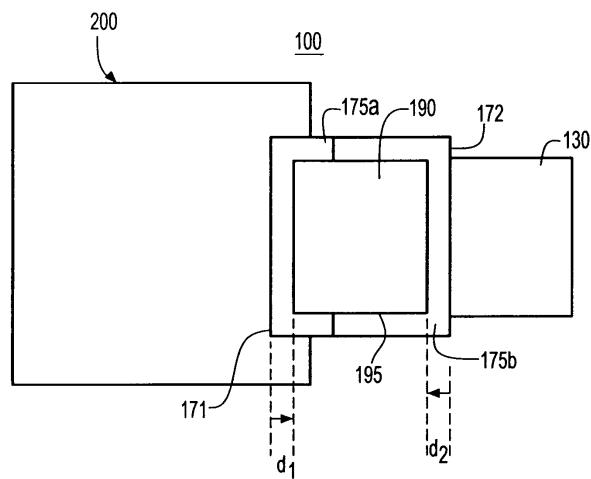

[0035] 도 4는 본 발명의 제 1 실시예에 따른 포토다이오드(200)와 같은 광감지 디바이스와, 폴리 실리콘과 같은 실리콘 함유 전송 게이트(125)를 포함하는 라인 CMOS 이미저(APS)(100)의 백 엔드의 단면도이다. 폴리실리콘 전송 게이트(125)는 다이오드를 형성하는 양극(p형 도핑) 영역과 인접하는 음극(n형 도핑) 영역을 포함한다. 일례에서, 폴리실리콘 전송 게이트(125)는 쇼트키 다이오드를 포함한다. 또한, 도 4에 도시된 바와 같이, 부분 실리사이드 "스트랩"(120)과 같은 도전성 구조는 이하에 상세히 설명하는 바와 같이 개선된 게이트 장벽 ac 특성을 위한 p형 부분(175a) 및 n형 부분(175b)을 갖는 폴리 게이트의 표면 상에 형성된다.

[0036] 도 4에 도시된 바와 같이, 부분 실리사이드 스트랩층(190)은 폴리실리콘 게이트(125)의 p형 도핑 부분(175a) 및 n형 도핑 부분(175b)을 전기적으로 연결한다. 또한, 도 4에 도시된 바와 같이, 부분 실리사이드 "스트랩" 층(190)은 게이트의 경계로부터 이격되어 형성된 에지부를 갖는다. 즉, 실리사이드 스트랩(190)은 폴리 게이트층의 각 에지부(171, 172)로부터 예를 들어 거리  $d_1$  및  $d_2$ 와 같은 거리를 두고 삽입된다. 형성된 실리사이드 스트랩의 삽입 거리( $d_1$ ,  $d_2$ )는 동일할 필요는 없는데, 즉, 실리사이드 스트랩(190)이 p형 부분(175a)을 n형 부분(175b)에 전기적으로 단락시키는 한, 스트랩은 단지 폴리 폭의 부분 위에 위치하도록 형성된다. 따라서, 도 5a의 평면도에 도시된 바와 같이, 실리사이드 스트랩(190)은 폴리 폭의 일부분 위에 형성된다. 바람직한 실시예에서, 실리사이드 스트랩(190)은 확산부(130)로부터 떨어져 있다.

[0037] 도시되어 있지는 않지만, 도 4에 도시된 CMOS 이미저 APS(100) 구조를 제조하는 하나의 예시적인 방법을 이제 설명한다. 당해 기술분야에 알려져 있는 다른 방법을 사용하여 다이오드 구조, 즉 인접한 p형 및 n형 게이트 폴리 영역을 갖는 전송 게이트를 형성할 수도 있다. 디바이스(100)는 기판(15) 상에 형성되는데, 기판(15)은 예를 들어 Si, SiGe, SiC, SiGeC, GaAs, InP, InAs 및 다른 반도체를 포함하는 별크 반도체일 수도 있고 또는

SOI(silicon-on-insulator), SiCOI(SiC-on-insulator) 또는 SGOI(silicon germanium-on-insulator)와 같은 층형 반도체일 수도 있다. 설명을 위해, 기판(15)은 예를 들어 봉소 또는 인듐(III-V족 반도체용의 베릴륨 또는 마그네슘)과 같은 p형 도편트 재료로  $1 \times 10^{14}$  내지  $1 \times 10^{16} \text{ cm}^{-3}$ 의 표준 농도 범위로 약하게 도핑된 제 1 도전형의 Si 함유 반도체 기판이다. 그 다음에, 표준 증착/성장 기법에 의해 기판(15) 위에 유전체 재료층(60)을 형성한다. 이 유전체 재료층(60)은 결국 전송 게이트 유전체를 형성할 것이다. 유전체 층은 예를 들어 40Å 내지 100Å의 두께 범위로 형성될 수 있으며, 산화물(예를 들면,  $\text{SiO}_2$ ), 질화물(예를 들면, 실리콘 질화물), 질산화물(예를 들면, Si 산 질화물),  $\text{N}_2\text{O}$ , NO,  $\text{ZrO}_2$  또는 이와 유사한 재료를 포함하는 적절한 게이트 유전체 재료를 포함할 수 있다. 일실시예에서, 게이트 유전체(60)는 예를 들어  $\text{SiO}_2$ ,  $\text{HfO}_2$ ,  $\text{ZrO}_2$ ,  $\text{Al}_2\text{O}_3$ ,  $\text{TiO}_2$ ,  $\text{La}_2\text{O}_3$ ,  $\text{SrTiO}_3$  및 그 혼합물과 같은 산화물로 이루어진다. 유전체층(60)은 종래의 열 산화를 이용하거나 또는 화학 기상 증착, 플라즈마 지원 화학 기상 증착, 원자층 증착(ALD), 증류(evaporation), 반응 스퍼터링, 화학 용액 증착 및 기타 유사한 증착 공정과 같은 적절한 증착 공정에 의해 Si 함유 반도체 기판(15)의 표면 상에 형성된다. 게이트 유전체(16)는 또한 위 공정의 임의의 조합을 이용하여 형성될 수도 있다. 도시되어 있지는 않지만, 유전체층은 유전체 재료의 스택을 포함할 수도 있다.

[0038] 그 다음에, CVD, 플라즈마 지원 CVD, 스퍼터링, 도금, 증류 및 기타 유사한 증착 공정(예를 들어 저압 CVD)을 포함하는 종래의 증착 공정을 이용하여 유전체층(60) 위에 다결정 실리콘과 같은 실리콘 함유층을 형성한다. 폴리실리콘층은 약 1kÅ 내지 2kÅ 범위의 두께로 형성될 수 있지만 이 범위를 벗어날 수도 있다. 이와 달리, 실리콘 함유층은 폴리실리콘층의 스택을 포함할 수도 있다. 그 다음에, 예를 들어 폴리실리콘층 위에 포토레지스트층으로 마스크를 도포하고, 형성할 전송 게이트의 유효 채널 길이를 결정하는 길이의 게이트 영역을 규정하도록 마스크를 패터닝한 후에, 레지스트를 현상하고 에치 공정을 수행하는 포토리소그래픽 공정에 의해 전송 게이트(125)를 형성한다. 기본적으로는, 레지스트 마스크에, 형성할 게이트 영역의 측면 사이즈 및 형상을 대략적으로 규정하는 사이즈 및 형상을 갖는 에치 윈도우를 제공한다. 그 다음에, 예를 들어 폴리실리콘층 및 유전체층(60) 또는 유전체층 스택을 적절히 에칭하여 전송 게이트 구조를 형성하도록 최적화되는 반응성 이온 에치(RIE) 공정과 같은 하나 이상의 에치 공정을 수행한다.

[0039] 게이트 유전체층 상에 진성 폴리실리콘층을 포함하는 전송 게이트 구조물을 형성한 후에, 전송 게이트 구조의 일부분을 덮는 후속 마스크 증착 공정 및 이온 주입 공정을 수행하여 제 2 도전형의 도편트 재료, 예컨대 인, 비소 또는 안티몬과 같은 n형 도편트 재료를 폴리실리콘층에 주입하여 n형 도핑된 게이트 폴리 부분(175b)을 형성한다. n형 도편트 재료는  $1 \times 10^{17}$  내지  $1 \times 10^{20} \text{ cm}^{-3}$ 의 불순물 농도 범위를 달성하도록 주입될 수 있다. 마찬가지로, 나머지 부분, 즉 게이트 구조물의 다른 쪽을 덮는 후속 마스크 증착 공정을 수행하여, 제 1 도전형의 도편트 재료, 예를 들어 봉소 또는 갈륨 또는 인듐과 같은 p형 도편트 재료를 폴리실리콘층에 주입하여 도 4에 도시된 바와 같이 p형 도핑 게이트 폴리 부분(175)을 형성한다. p형 도편트 재료는  $1 \times 10^{17}$  내지  $1 \times 10^{20} \text{ cm}^{-3}$ 의 불순물 농도 범위를 달성하도록 주입될 수 있다. 이와 달리, 폴리실리콘의 도핑은 주입 마스크의 적절한 사용에 의해 공정에 이미 존재하는 주입을 사용하여 달성될 수 있고, 동시에 그러한 주입은 침내의 다른 장소에서 수행된다. (일례로는 소스 드레인 주입 및 마스크가 있으며, 다른 예도 또한 가능하다.)

[0040] 전술한 방법의 변형예에서는, 인시튜 도핑 증착 공정 또는 증착(예를 들어, CVD, 플라즈마 지원 등)에 따라 인시튜(in-situ) n형, p형 도핑 또는 n형 및 p형 폴리실리콘 재료가 게이트 유전체층(60)의 상부에 증착될 수도 있다. 인시튜 도핑 증착 프로세스는, 예를 들어 게이트 유전체가 후속하는 고온 어닐링에 견딜 수 없을 때 이용될 수 있는 반면에, 이온 주입 및 어닐링은 게이트 유전체가 그러한 고온 어닐링에 견딜 수 있을 때 이용될 수 있다.

[0041] 다른 선택적 단계에서, 게이트 측벽 스페이서(도시되어 있지 않음)가 당해분야에 공지되어 있는 종래의 증착 공정에 의해 전송 게이트의 어느 한 쪽에 형성될 수 있으며, RIE 또는 다른 유사한 에치 공정에 의해 에칭되는 임의의 종래의 산화물 또는 질화물(예를 들면,  $\text{Si}_3\text{N}_4$ ) 또는 산화물/질화물을 포함할 수도 있다. 스페이서의 두께는 변할 수 있지만, 통상적으로는 이들은 약 5mm 내지 약 150mm의 두께를 갖는다.

[0042] 전송 게이트 측벽 스페이서를 선택적으로 형성한 후에, 포토다이오드 피닝 영역(180)을 제공하는 다음 단계를 수행한다. 이 단계는 포토레지스트층(도시되어 있지 않음) 패터닝을 형성하는 단계와, 당해 분야에 공지되어 있는 기법들에 따라서 이온 주입 마스크를 생성하여 게이트 에지부와 거의 일치하거나 또는 가능한 한 주어진 정렬 오차에 가깝게 마스크 에지부를 형성하여, 포토다이오드의 전하 축적 영역이 형성되는, 게이트의 에지부와 형성된 격리 영역, 예컨대 STI 영역(도시되어 있지 않음) 사이의 영역에 개구를 제공하는 단계를 포함한다. 이

개구는 도 4에 도시된 p형 도편트 피닝 영역(180)을 형성하기에 충분한 농도로 붕소와 같은 p형 도편트 재료의 이온을 주입할 수 있게 한다. 이 피닝 영역(180)은 스페이서의 에지부까지 형성될 수 있다(도시되어 있지 않음). 그 다음에 활성 p형 도편트 재료를  $1\times10^{17}$  내지  $1\times10^{19} \text{ cm}^{-3}$  의 불순물 농도로 이온 주입한다. 이와 달리, p형 피닝 포토다이오드 표면층(180)이 다른 공지된 기법에 의해 형성될 수도 있다. 예를 들어, p형 표면층(180)은 기체 소스 플라즈마 도핑 공정에 의해 또는 포토다이오드가 형성될 영역 위에 증착된 인시튜 도핑층 또는 도핑된 산화물층으로부터 p형 도편트를 확산시킴으로써 형성될 수도 있다.

[0043] 그 다음에 포토다이오드 소자(200)의 기판 표면의 p형 도핑 영역(180) 아래에 n형 도편트를 이온 주입하는 다른 단계를 수행한다. 동일한 이온 주입 마스크를 사용하여, 피닝 영역을 형성하기 위해 p형 재료를 주입할 때, 제 2 도전형 도편트 재료, 예를 들어 인, 비소 또는 안티몬과 같은 n형 도편트 재료를 주입하여 이온 주입된 p형 피닝층(180) 아래에 전하 수집층을 형성하는 이온 주입 공정을 수행할 수 있다. 도 4에 도시된 바와 같이 포토다이오드(190)의 n형 도핑 영역(170)을 형성하기 위해 n형 도편트 재료는 보다 높은 에너지 레벨에서 주입된다. 활성 n형 도편트 재료는  $1\times10^{16}$  내지  $1\times10^{18} \text{ cm}^{-3}$  의 불순물 농도로 이온 주입될 수 있다. 도 4에 도시된 바와 같이, 광 생성 전자를 수집하기 위한 광감 전하 영역(170)은 n형 영역(170)의 프로파일을 조정하는 복수의 불순물에 의해 형성될 수 있다.

[0044] 포토다이오드(200)의 형성 외에, 전송 게이트의 다른 쪽에 n형 플로팅 확산 영역(130)을 형성하는 부가적인 단계를 수행한다. 이 단계는 당해 기술분야에서 알려진 기법에 따라서 포토레지스트층을 형성하여 패터닝하고 이온 주입 마스크를 에칭하여, 게이트 에지부와 대략 일치하거나 또는 가능한 한 소정의 정렬 오차에 가깝게 마스크 에지부를 형성하고, 인, 비소 또는 안티몬과 같은 n형 도편트 재료를 도 4에 도시된 n+ 형 도핑된 플로팅 확산 영역(130)을 형성하기에 충분한 농도로 또는 게이트 측벽 스페이서(도시되어 있지 않음)의 에지부까지 주입할 수 있게 하는 개구를 제공하는 것을 포함한다. 활성 n+ 형 도편트 재료는  $1\times10^{18}$  내지  $1\times10^{20} \text{ cm}^{-3}$  의 불순물 농도 범위로 플로팅 확산 영역에서 이온 주입된다. 이 이온 주입 단계의 결과, n형 도편트 재료가 도핑된 전송 게이트 폴리실리콘층(175b) 부분에 추가적으로 주입될 수 있다.

[0045] 그 다음에, 폴리실리콘 게이트(125)를 사용하여 살리사이드 공정을 수행하여, 도 5a 내지 5d에 도시된 바와 같이, 본 발명에 따른 금속 실리사이드 스트랩(190)을 형성한다.

[0046] 살리사이드 프로세스의 제 1 단계는 먼저 공지되어 있는 증착 기법들을 이용하여 p형 도핑(175a) 및 n형 도핑(175b) 폴리실리콘 게이트층 상에 블랭킷 절연 캡을 형성하는 것을 포함한다. 예를 들어, 물리적 기상 증착 또는 화학 기상 증착과 같은 증착 공정을 이용하여 폴리실리콘 게이트층(175a, b) 상에 절연캡층을 형성한다. 절연캡층은 산화물, 질화물, 질산화물 또는 이들의 임의의 조합일 수 있다. 일실시예에서는, 유전체캡층으로서 예를 들어 Si<sub>3</sub>N<sub>4</sub>와 같은 질화물을 이용한다. 두께, 즉 유전체캡층의 높이는 약 20nm 내지 약 180nm 범위일 수 있다.

[0047] 그 다음에, 통상의 리소그래피 단계들, 즉 캡(예를 들면, 질화물) 유전체층 위에 패터닝된 레지스트 마스크를 형성하는 단계를 이용하여, 형성할 실리사이드 스트랩의 윤곽을 나타내는 영역을 에칭한다. 리소그래피 단계는 유전체캡층의 상부면에 포토레지스트를 도포하고, 포토레지스트를 원하는 패턴의 방사에 노광하고, 종래의 레지스트 현상액을 이용하여 노광된 포토레지스트를 현상하는 단계를 포함한다. 그 다음에 하부 폴리실리콘 게이트층을 노출한 채, 구체적으로는, 유전체캡층 내의 윈도우를 오픈하여 노출된 하부 폴리실리콘층 내의 두 도핑 영역(175a, b)의 인접 부분을 노출한 채, 하나 이상의 건식 에칭 단계를 이용하여 포토레지스트 내의 패턴을 유전체캡층에 전사한다. 본 발명에 따르면, 원하는 패턴은 도 5a 내지 5d에 도시된 바와 같이 형성되는 실리사이드 스트랩의 영역 및 크기이다. 따라서, 도 5a에 도시된 본 발명의 평면도에 도시된 바와 같이, 상부 캡 유전체(예를 들면, 질화물)층(도시되어 있지 않음)에 적용된 포토리소그래픽 마스크, 현상 및 에치 프로세스의 결과, 실리사이드 접촉부의 형성에 따르는 게이트의 길이를 따라 각각의 게이트 에지부(171, 172)로부터 거리(d1, d2)만큼 떨어지도록 삽입되는 하부 폴리실리콘층의 노출 영역(195)이 형성된다. 일부 실시예에서는, 패턴이 유전체캡층에 전사된 후에 패터닝된 포토레지스트가 제거될 수 있다.

[0048] 패터닝된 게이트를 형성하는데 본 발명에 사용될 수 있는 적절한 건식 에칭 공정들은 반응성 이온 에칭, 이온 빔 에칭, 플라즈마 에칭 또는 레이저 어블레이션(laser ablation)를 포함하지만, 이들에 한정되는 것은 아니다.

[0049] 그 다음에, 노출된 하부 폴리실리콘층이 실리사이드 금속으로 채워지도록 에칭된 패터닝된 질화물층에서 실리사이드 금속(도시되어 있지 않음)을 증착하는 단계를 수행한다. 실리사이드 스트랩을 형성하는데 사용된 금속은 실리콘과 반응하여 금속 실리사이드를 형성할 수 있는 임의의 금속을 포함한다. 그러한 금속의 예로는 Ti, Ta,

W, Co, Mo, ni, Pt, Pd 또는 이들의 합금을 들 수 있다. 금속은 예를 들어 스퍼터링, 화학 기상 증착, 실리사이드 증류의 물리적 기상 증착(PVD), 화학 용액 증착, 도금 등을 포함하는 임의의 종래의 증착 공정을 이용하여 증착될 수 있다.

[0050] 실리사이드 스트랩(190)의 크기를 규정하는 노출된 폴리실리콘 영역 상에 실리사이드 금속을 증착한 후에, 열적 어닐링 공정을 수행하여 구조물 내에 실리사이드 상(silicide phase), 바람직하게는, 금속 실리사이드의 최저 저항력 상을 나타내는 실리사이드를 형성한다. 어닐링은 실리사이드 금속이 하부 폴리실리콘과 반응하여 도 4에 도시된 금속 실리사이드층(190)을 형성하게 하는 공지되어 있는 환경 및 온도를 이용하여 수행된다. 일실시 예에서는, 실리사이드 금속이 Co를 포함할 수 있으며,  $\text{CoSi}_2$ 는 공지되어 있는 2 단계 어닐링 공정을 이용하여 형성된다. 본 발명의 다른 실시예에서는, 실리사이드 금속은 Ni 또는 Pt이고, 단일 어닐링 단계를 이용하여  $\text{NiSi}$  및  $\text{PtSi}$ 가 형성된다. 그 다음에, 선택적 습식 에치 단계를 이용하여 구조물로부터 임의의 비반응 실리사이드 금속을 제거할 수 있다.

[0051] 일실시예에서는, 웨이퍼를 질소 분위기에서 약 500°C 내지 약 800°C의 온도로 약 30분 동안 어닐링하여 폴리실리콘층(175a,b)의 부분과 반응하여 도전성 실리사이드 스트랩(190)을 형성한다.

[0052] 전술한 본 발명의 금속 실리사이드 게이트 프로세싱의 완료 후에, 트랜지스터와 트랜지스터 및 트랜지스터와 외부 접촉부에 대한 상호접속 구조물을 형성하는 종래의 방법이 이용될 수 있다.

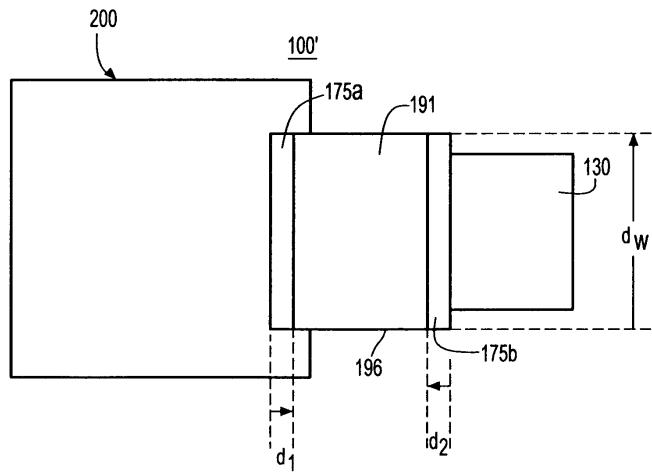

[0053] 도 5b는 도 5a에 도시된 본 발명의 실시예의 제 1 변형예에 따라 형성된 CMOS APS 셀의 평면도로서, 여기서 실리사이드 스트랩(191)은 바운다리 게이트의 에지부로부터 삽입 거리( $d_1$ ,  $d_2$ )에 형성된 에지부를 갖는 본 명세서에서 개시한 공정을 이용하여 형성되지만, 실질적으로 폴리의 전체 폭에 걸쳐 연장하도록 형성된다. 따라서, 예를 들어 도 5a와 관련하여 본 명세서에서 설명한 실리사이드 공정을 참조하면, 상부 캡 유전체(예를 들어, 질화물)층(도시되어 있지 않음)에 적용된 포토리소그래픽 마스크, 현상 및 에치 프로세스의 결과, 게이트의 길이를 따라 각각의 게이트 에지부(171, 172)로부터 거리( $d_1$  및  $d_2$ )만큼 삽입되지만, 예를 들어 폴리층 폭의 양 에지부 쪽으로 거리  $d_w$ 만큼 연장되는 하부 폴리실리콘층의 노출 영역(196)을 형성한다.

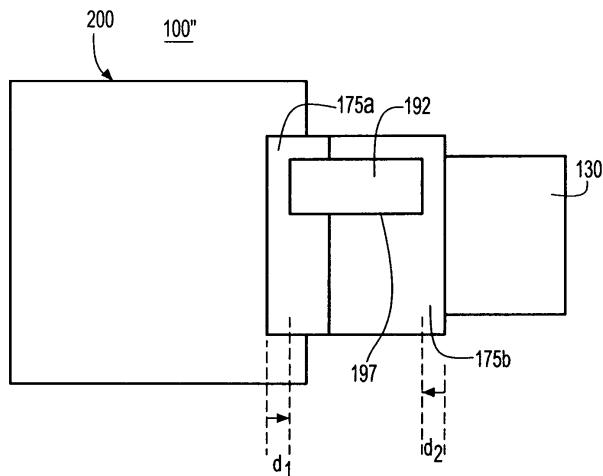

[0054] 도 5c는 도 5a에 도시된 본 발명의 실시예의 제 2 변형예에 따라 형성된 CMOS APS 셀(100")을 도시한 것으로, 여기서 바운다리 게이트의 에지부로부터 삽입 거리( $d_1$ ,  $d_2$ )를 두고 형성된 에지부를 갖지만 폴리 게이트의 짧은 거리만큼 연장되는 실리사이드 스트랩(192)이 본 명세서에서 설명한 공정을 이용하여 형성된다. 따라서, 예를 들어, 도 5a를 참조하여 여기서 설명한 실리사이드 공정을 참조하면, 도 5c에 도시된 바와 같이, 상부 캡 유전체(예를 들어, 질화물)층(도시되어 있지 않음)에 적용된 포토리소그래픽 마스크, 현상 및 에치 공정의 결과, 게이트의 길이를 따라 각각의 게이트 에지부(171, 172)로부터 거리( $d_1$ ,  $d_2$ )만큼 삽입되지만, 예를 들어 폴리 게이트의 짧은 거리에 대해서만 연장되는 하부 폴리실리콘층의 노출 영역(197)이 형성된다.

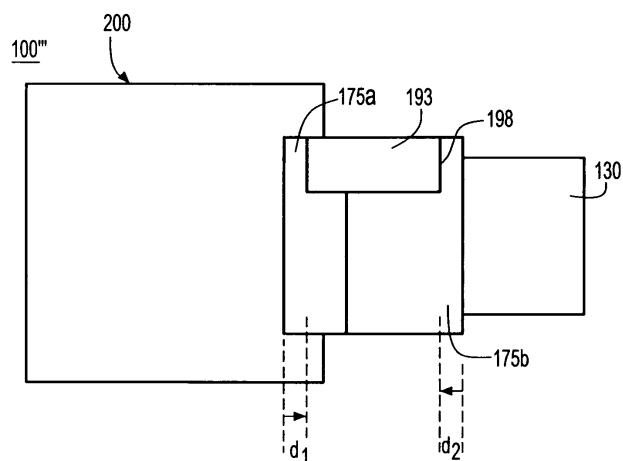

[0055] 본 발명의 다른 실시예에 따르면, (즉, n 및 p 영역이 어디선가 스트랩에 의해 단락되지 않는 한)CMOS 이미저 APS 전송 게이트의 실리사이드 스트랩이 도전성 채널 바로 위가 아닌 폴리실리콘의 일부분 상에 만들어질 수 있다. 도 5d는 도 5a에 도시된 본 발명의 실시예의 제 3 변형예에 따라 형성된 CMOS APS 셀(100'')의 평면도로서, 여기서 바운다리 게이트의 에지로부터 삽입 거리를 두고 형성된 에지부를 가지며 폴리 게이트의 짧은 거리만큼 연장되는 실리사이드 스트랩(193)이 전술한 공정을 이용하여 형성된다. 그러나, 스트랩(193)은 전송 디바이스에 대한 채널 영역을 규정하는 게이트(175a, b)의 부분으로부터 오프셋된다. 즉, 실리사이드 스트랩(193)은 도전성 채널 바로 위가 아니라 폴리실리콘 게이트의 일부분 상에 형성된다. 따라서, 예를 들어, 도 5a를 참조하여 전술한 실리사이드 공정을 참조하면, 도 5d에 도시된 바와 같이, 상부 캡 유전체(예를 들어 질화물)층(도시되어 있지 않음)에 적용된 포토리소그래픽 마스크, 현상 및 에치 프로세스의 결과, 게이트의 길이를 따른 각각의 게이트 에지(171, 172)로부터 소정 거리 삽입되고 예를 들어 디바이스 채널 영역 바로 위가 아닌 영역에서 폴리 게이트의 짧은 거리만큼만 연장되는 하부 폴리실리콘층의 노출 영역(198)이 형성된다.

[0056] 전송 게이트 폴리의 애노드(175a) 및 캐소드(175b) 부분을 전기적으로 단락시키는 임의의 도전성 구조는 전술한 실리사이드 접촉 구조를 제외하고 구현될 수 있다. 그러나, 광검출 영역 및 플로팅 확산 영역은 실리사이드가 없다.

[0057] 도 5a 내지 5d와 관련하여 도시 및 설명된 구조의 이점은 암전류 누설을 감소시키기 위해 포토다이오드에 높은 장벽이 존재하고, 보다 낮은 랙을 위해 플로팅 확산부에 낮은 장벽이 존재한다는 것이다. 실리사이드 스트랩은 다이오드 동작이 게이트의 한 쪽 또는 다른 쪽이 미정 전압으로 플로팅하지 않게 방지한다.

[0058] 도 6은 도 5a 내지 5d에 도시된 본 발명의 각 실시예에 따라 형성된 CMOS APS(Active Pixel Sensor) 셀(100-100'')을 갖는 이미지 센서(1302)를 구현하는 카메라 디바이스의 측면도이다.

[0059] 이상, 본 발명의 바람직한 실시예를 설명하였지만, 본 발명의 사상으로부터 벗어나지 않고 형식 또는 세부사항에 있어서 다양한 변형 및 수정이 쉽게 이루어질 수 있다는 것을 알 수 있을 것이다. 예를 들어, 전술한 바람직한 실시예는 n형 포토다이오드 및 p형 피닝층 및 nFET에 관한 것이었지만, 본 발명의 원리는 p형 포토다이오드, pFET를 갖는 n형 피닝층에도 바람직하게 적용될 수도 있다. 따라서, 본 발명은 전술한 정확한 형태로 한정되지 않고, 첨부한 청구범위 내의 모든 변형예들을 커버한다.

### 도면의 간단한 설명

[0023] 도 1은 종래기술에 따른 이미지 센서에 대한 CMOS APS(Active Pixel Sensor)를 도시한 도면.

[0024] 도 2는 내장 다이오드(built in diode), 예를 들어 pn 접합을 갖는 게이트 폴리실리콘층을 갖는 종래기술에 따른 CMOS APS(Active Pixel Sensor) 셀(10')의 단면도.

[0025] 도 3a 및 3b는 종래기술에 따른 실리사이드 접촉 영역이 포토다이오드로부터 제거된 CMOS APS 셀(12)(도 3a) 및 실리사이드 표면층 접촉 영역이 게이트 폴리층 및 플로팅 확산층으로부터 제거된 CMOS APS 셀(12)(도 3b)의 단면도.

[0026] 도 3c는 실리사이드 표면층이 포토다이오드(20), 게이트 폴리 영역(70a, 70b) 및 플로팅 확산 노드(30)로부터 제거된 도 2의 CMOS 이미저(10')의 평면도.

[0027] 도 4는 본 발명의 제 1 실시예에 따른, 실리사이드 접촉 영역이 포토다이오드 및 플로팅 노드 확산 영역으로부터 제거되었고, 향상된 게이트 장벽 ac 특성을 위해 게이트 폴리실리콘 상에 형성된 부분 도전성 스트랩을 갖는 CMOS APS 셀(100)의 단면도.

[0028] 도 5a는 도 4에 도시된 본 발명의 실시예에 따라 형성된 CMOS APS 셀(100)의 평면도.

[0029] 도 5b는 도 4에 도시된 본 발명의 실시예의 제 1 변형예에 따라 형성된 CMOS APS 셀(100')의 평면도.

[0030] 도 5c는 도 4에 도시된 본 발명의 실시예의 제 2 변형예에 따라 형성된 CMOS APS 셀(100'')의 평면도.

[0031] 도 5d는 도 4에 도시된 본 발명의 실시예의 제 3 변형예에 따라 형성된 CMOS APS 셀(100'')의 평면도.

[0032] 도 6은 본 발명에 따라 형성된 CMOS APS 셀을 갖는 이미지 센서를 구현하는 카메라 디바이스의 측면도.

도면

도면1

(종래기술)

도면2

도면3a

도면3b

도면3c

도면4

도면5a

도면5b

도면5c

도면5d

도면6