(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5899653号

(P5899653)

(45) 発行日 平成28年4月6日(2016.4.6)

(24) 登録日 平成28年3月18日(2016.3.18)

(51) Int.Cl.

F 1

|             |              |                  |        |       |       |

|-------------|--------------|------------------|--------|-------|-------|

| <b>HO4N</b> | <b>5/369</b> | <b>(2011.01)</b> | HO 4 N | 5/335 | 6 9 0 |

| <b>HO4N</b> | <b>5/374</b> | <b>(2011.01)</b> | HO 4 N | 5/335 | 7 4 0 |

| <b>HO4N</b> | <b>5/353</b> | <b>(2011.01)</b> | HO 4 N | 5/335 | 5 3 0 |

| <b>G02B</b> | <b>7/34</b>  | <b>(2006.01)</b> | G0 2 B | 7/34  |       |

| <b>G03B</b> | <b>13/36</b> | <b>(2006.01)</b> | G0 3 B | 13/36 |       |

請求項の数 8 (全 27 頁)

(21) 出願番号

特願2011-105193 (P2011-105193)

(22) 出願日

平成23年5月10日 (2011.5.10)

(65) 公開番号

特開2012-238951 (P2012-238951A)

(43) 公開日

平成24年12月6日 (2012.12.6)

審査請求日

平成26年3月28日 (2014.3.28)

(73) 特許権者 000004112

株式会社ニコン

東京都港区港南二丁目15番3号

(74) 代理人 100072718

弁理士 古谷 史旺

(74) 代理人 100116001

弁理士 森 俊秀

(72) 発明者 村田 寛信

東京都千代田区有楽町一丁目12番1号

株式会社ニコン内

審査官 鈴木 肇

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

入射光を光電変換して電荷を生成する第1光電変換部と、電極を有し前記電極に印加される電圧により制御され前記第1光電変換部から転送される電荷を蓄積するメモリ部と、電極を有し前記電極に印加される電圧により制御され前記第1光電変換部から前記メモリ部に電荷を転送する第1の転送部と、前記メモリ部から増幅部に電荷を転送する第2の転送部と、前記メモリ部を遮光する遮光部とを有する複数の焦点検出用画素と、

入射光を光電変換して電荷を生成する第2光電変換部を有する複数の撮像用画素と、

前記焦点検出用画素および前記撮像用画素が配置された画素アレイとを備え、

前記第1光電変換部は、前記第2光電変換部より小さく、

前記メモリ部は、前記焦点検出用画素の前記遮光部で遮光された領域であって、前記第1光電変換部がない領域にのみ配置され、

前記メモリ部の電極および前記第1の転送部の電極には共通の信号電圧が印加される撮像装置。

## 【請求項 2】

請求項1記載の撮像装置において、

前記遮光部は、前記撮像用画素の前記第2光電変換部と比べて前記焦点検出用画素の前記第1光電変換部が半分となるように前記焦点検出用画素の受光領域を遮光する撮像装置。

## 【請求項 3】

10

20

請求項 1 または請求項 2 記載の撮像装置において、

前記第 1 光電変換部と前記メモリ部は同じ導電型の半導体領域である撮像装置。

**【請求項 4】**

請求項 1 から請求項 3 のいずれか 1 項に記載の撮像装置において、

前記撮像用画素および前記焦点検出用画素の動作を制御する制御部を備えている撮像装置。

**【請求項 5】**

請求項 4 記載の撮像装置において、

前記制御部は、前記焦点検出用画素の露光時間と前記撮像用画素の露光時間とをそれぞれ独立に制御する撮像装置。

**【請求項 6】**

請求項 4 記載の撮像装置において、

前記制御部は、前記画素アレイで異なる行に配置された複数の前記焦点検出用画素の露光タイミングが互いに同じになるように、前記焦点検出用画素の動作を制御する撮像装置。

**【請求項 7】**

入射光を光電変換して電荷を生成する第 1 光電変換部と、前記第 1 光電変換部から転送される電荷を蓄積するメモリ部と、前記第 1 光電変換部から前記メモリ部に電荷を転送する第 1 の転送部と、前記メモリ部から増幅部に電荷を転送する第 2 の転送部と、前記メモリ部を遮光する遮光部とを有する複数の焦点検出用画素と、

入射光を光電変換して電荷を生成する第 2 光電変換部を有する複数の撮像用画素と、

前記焦点検出用画素および前記撮像用画素が配置された画素アレイと、

前記撮像用画素および前記焦点検出用画素の動作を制御する制御部とを備え、

前記第 1 光電変換部は、前記第 2 光電変換部より小さく、

前記メモリ部は、前記焦点検出用画素の前記遮光部で遮光された領域であって、前記第 1 光電変換部がない領域にのみ配置され、

前記制御部は、前記画素アレイで異なる行に配置された複数の前記焦点検出用画素の露光タイミングが互いに同じになるように、前記焦点検出用画素の動作を制御する撮像装置。

**【請求項 8】**

請求項 1 から請求項 7 のいずれか 1 項に記載の撮像装置において、

前記第 2 の転送部は、前記増幅部のフローティングディフェュージョンに電荷を転送する撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は、撮像装置に関する。

**【背景技術】**

**【0 0 0 2】**

近年、自動焦点調節機能（A F 機能）を有するビデオカメラやデジタルカメラが広く一般に普及している。この種のデジタルカメラには、C M O S 型の撮像装置やC C D 型の撮像装置が用いられる。例えば、C M O S 型の撮像装置は、複数の画素が 2 次元行列状に配置された画素アレイを有している。各画素は、光信号を電気信号に変換する光電変換部を有している。また、デジタルカメラは、撮像用の画素アレイとは別に、焦点検出を実施するための専用の焦点検出素子を有する場合もある。なお、撮像用の画素と焦点検出用の画素とを混在して配置した撮像装置も提案されている（例えば、特許文献 1）。

**【先行技術文献】**

**【特許文献】**

**【0 0 0 3】**

10

20

30

40

50

【特許文献 1】特許第 4027113 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

C M O S 型の撮像装置では、選択された行毎にシャッタ動作を行うローリングシャッタ方式が用いられる場合が多い。このため、特許文献 1 の構成では、複数の焦点検出用の画素の露光タイミングを互いに同一にすることは、困難である。焦点検出用の画素の露光タイミングが複数の焦点検出用の画素で互いに異なる場合、焦点検出精度が低下するおそれがある。また、撮像用の画素と焦点検出用の画素とが同じ行に配置されている場合、撮像用の画素を適切な露光時間で露光しているときに、焦点検出用の画素を適切な露光時間で露光することは、困難である。焦点検出用の画素を適切な露光時間で露光できない場合、焦点検出精度が低下する。

10

【0005】

本発明の目的は、焦点検出用の画素の露光タイミングを適切に制御可能な撮像装置を提供することである。

【課題を解決するための手段】

【0006】

撮像装置の一例は、複数の焦点検出用画素および複数の撮像用画素が配置された画素アレイを有している。各焦点検出用画素は、入射光を光電変換して電荷を生成する第 1 光電変換部と、電極を有し電極に印加される電圧により制御され第 1 光電変換部から転送される電荷を蓄積するメモリ部と、電極を有し電極に印加される電圧により制御され第 1 光電変換部からメモリ部に電荷を転送する第 1 の転送部と、メモリ部から増幅部に電荷を転送する第 2 の転送部と、メモリ部を遮光する遮光部とを有している。また、各撮像用画素は、入射光を光電変換して電荷を生成する第 2 光電変換部を有している。また、第 1 光電変換部は、第 2 光電変換部より小さく、メモリ部は、焦点検出用画素の遮光部で遮光された領域であって、第 1 光電変換部がない領域にのみ配置される。また、メモリ部の電極および第 1 の転送部の電極には共通の信号電圧が印加される。

20

撮像装置の他の例は、複数の焦点検出用画素および複数の撮像用画素が配置された画素アレイと、撮像用画素および焦点検出用画素の動作を制御する制御部とを有している。各焦点検出用画素は、入射光を光電変換して電荷を生成する第 1 光電変換部と、第 1 光電変換部から転送される電荷を蓄積するメモリ部と、第 1 光電変換部からメモリ部に電荷を転送する第 1 の転送部と、メモリ部から増幅部に電荷を転送する第 2 の転送部と、メモリ部を遮光する遮光部とを有している。また、各撮像用画素は、入射光を光電変換して電荷を生成する第 2 光電変換部を有している。また、第 1 光電変換部は、第 2 光電変換部より小さく、メモリ部は、焦点検出用画素の遮光部で遮光された領域であって、第 1 光電変換部がない領域にのみ配置される。また、制御部は、画素アレイで異なる行に配置された複数の焦点検出用画素の露光タイミングが互いに同じになるように、焦点検出用画素の動作を制御する。

30

【発明の効果】

【0007】

本発明によれば、焦点検出用の画素の露光タイミングを適切に制御可能な撮像装置を提供できる。

40

【図面の簡単な説明】

【0008】

【図 1】一実施形態における撮像装置の概要を示す図である。

【図 2】図 1 に示した撮像用画素および焦点検出用画素の概要を示す図である。

【図 3】図 2 に示した撮像用画素の A - A' 線に沿う断面を示す図である。

【図 4】図 2 に示した焦点検出用画素の B - B' 線に沿う断面を示す図である。

【図 5】図 1 に示した制御部の概要を示す図である。

【図 6】図 1 に示した撮像用画素の構成の一例を示す図である。

50

【図7】図1に示した焦点検出用画素の構成の一例を示す図である。

【図8】図6に示した撮像用画素の動作の一例を示す図である。

【図9】図7に示した焦点検出用画素の動作の一例を示す図である。

【図10】図7に示した焦点検出用画素の動作の別の例を示す図である。

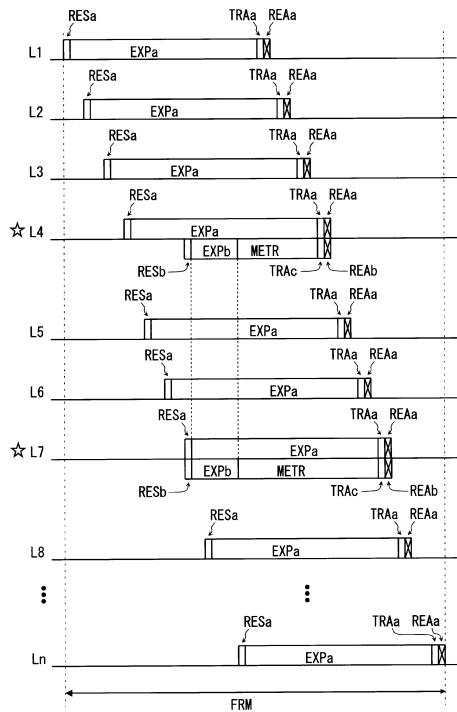

【図11】図5に示した画素アレイの動作の一例を示す図である。

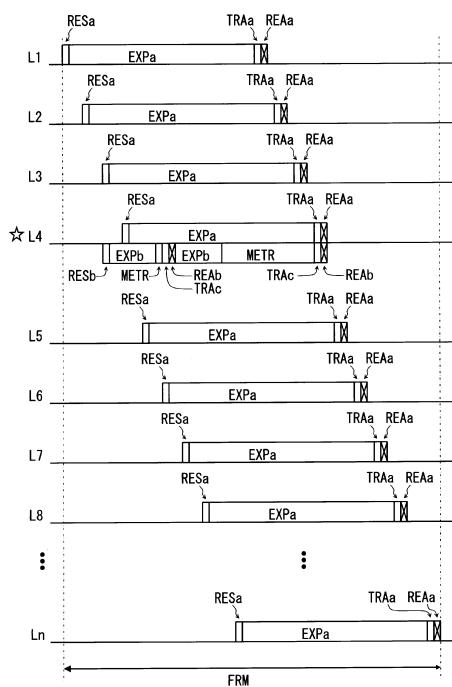

【図12】図5に示した画素アレイの動作の別の例を示す図である。

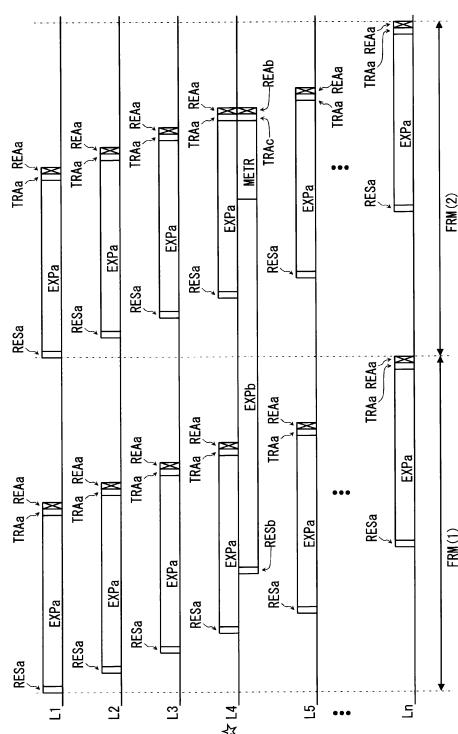

【図13】複数の行に焦点検出用画素が配置された画素アレイの動作の一例を示す図である。

【図14】焦点検出用画素の露光が1フレーム中に複数回実施されるときの画素アレイの動作の一例を示す図である。 10

【図15】焦点検出用画素の露光が複数フレームをまたいで実施されるときの画素アレイの動作の一例を示す図である。

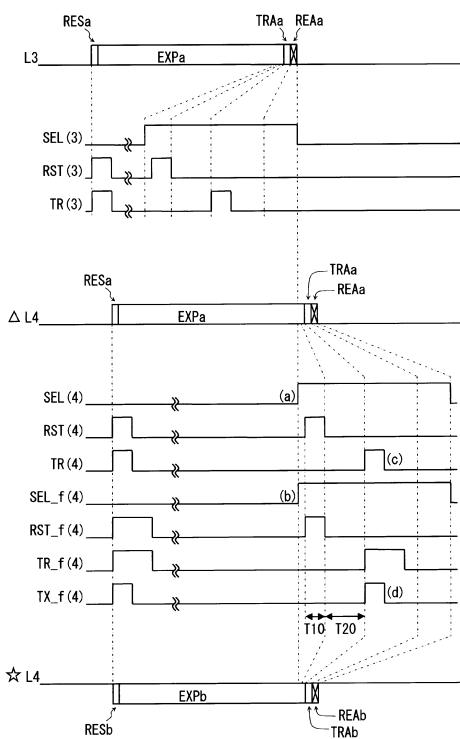

【図16】相関二重サンプリングが実施されるときの画素アレイの動作の一例を示す図である。

【図17】相関二重サンプリングが実施されるときの画素アレイの動作の別の例を示す図である。

【図18】フローティングディフュージョンをリセットするときの撮像用画素の各部のポテンシャルの一例を示す図である。

【図19】フローティングディフュージョンをリセットするときの焦点検出用画素の各部のポテンシャルの一例を示す図である。 20

【発明を実施するための形態】

【0009】

以下、本発明の実施形態を図面を用いて説明する。

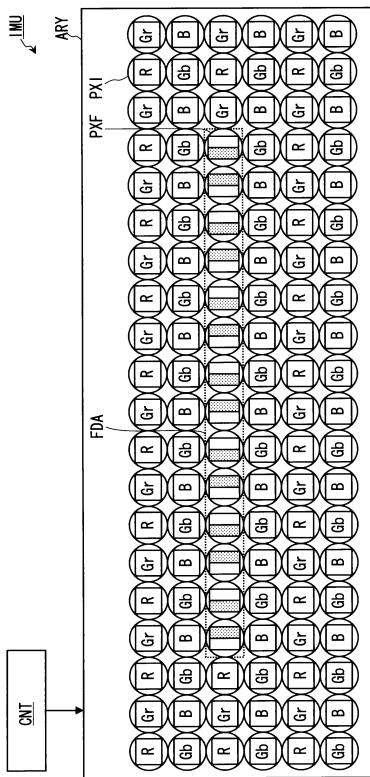

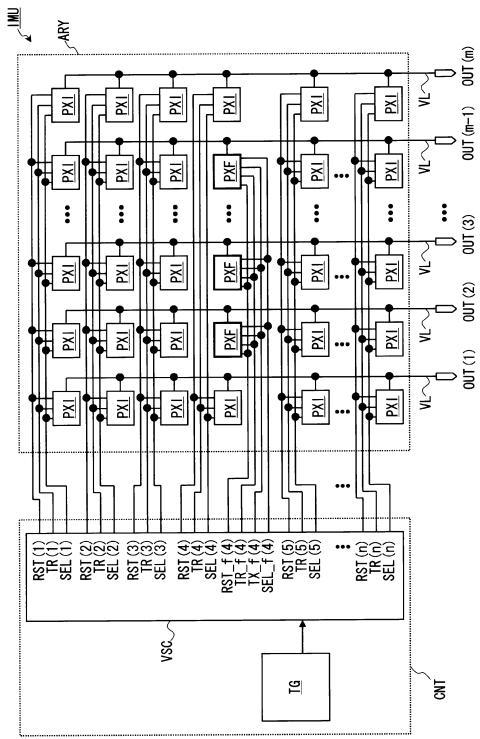

【0010】

図1は、本発明の一実施形態を示している。図1の網掛け部分は、図2で説明する焦点検出用画素PXF内のメモリ部MUを示している。この実施形態の撮像装置IMUは、例えば、CMOS型の撮像装置であり、デジタルカメラに搭載される。例えば、撮像装置IMUは、画素アレイARRYおよび制御部CNTを有している。

【0011】

画素アレイARRYは、例えば、マイクロレンズおよびカラーフィルタを介して入射される光の量に応じた電気信号（以下、画像信号とも称する）を生成する複数の撮像用画素PXIと、複数の焦点検出用画素PXFとを有している。例えば、複数の撮像用画素PXIは、赤色(R)、緑色(Gr、Gb)、青色(B)のカラーフィルタをそれぞれ有し、ベイヤー配列で配置されている。なお、赤色(R)、緑色(Gr、Gb)、青色(B)のカラーフィルタをそれぞれ有する撮像用画素PXIの配列は、ベイヤー配列に限定されない。

【0012】

焦点検出用画素PXFは、例えば、公知の瞳分割方式による自動焦点検出処理に用いられる信号を生成するための画素であり、行方向（図1の横方向）に延在する焦点検出領域FDA（図1の破線で囲んだ領域）に配置される。なお、焦点検出用画素PXFが配置される焦点検出領域FDAは、列方向（図1の縦方向）に延在して設けられてもよいし、複数設けられてもよい。 40

【0013】

制御部CNTは、例えば、画素アレイARRYの撮像用画素PXIおよび焦点検出用画素PXFの動作を制御する。なお、制御部CNTは、撮像装置IMUとは別に設けられてもよい。すなわち、撮像装置IMUは、図1の構成から制御部CNTが省かれた構成でもよい。

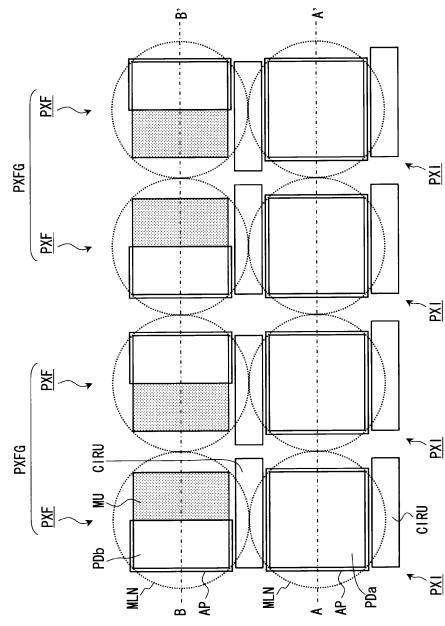

【0014】

図2は、図1に示した撮像用画素PXIおよび焦点検出用画素PXFの概要を示している。なお、図2は、画素アレイARRYの撮像面側（後述する図3、図4の上側）から見た

撮像用画素 P X I および焦点検出用画素 P X F を示している。また、図 2 では、図を見やすくするために、配線やカラーフィルタ等の記載を省略している。図 2 の網掛け部分は、メモリ部 M U を示している。

#### 【 0 0 1 5 】

撮像用画素 P X I は、光電変換部としてのフォトダイオード P D a と、画像信号を読み出すための回路部 C I R U とを有している。例えば、フォトダイオード P D a は、マイクロレンズ M L N および開口部 A P を介して入射される光を光電変換して電荷を生成する。なお、例えば、開口部 A P 以外の回路部 C I R U 等の領域では、マイクロレンズ M L N を介して入射される光は、図 3 に示す遮光部 M S 等により遮蔽される。

#### 【 0 0 1 6 】

回路部 C I R U は、例えば、後述する図 6、図 7 に示す転送トランジスタ M T R 、増幅トランジスタ M A M 、画素選択トランジスタ M S E 、リセットトランジスタ M R S およびフローティングディフュージョン F D を有している。例えば、撮像用画素 P X I では、回路部 C I R U の転送トランジスタ M T R は、フォトダイオード P D a に隣接して配置される。また、例えば、焦点検出用画素 P X F では、回路部 C I R U の転送トランジスタ M T R は、メモリ部 M U に隣接して配置される。なお、回路部 C I R U の配置は、この例に限定されない。

10

#### 【 0 0 1 7 】

焦点検出用画素 P X F は、光電変換部としてのフォトダイオード P D b と、フォトダイオード P D b から転送される電荷を蓄積するメモリ部 M U と、画像信号を読み出すための回路部 C I R U とを有している。例えば、フォトダイオード P D b は、マイクロレンズ M L N および開口部 A P を介して入射される光を光電変換して電荷を生成する。なお、例えば、開口部 A P 以外のメモリ部 M U 等の領域では、マイクロレンズ M L N を介して入射される光は、図 4 に示す遮光部 M S 等により遮蔽される。

20

#### 【 0 0 1 8 】

焦点検出用画素群 P X F G は、例えば、行方向（図 2 の横方向）に配置された一対の焦点検出用画素 P X F により構成され、行方向に瞳分割した一対の像を生成する。例えば、焦点検出用画素群 P X F G (一対の焦点検出用画素 P X F ) から生成される一対の像の像ずれ量を検出することにより、デフォーカス量が算出される。

#### 【 0 0 1 9 】

30

ここで、例えば、焦点検出用画素群 P X F G のうちの左側の焦点検出用画素 P X F では、フォトダイオード P D b およびメモリ部 M U がマイクロレンズ M L N の左半分および右半分にそれぞれ配置される。また、例えば、焦点検出用画素群 P X F G のうちの右側の焦点検出用画素 P X F では、フォトダイオード P D b およびメモリ部 M U は、マイクロレンズ M L N の右半分および左半分にそれぞれ配置される。

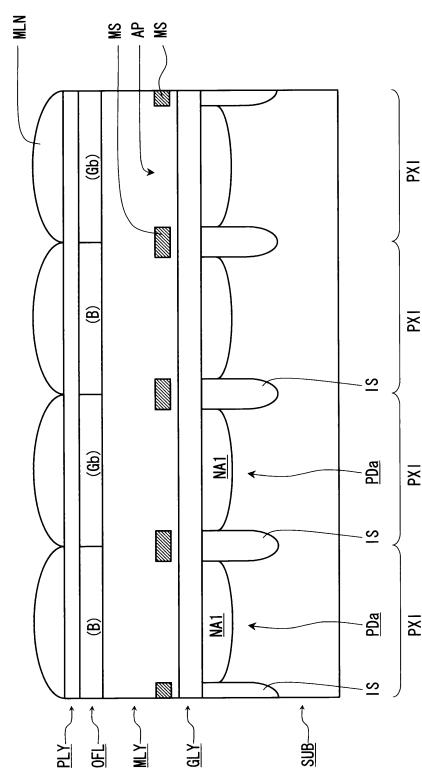

#### 【 0 0 2 0 】

図 3 は、図 2 に示した撮像用画素 P X I の A - A' 線に沿う断面を示している。なお、図 3 では、配線等の記載を省略している。例えば、フォトダイオード P D a は、p 型の半導体基板 S U B の受光面側（図 3 では上側）に形成された n 型の半導体領域 N A 1 を有している。なお、フォトダイオード P D a の導電型は、この例に限定されない。半導体基板 S U B に形成された絶縁部 I S は、例えば、互いに隣接するフォトダイオード P D a 間を絶縁するための領域である。また、例えば、半導体基板 S U B 上に設けられたゲート層 G L Y には、上述した図 2 に示した回路部 C I R U のトランジスタのゲート電極等が形成される。

40

#### 【 0 0 2 1 】

そして、ゲート層 G L Y 上には、複数の層を有する配線層 M L Y が設けられる。例えば、遮光部 M S は、配線層 M L Y の最下層（半導体基板 S U B 側の層）に金属膜等で形成され、フォトダイオード P D a 以外の領域（絶縁部 I S 等）に対応する位置に配置される。すなわち、フォトダイオード P D a 上には、開口部 A P が形成される。なお、遮光部 M S は、配線層 M L Y の最下層以外に形成されてもよいし、配線と兼用されてもよい。例えば

50

、配線は、遮光部 M S が設けられる層と別の層に形成されてもよいし、遮光部 M S が設けられる層と同じ層に形成されてもよい。

#### 【 0 0 2 2 】

配線層 M L Y 上には、カラーフィルタとして機能する光学フィルタ O F L が配置される。図 3 では、緑色 ( G b ) および青色 ( B ) のカラーフィルタとしてそれぞれ機能する光学フィルタ O F L が交互に配置されている。光学フィルタ O F L 上には、平坦層 P L Y が形成されている。そして、平坦層 P L Y 上にマイクロレンズ M L N が配置されている。例えば、撮像用画素 P X I では、フォトダイオード P D a は、マイクロレンズ M L N 、光学フィルタ O F L ( カラーフィルタ ) および開口部 A P を通過した光を受ける。

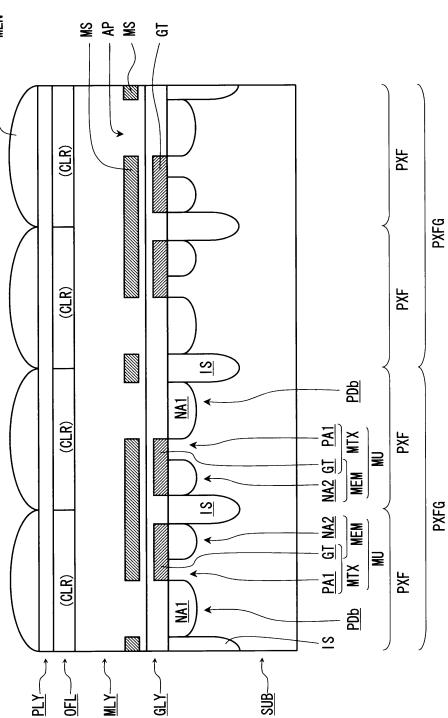

#### 【 0 0 2 3 】

図 4 は、図 2 に示した焦点検出用画素 P X F の B - B ' 線に沿う断面を示している。なお、図 4 では、配線等の記載を省略している。例えば、フォトダイオード P D b は、 p 型の半導体基板 S U B の受光面側 ( 図 4 では上側 ) に形成された n 型の半導体領域 N A 1 を有している。

#### 【 0 0 2 4 】

メモリ部 M U は、フォトダイオード P D b から転送される電荷を蓄積する蓄積部 M E M と、フォトダイオード P D b の電荷を蓄積部 M E M に転送するメモリ転送部 M T X とを有している。例えば、メモリ転送部 M T X は、 p 型の半導体基板 S U B に形成された n 型の半導体領域 N A 2 と、ゲート層 G L Y に形成されたゲート電極 G T の一部 ( 領域 N A 2 上の部分のゲート電極 G T ) とを有している。

#### 【 0 0 2 5 】

また、例えば、メモリ転送部 M T X は、領域 N A 1 、 N A 2 間に形成される p 型の半導体領域 P A 1 と、ゲート電極 G T の一部 ( 領域 P A 1 上の部分のゲート電極 G T ) と有している。すなわち、メモリ転送部 M T X は、蓄積部 M E M とフォトダイオード P D b との間に形成される。なお、絶縁部 I S は、互いに隣接する領域 N A 1 間と、互いに隣接する領域 N A 2 間とにそれぞれ形成される。すなわち、領域 N A 1 、 P A 1 、 N A 2 は、絶縁部 I S 間に形成される。

#### 【 0 0 2 6 】

ここで、例えば、フォトダイオード P D b の領域 N A 1 、メモリ転送部 M T X の領域 P A 1 および蓄積部 M E M の領域 N A 2 の不純物濃度は、互いに異なる。領域 N A 1 、 P A 1 、 N A 2 の不純物濃度は、例えば、後述する図 9 、図 10 に示すポテンシャルの関係を実現するように、それぞれ設定される。例えば、ゲート電極 G T の電圧が接地電圧 G N D のときの蓄積部 M E M のポテンシャルがフォトダイオード P D b のポテンシャルとフローティングディフュージョン F D のポテンシャルとの間に位置するように、領域 N A 1 、 N A 2 の不純物濃度は、それぞれ設定される。なお、領域 P A 1 の不純物濃度は、半導体基板 S U B の不純物濃度と異なっていてもよいし、半導体基板 S U B の不純物濃度と同じでもよい。

#### 【 0 0 2 7 】

半導体基板 S U B 上には、ゲート層 G L Y が形成される。上述したように、蓄積部 M E M およびメモリ転送部 M T X のゲート電極 G T は、ゲート層 G L Y に形成される。例えば、蓄積部 M E M およびメモリ転送部 M T X のゲート電極 G T は、互いに共通に設けられている。なお、蓄積部 M E M およびメモリ転送部 M T X のゲート電極 G T は、互いに分離して設けられてもよい。また、例えば、ゲート層 G L Y には、蓄積部 M E M およびメモリ転送部 M T X のゲート電極 G T とは別に、上述した図 2 に示した回路部 C I R U のトランジスタのゲート電極等が形成される。

#### 【 0 0 2 8 】

そして、ゲート層 G L Y 上には、複数の層を有する配線層 M L Y が設けられる。例えば、遮光部 M S は、配線層 M L Y の最下層 ( 半導体基板 S U B 側の層 ) に金属膜等で形成され、フォトダイオード P D b 以外の領域 ( メモリ部 M U 、絶縁部 I S 等 ) に対応する位置に配置される。すなわち、フォトダイオード P D b 上には、開口部 A P が形成される。こ

10

20

30

40

50

のように、焦点検出用画素 P X F は、メモリ部 M U を遮光する遮光部 M S を有している。なお、遮光部 M S は、配線層 M L Y の最下層以外に形成されてもよいし、配線と兼用されてもよい。例えば、配線は、遮光部 M S が設けられる層と別の層に形成されてもよいし、遮光部 M S が設けられる層と同じ層に形成されてもよい。

#### 【 0 0 2 9 】

配線層 M L Y 上には、例えば、青色の波長から赤色の波長までの光を透過する光学フィルタ O F L ( C L R ) が配置される。光学フィルタ O F L 上には、平坦層 P L Y が形成されている。そして、平坦層 P L Y 上にマイクロレンズ M L N が配置されている。例えば、焦点検出用画素 P X F では、フォトダイオード P D b は、マイクロレンズ M L N 、光学フィルタ O F L ( C L R ) および開口部 A P を通過した光を受ける。また、フォトダイオード P D b で生成された電荷は、例えば、ゲート電極 G T を制御することにより、メモリ転送部 M T X を介して蓄積部 M E M に転送される。したがって、この実施形態では、焦点検出用画素 P X F のフォトダイオード P D b で生成された電荷を蓄積部 M E M に蓄積できる。

#### 【 0 0 3 0 】

なお、フォトダイオード P D b 、メモリ転送部 M T X および蓄積部 M E M 等の半導体の導電型は、この例に限定されない。

#### 【 0 0 3 1 】

図 5 は、図 1 に示した制御部 C N T の概要を示している。なお、図 5 は、n 行 m 列の画素アレイ A R Y の撮像用画素 P X I および焦点検出用画素 P X F の動作を制御する制御部 C N T の概要を示している。例えば、焦点検出用画素 P X F は、4 行目の 2 列目から “m - 1” 列目に配置されている。

#### 【 0 0 3 2 】

制御部 C N T は、例えば、垂直走査回路 V S C およびタイミングジェネレータ T G を有している。垂直走査回路 V S C は、制御信号 R S T 、 T R 、 S E L を用いて、画素アレイ A R Y の撮像用画素 P X I を行毎に制御する。例えば、垂直走査回路 V S C は、制御信号 R S T ( 1 ) 、 T R ( 1 ) 、 S E L ( 1 ) を制御し、1 行目の撮像用画素 P X I を制御する。また、例えば、垂直走査回路 V S C は、制御信号 R S T ( 4 ) 、 T R ( 4 ) 、 S E L ( 4 ) を制御し、4 行目の 1 列目および m 列目の撮像用画素 P X I を制御する。

#### 【 0 0 3 3 】

さらに、垂直走査回路 V S C は、制御信号 R S T \_ f 、 T R \_ f 、 T X \_ f 、 S E L \_ f を用いて、画素アレイ A R Y の焦点検出用画素 P X F を、撮像用画素 P X I とは独立に制御する。例えば、垂直走査回路 V S C は、制御信号 R S T \_ f ( 4 ) 、 T R \_ f ( 4 ) 、 T X \_ f ( 4 ) 、 S E L \_ f ( 4 ) を制御し、4 行目の焦点検出用画素 P X F を制御する。以下、制御信号 R S T 、 R S T \_ f をリセット信号 R S T とも称する。また、制御信号 T R 、 T R \_ f を転送信号 T R とも称する。制御信号 S E L 、 S E L \_ f を選択信号 S E L とも称する。さらに、制御信号 T X \_ f をメモリ転送信号 T X \_ f とも称する。

#### 【 0 0 3 4 】

タイミングジェネレータ T G は、例えば、垂直走査回路 V S C に駆動クロック等を供給し、垂直走査回路 V S C の制御信号 R S T 、 T R 、 S E L 、 R S T \_ f 、 T R \_ f 、 T X \_ f 、 S E L \_ f の出力タイミングを制御する。なお、タイミングジェネレータ T G は、撮像装置 I M U とは別に設けられてもよい。すなわち、撮像装置 I M U は、図 5 の構成からタイミングジェネレータ T G が省かれた構成でもよい。

#### 【 0 0 3 5 】

ここで、画素アレイ A R Y は、各画素（撮像用画素 P X I および焦点検出用画素 P X F ）の出力信号 O U T を出力するための垂直信号線 V L を有している。例えば、列方向（図の縦方向）に配置された複数の画素（撮像用画素 P X I および焦点検出用画素 P X F ）は、列毎に設けられた垂直信号線 V L に接続されている。また、各垂直信号線 V L には、各画素からの出力信号 O U T を読み出すために、後述する図 6 、図 7 に示す定電流源 C S が接続されている。

10

20

30

40

50

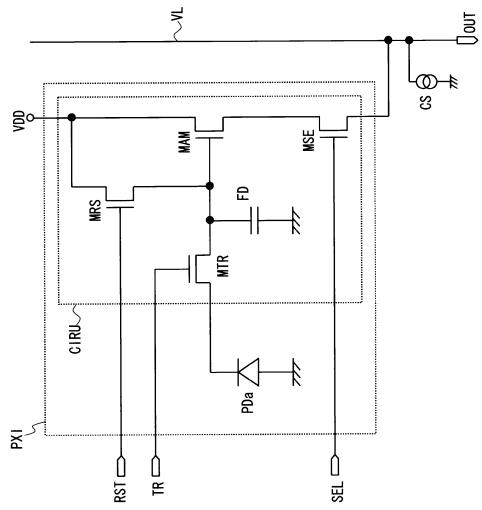

## 【0036】

図6は、図1に示した撮像用画素P XIの構成の一例を示している。撮像用画素P XIは、フォトダイオードP Daおよび回路部C IR Uを有している。回路部C IR Uは、例えば、転送トランジスタM TR、増幅トランジスタM AM、画素選択トランジスタM SE、リセットトランジスタM RSおよびフローティングディフュージョンFD(フローティングディフュージョン領域)を有している。例えば、回路部C IR U内に形成されるトランジスタM TR、M AM、M SE、M RSは、全てn MOSトランジスタである。

## 【0037】

フォトダイオードP Daは、アノードが接地され、カソードが転送トランジスタM TRのソースに接続されている。転送トランジスタM TRは、ゲートに印加される転送信号TRが高レベルの期間にオンし、フォトダイオードP Daに蓄積されている信号電荷をフローティングディフュージョンFDに転送する。10

## 【0038】

フローティングディフュージョンFDは、フォトダイオードP Daから転送される電荷を蓄積する寄生容量が形成される領域(トランジスタM TRのドレイン領域、トランジスタM TR、M AM間の配線領域、トランジスタM AMのゲート領域、リセットトランジスタM RSのソース領域等)である。したがって、フォトダイオードP Daから転送された信号電荷は、フローティングディフュージョンFDに蓄積される。

## 【0039】

増幅トランジスタM AMは、ソースが画素選択トランジスタM SEのドレインに接続され、ドレインが電源V DDに接続され、ゲートが転送トランジスタM TRのドレインに接続されている。すなわち、フローティングディフュージョンFDに転送された信号電荷に応じた電圧は、増幅トランジスタM AMのゲートに入力される。そして、増幅トランジスタM AMは、例えば、ゲートの電圧から増幅トランジスタM AMの閾値電圧分降下した電圧を、ソースから出力する。このように、増幅トランジスタM AMは、フローティングディフュージョンFDに転送された信号電荷に応じた信号を生成する。20

## 【0040】

画素選択トランジスタM SEは、ゲートに印加される選択信号SELが高レベルの期間にオンし、ソースに接続された垂直信号線VLと増幅トランジスタM AMのソースとの間を導通させる。したがって、画素選択トランジスタM SEがオンの期間では、増幅トランジスタM AMと、画素選択トランジスタM SEと、垂直信号線VLに接続された定電流源CSにより、ソースフォロア回路が構成される。これにより、画素選択トランジスタM SEにより選択された撮像用画素P XIの信号が、垂直信号線VLに出力される。30

## 【0041】

リセットトランジスタM RSは、ソースが増幅トランジスタM AMのゲートに接続され、ドレインが電源V DDに接続されている。例えば、リセットトランジスタM RSは、ゲートに印加されるリセット信号RSTが高レベルの期間にオンし、フローティングディフュージョンFDの電荷をリセットする。

## 【0042】

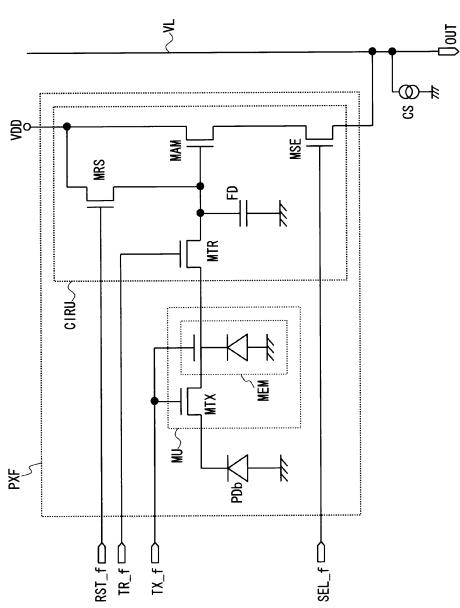

図7は、図1に示した焦点検出用画素P XFの構成の一例を示している。焦点検出用画素P XFは、フォトダイオードP Db、メモリ部MUおよび回路部C IR Uを有している。焦点検出用画素P XFの回路部C IR Uの構成は、制御信号および転送トランジスタM TRのソースの接続先を除いて、撮像用画素P XIの回路部C IR Uの構成と同じである。このため、回路部C IR Uについては、詳細な説明を省略する。例えば、制御信号RST\_f、TR\_f、SEL\_fは、図6に示した制御信号RST、TR、SELにそれぞれ対応している。40

## 【0043】

フォトダイオードP Dbは、アノードが接地され、カソードがメモリ転送部MTXに接続されている。メモリ部MUは、メモリ転送部MTXおよび蓄積部MEMを有している。例えば、メモリ転送部MTXは、n MOSトランジスタであり、ドレインが蓄積部MEM50

に接続され、ソースがフォトダイオード P D b のカソードに接続され、ゲートでメモリ転送信号 T X \_ f を受ける。以下、メモリ転送部 M T X をメモリ転送トランジスタ M T X とも称する。例えば、メモリ転送トランジスタ M T X は、メモリ転送信号 T X \_ f が高レベルの期間にオンし、フォトダイオード P D b により生成された信号電荷を蓄積部 M E M に転送する。

#### 【 0 0 4 4 】

蓄積部 M E M は、例えば、M O S 構造で形成され、ゲート電極の下に形成されるポテンシャル井戸に電荷を蓄積する。例えば、蓄積部 M E M は、フォトダイオード P D b に蓄積される電荷の量より多い量の電荷を蓄積できるポテンシャル井戸を有している。なお、蓄積部 M E M のゲート電極（ポテンシャル井戸上のゲート電極）は、例えば、メモリ転送信号 T X \_ f により制御される。10

#### 【 0 0 4 5 】

この実施形態では、蓄積部 M E M のゲート電極とメモリ転送トランジスタ M T X のゲートとが共通のメモリ転送信号 T X \_ f により制御されるため、メモリ部 M U の動作の制御を簡易にできる。なお、例えば、蓄積部 M E M のゲート電極とメモリ転送トランジスタ M T X のゲートとが互いに分離された構成では、蓄積部 M E M のゲート電極は、メモリ転送トランジスタ M T X のゲートと異なる制御信号で制御されてもよい。

#### 【 0 0 4 6 】

転送トランジスタ M T R は、ドレインが増幅トランジスタ M A M のゲートに接続され、ソースが蓄積部 M E M に接続され、ゲートで転送信号 T R \_ f を受ける。例えば、転送トランジスタ M T R は、転送信号 T R \_ f が高レベルの期間にオンし、フォトダイオード P D b により生成された信号電荷を、メモリ部 M U を介してフローティングディフュージョン F D に転送する。あるいは、例えば、転送信号 T R \_ f が高レベルの期間に、転送トランジスタ M T R は、蓄積部 M E M に蓄積された信号電荷をフローティングディフュージョン F D に転送する。20

#### 【 0 0 4 7 】

増幅トランジスタ M A M は、ソースが画素選択トランジスタ M S E のドレインに接続され、ドレインが電源 V D D に接続され、ゲートが転送トランジスタ M T R のドレインに接続されている。画素選択トランジスタ M S E は、ゲートに印加される選択信号 S E L \_ f が高レベルの期間にオンし、垂直信号線 V L と増幅トランジスタ M A M のソースとの間を導通させる。これにより、画素選択トランジスタ M S E により選択された焦点検出用画素 P X F の信号が、垂直信号線 V L に出力される。30

#### 【 0 0 4 8 】

リセットトランジスタ M R S は、ソースが増幅トランジスタ M A M のゲートに接続され、ドレインが電源 V D D に接続されている。例えば、リセットトランジスタ M R S は、ゲートに印加されるリセット信号 R S T \_ f が高レベルの期間にオンし、フローティングディフュージョン F D の電荷をリセットする。

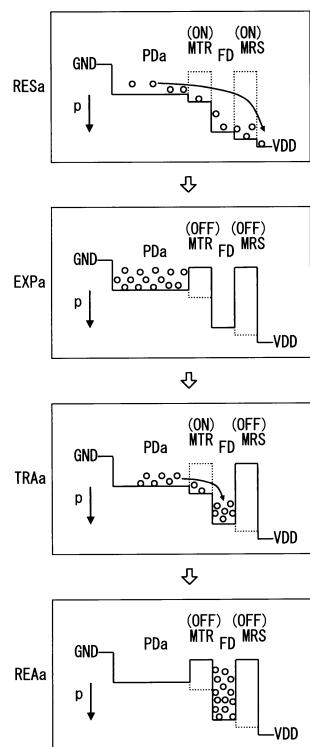

#### 【 0 0 4 9 】

図 8 は、図 6 に示した撮像用画素 P X I の動作の一例を示している。図中の符号 p は、ポテンシャル（電位）を示している。なお、図中の破線は、トランジスタの状態（オン・オフ）が切り替わる前のポテンシャルを示している。40

#### 【 0 0 5 0 】

リセット期間 R E S a では、転送信号 T R およびリセット信号 R S T は、高レベルに維持され、転送トランジスタ M T R およびリセットトランジスタ M R S は、オン（O N）状態に維持される。これにより、フォトダイオード P D a およびフローティングディフュージョン F D に蓄積された電荷は、電源 V D D に排出される。

#### 【 0 0 5 1 】

露光期間 E X P a では、転送信号 T R およびリセット信号 R S T は、低レベルに維持され、転送トランジスタ M T R およびリセットトランジスタ M R S は、オフ（O F F）状態に維持される。これにより、フォトダイオード P D a は、入射光に応じて電荷を生成し、50

生成した電荷を蓄積する。

**【0052】**

転送期間 T R A a では、転送信号 T R およびリセット信号 R S T は、それぞれ高レベルおよび低レベルに維持される。したがって、転送期間 T R A a では、転送トランジスタ M T R およびリセットトランジスタ M R S は、それぞれオン状態およびオフ状態に維持される。これにより、フォトダイオード P D a に蓄積された電荷は、フローティングディフュージョン F D に転送される。なお、リセットトランジスタ M R S がオフ状態であるため、フローティングディフュージョン F D に転送された電荷は、電源 V D D に排出されない。

**【0053】**

読み出し期間 R E A a では、転送信号 T R およびリセット信号 R S T は、低レベルに維持され、転送トランジスタ M T R およびリセットトランジスタ M R S はオフ状態に維持される。これにより、フォトダイオード P D a からフローティングディフュージョン F D に転送された電荷は、フローティングディフュージョン F D に蓄積される。さらに、読み出し期間 R E A a では、選択信号 S E L が高レベルに維持され、フローティングディフュージョン F D に蓄積された信号電荷に応じた電圧が垂直信号線 V L に出力される。

**【0054】**

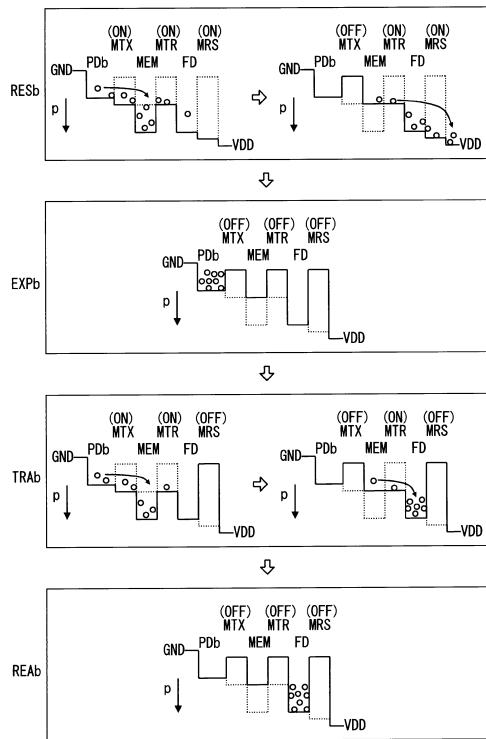

図 9 は、図 7 に示した焦点検出用画素 P X F の動作の一例を示している。なお、図 9 は、蓄積部 M E M に電荷を蓄積しないときの焦点検出用画素 P X F の動作の一例を示している。図中の破線の意味は、上述した図 8 と同じである。

**【0055】**

リセット期間 R E S b では、メモリ転送信号 T X \_ f 、転送信号 T R およびリセット信号 R S T は、高レベルに一定期間維持される（リセット期間 R E S b のうちの左側の図）。これにより、メモリ転送トランジスタ M T X 、転送トランジスタ M T R およびリセットトランジスタ M R S はオン（ON）状態に一定期間維持される。高レベルのメモリ転送信号 T X \_ f が蓄積部 M E M のゲート電極 G T に印加されているため、蓄積部 M E M のポテンシャルは、フォトダイオード P D b のポテンシャルより電源 V D D 側に維持される。これにより、フォトダイオード P D b に蓄積された電荷は、少なくとも蓄積部 M E M に移動する。

**【0056】**

メモリ転送信号 T X \_ f 、転送信号 T R およびリセット信号 R S T が高レベルに一定期間維持された後、メモリ転送信号 T X \_ f は、高レベルから低レベルに変化する。そして、メモリ転送信号 T X \_ f 、転送信号 T R およびリセット信号 R S T は、それぞれ低レベル、高レベルおよび高レベルに維持される（リセット期間 R E S b のうちの右側の図）。これにより、メモリ転送トランジスタ M T X 、転送トランジスタ M T R およびリセットトランジスタ M R S は、それぞれオフ（OFF）状態、オン状態およびオン状態に維持される。

**【0057】**

低レベルのメモリ転送信号 T X \_ f が蓄積部 M E M のゲート電極 G T に印加されているため、蓄積部 M E M のポテンシャルは、フローティングディフュージョン F D のポテンシャルより接地電圧 G N D 側に維持される。これにより、蓄積部 M E M およびフローティングディフュージョン F D に蓄積された電荷は、電源 V D D に排出される。この結果、リセット期間 R E S b では、フォトダイオード P D b 、蓄積部 M E M およびフローティングディフュージョン F D に蓄積された電荷は、電源 V D D に排出される。

**【0058】**

露光期間 E X P b では、メモリ転送信号 T X \_ f 、転送信号 T R およびリセット信号 R S T は、低レベルに維持され、メモリ転送トランジスタ M T X 、転送トランジスタ M T R およびリセットトランジスタ M R S はオフ状態に維持される。これにより、フォトダイオード P D b は、入射光に応じて電荷を生成し、生成した電荷を蓄積する。

**【0059】**

転送期間 T R A b では、メモリ転送信号 T X \_ f 、転送信号 T R およびリセット信号 R

10

20

30

40

50

S Tは、それぞれ高レベル、高レベルおよび低レベルに一定期間維持される（転送期間T R A bのうちの左側の図）。これにより、メモリ転送トランジスタM T X、転送トランジスタM T RおよびリセットトランジスタM R Sは、それぞれオン状態、オン状態およびオフ状態に一定期間維持される。高レベルのメモリ転送信号T X \_ fが蓄積部M E Mのゲート電極G Tに印加されているため、蓄積部M E Mのポテンシャルは、フォトダイオードP D bのポテンシャルより電源V D D側に維持される。これにより、フォトダイオードP D bに蓄積された電荷は、蓄積部M E Mに移動する。

#### 【0060】

メモリ転送信号T X \_ f、転送信号T Rおよびリセット信号R S Tがそれぞれ高レベル、高レベルおよび低レベルに一定期間維持された後、メモリ転送信号T X \_ fは、高レベルから低レベルに変化する。そして、メモリ転送信号T X \_ f、転送信号T Rおよびリセット信号R S Tは、それぞれ低レベル、高レベルおよび低レベルに維持される（転送期間T R A bのうちの右側の図）。これにより、メモリ転送トランジスタM T X、転送トランジスタM T RおよびリセットトランジスタM R Sは、それぞれオフ状態、オン状態およびオフ状態に維持される。

10

#### 【0061】

低レベルのメモリ転送信号T X \_ fが蓄積部M E Mのゲート電極G Tに印加されているため、蓄積部M E Mのポテンシャルは、フローティングディフュージョンF Dのポテンシャルより接地電圧G N D側に維持される。これにより、フォトダイオードP D bから蓄積部M E Mに転送された電荷は、フローティングディフュージョンF Dに移動する。この結果、転送期間T R A bでは、フォトダイオードP D bに蓄積された電荷は、フローティングディフュージョンF Dに転送される。なお、リセットトランジスタM R Sがオフ状態であるため、フローティングディフュージョンF Dに転送された電荷は、電源V D Dに排出されない。

20

#### 【0062】

読み出し期間R E A bでは、メモリ転送信号T X \_ f、転送信号T Rおよびリセット信号R S Tは、低レベルに維持され、メモリ転送トランジスタM T X、転送トランジスタM T RおよびリセットトランジスタM R Sは、オフ状態に維持される。これにより、フォトダイオードP D bからフローティングディフュージョンF Dに転送された電荷は、フローティングディフュージョンF Dに蓄積される。さらに、読み出し期間R E A bでは、選択信号S E Lが高レベルに維持され、フローティングディフュージョンF Dに蓄積された信号電荷に応じた電圧が垂直信号線V Lに出力される。

30

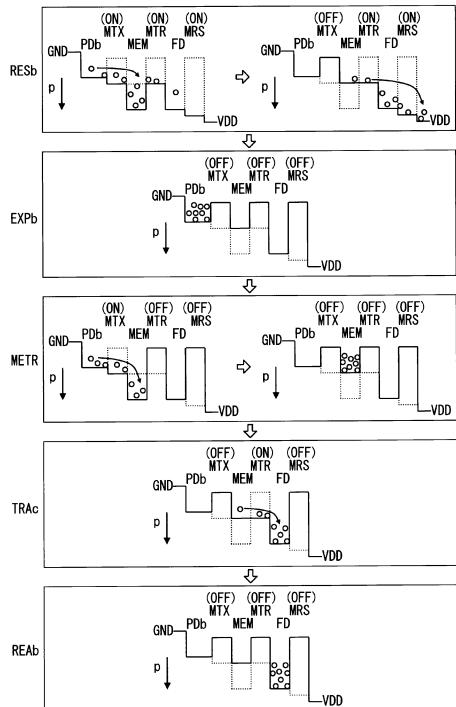

#### 【0063】

図10は、図7に示した焦点検出用画素P X Fの動作の別の例を示している。なお、図10は、蓄積部M E Mに電荷を蓄積するときの焦点検出用画素P X Fの動作の一例を示している。図中の破線の意味は、上述した図8と同じである。また、図10に示した焦点検出用画素P X Fの動作では、露光期間E X P bの後にメモリ転送期間M E T Rの動作が実施され、図9示した転送期間T R A bの動作の代わりに転送期間T R A cの動作が実施される。その他の動作は、図9に示した焦点検出用画素P X Fの動作と同じである。このため、メモリ転送期間M E T Rおよび転送期間T R A cについて説明する。

40

#### 【0064】

メモリ転送期間M E T Rでは、メモリ転送信号T X \_ f、転送信号T Rおよびリセット信号R S Tは、それぞれ高レベル、低レベルおよび低レベルに一定期間維持される（メモリ転送期間M E T Rのうちの左側の図）。これにより、メモリ転送トランジスタM T X、転送トランジスタM T RおよびリセットトランジスタM R Sは、それぞれオン状態、オフ状態およびオフ状態に一定期間維持される。

#### 【0065】

高レベルのメモリ転送信号T X \_ fが蓄積部M E Mのゲート電極G Tに印加されているため、蓄積部M E Mのポテンシャルは、フォトダイオードP D bのポテンシャルより電源V D D側に維持される。これにより、フォトダイオードP D bに蓄積された電荷は、蓄積

50

部MEMに移動する。なお、転送トランジスタMTRがオフ状態であるため、蓄積部MEMに転送された電荷は、フローティングディフュージョンFDに移動しない。

#### 【0066】

メモリ転送信号TX\_f、転送信号TRおよびリセット信号RSTがそれぞれ高レベル、低レベルおよび低レベルに一定期間維持された後、メモリ転送信号TX\_fは、高レベルから低レベルに変化する。そして、メモリ転送信号TX\_f、転送信号TRおよびリセット信号RSTは、低レベルに維持される（メモリ転送期間METRのうちの右側の図）。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、オフ状態に維持される。この結果、蓄積部MEMに電荷が蓄積される。このように、メモリ転送期間METRでは、露光期間EXPbにフォトダイオードPDbで生成された電荷が蓄積部MEMに蓄積される。以下、メモリ転送期間METRのうち、メモリ転送信号TX\_f、転送信号TRおよびリセット信号RSTが低レベルに維持される期間（メモリ転送期間METRのうちの右側の図）を、電荷保持期間とも称する。

10

#### 【0067】

転送期間TRAcでは、メモリ転送信号TX\_f、転送信号TRおよびリセット信号RSTは、それぞれ低レベル、高レベルおよび低レベルに維持される。したがって、転送期間TRAcでは、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、それぞれオフ状態、オン状態およびオフ状態に維持される。これにより、蓄積部MEMに蓄積された電荷（露光期間EXPbにフォトダイオードPDbで生成された電荷）は、フローティングディフュージョンFDに転送される。なお、リセットトランジスタMRSがオフ状態であるため、フローティングディフュージョンFDに転送された電荷は、電源VDDに排出されない。

20

#### 【0068】

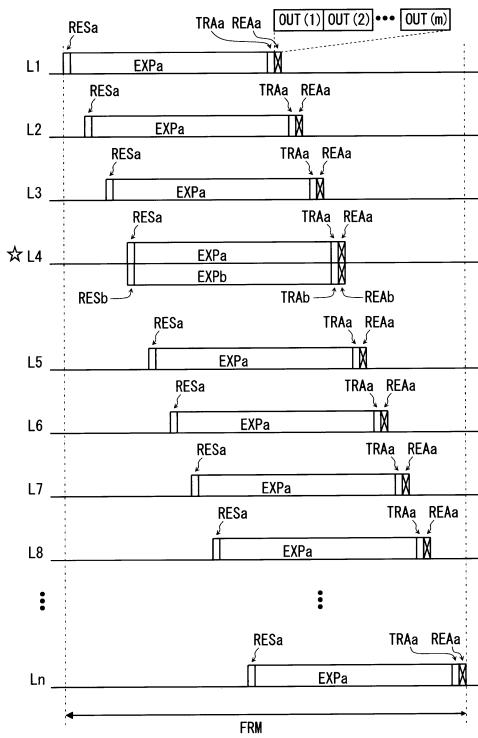

図11は、図5に示した画素アレイARYの動作の一例を示している。なお、図11は、焦点検出用画素PXFの露光期間EXPbが撮像用画素PXIの露光期間EXPaと同じときの画素アレイARYの動作の一例を示している。すなわち、図11は、蓄積部MEMに電荷を蓄積しないときの画素アレイARYの動作の一例を示している。図中の星印は、焦点検出用画素PXFを含む行を示している。例えば、焦点検出用画素PXFは、4行目（L4）に配置されている。したがって、4行目（L4）では、上側に撮像用画素PXIの動作を示し、下側に焦点検出用画素PXFの動作を示している。

30

#### 【0069】

垂直走査回路VSCは、例えば、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順に実施される一連の動作（上述した図8に示した動作）を、撮像用画素PXIに対して行毎に順次実施する。例えば、垂直走査回路VSCは、先ず、1行目（L1）の撮像用画素PXIに対して、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順にそれぞれの動作を実施する。これにより、読み出し期間REAaでは、1行目（L1）の各列の撮像用画素PXIの出力信号OUT（OUT(1)、OUT(2)、…、OUT(m)）が出力される。

40

#### 【0070】

そして、垂直走査回路VSCは、例えば、1行目（L1）のリセット期間RESaが終了した後に、2行目（L2）の撮像用画素PXIに対して、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順にそれぞれの動作を実施する。例えば、1行目（L1）の読み出し期間REAaが終了した後に2行目（L2）の転送期間TRAaが開始されるように、2行目（L2）のリセット期間RESaは、開始される。ここで、例えば、1行目（L1）のリセット期間RESaの開始から最終行（Ln）の読み出し期間REAaの終了までが、1フレームFRMである。

#### 【0071】

さらに、垂直走査回路VSCは、例えば、リセット期間RESb、露光期間EXPb、転送期間TRAb、読み出し期間REAbの順に実施される一連の動作（上述した図9に

50

示した動作)を、焦点検出用画素 P X F に対して実施する。例えば、垂直走査回路 V S C は、4 行目 (L 4) の撮像用画素 P X I の動作に合わせて、リセット期間 R E S b、露光期間 E X P b、転送期間 T R A b、読み出し期間 R E A b のそれぞれの動作を、4 行目 (L 4) の焦点検出用画素 P X F に対して実施する。

#### 【0072】

このように、この実施形態では、焦点検出用画素 P X F の蓄積部 M E M に電荷を蓄積しないとき、焦点検出用画素 P X F の動作を撮像用画素 P X I の動作に合わせて実施できるため、画素アレイ A R Y からの信号の読み出し動作を簡易にできる。なお、垂直走査回路 V S C は、図 16 に示すように、転送期間 T R A a、T R A b の前 (露光期間 E X P a、E X P b) に選択信号 S E L を高レベルにし、相關二重サンプリングのためのノイズ信号 10 を読み出してもよい。ここで、ノイズ信号は、例えば、画素 P X I、P X F のリセットノイズ成分等を含む固定ノイズ成分を示す信号である。

#### 【0073】

また、ノイズ信号等を読み出さない場合、各行の転送期間 T R A (T R A a、T R A b) は、前の行の読み出し期間 R E A (R E A a、R E A b) が終了する前に、開始されてもよい。例えば、垂直走査回路 V S C は、各行の読み出し期間 R E A の開始が前の行の読み出し期間 R E A の終了とほぼ同じタイミングになるように、転送期間 T R A を開始してもよい。

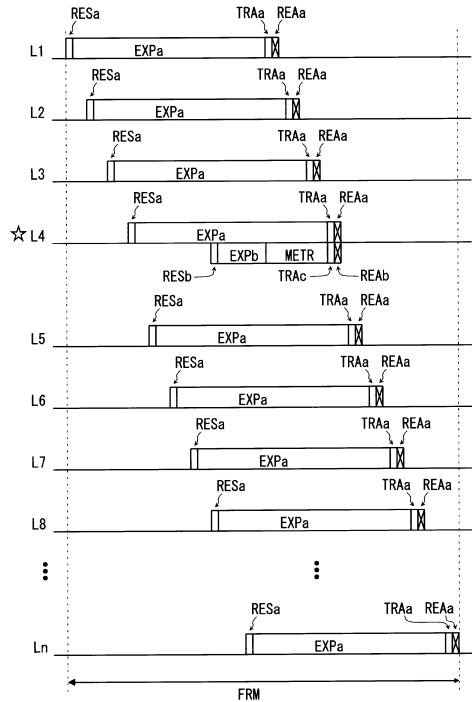

#### 【0074】

図 12 は、図 5 に示した画素アレイ A R Y の動作の別の例を示している。なお、図 12 は、焦点検出用画素 P X F の露光期間 E X P b が撮像用画素 P X I の露光期間 E X P a より短いときの画素アレイ A R Y の動作の一例を示している。すなわち、図 12 は、蓄積部 M E M に電荷を蓄積するときの画素アレイ A R Y の動作の一例を示している。図中の星印の意味は上述した図 11 と同じである。また、撮像用画素 P X I の動作は、図 11 と同じである。このため、焦点検出用画素 P X F の動作について説明する。 20

#### 【0075】

垂直走査回路 V S C は、例えば、リセット期間 R E S b、露光期間 E X P b、メモリ転送期間 M E T R、転送期間 T R A c、読み出し期間 R E A b の順に実施される一連の動作 (上述した図 10 に示した動作) を、焦点検出用画素 P X F に対して実施する。例えば、垂直走査回路 V S C は、4 行目 (L 4) の焦点検出用画素 P X F に対して、リセット期間 30 R E S b、露光期間 E X P b、メモリ転送期間 M E T R、転送期間 T R A c、読み出し期間 R E A b の順にそれぞれの動作を実施する。

#### 【0076】

例えば、垂直走査回路 V S C は、4 行目 (L 4) の撮像用画素 P X I の転送期間 T R A a と 4 行目 (L 4) の焦点検出用画素 P X F の転送期間 T R A c とが互いに同じタイミングになるように、メモリ転送期間 M E T R の電荷保持期間を調整する。なお、焦点検出用画素 P X F のリセット期間 R E S b の動作は、撮像用画素 P X I のリセット期間 R E S a に合わせて実施されてもよい。このときにも、垂直走査回路 V S C は、メモリ転送期間 M E T R の電荷保持期間を調整することにより、焦点検出用画素 P X F の転送期間 T R A c を撮像用画素 P X I の転送期間 T R A a に合わせることができる。このように、垂直走査回路 V S C は、蓄積部 M E M に電荷を蓄積することにより、焦点検出用画素 P X F の露光時間 (露光期間 E X P b) と撮像用画素 P X I の露光時間 (露光期間 E X P a) とをそれぞれ独立に制御する。これにより、この実施形態では、焦点検出用画素 P X F の露光を、1 フレーム F R M 内の任意のタイミングで任意の時間実施できる。 40

#### 【0077】

したがって、この実施形態では、焦点検出用画素 P X F の露光期間 E X P b が撮像用画素 P X I の露光期間 E X P a と異なるときにも、焦点検出用画素 P X F の転送期間 T R A c を撮像用画素 P X I の転送期間 T R A a に合わせることができる。これにより、この実施形態では、焦点検出用画素 P X F の露光期間 E X P b が撮像用画素 P X I の露光期間 E X P a と異なるときにも、焦点検出用画素 P X F の読み出し期間 R E A b を撮像用画素 P 50

X I の読み出し期間 R E A a に合わせることができる。この結果、この実施形態では、画素アレイ A R Y からの信号の読み出し動作を簡易にできる。

#### 【 0 0 7 8 】

なお、垂直走査回路 V S C は、図 1 7 に示すように、転送期間 T R A a 、 T R A c の前（露光期間 E X P a 、メモリ転送期間 M E T R ）に選択信号 S E L を高レベルにし、相関二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、フローティングディフィュージョン F D に電荷を転送するタイミングが撮像用画素 P X I と焦点検出用画素 P X F とで互いに同じであるため、簡易にノイズ信号を読み出すことができる。

#### 【 0 0 7 9 】

また、ノイズ信号等を読み出さない場合、各行の転送期間 T R A ( T R A a 、 T R A c ) は、前の行の読み出し期間 R E A ( R E A a 、 R E A b ) が終了する前に、開始されてもよい。例えば、垂直走査回路 V S C は、各行の読み出し期間 R E A の開始が前の行の読み出し期間 R E A の終了とほぼ同じタイミングになるように、転送期間 T R A を開始してもよい。

#### 【 0 0 8 0 】

図 1 3 は、複数の行に焦点検出用画素 P X F が配置された画素アレイ A R Y の動作の一例を示している。なお、図 1 3 は、4 行目 ( L 4 ) および 7 行目 ( L 7 ) に焦点検出用画素 P X F が配置された画素アレイ A R Y の動作の一例を示している。図中の星印の意味は上述した図 1 1 と同じである。また、撮像用画素 P X I の動作は、図 1 1 と同じである。このため、焦点検出用画素 P X F の動作について説明する。なお、例えば、焦点検出用画素 P X F の露光期間 E X P b は、撮像用画素 P X I の露光期間 E X P a より短い。

#### 【 0 0 8 1 】

垂直走査回路 V S C は、例えば、リセット期間 R E S b 、露光期間 E X P b 、メモリ転送期間 M E T R 、転送期間 T R A c 、読み出し期間 R E A b の順に実施される一連の動作（上述した図 1 0 に示した動作）を、4 行目 ( L 4 ) および 7 行目 ( L 7 ) の焦点検出用画素 P X F に対して実施する。

#### 【 0 0 8 2 】

例えば、垂直走査回路 V S C は、4 行目 ( L 4 ) の撮像用画素 P X I の転送期間 T R A a と 4 行目 ( L 4 ) の焦点検出用画素 P X F の転送期間 T R A c とが互いに同じタイミングになるように、4 行目 ( L 4 ) の焦点検出用画素 P X F のメモリ転送期間 M E T R の電荷保持期間を調整する。さらに、垂直走査回路 V S C は、4 行目 ( L 4 ) および 7 行目 ( L 7 ) の焦点検出用画素 P X F のそれぞれの露光期間 E X P b が互いに同じタイミングになるように、7 行目 ( L 7 ) の焦点検出用画素 P X F に対して、リセット期間 R E S b の動作を開始する。そして、垂直走査回路 V S C は、例えば、7 行目 ( L 7 ) の撮像用画素 P X I の転送期間 T R A a と 7 行目 ( L 7 ) の焦点検出用画素 P X F の転送期間 T R A c とが互いに同じタイミングになるように、7 行目 ( L 7 ) の焦点検出用画素 P X F のメモリ転送期間 M E T R の電荷保持期間を調整する。

#### 【 0 0 8 3 】

このように、垂直走査回路 V S C は、蓄積部 M E M に電荷を蓄積することにより、互いに異なる行に配置された焦点検出用画素 P X F の露光タイミングが互いに同じになるように、各行の焦点検出用画素 P X F の動作を制御する。すなわち、焦点検出用画素 P X F が複数の行に配置されたときにも、垂直走査回路 V S C は、複数の焦点検出用画素 P X F の露光タイミングが互いに同じになるように、複数の焦点検出用画素 P X F の動作を制御する。

#### 【 0 0 8 4 】

これにより、この実施形態では、焦点検出時の露光を互いに異なる行に配置された焦点検出用画素 P X F で同時に実施できる。この結果、この実施形態では、焦点検出精度を向上できる。さらに、この実施形態では、焦点検出用画素 P X F が複数の行に配置されたときにも、焦点検出用画素 P X F の読み出し期間 R E A b を撮像用画素 P X I の読み出し期間 R E A a に簡易に合わせることができるため、画素アレイ A R Y からの信号の読み出しき

10

20

30

40

50

動作を簡易にできる。

**【0085】**

なお、垂直走査回路VSCは、焦点検出用画素PXFが複数の行に配置されたときにも、図17に示すように、転送期間TRAa、TRAcの前（露光期間EXPa、メモリ転送期間METR）に選択信号SELを高レベルにし、相間二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、焦点検出用画素PXFが複数の行に配置されたときにも、互いに同じ行に配置された焦点検出用画素PXFおよび撮像用画素PXIのそれぞれの転送期間TRAc、TRAaを互いに合わせることができる。したがって、この実施形態では、焦点検出用画素PXFが複数の行に配置されたときにも、簡易にノイズ信号を読み出すことができる。

10

**【0086】**

また、ノイズ信号等を読み出さない場合、各行の転送期間TRA（TRAa、TRAc）は、前の行の読み出し期間REA（REAA、REAb）が終了する前に、開始されてもよい。例えば、垂直走査回路VSCは、各行の読み出し期間REAの開始が前の行の読み出し期間REAの終了とほぼ同じタイミングになるように、転送期間TRAを開始してもよい。

**【0087】**

図14は、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときの画素アレイARYの動作の一例を示している。図中の星印の意味は上述した図11と同じである。また、撮像用画素PXIの動作は、図11と同じである。このため、焦点検出用画素PXFの動作について説明する。なお、例えば、焦点検出用画素PXFの露光期間EXPbは、撮像用画素PXIの露光期間EXPaより短い。

20

**【0088】**

垂直走査回路VSCは、例えば、4行目（L4）の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAb、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施する。なお、1フレームFRM中に実施される焦点検出用画素PXFの露光の回数は、2回に限定されない。この実施形態では、焦点検出用画素PXFの独立露光および独立読み出しが可能であるため、焦点検出用画素PXFの任意時間の露光を、1フレームFRM内で複数回実施できる。

30

**【0089】**

例えば、図14の動作では、焦点検出用画素PXFの信号（焦点検出に用いられる信号）は、1フレームFRM中に複数回出力される。したがって、この実施形態では、1フレームFRM中に複数回の焦点検出を実施でき、高速な焦点検出を実現できる。なお、垂直走査回路VSCは、1回目のメモリ転送期間METRおよび転送期間TRAcの動作を実施する代わりに、転送期間TRAbの動作を実施してもよい。また、垂直走査回路VSCは、上述した図9に示した動作と上述した図10に示した動作とを1フレームFRM中に順に実施してもよい。あるいは、垂直走査回路VSCは、上述した図9や図10に示した動作を1フレームFRM中に複数回繰り返し実施してもよい。

**【0090】**

ここで、例えば、焦点検出用画素PXFのフォトダイオードPDbに蓄積される電荷の量より多い量の電荷を十分に蓄積できるポテンシャル井戸を焦点検出用画素PXFの蓄積部MEMが有しているとき、1回目の転送期間TRAcおよび読み出し期間REAbの動作は、省かれてもよい。例えば、垂直走査回路VSCは、4行目（L4）の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPb、メモリ転送期間METR、露光期間EXPb、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施してもよい。この場合、フォトダイオードPDbに蓄積された電荷が溢れる前に、フォトダイオードPDbの電荷を蓄積部MEMに転送できる。この結果、この実施形態では、フォトダイオードPDbに蓄積された電荷が溢れることを防止でき、焦点検出精度を向上できる。例えば、この実施形態では、高輝度の被写体の焦点

40

50

検出および高照度の環境下での焦点検出を精度よく実施できる。

#### 【0091】

また、垂直走査回路VSCは、4行目(L4)の撮像用画素PIXIの転送期間TRAaと4行目(L4)の焦点検出用画素PXFの転送期間TRAcが互いに同じタイミングになるように、4行目(L4)の焦点検出用画素PXFの2回目のメモリ転送期間METRの電荷保持期間を調整する。これにより、この実施形態では、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、画素アレイARRYからの信号の読み出し動作を簡易にできる。

#### 【0092】

また、垂直走査回路VSCは、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、図17に示すように、転送期間TRAa、TRAcの前(露光期間EXPa、メモリ転送期間METR)に選択信号SELを高レベルにし、相關二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、焦点検出用画素PXFの転送期間TRAcを撮像用画素PIXIの転送期間TRAaに合わせることができる。したがって、この実施形態では、焦点検出用画素PXFの露光が1フレームFRM中に複数回実施されるときにも、簡易にノイズ信号を読み出すことができる。

10

#### 【0093】

なお、ノイズ信号等を読み出さない場合、各行の転送期間TRA(TRAc)は、前の行の読み出し期間REA(REAa、REAb)が終了する前に、開始されてもよい。例えば、垂直走査回路VSCは、各行の読み出し期間REAの開始が前の行の読み出し期間REAの終了とほぼ同じタイミングになるように、転送期間TRAを開始してもよい。

20

#### 【0094】

図15は、焦点検出用画素PXFの露光が複数フレームFRMをまたいで実施されるときの画素アレイARRYの動作の一例を示している。図中の星印の意味は上述した図11と同じである。また、撮像用画素PIXIの動作は、図11と同じである。このため、焦点検出用画素PXFの動作について説明する。なお、例えば、焦点検出用画素PXFの露光期間EXPbは、撮像用画素PIXIの露光期間EXPaより長い。

#### 【0095】

30

フレームFRM(1)の期間では、垂直走査回路VSCは、例えば、4行目(L4)の撮像用画素PIXIに対して露光期間EXPaの動作を実施しているときに、4行目(L4)の焦点検出用画素PXFに対して、リセット期間RESb、露光期間EXPbの順にそれぞれの動作を実施する。なお、4行目(L4)の焦点検出用画素PXFの露光期間EXPbの動作は、フレームFRM(2)の途中まで継続される。

#### 【0096】

例えば、フレームFRM(1)の最後の読み出し期間REAaの動作が最終行(Ln)の撮像用画素PIXIに対して実施された後に、フレームFRM(2)の最初のリセット期間RESaの動作が、1行目(L1)の撮像用画素PIXIに対して実施される。すなわち、垂直走査回路VSCは、例えば、最終行(Ln)の読み出し期間REAaの後に、1行目(L1)の撮像用画素PIXIに対して、リセット期間RESa、露光期間EXPa、転送期間TRAa、読み出し期間REAaの順にそれぞれの動作を実施する。

40

#### 【0097】

フレームFRM(2)の期間では、垂直走査回路VSCは、例えば、4行目(L4)の撮像用画素PIXIに対して露光期間EXPaの動作を実施しているときに、4行目(L4)の焦点検出用画素PXFに対する露光期間EXPbの動作を終了する。すなわち、垂直走査回路VSCは、例えば、4行目(L4)の撮像用画素PIXIの動作を制御しているときに、4行目(L4)の焦点検出用画素PXFに対して、メモリ転送期間METR、転送期間TRAc、読み出し期間REAbの順にそれぞれの動作を実施する。

#### 【0098】

50

この実施形態では、焦点検出用画素 P X F の独立露光および独立読み出しが可能であるため、焦点検出用画素 P X F の任意時間の露光を、複数フレーム F R M にまたいで実施できる。このように、この実施形態では、複数フレーム F R M をまたいで焦点検出用画素 P X F の露光を実施することにより、撮像用画素 P X I の露光時間に拘わらず、長時間の露光を焦点検出用画素 P X F に対して実施できる。これにより、この実施形態では、低輝度の被写体の焦点検出および低照度の環境下での焦点検出を精度よく実施できる。

#### 【 0 0 9 9 】

また、フレーム F R M ( 2 ) の期間では、垂直走査回路 V S C は、4 行目 ( L 4 ) の撮像用画素 P X I の転送期間 T R A a と 4 行目 ( L 4 ) の焦点検出用画素 P X F の転送期間 T R A c とが互いに同じタイミングになるように、4 行目 ( L 4 ) の焦点検出用画素 P X F のメモリ転送期間 M E T R の電荷保持期間を調整する。これにより、この実施形態では、焦点検出用画素 P X F の露光が複数フレーム F R M をまたいで実施されるときにも、画素アレイ A R Y からの信号の読み出し動作を簡易にできる。なお、焦点検出用画素 P X F の露光は、3 フレーム F R M 以上またいで実施されてもよい。

10

#### 【 0 1 0 0 】

また、垂直走査回路 V S C は、焦点検出用画素 P X F の露光が複数フレーム F R M をまたいで実施されるときにも、図 17 に示すように、転送期間 T R A a 、 T R A c の前 ( 露光期間 E X P a 、メモリ転送期間 M E T R ) に選択信号 S E L を高レベルにし、相關二重サンプリングのためのノイズ信号を読み出してもよい。この実施形態では、焦点検出用画素 P X F の露光が複数フレーム F R M をまたいで実施されるときにも、焦点検出用画素 P X F の転送期間 T R A c を撮像用画素 P X I の転送期間 T R A a に合わせることができる。したがって、この実施形態では、焦点検出用画素 P X F の露光が複数フレーム F R M をまたいで実施されるときにも、簡易にノイズ信号を読み出すことができる。

20

#### 【 0 1 0 1 】

なお、ノイズ信号等を読み出さない場合、各行の転送期間 T R A ( T R A a 、 T R A c ) は、前の行の読み出し期間 R E A ( R E A a 、 R E A b ) が終了する前に、開始されてもよい。例えば、垂直走査回路 V S C は、各行の読み出し期間 R E A の開始が前の行の読み出し期間 R E A の終了とほぼ同じタイミングになるように、転送期間 T R A を開始してもよい。

#### 【 0 1 0 2 】

30

図 16 は、相關二重サンプリングが実施されるときの画素アレイ A R Y の動作の一例を示している。図中の三角形は、焦点検出用画素 P X F を含む行 ( L 4 ) の撮像用画素 P X I の動作を示している。また、星印は、焦点検出用画素 P X F を含む行 ( L 4 ) の焦点検出用画素 P X F の動作を示している。図 16 の動作は、転送期間 T R A ( T R A a 、 T R A b ) の前にフローティングディフュージョン F D をリセットしている点が図 11 の動作と相違する。

#### 【 0 1 0 3 】

例えば、4 行目 ( L 4 ) の撮像用画素 P X I および焦点検出用画素 P X F では、3 行目 ( L 3 ) の撮像用画素 P X I の読み出し期間 R E A a が終了したとき、選択信号 S E L ( 4 ) 、 S E L \_ f ( 4 ) が低レベルから高レベルに変化する ( 図 16 ( a ) 、 ( b ) ) 。そして、リセット信号 R S T ( 4 ) 、 R S T \_ f ( 4 ) が高レベルに一定期間 T 1 0 維持される。これにより、リセットトランジスタ M R S がオンし、フローティングディフュージョン F D がリセットされる。なお、選択信号 S E L ( 4 ) 、 S E L \_ f ( 4 ) が高レベルに維持されているため、リセットされたフローティングディフュージョン F D のポテンシャルに応じた電圧 ( ノイズ信号 ) が、垂直信号線 V L に出力される。

40

#### 【 0 1 0 4 】

垂直信号線 V L に出力されたノイズ信号は、例えば、期間 T 2 0 に読み出される。なお、ノイズ信号は、リセット信号 R S T 、 R S T \_ f が高レベルの期間に読み出されてもよい。ノイズ信号が読み出された後、転送期間 T R A ( T R A a 、 T R A b ) に、フォトダイオード P D ( P D a 、 P D b ) に蓄積された電荷がフローティングディフュージョン F

50

Dに転送される。なお、転送期間TRAでは、リセットトランジスタMRSがオフ状態であるため、フローティングディフュージョンFDに転送された電荷は、電源VDDに排出されない。

#### 【0105】

例えば、撮像用画素PXIでは、ノイズ信号が読み出された後、転送信号TR(4)が高レベルに一定期間維持される。これにより、転送トランジスタMTRがオンし、フォトダイオードPDAに蓄積された電荷がフローティングディフュージョンFDに転送される。なお、転送トランジスタMTRがオンしているときにも、フォトダイオードPDAは露光されている。すなわち、フォトダイオードPDAは、転送信号TRが立ち下がる(図16(c))まで露光されている。したがって、撮像用画素PXIでは、転送信号TRが立ち下がるまでにフォトダイオードPDAに蓄積された電荷が、フローティングディフュージョンFDに転送される。10

#### 【0106】

また、例えば、焦点検出用画素PXFでは、ノイズ信号が読み出された後、転送信号TR\_f(4)およびメモリ転送信号TX\_f(4)が低レベルから高レベルに変化する。これにより、転送トランジスタMTRおよびメモリ転送トランジスタMTXがオンし、フォトダイオードPDbに蓄積された電荷は、少なくとも蓄積部MEMに移動する。そして、メモリ転送信号TX\_f(4)が高レベルから低レベルに変化してから一定期間後に、転送信号TR\_f(4)が高レベルから低レベルに変化する。転送トランジスタMTRがオンしている間に、蓄積部MEMの電荷がフローティングディフュージョンFDに転送される。20

#### 【0107】

なお、メモリ転送トランジスタMTXがオンしているときにも、フォトダイオードPDbは露光されている。すなわち、フォトダイオードPDbは、メモリ転送信号TX\_fが立ち下がる(図16(d))まで露光されている。したがって、焦点検出用画素PXFでは、メモリ転送信号TX\_fが立ち下がるまでにフォトダイオードPDbに蓄積された電荷が、フローティングディフュージョンFDに転送される。

#### 【0108】

読み出し期間REA(REAa、REAb)では、選択信号SEL(4)、SEL\_f(4)が高レベルに維持されているため、フローティングディフュージョンFDに転送された電荷に応じた電圧が垂直信号線VLに出力される。30

#### 【0109】

図17は、相關二重サンプリングが実施されるときの画素アレイARYの動作の別の例を示している。図中の三角形および星印の意味は、上述した図16と同じである。図17の動作は、転送期間TRA(TRAa、TRAc)の前にフローティングディフュージョンFDをリセットしている点が図12の動作と相違する。なお、撮像用画素PXIの動作は、図16に示した撮像用画素PXIの動作と同じである。このため、焦点検出用画素PXFの動作について説明する。

#### 【0110】

例えば、4行目(L4)の焦点検出用画素PXFでは、3行目(L3)の撮像用画素PXIの読み出し期間REAaが終了したとき、選択信号SEL\_f(4)が低レベルから高レベルに変化する(図17(b))。そして、リセット信号RST\_f(4)が高レベルに一定期間T10維持される。これにより、リセットトランジスタMRSがオンし、フローティングディフュージョンFDがリセットされる。なお、選択信号SEL\_f(4)が高レベルに維持されているため、リセットされたフローティングディフュージョンFDのポテンシャルに応じた電圧(ノイズ信号)が、垂直信号線VLに出力される。40

#### 【0111】

垂直信号線VLに出力されたノイズ信号は、例えば、期間T20に読み出される。ノイズ信号が読み出された後、転送期間TRAcにおいて、転送信号TR\_f(4)が高レベルに一定期間維持される。これにより、転送トランジスタMTRがオンし、蓄積部MEM

の電荷がフローティングディフュージョンFDに転送される。なお、蓄積部MEMには、メモリ転送期間METERに、フォトダイオードPDbから電荷が転送されている。

#### 【0112】

例えば、メモリ転送トランジスタMTXがオンしているときにも、フォトダイオードPD<sub>b</sub>は露光されている。すなわち、フォトダイオードPD<sub>b</sub>は、メモリ転送信号TX\_fが立ち下がる(図17(d))まで露光されている。したがって、焦点検出用画素PXFでは、メモリ転送信号TX\_fが立ち下がるまでにフォトダイオードPD<sub>b</sub>に蓄積された電荷が、蓄積部MEMを介してフローティングディフュージョンFDに転送される。なお、リセットトランジスタMRSがオフ状態であるため、フローティングディフュージョンFDに転送された電荷は、電源VDDに排出されない。

10

#### 【0113】

読み出し期間REA<sub>b</sub>では、選択信号SEL\_f(4)が高レベルに維持されているため、フローティングディフュージョンFDに転送された電荷に応じた電圧が垂直信号線VLに出力される。

#### 【0114】

ここで、フローティングディフュージョンFDをリセットする構成(図16や図17の動作を実施する構成)では、連写等によりフレームFRMが連続するとき、2番目以降のフレームFRMのリセット期間RESa、RESbの動作を省略してもよい。例えば、2番目以降のフレームFRMでは、前のフレームFRMの転送期間TRAやメモリ転送期間METERの動作により、フォトダイオードPDおよび蓄積部MEMがリセットされる。このため、2番目以降のフレームFRMでは、各画素は、フローティングディフュージョンFDをリセットすることにより、リセット期間RESの動作が実施されたときと同様の状態になる。また、フローティングディフュージョンFDのリセットは、メモリ転送期間METERに実施されてもよい。

20

#### 【0115】

図18は、フローティングディフュージョンをリセットするときの撮像用画素PXIの各部のポテンシャルの一例を示している。図中の破線の意味は、上述した図8と同じである。

#### 【0116】

フローティングディフュージョンをリセットするとき(例えば、図16や図17の期間T10)、転送信号TRおよびリセット信号RSTは、低レベルおよび高レベルにそれぞれ維持される。これにより、転送トランジスタMTRおよびリセットトランジスタMRSは、オフ状態およびオン状態にそれぞれ維持される。この結果、フローティングディフュージョンFDに蓄積された電荷は、電源VDDに排出される。なお、転送トランジスタMTRがオフ状態であるため、フォトダイオードPDaに蓄積された電荷は、電源VDDに排出されない。

30

#### 【0117】

図19は、フローティングディフュージョンをリセットするときの焦点検出用画素PXFの各部のポテンシャルの一例を示している。図中の破線の意味は、上述した図8と同じである。

40

#### 【0118】

フローティングディフュージョンをリセットするとき(例えば、図16や図17の期間T10)、メモリ転送信号TX\_f、転送信号TRおよびリセット信号RSTは、低レベル、低レベルおよび高レベルにそれぞれ維持される。これにより、メモリ転送トランジスタMTX、転送トランジスタMTRおよびリセットトランジスタMRSは、オフ状態、オフ状態およびオン状態にそれぞれ維持される。この結果、フローティングディフュージョンFDに蓄積された電荷は、電源VDDに排出される。なお、転送トランジスタMTRおよびメモリ転送トランジスタMTXがオフ状態であるため、フォトダイオードPDbや蓄積部MEMに蓄積された電荷は、電源VDDに排出されない。

#### 【0119】

50

以上、この実施形態では、撮像装置 I M U は、メモリ部 M U を含む焦点検出用画素 P X F を有している。例えば、メモリ部 M U は、フォトダイオード P D b から転送される電荷を蓄積する蓄積部 M E M と、フォトダイオード P D b の電荷を蓄積部 M E M に転送するメモリ転送部 M T X を有している。これにより、この実施形態では、焦点検出用画素 P X F の露光タイミングを適切に制御でき、焦点検出精度を向上できる。

#### 【 0 1 2 0 】

なお、上述した実施形態では、ゲート電極 G T の電圧が接地電圧 G N D のときの蓄積部 M E M のポテンシャルがフォトダイオード P D b のポテンシャルとフローティングディフュージョン F D のポテンシャルとの間に位置するように、領域 N A 1、N A 2 の不純物濃度がそれぞれ設定される例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、ゲート電極 G T の電圧が接地電圧 G N D のときの蓄積部 M E M のポテンシャルは、フォトダイオード P D b のポテンシャル以上でもよい。すなわち、蓄積部 M E M のポテンシャルは、ゲート電極 G T の電圧が接地電圧 G N D のとき、フローティングディフュージョン F D のポテンシャルより接地電圧 G N D 側に維持され、ゲート電極 G T の電圧が電源 V D D のとき、フォトダイオード P D b のポテンシャルより電源 V D D 側に維持されればよい。この場合にも、上述した実施形態と同様の効果を得ることができる。

10

#### 【 0 1 2 1 】

上述した実施形態では、蓄積部 M E M がゲート電極 G T を有する例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、蓄積部 M E M は、ゲート電極 G T を含まずに形成されてもよい。この場合、蓄積部 M E M のポテンシャルがフォトダイオード P D b のポテンシャルとフローティングディフュージョン F D のポテンシャルとの間に位置するように、領域 N A 1、N A 2 の不純物濃度は、それぞれ設定される。この場合にも、上述した実施形態と同様の効果を得ることができる。

20

#### 【 0 1 2 2 】

上述した実施形態では、回路部 C I R U が画素（撮像用画素 P X I、焦点検出用画素 P X F ）毎に設けられる例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、転送トランジスタ M T R を除く回路部 C I R U は、列方向に互いに隣接する複数の画素（撮像用画素 P X I、焦点検出用画素 P X F ）に共用されてもよい。すなわち、フローティングディフュージョン F D は、複数の画素（撮像用画素 P X I、焦点検出用画素 P X F ）に共用されてもよい。なお、転送トランジスタ M T R は、画素（撮像用画素 P X I、焦点検出用画素 P X F ）毎に設けられる。この場合にも、焦点検出用画素 P X F のフォトダイオード P D b で生成された電荷を蓄積部 M E M に蓄積できるため、上述した実施形態と同様の効果を得ることができる。

30

#### 【 0 1 2 3 】

上述した実施形態では、焦点検出用画素 P X F の制御信号 R S T \_ f、T R \_ f、S E L \_ f が撮像用画素 P X I の制御信号 R S T、T R、S E L とそれぞれ独立に制御される例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、焦点検出用画素 P X F の制御信号 S E L \_ f は、撮像用画素 P X I の制御信号 S E L と兼用されてもよい。この場合にも、上述した実施形態と同様の効果を得ることができる。

40

#### 【 0 1 2 4 】

上述した実施形態では、1行目から順に最終行まで撮像用画素 P X I の画像信号が読み出される例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、制御部 C N T は、奇数行の撮像用画素 P X I から画像信号を読み出した後に、偶数行の撮像用画素 P X I から画像信号を読み出してもよい。この場合にも、上述した実施形態と同様の効果を得ることができる。

#### 【 0 1 2 5 】

上述した実施形態では、焦点検出用画素 P X F の信号が焦点検出に用いられる例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、焦点検出用画素 P X F の信号は、露出検出に用いられてもよい。この場合にも、上述した実施形態と同様の効果を得ることができる。また、この場合、例えば、焦点検出用画素 P X F の露光を

50

1フレームFRM中に複数回実施できるため、明滅光源等による露出の定期的な変化を検出できる。さらに、この場合、図12-図15等で説明した動作を実施することにより、高速な露出検出、高照度の環境下での露出検出および低照度の環境下での露出検出等を実施できる。

#### 【0126】

上述した実施形態では、フレームFRM(1)の最後の読み出し期間REAaの動作が最終行(Ln)の撮像用画素PXIに対して実施された後に、フレームFRM(2)の最初のリセット期間RESaの動作が、1行目(L1)の撮像用画素PXIに対して実施される例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、フレームFRM(1)の最後の読み出し期間REAaの動作が最終行(Ln)の撮像用画素PXIに対して実施される前に、フレームFRM(2)の最初のリセット期間RESaの動作が、1行目(L1)の撮像用画素PXIに対して実施されてもよい。この場合にも、上述した実施形態と同様の効果を得ることができる。10

#### 【0127】

上述した実施形態では、撮像用画素PXIの転送期間TRAaと焦点検出用画素PXFの転送期間TRAcとを互いに同じタイミングにする例について述べた。本発明は、かかる実施形態に限定されるものではない。例えば、焦点検出用画素PXFの転送期間TRAcは、撮像用画素PXIの転送期間TRAaと異なるタイミングでもよい。この場合にも、焦点検出用画素PXFの露光タイミングを適切に制御でき、焦点検出精度を向上できる。20

#### 【0128】

以上、本発明について詳細に説明してきたが、上記の実施形態およびその変形例は発明の一例に過ぎず、本発明はこれに限定されるものではない。本発明を逸脱しない範囲で変形可能であることは明らかである。

#### 【産業上の利用可能性】

#### 【0129】

撮像装置に利用できる。

#### 【符号の説明】

#### 【0130】

A P 開口部； A R Y 画素アレイ； C I R U 回路部； C N T 制御部； F D A 焦点検出領域； I M U 撮像装置； M E M 蓄積部； M L N マイクロレンズ； M S 遮光部； M T X メモリ転送部； M U メモリ部； P D a、P D b フォトダイオード； P X F 焦点検出用画素； P X F G 焦点検出用画素群； P X I 撮像用画素； T G タイミングジェネレータ； V S C 垂直走査回路30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開2008-085535(JP,A)

特開2008-193527(JP,A)

特開2009-141390(JP,A)

特開2010-288083(JP,A)

特開2010-186942(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |             |   |             |

|--------|-------------|---|-------------|

| H 04 N | 5 / 3 0     | - | 5 / 3 7 8   |

| H 04 N | 5 / 2 2 2   | - | 5 / 2 5 7   |

| H 01 L | 2 1 / 3 3 9 |   |             |

| H 01 L | 2 7 / 1 4   | - | 2 7 / 1 4 8 |

| H 01 L | 2 9 / 7 6 2 |   |             |

| G 02 B | 7 / 2 8     | - | 7 / 4 0     |

| G 03 B | 3 / 0 0     | - | 3 / 1 2     |

| G 03 B | 1 3 / 3 0   | - | 1 3 / 3 6   |

| G 03 B | 2 1 / 5 3   |   |             |