# (10) **DE 10 2010 040 062 B4** 2014.05.22

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2010 040 062.9

(22) Anmeldetag: 31.08.2010(43) Offenlegungstag: 01.03.2012

(45) Veröffentlichungstag

der Patenterteilung: 22.05.2014

(51) Int Cl.: **H01L 21/784** (2006.01)

**H01L 21/301** (2006.01) **H01L 23/48** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(73) Patentinhaber:

GLOBALFOUNDRIES Dresden Module One Limited Liability Company & Co. KG, 01109, Dresden, DE; GLOBALFOUNDRIES Inc., Grand Cayman, KY

(74) Vertreter:

Grünecker, Kinkeldey, Stockmair & Schwanhäusser, 80802, München, DE

(72) Erfinder:

Richter, Daniel, 01445, Radebeul, DE; Kuchenmeister, Frank, 01159, Dresden, DE

(56) Ermittelter Stand der Technik:

| DE | 101 16 791    | A1        |

|----|---------------|-----------|

| US | 6 955 947     | <b>B2</b> |

| US | 7 674 689     | <b>B2</b> |

| US | 5 128 282     | Α         |

| wo | 2003/ 030 271 | A2        |

(54) Bezeichnung: Eine Substratzerteilungstechnik für das Separieren von Halbleiterchips mit geringerem Flächenverbrauch

(57) Hauptanspruch: Verfahren mit:

Bilden eines Arrays aus Halbleiterchips über einer Vorderseite eines Substrats;

Separieren des Arrays in einzelne Halbleiterchips durch Bilden einer abnehmbaren Materialschicht über der Vorderseite und durch Bilden erster Gräben in einer Rückseite des Substrats, die eine erste Breite besitzen, und durch nachfolgendes Erzeugen zweiter Gräben mit einer zweiten Breite in der Vorderseite, so dass diese sich mit den ersten Gräben verbinden, wobei die zweite Breite kleiner ist als die erste Breite;

Anbringen eines Gehäusesubstrats an jedem von mindestens einigen der einzelnen Halbleiterchips; und

Ausführen mindestens eines mechnischen Reinigungsprozesses nach dem Entfernen der Materialschicht und vor dem Erzeugen der zweiten Gräben.

#### **Beschreibung**

Gebiet der vorliegenden Erfindung

**[0001]** Im Allgemeinen betrifft die vorliegende Erfindung Techniken zum Schneiden von Substraten, so dass die einzelnen Bauelemente bereitgestellt werden.

Beschreibung des Stands der Technik

[0002] Halbleiterbauelemente werden typischerweise auf im Wesentlichen scheibenförmigen Substraten hergestellt, die aus einem geeigneten Material aufgebaut sind. Der Hauptanteil der Halbleiterbauelemente, die sehr komplexe elektronische Schaltungen enthalten, werden gegenwärtig und in der vorhersehbaren Zukunft auf der Grundlage von Silizium hergestellt, so dass Siliziumsubstrate und siliziumenthaltende Substrate, etwa SOI-(Silizium-auf-Isolator-)Substrate, geeignete Basismaterialien sind, um Halbleiterbauelemente, etwa Mikroprozessoren, SRAM's, ASIC's (anwendungsspezifische IC's), Systeme auf einem Chip (SOC) und dergleichen herzustellen. Die einzelnen integrierten Schaltungen sind als Array auf der Scheibe angeordnet, wobei die meisten Fertigungsschritte, die sich auf mehrere 100 oder mehr einzelne Prozessschritte in komplexen integrierten Schaltungen belaufen können, gleichzeitig für alle Chipbereiche auf dem Substrat ausgeführt werden, mit Ausnahme von Photolithographieprozessen, Messprozessen und dem Einbringen der einzelnen Bauelemente in ein Gehäuse nach dem Zerteilen des Halbleitersubstrats. Somit zwingen ökonomische Rahmenbedingungen die Halbleiterhersteller dazu, stetig die Substratabmessungen zu vergrößern, wodurch ebenfalls die Fläche vergrößert wird, die zum Erzeugen der eigentlichen Halbleiterbauelemente verfügbar ist, so dass damit auch die Produktionsausbeute ansteigt.

[0003] Zusätzlich zu der Vergrößerung der Substratfläche ist es auch wichtig, die Ausnutzung der Substratfläche bei einer vorgegebenen Substratgröße zu optimieren, so dass möglichst viele Substratfläche für Halbleiterbauelemente und/oder Teststrukturen, die für die Prozesssteuerung verwendet werden, genutzt wird. In dem Versuch, die nutzbare Oberfläche bei einer vorgegebenen Substratgröße zu maximieren, werden die Strukturgrößen der Schaltungselemente stetig verringert. Auf Grund dieser voranschreitenden Verringerung der Strukturgrößen in sehr komplexen Halbleiterbauelementen wird Kupfer in Verbindung mit dielektrischen Materialien mit kleinem ε zunehmend als Alternative bei der Herstellung sogenannter Verbindungsstrukturen verwendet, die Metallleitungsschichten und dazwischen liegende Kontaktdurchführungsschichten aufweisen, die somit Metallleitungen als Verbindungen innerhalb der Schichten und Kontaktdurchführungen als Verbindungen zwischen den Schichten enthalten, die gemeinsam die einzelnen Schaltungselemente verbinden, so dass die erforderliche Funktionsfähigkeit der Integrierten Schaltungen sichergestellt ist. Typischerweise ist eine Vielzahl an Metallleitungsschichten und Kontaktdurchführungsschichten, die aufeinander gestapelt sind, vorgesehen, um die Verbindungen zwischen allen internen Schaltungselementen und I/O-(Eingangs/Ausgangs), Leistungs- und Masseanschlussflächen des betrachteten Schaltungsaufbaus zu verwirklichen.

[0004] In komplexen Halbleiterbauelementen sorgt die stetige Verringerung der kritischen Abmessungen von Transistoren und damit auch der Metallstrukturelemente nicht nur für eine Leistungssteigerung im Hinblick auf die Arbeitsgeschwindigkeit, sondern führt auch zu einer deutlichen Zunahme der Leistungsaufnahme, wodurch bessere Wärmeableiteigenschaften der Halbleiterbauelemente und der entsprechenden Gehäusesubstrate erforderlich sind. Typischerweise ist das Metallisierungssystem des Halbleiterbauelements in unmittelbarer Nähe zu den halbleiterbasierten Schaltungselementen angeordnet, etwa zu schnell schaltenden Transistoren und dergleichen, und stellt zusätzlich zu der elektrischen Kontaktierung der halbleiterbasierten Schaltungselemente auch einen effizient thermisch leitenden Pfad bereit, um damit die Abwärme, die innerhalb der Bauteilebene erzeugt wird, in das Metallisierungssystem und schließlich in das Gehäusesubstrat abzuleiten, das wiederum mit einer externen Wärmesenke bei Bedarf verbunden ist. Auf Grund der zunehmenden Komplexität des Metallisierungssystems in komplexen Halbleiterbauelementen wird jedoch die Anzahl der gestapelten Metallisierungsschichten erhöht, während gleichzeitig die komplexen dielektrischen Materialien, etwa dielektrische Materialien mit kleinem ε oder ULK-(sehr kleines ε) Materialien zunehmend verwendet werden, um die parasitäre Kapazität zu verringern, wodurch das gesamte elektrische Verhalten verbessert wird. Andererseits wird jedoch das thermische Leistungsvermögen, d. h. die Wärmeableiteigenschaften, derartiger komplexer Metallisierungssysteme jedoch deutlich beeinträchtigt, da typischerweise die dielektrischen Materialien mit kleinem ε und die ULK-Materialien eine deutlich geringere Wärmeleitfähigkeit im Vergleich zu konventionellen dielektrischen Materialien, etwa Siliziumdioxid, Siliziumnitrid und dergleichen besitzen. Somit kann der thermische Widerstand komplexer Metallisierungssysteme ansteigen, während gleichzeitig der Anteil an Abwärme, der in der Bauteilebene erzeugt wird, d. h. in den halbleiterbasierten Schaltungselementen, zunehmen kann, wodurch zusätzlich Wärmeableiteigenschaften in komplexen Halbleiterbauelementen notwendig werden. Dazu wird häufig das Substratmaterial des Halbleiterbauelements, das typischerweise in Form eines Siliziummaterials bereitgestellt wird, verwendet, um Wärme an die Periphe-

rie des Halbleiterbauelements abzugeben. D. h., das Substratmaterial besitzt eine moderat hohe thermische Leitfähigkeit und ist auch ebenfalls in unmittelbarer Nähe zu den wärmeerzeugenden Halbleiterschaltungselementen angeordnet, so dass ein effizienter Wärmeableitpfad von dem aktiven Halbleitermaterial in das Volumen des Substrats eingerichtet wird. Aus diesem Grunde erhält häufig die Rückseite des Substrats ein geeignetes Wärmeübertragungsmaterial, um damit in effizienter Weise eine Verbindung zu dem Gehäusesubstrat herzustellen, wobei gut etablierte metallbasierte Materialien, etwa Indium und dergleichen, als thermisches Grenzflächenmaterial auf Grund der guten Wärmeleitfähigkeit verwendet werden. In anderen Fällen werden Gallium, Silber, Kupfer und dergleichen ebenfalls effizient als thermische Grenzflächenmaterialien verwendet. Auf Grund der Materialeigenschaften, etwa dem Diffusionsverhalten, der Haftung an speziellen Materialien, etwa an Silizium und dergleichen, wird das thermische Grenzflächenmaterial typischerweise nicht direkt auf der Substratrückseite aufgebracht, sondern es werden weitere Materialschichten notwendig, um die gewünschten thermischen, mechanischen oder chemischen Eigenschaften, die gewünschte Kopplung zwischen der Substratrückseite und einem Gehäuse zu erhalten. Zu diesem Zweck wird häufig eine Haftschicht auf der Oberfläche der Substratrückseite angebracht, um damit die Haftung der nachfolgenden Materialien an dem Halbleitermaterial des Substrats zu verbessern. Beispielsweise sind Aluminium, Aluminiumlegierungen, Titan, Titannitrid, Tantal, Tantalnitrid und Tantalsilizidmaterialien, die häufig als ein Haftmaterial Verwendung finden. Daraufhin wird ein Barrierenmaterial, etwa Titan, Tantal, Tantalnitrid, Tantalsilizid, Nickel, Chrom, und dergleichen vorgesehen, um die Diffusion des Indiums, d. h. des thermischen Grenzflächenmaterials, in das Material des Substrats, etwa das Siliziummaterial und dergleichen, zu verhindern. Zusätzlich zu diesen Materialschichten werden auch eine oder mehrere Schichten bereitgestellt, so dass diese als eine Haftschicht dient, um in geeigneter Weise das thermische Grenzflächenmaterial an den Rückseitenmetallisierungsstapel anzubringen und somit auch an dem Halbleitersubstrat zu befestigen. Zu diesem Zweck werden Materialien, die aus Gold, Goldlegierungen, Platin, Gold/Platin-Legierungen, Kupfer, Silber und dergleichen bestehen, verwendet. Folglich ist häufig ein moderat komplexer Metallisierungsschichtstapel auf der Rückseite des Halbleitersubstrats herzustellen, wobei eine Vielzahl unterschiedlicher Materialien abzuscheiden sind, wovon zumindest einige eine negative Wirkung auf die Halbleiterbauelemente und Prozesstechniken ausüben, so dass im Hinblick auf das Vermeiden einer Kreuzkontamination die Rückseitenmetallisierung typischerweise in einem sehr fortgeschrittenen Fertigungsstadium bereitgestellt wird. Es zeigt sich jedoch, dass die Anwesenheit der Rückseitenmetallisierung dennoch negativ die weitere Bearbeitung beeinflusst, insbesondere im Hinblick auf komplexe Metallisierungssysteme, die eine Kontaktstruktur als abschließenden Teil des Metallisierungssystems besitzen, um damit eine direkte Verbindung zu einem Gehäusesubstrat herzustellen, insbesondere während des Prozesses zum Zerschneiden des Halbleitersubstrats, um damit die einzelnen Halbleiterchips bereitzustellen.

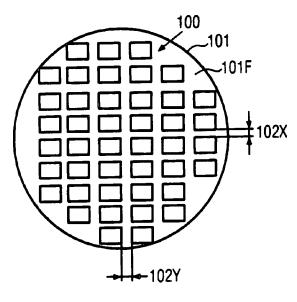

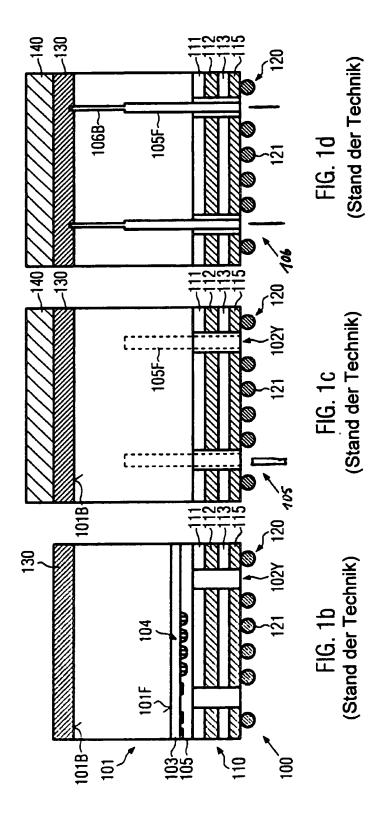

[0005] Fig. 1a zeigt schematisch eine Draufsicht eines Halbleitersubstrats 101, wobei mehrere Halbleiterbauelemente 100 über einer Vorderseite 101f des Substrats 101 ausgebildet sind. Die Halbleiterbauelemente 100 in dieser Fertigungsphase können als Chipgebiete verstanden werden, d. h. als Bereiche des Substrats 101, in und über welchem ein oder mehrere integrierte Schaltungsbereiche möglicherweise in Verbindung mit mikromechanischen, optischen oder anderen Bauelementen, gemäß einem spezifizierten Gesamtschaltungsaufbau angeordnet sind. Somit besitzen die Halbleiterbauelemente 100 eine spezielle Größe und Form, die der Komplexität des einen oder der mehreren der integrierten Schaltungsbereiche und andere Mikrostrukturbauelementen, die darin ausgebildet sind, entspricht. Wie zuvor angegeben ist, werden die Halbleiterbauelemente oder Chips 100 in einer Arrayform auf und über der Vorderseite 101f bereitgestellt, wobei die Anzahl an Halbleiterchips 100, die auf dem Substrat 101 angeordnet sind, von der Gesamtgröße des Substrats 101, der Größe und der Form der Halbleiterchips 100 und von der Größe entsprechender "Randgebiete" oder Schnittlinien abhängt, die den lateralen Abstand zwischen benachbarten Halbleiterchips 100 bestimmen. Beispielsweise sind in dem in Fig. 1a gezeigten Beispiel vertikale Randgebiete oder Schneidelinien, die durch 102y gekennzeichnet sind, mit im Wesentlichen der gleichen Breite wie die horizontalen Schneidelinie 102x vorgesehen. Es sollte jedoch beachtet werden, dass die Breite der Schneidelinien 102x, 102y unterschiedlich sein kann, solange prozessspezifische Erfordernisse von den Schneidelinien 102x, 102y erfüllt werden. Beispielsweise muss die Breite dieser Schneidelinien zumindest den Abstand berücksichtigen, der zum Schneiden erforderlich ist, d. h. zum Sägen, wenn das Substrat 101 in die einzelnen Halbleiterchips unterteilt wird, wovon jeder somit ein einzelnes Bauelement der Halbleiterbauelemente 100 enthält. Beispielsweise wird die Breite der Schneidelinien 102x, 102y so festgelegt, dass diese größer ist als eine Dicke eines entsprechenden Deckblattes, das zum Sägen des Substrats 101 in einer fortgeschrittenen Fertigungsphase verwendet wird.

[0006] Fig. 1b zeigt schematisch eine Querschnittsansicht des Substrats 101, das mehrere Halbleiterchips 100 aufweist. Wie gezeigt, umfasst jeder der Halbleiterchips 100 eine Halbleiterschicht 103, die über oder auf der Vorderseite 101f des Substrats

101 ausgebildet ist, wobei in und über der Halbleiterschicht 103 mehrere Schaltungselemente 104, etwa Transistoren, Kondensatoren, Widerstände und dergleichen, gemäß dem gesamten Aufbau der einen oder mehreren Schaltungen vorgesehen sind, die in den Halbleiterchips 100 bereitgestellt sind. Beispielsweise umfassen die Schaltungselemente 104 solche Schaltungselemente, die auf der Grundlage kritischer Abmessungen von 50 nm oder weniger in komplexen Anwendungen aufgebaut sind. In anderen Fällen werden deutlich größere kritische Abmessungen verwendet, wenn Halbleiterbauelemente mit geringerer Packungsdichte in der Halbleiterschicht 103 betrachtet werden. Des weiteren umfasst jeder der Halbleiterchips 100 eine Kontaktebene, die als ein dielektrisches Material in Verbindung mit geeigneten Kontaktpfropfen oder Elementen (nicht gezeigt) zu verstehen sind, um damit eine Verbindung zu den Schaltungselementen 104 und auch zu einem Metallisierungssystem 110 herzustellen, das über der Kontaktebene 105 ausgebildet ist. Das Metallisierungssystem 110 umfasst typischerweise mehrere Metallisierungsschichten 111, ..., 115, wobei die Anzahl der Metallisierungsschichten von der Gesamtkomplexität der Gestaltung in und über der Halbleiterschicht 103 abhängt, wie dies auch zuvor erläutert ist. In anspruchsvollen Anwendungen umfasst das Metallisierungssystem 110 zumindest in einigen kritischen Metallisierungsschichten empfindliche dielektrische Materialien, die zu einer beeinträchtigten Wärmeableitfähigkeit führen, wie dies auch zuvor erläutert ist. Ferner umfasst in einigen komplexen Halbleiterbauelementen das Metallisierungssystem 110 eine Kontaktstruktur 120, die geeignet so gestaltet ist, dass ein direkter Kontakt mit einem Gehäusesubstrat möglich ist, das darauf ausgebildet eine "komplementäre" Kontaktstruktur aufweist, beispielsweise in Form von Lötflächen und dergleichen, wodurch eine direkte Verbindung entsprechender Kontaktelemente 121, etwa von Lotkugeln, Metallsäulen und dergleichen, mit dem Gehäusesubstrat möglich ist. Folglich ist in einer entsprechend gestalteten Kontaktstruktur 120 im Wesentlichen die gesamte Oberfläche jedes der Halbleiterchips 100 für das Bereitstellen von Kontaktelementen 121 darauf verfügbar, so dass eine große Anzahl an elektrischen Verbindungen mit der Peripherie eingerichtet werden kann, wie dies typischerweise in sehr komplexen Halbleiterbauelementen, die komplexe Steuerschaltungen, etwa CPU's, GPU's und dergleichen enthalten, erforderlich ist. Abhängig von der benötigten Anzahl an Kontaktelementen 121 wird der laterale Abstand der Kontaktelemente 121 so festgelegt, dass dies den elektrischen Erfordernissen genügt. Beispielsweise liegt die laterale Größe der Kontaktelemente 121 in der Größenordnung von 200 µm und weniger, wobei ein Abstand ebenfalls in der gleichen Größenordnung liegt.

[0007] In anderen Halbleiterbauelementen sind auf der Kontaktstruktur 120 geeignete Anschlussflächen

(nicht gezeigt) vorgesehen, die typischerweise am Rand der Halbleiterchips **100** bereitgestellt sind, um damit eine Drahtverbindungskontakttechnologie nach dem Separieren der einzelnen Halbleiterchips **100** zu ermöglichen.

[0008] Wie ferner zuvor erläutert ist, ist in anspruchsvollen Anwendungen auf den Halbleiterchips 100 und somit auf dem Substrat 101 auf einer Rückseite 101b eine Rückseitenmetallisierung 130 aufgebracht, die typischerweise mehrere einzelne metallenthaltende Materialschichten aufweist, wie dies auch zuvor erläutert ist. Auf diese Weise wird ein zusätzlicher effizienter Pfad für die Wärmeableitung von der Halbleiterschicht 103 in die Peripherie über das Substratmaterial 101 und die Rückseitenmetallisierung 120 bereitgestellt.

[0009] Die Halbleiterchips 100, wie sie in den Fig. 1a und Fig. 1b gezeigt sind, können auf der Grundlage einer beliebigen geeigneten Prozessstrategie hergestellt werden. D. h., die Schaltungselemente 104 werden in und über der Halbleiterschicht 103 mittels einer geeigneten Prozesstechnik hergestellt, wobei auch in gewissen Fällen die Schaltungselemente oder Bereiche davon innerhalb des Substratmaterials 101 aufgebaut werden. Als nächstes wird die Kontaktebene 105 vorgesehen, indem ein geeignetes dielektrisches Material abgeschieden wird und indem leitende Elemente darin so erzeugt werden, dass sie mit den Schaltungselementen 104 in Verbindung stehen. Daraufhin werden die Metallisierungsschichten 111, 112, 113, 115 gemäß einer Prozessstrategie hergestellt, um damit das gewünschte elektrische Leistungsverhalten etwa im Hinblick auf die Stromdichte, die parasitären RC-(Widerstand/Kapazitäts-)Zeitkonstanten und dergleichen zu erreichen. Schließlich wird die Kontaktstruktur 120 hergestellt, indem geeignete Lothöcker, Metallsäulen, Anschlussflächen und dergleichen abhängig von der Komplexität der Kontaktstruktur und allgemein der Bauelemente 100 und abhängig von der gewünschten Kontakttechnologie bereitgestellt, die zum Anbringen der Halbleiterchips 100 an einem Gehäusesubstrat oder an einem anderen Trägermaterial anzuwenden ist. Wie zuvor erläutert ist, wird in einer sehr fortgeschrittenen Fertigungsphase die Rückseite der Metallisierung 130 bereitgestellt, beispielsweise durch Abscheiden mehrerer geeigneter Materialschichten, wie dies zuvor erläutert ist. Die Bauelemente 100, die auf dem Substrat 101 ausgebildet sind, wie in Fig. 1b gezeigt ist, sind somit in einer geeigneten Fertigungsphase, um die einzelnen Halbleiterchips 100 voneinander zu trennen.

[0010] Fig. 1c zeigt schematisch das Substrat 101 und die mehreren Halbleiterchips 100 in einer weiter fortgeschrittenen Fertigungsphase. Die Separierung der mehreren Halbeiterchips 100 wird typischerweise auf der Grundlage eines mechanischen Säge-

prozesses bewerkstelligt, in welchem ein Diamantsägeblatt verwendet wird, um durch das Substrat 101 und durch das Metallisierungssystem 110, und, falls dieses vorgesehen ist, durch die Rückseitenmetallisierung 130 zu sägen. Auf Grund der Zunahme der Substratabmessungen zur Erhöhung der Anzahl der einzelnen Halbleiterchips 100 pro Substrat im Hinblick auf eine höhere Produktivität, muss jedoch auch die Dicke des Substrats 101 entsprechend angepasst werden, um die mechanische Stabilität und dergleichen zu gewährleisten. Beispielsweise besitzt bei einem Durchmesser von 200 bis 300 mm, was ein häufig verwendeter Standard in der Halbleiterherstellung ist, das Substrat 101 eine Dicke von ungefähr 700 µm und mehr. Die Schneidelinien, beispielsweise die Schneidelinie 102y, wie sie in Fig. 1c gezeigt ist, ist somit geeignet in ihrer Breite so gestaltet, dass ein zuverlässiger Schneideprozess auf der Grundlage eines Diamantsägeblatts erfolgt, wobei jedoch die Dicke nicht beliebig verringert werden kann, da in diesem Falle ein erhöhter Grad an Absplitterung auftreten kann und somit die gesamte Produktionsausbeute beim Zerschneiden der Substrate auftreten kann, die eine Dicke von mehreren 100 µm besitzen. Die Verwendung eines dünnen Sägeblatts würde jedoch deutlich die Lebensdauer des Sägeblatts verkürzen, wenn durch die gesamte Dicke des Substrats 101 geschnitten wird. Folglich wird in konventionellen Strategien ein zweistufiger Schneideprozess typischerweise angewendet, in welchem ein Sägeblatt 105 mit geeigneter Dicke so gewählt wird, dass in das Substrat 101 und durch das Metallisierungssystem 110 geschnitten wird, d. h. durch entsprechende Bereiche, die den Schneidelinien 102y und 102x (siehe Fig. 1a) entsprechen, wodurch Gräben 105f erzeugt werden, die sich in die Tiefe des Substrats 101 erstrecken. Beispielsweise werden die Gräben 105f so erzeugt, dass diese sich ungefähr bis zu der Hälfte der Dicke des Substrats 101 erstrecken. Dazu wird ein Klebeband 140 auf der Rückseite vorgesehen, d. h. auf der Rückseite der Metallisierung 130, wenn diese vorgesehen ist, oder direkt auf der Rückseite 101b des Substrats 101.

[0011] Fig. 1d zeigt schematisch das Substrat 101 und die mehreren Halbleiterchips 100 in einer weiter fortgeschrittenen Fertigungsphase. In dieser Phase wird ein weiterer Schneideprozess auf der Grundlage eines Sägeblattes 106 ausgeführt, das eine geringere Dicke besitzt, um weitere Gräben 106b durch die zuvor erzeugten breiteren Graben 105f herzustellen. Folglich kann das Substrat 101 in die einzelnen Halbleiterchips separiert werden, indem das Sägeblatt 106 verwendet wird und indem die Graben 106b erzeugt werden, wobei das Band 140 weiterhin die erforderliche mechanische Stabilität der separierten Halbleiterchips sicherstellt.

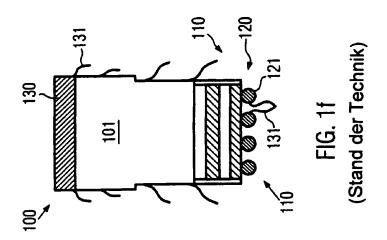

[0012] Fig. 1e zeigt schematisch ein weiter fortgeschrittenes Fertigungsstadium. Wie gezeigt, sind

mehrere einzelne Halbleiterchips, die ebenfalls mit den Bezugszeichen 100 bezeichnet werden, vorgesehen, nachdem die separierten Bauelemente von dem Klebeband 140 (siehe Fig. 1d) herausgenommen wurden. In Halbleiterchips, etwa dem Chip 100, in denen die Rückseitenmetallisierung 130 vorgesehen ist, kann der Schneideprozess zu der Erzeugung einer gewissen Menge an Metallresten führen, die zu der Vorderseite wandern können und die schließlich in das Metallisierungssystem 110 wandern.

[0013] Fig. 1f zeigt schematisch eine Querschnittsansicht eines der Halbleiterchips 100, wobei Metallreste 131, die während des Schneidens durch die Rückseitenmetallisierung 130 erzeugt wurden, schließlich das Metallisierungssystem 110 und somit die Kontaktstruktur 120 erreichen. Da insbesondere die dicht liegenden Kontaktelemente 121 in der Struktur 120 vorgesehen sind, können die Metallreste 131 eine hohe Wahrscheinlichkeit des Erzeugens von Kurzschlüssen nach sich ziehen, wodurch zu hohen Ausbeuteverlusten während der weiteren Bearbeitung beigetragen wird, d. h. während des Verbindens des Halbleiterchips 100 mit einem Gehäusesubstrat.

[0014] Folglich werden in konventionellen Techniken zum Separieren von Halbleitersubstraten in einzelne Halbleiterchips Schneidelinien mit geeigneter Breite benötigt, um somit den Erfordernissen der notwendigen Dicke der Sägeblätter zu genügen, während gleichzeitig ausgeprägte Ausbeuteverluste in komplexen Halbleiterbauelementen beobachtet werden, in denen eine Rückseitenmetallisierung vorzusehen ist. In diesem Falle wurde in einigen konventionellen Vorgehensweisen vorgeschlagen, eine Rückseitenstrukturierungsstrategie anzuwenden, in der die Rückseitenmetallisierung so strukturiert wird, dass diese Schneidelinien enthält, um damit die Wahrscheinlichkeit des Erzeugens von Metallresten zu verringern. In diesem Falle sind jedoch komplexe Lithographie- und Ätzprozesse in einer sehr frühen fortgeschrittenen Fertigungsphase an der Rückseite des Substrats auszuführen, wodurch die gesamte Prozesskomplexität und somit auch die Herstellungskosten drastisch ansteigen.

**[0015]** Im Hinblick auf die zuvor beschriebene Situation betrifft die vorliegende Erfindung Fertigungstechniken und Halbleiterbauelemente, in denen Halbleitersubstrate in einzelne Halbleiterchips separiert werden, wobei eines oder mehrere der oben erkannten Probleme vermieden oder zumindest in der Auswirkung reduziert werden.

[0016] Das Dokument US 7674689 B2 betrifft ein Verfahren zur Herstellung einer integrierten Schaltung einschließlich der Vereinzelung einer Halbleiterscheibe. Das Dokument zeigt keinen Reinigungsschritt zwischen den Schritten für die Erzeugung der

## DE 10 2010 040 062 B4 2014.05.22

jeweiligen Gräben in dem Halbleitersubstrat und verweist auch nicht auf die möglichen negativen Auswirkungen, die das Erzeugen der Gräben auf der Rückseite, insbesondere auf empfindliche Kontaktstrukturen auf der Vorderseite ausüben kann. Insbesondere werden keine Vorteile eines zwischengeschalteten Reinigungsschritts während des gesamten Ablaufs für das Erzeugen der Gräben beschrieben.

[0017] Das Dokument US 5128282 A betrifft ein Verfahren zum Separieren von Bildsensorblättchen und ähnlichem von einer Halbleiterscheibe. In diesem Dokument wird vorzugsweise eine Reinigung mit Wasser mit anschließender Lufttrocknung wiederholt angewendet, um eine Verschmutzung zu entfernen, die während der Herstellung V-förmigen Gräben erzeugt wurde. Es findet sich jedoch kein Hinweis, dass insbesondere bei der Herstellung der V-förmigen Gräben zunächst eine Materialschicht auf der Vorderseite aufgebracht werden könnte, wobei zuvor auf der Rückseite eine Metallisierungsschicht aufgebracht wird.

[0018] Das Dokument US 6955947 B2 betrifft eine mikroelektronische Vorrichtung und Verfahren zur Herstellung desselben, wobei im Rahmen der Herstellung der Gräben, ein Abbau von Verspannungen, die sich beim Erzeugen der Gräben ergeben könnten, dadurch bewerkstelligt werden kann, dass eine Ätzung unter Anwendung eines geeigneten anisotropen Ätzmittels durchgeführt werden kann. Das Dokument zeigt keinen mechanischen Reinigungsschritt.

[0019] Das Dokument DE 101 16 791 A1 betrifft ein Verfahren zur Herstellung einer großen Anzahl von Halbleiterchips aus einem Halbleiterwafer. Das Verfahren umfasst die Schritte eines Ausbilden einer Vielzahl von Rillen bzw. Nuten, welche eine vorbestimmte Tiefe aufweisen, in der hinteren Oberfläche des Halbleiterwafers, eines Schleifens der hinteren Oberfläche des Halbleiterwafers, um die Dicke des Halbleiterwafers auf einen vorbestimmten Wert zu reduzieren, und danach eines Schneidens des Halbleiterwafers entlang der Straßen, um die rechtwinkligen Bereiche voneinander zu trennen. Dieses Dokument zeigt keinen Reinigungsprozess in der in der vorliegenden Erfindung angegebenen Prozessphase.

**[0020]** Das Dokument WO 2003/030271 A2 betrifft einen strahlungsemittierenden Halbleiterchip mit einer auf einem SiC-basierten Aufwachssubstrat aufgebrachten Nitrid-basierten strahlungsemittierenden aktiven Mehrschichtsstruktur und auf ein mit einem solchen strahlungsemittierenden Halbleiterelement ausgestattetes strahlungsemittierendes optisches Bauelement. Auch dieses Dokument zeigt keinen Reinigungsprozess in der in der vorliegenden Erfindung aufgegebenen Prozessphase.

Überblick über die vorliegende Erfindung

**[0021]** Die zuvor erwähnten Probleme werden durch ein Verfahren gemäß Anspruch 1 gelöst.

**[0022]** Weitere Ausführungsformen der vorliegenden Erfindung sind in den angefügten Patentansprüchen definiert und gehen deutlicher aus der folgenden detaillierten Beschreibung hervor, wenn diese mit Bezug zu den begleitenden Zeichnungen studiert wird, in denen

Kurze Beschreibung der Zeichnungen

**[0023] Fig.** 1a schematisch eine Draufsicht eines Substrats mit mehreren Halbleiterchips zeigt, die in Arrayform mit Schneidelinien gemäß konventioneller Strategien angeordnet sind;

**[0024]** Fig. 1b bis Fig. 1d schematisch Querschnittsansichten des konventionellen Substrats während einer Prozesssequenz zum Separieren des Halbleitersubstrats in einzelne Halbleiterchips zeigen;

**[0025]** Fig. 1e und Fig. 1f schematisch Querschnittsansicht eines separierten Halbleiterchips zeigen, wobei eine hohe Wahrscheinlichkeit zum Kontaminieren des Metallisierungssystems durch Metallreste einer Rückseitenmetallisierung gemäß konventioneller Strategien besteht.

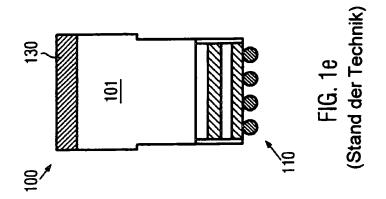

**[0026] Fig.** 2a bis **Fig.** 2c schematisch Querschnittsansichten eines Halbleitersubstrats mit mehreren Halbleiterchips in einer Prozesssequenz zeigen, um Gräben von der Rückseite des Substrats aus unter Anwendung einer geeigneten Grabenbreite gemäß anschaulicher Ausführungsformen zu erzeugen;

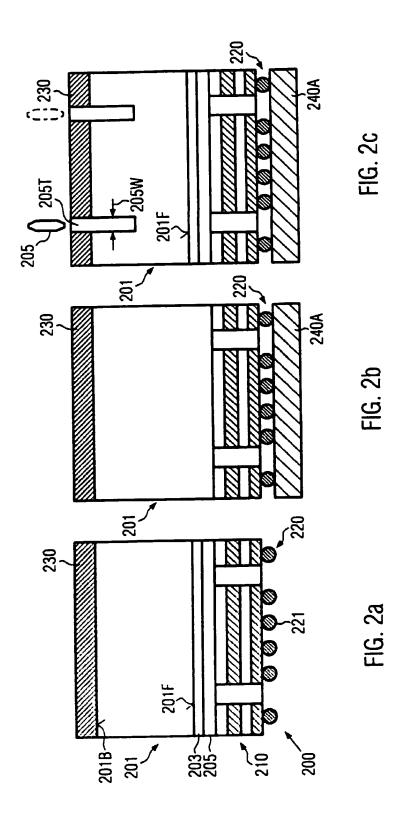

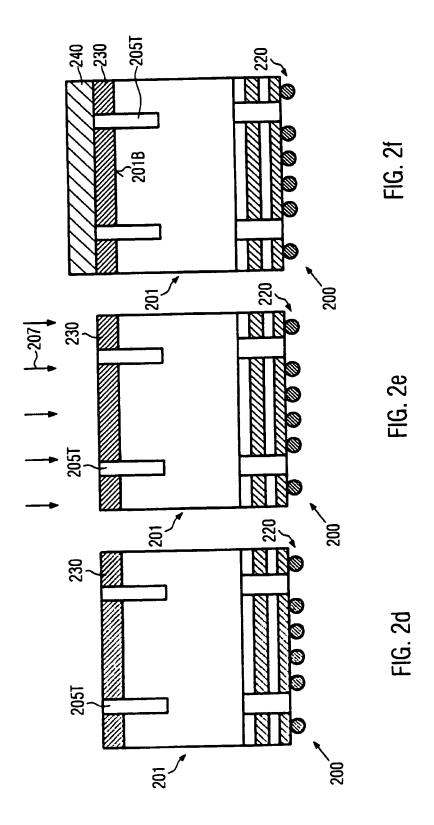

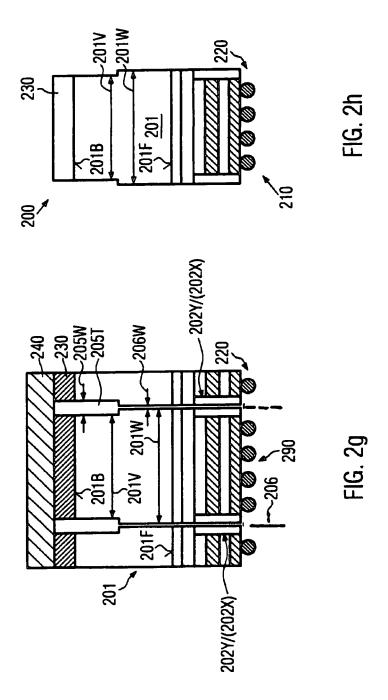

**[0027] Fig.** 2d bis **Fig.** 2g schematisch Querschnittsansichten des Substrats während diverser Fertigungsphasen zeigen, wenn Gräben mit geringerer Breite von der Vorderseite des Substrats so erzeugt werden, dass sie sich mit den zuvor erzeugten Gräben verbinden und somit das Substrat in einzelne Halbleiterchips gemäß anschaulicher Ausführungsformen trennen;

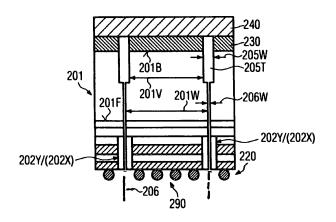

[0028] Fig. 2h schematisch einen einzelnen Halbleiterchips zeigt, dessen Substrat eine entsprechende Länge und Breite besitzt, die durch den vorhergehenden Rückseiten-Vorderseitenseparierungsprozess gemäß anschaulicher Ausführungsformen erhalten werden;

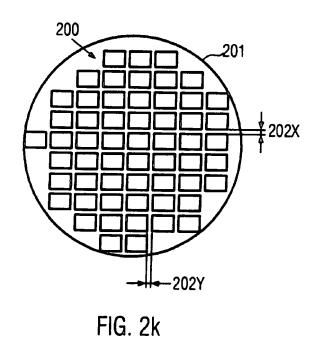

[0029] Fig. 2i und Fig. 2j schematisch Halbleiterbauelemente mit Gehäuse zeigen, wobei die Halbleiterchips enthalten sind, die gemäß den zuvor beschriebenen Prozesstechniken separiert sind; und **[0030] Fig.** 2k schematisch eine Draufsicht des Substrats mit mehreren Halbleitersubstraten zeigt, die mit dem geringeren lateralen Abstand auf Grund des verbesserten Separierungsprozesses gemäß anschaulicher Ausführungsformen der vorliegenden Erfindung angeordnet sind.

#### Detaillierte Beschreibung

[0031] Die vorliegende Erfindung stellt allgemein Halbleiterbauelemente und Fertigungstechniken bereit, in denen ein sehr raumeffizienter Separierungsprozess bereitgestellt wird, indem Gräben mit geeigneter Breite von einer Rückseite des Substrats aus hergestellt werden und indem das Substrat vollständig getrennt wird, indem Graben mit geringerer Breite von einer Vorderseite aus erzeugt werden, was auf der Grundlage von Sägeblättern mit unterschiedlicher Dicke und dergleichen bewerkstelligt werden kann. Auf diese Weise können die Schneidelinien auf der Vorderseite des Substrats mit einer geringeren Breite bereitgestellt werden, was das Anordnen einer größeren Anzahl an Halbleiterchips bei einer vorgegebenen Größe des Substrats und einer vorgegebenen Größe und Form der Halbleiterchips ermöglicht. Ferner wird in anspruchsvollen Anwendungen, in denen das Bereitstellen einer Rückseitenmetallisierung erforderlich ist, die Wahrscheinlichkeit des Erzeugers einer Kontamination an der Vorderseite während des Schneideprozesses deutlich verringert, da die Rückseitenmetallisierung geschnitten wird, ohne dass eine Verbindung zu der Vorderseite besteht, wodurch die Wahrscheinlichkeit der Wanderung von Metallresten von der Rückseite zur Vorderseite verringert wird. Erfindungsgemäß wird ein mechanischer Reinigungsprozess angewendet nach dem Schneiden durch die Rückseitenmetallisierung, wodurch die Wahrscheinlichkeit der Kontamination der Vorderseite während der werteren Bearbeitung noch weiter verringert wird.

**[0032]** Mit Bezug zu den **Fig.** 2a bis **Fig.** 2k werden nunmehr weitere anschauliche Ausführungsformen detaillierter beschrieben, wobei auch bei Bedarf auf die **Fig.** 1a bis **Fig.** 1f verwiesen wird.

[0033] Fig. 2a zeigt schematisch eine Querschnittsansicht mehrerer Halbleiterchips 200, die über der Vorderseite 201f eines Substrats 201 ausgebildet sind. Die Halbleiterchips 200 umfassen eine Halbleiterschicht 203, in und über welcher Schaltungselemente, etwa Transistoren, Widerstände und dergleichen vorgesehen sind. Ferner ist ein Metallisierungssystem 210 über der Halbleiterschicht 203 ausgebildet und besitzt einen geeigneten Aufbau im Hinblick auf die Anzahl der Metallisierungsschichten, der Materialzusammensetzung von Dielektrika und metallenthaltenden Materialien und dergleichen. Ferner umfasst das Metallisierungssystem 210 eine Kontaktstruktur 220, um jeden der Halbleiterchips 200 mit eine

nem entsprechenden Gehäusesubstrat oder Trägersubstrat in einer späten Fertigungsphase elektrische zu verbinden. Beispielsweise umfasst die Kontaktstruktur **220** Kontaktelemente, etwa Lotkugeln, Metallsäulen, Drahtanschlussflächen und dergleichen.

[0034] Es sollte beachtet werden, dass im Hinblick auf bislang beschriebene Komponenten die gleichen Kriterien gelten, wie sei auch zuvor mit Bezug zu dem Substrat 101 und den Halbleiterchips 100 erläutert sind. Des weiteren ist anzumerken, dass der Begriff "über" im Hinblick auf die Lage von beispielsweise der Halbleiterschicht 203 des Metallisierungssystems 210 die entsprechende Substratoberfläche oder Grenzfläche als Referenz zu Grunde legt. D. h., die Halbleiterschicht 203 ist "über" der Vorderseite 201f ausgebildet, da diese Komponenten in unmittelbarer Nähe zu der "Referenzebene" 201f angeordnet sind. In ähnlicher Weise sind Materialschichten über einer Rückseite 201b des Substrats 201 ausgebildet, wenn der entsprechende Abstand derartiger Materialien kleiner ist im Vergleich zu den Abstand zur Vorderseite 201f. Beispielsweise wird in einigen anschaulichen Ausführungsformen eine Rückseitenmetallisierung 230 auf oder über der Rückseite 201b erzeugt, die geeignete Materialschichten aufweist, wie dies auch zuvor erläutert ist. In dem oben definierten Sinne ist somit die Rückseitenmetallisierung 230 auf oder über der Rückseite 201b aber nicht "über" der Vorderseite 201f ausgebildet.

[0035] Das Substrat 201 mit den mehreren Halbleiterchips 200 kann gemäß einer beliebigen geeigneten Prozessstrategie hergestellt werden, wie dies auch beispielsweise zuvor mit Bezug zu dem Substrat 201 und den Halbleiterchips 200 beschrieben ist. Es werden etwa Schaltungselemente in und über der Halbleiterschicht 203 mit kritischen Abmessungen von 100 nm und deutlicher weniger in komplexen Anwendungen hergestellt, während in anderen Fallen weniger kritische halbleiterbasierte Schaltungselemente bereitgestellt werden. In ähnlicher Weise wird das Metallisierungssystem 210 auf der Grundlage komplexer dielektrischer Materialien bei Bedarf hergestellt, möglicherweise in Verbindung mit den Kontaktelementen 221, die mit einem geeigneten Abstand vorgesehen sind, um damit die Eingangs/Ausgangsressourcen komplexer Halbleiterbauelemente bereitzustellen. In anderen Fällen werden die Kontaktelemente 221, beispielsweise in Form von Drahtanschlussflächen, auf dem Rand der einzelnen Halbleiterchips 200 beschränkt, wie dies auch zuvor erläutert ist. In ähnlicher Weise wird die Rückseitenmetallisierungsschicht 230 auf der Grundlage eines geeigneten Materialsystems bereitgestellt, wie dies auch zuvor erläutert ist.

[0036] Fig. 2b zeigt schematisch das Substrat 201 in einer weiter fortgeschrittenen Fertigungsphase, in der eine Schicht aus Material 240a, etwa ein flexibles

Klebeband und dergleichen, auf und über der Kontaktstruktur **220** so vorgesehen ist, dass das Anbringen einer Prozessanlage möglich ist, um einen Separierungsprozess auszuführen und auch um eine höhere Integrität der Kontaktstruktur **220** zu bewahren, beispielsweise im Hinblick auf deren Kontamination und dergleichen. Die Schicht aus Material **240a** kann auf der Grundlage gut etablierter Prozesstechniken aufgebracht werden, beispielsweise durch Anbringen eines Klebebandmaterials und dergleichen.

[0037] Fig. 2c zeigt schematisch das Substrat 201 während eines ersten Schrittes eines Prozesses 290 zum Separieren des Halbleitersubstrats 201 in einzelne Halbleiterchips. Wie gezeigt, werden während des Prozesses Gräben 205t in einem Teil des Substrats 201 von der Rückseite aus hergestellt, wobei in einigen anschaulichen Ausführungsformen geeignete Schneidemittel verwendet werden, die etwa ein Sägeblatt 205 mit einer geeigneten Dicke beinhalten, um die Gräben 205t mit einer Breite 205w zu erzeugen. Die Breite 205w und somit die Dicke des Deckblattes 205 sind so gewählt, dass ein zuverlässiger Schneideprozess erreicht wird, ohne dass eine unerwünschte Schädigung am Rand auftritt, wobei auch die Lebensdauer des Sägeblattes 205 innerhalb eines gewünschten akzeptablen Bereiches liegt. In der in Fig. 2a gezeigten Ausführungsform erfordert der Prozess 290 also das Schneiden durch die Rückseitenmetallisierung 230, was zu der Erzeugung von Metallresten führen kann, wie dies auch zuvor erläutert ist, wobei jedoch die Gräben 205t nicht direkt mit der Substratvorderseite 201f in Verbindung stehen. so dass eine direkte Vorderseitenkontamination im Wesentlichen vermieden wird. Ferner sorgt die Materialschicht 240a ebenfalls für einen höheren Schutz im Hinblick auf eine unerwünschte Vorderseitenkontamination.

[0038] Fig. 2d zeigt schematisch das Substrat 201 in einer weiter fortgeschrittenen Fertigungsphase, in der die Materialschicht 240a (siehe Fig. 2c) von der Kontaktstruktur 220 entfernt ist, was bewerkstelligt werden kann mittels einer geeigneten und gut etablierten Prozesstechnik, beispielsweise durch das Entfernen eines Klebebandmaterials von einem Halbleitersubstrat.

[0039] Fig. 2e zeigt schematisch das Substrat 201 gemäß einiger anschaulicher Ausführungsformen, in denen ein Reinigungsprozess 207 oder eine Sequenz aus Reinigungsprozessen durchgeführt wird, beispielsweise auf der Grundlage nasschemischer Ätzchemien, auf der Grundlage von Spülfluiden und dergleichen. Beispielsweise werden während des Prozesses 207 Metallreste, die während der vorhergehenden Ausbildung der Gräben 205t möglicherweise erzeugt wurden, effizient abtragen, beispielsweise durch Spülen der Substratoberfläche und/oder unter Anwendung von Ätzchemien. Erfindungsge-

mäß wird ein mechanischer Reinigungsprozess ausgeführt, beispielsweise unter Anwendung von bürstenartigen Komponenten und dergleichen. Folglich kann die Dichte von Metallresten deutlich verringert werden, bevor tatsächlich durch das gesamte Substrat 201 hindurchgeschnitten wird, um die einzelnen Halbleiterchips bereitzustellen.

[0040] Fig. 2f zeigt schematisch das Substrat 201 in einer weiter fortgeschrittenen Fertigungsphase, in der eine weitere Materialschicht, etwa ein Klebeband 240, über der Rückseite 201b ausgebildet ist, beispielsweise auf der Rückseitenmetallisierung 230, falls diese vorgesehen ist. Dazu können gut etablierte Prozesstechniken angewendet werden.

[0041] Fig. 2g zeigt schematisch das Substrat 201 in einer weiter fortgeschrittenen Fertigungsphase. Wie gezeigt, wird ein zweiter Schritt des Separierungsprozesses 290 ausgeführt, um weitere Gräben 206t in den Halbleiterchips 200 und in dem verbleibenden Bereich des Substrats 201 so zu erzeugen, dass eine Verbindung zu den zuvor erzeugten Gräben 205t entsteht. Dazu wird eine geeignete Schneideanlage verwendet, beispielsweise auf der Grundlage eines Sägeblattes 206 mit einer Dicke, die eine Breite 206w der Graben 206t ergibt, die kleiner ist als die Breite 205w der zuvor erzeugte Gräben 205t. Folglich wird in diesem Falle ein sehr effizienter Sägeprozess auf Grund der geringeren Breite der Gräben 206t erreicht. Andererseits ist eine unerwünschte Randschädigung und geringere Lebensdauer der Sägeblätter 206 weniger kritisch, da lediglich ein Teil des Substrats 201 zu schneiden ist. Der zweite Schritt des Prozesses 290 wird unter Anwendung entsprechender Schneidelinie 202y und 202x durchgeführt wird, wie diese auch nachfolgend detaillierter erläutert ist. Wie zuvor mit Bezug zu dem Substrat 101 erläutert ist, besitzen die Schneidelinie 202y, 202x eine Gestalt, so dass die Breite, der entsprechenden Gräben, die darin zu erzeugen sind, um durch das Substrat 201 zu schneiden, abgedeckt ist. Gemäß den hierin offenbarten Prinzipien wird die Breite 206w deutlich kleiner gewählt im Vergleich zu der Breite 205w, wodurch auch eine geringere Breite der Schneidelinie 202y, 202x möglich ist. Folglich wird in einigen anschaulichen Ausführungsformen, wie dies nachfolgend detaillierter erläutert ist, die Breite der Schneidelinien in geeigneter Weise an die Breite 206w der Graben 206t und somit an die Dicke der Sägeblätter angepasst, um damit einen größeren nutzbaren Oberflächenanteil des Substrats 201 zu erhalten.

[0042] Es sollte beachtet werden, dass eine unerwünschte Kontamination der Kontaktstruktur 220 deutlich weniger kritisch ist im Vergleich zu konventionellen Strategien, da der kritische Prozess des Schneidens in die Rückseite bereits in einer vorhergehenden Fertigungsphase möglicherweise in Verbindung mit zusätzlichen Reinigungsprozessen ausgeführt wurde.

[0043] Auf Grund des Vorsehens der Graben 206t, 205t mit unterschiedlichen Breiten unterscheiden sich auch die lateralen Abmessungen des Substrats 201 an der Vorderseite 201f und der Rückseite 201b. D. h., eine laterale Abmessung, die als 201v bezeichnet ist, an der Rückseite 201b ist kleiner als die entsprechende laterale Abmessung, die durch 201w bezeichnet ist an der Vorderseite 201f. Zu beachten ist, dass die laterale Abmessung 201v größer sein kann in ihrer entsprechenden Breitenabmessung, beispielsweise in der Horizontalen der Fig. 2g, und auch in der Längsrichtung größer sein kann, d. h. einer Richtung senkrecht zur Zeichenebene der Fig. 2g. Das gleiche gilt für die laterale Abmessung 201w.

[0044] Fig. 2h zeigt schematisch einen einzelnen Halbleiterchip, der ebenfalls durch das Bezugszeichen 200 bezeichnet ist. D. h., nach dem zweiten Schritt des Prozesses 290 aus Fig. 2g wird der einzelne Halbleiterchip 200 aufgenommen und einer weiteren Bearbeitung unterzogen. Wie gezeigt, besitzt das Substrat 201 des Halbleiterchips 200 die unterschiedlichen lateralen Abmessungen 201w und 201v, wie dies zuvor erläutert ist. Folglich wird die weitere Bearbeitung auf der Grundlage der einzelnen Halbleiterchips 200 fortgesetzt, die die charakteristische Querschnittsform besitzen, d. h. die Länge und die Breite, die durch 201w bezeichnet sind, an der Vorderseite 201f größer als die entsprechende laterale Abmessung 201v an der Rückseite 201b des Substrats 201. Daraufhin wird der Halbleiterchip 200 an einem geeigneten Träger oder Gehäusesubstrats mittels der Kontaktstruktur 220 angebracht.

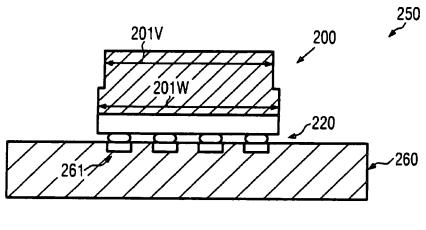

[0045] Fig. 2i zeigt schematisch ein "eingepacktes" bzw. im Gehäuse befindliches Halbleiterbauelement 250 mit dem Halbleiterchip 200 und einem Gehäusesubstrat 260. In der gezeigten Ausführungsform ist die Kontaktstruktur 220 direkt mit einer komplementären Kontaktstruktur 261 des Gehäusesubstrats 260 verbunden, was bewerkstelligt werden kann mittels geeigneter Aufschmelzprozesse, mechanischer Befestigung und dergleichen. Wie gezeigt, besitze der Halbleiterchip 200 seine charakteristische Querschnittsform, die durch die unterschiedlichen lateralen Abmessungen 201w und 201v festgelegt ist.

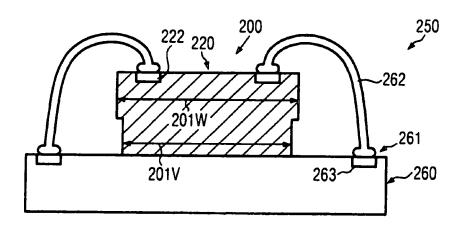

[0046] Fig. 2j zeigt schematisch das im Gehäuse befindliche Halbleiterbauelement 250 gemäß weiterer anschaulicher Ausführungsformen, in denen der Halbleiterchip 200 die Kontaktstruktur 220 so aufweist, dass diese Drahtanschlussflächen 222 besitzt, die elektrisch mit einer Kontaktstruktur 261 verbunden sind, d. h. entsprechenden Drahtanschlussflächen 263 des Gehäusesubstrats 260 mittels der Verbindungsdrähte 262. Dazu kann eine beliebige geeig-

nete Drahtverbindungstechnik angewendet werden. Auch in diesem Falle besitzt der Halbleiterchip 200 seine charakteristische Querschnittsform, die durch die lateralen Abmessungen 201w und 201v festgelegt ist.

[0047] Fig. 2k zeigt schematisch eine Draufsicht des Substrats 201 in einer Fertigungsphase vor dem Separieren der einzelnen Halbleiterchipbereiche 200 in die Halbleiterchips. Wie gezeigt, trennen die Schneidelinien 202y und 202x in geeigneter Weise die einzelnen Halbleiterchipgebiete 200, wobei in einigen anschaulichen Ausführungsformen die Breite der Schneidelinie 202x, 202y so gewählt ist, dass dies mit der geringeren Breite der entsprechenden Gräben oder der reduzierten Dicke des Sägeblatts, das zur Erzeugung der Graben verwendet wird, kompatibel ist, wie dies auch zuvor mit Bezug zu Fig. 2g erläutert ist. Beispielsweise ist die Schneidelinienbreite für die "horizontalen" Schneidelinien 202x und die "vertikalen" Schneidelinien 202y identisch festgelegt, wobei beide dann kleiner gemacht werden können, als die Schneidelinienbereite in konventionellen Strategien. Zu beachten ist jedoch, dass die Breite der Schneidelinie 202x und 202y unterschiedlich sein kann, wobei dies von den gesamten Prozesserfordernissen abhängt. Im Allgemeinen wird für eine vorgegebene Größe und Form der Halbleiterchips 200 eine größere Anzahl an Chips auf dem Substrat 201 bei einem vorgegebenen Substratdurchmesser angeordnet werden können. Wenn beispielsweise das Substrat 101, wie es in Fig. 1a gezeigt ist, mit dem Substrat 201, das in Fig. 2k gezeigt ist, verglichen wird, führt die Verringerung der Breite der Schneidelinien 202x und 202y im Vergleich zu der Breite der Schneidelinien 102x und 102y zu einer deutlichen Flächenzunahme auf Grund der entsprechenden Verringerung der Breite der Schneidelinien 202x, 202y.

[0048] Es gilt also: Die vorliegende Erfindung stellt ein Verfahren bereit, in dem Halbleitersubstrate in einzelne Halbleiterchips mit besserer Flächeneffizienz und/oder mit geringerer Vorderseitenkontamination separiert werden, beispielsweise wenn komplexe Rückseitenmetallisierungen vorzusehen sind, indem das Substrat von der Rückseite aus mit einer gewünschten Breite der resultierenden Gräben geschnitten wird, wobei schließlich die Halbleiterchips repariert werden, indem eine geringere Dicke der entsprechenden Sägeblätter zum Schneiden in das Substrat von der Vorderseite aus verwendet werden.

### Patentansprüche

#### 1. Verfahren mit:

Bilden eines Arrays aus Halbleiterchips über einer Vorderseite eines Substrats;

Separieren des Arrays in einzelne Halbleiterchips durch Bilden einer abnehmbaren Materialschicht über der Vorderseite und durch Bilden erster Gräben in einer Rückseite des Substrats, die eine erste Breite besitzen, und durch nachfolgendes Erzeugen zweiter Gräben mit einer zweiten Breite in der Vorderseite, so dass diese sich mit den ersten Gräben verbinden, wobei die zweite Breite kleiner ist als die erste Breite; Anbringen eines Gehäusesubstrats an jedem von mindestens einigen der einzelnen Halbleiterchips; und

Ausführen mindestens eines mechnischen Reinigungsprozesses nach dem Entfernen der Materialschicht und vor dem Erzeugen der zweiten Gräben.

- 2. Verfahren nach Anspruch 1, wobei Bilden eines Arrays aus Halbleiterchips über der Vorderseite umfasst: Bilden von halbleiterbasierten Schaltungselementen und eines Metallisierungssystems über der Vorderseite.

- 3. Verfahren nach Anspruch 2, wobei Bilden eines Arrays als Halbleiterchips ferner umfasst: Bilden einer oder mehrerer metallenthaltender Metallschichten auf der Rückseite.

- 4. Verfahren nach Anspruch 1, wobei Bilden der ersten und der zweiten Gräben umfasst: Sägen in das Substrat von der Rückseite aus unter Anwendung eines ersten Sägeblattes und Sägen in das Substrat von der Vorderseite aus unter Anwendung eines zweiten Sägeblattes.

- 5. Verfahren nach Anspruch 1, wobei Anbringen des Gehäusesubstrats umfasst: direktes Verbinden einer Kontaktstruktur, die in jedem der Halbleiterchips ausgebildet ist, mit einer komplementären Kontaktstruktur, die in dem Gehäusesubstrat ausgebildet ist.

- 6. Verfahren nach Anspruch 1, wobei Bilden eines Arrays aus Halbleiterchips umfasst: Bestimmen einer minimalen Schneidelinienbreite, die mit einer Breite der ersten Gräben kompatibel ist, und Anordnen der Halbeleiterchips unter Anwendung einer Schneidelinienbreite, die kleiner ist als die bestimmte minimale Schneidelinienbreite.

Es folgen 8 Seiten Zeichnungen

# Anhängende Zeichnungen

FIG. 1a (Stand der Technik)

FIG. 2i

FIG. 2j