República Federativa do Brasil

Ministério do Desenvolvimento, Indústria

e do Comércio Exterior

Instituto Nacional da Propriedade Industrial

**(11) PI 9813494-9 B1**

\* B R P I 9 8 1 3 4 9 4 B 1 \*

**(22) Data de Depósito:** 08/12/1998

**(45) Data da Concessão:** 25/08/2015

**(RPI 2329)**

---

**(54) Título:** "SISTEMA E MÉTODO PARA PROCESSAR UM CONJUNTO DE SINAIS DE LINK REVERSO PROVENIENTES DE UM CONJUNTO DE UNIDADES MÓVEIS"

**(51) Int.CI.:** H04B1/707

**(30) Prioridade Unionista:** 09/12/1997 US 08/987,172

**(73) Titular(es):** Qualcomm Incorporated

**(72) Inventor(es):** Jeffrey A. Levin

**"SISTEMA E MÉTODO PARA PROCESSAR UM CONJUNTO DE SINAIS DE

LINK REVERSO PROVENIENTES DE UM CONJUNTO DE UNIDADES

MÓVEIS"**

**HISTÓRICO DA INVENÇÃO**

5    **I. Campo da Invenção**

A presente invenção está relacionada a comunicações sem fio digitais. Mais particularmente, a presente invenção está relacionada a um demodulador novo e aperfeiçoado para processar um conjunto de sinais de usuário que facilita a implementação em um único circuito integrado.

10    **II. Descrição da Técnica Correlacionada**

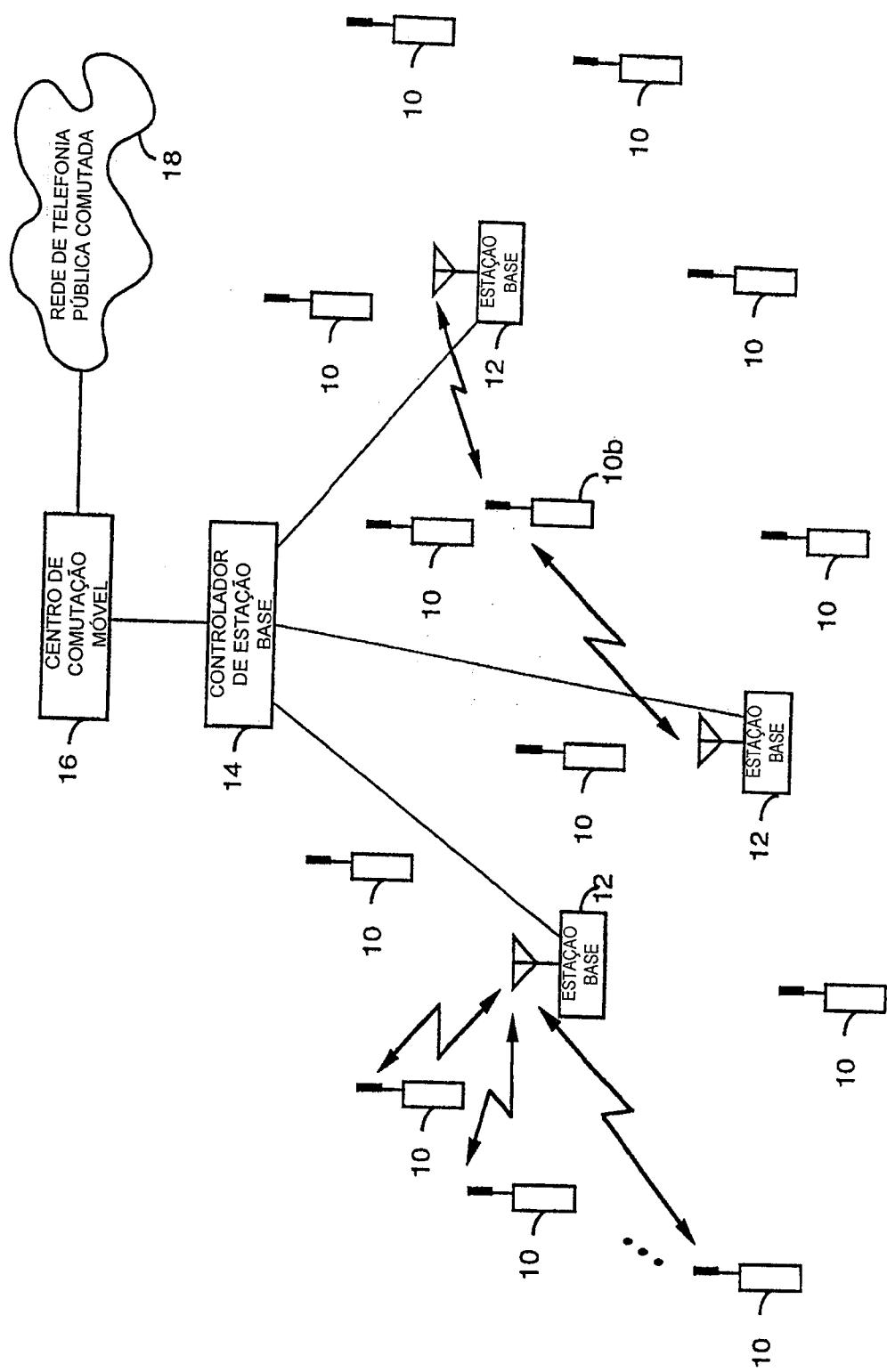

A Figura 1 é um diagrama de blocos de um telefone celular altamente simplificado configurado de acordo com o uso de uma interface aérea de múltiplo acesso por divisão de código (CDMA). Em particular, a Figura 1 ilustra um sistema de telefonia celular configurado de acordo com o uso da norma IS-95, que utiliza técnicas de processamento de sinais CDMA para fornecer um serviço de telefonia celular altamente eficiente e robusto. A IS-95 e suas derivadas, tais como a IS-95A e a ANSI J-STD-008 (referidas no presente documento coletivamente como a IS-95), são promulgadas pela Telecommunications Industry Association (TIA) bem como por outros organismos de padronização bem conhecidos. Adicionalmente, um sistema celular de telefonia configurado substancialmente de acordo com o uso da IS-95 está descrito na Patente U.S. Nº 5 103 459, intitulada "SYSTEM AND METHOD FOR GENERATING SIGNAL WAVEFORMS IN A CDMA CELLULAR TELEPHONE SYSTEM", em nome da Requerente da presente invenção.

30    Um benefício básico do uso de uma interface aérea CDMA é o de que as comunicações são conduzidas através da mesma banda de RF. Como exemplo, cada uma das unidades móveis 10 (tipicamente telefones celulares) apresentadas na Figura 1 pode se comunicar com uma mesma estação base 12

pela transmissão de um sinal de link reverso através dos mesmos 1,25 MHz do espectro de RF. De forma similar, cada estação base 12 pode se comunicar com unidades móveis 10 pela transmissão de um sinal de link direto através de 5 outros 1,25 MHz do espectro de RF. A transmissão de sinais através do mesmo espectro de RF fornece vários benefícios, incluindo um aumento no reuso da frequência de um sistema de telefonia celular, bem como a capacidade de conduzir o repasse suave (soft handoff) entre duas ou mais estações 10 base. O aumento no reuso de frequências permite que um maior número de chamadas seja conduzido através de uma dada faixa de espectro. O repasse suave constitui um método robusto para realizar a transição de uma unidade móvel da área de cobertura de duas ou mais estações base que envolve 15 realizar uma interface simultaneamente com duas estações base. O repasse suave pode ser comparado ao repasse abrupto (hard handoff), em que a interface com uma primeira estação base é finalizada antes que seja estabelecida uma interface com uma segunda estação base.

20 Durante a operação típica do sistema de telefonia celular da Figura 1, uma estação base 12 recebe um conjunto de sinais de link reverso provenientes de um conjunto de unidades móveis 10. As unidades móveis 10 estão efetuando chamadas telefônicas ou outras comunicações. Cada sinal de 25 link reverso é processado no interior de estações base 12 e os dados resultantes repassados ao controlador de estação base (BSC) 14. O BSC 14 provê alocação de recursos de chamada e funcionalidade de gerenciamento de mobilidade, incluindo a orquestração de repasses suaves entre as 30 estações base. O BSC 14 também direciona os dados recebidos para o centro de comutação móvel (MSC), que provê serviços de direcionamento adicionais para interface com o sistema da rede de telefonia pública comutada (PSTN).

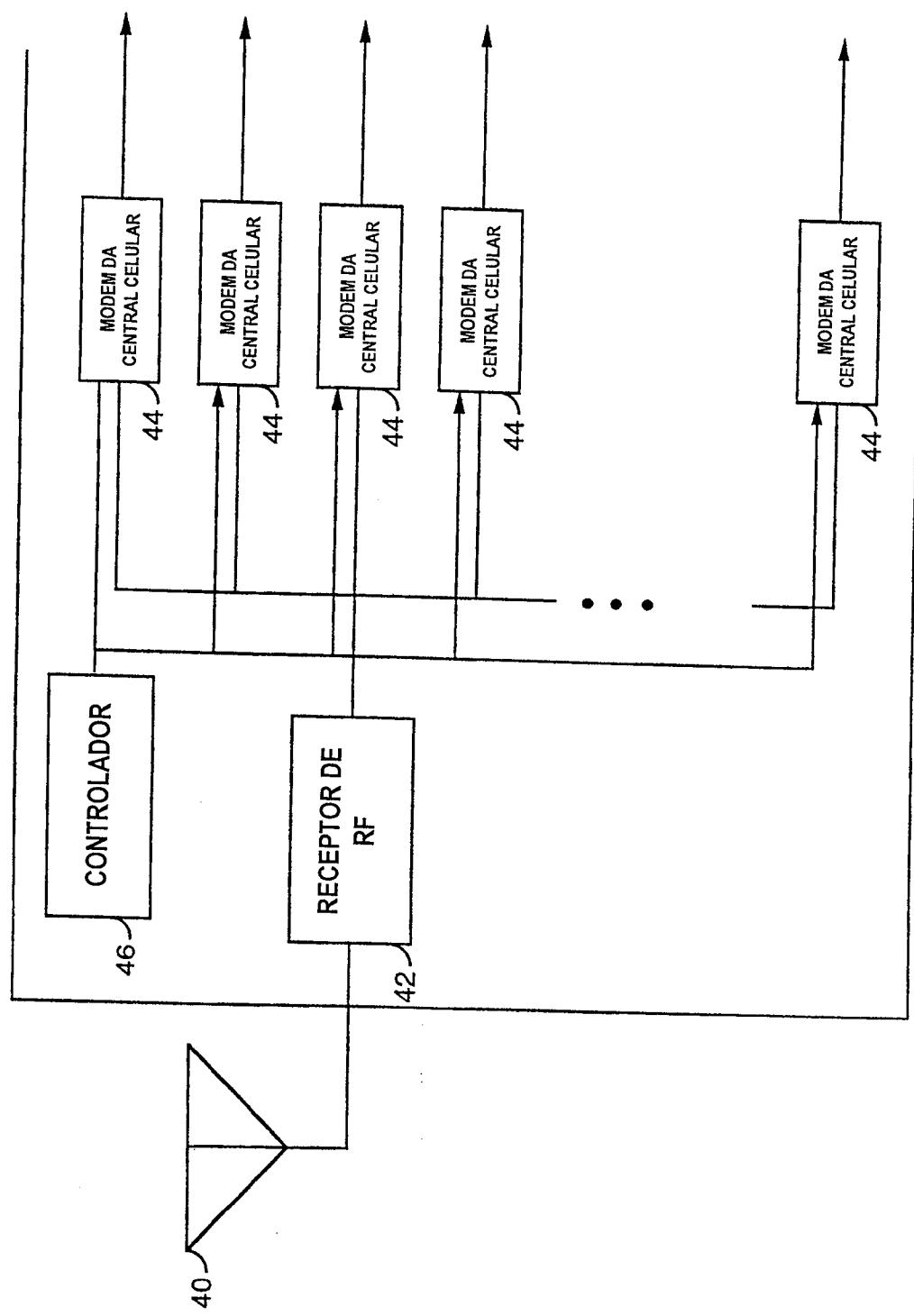

35 Na Figura 2 é apresentada uma parte de uma estação base da técnica anterior configurada para processar

um conjunto de sinais de link reverso provenientes de um conjunto de unidades móveis 10. Durante a operação, o sistema de antena 40 recebe um conjunto de sinais de link reverso transmitidos na mesma banda de RF a partir do 5 conjunto de unidades móveis 10 na área de cobertura associada. O receptor de RF 42 converte descendente e digitaliza o conjunto de sinais de link reverso produzindo amostras digitais que são recebidas pelos modems da central celular (cell site) (CSMs) 44. Cada CSM 44 é alocado pelo 10 controlador 46 para processar um sinal de link reverso específico proveniente de uma unidade móvel 10 específica e cada uma gera dados digitais que são repassados para o BSC 14. Um sistema e método para implementar cada CSM em um 15 único circuito integrado são descritos na Patente U.S. Nº 5 654 979, intitulada "CELL SITE DEMODULATOR ARCHITECTURE FOR A SPREAD SPECTRUM MULTIPLE ACCESS COMMUNICATION SYSTEM", e no Pedido Co-pendente de Patente U.S. Nº de Série 08/316 177, intitulado "MULTIPATH SEARCH PROCESSOR FOR ASPREAD SPECTRUM MULTIPLE ACCESS COMMUNICATION SYSTEM", ambos em 20 nome da Requerente da presente invenção.

De um modo geral, uma estação base deve ser capaz de realizar uma interface entre dezesseis e sessenta e quatro unidades móveis simultaneamente, de modo a fornecer capacidade adequada para uma típica demanda urbana. Isto 25 por sua vez, requer que cada estação base 12 contenha entre 16 e 64 CSMs. Apesar das estações base utilizando entre 16 e 64 CSMs terem sido implementadas e instaladas em ampla escala, o custo de tais estações base é relativamente elevado. Uma das principais causas de tal custo ocorre 30 pelas complexas e de certa forma sensíveis interconexões da unidade de RF para os vários CSMs e as interconexões entre os controladores de estação base e os CSMs. Tipicamente, um subconjunto de vinte e quatro (24) a cerca de três mil duzentos e vinte e seis (3226) CSMs é posicionado em uma 35 placa de circuito e o conjunto de placas de circuitos é

acoplado por meio de uma placa mãe (backplane), o qual por sua vez é acoplada a uma unidade de RF usando conjuntos de cabos coaxiais. Tal interconexão é cara e pouco confiável e contribui substancialmente para o custo total, complexidade 5 e manutenção de uma estação base 12. Portanto, tal configuração é altamente indesejável. A presente invenção está direcionada a um método e um equipamento para processar um conjunto de sinais de link reverso recebidos provenientes de um conjunto de unidades móveis sem a 10 necessidade de um conjunto considerável de modems de central celular.

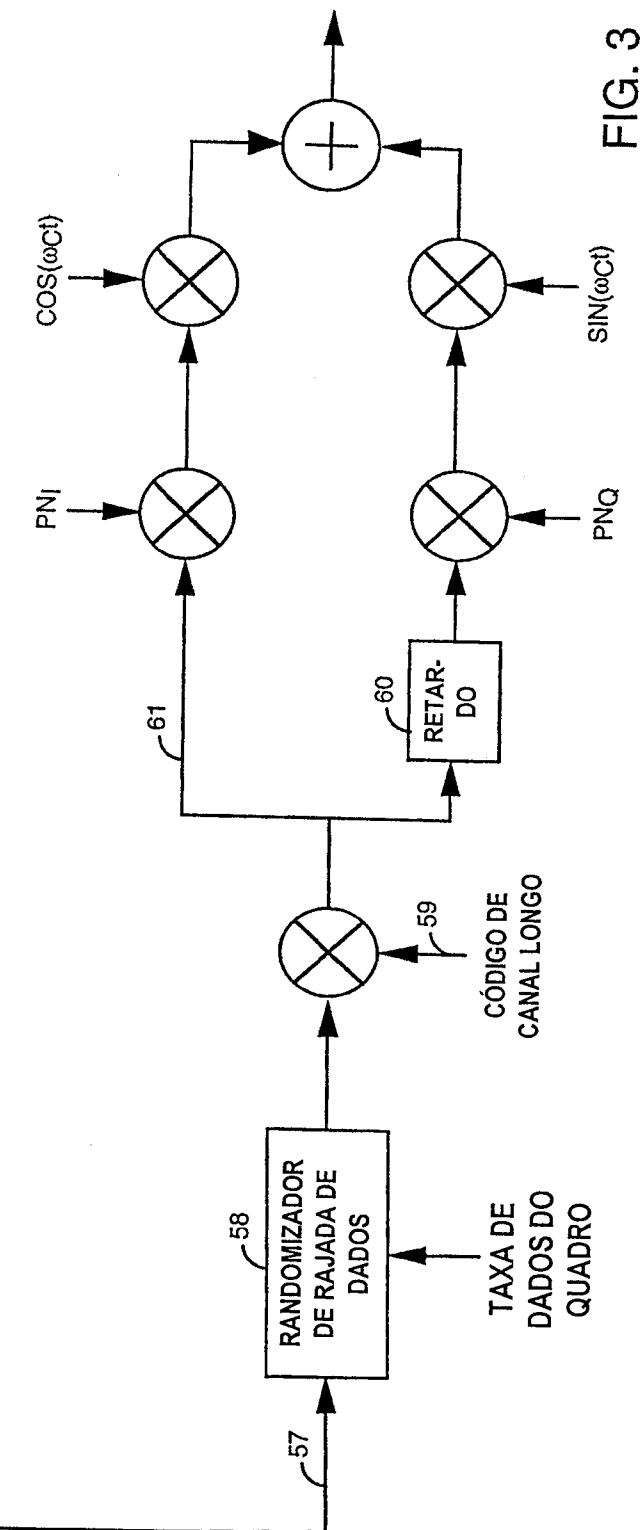

A Figura 3 é um diagrama de blocos que ilustra o processamento de sinais usado para a transmissão de um único canal de tráfego de link reverso de acordo com a 15 norma IS-95, fornecida para facilitar a compreensão da invenção. Dados 48 sendo transmitidos são fornecidos ao codificador convolucional 50 em segmentos de 20 ms, denominados quadros, em uma dentre quatro taxas, denominadas como "taxa total", "meia taxa", "um quarto de 20 taxa" e "um oitavo de taxa", respectivamente, uma vez que cada quadro contém metade dos dados que a anterior e, portanto, transmite dados em metade da taxa. Os dados 48 são tipicamente informações de áudio vocodificadas de taxa variável em que os quadros de taxas mais baixas são usados 25 quando uma menor quantidade de informações está presente, tal como durante uma pausa em uma conversação. O codificador convolucional 50 codifica convolucionalmente dados 48 produzindo símbolos codificados 51 e o repetidor de símbolos 52 gera símbolos repetidos 53 pela repetição de 30 símbolos 51 codificados em quantidade suficiente para gerar uma quantidade de dados equivalente à de um quadro de taxa total. Como exemplo, três cópias adicionais de um quadro de um quarto de taxa são geradas para um total de quatro cópias, enquanto que nenhuma cópia adicional de um quadro 35 de taxa total é gerada.

O intercalador de blocos 54 a seguir intercala em blocos os símbolos repetidos 53 para gerar símbolos intercalados 55. O modulador 56 realiza a modulação 64-ária sobre os símbolos intercalados 55 para produzir os símbolos Walsh 57. Isto é, um dentre sessenta e quatro possíveis códigos Walsh ortogonais, cada código consistindo de sessenta e quatro chips de modulação, é transmitido para cada seis símbolos intercalados 55. O randomizador de rajada de dados 58 realiza o bloqueio (gating), utilizando informações sobre taxa de quadros, sobre os símbolos Walsh 57 em rajadas pseudo-aleatórias, de tal forma que somente um exemplo completo dos dados seja transmitido. O bloqueio é realizado em incrementos de seis símbolos Walsh, denominados como "grupos de controle de potência", pois um comando de controle de potência é gerado na estação base a cada período correspondente. Dezesseis grupos de controle de potência ocorrem para cada quadro de 20 ms, com todos os dezesseis sendo transmitidos para um quadro de taxa total, oito para um quadro de meia taxa, quatro para um quadro de um quarto de taxa e dois para um quadro de um oitavo de taxa. Para cada quadro de taxa inferior, os grupos de controle de potência transmitidos constituem um subconjunto dos grupos transmitidos para um quadro de taxa mais elevada.

Os chips Walsh bloqueados são a seguir modulados em sequência direta usando um código de canal longo pseudo-aleatório (PN) 59 na taxa de quatro chips de código de canal longo para cada chip Walsh gerando dados modulados 61. O código de canal longo é exclusivo para cada unidade móvel 10 e é conhecido por cada estação base 12. Os dados modulados 61 são duplicados, com a primeira cópia sendo "espalhada" através de modulação com um código de espalhamento pseudo-aleatório em fase ( $PN_I$ ) produzindo os dados do canal I e a segunda cópia é retardada em metade de um chip de código de espalhamento pelo retardo 60 e

espalhada através de modulação com um código de espalhamento pseudo aleatório de fase em quadratura ( $PN_Q$ ) produzindo os dados do canal Q. Os conjuntos de dados espalhados ( $PN_I$ ) e ( $PN_Q$ ) são, cada um, filtrados por 5 passagem baixa (não mostrado), antes de serem usados para modular os sinais de portadora em fase e em quadratura, respectivamente. Os sinais de portadora modulados em fase e em quadratura são somados juntos antes de serem transmitidos para uma estação base ou outro sistema de 10 recepção (não mostrado).

O Pedido de Patente Europeu EP06900588 descreve um receptor RAKE para combinar todas as componentes de multipercorso úteis de um sinal de espalhamento espectral. O Pedido de Patente Europeu EP 0794623 descreve um receptor 15 de comunicação de espalhamento espectral. O Pedido de Patente Internacional WO 96/10873 descreve um processador de busca de multipercorso para um sistema de comunicação de acesso múltiplo com espalhamento espectral.

#### **SUMÁRIO DA INVENÇÃO**

20 A presente invenção consiste de um sistema e um método novos e aperfeiçoados para realizar o processamento digital de recepção para múltiplos sinais recebidos através da mesma banda de RF. Em uma modalidade preferida da invenção, amostras de RF digitais são armazenadas em uma 25 fila RAM que é acessada por um buscador e um demodulador. O buscador e o demodulador ficam de preferência localizados no mesmo circuito integrado juntamente com a fila RAM. O demodulador demodula um conjunto de sinais de link reverso armazenados dentro da fila RAM, em que cada sinal de link 30 reverso é recebido com um deslocamento de tempo específico e processado usando um código de canal específico. O buscador periodicamente procura sinais de link reverso não sendo processados pelo demodulador, e por requisições de acesso transmitidas através do canal de acesso. O buscador

procura de preferência durante os grupos de controle de potência relevantes de cada sinal de link reverso, os quais correspondem a dois dentre dezesseis grupos de controle de potência transmitidos durante um quadro de um oitavo de 5 taxa.

#### **BREVE DESCRIÇÃO DOS DESENHOS**

As características, objetivos e vantagens da presente invenção ficarão mais claros através da descrição detalhada apresentada a seguir, quando tomada em conjunto 10 com os desenhos, nos quais referências numéricas similares identificam itens correspondentes e nos quais:

A Figura 1 é um diagrama de blocos de um sistema de telefonia celular;

A Figura 2 é um diagrama de blocos de uma porção 15 de uma estação base configurada de acordo com a técnica anterior;

A Figura 3 é um diagrama de blocos de um sistema de transmissão usado para gerar um sinal de link reverso IS-95;

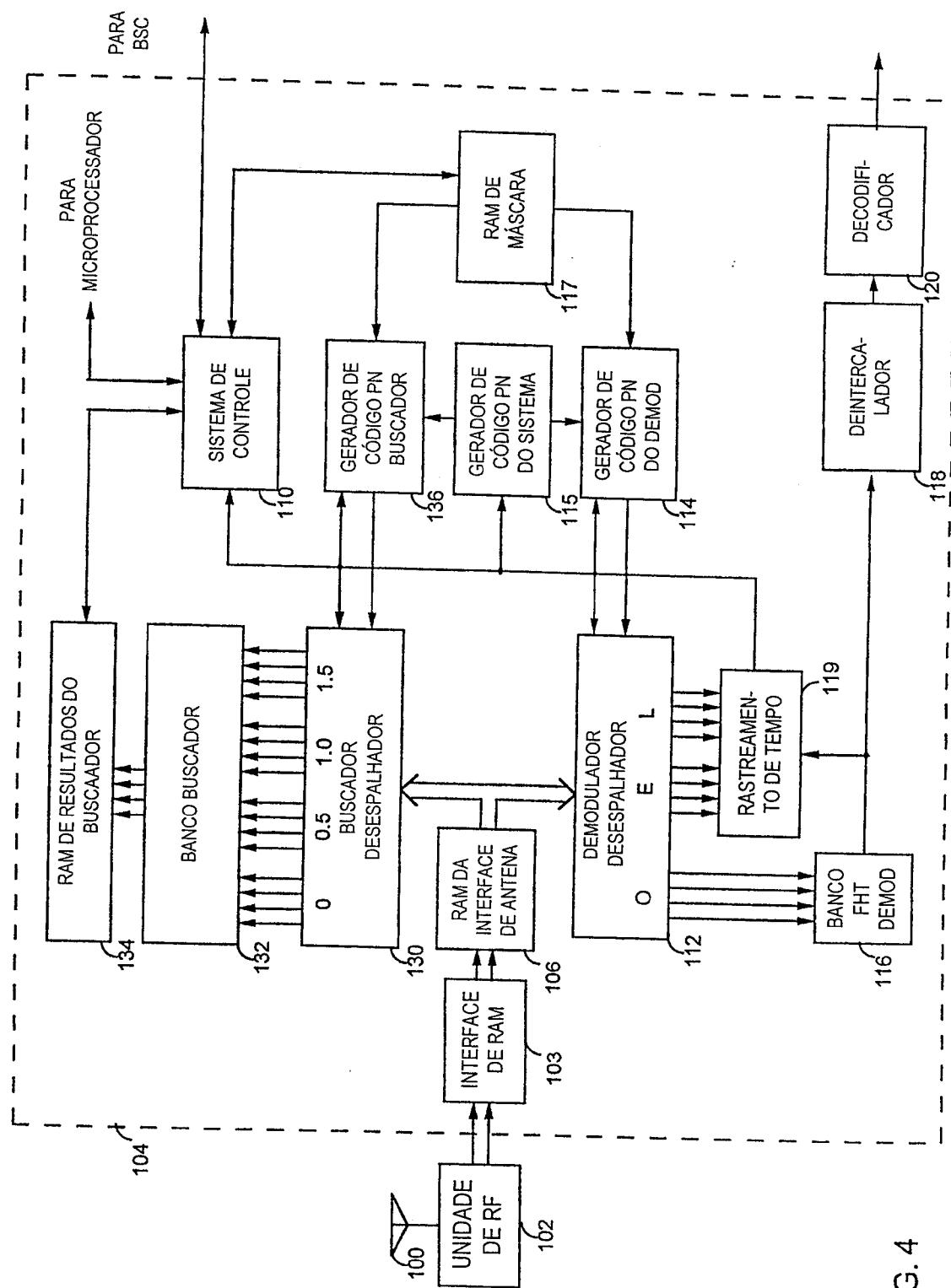

20 A Figura 4 é um diagrama de blocos de uma porção do sistema de processamento de recepção de uma estação base, quando configurado de acordo com uma modalidade da invenção;

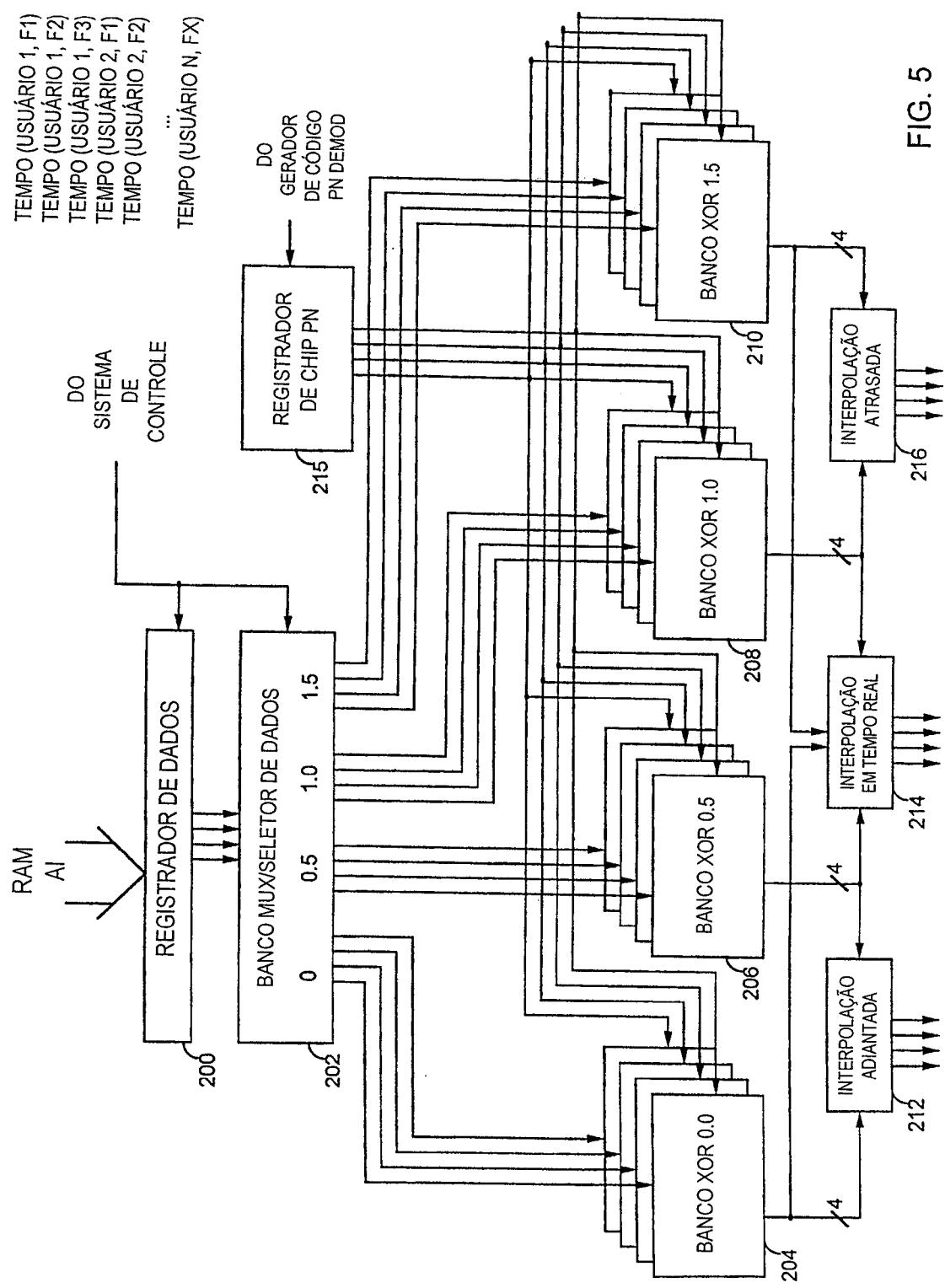

A Figura 5 é um diagrama de blocos do demodulador 25 quando configurado de acordo com uma modalidade da invenção;

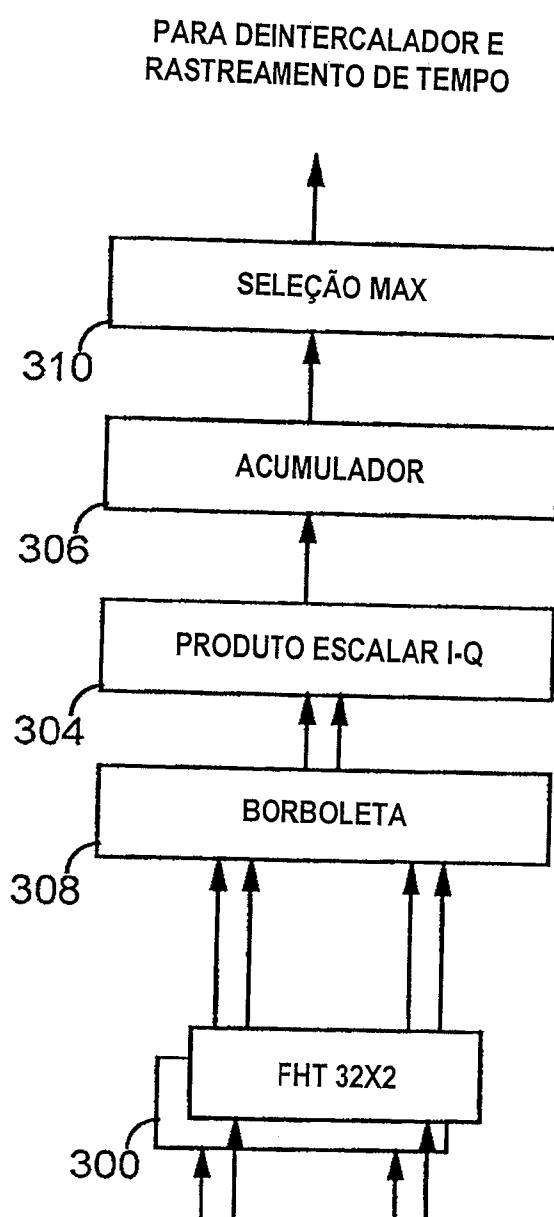

A Figura 6 é um diagrama de blocos do banco demod FHT quando configurado de acordo com uma modalidade da invenção;

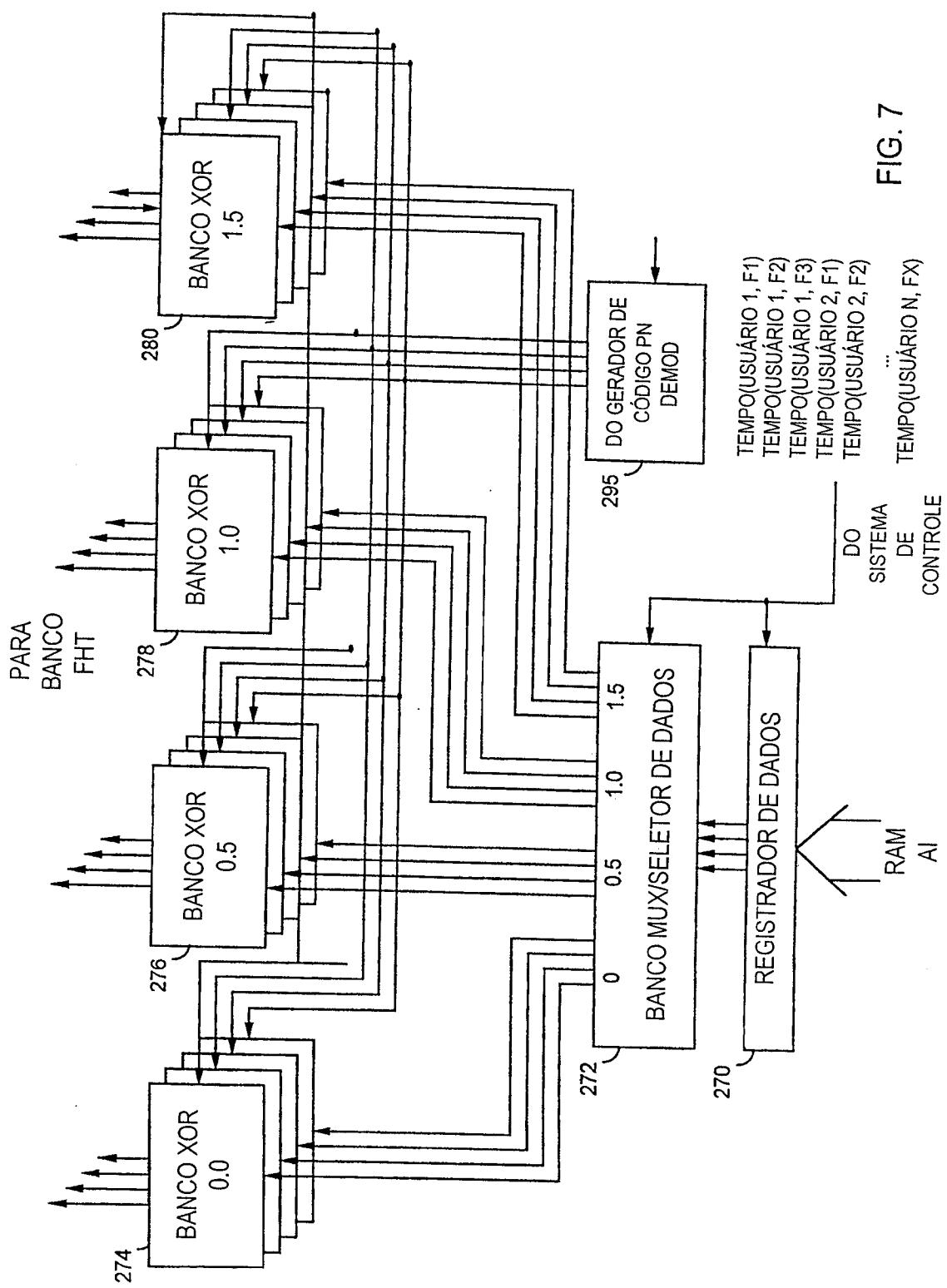

30 A Figura 7 é um diagrama de blocos do buscador quando configurado de acordo com uma modalidade da invenção;

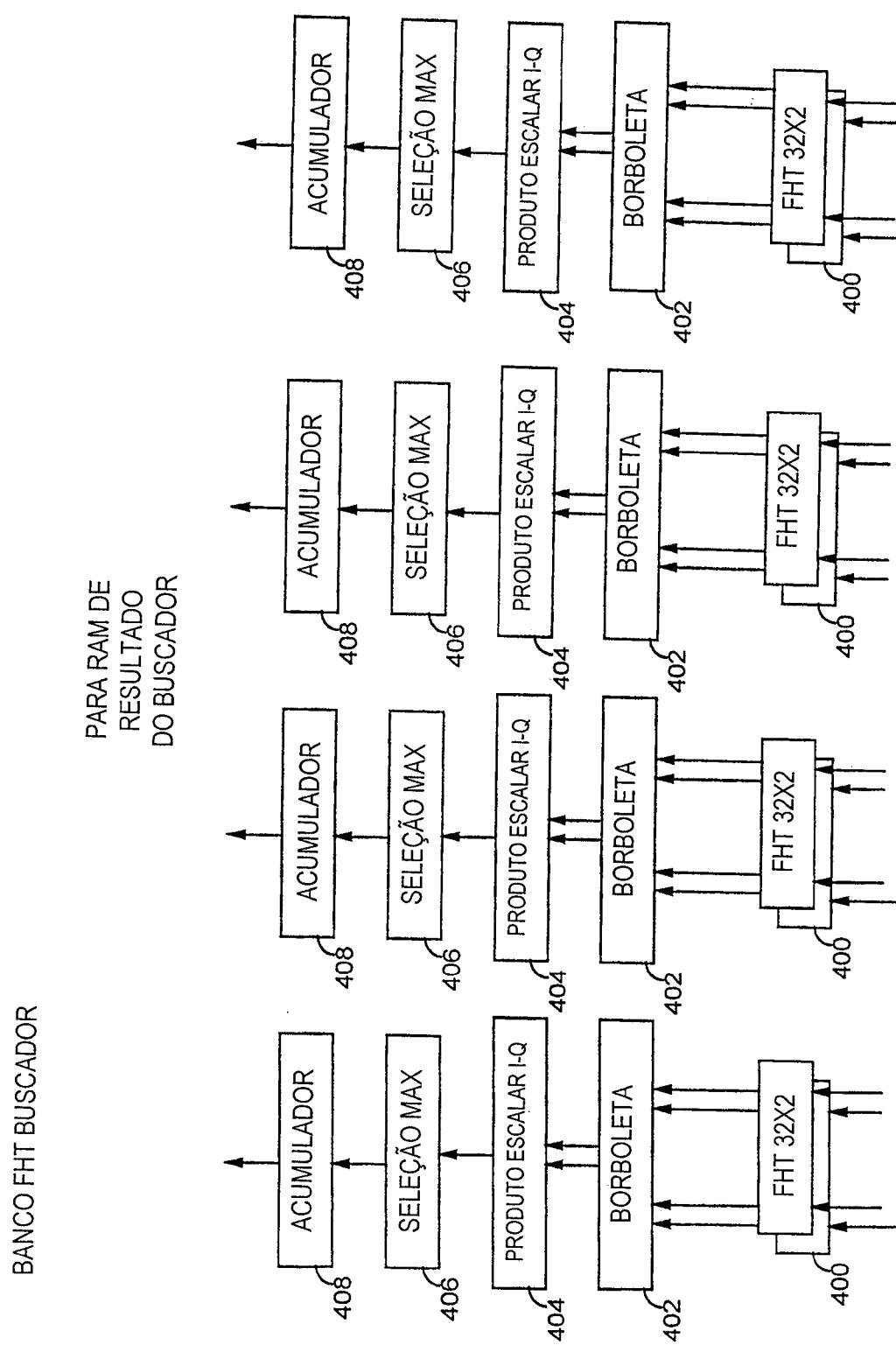

A Figura 8 é um diagrama de blocos do banco buscador FHT quando configurado de acordo com uma 35 modalidade da invenção;

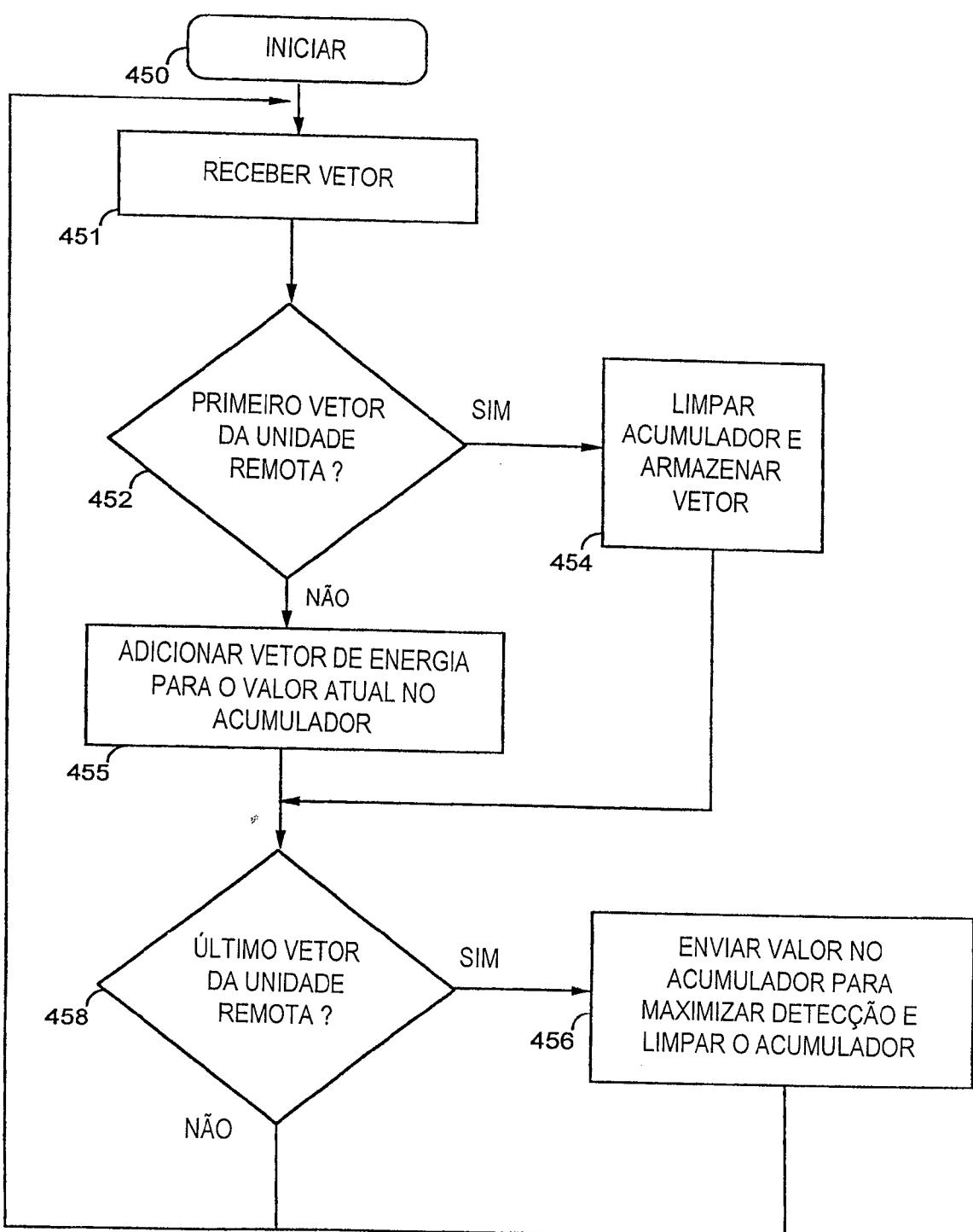

A Figura 9 é um fluxograma das etapas realizadas durante a fase de armazenamento da demodulação em tempo real quando realizada de acordo com uma modalidade da invenção;

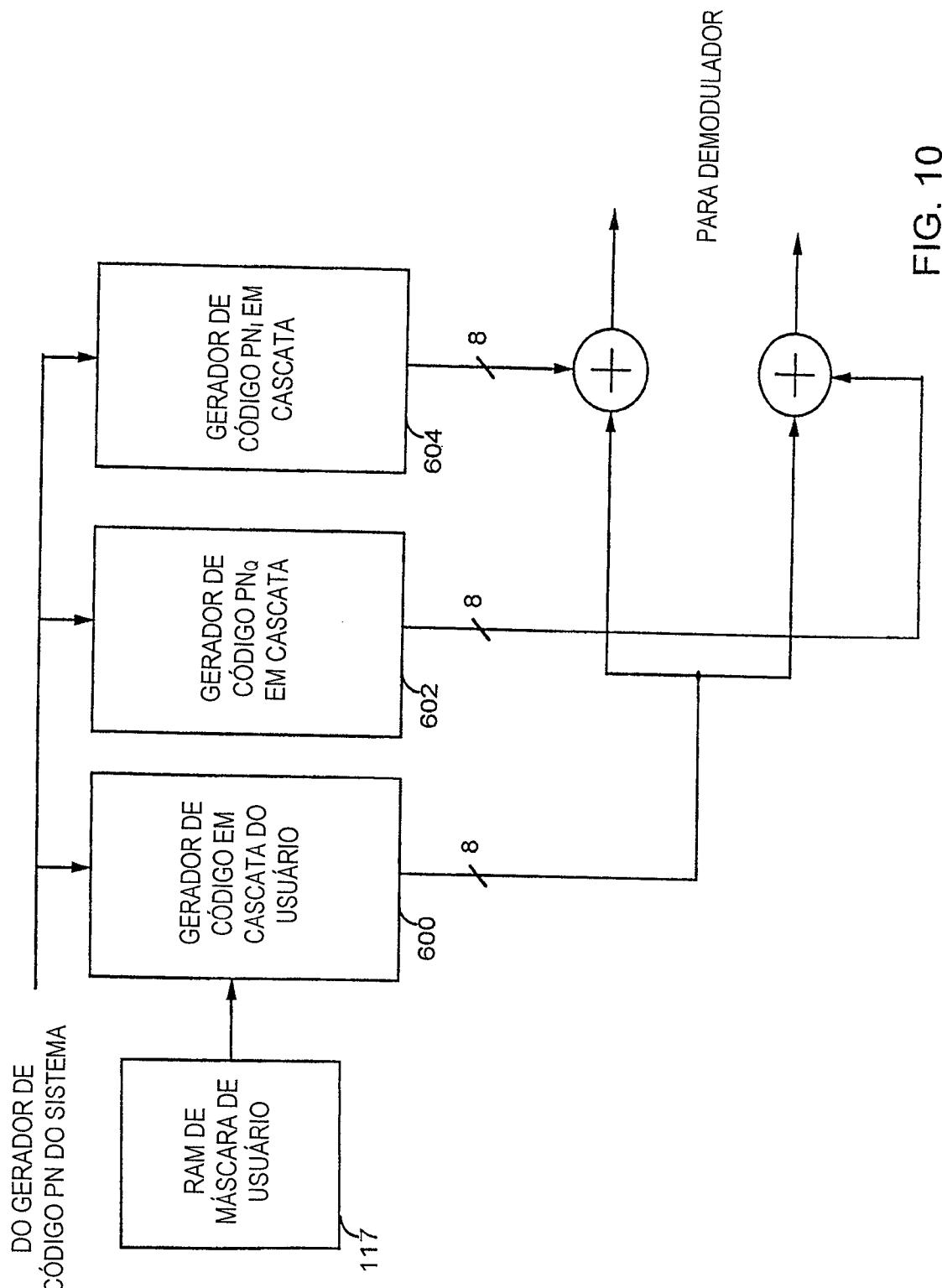

5 A Figura 10 é um diagrama de blocos do gerador de código PN demod quando configurado de acordo com uma modalidade da invenção;

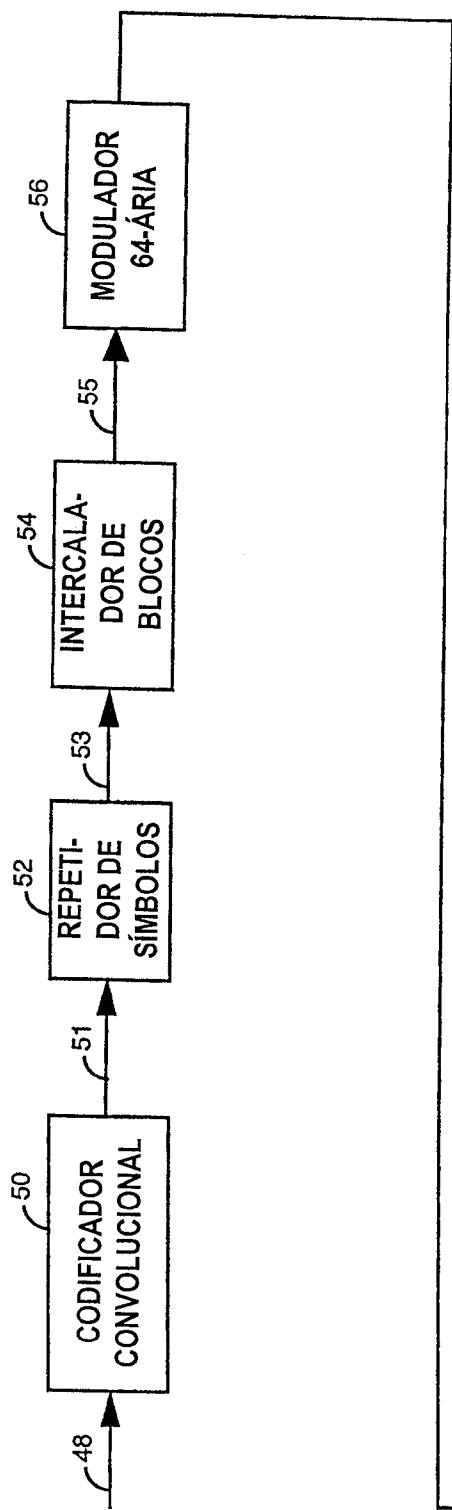

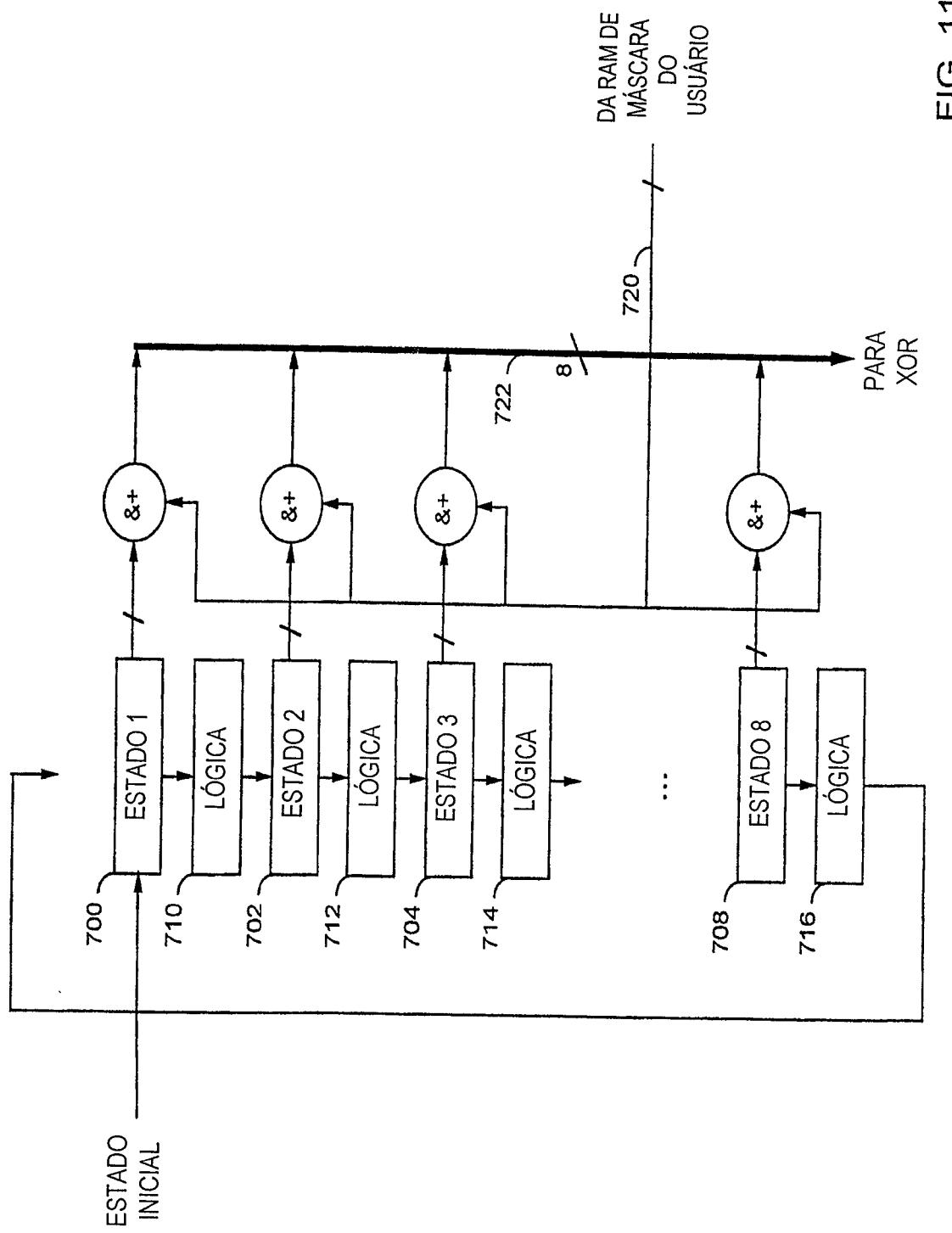

10 A Figura 11 é um diagrama de blocos de um gerador de código PN em cascata quando configurado de acordo com uma modalidade da invenção;

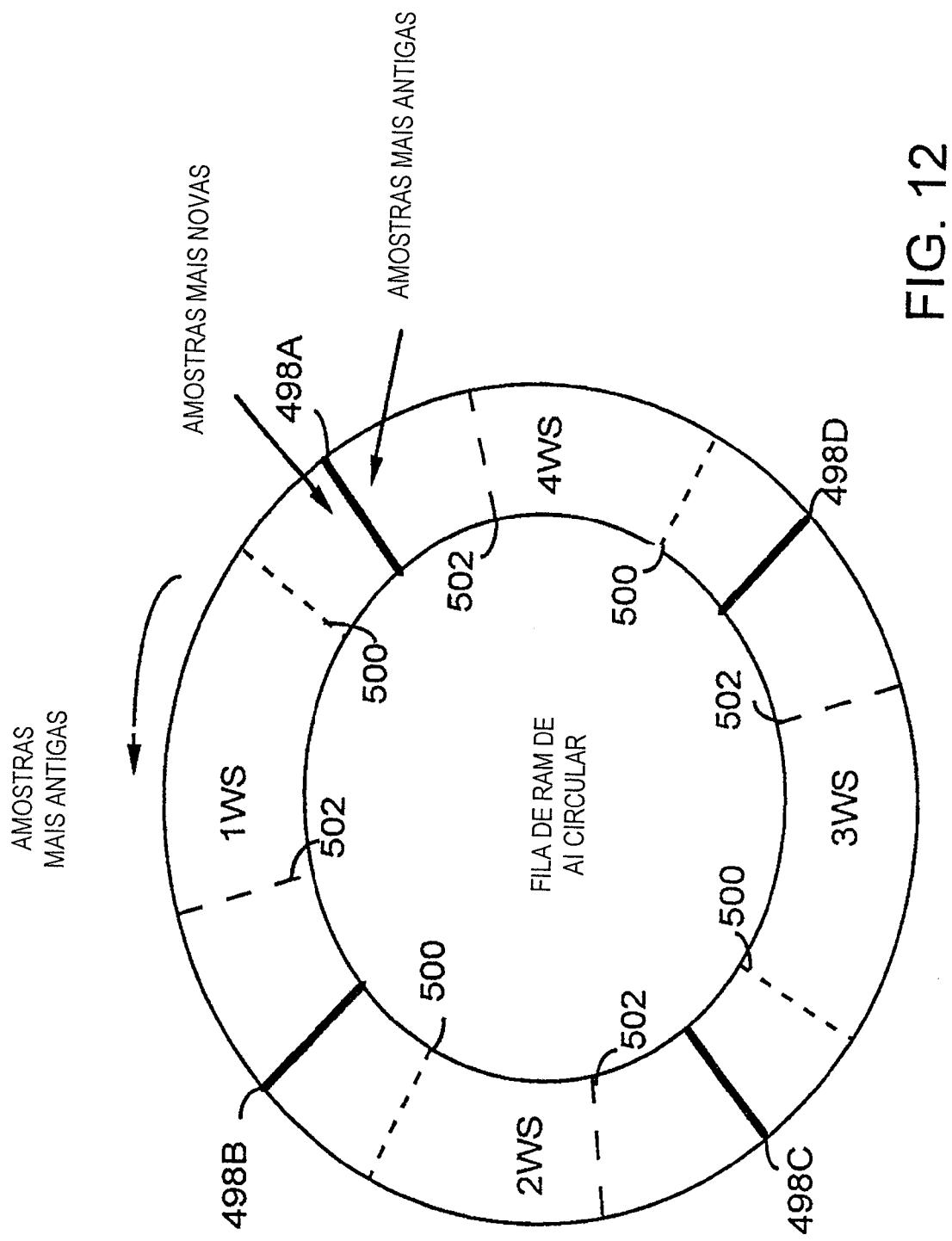

A Figura 12 é um diagrama de blocos da estrutura da fila RAM de interface de antena quando configurada de acordo com uma modalidade da invenção;

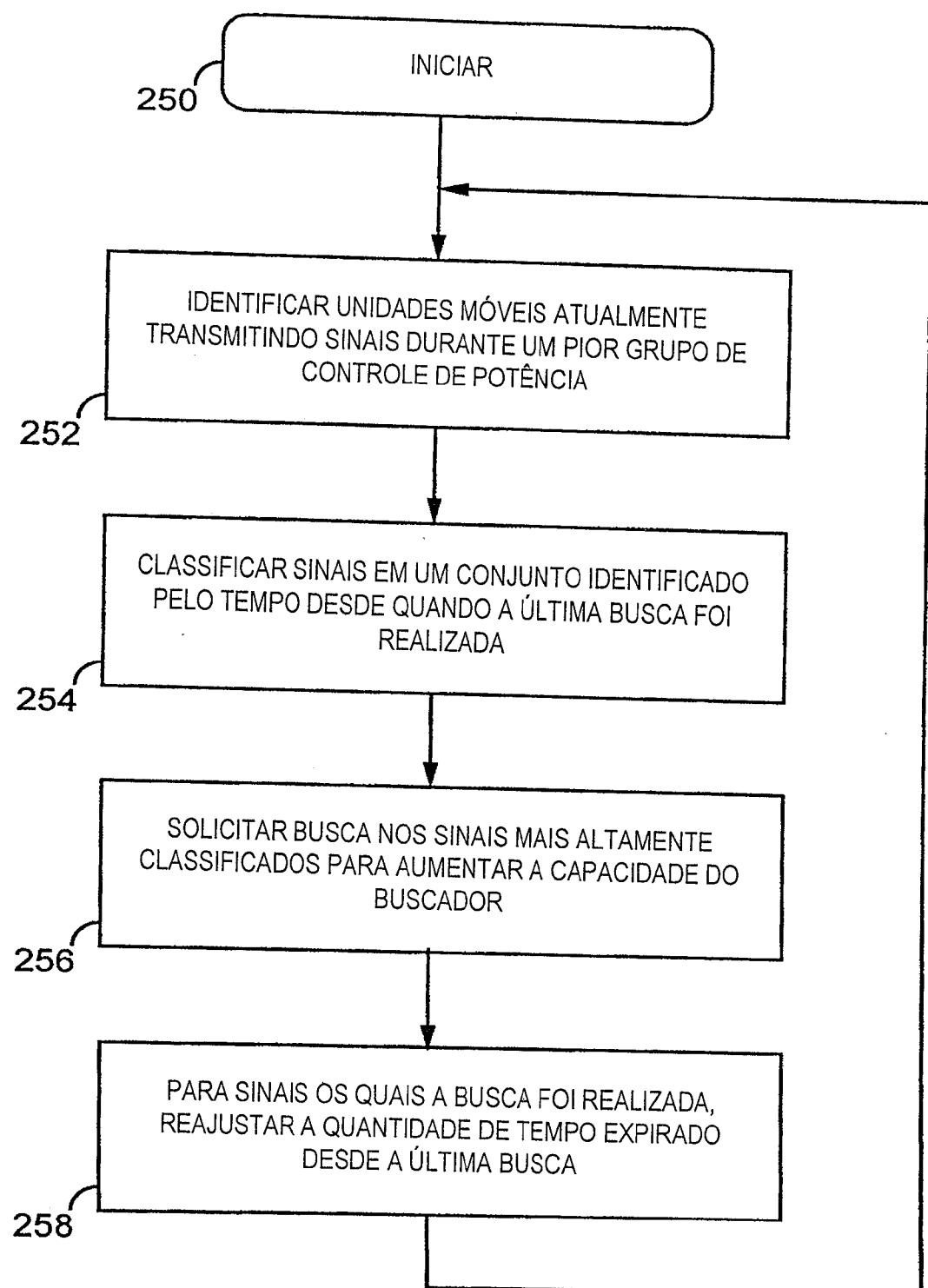

15 A Figura 13 é um fluxograma das etapas realizadas durante uma busca quando realizada de acordo com uma modalidade da invenção; e

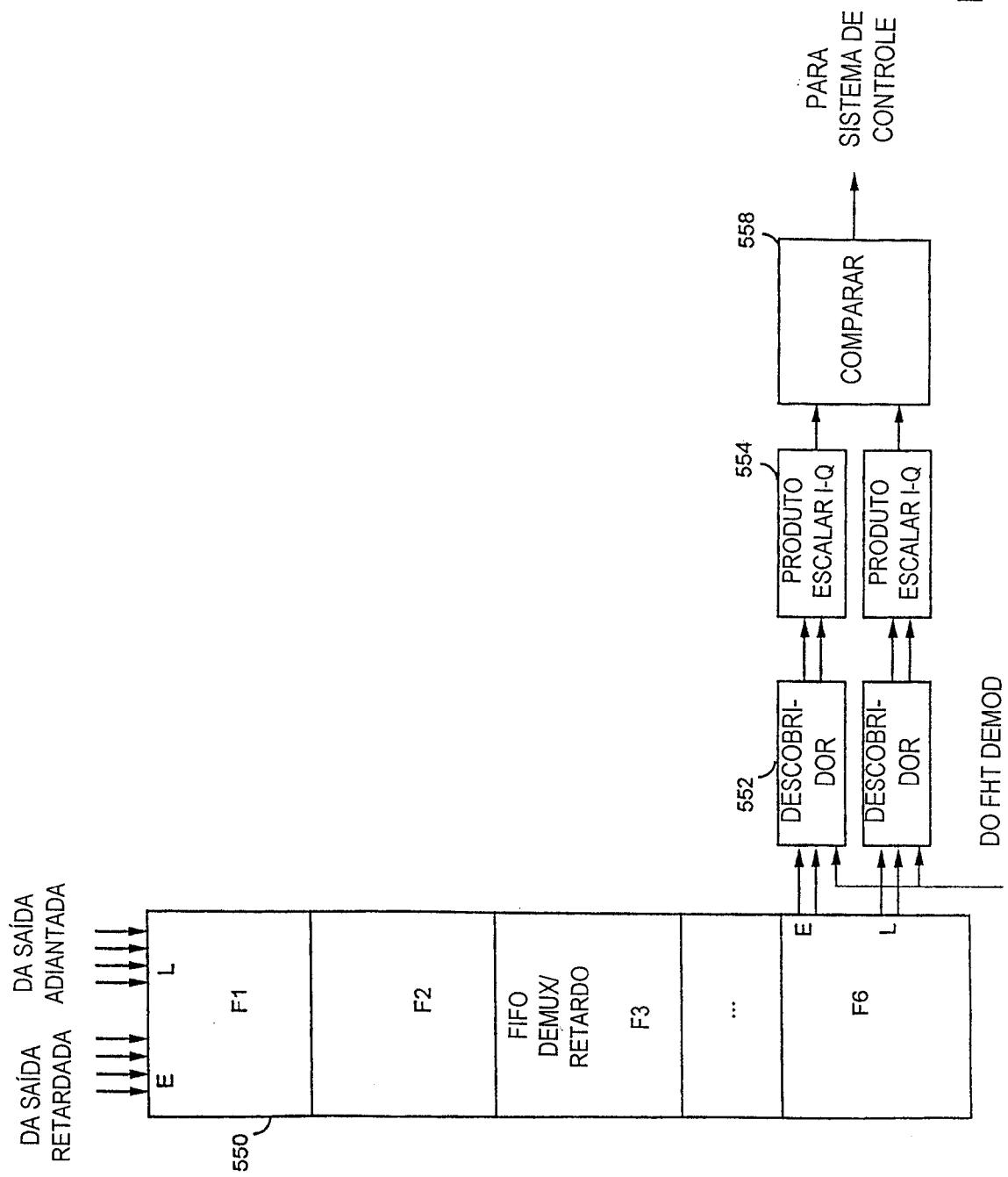

A Figura 14 é um diagrama de blocos de uma unidade de rastreamento de temporização quando configurada de acordo com uma modalidade da invenção.

20 **DESCRIÇÃO DETALHADA DAS MODALIDADES PREFERIDAS**

Um sistema e um método para demodular um conjunto de sinais é descrito no contexto de um sistema de telefone celular digital sem fio. Na modalidade preferida, o processamento digital de recepção é realizado com até 25 sessenta e quatro usuários e é substancialmente implementado usando-se um único circuito integrado. Apesar de tal configuração ser preferida, sendo a invenção particularmente bem adequada para tal configuração, a invenção pode também ser empregada em outras configurações, 30 incluindo sistemas de comunicação baseados em satélites, sistemas de comunicações por cabos e sistemas nos quais o processamento do sinal digital é realizado usando-se uma pluralidade de circuitos integrados.

A Figura 4 é um diagrama de blocos de um sistema 35 de processamento de recepção configurado de acordo com uma

modalidade da invenção. Em uma modalidade preferida da invenção, o sistema de processamento de recepção da Figura 4 fica localizado no interior de uma estação base 12 de um sistema de telefonia celular. Como mostrado, o sistema de processamento de recepção é constituído por um receptor de RF 102 acoplado a um sistema de antena 100 e um sistema de processamento digital 104. O sistema de processamento digital 104 está de preferência localizado em um único circuito integrado, o que é tornado possível pela configuração e operação do sistema digital aqui descrito. O sistema de processamento digital 104 troca dados de controle com um sistema de controle externo, de preferência constituído por um microprocessador executando software armazenado na memória (não é mostrada). Além disso, o sistema de processamento digital 104 gera dados de recepção que são transmitidos para o controlador da estação base 14 da Figura 1 para processamento adicional e direcionamento para seu destino final. Ainda, múltiplas unidades de RF podem realizar interfaces com o sistema de processamento digital 104 correspondendo a, por exemplo, diferentes antenas ou setores em uma estação base.

Durante a operação, o receptor 102 recebe energia de RF incluindo um conjunto de sinais de link reverso provenientes de unidades móveis, juntamente com quaisquer ruídos de fundo e interferência através do sistema de antena 100. O receptor 102 filtra, converte descendente e digitaliza uma banda de 1,25 MHz da energia de RF que inclui o conjunto de sinais de link reverso e fornece as amostras digitalizadas ao sistema de processamento digital 104. De preferência, as amostras digitalizadas são fornecidas no dobro da taxa de chips de espalhamento, a qual é de 1,2288 Megachips por segundo (Mcps), para uma taxa de amostra de aproximadamente 2,5 MHz. O receptor 102 gera amostras em fase e de fase em quadratura pela mistura com uma senóide em fase (SEN) e uma

senóide de fase em quadratura (COS) durante a conversão descendente (downconversion), cuja técnica é bem conhecida pelos técnicos na área. As amostras possuem de preferência uma resolução de 4 bits.

5                   No interior do sistema de processamento digital 104, as amostras digitais são recebidas pela interface RAM 103 que armazena as amostras 2x na RAM de armazenamento circular da interface de antena (AI) 106. A RAM de armazenamento circular 106 pode ser qualquer tipo de

10 sistema de memória, incluindo uma RAM estática. A decimalização é realizada para reduzir o tamanho necessário de RAM de armazenamento circular, fornecendo ainda resolução aceitável o suficiente para detectar e seguir

15 sinais específicos de link reverso dentro de um conjunto de sinais de link reverso e outros ruídos de fundo. A RAM de armazenamento circular de preferência armazena quatro (4) símbolos Walsh relevantes (Walsh symbols worth) para amostras 2x em fase e em quadratura em qualquer dado momento, o que corresponde a 2.048 amostras de fase em

20 quadratura (4 símbolos Walsh x 64 chips Walsh/símbolo x 4 chips de espalhamento/chip Walsh x 2 amostras/chip de espalhamento). Uma vez que cada amostras possui 4 bits, a memória total requerida na modalidade descrita é de 2.048 kbytes.

25                   Sob o controle do sistema de controle 110 e utilizando códigos de ruído pseudo-aleatório provenientes do gerador de código PN demod 114, o demodulador 112 recupera amostras a partir da RAM de armazenamento circular 106 e desespalha (despreads) um conjunto de sinais de link reverso ali armazenados. Como foi acima mencionado, de

30 acordo com as técnicas CDMA, cada sinal de link reverso é modulado e demodulado com um conjunto de códigos PN que é exclusivo para cada unidade móvel 10. Para o link reverso IS-95, o conjunto de códigos PN inclui um código PN em fase

35 ( $PN_I$ ) para os dados em fase, um código PN de fase em

quadratura ( $PN_Q$ ) e um código de usuário (PNU) que é usado para modular ambos os sinais em fase e em quadratura. A porção do conjunto de códigos PN para cada sinal de link reverso demodulado é fornecida pelo gerador de código PN 5 demod 114.

De acordo com a norma IS-95, o estado dos códigos PN usados durante a modulação depende de um tempo do sistema conhecido e seguido por cada estação base, de preferência pelo uso de receptores GPS (Global Positioning 10 System) e fornecido a cada unidade móvel 10 através do canal piloto e canais de sincronização. A unidade móvel 10 transmite o sinal de link reverso usando o conjunto de códigos PN determinados com base no tempo do sistema fornecido a partir da estação base. As estações base 15 recebem os sinais de link reverso após algum retardo de transmissão, com o estado dos códigos PN de link reverso usado para processar o deslocamento de sinal pelo retardo de transmissão com relação ao tempo do sistema na estação base.

20 Cada deslocamento é de um modo geral diferente para cada unidade de assinante, uma vez que elas estão posicionadas a distâncias diferentes em relação à estação base 12. Os sinais de link reverso são identificados por seu deslocamento, bem como pelo código de usuário (PNU) da 25 unidade móvel 10 a partir da qual eles são gerados. O código de usuário pode ser determinado a partir da MOBILE ID ou ESN da unidade móvel 10. Dessa forma, os sinais recebidos provenientes de uma unidade móvel 10 específica podem ser referenciados pelo fornecimento da ESN da unidade 30 móvel 10 e o deslocamento com o qual os sinais são recebidos. Múltiplas ocorrências de um sinal proveniente da mesma unidade móvel 10 são tipicamente geradas através de reflexão e outros fenômenos de multipercorso, em que os percursos possuem comprimentos diferentes. De preferência, 35 o demodulador 112 demodula em deslocamentos para os quais

sinais foram detectados e a demodulação é realizada continuamente naqueles deslocamentos até que a comunicação seja finalizada, ou o sinal não mais seja detectado.

Durante a operação, o demodulador 112 emite dados para cada sinal de link reverso processado nos deslocamentos especificados pelo sistema de controle 110 (rotulado como "0" para os dados em tempo real). Adicionalmente, o demodulador 112 emite sinais processados 1/2 da duração de um chip de espalhamento, antes dos deslocamentos especificados (rotulados como "E" de adiantados) e processados metade (1/2) da duração de um chip de espalhamento após os deslocamentos especificados (rotulados como "L" de atrasados). Na modalidade preferida da invenção, quatro saídas são geradas para cada deslocamento, com as quatro saídas correspondendo a versões pares e ímpares dos dados em fase e em quadratura. As versões pares e ímpares são meramente porções alternantes dos dados recebidos, com as versões separadas fornecidas de modo a facilitar o processamento pelo banco FHT demod 116, descrito em maiores detalhes a seguir.

O banco FHT demod 116 recebe os dados desespalhados em tempo real provenientes do demodulador 112 e realiza uma transformada Hadamard rápida tanto sobre os dados em fase como em quadratura a partir de cada um que gera dados de decisão suave em tempo real. Os dados de demodulação adiantados e atrasados são fornecidos ao sistema de rastreamento de tempo 119 que armazena os dados enquanto os dados de demodulação em tempo real são adicionais processados. Os dados em tempo real de decisão suave são fornecidos ao deintercalador 118. O deintercalador 118 deintercala os dados de decisão suave recebidos para cada sinal de link reverso em blocos de 20 ms e os dados de decisão suave deintercalados são fornecidos ao decodificador 120. O decodificador 120 de preferência realiza decodificação em treliça ou Viterbi

para fornecer os dados de decisão abrupta 122 repassados ao controlador de estação base 14 da Figura 1.

O sistema de rastreamento de tempo 119 recebe os dados desespalhados adiantados e atrasados bem como os dados de decisão suave em tempo real combinados e descobre (decovers) os dados desespalhados usando o símbolo Walsh indicado como o mais provável pelos dados de decisão suave combinados. Caso os dados de decisão suave adiantados contenham mais energia, o sistema de rastreamento de tempo 119 decrementa, incrementa, ou avança, um armazenador (buffer) resíduo de deslocamento de temporização associado com o exemplo de multipercurso do (ramo) do sinal de link reverso sendo processado em uma fração de chip PN. Em particular, o armazenador de deslocamento de tempo é deslocado em uma quantidade proporcional à magnitude da diferença dos dois níveis de energia. Caso os dados de decisão suave atrasados descobertos contenham mais energia, o sistema de rastreamento de tempo 119 incrementa ou decrementa ou retarda o armazenador de resíduo de deslocamento de temporização associado ao ramo que está sendo processado na mesma fração de um chip PN.

Quando a quantidade armazenada no armazenador de deslocamento de temporização pela qual o processamento é avançado ou retardado alcança um oitavo (1/8) da duração de um chip de espalhamento PN, o deslocamento real em que o sinal de link reverso específico é processado é incrementado ou decrementado em um oitavo (1/8) da duração de um chip de espalhamento PN. Na modalidade preferida da invenção, a quantidade em que o armazenador de deslocamento de temporização é incrementado é de um dois mil avos (1/204800) da duração de um chip de espalhamento para cada dezesseis chips de espalhamento demodulados, apesar do uso de outras quantidades de incremento ser consistente com o uso da presente invenção.

Simultaneamente com o processamento realizado pelo demodulador 112, o buscador 130 recupera amostras a partir da RAM de armazenamento circular 106 sob o controle do sistema de controle 110. Em particular, o sistema de controle 110 instrui o buscador 130 a recuperar porções específicas das amostras armazenadas na RAM de armazenamento circular 106 e a realizar um conjunto de demodulações de deslocamento de tempo usando o conjunto de códigos de espalhamento para uma unidade móvel 10 5 específica para determinar se um sinal de link reverso provém daquela unidade móvel que está sendo recebida naquele momento. De preferência, o buscador 130 demodula com deslocamentos para os quais os sinais de link reverso não são sinais que não estão sendo correntemente 10 10 demodulados pelo demodulador 112 de modo a detectar novos sinais de link reverso. As demodulações são de preferência realizadas em conjuntos de quatro, que correspondem a uma demodulação com deslocamento zero (rotulada como "0"), um deslocamento de chip de espalhamento de 0,5 (rotulado como 15 15 "0,5"), um deslocamento de chip de espalhamento de 1 (rotulado como "1") e um deslocamento de chip de espalhamento 1,5 (rotulado como "1,5"). Os códigos PN usados para realizar as demodulações são gerados pelo gerador de código PN buscador 136 sob o controle do sistema 20 20 de controle 110.

Os resultados das quatro demodulações são repassados para o banco FHT buscador 132 que realiza transformadas Hadamard rápidas sobre cada demodulação e acumula os resultados durante 6 símbolos Walsh ou um grupo 25 25 de controle de potência. Os níveis de energia de decisão suave resultantes provenientes do banco FHT buscador 132 são armazenados na RAM de resultados do buscador 134. O sistema de controle 110 acessa a RAM de resultados do buscador 134 e caso os níveis de energia sejam detectados 30 30 como estando acima de vários limites, instrui o demodulador 35 35

112 para iniciar o processamento no deslocamento de tempo associado.

De acordo com uma modalidade da invenção, o sistema de processamento digital 104 é configurado para 5 processar simultaneamente 256 sinais de link reverso que podem ser gerados ou transmitidos, a partir de até oitenta (80) diferentes unidades móveis 10. Adicionalmente, até seis (6) casos (ramos) de multipercorso de um sinal de link reverso específico podem ser processados em qualquer 10 momento. No entanto, uma vez que o número total de sinais de link reverso processados não pode superar duzentos e cinquenta e seis (256), o número de casos de multipercorso que pode ser processado para qualquer sinal de link reverso específico pode ser tipicamente menor que seis, dependendo 15 do número total de sinais de link reverso sendo processado e do número de casos de multipercorso sendo recebido para cada sinal de link reverso. Ao se permitir que até 80 diferentes sinais de link reverso sejam processados juntamente com até seis (6) casos de multipercorso para 20 cada sinal de link reverso, é fornecida maior flexibilidade pelo fato de que o sistema pode ser configurado para processar vários casos de multipercorso para um conjunto menor de sinais de link reverso, o que é preferido para um terreno altamente irregular, ou para processar menos casos 25 de multipercorso de muitos sinais de link reverso, o que é preferido para um terreno mais regular.

Adicionalmente, a capacidade de processar 6 casos de 80 diferentes sinais de link reverso permite que um único sistema de processamento digital 104 realize o 30 processamento de sinais necessário para uma estação base 12 de três seções possuindo vinte unidades móveis 10 por setor. Uma estação base 12 com três seções possuindo vinte unidades móveis por setor constitui uma configuração comum na indústria e, portanto, um sistema de processamento 35 digital 104 capaz de implementar tal estação base 12,

particularmente com um único circuito integrado, é altamente desejável.

Para processar simultaneamente 256 sinais, o sistema de processamento digital 104 opera em uma taxa de 5 relógio (clock) de trinta e duas (32) vezes àquela da taxa de chips de código de espalhamento PN (chipx32), ou aproximadamente 40 MHz. Em tal taxa de relógio, o demodulador 112 pode alocar 32 ciclos de relógio para cada um entre os 256 sinais sendo processados. De forma 10 similar, o buscador 130 pode realizar vinte e cinco mil seiscentos e trinta e duas (25632) operações de busca de quatro deslocamentos por operação proporcionando uma taxa de transferência (throughput) de 1024 percursos buscados durante cada grupo de controle de potência. O buscador 130 15 realiza 32 operações de demodulação para cada conjunto de novos chips de código de espalhamento PN recebidos. Adicionalmente, durante cada ciclo de relógio o buscador 130 recebe 16 chips de código de espalhamento PN para uma unidade móvel específica provenientes do gerador de código 20 de espalhamento PN do buscador 136 e o demodulador 112 recebe 16 chips de código de espalhamento PN para uma unidade móvel específica proveniente do gerador de código de espalhamento PN do demodulador 114. Dessa forma, o demodulador 112 realiza mil seiscentas e trinta e duas 25 (1632) operações de demodulação em desespalhamento (despread) (demods), cada uma envolvendo 16 chips de código de espalhamento PN por demodulação em desespalhamento, para cada conjunto de novos códigos de espalhamento recebidos das sessenta e quatro unidades móveis. O buscador 130 30 também realiza dezesseis demodulações de trinta e duas (32) espalhamentos, cada uma envolvendo 16 códigos de espalhamento PN em um conjunto de quatro deslocamentos de chip, 0, 0,5, 1,0 e 1,5.

Tanto o gerador de código PN do demodulador 114 35 quanto o gerador de código PN do buscador 136 recebem

códigos o sistema provenientes do gerador de código PN do sistema 114 e valores MASK da RAM de máscara 117. Durante cada símbolo Walsh, o gerador de código PN do sistema 114 provê 72 bits de dados de código PN do sistema para o gerador de código PN do demodulador 114 e o gerador de código PN do buscador 136 sob o controle do sistema de controle 110. Em particular, o gerador de código PN do sistema 114 gera o código de sistema em vários estados que correspondem ao deslocamento de tempo em que os vários sinais de link reverso estão sendo recebidos. Dessa forma, o demodulador 112 demodula um conjunto de sinais de link reverso usando os códigos PN supridos pelo gerador de código PN demod 114 e o buscador 130 demodula um conjunto de sinais de link reverso usando os códigos PN supridos pelo gerador de código PN do buscador 136.

A Figura 5 constitui um diagrama de blocos do demodulador 112 quando configurado de acordo com uma modalidade da invenção. O registrador de dados 200 recupera blocos de amostras digitais a partir da RAM de armazenador ou armazenamento circular 106 sob o controle do sistema de controle 110. O sistema de controle 110 especifica os blocos de dados a serem recuperados dentro da RAM de armazenador circular com base no deslocamento do sinal de link reverso sendo processado naquele momento específico, tal como descrito em maiores detalhes a seguir. A seleção de dados/banco mux (seleção de dados) 202 o deslocamento correto das amostras de dados 2x com base nas informações de deslocamento provenientes do sistema de controle 110 pelo deslocamento dos dados e aplica os dados de deslocamento de tempo aos bancos XOR 204 - 210. As amostras são fornecidas em porções pares e ímpares tanto das componentes em fase como em quadratura, portanto quatro linhas são apresentadas para a maioria das conexões.

Os bancos XOR 204 a 210 são constituídos por quatro sub-bancos XOR para processar as porções pares e

ímpares dos dados em fase e em quadratura de fase. Cada banco XOR recebe o código PN sendo descoberto e aplica o código PN às amostras em deslocamentos de 1/2 da duração de um chip de espalhamento uns dos outros proporcionando dados 5 desespalhados de deslocamento de chip 0,0, dados desespalhados de deslocamento de chip 0,5, dados desespalhados de deslocamento de chip 1,0 e dados desespalhados de deslocamento de chip 1,5. O código PN é recebido do gerador de código PN demod 114 da Figura 4 e 10 armazenado no registrador de chip PN 215.

Em uma modalidade preferida da invenção, o código PN para um sinal de link reverso específico é fornecido e a seguir o conjunto de até quatro deslocamentos para os quatro ramos daquele sinal de link reverso são processados 15 antes que o código PN para o próximo sinal de link reverso seja acoplado ao registrador de chips PN 115. Isto é, o mesmo segmento de código PN é usado para demodular até quatro casos de um sinal de link reverso específico, com diferentes casos sendo selecionados a partir de diferentes 20 conjuntos de amostras provenientes da RAM de armazenamento circular 106. As diferentes amostras são recuperadas pelo demodulador 112 em resposta às informações de deslocamento provenientes do sistema de controle 110. Pela demodulação com o mesmo segmento de código PN, os resultados de cada 25 ramo podem ser mais facilmente acumulados tal como descrito a seguir.

A presente invenção facilita o uso do mesmo segmento de código PN para demodular diferentes casos do mesmo sinal de link reverso pelo uso da RAM de 30 armazenamento circular 106 como um armazenador deskew no qual quatro símbolos Walsh de informações de sinal são armazenados até serem necessários. Pelo armazenamento de quatro símbolos Walsh relevantes de amostras fica provável que a mesma porção do sinal de link reverso será 35 simultaneamente armazenada na RAM de armazenamento circular

para cada ramo. Isto elimina a necessidade de usar memória adicional durante a combinação dos ramos para um sinal de link reverso específico. Outras modalidades da invenção podem usar alternativas para alinhar os dados provenientes de diferentes ramos dos mesmos sinais de link reverso tais como a introdução de retardo.

O circuito de interpolação adiantada 212 recebe dados desespalhados com deslocamento de chip 0,0 e dados desespalhados de deslocamento de chip 0,5 e calcula um valor para um deslocamento de dados desespalhados por 0; 0,1251/8; 0,251/4, ou 0,3753/8 da duração de um chip antes do deslocamento atual (dados desespalhados adiantados) usando interpolação. Em particular, o circuito de interpolação adiantada 212 calcula um valor para deslocamento de dados desespalhados por 0,5 em relação ao circuito de interpolação em tempo real 214. O circuito de interpolação adiantada 212 pode também receber dados de deslocamento de chips 1,0 e 1,5 em modalidades alternativas da invenção. Em uma modalidade da invenção é usada interpolação linear simples, entretanto, o uso de outros métodos de interpolação é consistente com a operação da invenção. Como exemplo, qualquer FIR de sete saídas é apropriada.

De forma similar, o circuito de interpolação em tempo real 214 recebe tanto dados desespalhados de deslocamento de chip 0,5 como dados desespalhados de deslocamento de chip 1,0 e calcula um valor para dados desespalhados em tempo real com um deslocamento de 0,5; 0,6255/8; 0,75\_ ou 0,8757/8, usando interpolação, dependendo do deslocamento atual do ramo que está sendo processado.

Adicionalmente, o circuito de interpolação tardia 216 recebe tanto dados desespalhados de deslocamento de chip 1,0 como dados desespalhados de deslocamento de chip 1,5 e calcula um valor para os dados desespalhados

retardados em 1,01, 1,1251 1/8, 1,251 2/8 ou 1,3751 3/8 a duração de um chip de espalhamento (dados desespalhados tardios) usando interpolação. Em particular, o circuito de interpolação tardia 216 calcula um valor para os dados desespalhados retardados em 0,5 a duração de um chip de espalhamento a partir dos dados desespalhados em tempo real, e um chip total a partir de dados desespalhados adiantados. Em uma modalidade da invenção, é também usada interpolação ILinear para calcular um valor para os dados desespalhados retardados. Como exemplo, é adequado um FIR de 15 saídas. Os dados adiantados, tardios e em tempo real são supridos ao banco FHT demod 116 da Figura 4.

A Figura 6 é um diagrama de blocos do banco FHT demod 116 quando configurado de acordo com uma modalidade da invenção. 32x2 FHTs 300 recebem dados desespalhados em tempo e efetuam transformadas Hadamard rápidas nas componentes em fase (I) e em quadratura (Q). Um sistema e método para realizar uma transformada Hadamard rápida estão descritos na Patente U.S. Nº 5 561 618, intitulada "METHOD AND APPARATUS FOR PERFORMING A FAST HADAMARD TRANSFORM", em nome da Requerente da presente invenção. A saída dos 32x2 FHTs 300 é processada pelo combinador borboleta (butterfly) somador - subtrator 308 que combina a saída das amostras pares e ímpares proporcionando um vetor de correlação I e um vetor de correlação Q. O produto escalar (dot product) I-Q 302 gera o produto escalar dos vetores de correlação I e Q proporcionando um vetor de energia de correlação que é emitido para o acumulador 306.

O acumulador 306 acumula os vetores de correlação de energia provenientes do produto escalar I-Q 304 para um conjunto de saídas que correspondem a diferentes exemplos (ramos) do mesmo sinal de link reverso. A armazenamento dos valores de correlação para um conjunto de ramos é facilitado pelo armazenamento de um volume de quatro símbolos Walsh de amostras no interior da RAM de

armazenamento circular, o que permite que o mesmo segmento de código PN seja usado para demodular vários exemplos do mesmo sinal de link reverso armazenados no interior da RAM de armazenamento circular 106.

5           Uma vez combinados os valores de correlação de energia provenientes de todos os ramos de um sinal de link reverso específico, o vetor de correlação de energia acumulado é fornecido à seleção MAX 310, que seleciona o valor de correlação máximo a partir do vetor de correlação 10 como sendo o mais provável ter sido transmitido e gera um correspondente valor índice. Um sistema e método para realizar uma operação de detecção de máximo estão descritos na Patente U.S. Nº 5 442 627, intitulada "NONCOHERENT RECEIVER EMPLOYING A DUAL-MAXIMA METRIC GENERATION 15 PROCESS", em nome da Requerente da presente invenção. A saída do seletor de máximo 310 é repassada ao deintercalador 140 da Figura 4.

A Figura 7 é um diagrama de blocos do buscador 130 quando configurado de acordo com uma modalidade da 20 invenção. O registrador de dados 270 recupera blocos de amostras digitais provenientes da RAM de armazenamento circular 106 sob o controle do sistema de controle 110. O sistema de controle 110 especifica os blocos de dados a 25 serem recuperados no interior da RAM de armazenamento circular com base no deslocamento do sinal de link reverso sendo processado naquele momento específico, tal como descrito em maiores detalhes a seguir. O seletor de dados/banco mux (seleção de dados) 272 ajusta o deslocamento de temporização ou temporização dos dados 30 sendo processados com base nas informações de deslocamento provenientes do sistema de controle 110 e aplica os dados de deslocamento de tempo aos bancos XOR 274 a 280. As amostras são fornecidas em porções pares e ímpares das componentes em fase e em quadratura, portanto quatro linhas 35 são apresentadas para a maioria das conexões.

Os bancos XOR 274 a 280 são, cada um, constituídos por quatro sub-bancos XOR para o processamento das porções pares e ímpares dos dados em fase e em quadratura. Cada banco XOR recebe o código PN que está 5 sendo demodulado e aplica o código PN às amostras em deslocamentos de 1/2 da duração de um chip de espalhamento umas em relação às outras, proporcionando dados espalhados de deslocamento de chip 0,0, dados espalhados de deslocamento 10 de chip 0,5, dados espalhados de deslocamento de chip 1,0 e dados espalhados de deslocamento de chip 1,5. O código PN é recebido do gerador de código PN do buscador 114 da Figura 4 e armazenado no registrador de chips PN 295. Os dados espalhados de deslocamento de chip para os quatro deslocamentos são repassados ao banco FHT de 15 buscador.

A Figura 8 é um diagrama de blocos do banco FHT do buscador 132 quando configurado de acordo com uma modalidade da invenção. Para cada deslocamento sendo processado, o par 32x2 FHT 400 recebe dados desespalhados 20 adiantados e realiza transformadas Hadamard rápidas sobre as componentes em fase (I) e em quadratura de fase (Q). A saída do par 32x2 FHT 400 é processada pelos combinadores borboleta soma - subtração 402, que combinam a saída das amostras pares e ímpares em uma forma alternante de soma - 25 subtração proporcionando um vetor de correlação I e um vetor de correlação Q. Os produtos escalares I-Q 404 geram o produto escalar dos vetores de correlação I e Q para cada deslocamento proporcionando um conjunto de vetores de energia de correlação.

30 Circuitos de seleção de máximo selecionam o valor de correlação de energia máximo a partir de cada vetor de correlação de energia e os acumuladores 408 acumulam o valor de correlação de energia por um conjunto de símbolos Walsh. De preferência, os acumuladores 408 acumulam os 35 valores de correlação de energia de um conjunto de seis

5 simbolos Walsh o que corresponde a um grupo de controle de potência. O uso de seis símbolos Walsh permite que uma quantidade suficiente de energia se acumule para detectar um sinal de link reverso com uma probabilidade suficientemente elevada, permitindo concomitantemente que um número suficiente de buscas seja realizado para detectar apropriadamente o suficiente dos sinais de link reverso sendo recebidos. As saídas dos acumuladores 410 são repassadas à RAM de resultados do buscador 134.

10 Voltando agora ao processo de demodulação, a Figura 9 é um fluxograma das etapas realizadas durante a fase de armazenamento da demodulação em tempo no interior do banco FHT demod 116 (Figura 4) de acordo com uma modalidade da invenção. O processamento se inicia na etapa 15 450 e na etapa 451 um vetor de valores de correlação de energia proveniente do FHT é recebido. Na etapa 452 é determinado se o vetor de energia que chega é o primeiro recebido a partir de uma unidade móvel 10 específica. Caso assim seja, o acumulador 306 (Figura 6) é limpo e os 20 vetores armazenados no acumulador que agora está vazio. Caso contrário, o vetor de energia é adicionado ao vetor de energia atualmente armazenado no acumulador 306 na etapa 455. Na etapa 455 é também determinado se o vetor que está sendo processado é o último vetor proveniente de uma 25 unidade móvel 10 específica. Caso não seja, a etapa 451 é novamente executada. Caso o seja, o valor armazenado no acumulador é repassado para o circuito detetor de máximo na etapa 456 e a etapa 451 é novamente executada.

30 A Figura 10 é um diagrama de blocos do gerador de código PN demod 114 quando configurado de acordo com uma modalidade da invenção. O gerador em cascata de código de espalhamento em fase (PNI) 600, o gerador em cascata de código de espalhamento de fase em quadratura (PNQ) 602 e o gerador em cascata de código de usuário 604 recebem, cada 35 um, informações de estado inicial provenientes do sistema

de controle 110. As informações de estado inicial informam de preferência o tempo do sistema em que o processamento de um link reverso específico deve se iniciar dada a forma de um número de 42 bits tal como usado na norma IS-95. O 5 estado inicial é de preferência fornecido a cada 256 chips de espalhamento, ou uma vez a cada símbolo Walsh.

Usando o estado inicial, os geradores em cascata 600 e 602 geram, cada um, oito (8) chips de código de espalhamento por ciclo de relógio. Adicionalmente, o 10 gerador em cascata 604 gera oito (8) bits de código de usuário por ciclo de relógio usando o estado inicial e a correspondente máscara de usuário proveniente da RAM de máscara de usuário 117. O código de usuário passa por "XOR" (EX-OU) com os códigos de espalhamento em fase e em 15 quadratura e os códigos combinados resultantes são repassados para o demodulador 112.

O gerador de código PN do buscador 136 de preferência opera de forma similar ao gerador de código PN demod 114, exceto pelo fato de que os estados iniciais e 20 códigos de máscara usados são diferentes uma vez que o sinal de link reverso específico sendo procurado em um dado momento não será necessariamente o mesmo que o sinal de link reverso sendo demodulado.

A Figura 11 é um diagrama de blocos do gerador em 25 cascata de código de usuário 604 quando configurado de acordo com uma modalidade da invenção. O registrador de estado 700 recebe o estado inicial a partir do sistema de controle 110 e o aplica aos circuitos lógicos 710. Os circuitos lógicos 710 efetuam as operações lógicas 30 necessárias para gerar o próximo estado de acordo com a norma IS-95 e portanto o estado do código do sistema avançado em um chip de espalhamento, que é armazenado no registrador de estado 2 702. Um sistema e método para formatar dados substancialmente de acordo com a norma IS-95 35 está descrito na Patente U.S. Nº 5 504 773, entitulada

"METHOD AND APPARATUS FOR THE FORMATTING OF DATA FOR TRANSMISSION", em nome da Requerente da presente invenção.

Os circuitos lógicos 712 a 716 e os registradores de estado 704 a 708, de modo similar, calculam e armazenam o tempo do sistema adiantado em um chip de código de espalhamento com relação ao registrador de estado anterior, com a saída dos circuitos lógicos 716 aplicada à alimentação do registrador de estado 1 700. Dessa forma, uma vez calculados oito estados os próximos oito estados podem ser calculados acoplando-se a saída dos circuitos lógicos 716 ao registrador de estado 1 700. Podem ser usados geradores em cascata calculando números menores ou maiores de registradores. Adicionalmente, o código de espalhamento pode ser calculado pelo uso de uma taxa de cálculo mais rápida, entretanto, o uso do gerador em cascata é preferido em vista de seu menor consumo de energia. Os técnicos na área reconhecerão métodos alternativos para calcular os códigos de espalhamento.

As saídas dos registradores de estado 700 a 708 passam também por "AND" (E) e "XOR" com a máscara de usuário 722 proveniente da RAM de máscara de usuário correspondente à unidade móvel 10 sendo demodulada e o número resultante passado pela XOR a um bit. Os oito bits resultantes formam o segmento de código de usuário de oito bits 722. O segmento de código de usuário de oito bits 722 é a seguir emitido para uma operação XOR adicional com os códigos de espalhamento em fase e em quadratura tal como foi acima descrito. Os geradores em cascata de código de espalhamento em fase e em quadratura 600 e 602 operam de maneira similar ao gerador em cascata de código de usuário 604, porém não usam a máscara de código de usuário e usam diferentes tamanhos de registradores de estado e diferentes circuitos lógicos tal como especificado pela norma IS-95.

A Figura 12 é um diagrama da estrutura virtual da fila RAM de armazenamento circular quando configurada de

acordo com uma modalidade da invenção. A fila é configurada em uma disposição circular, pelo que as amostras mais novas são gravadas sobre as amostras mais antigas. A capacidade da fila é suficiente para armazenar quatro (4) símbolos

5 Walsh de amostras digitais I e Q marcadas como 1WS a 4WS. As amostras mais novas se iniciam na linha 498A e as linhas 498B a D demarcam, cada uma, um valor de um símbolo de amostras. Outros sinais de link reverso são armazenados no interior dos símbolos Walsh relevantes de dados, com os

10 limites de símbolo Walsh para os sinais de link reverso que ocorrem com diferentes deslocamentos de tempo, dependendo do momento de chegada específico de tal sinal de link reverso. Como exemplo, as linhas 500 demarcam os limites de símbolo Walsh para um primeiro sinal de link reverso e as

15 linhas 502 demarcam os limites de símbolo Walsh para um segundo sinal de link reverso.

Como fica claro, alguns símbolos Walsh para alguns sinais de link reverso não são completamente armazenados no interior da fila RAM de armazenamento circular. Um símbolo Walsh parcialmente armazenado não é demodulado corretamente. No entanto, o armazenamento de um total de quatro símbolos Walsh de amostras assegura que pelo menos dois símbolos Walsh completos de amostras serão armazenados para cada sinal de link reverso. Amiúde, em

20 alguns casos, três símbolos Walsh podem ser demodulados através da RAM de armazenamento curricular por meio de transferências, pelo que o início de um símbolo Walsh é demodulado imediatamente antes de ser apagado.

Dois símbolos Walsh completos correspondem à

30 diferença máxima provável em deslocamento incorrida desde uma transmissão proveniente do limite da área de cobertura até uma transmissão proveniente de um local próximo à estação base. Dois símbolos Walsh completos correspondem também ao deslocamento máximo provável entre uma

35 transmissão de percurso direto de um sinal de link reverso

específico e outra componente de multipercurso refletida deste sinal de link reverso para o tamanho de célula geralmente aceito. Dessa forma, os sinais de link reverso transmitidos ao mesmo tempo do sistema serão 5 simultaneamente armazenados no interior da RAM de armazenamento circular, porém em locais diferentes, mesmo que eles tenham sido transmitidos a partir de diferentes locais dentro da área de cobertura da estação base. Tamanhos maiores de células podem ser acomodados pelo 10 aumento do tamanho da RAM de armazenamento circular. Adicionalmente, o uso de uma RAM de armazenamento circular de seis símbolos Walsh é útil para realizar a demodulação coerente, a qual requer tipicamente um certo grau de demodulação recorrente e portanto mais tempo de 15 processamento. O uso de uma RAM de armazenamento circular de oito símbolos Walsh é útil para demodulação auxiliada por dados, ou não causal, que envolve a busca por dados conhecidos e também utiliza processamento recorrente.

Fazendo novamente referência à Figura 4, durante 20 a operação o sistema de controle 110 segue o tempo do sistema na estação base das amostras mais recentes armazenadas na RAM de armazenamento circular. Adicionalmente, o sistema de controle 110 segue o deslocamento, ou retardo, de cada sinal de link reverso 25 correntemente conhecido e sendo processado pelo demodulador 112. Pelo uso do deslocamento, o sistema de controle 110 calcula a localização de endereçamento na memória, dentro da RAM de armazenamento circular, do próximo conjunto de amostras a ser processado para cada sinal de link reverso e 30 provê tal endereçamento inicial ao demodulador 112. Adicionalmente, o sistema de controle 110 provê ao gerador de código PN demod o conjunto de sinais de link reverso para os quais códigos PN devem ser gerados. O demodulador 112 a seguir recupera a memória da RAM de armazenamento 35 circular no deslocamento especificado e aplica o código de

espalhamento PN proveniente do gerador de código de espalhamento PN demod 114 no deslocamento especificado usando a seleção de dados 202 da Figura 4.

De forma similar, o sistema de controle 110 5 calcula quais sinais de link reverso buscar e em quais deslocamentos. Os cálculos são de preferência em resposta a um algoritmo de busca interno e em resposta a dados de controle recebidos do controlador de estação base 14 da Figura 1, notificando à estação base de que uma unidade 10 móvel 10 específica está entrando na área de cobertura daquela estação base. Tal notificação inclui informações de identificação sobre a unidade móvel que permitem a geração de códigos PN.

O sistema de controle 110 a seguir calcula a 15 localização do endereço da memória e provê tais localizações de endereço de memória ao buscador 130. Adicionalmente, o sistema de controle provê ao gerador de código PN do buscador 136 a identidade do usuário para o qual os códigos PN devem ser gerados. A medida que cada 20 nova leva de chips de amostras é recebida, o buscador recupera amostras da RAM de armazenamento circular começando por, ou contendo, as localizações de endereçamento provenientes do sistema de controle 110 e 25 aplica os códigos PN provenientes do gerador de código PN do buscador 136.

Em uma modalidade da invenção, o sistema de controle 110 considera dois fatores ao calcular quais sinais de link reverso buscar em qualquer momento, apesar de que fatores adicionais podem também ser considerados. Em 30 primeiro lugar, o sistema de controle 110 determina se o grupo de controle de potência de um sinal específico de link reverso está no grupo "relevante". Isto é, o sistema de controle 110 determina se o grupo de controle de potência atual seria transmitido para um quadro de um 35 oitavo de taxa. Caso assim seja, ele pode estar certo de

que o sinal de link reverso está sendo transmitido e recebido naquele momento, independente de qual a taxa que a unidade móvel escolheu e que portanto está disponível para detecção. Na modalidade preferida da invenção, os grupos de 5 controle de potência relevante são conhecidos pela estação base com base em um algoritmo predeterminado apresentado pela norma IS-95. Ademais, um sistema e método para a transmissão de dados de acordo substancialmente com a norma IS-95 está descrito na Patente U.S. Nº 5 659 569 entitulada 10 "DATA BURST RANDOMIZER", em nome da Requerente da presente invenção.

Para aquelas unidades móveis atualmente transmitindo um grupo de controle de potência relevante, o sistema de controle 110 a seguir determina quais sinais de 15 link reverso passaram o mais longo período de tempo sem que fosse realizada uma busca. O sistema de controle 110 determina também o número de buscas que podem ser realizadas dada a capacidade do buscador 130 e requisita buscas para tantos dentre os sinais do conjunto de sinais 20 de link reverso que ficaram mais tempo sem uma busca até a capacidade disponível. Adicionalmente, o sistema de controle 110 requisita que sejam realizadas buscas quanto a transmissões de canais de acesso durante cada grupo de controle de potência, sobre os quais são realizadas 25 requisições para início de comunicações. O canal de acesso é simplesmente o sinal de link reverso normal gerado com um código longo de acesso publicamente conhecido que é o mesmo para todas as unidades móveis 10, em lugar do código de usuário privado (PNU) gerado com a máscara de usuário.

30 A Figura 13 é um fluxograma das etapas realizadas durante uma busca de acordo com uma modalidade da invenção. A busca se inicia na etapa 250 e na etapa 252 as unidades móveis 10 sendo recebidas durante um grupo de controle de potência relevante são identificadas nos sinais relevantes. 35 Na etapa 254 os sinais relevantes são classificados de

acordo com o tempo decorrido desde que a última busca foi realizada para aquele sinal e na etapa 256 são requisitadas buscas para um conjunto de sinais relevantes para os quais o maior intervalo de tempo decorreu desde a última busca 5 até a capacidade máxima do buscador. Uma vez que as buscas tenham sido requisitadas, o tempo decorrido desde que uma última busca foi realizada para cada sinal de link reverso é atualizado e a busca termina na etapa 258. Na modalidade preferida da invenção, são realizadas buscas repetidamente 10 durante a operação normal de uma forma constante.

A Figura 14 é um diagrama de blocos de uma unidade de seguimento do tempo 119 quando configurada de acordo com uma modalidade da invenção. FIFO de retardo/demux 550 recebe dados desespalhados adiantados e atrasados 15 provenientes do demodulador 112 e armazena até seis diferentes ocorrências (ramos) do mesmo sinal de link reverso nos registradores F1 a F6 no interior do FIFO retardo/demux 550. Caso menos de seis multipercursos estejam sendo demoduladas, todos os registradores F1 a F6 20 não conterão dados. As porções pares e ímpares tanto dos dados adiantados como dos atrasados são demultiplexadas em fluxos de dados únicos para cada ramo e os fluxos demultiplexados são alimentados aos circuitos de descobertura 552. Os circuitos de descobertura 552 também 25 recebem o índice Walsh do símbolo Walsh selecionado.

Quando a utilização do índice Walsh se torna disponível, os circuitos de descobertura 552 começam a descobrir, ou demodular, em série, os dados desespalhados adiantados e atrasados armazenados nos registradores F1 a 30 F6 que contêm dados com o símbolo Walsh que corresponde ao índice Walsh, proporcionando a demodulação em fase e em quadratura, adiantada e atrasada para cada ramo. Os dados de demodulação em fase e em quadratura, adiantada e atrasada para cada ramo são alimentados aos circuitos de 35 produto escalar I e Q 554 que geram o produto escalar de

computação de magnitude dos dados em fase e em quadratura proporcionando valores de energia adiantados e atrasados para cada ramo. Os circuitos comparadores 508 indicam se o processo adiantado ou atrasado para cada ramo produziu o 5 nível de energia mais alto e repassam tal indicação para o sistema de controle 110.

O sistema de controle 110 responde aos dados de indicação a partir dos circuitos de comparação 508 ao incrementar ou decrementar um armazenador de rastreamento 10 de tempo residente pelo deslocamento do ramo associado e portanto contribuindo para a duração de 1/2.000 de um chip de código de espalhamento para cada operação de demodulação e avançando ou retardando o processamento do ramo associado quando o valor no armazenador de rastreamento de tempo se 15 modifica em um oitavo da duração de um chip de espalhamento, tal como foi acima descrito. Como deve estar claro, os ramos são processados separadamente pois o deslocamento para cada ramo muda independentemente. No entanto, ao retardar o processamento de cada ramo enquanto 20 os vetores de correlação em tempo real podem ser combinados, o símbolo Walsh mais provável pode ser selecionado usando-se a energia proveniente de todos os ramos, dessa forma aumentando a probabilidade de uma seleção correta.

25 Dessa forma, foram descritos um sistema e um método para o processamento de uma pluralidade de sinais, de preferência sinais CDMA, que podem ser implementados em um único circuito integrado, ou em um número reduzido de circuitos integrados. A descrição acima das modalidades 30 preferidas é fornecida para permitir que os técnicos na área efetivem ou façam uso da presente invenção. As diferentes modificações dessas modalidades ficarão prontamente claras para os técnicos na área e os princípios genéricos aqui definidos podem ser aplicados a outras 35 modalidades sem o uso das faculdades inventivas. Dessa

forma, a presente invenção não deve ser limitada às modalidades aqui apresentadas, devendo receber o escopo mais amplo, consistente com os princípios e características novas aqui descritos.

## REIVINDICAÇÕES

1. Sistema (104) para processar um conjunto de sinais de link reverso provenientes de um conjunto de unidades móveis:

5 uma memória de entrada de antena (106) para armazenar amostras digitais de energia de rádio frequência;

um demodulador (112) para demodular as amostras digitais em um primeiro conjunto de deslocamentos;

10 um buscador (130) para demodular as amostras digitais em um segundo conjunto de deslocamentos de tempo;

caracterizado pelo fato de que as amostras digitais de energia de rádio frequência são recebidas provenientes de um conjunto de unidades móveis (10);

o demodulador (12) é adaptado para demodular as amostras digitais no primeiro conjunto de deslocamentos de tempo com o qual os sinais de link reverso foram detectados; e

o buscador (130) é adaptado para demodular as amostras digitais no segundo conjunto de deslocamentos de tempo utilizando um conjunto de códigos de espalhamento para uma unidade móvel particular para determinar se um sinal de link reverso está sendo recebido proveniente de tal unidade móvel naquele momento.

2. Sistema, de acordo com a reivindicação 1,

25 caracterizado pelo fato de que compreende adicionalmente:

um sistema de controle (110) para especificar o primeiro conjunto de deslocamentos de tempo e o segundo conjunto de deslocamentos de tempo, em que o demodulador (112) serve adicionalmente para:

30 recuperar um primeiro conjunto de amostras a partir da memória de entrada de antena (106); e

demodular o primeiro conjunto de amostras com um primeiro código PN aplicado em um deslocamento proveniente do primeiro conjunto de deslocamentos.

3. Sistema, de acordo com a reivindicação 2, caracterizado pelo fato de que o buscador (130) serve adicionalmente para:

recuperar um segundo conjunto de amostras a 5 partir da memória de entrada de antena (106); e

demodular o segundo conjunto de amostras com um segundo código PN aplicado com um deslocamento a partir do segundo conjunto de deslocamentos.

4. Sistema, de acordo com a reivindicação 1, 10 caracterizado pelo fato de que o segundo conjunto de deslocamentos muda mais rapidamente que o primeiro conjunto de deslocamentos.

5. Sistema, de acordo com a reivindicação 1, caracterizado pelo fato de que o primeiro conjunto de 15 deslocamentos possui menos membros que o segundo conjunto de deslocamentos.

6. Sistema, de acordo com a reivindicação 1, caracterizado pelo fato de que compreende adicionalmente:

um gerador de código PN demodulador (114) para 20 gerar um primeiro conjunto de códigos PN para demodular as amostras digitais no primeiro conjunto de deslocamentos; e

um gerador de código PN buscador (136) para gerar um segundo conjunto de códigos PN para demodular as 25 amostras digitais no segundo conjunto de deslocamentos.

7. Sistema, de acordo com a reivindicação 1, caracterizado pelo fato de que a memória de entrada de antena (106) armazena as amostras digitais em um arranjo de fila circular.

8. Sistema, de acordo com a reivindicação 1, 30 caracterizado pelo fato de que a memória de entrada de antena (106) armazena aproximadamente quatro símbolos Walsh relevantes de amostras digitais.

9. Sistema, de acordo com a reivindicação 1, caracterizado pelo fato de que compreende adicionalmente:

uma unidade de rastreamento de tempo (119) para indicar se um deslocamento de tempo no primeiro conjunto de deslocamentos deve ser avançado ou retardado.

10. Sistema, de acordo com a reivindicação 2,

5 caracterizado pelo fato de que o sistema de controle (110) serve adicionalmente para determinar sinais CDMA das unidades móveis (10) que passaram um período de tempo mais longo sem uma busca e para selecionar os sinais CDMA para busca.

10 11. Método para processar um conjunto de sinais de link reverso recebidos provenientes de um conjunto de unidades móveis, compreendendo as etapas de:

armazenar amostras digitais de energia de rádio frequência em uma memória de entrada de antena (106);

15 demodular as amostras digitais em um primeiro conjunto de deslocamentos de tempo;

demodular as amostras digitais em um segundo conjunto de deslocamentos de tempo;

caracterizado pelo fato de que:

20 armazenar as amostras digitais compreende armazenar amostras digitais de energia de rádio frequência provenientes de uma pluralidade de unidades móveis (10) em uma memória de entrada de antena (106);

25 demodular as amostras digitais em um primeiro conjunto de deslocamentos de tempo compreende demodular as amostras digitais em um conjunto de deslocamentos de tempo para o qual sinais de link reverso foram detectados; e

30 demodular as amostras digitais em um segundo conjunto de deslocamentos de tempo compreende demodular as amostras digitais em um conjunto de deslocamentos de tempo utilizando um conjunto de códigos de espalhamento para uma unidade móvel particular para determinar se um sinal de link reverso está sendo recebido proveniente de tal unidade móvel naquele momento.

12. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que compreende adicionalmente as etapas de:

5 recuperar um primeiro conjunto de amostras a partir da memória de entrada de antena (106); e

demodular o primeiro conjunto de amostras com um primeiro código PN aplicado em um deslocamento proveniente do primeiro conjunto de deslocamentos.

13. Método, de acordo com a reivindicação 12, caracterizado pelo fato de que compreende adicionalmente as etapas de:

recuperar um segundo conjunto de amostras a partir da memória de entrada de antena (106); e

15 demodular o segundo conjunto de amostras com um segundo código PN aplicado com um deslocamento proveniente do segundo conjunto de deslocamentos.

14. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que o segundo conjunto de deslocamentos muda mais rapidamente que o primeiro conjunto de deslocamentos.

15. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que o primeiro conjunto de deslocamentos possui menos membros que o segundo conjunto de deslocamentos.

25 16. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que compreende adicionalmente as etapas de:

30 gerar um primeiro conjunto de códigos PN para demodular as amostras digitais no primeiro conjunto de deslocamentos; e

gerar um segundo conjunto de códigos PN para demodular as amostras digitais no segundo conjunto de deslocamentos.

17. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que as amostras digitais são armazenadas em um arranjo de fila circular.

18. Método, de acordo com a reivindicação 11, 5 caracterizado pelo fato de aproximadamente quatro símbolos Walsh relevantes para amostras digitais são armazenados.

19. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que compreende adicionalmente a etapa de indicar se um deslocamento de tempo no primeiro 10 conjunto de deslocamentos deve ser avançado ou retardado.

20. Método, de acordo com a reivindicação 11, caracterizado pelo fato de que compreende adicionalmente as etapas de:

determinar sinais CDMA provenientes de unidades 15 móveis (10) que passaram um período de tempo mais longo sem uma busca; e

selecionar os sinais CDMA para busca.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

## BANCO FHT DEMOD

DA SAÍDA EM TEMPO

REAL

FIG. 6

FIG. 8

FIG. 9

FIG. 11

FIG. 14

## RESUMO

“SISTEMA E MÉTODO PARA PROCESSAR UM CONJUNTO DE SINAIS DE

LINK REVERSO PROVENIENTES DE UM CONJUNTO DE UNIDADES

MÓVEIS”

5 São descritos um sistema e um método para realizar processamento de recepção digital para múltiplos sinais recebidos através da mesma banda de RF. Em uma modalidade preferida da invenção, amostras digitais de RF são armazenadas em uma fila que é acessada por um buscador 10 (130) e um demodulador (112). O buscador (130) e o demodulador (112) estão de preferência localizados no mesmo circuito integrado juntamente com a fila. O demodulador (112) demodula um conjunto de sinais de link reverso armazenado dentro da fila, em que cada sinal de link 15 reverso é recebido com um deslocamento de tempo específico e processado usando-se um código de canal específico. O buscador (130) periodicamente busca sinais de link reverso que não estão sendo processados pelo demodulador (112) e requisições de acesso transmitidas através do canal de 20 acesso. O buscador (130) busca de preferência durante os grupos de controle de potência relevantes de cada sinal de link reverso, o que corresponde a dois dos dezesseis grupos de controle de potência transmitidos durante um quadro de um oitavo de taxa.